半導体装置の製造方法

【課題】貫通電極の形成時スループットやコスト悪化を回避する。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSI(Large Scale Integration)は、演算処理用のロジック部や、データを記録す

るメモリ部のように、複数のチップ(モジュール)で構成されることがある。さらに、チ

ップ間の電気的な接続には、細い金線を利用したワイヤ・ボンディングが用いられている

。

【0003】

ここで、近年では、LSIの小型化や高性能化のために、回路パターンの微細化や高集

積化が図られている。ところが、回路パターンを微細化したり、高集積化したりすると、

信号伝播速度の遅延や、発熱を伴うリーク電流が増加し易くなる。さらに、従来のLSI

でチップ間の接続に使われる細線のワイヤは、抵抗値が高くなり易いので、配線容量の増

加に伴う信号遅延が生じる可能性があった。また、ワイヤ・ボンディングは、ワイヤを引

き回す空間が必要になるので、LSIをさらに小型化することは困難であった。

【0004】

そこで、近年では、配線を微細化させる代わりに、又はこれに加えて、LSIを構成す

る複数のチップ間の信号の授受を高速化することでLSIの性能を向上させることが図ら

れている。その一例としては、ワイヤ・ボンディングの代替技術として、シリコン貫通電

極(Through Silicon Via、TSV)と呼ばれるチップ間接合構造がある。シリコン貫通

電極は、チップを貫通するビアを用いて形成されたチップ間接合用の配線構造体であり、

シリコン貫通電極を縦方向のチップ集積に用いれば、より短い長さでチップ同士を接合で

きるので、信号授受の高速化や電力ロスを軽減できる。さらに、ワイヤ・ボンディングを

用いてチップを3次元実装する場合に比べて、省スペース化が図れ、LSIを小型化させ

易くなる。

【0005】

ここで、従来のシリコン貫通電極の製造方法の一例について説明する。最初に、素子形

成後にシリコン基板の上方に窒化シリコン膜(以下、SiN)などからなる絶縁膜をCVD

(Chemical Vapor Deposition)法によって形成する。この後、レジストマスクを用いた

異方性ドライエッチングによってシリコン基板にビアホールを形成する。続いて、ビアホ

ールの内壁、即ち側壁及び底部を覆うように絶縁膜を形成する。さらに、ビアホールの内

壁にバリアメタル層とシード層を形成し、めっき法によってビアホール内にCu膜を埋め

込む。一般に、電解めっき法で配線溝などにCu膜を埋め込むときには、配線溝の下部か

ら上部にCuの充填が進むような、いわゆるボトム・アップと呼ばれる成長形式が採用さ

れる。従って、シリコン貫通電極の製造工程においても、ボトム・アップ成長が用いるこ

とで、埋め込み欠陥の発生を防止する。

【0006】

この後、CMP(Chemical Mechanical Polishing)法によって表面のCu膜、バリア

メタル層、及び絶縁膜を除去する。さらに、シリコン基板の上方に、ビアホール内のCu

膜に電気的に接続される配線層を形成する。続いて、シリコン基板の裏面側を研磨及びエ

ッチングし、ビアホール内のCu膜を露出させる。これによって、シリコン基板を貫通す

るビアホールにCu膜が埋め込まれたシリコン貫通電極が形成される。

【0007】

また、貫通電極を形成する別の方法としては、例えば、ガラスエポキシ製の基板に貫通

電極を形成するケースがある。このケースでは、ビアホールを形成した基板の上に絶縁層

を形成し、絶縁層をパターニングしてビアホールに連結される配線溝を形成する。ビアホ

ールの内壁と絶縁層の全面に無電解銅めっき用の触媒を付着させた後、絶縁層の表面を研

磨し、絶縁層上の触媒を除去し、ビアホールの内壁及び配線溝のみに触媒を残す。この後

、触媒を残された領域に無電解めっき層を形成する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−205990

【特許文献2】特開平8−307057

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、シリコン貫通電極は、配線に比べて容積が大きいので、Cu膜のボトム

・アップ成長に多くの時間が必要である。このため、ビアホール内にCu膜が充填される

までの間にシリコン基板の上方に余分なCu膜が厚く堆積する。このように厚く堆積した

Cu膜は、高ストレスになり易いので、Cu膜の剥がれや、シリコン基板の反りの原因に

なる可能性がある。さらに、余分なCu膜は、CMP法による研磨で除去するが、厚いC

u膜の研磨には時間がかかるので、半導体装置の製造のスループットが低下し、コスト増

大を招く。

この発明は、このような事情に鑑みてなされたものであり、シリコン貫通電極の形成時

のスループットやコスト悪化を回避することを目的とする。

【課題を解決するための手段】

【0010】

実施形態の一観点によれば、基板にホールを形成する工程と、前記基板の上方に形成し

た絶縁膜に、前記ホールから前記基板の周辺部分に至る溝を複数形成する工程と、前記ホ

ールの内壁及び前記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と、前記ホ

ール内及び前記溝内以外の前記シード層を研磨によって除去する工程と、前記基板の周辺

部分の前記溝に形成した前記シード層から、前記ホール内の前記シード層に通電し、前記

ホール内に導電膜を成長させる工程と、前記基板を薄化して前記ビアホールの底部の前記

導電膜を露出させる工程と、を含むことを特徴とする半導体装置の製造方法が提供される

。

【発明の効果】

【0011】

貫通電極のホール内に導電膜を形成するときに、シード層が形成された領域のみに導電

膜を成長させることができるので、表面層の全面に導電膜を成長させた場合に比べて導電

膜に起因するストレスや基板の反りを防止できる。

【図面の簡単な説明】

【0012】

【図1A】図1Aは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図1M】図1Mは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その13)である。

【図1N】図1Nは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その14)である。

【図1O】図1Oは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その15)である。

【図1P】図1Pは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その16)である。

【図1Q】図1Qは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その17)である。

【図1R】図1Rは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その18)である。

【図1S】図1Sは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その19)である。

【図1T】図1Tは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その20)である。

【図2】図2は、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、(a)はレジスト膜の開口部のレイアウトを示す平面図であり、(b)はエッジ部分を拡大した平面図である。

【図3】図3は、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、(a)は溝のレイアウトを示す平面図であり、(b)はエッジ部分を拡大した平面図である。

【図4A】図4Aは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、チップ領域のホールと溝のレイアウトを示す平面図である。

【図4B】図4Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、図4Aの領域Aの拡大図である。

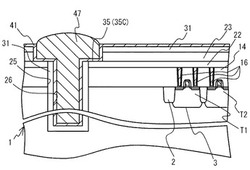

【図5A】図5Aは、本発明の実施の形態に係る半導体装置の製造工程に使用される電解めっき装置の一例を示す概略図である。

【図5B】図5Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、図5Aの領域Bの拡大図である。

【図6】図6は、本発明の実施の形態の変形例に係る半導体装置の製造工程の一例を示し、チップ領域のホールと溝のレイアウトを示す平面図である。

【発明を実施するための形態】

【0013】

発明の目的及び利点は、請求の範囲に具体的に記載された構成要素及び組み合わせによ

って実現され達成される。

前述の一般的な説明及び以下の詳細な説明は、典型例及び説明のためのものであって、

本発明を限定するためのものではない。

【0014】

まず、図1Aに示す断面構造を得るまでの工程について説明する。

最初に、n型又はp型のシリコン(半導体)基板1の一方の面(表面)を例えば、ST

I(Shallow Trench Isolation)により素子分離絶縁膜2を形成して、活性領域を画定す

る。

【0015】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入し

てウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、

シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表

面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6n

m〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合につい

て説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0016】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて10

0nm〜200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチン

グ技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を

形成する。

【0017】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、ゲート電極6の横

のpウェル3にn型不純物としてリンを導入する。これにより、第1、第2ソース/ドレ

インエクステンション8が形成される。第1、第2ソース/ドレインエクステンション8

は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン

基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて100nm

〜200nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッ

チバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0018】

続いて、絶縁性サイドウォール10とゲート電極6をマスクとして用い、シリコン基板

1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6

の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡

散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0019】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高

融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これに

より、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等

の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。

この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えばウェ

ットエッチングにより除去する。これにより、ソース/ドレイン拡散層11上に、例えば

コバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲー

ト電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される

。

【0020】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極

6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT

1,T2が形成される。

【0021】

さらに、シリコン基板1の上側の全面に、コンタクトビア層間絶縁膜14として酸化シ

リコン(SiO2)膜をTEOS(Tetra Ethoxy Silane)ガスを使用するプラズマCVD

法により、約300nmの厚さに形成する。

【0022】

続いて、コンタクトビア層間絶縁膜14とをエッチングして、コンタクトビア15を形

成する。コンタクトビア15の径は、例えば0.08μm〜0.15μmとし、ソース/

ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。

【0023】

そして、コンタクトビア15を用いてソース/ドレイン電極12Aに電気的に接続され

る導電性プラグ16を形成する。具体的には、コンタクトビア15の内面に厚さが5nm

〜15nmのTi膜と、厚さが5nm〜15nmのTiN膜とを順番にスパッタリング法

等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着

膜上にW膜をCVD法により成長させる。この膜厚は、コンタクトビア層間絶縁膜14上

で例えば200nm〜300nmに達する厚さとする。これにより、W膜でコンタクトビ

ア15の空隙が埋まる。この後、コンタクトビア層間絶縁膜14の上面上に成長した余分

なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトビア15に、導電性

プラグ16が形成される。

【0024】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

コンタクトビア層間絶縁膜14上の全面に、絶縁膜22を形成する。絶縁膜22は、例

えばCVD法によりシリコンカーバイド系の膜で、その厚さは例えば100nmとする。

その上に、絶縁膜23として、例えば、TEOSガスを用いたプラズマCVD法によって

形成されたSiO2膜を600nm形成する。さらに、絶縁膜23の上にフォトレジスト

層24を例えば3μmの厚さにスピンコート法によって形成し、リソグラフィ法を用いて

貫通電極用のパターンを焼き付ける。これによって、素子の形成領域の外側でフォトレジ

スト膜24に開口部24Aが形成される。

【0025】

続いて、図1Cに示す断面構造を得るまでの工程について説明する。

フォトレジスト膜24をマスクにした異方性ドライエッチングによって、絶縁膜22,

23、コンタクトビア層間絶縁膜14、及びシリコン基板1をエッチングして貫通電極用

のビアホール25(第1のホール)を形成する。絶縁膜22、コンタクトビア層間絶縁膜

14のエッチングガスは、例えばC4F6、O2、Arを使用する。シリコン基板1のエ

ッチングガスは、例えばSF6、C4F8を使用する。ビアホール25は、例えば直径が

1μm〜20μmで深さは50μm以上とする。ここでは、ビアホール25の直径は5μ

m、深さは50μmとした。この後、残存するフォトレジスト膜24は、アッシングによ

って除去する。

【0026】

続いて、図1Dに示すように、ビアホール25内に側壁保護膜31を例えばCVD法に

よって200nmの厚さに形成する。これによって、シリコン基板1のビアホール25内

にホール26(第2のホール)が形成される。ここで、側壁保護膜31は、ビアホール2

5を形成するドライエッチング時に、シリコン基板1のエッチングと同時に形成しても良

い。

【0027】

さらに、図1Eに示すように、ホール26の上を含む全面に例えば、i線レジスト膜3

2を2μmの厚さにスピンコート法を用いて形成する。i線レジスト膜32を露光・現像

して複数の開口部32Aを形成する。開口部32Aは、ホール26の上方を含むライン形

状に形成される。開口部32Aの幅は、ホール26の幅より大きく、1つの開口部32A

には、複数のホール26を通るように形成される。

【0028】

図2に一例を示すように、レジスト膜32には、複数の開口部32A,32B,32C

が形成される。図2(a)に示すように、開口部32Aは、各チップ領域40内に複数形

成されている。各開口部32Aは、チップ領域40の外周に平行な複数のラインになって

おり、チップ領域40の外側に形成された開口部32Bに接続されている。開口部32B

は、チップ領域40外に、各チップ領域40を囲むように格子状に形成されている。さら

に、開口部32Bは、シリコン基板1のエッジ部分に形成された開口部32Cに接続され

ている。開口部32Cは、エッジ部分に沿って形成され、リング状に配置されている。図

2(b)に一部を拡大して示すように、開口部32Cは、格子状のラインになっている。

【0029】

次に、図1Fに示す断面構造を得るまでの工程について説明する。

まず、i線レジスト膜32を用いて側壁保護膜31、絶縁膜22,23をドライエッチ

ングして溝35を形成する。エッチングガスには、例えば、CF4やCHF3のフッ素系

ガスが用いられる。この後、ダウンフローのアッシング装置(不図示)を用いて、残存す

るi線レジスト膜32を除去する。i線レジスト膜32の除去は、SPM(Sulfuric aci

d Hydrogen Peroxide Mixture:硫酸過水)による溶解除去を用いても良い。

【0030】

ここで、図1(F)と、図3から図4Bを主に参照して、シリコン基板1の上方に形成

される溝35の配置と形状の一例について説明する。

図3(a)に示すように、溝35は、シリコン基板1のエッジ部分に形成される第1の

溝35Aと、チップ領域40を区画するスクライブライン領域上の第2の溝35Bと、各

チップ領域40内の第3の溝35Cとを有する。第3の溝35Cは、図1Fの溝35に相

当する。

【0031】

図3(b)にシリコン基板1のエッジ部分を拡大して示すように、第1の溝35Aは、

シリコン基板1のエッジ部分から1mm〜2mmの領域に格子状に形成されている。各溝

35Aの幅は、100μm〜300μmの幅で、配置間隔は100μm以下である。第1

の溝35Aの形状及び配置は、図2(b)に示すレジスト膜32の開口部32Cと略一致

する。これらの第1の溝35Aは、めっき装置のコンタクトピンと電気的に接続するため

に形成されている。

【0032】

また、図3(a)に示すように、第2の溝35Bは、チップ領域40を囲むように格子

状に形成されており、その線幅は、例えば、100μm〜300μmで深さは例えば0.

8μmである。図3(b)に示すように、第2の溝35Bは、第1の溝35Aに接続され

ている。さらに、図3(a)に示すように、第2の溝35Bは、複数の第3の溝35Cに

接続されている。従って、第2の溝35Bは、第1の溝35Aと第3の溝35Cを連結さ

せる役割を担う。このような第2の溝35Bは、形状及び配置は図2(b)に示すレジス

ト膜24の開口部24Bと略一致しており、スクライブライン領域に形成されることで、

広い断面積を確保している。

【0033】

さらに、図3(a)と、図4Aの拡大図に示すように、第3の溝35Cは、複数のホー

ル26の中心を通るラインとして形成される。ここで、チップ領域40内には、ホール2

6がチップ領域40の外周に沿って2列ずつ形成されている。これに従って、第3の溝3

5Cはチップ領域40の外周に沿って2列ずつ形成される。各第3の溝35Cは、チップ

領域40を横断又は縦断している。図4と、図4Aの領域Aの拡大図である図4Bに示す

ように、第3の溝35Cのそれぞれの端部は、第2の溝35Bに接続されている。第3の

溝35Cの幅は、ビアホール25の径より大きくて10μm〜100μmで、深さは0.

8μmである。このような第3の溝35Cの形状及び配置は、図2(b)に示すレジスト

膜32の開口部32Aと略一致する。第3の溝35Cの中心と、ホール26の中心は、一

致させても良いし、一方を他方に対してオフセットさせても良い。

【0034】

次に、図1Gに示す断面構造を得るまでの工程について説明する。

ホール26の内面及び溝35を含む側壁保護膜31の全面に、バリアメタル層41とし

て、例えばTa化合物を200nmの厚さにPVD法を用いて形成する。バリアメタル層

41には、Ti系化合物を用いても良い。また、バリアメタル層41の形成前に、還元性

ガス(H2、NH3など)を導入しながら150〜350℃で1〜5分間、熱処理して基

板表面の吸着水分や異物を除去しても良い。熱処理の代わりに、Arイオンを用いて膜表

面を物理的にエッチングしても良い。この後、バリアメタル層41の上に、シード層42

として、例えばCuを800nmの厚さにPVD法を用いて形成する。

【0035】

ここで、図1G(a)に示すように、ホール26の形成領域では、第3の溝35のホー

ル26の入り口部分が開口している。また、図1G(b)に示すように、チップ領域40

内でホール26が形成されていない領域で、第3の溝35Cは、バリアメタル層41及び

シード層42で殆ど埋められるが一部に凹部43が形成される。また、図1G(c)に示

すように、チップ領域40の外側の領域では、第2の溝35Bは、バリアメタル層41及

びシード層42で殆ど埋められるが、中央部分に凹部44が形成される。凹部44は、第

3の溝35Cの凹部43より大きい。これは、第2の溝35Bの幅が、第3の溝35Cよ

り広いためである。同様に、第1の溝35Aにおいても、凹部44が形成される。ここで

、溝35の幅とバリアメタル層41及びシード層42の膜厚によっては、凹部43,44

が形成されないこともある。

【0036】

続いて、図1Hに示すように、シード層42の全面にレジスト膜45をスピンコート法

によって形成する。図1H(a)に示すように、ホール26の入り口は、レジスト材料が

入り込むことでキャップされる。レジスト膜45には、例えば、ノボラック樹脂系のi線

レジストを用いる。図1H(b)に示すように、チップ領域40内でホール26が形成さ

れていない領域においては、凹部43を含むシード層42の全面がレジスト膜45で覆わ

れる。同様に、図1H(c)に示すように、第1の溝35A及び第2の溝35Bの形成領

域においても、凹部44を含むシード層42の全面がレジスト膜45で覆われる。

【0037】

さらに、図1Iに示すように、溝35内と、ホール26の内壁を除いてレジスト膜45

及びシード層42をCMP法によって除去し、最表面にバリアメタル層41を露出させる

。ここでの研磨工程は、ホール26及び溝35以外の表面のシード層42を除去するだけ

なので、短時間かつ簡単に終了する。

【0038】

図1I(a)に示すように、ホール26の入り口は、レジスト膜45が埋め込まれたま

まになるので、ホール26の内面は研磨剤などから保護される。ホール26の保護膜は、

レジスト膜45の代わりに、SOG(Spin On Glass)塗布膜を用いても良い。また、C

MP法による研磨の代わりにウェットエッチング法を用いても良い。その場合、エッチン

グ液には、フッ酸過水溶液、硫酸過水溶液、アンモニア過水溶液を用いる。この後、ホー

ル26内の保護膜を有機溶剤例えば、NMP(N-メチルピロドリン)で除去する。

【0039】

ここで、図1I(b)に示すように、ホール26が形成されていない領域の第3の溝3

5Cにおいても、CMP法による研磨でシード層42が露出する。バリアメタル層41及

びシード層42によって形成される凹部43と、凹部43を埋めていたレジスト膜45は

、研磨によって除去される。第3の溝35Cの断面積は、シード層42に電流を流したと

きの電流損失を無視でき、ホール26の電解めっきに十分な電流を流せる大きさを有する

。

【0040】

同様に、図1I(c)に示すように、第1の溝35A及び第2の溝35BにおいてもC

MP法による研磨でシード層42が露出する。第1の溝35A及び第2の溝35Bの断面

積は、第3の溝35Cのシード層42の断面積より大きい。これには、複数の第3の溝3

5のそれぞれに確実に電流を供給するためである。

【0041】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

最初に、ホール26の入り口に充填されているレジスト膜45をアッシング又は薬液処

理によって除去する。続いて、電解めっき法を用いてホール26内にCu膜47を充填す

る。

【0042】

ここで、電解めっきには、図5A及び図5Bに一例を示すような、めっき装置51を使

用する。

図5Aに全体構成の概略を示すように、めっき装置51は、硫酸銅めっき液を貯留させ

ためっき槽52を有する。硫酸銅めっき液は、H2SO4を10〜200g/l、Cuを

20〜50g/l、HClを20〜80mg/lを混合し、添加剤として硫黄系有機化合

物である促進剤と、ポリエチレン系の非イオン性界面活性剤等の抑制剤を100〜500

mg/l、添加している。めっき槽52は、硫酸銅めっき液等を不図示のポンプを用いて

5l/min〜20l/minの速度で循環させる。シリコン基板1は、回転可能な基板

ホルダ53のクランプ54にホール26の入り口が下向きになるように支持される。

【0043】

図5Aの領域Bを図5Bに拡大して示すように、クランプ54には導電性を有するピン

55が複数取り付けられている。ピン55は、シリコン基板1のエッジ部分の第1の溝3

5Aに電気的に接触させられる。第1の溝35Aが格子状に形成されているので、ピン5

5と確実に電気的に接続される。

【0044】

めっき時には、基板ホルダ53を10rpm〜90rpmで回転させる。基板ホルダ5

3に支持されたシリコン基板1がめっき液中で回転することで、ホール26内に硫酸銅め

っき液が撹拌されながら供給される。シリコン基板1をめっき液に挿入させた後、ピン5

5を通してシリコン基板1に電流を印加し、1mA/cm2〜60mA/cm2の範囲内

で電流を段階的に上昇させ、Cuの電解めっきを行う。

【0045】

ここで、電流は、最初に、図5Bに示すピン55に電気的に接続されている第1の溝3

5A中のシード層42に供給される。電流は、第1の溝35Aのシード層42から、図1

I(c)に示す第2の溝35Bに埋め込まれたシード層42に供給される。さらに、電流

は、第2の溝35B内のシード層42を経て、図1I(b)に示す各チップ領域40内の

第3の溝35C内のシード層42に供給される。図1I(a)に示すように、第3の溝3

5C内のシード層42は、ホール26の内壁のシード層42に電気的に接続されている。

このために、ピン55からシリコン基板1に供給された電流は、溝35内のシード層42

を介して各ホール26内に供給される。この結果、ホール26内でCu膜47が成長する

。Cu膜47は、例えばボトム・アップ成長によって形成される。同様に、シリコン基板

1のエッジ部分から各ホール26に至るまでの電流の経路上においても各溝35の上方に

Cu膜47が成長する。これに対して、溝35以外の表面、即ちバリアメタル層41上に

は、Cu膜は成長しない。これは、バリアメタル層41は、Cuより抵抗が高いためであ

る。

【0046】

そして、ホール26内にCu膜47を充填したら、シリコン基板1をめっき槽52から

取り出す。続いて、シリコン基板1を熱処理して、ホール26内のCu膜47を結晶化さ

せ、安定化させる。熱処理の条件は、例えば、H2及びN2を用いた還元性雰囲気、又は

Ar不活性ガス雰囲気で、基板温度は350℃〜450℃とし、処理時間は10分〜60

分とする。ここで、従来のように、シリコン基板1の全面に厚さが5μmを越えるCu膜

47を形成する場合には、Cu膜47の熱膨張に起因するストレスで膜剥がれや、シリコ

ン基板1の反りが生ることがある。これに対して、この実施形態では、シリコン基板1上

の溝35及びホール26内のみにCu膜47が形成される。このために、最表面のCu膜

47のストレスが抑制され、膜剥がれや反りが生じない。

【0047】

この後、図1Kに示すように、CMP法を用いた研磨によって、バリアメタル層41と

、側壁保護膜31と、絶縁膜23を除去する。この際、めっき時の導通用に使用した溝3

5と、溝35上に成長したCu膜も同時に除去される。溝35上のCu膜は、シリコン基

板1の全体の面積に比べて少ないので、短時間で簡単に研磨によって除去される。

【0048】

続いて、図1Lに示す断面構造を得るまでの工程について説明する。

まず、ホール26の表面のCu膜47の酸化防止と、Cu膜47の拡散防止のために保

護膜60を形成する。保護膜60は、例えば、CVD法によって形成したSiC又はSi

Nとする。保護膜60の厚さは、例えば、30nm〜50nmになる。

【0049】

次に、シリコン基板1の上方に、ホール26及びコンタクトビア15に接続する配線層

を形成する。保護膜60を覆うように、層間絶縁膜61を形成する。層間絶縁膜61は、

例えば、プラズマCVD法により成膜したSIOCが用いられる。層間絶縁膜61の厚さ

は、120nm〜250nmとする。

【0050】

続いて、レジスト膜又はハードマスクを使用して層間絶縁膜61をドライエッチングし

、配線溝68A,68Bを形成する。配線溝58A,58Bには、バリアメタル層69と

、不図示のシード層とが順番にスパッタ法によって形成される。さらに、めっき法によっ

て配線溝68A,68B中にCu膜71が埋め込まれる。余分なCu膜71及びバリアメ

タル層69は、CMP法によって除去される。これによって、層間絶縁膜61に、配線7

2A,72Bが埋め込まれた第1の配線層73が形成される。配線72Aは、ホール26

内のCu膜47と電気的に接続される。配線72Bは、導電性プラグ16を介してトラン

ジスタT1,T2に電気的に接続される。以降は、同様の処理を繰り返して、必要な層数

の多層配線層80を形成する。

【0051】

次に、図1Mを参照して、シリコン基板1の裏面(他方の面)側の処理について説明す

る。

最初に、シリコン基板1上に形成した多層配線層80の表面をポリイミド膜などの保護

膜81で覆う。さらに、接着剤82を用いてサポート基板(ガラスキャリア)83に保護膜

81を接着する。これによって、シリコン基板1は、表面をフェイスダウンさせた状態で

サポート基板83に固定される。この後、シリコン基板1を裏面側からホール26内のC

u膜47が露出する直前まで研削し、薄化する。

【0052】

続いて、図1Nに示す断面構造を得るまでの工程について説明する。

例えば、異方性ドライエッチングによって、シリコン基板1の裏面をエッチングし、ホ

ール26の底部に形成されていたCu膜47の頭部(Cuポスト)47Aを露出させる。C

uポスト47Aの露出長さは、例えば5μm〜10μmにする。このときのエッチングガ

スには、例えばSF6、C4F8を使用する。

【0053】

次に、シリコン基板1の裏面を保護するために、絶縁膜84を例えばCVD法によって

形成する。絶縁膜84には、例えば、SiCOHなどからなるポーラスシリカ系膜が用い

られ、その厚さは10μm〜15μmとする。ここで、絶縁膜84は、ホール26内に充填した側壁保護膜31と同じ膜であることが望ましい。

【0054】

さらに、図1Oに示す断面構造を得るまでの工程について説明する。

異方性エッチバックによって、絶縁膜84をエッチングする。エッチングは、絶縁膜8

4に対するCu膜47のエッチング選択比が高い条件で行うと良い。エッチング時間の調

整によって、Cuポスト47Aの頭部(頂点)のみCuを露出させることや、Cuポスト4

7Aの頭部(頂点)及び側壁のCuを露出することができる。Cuポスト47Aの側部の側

壁保護膜31は、残ったままでも良い。これによって、貫通電極85が形成される。

【0055】

次に、半導体チップをダイシングして実装するまでの工程について説明する。

まず、図1Pに示す断面構造を得るまでの工程について説明する。シリコン基板1の裏

面上にレジスト膜90を塗布によって形成する。さらに、レジスト膜90を露光及び現像

して複数の貫通電極85のそれぞれの上に開口部90Aを形成する。続いて、電解めっき

法によって開口部90A内に、例えばNi/Auなどの導電性材料を成長させ、バンプ9

1を形成する。バンプ91を形成した後は、レジスト膜90をアッシング等によって除去

する。

【0056】

この後、図1Qに示すように、シリコン基板1を裏返してダイシングテープ92に貼り

付ける。さらに、図1Rに示すように、シリコン基板1から接着剤82を剥がしてサポー

ト基板83を取り除く。さらに、シリコン基板1から保護膜81を除去する。この後、図

1Sに示すように、シリコン基板1をダイシングによって個片化して半導体装置95を複

数形成する。半導体装置95は、半導体素子、多層配線層80、及び複数の貫通電極85

を含んで構成されている。

【0057】

ここで、半導体装置95は、貫通電極85及びバンプ91を利用して3次元実装するこ

とができる。例えば、図1Tに示すように、半導体装置95は、他の半導体装置101の

上に実装される。他の半導体装置101は、半導体回路が形成された配線層102と、配

線層102に電気的に接続された貫通電極85Aを有し、貫通電極85Aにはバンプ91

Aが形成されている。貫通電極85A及びバンプ91Aの形成方法は、半導体装置95の

貫通電極85及びバンプ91と同様である。

【0058】

半導体装置95は、不図示のマウンターなどを用いてピックアップすることでダイシン

グテープ92から取り外される。さらに、バンプ91が他の半導体装置101の貫通電極

85A上に配置されるように位置決めして載置される。この後、例えば、リフロー工程に

よってバンプ91を溶融させ、他の半導体装置101の貫通電極85Aと半導体装置95

の貫通電極85を接合する。これによって、複数の半導体装置95,101が貫通電極8

5,85Aを用いて電気的に接続された電子部品111が形成される。

【0059】

以上、説明したように、この実施の形態では、シリコン基板1の上方に部分的に形成し

たシード層42を利用し、ホール26内にCu膜47をめっき成長させるようにしたので

、ホール26を含む一部の領域のみにCu膜47を成長させることが可能になる。これに

よって、Cu膜47が最表面の全面にわたって厚く成長することが防止され、Cu膜47

が厚く形成されたときに生じるストレスに起因する剥がれや、シリコン基板1の反りを防

止できる。また、余分なCu膜47の量が少なくなるので、CMP法による研磨時間を短

くでき、半導体装置95の製造効率が向上する。さらに、Cu膜47の成長に必要な電流

を低減できる。

【0060】

絶縁膜23,31をエッチングして形成して溝35を形成した後にシード層42を形成

し、溝35以外のシード層42を除去するようにしたので、一部分のみにシード層42を

簡単に形成できる。また、複数のライン状の溝35をシリコン基板1のエッジ部分から、

各チップ領域40内の各ホール26に至るまで形成したので、電解めっき時に外部からの

電流を供給し易い。シリコン基板1のエッジ部分の第1の溝35Aを格子状に形成したの

で、電解めっき装置51の電流供給用のピン55とシード層42を確実に接続できる。1

つの溝35は、他の複数の溝35に接続されているので、電流の供給経路を確実に確保で

き、ホール26内へのCu膜47を確実に埋め込める。第1及び第2の溝35A、35B

は、第3の溝35Cに比べて断面積が大きいので、シード層42を介したホール26内へ

の電流供給を安定して実現できる。

【0061】

ここで、実施形態の変形例として、図6にレイアウトの他の例を示す。

シリコン基板1上のチップ領域40には、ホール26がチップ領域40の両側部と中央

のそれぞれに2列ずつ平行に配列されている。これに伴って、第3の溝35Cは、チップ

領域40の両側部と中央のそれぞれに2本ずつ形成されている。各第3の溝35Cは、チ

ップ領域40の周囲に形成された第2の溝35Bに接続されている。これら溝35Cのサ

イズの下限値は、断面積がめっき工程時の電流損失を無視するのに十分になる大きさであ

る。また、溝35Cのサイズの上限値は、全面にめっきする場合に比べて電流効率的が改

善されるような値である。

【0062】

ここで挙げた全ての例及び条件的表現は、発明者が技術促進に貢献した発明及び概念を

読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例及び条

件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は

本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の

精神及び範囲から逸脱することなく、それに対して種々の変更、置換及び変形を施すこと

ができる。

【0063】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 基板にホールを形成する工程と、前記基板の上方に形成した絶縁膜に、前記

ホールから前記基板の周辺部分に至る溝を複数形成する工程と、前記ホールの内壁及び前

記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と、前記ホール内及び前記溝

内以外の前記シード層を研磨によって除去する工程と、前記基板の周辺部分の前記溝に形

成した前記シード層から、前記ホール内の前記シード層に通電し、前記ホール内に導電膜

を成長させる工程と、前記基板を薄化して前記ビアホールの底部の前記導電膜を露出させ

る工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2) 半導体回路が形成されるチップ領域内において、前記溝を前記ホールの直径

より幅広に形成することを特徴とする付記1に記載の半導体装置の製造方法。

(付記3) 前記基板のエッジ部分には、前記溝が前記エッジの全周にわたって格子状に

形成することを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4) 前記基板上のスクライブライン領域に前記溝を形成する付記2又は付記3に

記載の半導体装置の製造方法。

(付記5) 前記チップ領域内の前記溝の断面積は、前記チップ領域の外側の前記溝の断

面積以下であることを特徴とする付記2乃至付記4のいずれか一項に記載の半導体装置の

製造方法。

(付記6)

1つの前記溝を少なくとも2箇所で他の前記溝に接続させることを特徴とする付記1乃

至付記5のいずれか一項に記載の半導体装置の製造方法。

【符号の説明】

【0064】

1 シリコン基板

23 絶縁膜

26 ホール

35 溝

35A 第1の溝

35B 第2の溝

35C 第3の溝

40 チップ領域

42 シード層

47 Cu膜(導電膜)

95 半導体装置

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSI(Large Scale Integration)は、演算処理用のロジック部や、データを記録す

るメモリ部のように、複数のチップ(モジュール)で構成されることがある。さらに、チ

ップ間の電気的な接続には、細い金線を利用したワイヤ・ボンディングが用いられている

。

【0003】

ここで、近年では、LSIの小型化や高性能化のために、回路パターンの微細化や高集

積化が図られている。ところが、回路パターンを微細化したり、高集積化したりすると、

信号伝播速度の遅延や、発熱を伴うリーク電流が増加し易くなる。さらに、従来のLSI

でチップ間の接続に使われる細線のワイヤは、抵抗値が高くなり易いので、配線容量の増

加に伴う信号遅延が生じる可能性があった。また、ワイヤ・ボンディングは、ワイヤを引

き回す空間が必要になるので、LSIをさらに小型化することは困難であった。

【0004】

そこで、近年では、配線を微細化させる代わりに、又はこれに加えて、LSIを構成す

る複数のチップ間の信号の授受を高速化することでLSIの性能を向上させることが図ら

れている。その一例としては、ワイヤ・ボンディングの代替技術として、シリコン貫通電

極(Through Silicon Via、TSV)と呼ばれるチップ間接合構造がある。シリコン貫通

電極は、チップを貫通するビアを用いて形成されたチップ間接合用の配線構造体であり、

シリコン貫通電極を縦方向のチップ集積に用いれば、より短い長さでチップ同士を接合で

きるので、信号授受の高速化や電力ロスを軽減できる。さらに、ワイヤ・ボンディングを

用いてチップを3次元実装する場合に比べて、省スペース化が図れ、LSIを小型化させ

易くなる。

【0005】

ここで、従来のシリコン貫通電極の製造方法の一例について説明する。最初に、素子形

成後にシリコン基板の上方に窒化シリコン膜(以下、SiN)などからなる絶縁膜をCVD

(Chemical Vapor Deposition)法によって形成する。この後、レジストマスクを用いた

異方性ドライエッチングによってシリコン基板にビアホールを形成する。続いて、ビアホ

ールの内壁、即ち側壁及び底部を覆うように絶縁膜を形成する。さらに、ビアホールの内

壁にバリアメタル層とシード層を形成し、めっき法によってビアホール内にCu膜を埋め

込む。一般に、電解めっき法で配線溝などにCu膜を埋め込むときには、配線溝の下部か

ら上部にCuの充填が進むような、いわゆるボトム・アップと呼ばれる成長形式が採用さ

れる。従って、シリコン貫通電極の製造工程においても、ボトム・アップ成長が用いるこ

とで、埋め込み欠陥の発生を防止する。

【0006】

この後、CMP(Chemical Mechanical Polishing)法によって表面のCu膜、バリア

メタル層、及び絶縁膜を除去する。さらに、シリコン基板の上方に、ビアホール内のCu

膜に電気的に接続される配線層を形成する。続いて、シリコン基板の裏面側を研磨及びエ

ッチングし、ビアホール内のCu膜を露出させる。これによって、シリコン基板を貫通す

るビアホールにCu膜が埋め込まれたシリコン貫通電極が形成される。

【0007】

また、貫通電極を形成する別の方法としては、例えば、ガラスエポキシ製の基板に貫通

電極を形成するケースがある。このケースでは、ビアホールを形成した基板の上に絶縁層

を形成し、絶縁層をパターニングしてビアホールに連結される配線溝を形成する。ビアホ

ールの内壁と絶縁層の全面に無電解銅めっき用の触媒を付着させた後、絶縁層の表面を研

磨し、絶縁層上の触媒を除去し、ビアホールの内壁及び配線溝のみに触媒を残す。この後

、触媒を残された領域に無電解めっき層を形成する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−205990

【特許文献2】特開平8−307057

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、シリコン貫通電極は、配線に比べて容積が大きいので、Cu膜のボトム

・アップ成長に多くの時間が必要である。このため、ビアホール内にCu膜が充填される

までの間にシリコン基板の上方に余分なCu膜が厚く堆積する。このように厚く堆積した

Cu膜は、高ストレスになり易いので、Cu膜の剥がれや、シリコン基板の反りの原因に

なる可能性がある。さらに、余分なCu膜は、CMP法による研磨で除去するが、厚いC

u膜の研磨には時間がかかるので、半導体装置の製造のスループットが低下し、コスト増

大を招く。

この発明は、このような事情に鑑みてなされたものであり、シリコン貫通電極の形成時

のスループットやコスト悪化を回避することを目的とする。

【課題を解決するための手段】

【0010】

実施形態の一観点によれば、基板にホールを形成する工程と、前記基板の上方に形成し

た絶縁膜に、前記ホールから前記基板の周辺部分に至る溝を複数形成する工程と、前記ホ

ールの内壁及び前記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と、前記ホ

ール内及び前記溝内以外の前記シード層を研磨によって除去する工程と、前記基板の周辺

部分の前記溝に形成した前記シード層から、前記ホール内の前記シード層に通電し、前記

ホール内に導電膜を成長させる工程と、前記基板を薄化して前記ビアホールの底部の前記

導電膜を露出させる工程と、を含むことを特徴とする半導体装置の製造方法が提供される

。

【発明の効果】

【0011】

貫通電極のホール内に導電膜を形成するときに、シード層が形成された領域のみに導電

膜を成長させることができるので、表面層の全面に導電膜を成長させた場合に比べて導電

膜に起因するストレスや基板の反りを防止できる。

【図面の簡単な説明】

【0012】

【図1A】図1Aは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図1M】図1Mは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その13)である。

【図1N】図1Nは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その14)である。

【図1O】図1Oは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その15)である。

【図1P】図1Pは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その16)である。

【図1Q】図1Qは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その17)である。

【図1R】図1Rは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その18)である。

【図1S】図1Sは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その19)である。

【図1T】図1Tは、本発明の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その20)である。

【図2】図2は、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、(a)はレジスト膜の開口部のレイアウトを示す平面図であり、(b)はエッジ部分を拡大した平面図である。

【図3】図3は、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、(a)は溝のレイアウトを示す平面図であり、(b)はエッジ部分を拡大した平面図である。

【図4A】図4Aは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、チップ領域のホールと溝のレイアウトを示す平面図である。

【図4B】図4Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、図4Aの領域Aの拡大図である。

【図5A】図5Aは、本発明の実施の形態に係る半導体装置の製造工程に使用される電解めっき装置の一例を示す概略図である。

【図5B】図5Bは、本発明の実施の形態に係る半導体装置の製造工程の一例を示し、図5Aの領域Bの拡大図である。

【図6】図6は、本発明の実施の形態の変形例に係る半導体装置の製造工程の一例を示し、チップ領域のホールと溝のレイアウトを示す平面図である。

【発明を実施するための形態】

【0013】

発明の目的及び利点は、請求の範囲に具体的に記載された構成要素及び組み合わせによ

って実現され達成される。

前述の一般的な説明及び以下の詳細な説明は、典型例及び説明のためのものであって、

本発明を限定するためのものではない。

【0014】

まず、図1Aに示す断面構造を得るまでの工程について説明する。

最初に、n型又はp型のシリコン(半導体)基板1の一方の面(表面)を例えば、ST

I(Shallow Trench Isolation)により素子分離絶縁膜2を形成して、活性領域を画定す

る。

【0015】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入し

てウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、

シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表

面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6n

m〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合につい

て説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0016】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて10

0nm〜200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチン

グ技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を

形成する。

【0017】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、ゲート電極6の横

のpウェル3にn型不純物としてリンを導入する。これにより、第1、第2ソース/ドレ

インエクステンション8が形成される。第1、第2ソース/ドレインエクステンション8

は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン

基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて100nm

〜200nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッ

チバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0018】

続いて、絶縁性サイドウォール10とゲート電極6をマスクとして用い、シリコン基板

1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6

の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡

散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0019】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高

融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これに

より、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等

の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。

この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えばウェ

ットエッチングにより除去する。これにより、ソース/ドレイン拡散層11上に、例えば

コバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲー

ト電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される

。

【0020】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極

6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT

1,T2が形成される。

【0021】

さらに、シリコン基板1の上側の全面に、コンタクトビア層間絶縁膜14として酸化シ

リコン(SiO2)膜をTEOS(Tetra Ethoxy Silane)ガスを使用するプラズマCVD

法により、約300nmの厚さに形成する。

【0022】

続いて、コンタクトビア層間絶縁膜14とをエッチングして、コンタクトビア15を形

成する。コンタクトビア15の径は、例えば0.08μm〜0.15μmとし、ソース/

ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。

【0023】

そして、コンタクトビア15を用いてソース/ドレイン電極12Aに電気的に接続され

る導電性プラグ16を形成する。具体的には、コンタクトビア15の内面に厚さが5nm

〜15nmのTi膜と、厚さが5nm〜15nmのTiN膜とを順番にスパッタリング法

等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着

膜上にW膜をCVD法により成長させる。この膜厚は、コンタクトビア層間絶縁膜14上

で例えば200nm〜300nmに達する厚さとする。これにより、W膜でコンタクトビ

ア15の空隙が埋まる。この後、コンタクトビア層間絶縁膜14の上面上に成長した余分

なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトビア15に、導電性

プラグ16が形成される。

【0024】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

コンタクトビア層間絶縁膜14上の全面に、絶縁膜22を形成する。絶縁膜22は、例

えばCVD法によりシリコンカーバイド系の膜で、その厚さは例えば100nmとする。

その上に、絶縁膜23として、例えば、TEOSガスを用いたプラズマCVD法によって

形成されたSiO2膜を600nm形成する。さらに、絶縁膜23の上にフォトレジスト

層24を例えば3μmの厚さにスピンコート法によって形成し、リソグラフィ法を用いて

貫通電極用のパターンを焼き付ける。これによって、素子の形成領域の外側でフォトレジ

スト膜24に開口部24Aが形成される。

【0025】

続いて、図1Cに示す断面構造を得るまでの工程について説明する。

フォトレジスト膜24をマスクにした異方性ドライエッチングによって、絶縁膜22,

23、コンタクトビア層間絶縁膜14、及びシリコン基板1をエッチングして貫通電極用

のビアホール25(第1のホール)を形成する。絶縁膜22、コンタクトビア層間絶縁膜

14のエッチングガスは、例えばC4F6、O2、Arを使用する。シリコン基板1のエ

ッチングガスは、例えばSF6、C4F8を使用する。ビアホール25は、例えば直径が

1μm〜20μmで深さは50μm以上とする。ここでは、ビアホール25の直径は5μ

m、深さは50μmとした。この後、残存するフォトレジスト膜24は、アッシングによ

って除去する。

【0026】

続いて、図1Dに示すように、ビアホール25内に側壁保護膜31を例えばCVD法に

よって200nmの厚さに形成する。これによって、シリコン基板1のビアホール25内

にホール26(第2のホール)が形成される。ここで、側壁保護膜31は、ビアホール2

5を形成するドライエッチング時に、シリコン基板1のエッチングと同時に形成しても良

い。

【0027】

さらに、図1Eに示すように、ホール26の上を含む全面に例えば、i線レジスト膜3

2を2μmの厚さにスピンコート法を用いて形成する。i線レジスト膜32を露光・現像

して複数の開口部32Aを形成する。開口部32Aは、ホール26の上方を含むライン形

状に形成される。開口部32Aの幅は、ホール26の幅より大きく、1つの開口部32A

には、複数のホール26を通るように形成される。

【0028】

図2に一例を示すように、レジスト膜32には、複数の開口部32A,32B,32C

が形成される。図2(a)に示すように、開口部32Aは、各チップ領域40内に複数形

成されている。各開口部32Aは、チップ領域40の外周に平行な複数のラインになって

おり、チップ領域40の外側に形成された開口部32Bに接続されている。開口部32B

は、チップ領域40外に、各チップ領域40を囲むように格子状に形成されている。さら

に、開口部32Bは、シリコン基板1のエッジ部分に形成された開口部32Cに接続され

ている。開口部32Cは、エッジ部分に沿って形成され、リング状に配置されている。図

2(b)に一部を拡大して示すように、開口部32Cは、格子状のラインになっている。

【0029】

次に、図1Fに示す断面構造を得るまでの工程について説明する。

まず、i線レジスト膜32を用いて側壁保護膜31、絶縁膜22,23をドライエッチ

ングして溝35を形成する。エッチングガスには、例えば、CF4やCHF3のフッ素系

ガスが用いられる。この後、ダウンフローのアッシング装置(不図示)を用いて、残存す

るi線レジスト膜32を除去する。i線レジスト膜32の除去は、SPM(Sulfuric aci

d Hydrogen Peroxide Mixture:硫酸過水)による溶解除去を用いても良い。

【0030】

ここで、図1(F)と、図3から図4Bを主に参照して、シリコン基板1の上方に形成

される溝35の配置と形状の一例について説明する。

図3(a)に示すように、溝35は、シリコン基板1のエッジ部分に形成される第1の

溝35Aと、チップ領域40を区画するスクライブライン領域上の第2の溝35Bと、各

チップ領域40内の第3の溝35Cとを有する。第3の溝35Cは、図1Fの溝35に相

当する。

【0031】

図3(b)にシリコン基板1のエッジ部分を拡大して示すように、第1の溝35Aは、

シリコン基板1のエッジ部分から1mm〜2mmの領域に格子状に形成されている。各溝

35Aの幅は、100μm〜300μmの幅で、配置間隔は100μm以下である。第1

の溝35Aの形状及び配置は、図2(b)に示すレジスト膜32の開口部32Cと略一致

する。これらの第1の溝35Aは、めっき装置のコンタクトピンと電気的に接続するため

に形成されている。

【0032】

また、図3(a)に示すように、第2の溝35Bは、チップ領域40を囲むように格子

状に形成されており、その線幅は、例えば、100μm〜300μmで深さは例えば0.

8μmである。図3(b)に示すように、第2の溝35Bは、第1の溝35Aに接続され

ている。さらに、図3(a)に示すように、第2の溝35Bは、複数の第3の溝35Cに

接続されている。従って、第2の溝35Bは、第1の溝35Aと第3の溝35Cを連結さ

せる役割を担う。このような第2の溝35Bは、形状及び配置は図2(b)に示すレジス

ト膜24の開口部24Bと略一致しており、スクライブライン領域に形成されることで、

広い断面積を確保している。

【0033】

さらに、図3(a)と、図4Aの拡大図に示すように、第3の溝35Cは、複数のホー

ル26の中心を通るラインとして形成される。ここで、チップ領域40内には、ホール2

6がチップ領域40の外周に沿って2列ずつ形成されている。これに従って、第3の溝3

5Cはチップ領域40の外周に沿って2列ずつ形成される。各第3の溝35Cは、チップ

領域40を横断又は縦断している。図4と、図4Aの領域Aの拡大図である図4Bに示す

ように、第3の溝35Cのそれぞれの端部は、第2の溝35Bに接続されている。第3の

溝35Cの幅は、ビアホール25の径より大きくて10μm〜100μmで、深さは0.

8μmである。このような第3の溝35Cの形状及び配置は、図2(b)に示すレジスト

膜32の開口部32Aと略一致する。第3の溝35Cの中心と、ホール26の中心は、一

致させても良いし、一方を他方に対してオフセットさせても良い。

【0034】

次に、図1Gに示す断面構造を得るまでの工程について説明する。

ホール26の内面及び溝35を含む側壁保護膜31の全面に、バリアメタル層41とし

て、例えばTa化合物を200nmの厚さにPVD法を用いて形成する。バリアメタル層

41には、Ti系化合物を用いても良い。また、バリアメタル層41の形成前に、還元性

ガス(H2、NH3など)を導入しながら150〜350℃で1〜5分間、熱処理して基

板表面の吸着水分や異物を除去しても良い。熱処理の代わりに、Arイオンを用いて膜表

面を物理的にエッチングしても良い。この後、バリアメタル層41の上に、シード層42

として、例えばCuを800nmの厚さにPVD法を用いて形成する。

【0035】

ここで、図1G(a)に示すように、ホール26の形成領域では、第3の溝35のホー

ル26の入り口部分が開口している。また、図1G(b)に示すように、チップ領域40

内でホール26が形成されていない領域で、第3の溝35Cは、バリアメタル層41及び

シード層42で殆ど埋められるが一部に凹部43が形成される。また、図1G(c)に示

すように、チップ領域40の外側の領域では、第2の溝35Bは、バリアメタル層41及

びシード層42で殆ど埋められるが、中央部分に凹部44が形成される。凹部44は、第

3の溝35Cの凹部43より大きい。これは、第2の溝35Bの幅が、第3の溝35Cよ

り広いためである。同様に、第1の溝35Aにおいても、凹部44が形成される。ここで

、溝35の幅とバリアメタル層41及びシード層42の膜厚によっては、凹部43,44

が形成されないこともある。

【0036】

続いて、図1Hに示すように、シード層42の全面にレジスト膜45をスピンコート法

によって形成する。図1H(a)に示すように、ホール26の入り口は、レジスト材料が

入り込むことでキャップされる。レジスト膜45には、例えば、ノボラック樹脂系のi線

レジストを用いる。図1H(b)に示すように、チップ領域40内でホール26が形成さ

れていない領域においては、凹部43を含むシード層42の全面がレジスト膜45で覆わ

れる。同様に、図1H(c)に示すように、第1の溝35A及び第2の溝35Bの形成領

域においても、凹部44を含むシード層42の全面がレジスト膜45で覆われる。

【0037】

さらに、図1Iに示すように、溝35内と、ホール26の内壁を除いてレジスト膜45

及びシード層42をCMP法によって除去し、最表面にバリアメタル層41を露出させる

。ここでの研磨工程は、ホール26及び溝35以外の表面のシード層42を除去するだけ

なので、短時間かつ簡単に終了する。

【0038】

図1I(a)に示すように、ホール26の入り口は、レジスト膜45が埋め込まれたま

まになるので、ホール26の内面は研磨剤などから保護される。ホール26の保護膜は、

レジスト膜45の代わりに、SOG(Spin On Glass)塗布膜を用いても良い。また、C

MP法による研磨の代わりにウェットエッチング法を用いても良い。その場合、エッチン

グ液には、フッ酸過水溶液、硫酸過水溶液、アンモニア過水溶液を用いる。この後、ホー

ル26内の保護膜を有機溶剤例えば、NMP(N-メチルピロドリン)で除去する。

【0039】

ここで、図1I(b)に示すように、ホール26が形成されていない領域の第3の溝3

5Cにおいても、CMP法による研磨でシード層42が露出する。バリアメタル層41及

びシード層42によって形成される凹部43と、凹部43を埋めていたレジスト膜45は

、研磨によって除去される。第3の溝35Cの断面積は、シード層42に電流を流したと

きの電流損失を無視でき、ホール26の電解めっきに十分な電流を流せる大きさを有する

。

【0040】

同様に、図1I(c)に示すように、第1の溝35A及び第2の溝35BにおいてもC

MP法による研磨でシード層42が露出する。第1の溝35A及び第2の溝35Bの断面

積は、第3の溝35Cのシード層42の断面積より大きい。これには、複数の第3の溝3

5のそれぞれに確実に電流を供給するためである。

【0041】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

最初に、ホール26の入り口に充填されているレジスト膜45をアッシング又は薬液処

理によって除去する。続いて、電解めっき法を用いてホール26内にCu膜47を充填す

る。

【0042】

ここで、電解めっきには、図5A及び図5Bに一例を示すような、めっき装置51を使

用する。

図5Aに全体構成の概略を示すように、めっき装置51は、硫酸銅めっき液を貯留させ

ためっき槽52を有する。硫酸銅めっき液は、H2SO4を10〜200g/l、Cuを

20〜50g/l、HClを20〜80mg/lを混合し、添加剤として硫黄系有機化合

物である促進剤と、ポリエチレン系の非イオン性界面活性剤等の抑制剤を100〜500

mg/l、添加している。めっき槽52は、硫酸銅めっき液等を不図示のポンプを用いて

5l/min〜20l/minの速度で循環させる。シリコン基板1は、回転可能な基板

ホルダ53のクランプ54にホール26の入り口が下向きになるように支持される。

【0043】

図5Aの領域Bを図5Bに拡大して示すように、クランプ54には導電性を有するピン

55が複数取り付けられている。ピン55は、シリコン基板1のエッジ部分の第1の溝3

5Aに電気的に接触させられる。第1の溝35Aが格子状に形成されているので、ピン5

5と確実に電気的に接続される。

【0044】

めっき時には、基板ホルダ53を10rpm〜90rpmで回転させる。基板ホルダ5

3に支持されたシリコン基板1がめっき液中で回転することで、ホール26内に硫酸銅め

っき液が撹拌されながら供給される。シリコン基板1をめっき液に挿入させた後、ピン5

5を通してシリコン基板1に電流を印加し、1mA/cm2〜60mA/cm2の範囲内

で電流を段階的に上昇させ、Cuの電解めっきを行う。

【0045】

ここで、電流は、最初に、図5Bに示すピン55に電気的に接続されている第1の溝3

5A中のシード層42に供給される。電流は、第1の溝35Aのシード層42から、図1

I(c)に示す第2の溝35Bに埋め込まれたシード層42に供給される。さらに、電流

は、第2の溝35B内のシード層42を経て、図1I(b)に示す各チップ領域40内の

第3の溝35C内のシード層42に供給される。図1I(a)に示すように、第3の溝3

5C内のシード層42は、ホール26の内壁のシード層42に電気的に接続されている。

このために、ピン55からシリコン基板1に供給された電流は、溝35内のシード層42

を介して各ホール26内に供給される。この結果、ホール26内でCu膜47が成長する

。Cu膜47は、例えばボトム・アップ成長によって形成される。同様に、シリコン基板

1のエッジ部分から各ホール26に至るまでの電流の経路上においても各溝35の上方に

Cu膜47が成長する。これに対して、溝35以外の表面、即ちバリアメタル層41上に

は、Cu膜は成長しない。これは、バリアメタル層41は、Cuより抵抗が高いためであ

る。

【0046】

そして、ホール26内にCu膜47を充填したら、シリコン基板1をめっき槽52から

取り出す。続いて、シリコン基板1を熱処理して、ホール26内のCu膜47を結晶化さ

せ、安定化させる。熱処理の条件は、例えば、H2及びN2を用いた還元性雰囲気、又は

Ar不活性ガス雰囲気で、基板温度は350℃〜450℃とし、処理時間は10分〜60

分とする。ここで、従来のように、シリコン基板1の全面に厚さが5μmを越えるCu膜

47を形成する場合には、Cu膜47の熱膨張に起因するストレスで膜剥がれや、シリコ

ン基板1の反りが生ることがある。これに対して、この実施形態では、シリコン基板1上

の溝35及びホール26内のみにCu膜47が形成される。このために、最表面のCu膜

47のストレスが抑制され、膜剥がれや反りが生じない。

【0047】

この後、図1Kに示すように、CMP法を用いた研磨によって、バリアメタル層41と

、側壁保護膜31と、絶縁膜23を除去する。この際、めっき時の導通用に使用した溝3

5と、溝35上に成長したCu膜も同時に除去される。溝35上のCu膜は、シリコン基

板1の全体の面積に比べて少ないので、短時間で簡単に研磨によって除去される。

【0048】

続いて、図1Lに示す断面構造を得るまでの工程について説明する。

まず、ホール26の表面のCu膜47の酸化防止と、Cu膜47の拡散防止のために保

護膜60を形成する。保護膜60は、例えば、CVD法によって形成したSiC又はSi

Nとする。保護膜60の厚さは、例えば、30nm〜50nmになる。

【0049】

次に、シリコン基板1の上方に、ホール26及びコンタクトビア15に接続する配線層

を形成する。保護膜60を覆うように、層間絶縁膜61を形成する。層間絶縁膜61は、

例えば、プラズマCVD法により成膜したSIOCが用いられる。層間絶縁膜61の厚さ

は、120nm〜250nmとする。

【0050】

続いて、レジスト膜又はハードマスクを使用して層間絶縁膜61をドライエッチングし

、配線溝68A,68Bを形成する。配線溝58A,58Bには、バリアメタル層69と

、不図示のシード層とが順番にスパッタ法によって形成される。さらに、めっき法によっ

て配線溝68A,68B中にCu膜71が埋め込まれる。余分なCu膜71及びバリアメ

タル層69は、CMP法によって除去される。これによって、層間絶縁膜61に、配線7

2A,72Bが埋め込まれた第1の配線層73が形成される。配線72Aは、ホール26

内のCu膜47と電気的に接続される。配線72Bは、導電性プラグ16を介してトラン

ジスタT1,T2に電気的に接続される。以降は、同様の処理を繰り返して、必要な層数

の多層配線層80を形成する。

【0051】

次に、図1Mを参照して、シリコン基板1の裏面(他方の面)側の処理について説明す

る。

最初に、シリコン基板1上に形成した多層配線層80の表面をポリイミド膜などの保護

膜81で覆う。さらに、接着剤82を用いてサポート基板(ガラスキャリア)83に保護膜

81を接着する。これによって、シリコン基板1は、表面をフェイスダウンさせた状態で

サポート基板83に固定される。この後、シリコン基板1を裏面側からホール26内のC

u膜47が露出する直前まで研削し、薄化する。

【0052】

続いて、図1Nに示す断面構造を得るまでの工程について説明する。

例えば、異方性ドライエッチングによって、シリコン基板1の裏面をエッチングし、ホ

ール26の底部に形成されていたCu膜47の頭部(Cuポスト)47Aを露出させる。C

uポスト47Aの露出長さは、例えば5μm〜10μmにする。このときのエッチングガ

スには、例えばSF6、C4F8を使用する。

【0053】

次に、シリコン基板1の裏面を保護するために、絶縁膜84を例えばCVD法によって

形成する。絶縁膜84には、例えば、SiCOHなどからなるポーラスシリカ系膜が用い

られ、その厚さは10μm〜15μmとする。ここで、絶縁膜84は、ホール26内に充填した側壁保護膜31と同じ膜であることが望ましい。

【0054】

さらに、図1Oに示す断面構造を得るまでの工程について説明する。

異方性エッチバックによって、絶縁膜84をエッチングする。エッチングは、絶縁膜8

4に対するCu膜47のエッチング選択比が高い条件で行うと良い。エッチング時間の調

整によって、Cuポスト47Aの頭部(頂点)のみCuを露出させることや、Cuポスト4

7Aの頭部(頂点)及び側壁のCuを露出することができる。Cuポスト47Aの側部の側

壁保護膜31は、残ったままでも良い。これによって、貫通電極85が形成される。

【0055】

次に、半導体チップをダイシングして実装するまでの工程について説明する。

まず、図1Pに示す断面構造を得るまでの工程について説明する。シリコン基板1の裏

面上にレジスト膜90を塗布によって形成する。さらに、レジスト膜90を露光及び現像

して複数の貫通電極85のそれぞれの上に開口部90Aを形成する。続いて、電解めっき

法によって開口部90A内に、例えばNi/Auなどの導電性材料を成長させ、バンプ9

1を形成する。バンプ91を形成した後は、レジスト膜90をアッシング等によって除去

する。

【0056】

この後、図1Qに示すように、シリコン基板1を裏返してダイシングテープ92に貼り

付ける。さらに、図1Rに示すように、シリコン基板1から接着剤82を剥がしてサポー

ト基板83を取り除く。さらに、シリコン基板1から保護膜81を除去する。この後、図

1Sに示すように、シリコン基板1をダイシングによって個片化して半導体装置95を複

数形成する。半導体装置95は、半導体素子、多層配線層80、及び複数の貫通電極85

を含んで構成されている。

【0057】

ここで、半導体装置95は、貫通電極85及びバンプ91を利用して3次元実装するこ

とができる。例えば、図1Tに示すように、半導体装置95は、他の半導体装置101の

上に実装される。他の半導体装置101は、半導体回路が形成された配線層102と、配

線層102に電気的に接続された貫通電極85Aを有し、貫通電極85Aにはバンプ91

Aが形成されている。貫通電極85A及びバンプ91Aの形成方法は、半導体装置95の

貫通電極85及びバンプ91と同様である。

【0058】

半導体装置95は、不図示のマウンターなどを用いてピックアップすることでダイシン

グテープ92から取り外される。さらに、バンプ91が他の半導体装置101の貫通電極

85A上に配置されるように位置決めして載置される。この後、例えば、リフロー工程に

よってバンプ91を溶融させ、他の半導体装置101の貫通電極85Aと半導体装置95

の貫通電極85を接合する。これによって、複数の半導体装置95,101が貫通電極8

5,85Aを用いて電気的に接続された電子部品111が形成される。

【0059】

以上、説明したように、この実施の形態では、シリコン基板1の上方に部分的に形成し

たシード層42を利用し、ホール26内にCu膜47をめっき成長させるようにしたので

、ホール26を含む一部の領域のみにCu膜47を成長させることが可能になる。これに

よって、Cu膜47が最表面の全面にわたって厚く成長することが防止され、Cu膜47

が厚く形成されたときに生じるストレスに起因する剥がれや、シリコン基板1の反りを防

止できる。また、余分なCu膜47の量が少なくなるので、CMP法による研磨時間を短

くでき、半導体装置95の製造効率が向上する。さらに、Cu膜47の成長に必要な電流

を低減できる。

【0060】

絶縁膜23,31をエッチングして形成して溝35を形成した後にシード層42を形成

し、溝35以外のシード層42を除去するようにしたので、一部分のみにシード層42を

簡単に形成できる。また、複数のライン状の溝35をシリコン基板1のエッジ部分から、

各チップ領域40内の各ホール26に至るまで形成したので、電解めっき時に外部からの

電流を供給し易い。シリコン基板1のエッジ部分の第1の溝35Aを格子状に形成したの

で、電解めっき装置51の電流供給用のピン55とシード層42を確実に接続できる。1

つの溝35は、他の複数の溝35に接続されているので、電流の供給経路を確実に確保で

き、ホール26内へのCu膜47を確実に埋め込める。第1及び第2の溝35A、35B

は、第3の溝35Cに比べて断面積が大きいので、シード層42を介したホール26内へ

の電流供給を安定して実現できる。

【0061】

ここで、実施形態の変形例として、図6にレイアウトの他の例を示す。

シリコン基板1上のチップ領域40には、ホール26がチップ領域40の両側部と中央

のそれぞれに2列ずつ平行に配列されている。これに伴って、第3の溝35Cは、チップ

領域40の両側部と中央のそれぞれに2本ずつ形成されている。各第3の溝35Cは、チ

ップ領域40の周囲に形成された第2の溝35Bに接続されている。これら溝35Cのサ

イズの下限値は、断面積がめっき工程時の電流損失を無視するのに十分になる大きさであ

る。また、溝35Cのサイズの上限値は、全面にめっきする場合に比べて電流効率的が改

善されるような値である。

【0062】

ここで挙げた全ての例及び条件的表現は、発明者が技術促進に貢献した発明及び概念を

読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例及び条

件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は

本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の

精神及び範囲から逸脱することなく、それに対して種々の変更、置換及び変形を施すこと

ができる。

【0063】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 基板にホールを形成する工程と、前記基板の上方に形成した絶縁膜に、前記

ホールから前記基板の周辺部分に至る溝を複数形成する工程と、前記ホールの内壁及び前

記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と、前記ホール内及び前記溝

内以外の前記シード層を研磨によって除去する工程と、前記基板の周辺部分の前記溝に形

成した前記シード層から、前記ホール内の前記シード層に通電し、前記ホール内に導電膜

を成長させる工程と、前記基板を薄化して前記ビアホールの底部の前記導電膜を露出させ

る工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2) 半導体回路が形成されるチップ領域内において、前記溝を前記ホールの直径

より幅広に形成することを特徴とする付記1に記載の半導体装置の製造方法。

(付記3) 前記基板のエッジ部分には、前記溝が前記エッジの全周にわたって格子状に

形成することを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4) 前記基板上のスクライブライン領域に前記溝を形成する付記2又は付記3に

記載の半導体装置の製造方法。

(付記5) 前記チップ領域内の前記溝の断面積は、前記チップ領域の外側の前記溝の断

面積以下であることを特徴とする付記2乃至付記4のいずれか一項に記載の半導体装置の

製造方法。

(付記6)

1つの前記溝を少なくとも2箇所で他の前記溝に接続させることを特徴とする付記1乃

至付記5のいずれか一項に記載の半導体装置の製造方法。

【符号の説明】

【0064】

1 シリコン基板

23 絶縁膜

26 ホール

35 溝

35A 第1の溝

35B 第2の溝

35C 第3の溝

40 チップ領域

42 シード層

47 Cu膜(導電膜)

95 半導体装置

【特許請求の範囲】

【請求項1】

基板にホールを形成する工程と、

前記基板の上方に形成した絶縁膜に、前記ホールから前記基板の周辺部分に至る溝を複

数形成する工程と、

前記ホールの内壁及び前記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と

、

前記ホール内及び前記溝内以外の前記シード層を除去する工程と、

前記基板の周辺部分の前記溝に形成した前記シード層から、前記ホール内の前記シード

層に通電し、前記ホール内に導電膜を形成する工程と、

前記基板を薄化して前記ホールの底部の前記導電膜を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

半導体回路が形成されるチップ領域内において、前記溝を前記ホールの直径より幅広に

形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記基板のエッジ部分には、前記溝が前記エッジの全周にわたって格子状に形成するこ

とを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記基板上のスクライブライン領域に前記溝を形成する請求項2又は請求項3に記載の

半導体装置の製造方法。

【請求項5】

1つの前記溝を少なくとも2箇所で他の前記溝に接続させることを特徴とする請求項1

乃至請求項4のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

基板にホールを形成する工程と、

前記基板の上方に形成した絶縁膜に、前記ホールから前記基板の周辺部分に至る溝を複

数形成する工程と、

前記ホールの内壁及び前記溝を覆う導電性のシード層を前記絶縁膜上に形成する工程と

、

前記ホール内及び前記溝内以外の前記シード層を除去する工程と、

前記基板の周辺部分の前記溝に形成した前記シード層から、前記ホール内の前記シード

層に通電し、前記ホール内に導電膜を形成する工程と、

前記基板を薄化して前記ホールの底部の前記導電膜を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

半導体回路が形成されるチップ領域内において、前記溝を前記ホールの直径より幅広に

形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記基板のエッジ部分には、前記溝が前記エッジの全周にわたって格子状に形成するこ

とを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記基板上のスクライブライン領域に前記溝を形成する請求項2又は請求項3に記載の

半導体装置の製造方法。

【請求項5】

1つの前記溝を少なくとも2箇所で他の前記溝に接続させることを特徴とする請求項1

乃至請求項4のいずれか一項に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図1P】

【図1Q】

【図1R】

【図1S】

【図1T】

【図2】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

【図6】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図1P】

【図1Q】

【図1R】

【図1S】

【図1T】

【図2】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

【図6】

【公開番号】特開2013−115350(P2013−115350A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262306(P2011−262306)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]