半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造方法において、下地層上にピラーを形成し、このピラーを絶縁層により埋め込んだ後に、ピラーの上面を絶縁層から露出させるプロセス(ピラーの頭出しプロセス)がある。このプロセスの課題は、CMP(chemical mechanical polishing)やエッチバックなどによりピラーの上面を絶縁層から露出させるときに、ピラーの上面が露出した時点を把握できないことにある。このため、従来は、CMP、RIE(reactive ion etching)、IBE(ion beam etching)などを組み合わる、サンプルを用いて、絶縁層のエッチング時間とピラーの上面の露出状況(絶縁層のエッチング量)との関係を検証し、最適なエッチング時間を求める、などの工夫が必要であった。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−186869号公報

【特許文献2】特開2007−59927号公報

【特許文献3】特開平5−206120号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

実施形態は、TAT(turn around time)の短縮及び製造コストの低下を図ることが可能な半導体装置の製造方法を提案する。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、前記下地層上に、前記ピラーを覆い、かつ、上面の最も低い部分が前記ピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、前記絶縁層及び前記ピラーを、前記絶縁層の上面の最も低い部分まで研磨する工程とを備える。

【図面の簡単な説明】

【0006】

【図1】基本プロセスを示す図。

【図2】基本プロセスを示す図。

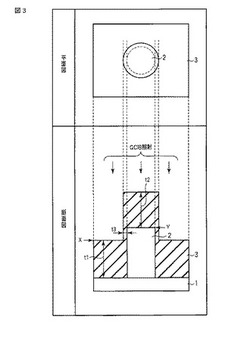

【図3】基本プロセスを示す図。

【図4】基本プロセスを示す図。

【図5】基本プロセスを示す図。

【図6】基本プロセスを示す図。

【図7】実施例に係わるプロセスを示す図。

【図8】実施例に係わるプロセスを示す図。

【図9】実施例に係わるプロセスを示す図。

【図10】実施例に係わるプロセスを示す図。

【図11】抵抗変化素子の例を示す図。

【図12】適用例としての半導体メモリを示す図。

【図13】適用例としての半導体メモリを示す図。

【図14】図13の半導体メモリの製造方法を示す図。

【図15】図13の半導体メモリの製造方法を示す図。

【図16】図13の半導体メモリの製造方法を示す図。

【図17】図13の半導体メモリの製造方法を示す図。

【発明を実施するための形態】

【0007】

以下、図面を参照しながら実施形態を説明する。

【0008】

1. 基本プロセス

図1乃至図6は、基本プロセスを示している。

このプロセスは、ピラーの頭出しプロセス(a process of exposing a head of a pillar)に関する。ここで、ピラーとは、下地層上に配置される柱状部材のことであり、単層構造/積層構造、導電体(抵抗体を含む)/半導体/絶縁体などに制限はない。また、ピラーは、複数の機能要素(プラグ、電極、メモリセルなど)を含んでいてもよい。

【0009】

まず、図1に示すように、第1の層(下地層)1上に第2の層2’を形成する。第1及び第2の層1,2’は、互いに異なる材料を備えるが、その材料の種類については、特に限定されない。また、第1及び第2の層1,2’の間にそれらよりも薄い界面層が存在していても構わない。

【0010】

この後、第2の層2’をパターニングし、図2に示すように、ピラー2を形成する。このパターニングの方法についても、特に限定されない。例えば、ハードマスクをマスクにして、イオンビームエッチング、RIE(Reactive ion etching)などの異方性エッチングにより、ピラー2を形成することができる。

【0011】

次に、図3に示すように、GCIB(Gas cluster ion beam)法を用いて、第1の層1上に、ピラー2を覆い、かつ、上面の最も低い部分がピラー2の上面よりも下にある絶縁層3を形成する。

【0012】

ここで、GCIB法とは、複数の元素を備えるクラスターをイオン化し、それをウェハーの表面に照射することにより、エッチング又は堆積を行う方法のことである。基本プロセスでは、このGCIB法を絶縁層3の堆積のために使用する。

【0013】

GCIB法によれば、イオン化されたクラスターの流れに強い方向性が生じるため、第1の層1上及びピラー2上に堆積する絶縁層3の上下方向の厚さt1、t2は、ピラー2の側壁上に付着する絶縁層3の左右方向の厚さt3よりも大きくなる。

【0014】

また、GCIB法により堆積する絶縁層3は、CVD法などの従来の方法により堆積する絶縁層比べて、絶縁層3の上面の最も低い部分X、即ち、絶縁層3の凹部の底部が平坦になる性質を有する。

【0015】

このため、絶縁層3の上面の最も低い部分Xをピラー2の上面Yよりも下にする制御が容易となる。特に、複数のピラーがアレイ状に配置される場合においては、複数のピラー間のスペースが絶縁層3により埋め込まれ易くなるが、GCIB法によれば、複数のピラー間のスペースを絶縁層3により完全に埋め込まない制御が可能になる。

【0016】

次に、図4に示すように、CMP法を用いて、絶縁層3及びピラー2を、絶縁層3の上面の最も低い部分X(図3のXに対応)まで研磨する。即ち、GCIB法により形成された絶縁層3の上面の最も低い部分XをCMPのエンドポイントとする。

【0017】

ここで、図3のステップにおいて、絶縁層3の上面の最も低い部分Xをピラー2の上面Yよりも下にしたことにより、その最も低い部分XをCMPのエンドポイントとすると、ピラー2の上面を絶縁層3から確実に露出させることができる。

【0018】

これについて以下説明する。

【0019】

図5は、CMP装置を示している。

台座部(例えば、回転台)21は、例えば、回転駆動(右回り/左回り)される。研磨パッド22は、台座部21上に搭載される。保持部23は、ウェハー24を保持し、かつ、ウェハー24を保持した状態でウェハー24を研磨パッド22の表面部に接触させる。保持部23は、例えば、回転駆動(右回り/左回り)される。

【0020】

供給部25は、台座部21の上方、例えば、台座部21が円柱形のとき、円の中央部の上方に配置され、研磨パッド22の表面部にスラリーを供給する。スラリーは、例えば、研磨剤などの薬液、水などを含む。制御部26は、台座部21、保持部23及び供給部25の動作を制御する。

【0021】

制御部26は、トルク電流モニター部27を有する。

【0022】

トルク電流モニター部27は、CMPのエンドポイントを判断する手段である。即ち、台座部21及び保持部23がそれぞれ一定回転で駆動されるとき、台座部21又は保持部23を回転駆動するトルク電流値をモニターすることにより、CMPのエンドポイントを決めることができる。

【0023】

例えば、図3に示すように、GCIB法により形成された絶縁層3の上面は、凹凸を有する。このため、CMPの初期段階では、研磨パッド22は、絶縁層3の上面の凸部のみに接触する。即ち、研磨パッド22とウェハー24との接触抵抗は小さく、トルク電流値も、小さい。

【0024】

これに対し、例えば、図6に示すように、CMPの研磨時間が長くなるにつれて、絶縁層3の上面の凹凸が小さくなるため、研磨パッド22とウェハー24との接触抵抗が次第に大きくなり、トルク電流値も大きくなる。そして、絶縁層3の凹凸が無くなった時点、即ち、CMPによる研磨量が絶縁層3の上面の最も低い部分Xに達した時点で、トルク電流値は、最大値となり、その後、ほぼ一定になる。

【0025】

従って、トルク電流値の変化点P1を検出することにより、CMPのエンドポイント(絶縁層3の上面の最も低い部分X)を決定することができる。

【0026】

尚、トルク電流値の変化点P1を検出するために、例えば、一定の判断期間を設けるのが望ましい。ここで、既に述べたように、GCIB法により堆積する絶縁層3は、その上面の最も低い部分Xが平坦であるため、CMPのエンドポイントの検出精度を向上させることができる。

【0027】

また、台座部21及び保持部23は、研磨量のむらをなくす観点から共に回転駆動されているのが望ましい。両者が回転駆動されるとき、保持部23の回転方向と台座部21の回転方向とは同じであるのが望ましい。

【0028】

このように、基本プロセスによれば、従来のように、サンプルを用いて最適なエッチング時間(CMPの研磨時間)を検証する必要がなく、TATの短縮を図ることができる。

【0029】

また、ピラー2をH2OやO2などから保護する場合、一般的には、ピラー2を覆う薄い保護層(例えば、窒化シリコン)と層間絶縁層(例えば、酸化シリコン)とは別々に形成される。この場合、保護層を形成するプロセスと層間絶縁層を形成するプロセスとが必要となると共に、ピラーの上部にも十分に厚い層間絶縁層が残存するため、層間絶縁層にピラーの上面に達するコンタクトホールを形成するプロセスが必要になる。結果として、製造ステップ数の増加により、製造コストが増大する。

【0030】

これに対し、基本プロセスによれば、GCIB法により形成される絶縁層3は、層間絶縁層であると共に、保護層として機能させることができる。

【0031】

例えば、SiH4とN2を含むクラスターを用いれば、GCIB法により形成される絶縁層3は、窒化シリコンとなる。この窒化シリコンは、層間絶縁層として及びピラー2を保護する保護層として機能させることができる。

【0032】

従って、基本プロセスによれば、半導体装置の製造ステップ数を削減でき、製造コストの低下を図ることができる。

【0033】

尚、コンベンショナルな堆積方法(例えば、CVD法など)により、保護層(例えば、窒化シリコン)を十分に厚く形成し、層間絶縁層として機能させることは現実的でない。なぜなら、コンベンショナルなプロセスでは、ピラーの上部にも十分に厚い保護層が残存してしまうからである。

【0034】

これに対し、基本プロセスによれば、保護層としての層間絶縁層は、ピラー2間のみに形成され、ピラー2の上部に形成されることはない。

【0035】

ところで、図2のパターニングプロセスにおいて、GCIB法を用いることも可能である。

【0036】

即ち、GCIB法は、エッチング方法として応用することもできる。この場合、図2のピラー2の形成と、図3の絶縁層3の堆積とを、同一装置内において行うことができるため、ウェハー移動によるピラー2の損傷や酸化などを防止できる。

【0037】

以上、説明したように、基本プロセスによれば、半導体装置の製造方法におけるピラーの頭出しプロセスにおいて、TATの短縮及び製造コストの低下を図ることができる。

【0038】

2. 実施例

図7乃至図10は、抵抗変化素子の頭出しプロセスを示している。

【0039】

ここで、抵抗変化素子とは、電流、電圧、熱、磁場などにより抵抗値が変化するメモリセルのことである。抵抗変化素子をメモリセルとする半導体メモリとしては、例えば、磁気抵抗効果素子をメモリセルとするMRAM(Magnetic Random Access Memory)、金属酸化物をメモリセルとするReRAM(Resistive Random Access Memory)などがある。

【0040】

尚、ピラーが抵抗変化素子(例えば、磁気抵抗効果素子)を含む場合、ピラー間に満たされる材料の比誘電率、即ち、ピラー間容量が抵抗変化素子の性能に与える影響はない。このため、基本プロセスで説明したように、層間絶縁層に保護層としての機能を持つ窒化シリコンを使用したとしても、ピラー2間のみに満たされる層間絶縁層が抵抗変化素子の性能に悪影響を与えることはない。

【0041】

まず、図7に示すように、下部電極(LE:Lower electrode)11上にメモリセル材料層(積層構造)12’を形成する。また、メモリセル材料層12’上にハードマスク材料層13’を形成する。

【0042】

この後、例えば、PEP(Photo engraving process)を用いてレジストパターンを形成し、このレジストパターンをマスクにして、イオンビームエッチング、RIEなどの異方性エッチングにより、ハードマスク材料層13’をパターニングし、ハードマスク層を形成する。この後、レジストパターンを除去する。

【0043】

続けて、ハードマスク層をマスクにして、物理エッチング、例えば、GCIBエッチングにより、メモリセル材料層12’をパターニングする。ここで、ハードマスク層をマスクとするのは、レジストパターンをマスクにしてメモリセル材料層12’をエッチングすると、レジストパターンをアッシングにより除去するときに、メモリセル材料層12’が酸化されてしまうからである。

【0044】

以上のパターニングの結果、図8に示すように、下部電極(LE)11上に、抵抗変化素子(MTJ)12及びハードマスク層(HM)13を備えるピラーが形成される。

【0045】

次に、図9に示すように、GCIB法を用いて、下部電極11上に、ピラー(抵抗変化素子12及びハードマスク層13)を覆い、かつ、上面の最も低い部分Xが、ハードマスク層13の上面Y1よりも下にあり、ハードマスク層13の下面Y2よりも上にある絶縁層14を形成する。

【0046】

ここで、本実施例では、基本プロセスにない条件として、「GCIB法により形成される絶縁層14の上面の最も低い部分がハードマスク層13の下面よりも上である」ことが追加されている。これは、ピラーの頭出しを行うに当たって、抵抗変化素子12がエッチングされることを防止するためである。

【0047】

また、「絶縁層14の上面の最も低い部分がハードマスク層13の上面よりも下である」という条件は、「絶縁層14の上面の最も低い部分がピラーの上面よりも下である」という条件に等価である。

【0048】

GCIB法によれば、イオン化されたクラスターの流れに強い方向性が生じるため、下部電極11上及びハードマスク層13上に堆積する絶縁層14の上下方向の厚さt1、t2は、ハードマスク層13の側壁上に付着する絶縁層14の左右方向の厚さt3よりも大きくなる。このため、絶縁層14の上面の最も低い部分Xを、ハードマスク層13の上面Y1よりも下にし、かつ、ハードマスク層13の下面Y2よりも上にする制御が容易となる。

【0049】

次に、図10に示すように、CMP法を用いて、絶縁層14及びハードマスク層13を、絶縁層14の上面の最も低い部分X(図9のXに対応)まで研磨する。即ち、基本プロセスで説明したように、GCIB法により形成した絶縁層14の上面の最も低い部分XをCMPのエンドポイントとする。

【0050】

ここで、図9のステップにおいて、絶縁層14の上面の最も低い部分Xを、ハードマスク層13の上面Y1よりも下にし、かつ、ハードマスク層13の下面Y2よりも上にしたことにより、その最も低い部分XをCMPのエンドポイントとすると、ハードマスク層13の上面を絶縁層14から確実に露出させることができる。

【0051】

以上のステップにより、抵抗変化素子の頭出しプロセスが完了する。

【0052】

尚、GCIB法は、CVD法やALD法に比べて、低温での絶縁層14の堆積が可能である。例えば、CVD法やALD法では、400〜600℃の温度が必要であるが、GCIB法は、室温で行うことができる。このため、GCIB法により絶縁層14を堆積している最中に、抵抗変化素子12に悪影響を与えることがない。

【0053】

図11は、抵抗変化素子の例を示している。

【0054】

抵抗変化素子(MTJ)12は、例えば、磁気抵抗効果素子である。

【0055】

この場合、抵抗変化素子12は、下地層と、下地層上の記憶層(磁気フリー層)と、記憶層上のトンネルバリア層と、トンネルバリア層上の参照層(磁気ピンド層)と、参照層上のシフト調整層とを備える。

【0056】

ハードマスク層13は、抵抗変化素子12上に配置される。

【0057】

記憶層及び参照層は、例えば、CoFeBを備え、トンネルバリア層は、例えば、MgOを備える。シフト調整層は、例えば、Pt、Pd、Irのうちの1つを備える。ハードマスク層13は、例えば、TiN、TaNのうちの1つを備える。

【0058】

シフト調整層は、磁気抵抗層の構造に起因する磁気フリー層の磁気ヒステリシス曲線のシフトを調整する機能を有する。シフト調整層は、磁気ピンド層に付加されることによりその機能を発揮する。

【0059】

第1の例と第2の例が異なる点は、記憶層と参照層の平面サイズの関係にある。

【0060】

即ち、第1の例では、抵抗変化素子12内の記憶層及び参照層の平面サイズは、互いに同じである。また、この例は、記憶層及び参照層の側壁が下に向かってテーパ状である場合を含む。この場合、記憶層及び参照層の平面サイズは、互いに異なり、かつ、記憶層及び参照層の側壁は、斜めに連続的に変化する。

【0061】

また、第2の例では、抵抗変化素子12内の記憶層及び参照層の平面サイズは、互いに異なる。この例での「平面サイズが異なる」とは、記憶層及び参照層の側壁が不連続である場合を意味する。

【0062】

第2の例の特徴は、抵抗変化素子12をパターニングするときに発生する再付着層(Re-deposition layer)による記憶層と参照層との電気的ショートを防止できる点にある。

【0063】

尚、本例では、抵抗変化素子MTJの平面図(平面形状)は、円形を有しているが、これに限られない。抵抗変化素子MTJの平面形状は、四角形又は楕円に近い形状であっても構わない。

【0064】

3. 適用例

近年、不揮発性半導体メモリとして、トンネル磁気抵抗効果(TMR: Tunneling Magneto Resistive))を利用した磁気ランダムアクセスメモリ(MRAM)が開発されている。MRAMは、高速読み出し/書き込み、低消費電力動作及び大容量化が可能といった特徴を持ち、次世代ワーキングメモリとしての応用が期待されている。

【0065】

MRAMのメモリセルは、抵抗変化素子としての磁気抵抗効果素子である。近年では、磁気抵抗効果素子の記憶層の磁化を反転させるに当たり、スピン角運動量移動(SMT: Spin-momentum-transfer)現象を利用する、いわゆるスピン注入磁化反転方式を採用するのが主流である。この方式によれば、磁気抵抗効果素子のサイズが小さくなるに従い、磁化反転電流も小さくなる、というスケーラビリティ性を実現できるため、将来の大容量化にとって望ましい。

【0066】

また、スピン注入磁化反転方式は、記憶層及び参照層が垂直磁化(perpendicular magnetization)を持つ場合に特に有効である。この場合、磁気抵抗効果素子を、その形状に関係なく、微細化することができるからである。記憶層及び参照層が面内磁化(in-plane magnetization)を持つ場合には、磁気抵抗効果素子に形状磁気異方性を付けなければならないため、微細化には望ましくない。

【0067】

ここで、垂直磁化とは、残留磁化の方向が記憶層及び参照層の膜面(上面/下面)に対して垂直又はほぼ垂直となることである。この明細書において、ほぼ垂直とは、残留磁化の方向が記憶層及び参照層の膜面に対して、45°<θ≦90°の範囲内にあることを意味する。

【0068】

以下、実施例に係わる抵抗変化素子(磁気抵抗効果素子)の製造方法をMRAMに適用した場合について説明する。

【0069】

図12は、MRAMのメモリセルアレイの例を示している。

【0070】

メモリセルアレイ30は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)、複数のビアV0(0)〜V0(4)及び複数のFET SW(1)〜SW(4)を備える。

【0071】

複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)は、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される。

【0072】

また、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)のみを見たとき、これら複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)は、一定ピッチで格子状に配置される。同様に、複数のビアV0(0)〜V0(4)のみを見たとき、これら複数のビアV0(0)〜V0(4)は、一定ピッチで格子状に配置される。

【0073】

複数のFET SW(1)〜SW(4)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)と同様に、格子状に配置される。1つのFETは、第1の方向に隣接する1つの磁気抵抗効果素子と1つのビアとの間に接続される。

【0074】

例えば、FET SW(1)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)のうち第1の方向に隣接する磁気抵抗効果素子MTJ(1)とビアV0(1)との間に接続される。また、FET SW(2)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)のうち第1の方向に隣接する磁気抵抗効果素子MTJ(2)とビアV0(2)との間に接続される。

【0075】

複数のワード線WL1,WL2,WL3,WL4,…は、第2の方向に延び、第2の方向に並ぶ複数のFETのゲートに共通に接続される。

【0076】

例えば、ワード線WL1は、FET SW(1)のゲートに接続され、ワード線WL2は、FET SW(2)のゲートに接続される。

【0077】

複数の上部電極UE(1)〜UE(5)の各々は、第2の方向に隣接する1つの磁気抵抗効果素子と1つのビアとの間に接続される。

【0078】

例えば、上部電極UE(1)は、ビアV0(0)及び磁気抵抗効果素子MTJ(1)に接続される。また、上部電極UE(2)は、ビアV0(1)及び磁気抵抗効果素子MTJ(2)に接続される。さらに、上部電極UE(3)は、ビアV0(2)及び磁気抵抗効果素子MTJ(3)に接続される。

【0079】

複数のビット線BL1a,BL1b,BL2a,BL2b,…は、第1の方向に延び、第1の方向に並ぶ複数の上部電極UE(1)〜UE(5)に一つおきに接続される。

【0080】

例えば、ビット線BL1a,BL2aは、奇数番目の上部電極UE(1),UE(3),UE(5)に接続される。また、ビット線BL1b,BL2bは、偶数番目の上部電極UE(2),UE(4)に接続される。

【0081】

第1の制御回路31は、複数のワード線WL1,WL2,WL3,WL4,…の電位を制御する。第2の制御回路32は、複数のビット線BL1a,BL1b,BL2a,BL2b,…の電位を制御する。

【0082】

例えば、磁気抵抗効果素子MTJ(1)について読み出し/書き込みを行うとき、第1の制御回路31を用いて、ワード線WL1の電位を“H”にし、その他のワード線WL2,WL3,WL4,…の電位を“L”にする。ここで、“H”とは、FETをオンにする電位のことであり、“L”とは、FETをオフにする電位のことである。

【0083】

この時、第2の制御回路32を用いて、複数のビット線BL1a,BL1b,BL2a,BL2b,…の電位を制御することにより、磁気抵抗効果素子MTJ(1)について読み出し/書き込みを行うことができる。

【0084】

図13は、図12のメモリセルアレイのデバイス構造の例を示している。

【0085】

半導体基板41内には、STI(Shallow Trench Isolation)構造の素子分離絶縁層42が配置される。素子分離絶縁層42に取り囲まれた素子領域(アクティブエリア)内には、複数のソース/ドレイン拡散層43が配置される。

【0086】

また、複数のソース/ドレイン拡散層43間のチャネル領域上には、ゲート絶縁層44、導電性シリコン層45、金属層46及びハードマスク層47が配置される。金属層46は、例えば、金属シリサイドを含む。金属層46は、単層でも、複数層でもよい。ハードマスク層47は、例えば、絶縁層である。

【0087】

導電性シリコン層45及び金属層46は、FETのゲートとして機能すると共に、第2の方向に延びることによりワード線WL1,WL2,WL3,WL4,…としても機能する。ゲート絶縁層44、導電性シリコン層45、金属層46及びハードマスク層47の側壁には、複数のソース/ドレイン拡散層43に対するコンタクトをセルフアラインで行うための側壁絶縁層48が配置される。

【0088】

複数のソース/ドレイン拡散層43上には、複数のコンタクトビア(プラグ)CBが配置される。複数のコンタクトビアCB上には、複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…が配置される。これら複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…上には、複数の上部電極UE(1),UE(2),UE(3),…が配置される。

【0089】

次に、図13のMRAMの製造方法を説明する。

【0090】

まず、図14に示すように、周知の技術を用いて、半導体基板41内に素子分離絶縁層42を形成し、かつ、半導体基板41上に複数のFETを形成する。複数のFETの各々は、ソース/ドレイン拡散層43、ゲート絶縁層44、導電性シリコン層45、金属層46、ハードマスク層47及び側壁絶縁層48を有する。

【0091】

また、ソース/ドレイン拡散層43上にセルフアラインでコンタクトビアCBを形成した後、コンタクトビアCB上に、複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…を形成する。複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…は、それぞれ、ピラー形状を有する。

【0092】

また、磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…は、ハードマスク層13をマスクにして、物理エッチング(例えば、GCIBエッチング)によりパターニングするのが望ましい。

【0093】

次に、図15に示すように、GCIB法を用いて、複数のFET上に、ピラー(複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…)を覆い、かつ、上面の最も低い部分Xが、ハードマスク層13(図14参照)の上面よりも下にあり、ハードマスク層13(図14参照)の下面よりも上にある絶縁層14を形成する。

【0094】

ここで、GCIB法により形成する絶縁層14が窒化シリコンである場合を説明する。

【0095】

まず、大気圧レベルのSiH4ガス及びN2ガスを真空チャンバー内に放出する。この時、これらのガスは、断熱膨張し、1K程度に冷却される。その結果、原子量10000程度のガスイオンクラスター29が形成される。また、クラスター29を、イオン化し、かつ、所定の加速電圧を与えることにより、クラスター29をウェハーの表面に照射する。

【0096】

このようなクラスター29の照射により、複数のFET上及びピラーの上面上には、厚い絶縁層14が形成され、ピラーの側壁上には、薄い絶縁層14が形成される。従って、絶縁層14の上面は、凹凸を有する形状となる。尚、絶縁層14の凸部は、ピラーの位置に対応する。

【0097】

尚、絶縁層14は、窒化シリコンに限られず、酸化シリコンであっても構わない

絶縁層14を酸化シリコンとするときは、例えば、大気圧レベルのSiH4ガス及びO2ガスを真空チャンバー内に放出すればよい。

【0098】

次に、図16に示すように、CMP法を用いて、絶縁層14を、絶縁層14の上面の最も低い部分X(図15のXに対応)まで研磨する。即ち、基本プロセスで説明したように、GCIB法により形成した絶縁層14の上面の最も低い部分XをCMPのエンドポイントとする。

【0099】

これにより、ハードマスク層13の上面及びビアV0(0),V0(1),V0(2),…の上面が、それぞれ、絶縁層14から露出する。

【0100】

最後に、第2の方向に隣接する1つのハードマスク層13と1つのビアV0(0),V0(1),V0(2),…とを、上部電極UE(1),UE(2),UE(3),…により互いに電気的に接続する。

【0101】

また、上部電極UE(1),UE(3),…に接続されるビット線BL1aを形成すると共に、上部電極UE(2),…に接続されるビット線BL1bを形成する。

【0102】

以上のステップにより、図13のMRAMが形成される。

【0103】

4. むすび

実施形態によれば、TATの短縮及び製造コストの低下を図ることができる。

【0104】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0105】

1: 第1の層(下地層)、 2’: 第2の層、 2: ピラー、 3,14: 絶縁層、 11: 下部電極、 12’: メモリセル材料層、 12: 抵抗変化素子、 13’: ハードマスク材料層、 13,47: ハードマスク層、 21: 台座部、 22: 研磨パッド、 23: 保持部、 24: ウェハー、 25: 供給部、 26: 制御部、 27: トルク電流モニター部、 30: メモリセルアレイ、 31: 第1の制御回路、 32: 第2の制御回路、 41: 半導体基板、 42: 素子分離絶縁層、 43: ソース/ドレイン拡散層、 44: ゲート絶縁層、 45: 導電性シリコン層、 46: 金属層、 48: 側壁絶縁層。

【技術分野】

【0001】

実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造方法において、下地層上にピラーを形成し、このピラーを絶縁層により埋め込んだ後に、ピラーの上面を絶縁層から露出させるプロセス(ピラーの頭出しプロセス)がある。このプロセスの課題は、CMP(chemical mechanical polishing)やエッチバックなどによりピラーの上面を絶縁層から露出させるときに、ピラーの上面が露出した時点を把握できないことにある。このため、従来は、CMP、RIE(reactive ion etching)、IBE(ion beam etching)などを組み合わる、サンプルを用いて、絶縁層のエッチング時間とピラーの上面の露出状況(絶縁層のエッチング量)との関係を検証し、最適なエッチング時間を求める、などの工夫が必要であった。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−186869号公報

【特許文献2】特開2007−59927号公報

【特許文献3】特開平5−206120号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

実施形態は、TAT(turn around time)の短縮及び製造コストの低下を図ることが可能な半導体装置の製造方法を提案する。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、前記下地層上に、前記ピラーを覆い、かつ、上面の最も低い部分が前記ピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、前記絶縁層及び前記ピラーを、前記絶縁層の上面の最も低い部分まで研磨する工程とを備える。

【図面の簡単な説明】

【0006】

【図1】基本プロセスを示す図。

【図2】基本プロセスを示す図。

【図3】基本プロセスを示す図。

【図4】基本プロセスを示す図。

【図5】基本プロセスを示す図。

【図6】基本プロセスを示す図。

【図7】実施例に係わるプロセスを示す図。

【図8】実施例に係わるプロセスを示す図。

【図9】実施例に係わるプロセスを示す図。

【図10】実施例に係わるプロセスを示す図。

【図11】抵抗変化素子の例を示す図。

【図12】適用例としての半導体メモリを示す図。

【図13】適用例としての半導体メモリを示す図。

【図14】図13の半導体メモリの製造方法を示す図。

【図15】図13の半導体メモリの製造方法を示す図。

【図16】図13の半導体メモリの製造方法を示す図。

【図17】図13の半導体メモリの製造方法を示す図。

【発明を実施するための形態】

【0007】

以下、図面を参照しながら実施形態を説明する。

【0008】

1. 基本プロセス

図1乃至図6は、基本プロセスを示している。

このプロセスは、ピラーの頭出しプロセス(a process of exposing a head of a pillar)に関する。ここで、ピラーとは、下地層上に配置される柱状部材のことであり、単層構造/積層構造、導電体(抵抗体を含む)/半導体/絶縁体などに制限はない。また、ピラーは、複数の機能要素(プラグ、電極、メモリセルなど)を含んでいてもよい。

【0009】

まず、図1に示すように、第1の層(下地層)1上に第2の層2’を形成する。第1及び第2の層1,2’は、互いに異なる材料を備えるが、その材料の種類については、特に限定されない。また、第1及び第2の層1,2’の間にそれらよりも薄い界面層が存在していても構わない。

【0010】

この後、第2の層2’をパターニングし、図2に示すように、ピラー2を形成する。このパターニングの方法についても、特に限定されない。例えば、ハードマスクをマスクにして、イオンビームエッチング、RIE(Reactive ion etching)などの異方性エッチングにより、ピラー2を形成することができる。

【0011】

次に、図3に示すように、GCIB(Gas cluster ion beam)法を用いて、第1の層1上に、ピラー2を覆い、かつ、上面の最も低い部分がピラー2の上面よりも下にある絶縁層3を形成する。

【0012】

ここで、GCIB法とは、複数の元素を備えるクラスターをイオン化し、それをウェハーの表面に照射することにより、エッチング又は堆積を行う方法のことである。基本プロセスでは、このGCIB法を絶縁層3の堆積のために使用する。

【0013】

GCIB法によれば、イオン化されたクラスターの流れに強い方向性が生じるため、第1の層1上及びピラー2上に堆積する絶縁層3の上下方向の厚さt1、t2は、ピラー2の側壁上に付着する絶縁層3の左右方向の厚さt3よりも大きくなる。

【0014】

また、GCIB法により堆積する絶縁層3は、CVD法などの従来の方法により堆積する絶縁層比べて、絶縁層3の上面の最も低い部分X、即ち、絶縁層3の凹部の底部が平坦になる性質を有する。

【0015】

このため、絶縁層3の上面の最も低い部分Xをピラー2の上面Yよりも下にする制御が容易となる。特に、複数のピラーがアレイ状に配置される場合においては、複数のピラー間のスペースが絶縁層3により埋め込まれ易くなるが、GCIB法によれば、複数のピラー間のスペースを絶縁層3により完全に埋め込まない制御が可能になる。

【0016】

次に、図4に示すように、CMP法を用いて、絶縁層3及びピラー2を、絶縁層3の上面の最も低い部分X(図3のXに対応)まで研磨する。即ち、GCIB法により形成された絶縁層3の上面の最も低い部分XをCMPのエンドポイントとする。

【0017】

ここで、図3のステップにおいて、絶縁層3の上面の最も低い部分Xをピラー2の上面Yよりも下にしたことにより、その最も低い部分XをCMPのエンドポイントとすると、ピラー2の上面を絶縁層3から確実に露出させることができる。

【0018】

これについて以下説明する。

【0019】

図5は、CMP装置を示している。

台座部(例えば、回転台)21は、例えば、回転駆動(右回り/左回り)される。研磨パッド22は、台座部21上に搭載される。保持部23は、ウェハー24を保持し、かつ、ウェハー24を保持した状態でウェハー24を研磨パッド22の表面部に接触させる。保持部23は、例えば、回転駆動(右回り/左回り)される。

【0020】

供給部25は、台座部21の上方、例えば、台座部21が円柱形のとき、円の中央部の上方に配置され、研磨パッド22の表面部にスラリーを供給する。スラリーは、例えば、研磨剤などの薬液、水などを含む。制御部26は、台座部21、保持部23及び供給部25の動作を制御する。

【0021】

制御部26は、トルク電流モニター部27を有する。

【0022】

トルク電流モニター部27は、CMPのエンドポイントを判断する手段である。即ち、台座部21及び保持部23がそれぞれ一定回転で駆動されるとき、台座部21又は保持部23を回転駆動するトルク電流値をモニターすることにより、CMPのエンドポイントを決めることができる。

【0023】

例えば、図3に示すように、GCIB法により形成された絶縁層3の上面は、凹凸を有する。このため、CMPの初期段階では、研磨パッド22は、絶縁層3の上面の凸部のみに接触する。即ち、研磨パッド22とウェハー24との接触抵抗は小さく、トルク電流値も、小さい。

【0024】

これに対し、例えば、図6に示すように、CMPの研磨時間が長くなるにつれて、絶縁層3の上面の凹凸が小さくなるため、研磨パッド22とウェハー24との接触抵抗が次第に大きくなり、トルク電流値も大きくなる。そして、絶縁層3の凹凸が無くなった時点、即ち、CMPによる研磨量が絶縁層3の上面の最も低い部分Xに達した時点で、トルク電流値は、最大値となり、その後、ほぼ一定になる。

【0025】

従って、トルク電流値の変化点P1を検出することにより、CMPのエンドポイント(絶縁層3の上面の最も低い部分X)を決定することができる。

【0026】

尚、トルク電流値の変化点P1を検出するために、例えば、一定の判断期間を設けるのが望ましい。ここで、既に述べたように、GCIB法により堆積する絶縁層3は、その上面の最も低い部分Xが平坦であるため、CMPのエンドポイントの検出精度を向上させることができる。

【0027】

また、台座部21及び保持部23は、研磨量のむらをなくす観点から共に回転駆動されているのが望ましい。両者が回転駆動されるとき、保持部23の回転方向と台座部21の回転方向とは同じであるのが望ましい。

【0028】

このように、基本プロセスによれば、従来のように、サンプルを用いて最適なエッチング時間(CMPの研磨時間)を検証する必要がなく、TATの短縮を図ることができる。

【0029】

また、ピラー2をH2OやO2などから保護する場合、一般的には、ピラー2を覆う薄い保護層(例えば、窒化シリコン)と層間絶縁層(例えば、酸化シリコン)とは別々に形成される。この場合、保護層を形成するプロセスと層間絶縁層を形成するプロセスとが必要となると共に、ピラーの上部にも十分に厚い層間絶縁層が残存するため、層間絶縁層にピラーの上面に達するコンタクトホールを形成するプロセスが必要になる。結果として、製造ステップ数の増加により、製造コストが増大する。

【0030】

これに対し、基本プロセスによれば、GCIB法により形成される絶縁層3は、層間絶縁層であると共に、保護層として機能させることができる。

【0031】

例えば、SiH4とN2を含むクラスターを用いれば、GCIB法により形成される絶縁層3は、窒化シリコンとなる。この窒化シリコンは、層間絶縁層として及びピラー2を保護する保護層として機能させることができる。

【0032】

従って、基本プロセスによれば、半導体装置の製造ステップ数を削減でき、製造コストの低下を図ることができる。

【0033】

尚、コンベンショナルな堆積方法(例えば、CVD法など)により、保護層(例えば、窒化シリコン)を十分に厚く形成し、層間絶縁層として機能させることは現実的でない。なぜなら、コンベンショナルなプロセスでは、ピラーの上部にも十分に厚い保護層が残存してしまうからである。

【0034】

これに対し、基本プロセスによれば、保護層としての層間絶縁層は、ピラー2間のみに形成され、ピラー2の上部に形成されることはない。

【0035】

ところで、図2のパターニングプロセスにおいて、GCIB法を用いることも可能である。

【0036】

即ち、GCIB法は、エッチング方法として応用することもできる。この場合、図2のピラー2の形成と、図3の絶縁層3の堆積とを、同一装置内において行うことができるため、ウェハー移動によるピラー2の損傷や酸化などを防止できる。

【0037】

以上、説明したように、基本プロセスによれば、半導体装置の製造方法におけるピラーの頭出しプロセスにおいて、TATの短縮及び製造コストの低下を図ることができる。

【0038】

2. 実施例

図7乃至図10は、抵抗変化素子の頭出しプロセスを示している。

【0039】

ここで、抵抗変化素子とは、電流、電圧、熱、磁場などにより抵抗値が変化するメモリセルのことである。抵抗変化素子をメモリセルとする半導体メモリとしては、例えば、磁気抵抗効果素子をメモリセルとするMRAM(Magnetic Random Access Memory)、金属酸化物をメモリセルとするReRAM(Resistive Random Access Memory)などがある。

【0040】

尚、ピラーが抵抗変化素子(例えば、磁気抵抗効果素子)を含む場合、ピラー間に満たされる材料の比誘電率、即ち、ピラー間容量が抵抗変化素子の性能に与える影響はない。このため、基本プロセスで説明したように、層間絶縁層に保護層としての機能を持つ窒化シリコンを使用したとしても、ピラー2間のみに満たされる層間絶縁層が抵抗変化素子の性能に悪影響を与えることはない。

【0041】

まず、図7に示すように、下部電極(LE:Lower electrode)11上にメモリセル材料層(積層構造)12’を形成する。また、メモリセル材料層12’上にハードマスク材料層13’を形成する。

【0042】

この後、例えば、PEP(Photo engraving process)を用いてレジストパターンを形成し、このレジストパターンをマスクにして、イオンビームエッチング、RIEなどの異方性エッチングにより、ハードマスク材料層13’をパターニングし、ハードマスク層を形成する。この後、レジストパターンを除去する。

【0043】

続けて、ハードマスク層をマスクにして、物理エッチング、例えば、GCIBエッチングにより、メモリセル材料層12’をパターニングする。ここで、ハードマスク層をマスクとするのは、レジストパターンをマスクにしてメモリセル材料層12’をエッチングすると、レジストパターンをアッシングにより除去するときに、メモリセル材料層12’が酸化されてしまうからである。

【0044】

以上のパターニングの結果、図8に示すように、下部電極(LE)11上に、抵抗変化素子(MTJ)12及びハードマスク層(HM)13を備えるピラーが形成される。

【0045】

次に、図9に示すように、GCIB法を用いて、下部電極11上に、ピラー(抵抗変化素子12及びハードマスク層13)を覆い、かつ、上面の最も低い部分Xが、ハードマスク層13の上面Y1よりも下にあり、ハードマスク層13の下面Y2よりも上にある絶縁層14を形成する。

【0046】

ここで、本実施例では、基本プロセスにない条件として、「GCIB法により形成される絶縁層14の上面の最も低い部分がハードマスク層13の下面よりも上である」ことが追加されている。これは、ピラーの頭出しを行うに当たって、抵抗変化素子12がエッチングされることを防止するためである。

【0047】

また、「絶縁層14の上面の最も低い部分がハードマスク層13の上面よりも下である」という条件は、「絶縁層14の上面の最も低い部分がピラーの上面よりも下である」という条件に等価である。

【0048】

GCIB法によれば、イオン化されたクラスターの流れに強い方向性が生じるため、下部電極11上及びハードマスク層13上に堆積する絶縁層14の上下方向の厚さt1、t2は、ハードマスク層13の側壁上に付着する絶縁層14の左右方向の厚さt3よりも大きくなる。このため、絶縁層14の上面の最も低い部分Xを、ハードマスク層13の上面Y1よりも下にし、かつ、ハードマスク層13の下面Y2よりも上にする制御が容易となる。

【0049】

次に、図10に示すように、CMP法を用いて、絶縁層14及びハードマスク層13を、絶縁層14の上面の最も低い部分X(図9のXに対応)まで研磨する。即ち、基本プロセスで説明したように、GCIB法により形成した絶縁層14の上面の最も低い部分XをCMPのエンドポイントとする。

【0050】

ここで、図9のステップにおいて、絶縁層14の上面の最も低い部分Xを、ハードマスク層13の上面Y1よりも下にし、かつ、ハードマスク層13の下面Y2よりも上にしたことにより、その最も低い部分XをCMPのエンドポイントとすると、ハードマスク層13の上面を絶縁層14から確実に露出させることができる。

【0051】

以上のステップにより、抵抗変化素子の頭出しプロセスが完了する。

【0052】

尚、GCIB法は、CVD法やALD法に比べて、低温での絶縁層14の堆積が可能である。例えば、CVD法やALD法では、400〜600℃の温度が必要であるが、GCIB法は、室温で行うことができる。このため、GCIB法により絶縁層14を堆積している最中に、抵抗変化素子12に悪影響を与えることがない。

【0053】

図11は、抵抗変化素子の例を示している。

【0054】

抵抗変化素子(MTJ)12は、例えば、磁気抵抗効果素子である。

【0055】

この場合、抵抗変化素子12は、下地層と、下地層上の記憶層(磁気フリー層)と、記憶層上のトンネルバリア層と、トンネルバリア層上の参照層(磁気ピンド層)と、参照層上のシフト調整層とを備える。

【0056】

ハードマスク層13は、抵抗変化素子12上に配置される。

【0057】

記憶層及び参照層は、例えば、CoFeBを備え、トンネルバリア層は、例えば、MgOを備える。シフト調整層は、例えば、Pt、Pd、Irのうちの1つを備える。ハードマスク層13は、例えば、TiN、TaNのうちの1つを備える。

【0058】

シフト調整層は、磁気抵抗層の構造に起因する磁気フリー層の磁気ヒステリシス曲線のシフトを調整する機能を有する。シフト調整層は、磁気ピンド層に付加されることによりその機能を発揮する。

【0059】

第1の例と第2の例が異なる点は、記憶層と参照層の平面サイズの関係にある。

【0060】

即ち、第1の例では、抵抗変化素子12内の記憶層及び参照層の平面サイズは、互いに同じである。また、この例は、記憶層及び参照層の側壁が下に向かってテーパ状である場合を含む。この場合、記憶層及び参照層の平面サイズは、互いに異なり、かつ、記憶層及び参照層の側壁は、斜めに連続的に変化する。

【0061】

また、第2の例では、抵抗変化素子12内の記憶層及び参照層の平面サイズは、互いに異なる。この例での「平面サイズが異なる」とは、記憶層及び参照層の側壁が不連続である場合を意味する。

【0062】

第2の例の特徴は、抵抗変化素子12をパターニングするときに発生する再付着層(Re-deposition layer)による記憶層と参照層との電気的ショートを防止できる点にある。

【0063】

尚、本例では、抵抗変化素子MTJの平面図(平面形状)は、円形を有しているが、これに限られない。抵抗変化素子MTJの平面形状は、四角形又は楕円に近い形状であっても構わない。

【0064】

3. 適用例

近年、不揮発性半導体メモリとして、トンネル磁気抵抗効果(TMR: Tunneling Magneto Resistive))を利用した磁気ランダムアクセスメモリ(MRAM)が開発されている。MRAMは、高速読み出し/書き込み、低消費電力動作及び大容量化が可能といった特徴を持ち、次世代ワーキングメモリとしての応用が期待されている。

【0065】

MRAMのメモリセルは、抵抗変化素子としての磁気抵抗効果素子である。近年では、磁気抵抗効果素子の記憶層の磁化を反転させるに当たり、スピン角運動量移動(SMT: Spin-momentum-transfer)現象を利用する、いわゆるスピン注入磁化反転方式を採用するのが主流である。この方式によれば、磁気抵抗効果素子のサイズが小さくなるに従い、磁化反転電流も小さくなる、というスケーラビリティ性を実現できるため、将来の大容量化にとって望ましい。

【0066】

また、スピン注入磁化反転方式は、記憶層及び参照層が垂直磁化(perpendicular magnetization)を持つ場合に特に有効である。この場合、磁気抵抗効果素子を、その形状に関係なく、微細化することができるからである。記憶層及び参照層が面内磁化(in-plane magnetization)を持つ場合には、磁気抵抗効果素子に形状磁気異方性を付けなければならないため、微細化には望ましくない。

【0067】

ここで、垂直磁化とは、残留磁化の方向が記憶層及び参照層の膜面(上面/下面)に対して垂直又はほぼ垂直となることである。この明細書において、ほぼ垂直とは、残留磁化の方向が記憶層及び参照層の膜面に対して、45°<θ≦90°の範囲内にあることを意味する。

【0068】

以下、実施例に係わる抵抗変化素子(磁気抵抗効果素子)の製造方法をMRAMに適用した場合について説明する。

【0069】

図12は、MRAMのメモリセルアレイの例を示している。

【0070】

メモリセルアレイ30は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)、複数のビアV0(0)〜V0(4)及び複数のFET SW(1)〜SW(4)を備える。

【0071】

複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)は、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される。

【0072】

また、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)のみを見たとき、これら複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)は、一定ピッチで格子状に配置される。同様に、複数のビアV0(0)〜V0(4)のみを見たとき、これら複数のビアV0(0)〜V0(4)は、一定ピッチで格子状に配置される。

【0073】

複数のFET SW(1)〜SW(4)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)と同様に、格子状に配置される。1つのFETは、第1の方向に隣接する1つの磁気抵抗効果素子と1つのビアとの間に接続される。

【0074】

例えば、FET SW(1)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)のうち第1の方向に隣接する磁気抵抗効果素子MTJ(1)とビアV0(1)との間に接続される。また、FET SW(2)は、複数の磁気抵抗効果素子MTJ(1)〜MTJ(5)及び複数のビアV0(0)〜V0(4)のうち第1の方向に隣接する磁気抵抗効果素子MTJ(2)とビアV0(2)との間に接続される。

【0075】

複数のワード線WL1,WL2,WL3,WL4,…は、第2の方向に延び、第2の方向に並ぶ複数のFETのゲートに共通に接続される。

【0076】

例えば、ワード線WL1は、FET SW(1)のゲートに接続され、ワード線WL2は、FET SW(2)のゲートに接続される。

【0077】

複数の上部電極UE(1)〜UE(5)の各々は、第2の方向に隣接する1つの磁気抵抗効果素子と1つのビアとの間に接続される。

【0078】

例えば、上部電極UE(1)は、ビアV0(0)及び磁気抵抗効果素子MTJ(1)に接続される。また、上部電極UE(2)は、ビアV0(1)及び磁気抵抗効果素子MTJ(2)に接続される。さらに、上部電極UE(3)は、ビアV0(2)及び磁気抵抗効果素子MTJ(3)に接続される。

【0079】

複数のビット線BL1a,BL1b,BL2a,BL2b,…は、第1の方向に延び、第1の方向に並ぶ複数の上部電極UE(1)〜UE(5)に一つおきに接続される。

【0080】

例えば、ビット線BL1a,BL2aは、奇数番目の上部電極UE(1),UE(3),UE(5)に接続される。また、ビット線BL1b,BL2bは、偶数番目の上部電極UE(2),UE(4)に接続される。

【0081】

第1の制御回路31は、複数のワード線WL1,WL2,WL3,WL4,…の電位を制御する。第2の制御回路32は、複数のビット線BL1a,BL1b,BL2a,BL2b,…の電位を制御する。

【0082】

例えば、磁気抵抗効果素子MTJ(1)について読み出し/書き込みを行うとき、第1の制御回路31を用いて、ワード線WL1の電位を“H”にし、その他のワード線WL2,WL3,WL4,…の電位を“L”にする。ここで、“H”とは、FETをオンにする電位のことであり、“L”とは、FETをオフにする電位のことである。

【0083】

この時、第2の制御回路32を用いて、複数のビット線BL1a,BL1b,BL2a,BL2b,…の電位を制御することにより、磁気抵抗効果素子MTJ(1)について読み出し/書き込みを行うことができる。

【0084】

図13は、図12のメモリセルアレイのデバイス構造の例を示している。

【0085】

半導体基板41内には、STI(Shallow Trench Isolation)構造の素子分離絶縁層42が配置される。素子分離絶縁層42に取り囲まれた素子領域(アクティブエリア)内には、複数のソース/ドレイン拡散層43が配置される。

【0086】

また、複数のソース/ドレイン拡散層43間のチャネル領域上には、ゲート絶縁層44、導電性シリコン層45、金属層46及びハードマスク層47が配置される。金属層46は、例えば、金属シリサイドを含む。金属層46は、単層でも、複数層でもよい。ハードマスク層47は、例えば、絶縁層である。

【0087】

導電性シリコン層45及び金属層46は、FETのゲートとして機能すると共に、第2の方向に延びることによりワード線WL1,WL2,WL3,WL4,…としても機能する。ゲート絶縁層44、導電性シリコン層45、金属層46及びハードマスク層47の側壁には、複数のソース/ドレイン拡散層43に対するコンタクトをセルフアラインで行うための側壁絶縁層48が配置される。

【0088】

複数のソース/ドレイン拡散層43上には、複数のコンタクトビア(プラグ)CBが配置される。複数のコンタクトビアCB上には、複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…が配置される。これら複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…上には、複数の上部電極UE(1),UE(2),UE(3),…が配置される。

【0089】

次に、図13のMRAMの製造方法を説明する。

【0090】

まず、図14に示すように、周知の技術を用いて、半導体基板41内に素子分離絶縁層42を形成し、かつ、半導体基板41上に複数のFETを形成する。複数のFETの各々は、ソース/ドレイン拡散層43、ゲート絶縁層44、導電性シリコン層45、金属層46、ハードマスク層47及び側壁絶縁層48を有する。

【0091】

また、ソース/ドレイン拡散層43上にセルフアラインでコンタクトビアCBを形成した後、コンタクトビアCB上に、複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…を形成する。複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…は、それぞれ、ピラー形状を有する。

【0092】

また、磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…は、ハードマスク層13をマスクにして、物理エッチング(例えば、GCIBエッチング)によりパターニングするのが望ましい。

【0093】

次に、図15に示すように、GCIB法を用いて、複数のFET上に、ピラー(複数の磁気抵抗効果素子MTJ(1),MTJ(2),MTJ(3),…及び複数のビアV0(0),V0(1),V0(2),…)を覆い、かつ、上面の最も低い部分Xが、ハードマスク層13(図14参照)の上面よりも下にあり、ハードマスク層13(図14参照)の下面よりも上にある絶縁層14を形成する。

【0094】

ここで、GCIB法により形成する絶縁層14が窒化シリコンである場合を説明する。

【0095】

まず、大気圧レベルのSiH4ガス及びN2ガスを真空チャンバー内に放出する。この時、これらのガスは、断熱膨張し、1K程度に冷却される。その結果、原子量10000程度のガスイオンクラスター29が形成される。また、クラスター29を、イオン化し、かつ、所定の加速電圧を与えることにより、クラスター29をウェハーの表面に照射する。

【0096】

このようなクラスター29の照射により、複数のFET上及びピラーの上面上には、厚い絶縁層14が形成され、ピラーの側壁上には、薄い絶縁層14が形成される。従って、絶縁層14の上面は、凹凸を有する形状となる。尚、絶縁層14の凸部は、ピラーの位置に対応する。

【0097】

尚、絶縁層14は、窒化シリコンに限られず、酸化シリコンであっても構わない

絶縁層14を酸化シリコンとするときは、例えば、大気圧レベルのSiH4ガス及びO2ガスを真空チャンバー内に放出すればよい。

【0098】

次に、図16に示すように、CMP法を用いて、絶縁層14を、絶縁層14の上面の最も低い部分X(図15のXに対応)まで研磨する。即ち、基本プロセスで説明したように、GCIB法により形成した絶縁層14の上面の最も低い部分XをCMPのエンドポイントとする。

【0099】

これにより、ハードマスク層13の上面及びビアV0(0),V0(1),V0(2),…の上面が、それぞれ、絶縁層14から露出する。

【0100】

最後に、第2の方向に隣接する1つのハードマスク層13と1つのビアV0(0),V0(1),V0(2),…とを、上部電極UE(1),UE(2),UE(3),…により互いに電気的に接続する。

【0101】

また、上部電極UE(1),UE(3),…に接続されるビット線BL1aを形成すると共に、上部電極UE(2),…に接続されるビット線BL1bを形成する。

【0102】

以上のステップにより、図13のMRAMが形成される。

【0103】

4. むすび

実施形態によれば、TATの短縮及び製造コストの低下を図ることができる。

【0104】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0105】

1: 第1の層(下地層)、 2’: 第2の層、 2: ピラー、 3,14: 絶縁層、 11: 下部電極、 12’: メモリセル材料層、 12: 抵抗変化素子、 13’: ハードマスク材料層、 13,47: ハードマスク層、 21: 台座部、 22: 研磨パッド、 23: 保持部、 24: ウェハー、 25: 供給部、 26: 制御部、 27: トルク電流モニター部、 30: メモリセルアレイ、 31: 第1の制御回路、 32: 第2の制御回路、 41: 半導体基板、 42: 素子分離絶縁層、 43: ソース/ドレイン拡散層、 44: ゲート絶縁層、 45: 導電性シリコン層、 46: 金属層、 48: 側壁絶縁層。

【特許請求の範囲】

【請求項1】

下地層上にピラーを形成する工程と、

GCIB法を用いて、前記下地層上に、前記ピラーを覆い、かつ、上面の最も低い部分が前記ピラーの上面よりも下にある絶縁層を形成する工程と、

CMP法を用いて、前記絶縁層及び前記ピラーを、前記絶縁層の上面の最も低い部分まで研磨する工程とを具備する半導体装置の製造方法。

【請求項2】

前記ピラーは、前記下地層上のメモリセルと、前記メモリセル上のハードマスク層とを備え、前記絶縁層を形成する工程において、前記絶縁層の上面の最も低い部分は、前記ハードマスク層の下面よりも上、前記ハードマスク層の上面よりも下にある請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁層を形成する工程において、前記下地層上の前記絶縁層の上下方向の厚さは、前記ピラーの側壁上の前記絶縁層の前記上下方向に垂直な左右方向の厚さよりも大きい請求項1に記載の半導体装置の製造方法。

【請求項4】

前記GCIB法は、SiH4とN2を含むクラスターを用いて行われる請求項1に記載の半導体装置の製造方法。

【請求項5】

前記ピラーは、GCIB法によりパターニングされる請求項1に記載の半導体装置の製造方法。

【請求項1】

下地層上にピラーを形成する工程と、

GCIB法を用いて、前記下地層上に、前記ピラーを覆い、かつ、上面の最も低い部分が前記ピラーの上面よりも下にある絶縁層を形成する工程と、

CMP法を用いて、前記絶縁層及び前記ピラーを、前記絶縁層の上面の最も低い部分まで研磨する工程とを具備する半導体装置の製造方法。

【請求項2】

前記ピラーは、前記下地層上のメモリセルと、前記メモリセル上のハードマスク層とを備え、前記絶縁層を形成する工程において、前記絶縁層の上面の最も低い部分は、前記ハードマスク層の下面よりも上、前記ハードマスク層の上面よりも下にある請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁層を形成する工程において、前記下地層上の前記絶縁層の上下方向の厚さは、前記ピラーの側壁上の前記絶縁層の前記上下方向に垂直な左右方向の厚さよりも大きい請求項1に記載の半導体装置の製造方法。

【請求項4】

前記GCIB法は、SiH4とN2を含むクラスターを用いて行われる請求項1に記載の半導体装置の製造方法。

【請求項5】

前記ピラーは、GCIB法によりパターニングされる請求項1に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−16557(P2013−16557A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−146577(P2011−146577)

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]