半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

フローティングゲートとコントロールゲートを有するスタック型フラッシュメモリを混載した半導体装置では、電源安定化に使用されるバイパスコンデンサとして、フラッシュメモリセルの構造を利用した素子が知られている。具体的には、シリコン基板に形成される不純物拡散領域とその上のトンネル酸化膜とフローティングゲート電極を含む第1のコンデンサ、およびフローティングゲート電極とONO膜とコントロールゲート電極を含む第2のコンデンサを有している。そして、第1、第2のコンデンサは並列に接続される。ONO膜は、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜を順に形成した積層構造の膜である。

【0003】

半導体基板の上に形成される別のコンデンサ(キャパシタ)として、多結晶シリコン膜、キャパシタ絶縁膜、多結晶シリコン膜を順に素子分離絶縁膜上に形成する構造が知られている。そのキャパシタ絶縁膜として、ONO膜、NO膜又はON膜が使用される。

【0004】

半導体基板の上に形成されるさらに別のコンデンサとして、EPROMの下部電極として使用される多結晶シリコン膜と、その上に順に形成される酸化膜(O)、多結晶シリコン膜とを有する構造が知られている。その酸化膜は、EPROMの下部電極である多結晶シリコン膜の上に順に形成される酸化膜(O)、ナイトライド膜(N)を除去した後に新たに形成される膜である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−016230号公報

【特許文献2】特開2004−356580号公報

【特許文献3】特開平5−21808号公報

【非特許文献1】Y. Yamaguchi et al., “ONO interpoly dielectric scaling limit for non-volatile memory devices”

【非特許文献2】S. Mori et al., “Polyoxide thinning limitation and superior ONO interpoly dielectric for nonvolatile memory device,” IEEE Trans. Elect. Dev., vol.ED-38, p.270, 1991

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のバイパスコンデンサの面積あたりの容量を増やす1つの方法として、例えば、フラッシュメモリの一部となるONO膜をできるだけ薄く形成する方法がある。しかし、ONO膜の層構造は、フラッシュメモリの信頼性に影響する重要なパラメータなので、コンデンサ容量を増やす目的で変更されることはない。

【0007】

例えば、フラッシュメモリのコントロールゲートとフローティングの間に挟まれるONO膜のうち上側の酸化膜(0)を薄くすると、フラッシュメモリのチャージロス量が増加することが知られている。従って、コンデンサの容量を増やすためだけにフラッシュメモリのONO膜の構造を変更することはできない。

【0008】

さらに、燐がドープされた2層のポリシリコン膜の間に形成される誘電体膜として単一

の酸化膜を下側のポリシリコン膜の上に形成する方法では、下側のポリシリコン膜表面のラフネスや酸化膜の膜質等によってリーク電流が発生することが知られている。また、燐を含むポリシリコン膜の表面は増速酸化し易いので、その上に単一の酸化膜を形成する場合には、酸化膜の厚さの制御が難しい。

【0009】

本発明の目的は、スループットを低下させずにメモリセルの誘電体膜とキャパシタの誘電体膜の構造を異ならせて同時に形成することができる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0010】

実施形態の1つの観点によれば、半導体基板の上方に第1の半導体膜を形成する工程と、第1領域の前記第1の半導体膜をエッチングする工程と、前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

実施形態の別の観点によれば、半導体基板の上方に第1の半導体膜を形成する工程と、第1領域内の前記第1の半導体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0011】

本実施形態によれば、酸化膜/窒化膜/酸化膜の複数層構造誘電体膜をメモリセル領域とコンデンサ形成領域に形成している。さらに、トランジスタ形成領域の半導体基板表面の他の酸化膜をエッチングして除去する際に、これと同時にコンデンサ形成領域の複数層構造誘電体膜の上側の酸化膜をエッチングしている。

このため、複数層構造誘電体膜の上側の酸化膜の除去のための独立したエッチング処理は不要になるので、コンデンサの誘電体膜として使用される複数層構造誘電体膜の面積当たりのコンデンサ容量を高めることが容易になる。しかも、半導体基板表面の酸化膜をエッチングする際に使用されるマスクを使用してメモリセル領域の複数層構造誘電体膜も覆うようにしている。従って、フラッシュメモリセルの2つの電極の間に挟まれる酸化膜/窒化膜/酸化膜の電気的特性を劣化させることはない。

【図面の簡単な説明】

【0012】

【図1A】図1A〜図1Cは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1D】図1D〜図1Fは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1G】図1G〜図1Iは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1J】図1J〜図1Lは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

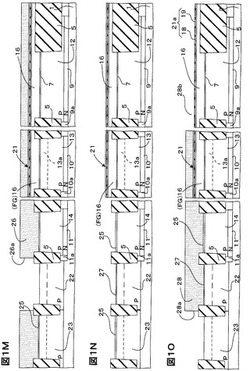

【図1M】図1M〜図1Oは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1P】図1P、図1Qは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1R】図1R、図1Sは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1T】図1T、図1Uは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1V】図1V、図1Wは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1X】図1X、図1Yは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図2】図2A、図2Bは、第1実施形態に係る半導体装置内のメモリセルの形成工程の一部を示す断面図である。

【図3】図3Aは、実施形態に係る半導体装置の製造工程で形成されるONO膜についての各種試験を行うために使用される試料の構造を示す断面図、図3Bは、実施形態に係る半導体装置の製造工程で形成されるNO膜についての各種試験を行うために使用される試料の構造を例示する断面図である。

【図4】図4は、実施形態に係る半導体装置の製造工程で形成されるONO膜、NO膜のそれぞれのコンデンサ容量の標準偏差の累積確率との関係を例示する図である。

【図5】図5は、図4の試験に使用されたONO膜、NO膜のそれぞれを酸化膜に換算した場合の厚さを例示する図である。

【図6】図6は、実施形態に係る半導体装置の製造工程で形成されるONO膜、NO膜のそれぞれの電圧と容量の関係を例示する図である。

【図7】図7は、図6の試験に使用されたONO膜、NO膜のそれぞれを酸化膜に換算した場合の厚さを例示する図である。

【図8】図8は、実施形態に係る半導体装置の製造工程で形成されるONO膜とNO膜のそれぞれについての絶縁破壊電圧の累積確率を例示する図である。

【図9】図9は、実施形態に係る半導体装置の製造工程で形成されるONO膜とNO膜のそれぞれについての印加電圧と電流の関係を例示する図である。

【図10】図10A〜図10Cは、第2実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図11A】図11A〜図11Cは、第3実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図11D】図11D〜図11Fは、第3実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【発明を実施するための最良の形態】

【0013】

以下に、図面を参照して本発明の好ましい実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

【0014】

(第1の実施の形態)

【0015】

図1A〜図1Yは、本実施形態に係る半導体装置の製造工程の一例を示す断面図である。図1A〜図1Yでは、図1Aに示すように周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。

【0016】

周辺トランジスタ領域Iでは、閾値電圧の高い順に第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VIが示されている。第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VIのそれぞれは、例えば、順に5.0V、3.3V、1.2V、の閾値電圧のMOSトランジスタが形成される領域である。また、周辺トランジスタ領域Iでは、特に図示しないが、p型MOSトランジスタ形成領域、その他の領域も有している。さらに、メモリセルアレイ領域IIでは、フラッシュメモリセルが形成されるメモリセル形成領域VII を縦横に複数有している。

【0017】

次に、図1Aに示す構造を形成するまでの工程を説明する。

【0018】

まず、半導体基板としてシリコン基板1を使用し、その上にイニシャル酸化膜2、シリコン窒化膜3を順に形成する。イニシャル酸化膜2は、熱酸化法、CVD法等のいずれかにより形成される。また、シリコン窒化膜3は、例えばCVD法により形成される。シリコン窒化膜3の上には、素子分離領域に開口部を有するとともにその他の領域を覆うレジストパターン(不図示)が形成される。

【0019】

続いて、レジストパターン(不図示)をマスクに使用してシリコン窒化膜3及びイニシャル酸化膜2を例えばフッ素系ガスを使用するドライエッチング法、例えば反応性イオンエッチング(RIE)法によりエッチングしてハードマスク4を形成する。ハードマスク4は、素子分離領域のシリコン基板1を露出する開口部4aを有する。

【0020】

さらに、ハードマスク4の開口部4aから露出したシリコン基板1をエッチングすることにより素子分離領域に素子分離溝1aを形成する。シリコン基板1のエッチング法として、例えば、塩素系ガス又は臭素系ガスを使用するRIE法が使用される。

【0021】

素子分離溝1aは、シリコン基板1のうち、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域III、第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VI、メモリセル形成領域VII 等を囲む位置に形成される。

【0022】

次に、図1Bに示す構造を形成するまでの工程を説明する。

【0023】

まず、素子分離溝1aの内周面を熱酸化して酸化膜(不図示)を形成した後に、シリコン酸化膜を素子分離溝1a内とシリコン窒化膜3上にCVD法により形成する。シリコン酸化膜は、素子分離溝1a内を完全に埋め込む厚さに形成される。続いて、シリコン窒化膜3の上面を露出させるまで、ハードマスク4上のシリコン酸化膜を例えば化学機械研磨(CMP)法により研磨する。これにより、素子分離溝1a内に残されたシリコン酸化膜を素子分離絶縁膜5として使用する。

【0024】

次に、図1Cに示すように、シリコン基板1及び素子分離絶縁膜5の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン6を形成する。レジストパターン6は、メモリセルアレイ領域IIを露出する開口部6aを有するとともに、周辺トランジスタ領域I、コンデンサ形成領域IIIを覆う形状を有する。

【0025】

次に、レジストパターン6の開口部6aを通してチャネルインプラントとしてn型又はp型の不純物をメモリセル形成領域VII のシリコン基板1にイオン注入してチャネル不純物濃度調整領域13aを形成する。その後に、レジストパターン6を除去する。

【0026】

続いて、図1Dに示す構造を形成するまでの工程を説明する。

【0027】

まず、シリコン窒化膜3を熱リン酸により除去し、さらにイニシャル酸化膜2をフッ酸により除去する。その後に、シリコン基板1の表面を熱酸化し、これによりシリコン基板1の表面に絶縁膜としてシリコン酸化膜7を形成する。シリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。続いて、シリコン基板1の上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン8を形成する。

【0028】

レジストパターン8は、コンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVを露出する開口部8a〜8cを有し、さらに第2、第3のn型MOSトランジスタ形成領域V、VIを覆う形状を有する。

【0029】

その後に、レジストパターン8の開口部8a〜8cを通してn型不純物、例えば燐又はヒ素をシリコン基板1内にイオン注入する。これにより、コンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVのそれぞれに深い第1〜第3のNウェル9、10、11を形成する。その後に、レジストパターン8の開口部8a〜8cを通してp型不純物、例えばホウ素をシリコン基板1内にイオン注入する。これによりコンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVにそれぞれ第1、第2及び第3のPウェル12、13、14を形成する。

【0030】

それらの不純物イオン注入の際には、第1、第2及び第3のPウェル12、13、14の下にそれぞれNウェル9、10、11が存在する不純物プロファイルを形成するように、n型及びp型の不純物のドーズ量、加速エネルギーが調整される。その後、レジストパターン8が除去される。

【0031】

次に、図1Eに示す構造を形成するまでの工程を説明する。

【0032】

まず、シリコン基板1の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン15を形成する。レジストパターン15は、第1のn型MOSトランジスタ形成領域IV、メモリセル形成領域VII及びコンデンサ形成領域IIIを囲んでいる素子分離絶縁膜5を露出する開口部15aを有し、さらに、第1、第2、第3のn型MOSトランジスタ形成領域IV、V、VI、メモリセル形成領域VII及びコンデンサ形成領域IIIを覆う形状を有する。

【0033】

その後に、レジストパターン15の開口部15aを通して、n型不純物をイオン注入することにより、第1、第2及び第3のPウェル12、13、14のそれぞれの周囲に高電圧用のNウェル9a、10a、11aを形成する。これにより、高電圧用のNウェル9a、10a、11aは、Pウェル12、13、14の下のNウェル9、10、11に接続される。その後、レジストパターン15は除去される。なお、イオン注入後に、シリコン基板1表面のシリコン酸化膜7を除去し、再び形成してもよい。

【0034】

次に、図1Fに示す構造を形成するまでの工程を説明する。

【0035】

まず、シリコン基板1上のシリコン酸化膜7と素子分離絶縁膜5の上に、半導体膜としてアモルファスシリコン膜16をCVD法により約50nm〜150nmの厚さに形成する。なお、その後、アモルファスシリコン膜16のうちコンデンサ形成領域IIIに例えば

n型不純物をイオン注入してもよい。

【0036】

続いて、アモルファスシリコン膜16上にフォトレジストを塗布した後に、フォトレジストを露光、現像することにより、レジストパターン17を形成する。レジストパターン17は、メモリセル形成領域VIIとコンデンサ形成領域IIIを覆うとともに、周辺トランジスタ領域Iを露出する形状を有する。また、レジストパターン17は、図2Aに示すように、メモリセル形成領域VIIのそれぞれの周囲に開口部17aを有している。図2A、図2Bは、それぞれ図1F、図1GのX−X線から見た断面図である。

【0037】

続いて、図1G、図2Bに示すように、レジストパターン17をマスクに使用し、露出しているアモルファスシリコン膜16をエッチングにより除去する。この場合のエッチング法として、例えば、塩素系ガス又は臭素系ガスを使用するRIE法を使用する。これにより、メモリセルアレイ領域II内でメモリセル形成領域VII毎に分割されたアモルファスシリコン膜16は、後の工程でさらにパターニングされてフラッシュメモリセルのフローティングゲート電極FGとして使用される。その後、レジストパターン17は除去される。

【0038】

次に、図1Hに示すように、シリコン基板1表面のシリコン酸化膜7、アモルファスシリコン膜16、素子分絶縁膜5等の上面に、シリコン酸化膜18をCVD法により例えば4nm〜6nmの厚さに形成する。さらに、シリコン酸化膜18上にシリコン窒化膜19をCVD法により例えば7nm〜9nmの厚さに形成する。続いて、シリコン窒化膜19表面を熱酸化法により酸化し、酸化膜20を形成する。この時の熱酸化量は、シリコンの酸化の厚さに換算すると厚さ200〜300nmで、シリコン窒化膜18上に形成される酸化膜20の膜厚は4〜6nmである。このようにして、シリコン酸化膜7の上とアモルファスシリコン膜16の上に、複数層構造誘電体膜であるONO膜21が形成される。

【0039】

次に、図1Iに示す構造を形成するまでの工程を説明する。

【0040】

まず、ONO膜21上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン(不図示)を形成する。このレジストパターンは、周辺トランジスタ領域Iの第2のn型MOSトランジスタ形成領域VのONO膜21を露出する開口部を有し、第1、第3のn型MOSトランジスタ形成領域IV、VI、メモリセルアレイ領域II、コンデンサ形成領域III等を覆う形状を有する。

【0041】

その後に、そのレジストパターンの開口部からONO膜21を通してシリコン基板1内にp型不純物をイオン注入することにより、第2のn型MOSトランジスタ形成領域Vのシリコン基板1内に第4のPウェル22を形成する。また、第4のPウェル22を形成する前か後に、そのレジストパターンの開口部を通してシリコン基板1内にチャネル不純物濃度調整用の不純物をイオン注入する。その後に、そのレジストパターンを除去する。

【0042】

この後に、ONO膜21上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン(不図示)を形成する。このレジストパターンは、周辺トランジスタ領域Iの第3のn型MOSトランジスタ形成領域VIのONO膜21を露出する開口部を有し、第1、第2のn型MOSトランジスタ形成領域IV、V、メモリセルアレイ領域II、コンデンサ形成領域III等を覆う形状を有する。その後に、そのレジストパターンの開口部を通してシリコン基板1内にp型不純物をイオン注入することにより、第3のn型MOSトランジスタ形成領域VIのシリコン基板1内に第5のPウェル23を形成する。また、第5のPウェル23を形成する前か後に、そのレジストパターンの開口部を通してシリコン基板1内にチャネル濃度調整用の不純物をイオン注入する。その後に、そのレジストパターンを除去する。

【0043】

次に、図1Jに示すように、ONO膜21の上にフォトレジストを塗布し、これを露光、現像することにより、周辺トランジスタ領域Iを露出するとともに、メモリセルアレイ領域II、コンデンサ形成領域IIIを覆うレジストパターン24を形成する。

【0044】

続いて、図1Kに示すように、レジストパターン24から露出した領域のONO膜21の酸化膜20、シリコン窒化膜19を例えばRIE法により除去する。その後に、周辺トランジスタ領域Iにおけるシリコン基板1表面上のシリコン酸化膜7、18をフッ酸によりウェットエッチングして除去する。

【0045】

レジストパターン24を除去した後に、図1Lに示すように、周辺トランジスタ領域Iにおけるシリコン基板1の露出面に熱酸化法又はCVD法により第1ゲート絶縁膜25としてシリコン酸化膜を約5nm〜15nmの厚さに形成する。この場合、メモリセルアレイ領域II、コンデンサ形成領域IIIに存在するONO膜21の酸化膜20表面は殆ど酸化されない。

【0046】

次に、図1Mに示す構造を形成するまでの工程を説明する。

まず、第1ゲート絶縁膜25及びONO膜21の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン26を形成する。レジストパターン26は、シリコン基板1において、第2のn型MOSトランジスタ形成領域Vの上に開口部26aを有する一方、第1、第3のn型MOSトランジスタ形成領域IV、VI、メモリセルアレイ領域II、コンデンサ形成領域IIIを覆う形状を有する。

【0047】

続いて、レジストパターン26をマスクに使用し、フッ酸を用いるウェットエッチングによって第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を除去し、そこからシリコン基板1を露出させる。その後にレジストパターン26を除去する。

【0048】

次に、図1Nに示すように、シリコン基板1の表面を熱酸化することにより、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27としてシリコン酸化膜を形成する。その熱酸化によれば、第1、第3のn型MOSトランジスタ形成領域IV、VIのシリコン基板1表面も酸化されるので、シリコン酸化膜である第1のゲート絶縁膜25の厚さが約10nm〜20nmまで増える。この場合、ONO膜21は殆ど酸化されない。その後に、レジストパターン26を除去する。

【0049】

次に、図1Oに示す構造を形成するまでの工程を説明する。

【0050】

まず、第1、第2ゲート絶縁膜25、27及びONO膜21の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン28を形成する。レジストパターン28は、シリコン基板1において、第3のn型MOSトランジスタ形成領域VI、コンデンサ形成領域IIIの上に開口部28a、28bを有する一方、第1、第2のn型MOSトランジスタ形成領域IV、V、メモリセル領域IIを覆う形状を有する。

【0051】

続いて、レジストパターン28をマスクに使用し、フッ酸を用いるウェットエッチングによって第3のn型MOSトランジスタ形成領域VIの第1のゲート絶縁膜25を除去し、そこからシリコン基板1を露出させる。同時に、コンデンサ形成領域IIIのONO膜21の酸化膜20を除去し、その下のシリコン窒化膜18を露出させてONO膜20を二層構造誘電体膜であるNO膜21aに変える。その後にレジストパターン28を除去する。

【0052】

次に、図1Pに例示するように、シリコン基板1の表面を熱酸化することにより、第3のn型MOSトランジスタ形成領域VI内に第3のゲート絶縁膜29としてシリコン酸化膜

を約1nm〜3nmの厚さに形成する。その熱酸化によれば、第1、第2のn型MOSトランジスタ形成領域IV、V内のシリコン基板1表面も酸化されるので、シリコン酸化膜である第1、第2のゲート絶縁膜25、27の厚さが増加する。その増加量は、例えば約1nm〜3nmである。この場合、ONO膜21は殆ど酸化されない。

【0053】

次に、図1Qに示すように、第1〜第3のゲート絶縁膜25、27、29、ONO膜21及びNO膜21aの上に、半導体膜としてポリシリコン膜30をCVD法により形成する。続いて、ポリシリコン膜30上に、シリコンリッチなシリコン窒化膜を反射防止(ARC)膜31としてCVD法により形成する。

【0054】

次に、図1Rに示す構造を形成するまでの工程を説明する。

【0055】

まず、ARC膜31上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン32を形成する。レジストパターン32は、周辺トランジスタ領域IではARC膜31を覆い、メモリセルアレイ領域IIではゲート電極及び配線の平面形状を有し、コンデンサ形成領域IIIではコンデンサの上部及び下部電極の平面形状を有している。

【0056】

続いて、レジストパターン32をマスクに使用して、ARC膜31からアモルファスシリコン16までの層をエッチングする。エッチング方法として、例えばRIE法を使用し、ARC膜31、NO膜21aのエッチングガスとしてフッ素系ガスを使用し、ポリシリコン膜30、アモルファスシリコン膜16のエッチングガスとして例えば塩素含有ガスを使用する。

【0057】

これにより、メモリセルアレイ領域IIにおいてパターニングされたポリシリコン膜30はワード線を兼ねたコントロールゲート電極CGとして使用され、その下のアモルファスシリコン膜16は、フローティングゲート電極FGとして使用される。

【0058】

また、コンデンサ形成領域IIIでは、パターニングされたポリシリコン膜30、アモルファスシリコン膜16はそれぞれ第1の電極33a、第2の電極33bとなり、それらの間のNO膜21aは誘電体膜33cとなる。これにより、第1の電極33a、第2の電極33b及びそれらの間のNO膜21aにより第1のコンデンサQ1が形成される。また、第2の電極33bとシリコン酸化膜7と第1のPウェル12により第2のコンデンサQ2が形成される。この場合、シリコン酸化膜7は誘電体膜である。第1のコンデンサQ1と第2のコンデンサQ2は、第2の電極33bを共通電極として接続されている。その後に、レジストパターン32を除去する。

【0059】

次に、図1Sに示すように、ARC膜31をマスクに使用して、コントロールゲート電極CG、フローティングゲート電極FGの側壁を熱酸化することにより、側壁酸化膜34aが形成される。これと同時に、コンデンサ形成領域IIIにおいて、第1の電極33a、第2の電極33bの側壁も酸化されて側壁酸化膜34bが形成される。

【0060】

その後に、パターニングされたARC膜31及びポリシリコン膜30をマスクに使用してメモリセル形成領域VII、コンデンサ形成領域IIIの第1、第2のPウェル12、13にn型不純物、例えばヒ素又は燐をイオン注入する。これにより、第2のPウェル13内において、フローティングゲート電極FGの両側にn型エクステンション領域35a、35bが形成される。これと同時に、第1のPウェル12内において、第2の電極33bの側方にもn型エクステンション領域35cが形成される。その後に、コントロールゲート電極CG、フローティングゲート電極FG、第1の電極33a、第2の電極33bの側壁を再び熱酸化することにより、側壁酸化膜34a、34bの膜厚を増加させる。

【0061】

続いて、図1Tに示す構造を形成するまでの工程について説明する。

【0062】

まず、コントロールゲート電極CG、ARC膜31、シリコン酸化膜7等の上に、シリコン窒化膜をCVD法により形成する。その後に、シリコン酸化膜7が露出するまでシリコン窒化膜及びARC膜31をエッチバックする。これにより、コントロールゲート電極CG、フローティングゲート電極FGと第1、第2の電極33a、33bのそれぞれの側方に残されたシリコン窒化膜をサイドウォール36a、36bとして使用する。

【0063】

次に、図1Uに示す構造を形成するまでの工程を説明する。

【0064】

まず、ポリシリコン膜30、コントロールゲート電極CG、フローティングゲート電極FG等の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン37を形成する。レジストパターン37は、周辺トランジスタ領域Iで複数のゲート電極の平面形状を有し、メモリセルアレイ領域IIでフローティングゲート電極FG、第2のウェル13を覆い、コンデンサ形成領域IIIで第1の電極33aの一部に重なる開口部37aを有する。

【0065】

続いて、レジストパターン37をマスクに使用し、ポリシリコン膜30をエッチングすることにより第1〜第3のn型MOSトランジスタ形成領域IV〜VIのそれぞれにゲート電極30a〜30cを形成する。これと同時に、第1の電極33aの一部にコンタクトホール33dを形成する。その後にレジストパターン37を除去する。

【0066】

次に、図1Vに示す構造を形成するまでの工程を説明する。

【0067】

まず、第3、第4、第5のPウェル14、22、23のいずれか1つの上に開口部を有し、さらに第1、第2のPウェル12、13を覆う3つのレジストパターン(不図示)をシリコン基板1の上方に順に交換して形成する。そして、それらのレジストパターンの開口部を通して第3、第4、第5のPウェル14、22、23のそれぞれに順にn型不純物をイオン注入する。この場合、第1、第2、第3のゲート電極30a、30b、30cはマスクとして機能する。これにより、第3、第4、第5のPウェル14、22、23ではそれぞれ第1、第2、第3のゲート電極30a、30b、30cの両側にn型エクステンション領域38a、38b、39a、39b、40a、40bが形成される。

【0068】

第5のPウェル23では、n型エクステンション領域40a、40bを形成する前にp型不純物をイオン注入することによりn型エクステンション領域40a、40bの下にポケット領域(不図示)を形成する。

【0069】

次に、図1Wに示す構造を形成するまでの工程を説明する。

【0070】

まず、シリコン基板1の上方の全体に絶縁膜としてシリコン酸化膜をCVD法により形成し、これにより第1〜第3のゲート電極30a〜30c等を覆う。その後、その絶縁膜をエッチバックする。そのエッチバックは、第1〜第3のゲート電極30a〜30cの両側において、第1〜第3のゲート絶縁膜30a〜30c又はシリコン基板1表面が露出するまで行う。

【0071】

これにより、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、第2の電極33bの側方にその絶縁膜をサイドウォール41a〜41eとして残す。この場合、第1のコンデンサQ1の第1の電極33aのコンタクトホール33d内にもサイドウォール41fが形成されるので、コンタクトホール33d内周面において第1の電極

33aがサイドウォール41fにより覆われる。このオーバーエッチングにより、コンタクトホール33dの底の誘電体膜33c、即ちNO膜21aは除去される。

【0072】

続いて、第1〜第5のPウェル12〜14、22、23のいずれか1つの上に開口部を有し、さらに他のPウェル12〜14、22、23を覆うレジストパターン(不図示)をシリコン基板1の上方に順に交換して形成する。さらに、それらの開口部を通して第1〜第5のPウェル12〜14、22、23のそれぞれにn型不純物をイオン注入する。不純物のイオン注入条件は、注入毎に調整される。

【0073】

n型不純物のイオン注入時には、第1の電極33a、コントロールゲート電極CG、第1〜第3のゲート電極30a〜30c及びサイドウォール36ab、36b、41a〜41fはそれぞれマスクとして機能する。

【0074】

これにより、第1の電極33aの側方の第1のPウェル12内に高不純物濃度拡散領域42が形成される。また、その他の電極30a〜30c、FGの両側方の第2〜第5のPウェル13、14、22、23内に高不純物濃度のn型ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bが形成される。n型ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bは、n型エクステンション領域35a〜35c、38a、38b、39a、39b、40a、40bに接続される。

【0075】

次に、図1Xに示す構造を形成するまでの工程を説明する。

【0076】

まず、シリコン基板1の表面に形成されたゲート絶縁膜25、27、29及びシリコン酸化膜7のうちゲート電極30a〜30c、フローティングゲート電極FG等に覆われずに露出した部分を例えばフッ酸により除去する。その後に、シリコン基板1の上方にコバルト膜(不図示)を例えばスパッタ法により形成する。さらに、加熱処理によって、シリコンとコバルトを合金化してコバルトシリサイド層47a〜47oを形成する。コバルトシリサイド層47a〜47oは、ソース/ドレイン領域42、43a、43b、44a、44b、45a、45b、46a、46bの上層と、ゲート電極30a〜30c、コントロールゲート電極CG、第1の電極33aの上層に形成される。さらに、第1の電極33aのコンタクトホール33dの底に露出している第2の電極33bの上層にも形成される。続いて、シリコン基板1の上方のコバルト膜を除去する。

【0077】

以上により、第1のn型MOSトランジスタ形成領域IVには、第3のPウェル14、ソース/ドレイン領域44a、44b、第1のゲート電極30a等を有する第1のn型MOSトランジスタT1が形成される。また、第2のn型MOSトランジスタ形成領域Vには、第4のPウェル22、ソース/ドレイン領域45a、45b、第2のゲート電極30b等を有する第2のn型MOSトランジスタT2が形成される。さらに、第3のn型MOSトランジスタ形成領域VIには、第5のPウェル23、ソース/ドレイン領域46a、46b、第3のゲート電極30c等を有する第3のn型MOSトランジスタT3が形成される。

【0078】

また、メモリセル形成領域VIIには、第2のPウェル13、ソース/ドレイン領域43a、43b、ゲート絶縁膜7、フローティングゲート電極FG、ONO膜21、コントロールゲート電極CG等を有するフラッシュメモリセルMCが形成される。

【0079】

次に、図1Yに示す構造を形成するまでの工程を説明する。

【0080】

まず、シリコン基板1の上方にカバー絶縁膜48としてシリコン窒化膜をCVD法によ

り形成し、そのカバー絶縁膜47により第1〜第3のゲート電極30a〜30c、コバルトシリサイド層47a〜47o、サイドウォール41a〜41f等を覆う。

【0081】

次に、カバー絶縁膜48の上に層間絶縁膜49としてシリコン酸化膜をCVD法により形成する。続いて、層間絶縁膜49の表面を化学機械研磨(CMP)法により研磨して平坦にする。

【0082】

続いて、層間絶縁膜49上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン(不図示)を形成する。このレジストパターンは、ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bの上方と、第1のPウェル12内の高不純物濃度拡散領域42、第1の電極33aのコンタクトホール33dとその側方の一部などの上方に開口部を有する。その後に、レジストパターンをマスクにして、層間絶縁膜49、カバー絶縁膜48をエッチングする。これにより、ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bと高不純物濃度拡散領域42表面のシリサイド層47c、47e、47f、47h、47i、47k、47l、47n、47oに達する深さのコンタクトホール49c〜49kを形成する。同時に、第1の電極33aの上にビアホール49bを形成し、さらに、第1の電極33aのコンタクトホール33dを通して第2の電極33bの表面のシリサイド層47bに達するビアホール49aを形成する。その後に、レジストパターンを除去する。

【0083】

続いて、ビアホール49a、49b、コンタクトホール49c〜49kの内面と層間絶縁膜49の上面にチタン膜、窒化チタン膜を順に形成する。続いて、ビアホール49a、49b、コンタクトホール49c〜49k内を完全に充填する厚さのタングステン膜を窒化チタン膜の上に形成する。さらに、層間絶縁膜49上のそれらの金属膜をCMPにより除去する。これにより、ビアホール49a、49b、コンタクトホール49c〜49k内に残された窒化チタン膜、チタン膜、タングステン膜を同遠征プラグ50a〜50kとして使用する。

【0084】

さらに、特に図示しないが、層間絶縁膜49の上に金属膜、例えばアルミニウム膜を形成した後に、アルミニウム膜をパターニングすることにより、コンタクトプラグの上に接続される配線、導電性パッド等などの金属パターンを形成する。その後に、特に図示しないが、層間絶縁膜49及び金属パターンの上に上側の層間絶縁膜を形成し、さらに上側の層間絶縁膜内にビアを形成し、その後に上側の層間絶縁膜の上に配線を形成する、といった工程を繰り返すことにより、半導体装置の基本構造を完成させる。

【0085】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用する際に、酸化膜20を選択的に除去してNO膜21aに変えている。また、NO膜21aの上に存在した酸化膜20は、図1Oに示したように、周辺トランジスタ領域Iの第5のPウェル23の上に形成された第1のゲート絶縁膜25であるシリコン酸化膜と同時に除去される。

【0086】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を入れる必要はなく、レジストパターン28の形状を調整するに留まるので、スループットの低下を防止することができる。しかも、NO膜21aの上に形成された酸化膜20は、その下のシリコン窒化膜19に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まり、エッチングの制御性に優れる。

【0087】

ところで、周辺トランジスタ領域の第3〜第5のPウェル14、22、23の表面を熱酸化する際に、NO膜21aの表面も酸化される。この場合、図1Pに示すように、NO

膜21aのシリコン窒化膜19の表面も酸化されてシリコン窒化酸化膜19aが形成される。しかし、その厚さは、ONO膜21の上側のシリコン酸化膜20よりも薄く、例えば1nmより小さい値、即ち数Åと極めて薄く、酸化前後のNO膜21aの静電容量は、実質的に同じ、又はONO膜21よりも大きい。

【0088】

次に、ONO膜21の上側の酸化膜20を除去せずにコンデンサの誘電体膜として使用する場合と、ONO膜21の上側の酸化膜20を除去して形成されたNO膜21aをコンデンサの誘電体膜として使用する場合の特性を比較する。ここで、図3Aに示すように、フローティングゲート電極FGとコントロールゲート電極CGによりONO膜21を挟んだ構造を有するコンデンサを第1の試料となし、シリコン基板1上に複数形成する。さらに、図3Bに示すように、フローティングゲート電極FGとコントロールゲート電極CGによりNO膜21aを挟んだ構造を有するコンデンサを第2の試料となし、シリコン基板1上に複数形成する。

【0089】

この場合のONO膜21aにおいて、下側のシリコン酸化膜18と上側の酸化膜20とそれらの間のシリコン窒化膜19のそれぞれの厚さを約5nm、約5nm、約5nmとする。また、NO膜21aにおいて、シリコン酸化膜18、シリコン窒化膜19のそれぞれの厚さを約5nm、約5nmとする。

【0090】

第1、第2の試料について、図3A、図3Bのそれぞれに示すコントロールゲート電極CGとフローティングゲート電極FGに電圧VCGを印可して種々の試験を行った。その試験結果を以下に説明する。

【0091】

まず、第1、第2の試料のコンデンサの容量値を調べたところ、図4に示す結果が得られた。また、図4に示す結果に基づいて第1、第2の試料のコンデンサの容量をシリコン酸化膜に換算した場合の膜厚を調べたところ、図5に示す結果が得られた。

【0092】

図4において、横軸はコンデンサ容量の値を示し、縦軸は標準偏差の累積確率の値を示している。これにより、NO膜21aを有する第2の試料は、ONO膜20を有する第1の試料よりも面積当たりの容量が約25%大きくなっている。また、図5において、第2の試料のNO膜は、第1の試料のONO膜に比べて酸化物換算膜厚が2.5nmほど薄くなっている。

【0093】

次に、第1の試料と第2の試料のそれぞれのコンデンサについて電圧の変化に対する容量の変化を調べたところ、図6に示す結果が得られた。図6によれば、第1、第2の試料のそれぞれのコンデンサのONO膜、NO膜について、電圧が変化してもそれらの容量は顕著に変化していない。図6の測定データに基づいて、容量をシリコン酸化膜に換算した場合の膜厚を図7に示す。

【0094】

ONO膜21を有する第1の試料とNO膜21aを有する第2の試料の絶縁耐圧を調べたところ、図8に示す結果が得られた。図8によれば、NO膜は、ONO膜に比べて、絶縁耐圧は低下するが、その耐圧は10V以上になっているので、コンデンサの誘電体膜として使用する場合に問題は生じない。

【0095】

また、NO膜とONO膜のそれぞれについてリーク電流を調べたところ、図9に示す結果が得られた。コンデンサに印加される電圧は−5V〜5Vの範囲が一般的であり、図9におけるその電圧範囲内ではONO膜、NO膜の双方のリーク電流は実質的に流れていない。従って、NO膜はコンデンサの誘電体膜として十分な能力を備えている。

【0096】

(第2の実施の形態)

図10A〜図10Cは、第2実施形態に係る半導体装置の製造工程の一例を示す断面図であり、図1A〜図1Yと同じ符号は同じ要素を示している。また、図10A〜図10Cでは、第1実施形態と同様に、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。特に図示しないが、周辺トランジスタ領域Iは、p型MOSトランジスタ形成領域、その他の領域もさらに有している。

【0097】

第2実施形態に係る半導体装置の製造工程では、まず、第1実施形態に係る図1A〜図1Eに示すと同様に、シリコン基板1に第1〜第3のPウェル12,13、14を形成し、第1〜第3のPウェル12〜13の下と横にねNウェル9,9a、10、10a、11、11aを形成する。さらに、第1実施形態に係る図1Fに示すと同様に、シリコン基板1の上にシリコン酸化膜7、アモルファスシリコン膜16を順に形成する。この場合のシリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。

【0098】

その後に、図1Gに示すと同様に、アモルファスシリコン膜16をパターニングすることにより、周辺トランジスタ領域Iからアモルファスシリコン膜16を除去し、メモリセル形成領域VIIではフローティングゲート電極FGを形成する。この場合、アモルファスシリコン膜16は、コンデンサ形成領域IIIの全体に残される。さらに、図1Hに示すように、アモルファスシリコン膜16の上とシリコン基板1の上方にONO膜21を形成する。続いて、図1Iに示すように、第2、第3のn型MOSトランジスタ形成領域V、VIのシリコン基板1内に第4、第5のPウェル22,23を形成する。その後に、図1J、図1Kに示すと同様に、周辺トランジスタ領域Iのシリコン酸化膜7及びONO膜21を除去する。

【0099】

続いて、図1Lに示すと同様に、周辺トランジスタ領域Iの第3〜第5のPウェル14、22、23の表面を熱酸化して、第1のゲート絶縁膜25を形成する。この場合、ONO膜21の表面は殆ど酸化されない。以上の工程は、第1実施形態と同様である。

【0100】

次に、図10Aに例示する構造を形成するまでの工程を説明する。

【0101】

まず、シリコン基板1の全体にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン51を形成する。レジストパターン51は、コンデンサ形成領域IIIのONO膜21と第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を露出するとともに、第1、第3のn型MOSトランジスタ形成領域IV、VIとメモリセルアレイ領域IIを覆う形状を有する。

【0102】

続いて、レジストパターン51をマスクに使用し、コンデンサ形成領域III内のONO膜21の酸化膜20、および第2のn型MOSトランジスタ形成領域V内の第1のゲート絶縁膜25を同時にフッ酸により除去する。これにより、コンデンサ形成領域III内におけるONO膜21は、シリコン酸化膜18とシリコン窒化膜19の二層構造を有するNO膜21aに変わる。その後に、レジストパターン51を除去する。

【0103】

次に、図10Bに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を熱酸化法により酸化し、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27を形成するとともに、第1のゲート絶縁膜25の厚さを増加させる。

【0104】

続いて、図10Cに例示するように、第1、第2のゲート絶縁膜25、27、ONO膜21、NO膜21aの上にフォトレジストを塗布し、これを現像してレジストパターン52を形成する。レジストパターン52は、第5のPウェル23の上に開口部52aを有し、また第3、第4のウェル14、22及びポリシリコン膜16を覆う形状を有している。その後に、レジストパターン52の開口部52aを通して第1のゲート絶縁膜25をフッ

酸により除去する。その後に、レジストパターン52を除去する。

【0105】

次に、第1実施形態の図1Pに示すと同様に、第5のPウェル23の表面を熱酸化して第3のゲート絶縁膜29を形成するとともに、第1、第2のゲート絶縁膜25、27の厚さを増加させる。第2、第3のゲート絶縁膜25、27を形成する熱酸化の際には、NO膜21aのシリコン窒化膜19の表面も酸化され、その表面には除去された第2のシリコン酸化膜20より薄い、例えば1nm以下の厚さのシリコン窒化酸化膜19aが形成される。その薄いシリコン窒化酸化膜19aはNO膜21aの誘電容量を実質的に変えない。

【0106】

さらに、第1実施形態と同様に、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、コントロールゲート電極CG,第1、第2の電極33a、33b等を形成する。さらに、第2〜第5のPウェル13,14、22、23内にソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bを形成し、併せて第1のPウェル13内に高不純物濃度拡散領域42を形成する。

【0107】

これにより、第1実施形態と同様に、第1〜第3のn型MOSトランジスタT1〜T3、フラッシュメモリセルMC、第1、第2のコンデンサQ1、Q2を形成する。フラッシュメモリセルMCにおいて、コントロールゲート電極CGとフローティングゲート電極FGの間にはONO膜21が形成されている。また、第1のコンデンサQ1は、第1実施形態と同様に、第1、第2の電極33a、33bの間に誘電体膜33cとしてNO膜21aが形成される。その後の工程は、第1実施形態と同様である。

【0108】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用する際に、酸化膜20を選択的に除去してNO膜21aに変えている。また、ONO膜21のうち上側の酸化膜20は、図10Aに示したように、周辺トランジスタ領域Iの第4のPウェル22の上に形成された第1のゲート絶縁膜25であるシリコン酸化膜と同時に除去される。

【0109】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を新たに入れる必要はなく、レジストパターン51の形状を変更するに留まるので、スループットの低下を防止することができる。しかも、ONO膜21の上側の酸化膜20は、その下のシリコン窒化膜に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まるのでエッチングの制御性に優れる。

【0110】

また、第1実施形態と同様に、NO膜21aを誘電体膜33cとして使用する第1のコンデンサQ1は、ONO膜21を使用する場合よりも単位面積当たりのコンデンサ容量を約25%増加させることができる。

【0111】

(第3の実施の形態)

図11A〜図11Fは、第3実施形態に係る半導体装置の製造工程の一例を示す断面図であり、図1A〜図1Yと同じ符号は同じ要素を示している。また、図11A〜図11Fでは、第1実施形態と同様に、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。特に図示しないが、周辺トランジスタ領域Iは、p型MOSトランジスタ形成領域、その他の領域もさらに有している。

【0112】

第3実施形態に係る半導体装置の製造工程は、まず、第1実施形態に係る図1A〜図1Eに示すと同様に、シリコン基板1に第1〜第3のPウェル12,13、14を形成し、第1〜第3のPウェル12〜13の下と横に深いNウェル9,9a、10、10a、11、11aを形成する。さらに、第1実施形態に係る図1Fに示すと同様に、シリコン基板

1の上にシリコン酸化膜7、アモルファスシリコン膜16を順に形成する。この場合のシリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。

【0113】

その後に、図1Gに示すと同様に、アモルファスシリコン膜16をパターニングすることにより、周辺トランジスタ領域Iからアモルファスシリコン膜16を除去し、メモリセル形成領域VIIではフローティングゲート電極FGを形成する。この場合、アモルファスシリコン膜16は、コンデンサ形成領域IIIの全体に残される。さらに、図1Hに示すように、アモルファスシリコン膜16の上とシリコン基板1の上方にONO膜21を形成する。続いて、図1Iに示すように、第2、第3のn型MOSトランジスタ形成領域V、VIのシリコン基板1内に第4、第5のPウェル22,23を形成する。

【0114】

次に、図11A示すように、ONO膜21の上にフォトレジストを塗布し、これを露光現像することによりレジストパターン53を形成する。レジストパターン53は、周辺トランジスタ領域IのONO膜21を露出させるとともに、メモリセルアレイ領域II、コンデンサ形成領域IIIのONO膜21を覆う形状を有している。

【0115】

その後に、周辺トランジスタ領域IのONO膜21の酸化膜20、シリコン窒化膜19を順にドライエッチングして除去する。酸化膜20、シリコン窒化膜19は、例えば、フッ素系ガスを使用するRIE法によりエッチングされる。その後にレジストパターン53を除去する。

【0116】

続いて、図11Bに示すように、ONO膜21、シリコン酸化膜18等の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン54を形成する。レジストパターン54は、メモリセルアレイ領域IIのONO膜21を覆い、コンデンサ形成領域IIIのONO膜21と周辺トランジスタ領域Iのシリコン酸化膜18を露出する形状を有している。

【0117】

続いて、レジストパターン54をマスクに使用して、コンデンサ形成領域IIIのONO膜21の酸化膜20と周辺トランジスタ領域Iのシリコン酸化膜18、7をフッ酸によりエッチングする。これにより、周辺トランジスタ領域Iでは第3〜第5のPウェル14、22、23が露出する。また、コンデンサ形成領域IIIのONO膜21は、シリコン酸化膜18とシリコン窒化膜19の二層構造を有するNO膜21aに変わる。その後に、レジストパターン54を除去する。

【0118】

次に、図11Cに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を熱酸化法により酸化し、第3〜第5のPウェル14、22、23の表面に第1のゲート絶縁膜25としてシリコン酸化膜を形成する。

【0119】

次に、図11Dに例示するように、シリコン基板1の全体にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン55を形成する。レジストパターン55は、第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を露出する開口部55aを有する。さらに、レジストパターン55は、少なくとも第1、第3のn型MOSトランジスタ形成領域IV、VIの第1のゲート絶縁膜25と、メモリセルアレイ領域IIのONO膜21とコンデンサ形成領域IIIのNO膜21aを覆う形状を有する。

【0120】

続いて、レジストパターン55をマスクに使用し、第2のn型MOSトランジスタ形成領域V内の第1のゲート絶縁膜25をフッ酸により除去し、第4のPウェル22の表面を露出させる。その後にレジストパターン55を除去する。

【0121】

次に、図11Eに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を

熱酸化法により酸化し、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27を形成するとともに、第1のゲート絶縁膜25の厚さを増加させる。

【0122】

続いて、図11Fに例示するように、第1、第2のゲート絶縁膜25、27、ONO膜21、NO膜21aの上にフォトレジストを塗布し、これを現像してレジストパターン56を形成する。レジストパターン56は、第5のPウェル23の上に開口部56aを有し、また、第3のPウェル14表面の第1のゲート絶縁膜25と第4のウェル22表面の第2のゲート絶縁膜27とONO膜21及びNO膜21aを覆う形状を有している。

【0123】

その後に、レジストパターン56の開口部56aを通して第1のゲート絶縁膜25をフッ酸により除去し、第5のPウェル23の表面を露出させる。その後に、レジストパターン56を除去する。

【0124】

次に、第1実施形態の図1Pに示すと同様に、第5のPウェル23の表面を熱酸化して第3のゲート電極29を形成するとともに、第1、第2のゲート絶縁膜25、27の厚さを増加させる。第2、第3のゲート絶縁膜25、27を形成する熱酸化の際には、NO膜21aのシリコン窒化膜19の表面も酸化されてその表面に1nmよりも薄いシリコン窒化酸化膜が形成される。その薄いシリコン窒化酸化膜は、NO膜21aの静電容量を実質的に変えないか、或いはその静電容量をONO膜21よりも大きくすることはない。

【0125】

さらに、第1実施形態と同様に、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、コントロールゲート電極CG,第1、第2の電極33a、33b等を形成する。さらに、第2〜第5のPウェル13,14、22、23内にソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bを形成し、第1のPウェル13内に高不純物濃度拡散領域42を形成する。

【0126】

これにより、第1〜第3のn型MOSトランジスタT1〜T3、フラッシュメモリセルMC、第1、第2のコンデンサQ1、Q2を形成する。その後の工程は、第1実施形態と同様である。フラッシュメモリセルMCにおいて、コントロールゲート電極CGとフローティングゲート電極FGの間にはONO膜21が形成されている。また、第1のコンデンサQ1は、第1実施形態と同様に、第1、第2の電極33a、33bの間に誘電体膜33cとしてNO膜21aが形成される。

【0127】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用するために、酸化膜20を選択的に除去してNO膜21aに変えている。また、ONO膜21のうち上側の酸化膜20は、図11Aに示したように、周辺トランジスタ領域Iに残されたシリコン酸化膜18、7と同時に除去される。

【0128】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を入れる必要はないので、スループットの低下を防止することができる。しかも、ONO膜21の上側の酸化膜20は、その下のシリコン窒化膜に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まるのでエッチングの制御性に優れる。

【0129】

また、第1実施形態と同様に、NO膜21aを誘電体膜33cとして使用する第1のコンデンサQ1は、ONO膜21を使用する場合よりも単位面積当たりのコンデンサ容量を約25%増加させることができる。

【0130】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概

念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈され、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができると理解される。

【0131】

次に、本発明の実施形態について特徴を付記する。

(付記1)半導体基板の上方に第1の半導体膜を形成する工程と、第1領域の前記第1の半導体膜をエッチングする工程と、前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(付記2)半導体基板の上方に第1の半導体膜を形成する工程と、第1領域内の前記第1の半導体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(付記3)前記第1領域はトランジスタ形成領域であり、前記第2領域はコンデンサ形成領域であり、前記第3領域はメモリセル形成領域であることを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4)前記第1絶縁膜、前記第1の誘電体膜及び前記第2の誘電体膜の上に第2の半導体膜を形成する工程と、前記メモリセル形成領域において、前記第2の半導体膜、前記第1の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第1の誘電体膜を挟むフローティングゲート電極とコントロールゲート電極を形成する工程と、前記コンデンサ形成領域において、前記第2の半導体膜、前記第2の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第2の誘電体膜を挟む第1、第2の電極を有するコンデンサを形成する工程と、前記第1トランジスタ形成領域において前記第2の半導体膜をパターニングすることによりMOSトランジスタのゲート電極を形成する工程と、有することを特徴とする付記3に記載の半導体装置の製造方法。

(付記5)前記第1の絶縁膜は、前記半導体基板の表面を熱酸化することにより形成されることを特徴とする付記1乃至付記4のいずれか1つに記載の半導体装置の製造方法。

(付記6)前記半導体基板の表面を熱酸化して前記第1の絶縁膜を形成すると同時に、前記第2の誘電体膜の前記窒化膜の表面を熱酸化し、前記第2の酸化膜よりも薄い窒化酸化膜を前記窒化膜の上に形成することを特徴とする付記1乃至付記5のいずれかに記載の半導体装置の製造方法。

(付記7)前記第1の絶縁膜は、前記第2領域内の前記第2酸化膜をエッチングする前に、前記半導体基板の表面を熱酸化することにより形成されることを特徴とする付記1又は付記3に記載の半導体装置の製造方法。

(付記8)前記第1の絶縁膜を前記半導体基板の第4領域にも形成する工程と、前記第4領域の前記第1の絶縁膜を除去した後に、前記半導体基板を熱酸化して前記第4領域に第2の絶縁膜を形成し、同時に前記第1領域の前記半導体基板の上の前記第1の絶縁膜の厚さを増やす工程と、を有することを特徴とする付記5に記載の半導体装置の製造方法。

(付記9)前記第1の誘電体膜を通して前記第1領域の前記半導体基板内に不純物をイオン注入し、第1の一導電型ウェルを形成する工程を有することを特徴とする付記1乃至付記8のいずれか1つに記載の半導体装置の製造方法。

(付記10)前記第1の半導体膜を形成する前に、前記半導体基板の上に第3の絶縁膜を形成する工程を有することを特徴とする付記1乃至付記9のいずれか1つに記載の半導体装置の製造方法。

(付記11)前記第2領域内の前記半導体基板の中に第2の一導電型ウェルを形成する工程と、前記一導電型ウェルと前記第1の半導体膜の間にコンデンサ用誘電体膜として第4の絶縁膜を形成する工程と、を有することを特徴とする付記1乃至付記10のいずれか1つに記載の半導体装置の製造方法。

【符号の説明】

【0132】

1 シリコン基板(半導体基板)

5 素子分離絶縁膜

7 シリコン酸化膜

9〜11、22、23 Pウェル

16 アモルファスシリコン膜

18 シリコン酸化膜

19 シリコン窒化膜

20 シリコン酸化膜

21 ONO膜

21a NO膜

25、26、27 ゲート絶縁膜

30 ポリシリコン膜

30a、30b、30c ゲート電極

33a 第1の電極

33b 第2の電極

33c 誘電体膜

33d コンタクトホール

FG フローティングゲート電極

CG コントロールゲート電極

Q1、Q2 コンデンサ

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

フローティングゲートとコントロールゲートを有するスタック型フラッシュメモリを混載した半導体装置では、電源安定化に使用されるバイパスコンデンサとして、フラッシュメモリセルの構造を利用した素子が知られている。具体的には、シリコン基板に形成される不純物拡散領域とその上のトンネル酸化膜とフローティングゲート電極を含む第1のコンデンサ、およびフローティングゲート電極とONO膜とコントロールゲート電極を含む第2のコンデンサを有している。そして、第1、第2のコンデンサは並列に接続される。ONO膜は、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜を順に形成した積層構造の膜である。

【0003】

半導体基板の上に形成される別のコンデンサ(キャパシタ)として、多結晶シリコン膜、キャパシタ絶縁膜、多結晶シリコン膜を順に素子分離絶縁膜上に形成する構造が知られている。そのキャパシタ絶縁膜として、ONO膜、NO膜又はON膜が使用される。

【0004】

半導体基板の上に形成されるさらに別のコンデンサとして、EPROMの下部電極として使用される多結晶シリコン膜と、その上に順に形成される酸化膜(O)、多結晶シリコン膜とを有する構造が知られている。その酸化膜は、EPROMの下部電極である多結晶シリコン膜の上に順に形成される酸化膜(O)、ナイトライド膜(N)を除去した後に新たに形成される膜である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−016230号公報

【特許文献2】特開2004−356580号公報

【特許文献3】特開平5−21808号公報

【非特許文献1】Y. Yamaguchi et al., “ONO interpoly dielectric scaling limit for non-volatile memory devices”

【非特許文献2】S. Mori et al., “Polyoxide thinning limitation and superior ONO interpoly dielectric for nonvolatile memory device,” IEEE Trans. Elect. Dev., vol.ED-38, p.270, 1991

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のバイパスコンデンサの面積あたりの容量を増やす1つの方法として、例えば、フラッシュメモリの一部となるONO膜をできるだけ薄く形成する方法がある。しかし、ONO膜の層構造は、フラッシュメモリの信頼性に影響する重要なパラメータなので、コンデンサ容量を増やす目的で変更されることはない。

【0007】

例えば、フラッシュメモリのコントロールゲートとフローティングの間に挟まれるONO膜のうち上側の酸化膜(0)を薄くすると、フラッシュメモリのチャージロス量が増加することが知られている。従って、コンデンサの容量を増やすためだけにフラッシュメモリのONO膜の構造を変更することはできない。

【0008】

さらに、燐がドープされた2層のポリシリコン膜の間に形成される誘電体膜として単一

の酸化膜を下側のポリシリコン膜の上に形成する方法では、下側のポリシリコン膜表面のラフネスや酸化膜の膜質等によってリーク電流が発生することが知られている。また、燐を含むポリシリコン膜の表面は増速酸化し易いので、その上に単一の酸化膜を形成する場合には、酸化膜の厚さの制御が難しい。

【0009】

本発明の目的は、スループットを低下させずにメモリセルの誘電体膜とキャパシタの誘電体膜の構造を異ならせて同時に形成することができる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0010】

実施形態の1つの観点によれば、半導体基板の上方に第1の半導体膜を形成する工程と、第1領域の前記第1の半導体膜をエッチングする工程と、前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

実施形態の別の観点によれば、半導体基板の上方に第1の半導体膜を形成する工程と、第1領域内の前記第1の半導体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0011】

本実施形態によれば、酸化膜/窒化膜/酸化膜の複数層構造誘電体膜をメモリセル領域とコンデンサ形成領域に形成している。さらに、トランジスタ形成領域の半導体基板表面の他の酸化膜をエッチングして除去する際に、これと同時にコンデンサ形成領域の複数層構造誘電体膜の上側の酸化膜をエッチングしている。

このため、複数層構造誘電体膜の上側の酸化膜の除去のための独立したエッチング処理は不要になるので、コンデンサの誘電体膜として使用される複数層構造誘電体膜の面積当たりのコンデンサ容量を高めることが容易になる。しかも、半導体基板表面の酸化膜をエッチングする際に使用されるマスクを使用してメモリセル領域の複数層構造誘電体膜も覆うようにしている。従って、フラッシュメモリセルの2つの電極の間に挟まれる酸化膜/窒化膜/酸化膜の電気的特性を劣化させることはない。

【図面の簡単な説明】

【0012】

【図1A】図1A〜図1Cは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1D】図1D〜図1Fは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1G】図1G〜図1Iは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1J】図1J〜図1Lは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1M】図1M〜図1Oは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1P】図1P、図1Qは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1R】図1R、図1Sは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1T】図1T、図1Uは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1V】図1V、図1Wは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図1X】図1X、図1Yは、第1実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図2】図2A、図2Bは、第1実施形態に係る半導体装置内のメモリセルの形成工程の一部を示す断面図である。

【図3】図3Aは、実施形態に係る半導体装置の製造工程で形成されるONO膜についての各種試験を行うために使用される試料の構造を示す断面図、図3Bは、実施形態に係る半導体装置の製造工程で形成されるNO膜についての各種試験を行うために使用される試料の構造を例示する断面図である。

【図4】図4は、実施形態に係る半導体装置の製造工程で形成されるONO膜、NO膜のそれぞれのコンデンサ容量の標準偏差の累積確率との関係を例示する図である。

【図5】図5は、図4の試験に使用されたONO膜、NO膜のそれぞれを酸化膜に換算した場合の厚さを例示する図である。

【図6】図6は、実施形態に係る半導体装置の製造工程で形成されるONO膜、NO膜のそれぞれの電圧と容量の関係を例示する図である。

【図7】図7は、図6の試験に使用されたONO膜、NO膜のそれぞれを酸化膜に換算した場合の厚さを例示する図である。

【図8】図8は、実施形態に係る半導体装置の製造工程で形成されるONO膜とNO膜のそれぞれについての絶縁破壊電圧の累積確率を例示する図である。

【図9】図9は、実施形態に係る半導体装置の製造工程で形成されるONO膜とNO膜のそれぞれについての印加電圧と電流の関係を例示する図である。

【図10】図10A〜図10Cは、第2実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図11A】図11A〜図11Cは、第3実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【図11D】図11D〜図11Fは、第3実施形態に係る半導体装置の製造方法の一部を例示する断面図である。

【発明を実施するための最良の形態】

【0013】

以下に、図面を参照して本発明の好ましい実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

【0014】

(第1の実施の形態)

【0015】

図1A〜図1Yは、本実施形態に係る半導体装置の製造工程の一例を示す断面図である。図1A〜図1Yでは、図1Aに示すように周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。

【0016】

周辺トランジスタ領域Iでは、閾値電圧の高い順に第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VIが示されている。第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VIのそれぞれは、例えば、順に5.0V、3.3V、1.2V、の閾値電圧のMOSトランジスタが形成される領域である。また、周辺トランジスタ領域Iでは、特に図示しないが、p型MOSトランジスタ形成領域、その他の領域も有している。さらに、メモリセルアレイ領域IIでは、フラッシュメモリセルが形成されるメモリセル形成領域VII を縦横に複数有している。

【0017】

次に、図1Aに示す構造を形成するまでの工程を説明する。

【0018】

まず、半導体基板としてシリコン基板1を使用し、その上にイニシャル酸化膜2、シリコン窒化膜3を順に形成する。イニシャル酸化膜2は、熱酸化法、CVD法等のいずれかにより形成される。また、シリコン窒化膜3は、例えばCVD法により形成される。シリコン窒化膜3の上には、素子分離領域に開口部を有するとともにその他の領域を覆うレジストパターン(不図示)が形成される。

【0019】

続いて、レジストパターン(不図示)をマスクに使用してシリコン窒化膜3及びイニシャル酸化膜2を例えばフッ素系ガスを使用するドライエッチング法、例えば反応性イオンエッチング(RIE)法によりエッチングしてハードマスク4を形成する。ハードマスク4は、素子分離領域のシリコン基板1を露出する開口部4aを有する。

【0020】

さらに、ハードマスク4の開口部4aから露出したシリコン基板1をエッチングすることにより素子分離領域に素子分離溝1aを形成する。シリコン基板1のエッチング法として、例えば、塩素系ガス又は臭素系ガスを使用するRIE法が使用される。

【0021】

素子分離溝1aは、シリコン基板1のうち、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域III、第1、第2及び第3のn型MOSトランジスタ形成領域IV、V、VI、メモリセル形成領域VII 等を囲む位置に形成される。

【0022】

次に、図1Bに示す構造を形成するまでの工程を説明する。

【0023】

まず、素子分離溝1aの内周面を熱酸化して酸化膜(不図示)を形成した後に、シリコン酸化膜を素子分離溝1a内とシリコン窒化膜3上にCVD法により形成する。シリコン酸化膜は、素子分離溝1a内を完全に埋め込む厚さに形成される。続いて、シリコン窒化膜3の上面を露出させるまで、ハードマスク4上のシリコン酸化膜を例えば化学機械研磨(CMP)法により研磨する。これにより、素子分離溝1a内に残されたシリコン酸化膜を素子分離絶縁膜5として使用する。

【0024】

次に、図1Cに示すように、シリコン基板1及び素子分離絶縁膜5の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン6を形成する。レジストパターン6は、メモリセルアレイ領域IIを露出する開口部6aを有するとともに、周辺トランジスタ領域I、コンデンサ形成領域IIIを覆う形状を有する。

【0025】

次に、レジストパターン6の開口部6aを通してチャネルインプラントとしてn型又はp型の不純物をメモリセル形成領域VII のシリコン基板1にイオン注入してチャネル不純物濃度調整領域13aを形成する。その後に、レジストパターン6を除去する。

【0026】

続いて、図1Dに示す構造を形成するまでの工程を説明する。

【0027】

まず、シリコン窒化膜3を熱リン酸により除去し、さらにイニシャル酸化膜2をフッ酸により除去する。その後に、シリコン基板1の表面を熱酸化し、これによりシリコン基板1の表面に絶縁膜としてシリコン酸化膜7を形成する。シリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。続いて、シリコン基板1の上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン8を形成する。

【0028】

レジストパターン8は、コンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVを露出する開口部8a〜8cを有し、さらに第2、第3のn型MOSトランジスタ形成領域V、VIを覆う形状を有する。

【0029】

その後に、レジストパターン8の開口部8a〜8cを通してn型不純物、例えば燐又はヒ素をシリコン基板1内にイオン注入する。これにより、コンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVのそれぞれに深い第1〜第3のNウェル9、10、11を形成する。その後に、レジストパターン8の開口部8a〜8cを通してp型不純物、例えばホウ素をシリコン基板1内にイオン注入する。これによりコンデンサ形成領域IIIとメモリセル形成領域VIIと第1のn型MOSトランジスタ形成領域IVにそれぞれ第1、第2及び第3のPウェル12、13、14を形成する。

【0030】

それらの不純物イオン注入の際には、第1、第2及び第3のPウェル12、13、14の下にそれぞれNウェル9、10、11が存在する不純物プロファイルを形成するように、n型及びp型の不純物のドーズ量、加速エネルギーが調整される。その後、レジストパターン8が除去される。

【0031】

次に、図1Eに示す構造を形成するまでの工程を説明する。

【0032】

まず、シリコン基板1の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン15を形成する。レジストパターン15は、第1のn型MOSトランジスタ形成領域IV、メモリセル形成領域VII及びコンデンサ形成領域IIIを囲んでいる素子分離絶縁膜5を露出する開口部15aを有し、さらに、第1、第2、第3のn型MOSトランジスタ形成領域IV、V、VI、メモリセル形成領域VII及びコンデンサ形成領域IIIを覆う形状を有する。

【0033】

その後に、レジストパターン15の開口部15aを通して、n型不純物をイオン注入することにより、第1、第2及び第3のPウェル12、13、14のそれぞれの周囲に高電圧用のNウェル9a、10a、11aを形成する。これにより、高電圧用のNウェル9a、10a、11aは、Pウェル12、13、14の下のNウェル9、10、11に接続される。その後、レジストパターン15は除去される。なお、イオン注入後に、シリコン基板1表面のシリコン酸化膜7を除去し、再び形成してもよい。

【0034】

次に、図1Fに示す構造を形成するまでの工程を説明する。

【0035】

まず、シリコン基板1上のシリコン酸化膜7と素子分離絶縁膜5の上に、半導体膜としてアモルファスシリコン膜16をCVD法により約50nm〜150nmの厚さに形成する。なお、その後、アモルファスシリコン膜16のうちコンデンサ形成領域IIIに例えば

n型不純物をイオン注入してもよい。

【0036】

続いて、アモルファスシリコン膜16上にフォトレジストを塗布した後に、フォトレジストを露光、現像することにより、レジストパターン17を形成する。レジストパターン17は、メモリセル形成領域VIIとコンデンサ形成領域IIIを覆うとともに、周辺トランジスタ領域Iを露出する形状を有する。また、レジストパターン17は、図2Aに示すように、メモリセル形成領域VIIのそれぞれの周囲に開口部17aを有している。図2A、図2Bは、それぞれ図1F、図1GのX−X線から見た断面図である。

【0037】

続いて、図1G、図2Bに示すように、レジストパターン17をマスクに使用し、露出しているアモルファスシリコン膜16をエッチングにより除去する。この場合のエッチング法として、例えば、塩素系ガス又は臭素系ガスを使用するRIE法を使用する。これにより、メモリセルアレイ領域II内でメモリセル形成領域VII毎に分割されたアモルファスシリコン膜16は、後の工程でさらにパターニングされてフラッシュメモリセルのフローティングゲート電極FGとして使用される。その後、レジストパターン17は除去される。

【0038】

次に、図1Hに示すように、シリコン基板1表面のシリコン酸化膜7、アモルファスシリコン膜16、素子分絶縁膜5等の上面に、シリコン酸化膜18をCVD法により例えば4nm〜6nmの厚さに形成する。さらに、シリコン酸化膜18上にシリコン窒化膜19をCVD法により例えば7nm〜9nmの厚さに形成する。続いて、シリコン窒化膜19表面を熱酸化法により酸化し、酸化膜20を形成する。この時の熱酸化量は、シリコンの酸化の厚さに換算すると厚さ200〜300nmで、シリコン窒化膜18上に形成される酸化膜20の膜厚は4〜6nmである。このようにして、シリコン酸化膜7の上とアモルファスシリコン膜16の上に、複数層構造誘電体膜であるONO膜21が形成される。

【0039】

次に、図1Iに示す構造を形成するまでの工程を説明する。

【0040】

まず、ONO膜21上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン(不図示)を形成する。このレジストパターンは、周辺トランジスタ領域Iの第2のn型MOSトランジスタ形成領域VのONO膜21を露出する開口部を有し、第1、第3のn型MOSトランジスタ形成領域IV、VI、メモリセルアレイ領域II、コンデンサ形成領域III等を覆う形状を有する。

【0041】

その後に、そのレジストパターンの開口部からONO膜21を通してシリコン基板1内にp型不純物をイオン注入することにより、第2のn型MOSトランジスタ形成領域Vのシリコン基板1内に第4のPウェル22を形成する。また、第4のPウェル22を形成する前か後に、そのレジストパターンの開口部を通してシリコン基板1内にチャネル不純物濃度調整用の不純物をイオン注入する。その後に、そのレジストパターンを除去する。

【0042】

この後に、ONO膜21上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン(不図示)を形成する。このレジストパターンは、周辺トランジスタ領域Iの第3のn型MOSトランジスタ形成領域VIのONO膜21を露出する開口部を有し、第1、第2のn型MOSトランジスタ形成領域IV、V、メモリセルアレイ領域II、コンデンサ形成領域III等を覆う形状を有する。その後に、そのレジストパターンの開口部を通してシリコン基板1内にp型不純物をイオン注入することにより、第3のn型MOSトランジスタ形成領域VIのシリコン基板1内に第5のPウェル23を形成する。また、第5のPウェル23を形成する前か後に、そのレジストパターンの開口部を通してシリコン基板1内にチャネル濃度調整用の不純物をイオン注入する。その後に、そのレジストパターンを除去する。

【0043】

次に、図1Jに示すように、ONO膜21の上にフォトレジストを塗布し、これを露光、現像することにより、周辺トランジスタ領域Iを露出するとともに、メモリセルアレイ領域II、コンデンサ形成領域IIIを覆うレジストパターン24を形成する。

【0044】

続いて、図1Kに示すように、レジストパターン24から露出した領域のONO膜21の酸化膜20、シリコン窒化膜19を例えばRIE法により除去する。その後に、周辺トランジスタ領域Iにおけるシリコン基板1表面上のシリコン酸化膜7、18をフッ酸によりウェットエッチングして除去する。

【0045】

レジストパターン24を除去した後に、図1Lに示すように、周辺トランジスタ領域Iにおけるシリコン基板1の露出面に熱酸化法又はCVD法により第1ゲート絶縁膜25としてシリコン酸化膜を約5nm〜15nmの厚さに形成する。この場合、メモリセルアレイ領域II、コンデンサ形成領域IIIに存在するONO膜21の酸化膜20表面は殆ど酸化されない。

【0046】

次に、図1Mに示す構造を形成するまでの工程を説明する。

まず、第1ゲート絶縁膜25及びONO膜21の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン26を形成する。レジストパターン26は、シリコン基板1において、第2のn型MOSトランジスタ形成領域Vの上に開口部26aを有する一方、第1、第3のn型MOSトランジスタ形成領域IV、VI、メモリセルアレイ領域II、コンデンサ形成領域IIIを覆う形状を有する。

【0047】

続いて、レジストパターン26をマスクに使用し、フッ酸を用いるウェットエッチングによって第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を除去し、そこからシリコン基板1を露出させる。その後にレジストパターン26を除去する。

【0048】

次に、図1Nに示すように、シリコン基板1の表面を熱酸化することにより、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27としてシリコン酸化膜を形成する。その熱酸化によれば、第1、第3のn型MOSトランジスタ形成領域IV、VIのシリコン基板1表面も酸化されるので、シリコン酸化膜である第1のゲート絶縁膜25の厚さが約10nm〜20nmまで増える。この場合、ONO膜21は殆ど酸化されない。その後に、レジストパターン26を除去する。

【0049】

次に、図1Oに示す構造を形成するまでの工程を説明する。

【0050】

まず、第1、第2ゲート絶縁膜25、27及びONO膜21の上にフォトレジストを塗布した後に、これを露光、現像することによりレジストパターン28を形成する。レジストパターン28は、シリコン基板1において、第3のn型MOSトランジスタ形成領域VI、コンデンサ形成領域IIIの上に開口部28a、28bを有する一方、第1、第2のn型MOSトランジスタ形成領域IV、V、メモリセル領域IIを覆う形状を有する。

【0051】

続いて、レジストパターン28をマスクに使用し、フッ酸を用いるウェットエッチングによって第3のn型MOSトランジスタ形成領域VIの第1のゲート絶縁膜25を除去し、そこからシリコン基板1を露出させる。同時に、コンデンサ形成領域IIIのONO膜21の酸化膜20を除去し、その下のシリコン窒化膜18を露出させてONO膜20を二層構造誘電体膜であるNO膜21aに変える。その後にレジストパターン28を除去する。

【0052】

次に、図1Pに例示するように、シリコン基板1の表面を熱酸化することにより、第3のn型MOSトランジスタ形成領域VI内に第3のゲート絶縁膜29としてシリコン酸化膜

を約1nm〜3nmの厚さに形成する。その熱酸化によれば、第1、第2のn型MOSトランジスタ形成領域IV、V内のシリコン基板1表面も酸化されるので、シリコン酸化膜である第1、第2のゲート絶縁膜25、27の厚さが増加する。その増加量は、例えば約1nm〜3nmである。この場合、ONO膜21は殆ど酸化されない。

【0053】

次に、図1Qに示すように、第1〜第3のゲート絶縁膜25、27、29、ONO膜21及びNO膜21aの上に、半導体膜としてポリシリコン膜30をCVD法により形成する。続いて、ポリシリコン膜30上に、シリコンリッチなシリコン窒化膜を反射防止(ARC)膜31としてCVD法により形成する。

【0054】

次に、図1Rに示す構造を形成するまでの工程を説明する。

【0055】

まず、ARC膜31上にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン32を形成する。レジストパターン32は、周辺トランジスタ領域IではARC膜31を覆い、メモリセルアレイ領域IIではゲート電極及び配線の平面形状を有し、コンデンサ形成領域IIIではコンデンサの上部及び下部電極の平面形状を有している。

【0056】

続いて、レジストパターン32をマスクに使用して、ARC膜31からアモルファスシリコン16までの層をエッチングする。エッチング方法として、例えばRIE法を使用し、ARC膜31、NO膜21aのエッチングガスとしてフッ素系ガスを使用し、ポリシリコン膜30、アモルファスシリコン膜16のエッチングガスとして例えば塩素含有ガスを使用する。

【0057】

これにより、メモリセルアレイ領域IIにおいてパターニングされたポリシリコン膜30はワード線を兼ねたコントロールゲート電極CGとして使用され、その下のアモルファスシリコン膜16は、フローティングゲート電極FGとして使用される。

【0058】

また、コンデンサ形成領域IIIでは、パターニングされたポリシリコン膜30、アモルファスシリコン膜16はそれぞれ第1の電極33a、第2の電極33bとなり、それらの間のNO膜21aは誘電体膜33cとなる。これにより、第1の電極33a、第2の電極33b及びそれらの間のNO膜21aにより第1のコンデンサQ1が形成される。また、第2の電極33bとシリコン酸化膜7と第1のPウェル12により第2のコンデンサQ2が形成される。この場合、シリコン酸化膜7は誘電体膜である。第1のコンデンサQ1と第2のコンデンサQ2は、第2の電極33bを共通電極として接続されている。その後に、レジストパターン32を除去する。

【0059】

次に、図1Sに示すように、ARC膜31をマスクに使用して、コントロールゲート電極CG、フローティングゲート電極FGの側壁を熱酸化することにより、側壁酸化膜34aが形成される。これと同時に、コンデンサ形成領域IIIにおいて、第1の電極33a、第2の電極33bの側壁も酸化されて側壁酸化膜34bが形成される。

【0060】

その後に、パターニングされたARC膜31及びポリシリコン膜30をマスクに使用してメモリセル形成領域VII、コンデンサ形成領域IIIの第1、第2のPウェル12、13にn型不純物、例えばヒ素又は燐をイオン注入する。これにより、第2のPウェル13内において、フローティングゲート電極FGの両側にn型エクステンション領域35a、35bが形成される。これと同時に、第1のPウェル12内において、第2の電極33bの側方にもn型エクステンション領域35cが形成される。その後に、コントロールゲート電極CG、フローティングゲート電極FG、第1の電極33a、第2の電極33bの側壁を再び熱酸化することにより、側壁酸化膜34a、34bの膜厚を増加させる。

【0061】

続いて、図1Tに示す構造を形成するまでの工程について説明する。

【0062】

まず、コントロールゲート電極CG、ARC膜31、シリコン酸化膜7等の上に、シリコン窒化膜をCVD法により形成する。その後に、シリコン酸化膜7が露出するまでシリコン窒化膜及びARC膜31をエッチバックする。これにより、コントロールゲート電極CG、フローティングゲート電極FGと第1、第2の電極33a、33bのそれぞれの側方に残されたシリコン窒化膜をサイドウォール36a、36bとして使用する。

【0063】

次に、図1Uに示す構造を形成するまでの工程を説明する。

【0064】

まず、ポリシリコン膜30、コントロールゲート電極CG、フローティングゲート電極FG等の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン37を形成する。レジストパターン37は、周辺トランジスタ領域Iで複数のゲート電極の平面形状を有し、メモリセルアレイ領域IIでフローティングゲート電極FG、第2のウェル13を覆い、コンデンサ形成領域IIIで第1の電極33aの一部に重なる開口部37aを有する。

【0065】

続いて、レジストパターン37をマスクに使用し、ポリシリコン膜30をエッチングすることにより第1〜第3のn型MOSトランジスタ形成領域IV〜VIのそれぞれにゲート電極30a〜30cを形成する。これと同時に、第1の電極33aの一部にコンタクトホール33dを形成する。その後にレジストパターン37を除去する。

【0066】

次に、図1Vに示す構造を形成するまでの工程を説明する。

【0067】

まず、第3、第4、第5のPウェル14、22、23のいずれか1つの上に開口部を有し、さらに第1、第2のPウェル12、13を覆う3つのレジストパターン(不図示)をシリコン基板1の上方に順に交換して形成する。そして、それらのレジストパターンの開口部を通して第3、第4、第5のPウェル14、22、23のそれぞれに順にn型不純物をイオン注入する。この場合、第1、第2、第3のゲート電極30a、30b、30cはマスクとして機能する。これにより、第3、第4、第5のPウェル14、22、23ではそれぞれ第1、第2、第3のゲート電極30a、30b、30cの両側にn型エクステンション領域38a、38b、39a、39b、40a、40bが形成される。

【0068】

第5のPウェル23では、n型エクステンション領域40a、40bを形成する前にp型不純物をイオン注入することによりn型エクステンション領域40a、40bの下にポケット領域(不図示)を形成する。

【0069】

次に、図1Wに示す構造を形成するまでの工程を説明する。

【0070】

まず、シリコン基板1の上方の全体に絶縁膜としてシリコン酸化膜をCVD法により形成し、これにより第1〜第3のゲート電極30a〜30c等を覆う。その後、その絶縁膜をエッチバックする。そのエッチバックは、第1〜第3のゲート電極30a〜30cの両側において、第1〜第3のゲート絶縁膜30a〜30c又はシリコン基板1表面が露出するまで行う。

【0071】

これにより、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、第2の電極33bの側方にその絶縁膜をサイドウォール41a〜41eとして残す。この場合、第1のコンデンサQ1の第1の電極33aのコンタクトホール33d内にもサイドウォール41fが形成されるので、コンタクトホール33d内周面において第1の電極

33aがサイドウォール41fにより覆われる。このオーバーエッチングにより、コンタクトホール33dの底の誘電体膜33c、即ちNO膜21aは除去される。

【0072】

続いて、第1〜第5のPウェル12〜14、22、23のいずれか1つの上に開口部を有し、さらに他のPウェル12〜14、22、23を覆うレジストパターン(不図示)をシリコン基板1の上方に順に交換して形成する。さらに、それらの開口部を通して第1〜第5のPウェル12〜14、22、23のそれぞれにn型不純物をイオン注入する。不純物のイオン注入条件は、注入毎に調整される。

【0073】

n型不純物のイオン注入時には、第1の電極33a、コントロールゲート電極CG、第1〜第3のゲート電極30a〜30c及びサイドウォール36ab、36b、41a〜41fはそれぞれマスクとして機能する。

【0074】

これにより、第1の電極33aの側方の第1のPウェル12内に高不純物濃度拡散領域42が形成される。また、その他の電極30a〜30c、FGの両側方の第2〜第5のPウェル13、14、22、23内に高不純物濃度のn型ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bが形成される。n型ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bは、n型エクステンション領域35a〜35c、38a、38b、39a、39b、40a、40bに接続される。

【0075】

次に、図1Xに示す構造を形成するまでの工程を説明する。

【0076】

まず、シリコン基板1の表面に形成されたゲート絶縁膜25、27、29及びシリコン酸化膜7のうちゲート電極30a〜30c、フローティングゲート電極FG等に覆われずに露出した部分を例えばフッ酸により除去する。その後に、シリコン基板1の上方にコバルト膜(不図示)を例えばスパッタ法により形成する。さらに、加熱処理によって、シリコンとコバルトを合金化してコバルトシリサイド層47a〜47oを形成する。コバルトシリサイド層47a〜47oは、ソース/ドレイン領域42、43a、43b、44a、44b、45a、45b、46a、46bの上層と、ゲート電極30a〜30c、コントロールゲート電極CG、第1の電極33aの上層に形成される。さらに、第1の電極33aのコンタクトホール33dの底に露出している第2の電極33bの上層にも形成される。続いて、シリコン基板1の上方のコバルト膜を除去する。

【0077】

以上により、第1のn型MOSトランジスタ形成領域IVには、第3のPウェル14、ソース/ドレイン領域44a、44b、第1のゲート電極30a等を有する第1のn型MOSトランジスタT1が形成される。また、第2のn型MOSトランジスタ形成領域Vには、第4のPウェル22、ソース/ドレイン領域45a、45b、第2のゲート電極30b等を有する第2のn型MOSトランジスタT2が形成される。さらに、第3のn型MOSトランジスタ形成領域VIには、第5のPウェル23、ソース/ドレイン領域46a、46b、第3のゲート電極30c等を有する第3のn型MOSトランジスタT3が形成される。

【0078】

また、メモリセル形成領域VIIには、第2のPウェル13、ソース/ドレイン領域43a、43b、ゲート絶縁膜7、フローティングゲート電極FG、ONO膜21、コントロールゲート電極CG等を有するフラッシュメモリセルMCが形成される。

【0079】

次に、図1Yに示す構造を形成するまでの工程を説明する。

【0080】

まず、シリコン基板1の上方にカバー絶縁膜48としてシリコン窒化膜をCVD法によ

り形成し、そのカバー絶縁膜47により第1〜第3のゲート電極30a〜30c、コバルトシリサイド層47a〜47o、サイドウォール41a〜41f等を覆う。

【0081】

次に、カバー絶縁膜48の上に層間絶縁膜49としてシリコン酸化膜をCVD法により形成する。続いて、層間絶縁膜49の表面を化学機械研磨(CMP)法により研磨して平坦にする。

【0082】

続いて、層間絶縁膜49上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン(不図示)を形成する。このレジストパターンは、ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bの上方と、第1のPウェル12内の高不純物濃度拡散領域42、第1の電極33aのコンタクトホール33dとその側方の一部などの上方に開口部を有する。その後に、レジストパターンをマスクにして、層間絶縁膜49、カバー絶縁膜48をエッチングする。これにより、ソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bと高不純物濃度拡散領域42表面のシリサイド層47c、47e、47f、47h、47i、47k、47l、47n、47oに達する深さのコンタクトホール49c〜49kを形成する。同時に、第1の電極33aの上にビアホール49bを形成し、さらに、第1の電極33aのコンタクトホール33dを通して第2の電極33bの表面のシリサイド層47bに達するビアホール49aを形成する。その後に、レジストパターンを除去する。

【0083】

続いて、ビアホール49a、49b、コンタクトホール49c〜49kの内面と層間絶縁膜49の上面にチタン膜、窒化チタン膜を順に形成する。続いて、ビアホール49a、49b、コンタクトホール49c〜49k内を完全に充填する厚さのタングステン膜を窒化チタン膜の上に形成する。さらに、層間絶縁膜49上のそれらの金属膜をCMPにより除去する。これにより、ビアホール49a、49b、コンタクトホール49c〜49k内に残された窒化チタン膜、チタン膜、タングステン膜を同遠征プラグ50a〜50kとして使用する。

【0084】

さらに、特に図示しないが、層間絶縁膜49の上に金属膜、例えばアルミニウム膜を形成した後に、アルミニウム膜をパターニングすることにより、コンタクトプラグの上に接続される配線、導電性パッド等などの金属パターンを形成する。その後に、特に図示しないが、層間絶縁膜49及び金属パターンの上に上側の層間絶縁膜を形成し、さらに上側の層間絶縁膜内にビアを形成し、その後に上側の層間絶縁膜の上に配線を形成する、といった工程を繰り返すことにより、半導体装置の基本構造を完成させる。

【0085】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用する際に、酸化膜20を選択的に除去してNO膜21aに変えている。また、NO膜21aの上に存在した酸化膜20は、図1Oに示したように、周辺トランジスタ領域Iの第5のPウェル23の上に形成された第1のゲート絶縁膜25であるシリコン酸化膜と同時に除去される。

【0086】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を入れる必要はなく、レジストパターン28の形状を調整するに留まるので、スループットの低下を防止することができる。しかも、NO膜21aの上に形成された酸化膜20は、その下のシリコン窒化膜19に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まり、エッチングの制御性に優れる。

【0087】

ところで、周辺トランジスタ領域の第3〜第5のPウェル14、22、23の表面を熱酸化する際に、NO膜21aの表面も酸化される。この場合、図1Pに示すように、NO

膜21aのシリコン窒化膜19の表面も酸化されてシリコン窒化酸化膜19aが形成される。しかし、その厚さは、ONO膜21の上側のシリコン酸化膜20よりも薄く、例えば1nmより小さい値、即ち数Åと極めて薄く、酸化前後のNO膜21aの静電容量は、実質的に同じ、又はONO膜21よりも大きい。

【0088】

次に、ONO膜21の上側の酸化膜20を除去せずにコンデンサの誘電体膜として使用する場合と、ONO膜21の上側の酸化膜20を除去して形成されたNO膜21aをコンデンサの誘電体膜として使用する場合の特性を比較する。ここで、図3Aに示すように、フローティングゲート電極FGとコントロールゲート電極CGによりONO膜21を挟んだ構造を有するコンデンサを第1の試料となし、シリコン基板1上に複数形成する。さらに、図3Bに示すように、フローティングゲート電極FGとコントロールゲート電極CGによりNO膜21aを挟んだ構造を有するコンデンサを第2の試料となし、シリコン基板1上に複数形成する。

【0089】

この場合のONO膜21aにおいて、下側のシリコン酸化膜18と上側の酸化膜20とそれらの間のシリコン窒化膜19のそれぞれの厚さを約5nm、約5nm、約5nmとする。また、NO膜21aにおいて、シリコン酸化膜18、シリコン窒化膜19のそれぞれの厚さを約5nm、約5nmとする。

【0090】

第1、第2の試料について、図3A、図3Bのそれぞれに示すコントロールゲート電極CGとフローティングゲート電極FGに電圧VCGを印可して種々の試験を行った。その試験結果を以下に説明する。

【0091】

まず、第1、第2の試料のコンデンサの容量値を調べたところ、図4に示す結果が得られた。また、図4に示す結果に基づいて第1、第2の試料のコンデンサの容量をシリコン酸化膜に換算した場合の膜厚を調べたところ、図5に示す結果が得られた。

【0092】

図4において、横軸はコンデンサ容量の値を示し、縦軸は標準偏差の累積確率の値を示している。これにより、NO膜21aを有する第2の試料は、ONO膜20を有する第1の試料よりも面積当たりの容量が約25%大きくなっている。また、図5において、第2の試料のNO膜は、第1の試料のONO膜に比べて酸化物換算膜厚が2.5nmほど薄くなっている。

【0093】

次に、第1の試料と第2の試料のそれぞれのコンデンサについて電圧の変化に対する容量の変化を調べたところ、図6に示す結果が得られた。図6によれば、第1、第2の試料のそれぞれのコンデンサのONO膜、NO膜について、電圧が変化してもそれらの容量は顕著に変化していない。図6の測定データに基づいて、容量をシリコン酸化膜に換算した場合の膜厚を図7に示す。

【0094】

ONO膜21を有する第1の試料とNO膜21aを有する第2の試料の絶縁耐圧を調べたところ、図8に示す結果が得られた。図8によれば、NO膜は、ONO膜に比べて、絶縁耐圧は低下するが、その耐圧は10V以上になっているので、コンデンサの誘電体膜として使用する場合に問題は生じない。

【0095】

また、NO膜とONO膜のそれぞれについてリーク電流を調べたところ、図9に示す結果が得られた。コンデンサに印加される電圧は−5V〜5Vの範囲が一般的であり、図9におけるその電圧範囲内ではONO膜、NO膜の双方のリーク電流は実質的に流れていない。従って、NO膜はコンデンサの誘電体膜として十分な能力を備えている。

【0096】

(第2の実施の形態)

図10A〜図10Cは、第2実施形態に係る半導体装置の製造工程の一例を示す断面図であり、図1A〜図1Yと同じ符号は同じ要素を示している。また、図10A〜図10Cでは、第1実施形態と同様に、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。特に図示しないが、周辺トランジスタ領域Iは、p型MOSトランジスタ形成領域、その他の領域もさらに有している。

【0097】

第2実施形態に係る半導体装置の製造工程では、まず、第1実施形態に係る図1A〜図1Eに示すと同様に、シリコン基板1に第1〜第3のPウェル12,13、14を形成し、第1〜第3のPウェル12〜13の下と横にねNウェル9,9a、10、10a、11、11aを形成する。さらに、第1実施形態に係る図1Fに示すと同様に、シリコン基板1の上にシリコン酸化膜7、アモルファスシリコン膜16を順に形成する。この場合のシリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。

【0098】

その後に、図1Gに示すと同様に、アモルファスシリコン膜16をパターニングすることにより、周辺トランジスタ領域Iからアモルファスシリコン膜16を除去し、メモリセル形成領域VIIではフローティングゲート電極FGを形成する。この場合、アモルファスシリコン膜16は、コンデンサ形成領域IIIの全体に残される。さらに、図1Hに示すように、アモルファスシリコン膜16の上とシリコン基板1の上方にONO膜21を形成する。続いて、図1Iに示すように、第2、第3のn型MOSトランジスタ形成領域V、VIのシリコン基板1内に第4、第5のPウェル22,23を形成する。その後に、図1J、図1Kに示すと同様に、周辺トランジスタ領域Iのシリコン酸化膜7及びONO膜21を除去する。

【0099】

続いて、図1Lに示すと同様に、周辺トランジスタ領域Iの第3〜第5のPウェル14、22、23の表面を熱酸化して、第1のゲート絶縁膜25を形成する。この場合、ONO膜21の表面は殆ど酸化されない。以上の工程は、第1実施形態と同様である。

【0100】

次に、図10Aに例示する構造を形成するまでの工程を説明する。

【0101】

まず、シリコン基板1の全体にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン51を形成する。レジストパターン51は、コンデンサ形成領域IIIのONO膜21と第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を露出するとともに、第1、第3のn型MOSトランジスタ形成領域IV、VIとメモリセルアレイ領域IIを覆う形状を有する。

【0102】

続いて、レジストパターン51をマスクに使用し、コンデンサ形成領域III内のONO膜21の酸化膜20、および第2のn型MOSトランジスタ形成領域V内の第1のゲート絶縁膜25を同時にフッ酸により除去する。これにより、コンデンサ形成領域III内におけるONO膜21は、シリコン酸化膜18とシリコン窒化膜19の二層構造を有するNO膜21aに変わる。その後に、レジストパターン51を除去する。

【0103】

次に、図10Bに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を熱酸化法により酸化し、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27を形成するとともに、第1のゲート絶縁膜25の厚さを増加させる。

【0104】

続いて、図10Cに例示するように、第1、第2のゲート絶縁膜25、27、ONO膜21、NO膜21aの上にフォトレジストを塗布し、これを現像してレジストパターン52を形成する。レジストパターン52は、第5のPウェル23の上に開口部52aを有し、また第3、第4のウェル14、22及びポリシリコン膜16を覆う形状を有している。その後に、レジストパターン52の開口部52aを通して第1のゲート絶縁膜25をフッ

酸により除去する。その後に、レジストパターン52を除去する。

【0105】

次に、第1実施形態の図1Pに示すと同様に、第5のPウェル23の表面を熱酸化して第3のゲート絶縁膜29を形成するとともに、第1、第2のゲート絶縁膜25、27の厚さを増加させる。第2、第3のゲート絶縁膜25、27を形成する熱酸化の際には、NO膜21aのシリコン窒化膜19の表面も酸化され、その表面には除去された第2のシリコン酸化膜20より薄い、例えば1nm以下の厚さのシリコン窒化酸化膜19aが形成される。その薄いシリコン窒化酸化膜19aはNO膜21aの誘電容量を実質的に変えない。

【0106】

さらに、第1実施形態と同様に、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、コントロールゲート電極CG,第1、第2の電極33a、33b等を形成する。さらに、第2〜第5のPウェル13,14、22、23内にソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bを形成し、併せて第1のPウェル13内に高不純物濃度拡散領域42を形成する。

【0107】

これにより、第1実施形態と同様に、第1〜第3のn型MOSトランジスタT1〜T3、フラッシュメモリセルMC、第1、第2のコンデンサQ1、Q2を形成する。フラッシュメモリセルMCにおいて、コントロールゲート電極CGとフローティングゲート電極FGの間にはONO膜21が形成されている。また、第1のコンデンサQ1は、第1実施形態と同様に、第1、第2の電極33a、33bの間に誘電体膜33cとしてNO膜21aが形成される。その後の工程は、第1実施形態と同様である。

【0108】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用する際に、酸化膜20を選択的に除去してNO膜21aに変えている。また、ONO膜21のうち上側の酸化膜20は、図10Aに示したように、周辺トランジスタ領域Iの第4のPウェル22の上に形成された第1のゲート絶縁膜25であるシリコン酸化膜と同時に除去される。

【0109】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を新たに入れる必要はなく、レジストパターン51の形状を変更するに留まるので、スループットの低下を防止することができる。しかも、ONO膜21の上側の酸化膜20は、その下のシリコン窒化膜に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まるのでエッチングの制御性に優れる。

【0110】

また、第1実施形態と同様に、NO膜21aを誘電体膜33cとして使用する第1のコンデンサQ1は、ONO膜21を使用する場合よりも単位面積当たりのコンデンサ容量を約25%増加させることができる。

【0111】

(第3の実施の形態)

図11A〜図11Fは、第3実施形態に係る半導体装置の製造工程の一例を示す断面図であり、図1A〜図1Yと同じ符号は同じ要素を示している。また、図11A〜図11Fでは、第1実施形態と同様に、周辺トランジスタ領域I、メモリセルアレイ領域II、コンデンサ形成領域IIIの一部が示されている。特に図示しないが、周辺トランジスタ領域Iは、p型MOSトランジスタ形成領域、その他の領域もさらに有している。

【0112】

第3実施形態に係る半導体装置の製造工程は、まず、第1実施形態に係る図1A〜図1Eに示すと同様に、シリコン基板1に第1〜第3のPウェル12,13、14を形成し、第1〜第3のPウェル12〜13の下と横に深いNウェル9,9a、10、10a、11、11aを形成する。さらに、第1実施形態に係る図1Fに示すと同様に、シリコン基板

1の上にシリコン酸化膜7、アモルファスシリコン膜16を順に形成する。この場合のシリコン酸化膜7はトンネル絶縁膜として機能する条件で形成される。

【0113】

その後に、図1Gに示すと同様に、アモルファスシリコン膜16をパターニングすることにより、周辺トランジスタ領域Iからアモルファスシリコン膜16を除去し、メモリセル形成領域VIIではフローティングゲート電極FGを形成する。この場合、アモルファスシリコン膜16は、コンデンサ形成領域IIIの全体に残される。さらに、図1Hに示すように、アモルファスシリコン膜16の上とシリコン基板1の上方にONO膜21を形成する。続いて、図1Iに示すように、第2、第3のn型MOSトランジスタ形成領域V、VIのシリコン基板1内に第4、第5のPウェル22,23を形成する。

【0114】

次に、図11A示すように、ONO膜21の上にフォトレジストを塗布し、これを露光現像することによりレジストパターン53を形成する。レジストパターン53は、周辺トランジスタ領域IのONO膜21を露出させるとともに、メモリセルアレイ領域II、コンデンサ形成領域IIIのONO膜21を覆う形状を有している。

【0115】

その後に、周辺トランジスタ領域IのONO膜21の酸化膜20、シリコン窒化膜19を順にドライエッチングして除去する。酸化膜20、シリコン窒化膜19は、例えば、フッ素系ガスを使用するRIE法によりエッチングされる。その後にレジストパターン53を除去する。

【0116】

続いて、図11Bに示すように、ONO膜21、シリコン酸化膜18等の上にフォトレジストを塗布し、これを露光、現像することによりレジストパターン54を形成する。レジストパターン54は、メモリセルアレイ領域IIのONO膜21を覆い、コンデンサ形成領域IIIのONO膜21と周辺トランジスタ領域Iのシリコン酸化膜18を露出する形状を有している。

【0117】

続いて、レジストパターン54をマスクに使用して、コンデンサ形成領域IIIのONO膜21の酸化膜20と周辺トランジスタ領域Iのシリコン酸化膜18、7をフッ酸によりエッチングする。これにより、周辺トランジスタ領域Iでは第3〜第5のPウェル14、22、23が露出する。また、コンデンサ形成領域IIIのONO膜21は、シリコン酸化膜18とシリコン窒化膜19の二層構造を有するNO膜21aに変わる。その後に、レジストパターン54を除去する。

【0118】

次に、図11Cに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を熱酸化法により酸化し、第3〜第5のPウェル14、22、23の表面に第1のゲート絶縁膜25としてシリコン酸化膜を形成する。

【0119】

次に、図11Dに例示するように、シリコン基板1の全体にフォトレジストを塗布し、これを露光、現像することにより、レジストパターン55を形成する。レジストパターン55は、第2のn型MOSトランジスタ形成領域Vの第1のゲート絶縁膜25を露出する開口部55aを有する。さらに、レジストパターン55は、少なくとも第1、第3のn型MOSトランジスタ形成領域IV、VIの第1のゲート絶縁膜25と、メモリセルアレイ領域IIのONO膜21とコンデンサ形成領域IIIのNO膜21aを覆う形状を有する。

【0120】

続いて、レジストパターン55をマスクに使用し、第2のn型MOSトランジスタ形成領域V内の第1のゲート絶縁膜25をフッ酸により除去し、第4のPウェル22の表面を露出させる。その後にレジストパターン55を除去する。

【0121】

次に、図11Eに例示するように、周辺トランジスタ領域Iのシリコン基板1の表面を

熱酸化法により酸化し、第2のn型MOSトランジスタ形成領域Vに第2のゲート絶縁膜27を形成するとともに、第1のゲート絶縁膜25の厚さを増加させる。

【0122】

続いて、図11Fに例示するように、第1、第2のゲート絶縁膜25、27、ONO膜21、NO膜21aの上にフォトレジストを塗布し、これを現像してレジストパターン56を形成する。レジストパターン56は、第5のPウェル23の上に開口部56aを有し、また、第3のPウェル14表面の第1のゲート絶縁膜25と第4のウェル22表面の第2のゲート絶縁膜27とONO膜21及びNO膜21aを覆う形状を有している。

【0123】

その後に、レジストパターン56の開口部56aを通して第1のゲート絶縁膜25をフッ酸により除去し、第5のPウェル23の表面を露出させる。その後に、レジストパターン56を除去する。

【0124】

次に、第1実施形態の図1Pに示すと同様に、第5のPウェル23の表面を熱酸化して第3のゲート電極29を形成するとともに、第1、第2のゲート絶縁膜25、27の厚さを増加させる。第2、第3のゲート絶縁膜25、27を形成する熱酸化の際には、NO膜21aのシリコン窒化膜19の表面も酸化されてその表面に1nmよりも薄いシリコン窒化酸化膜が形成される。その薄いシリコン窒化酸化膜は、NO膜21aの静電容量を実質的に変えないか、或いはその静電容量をONO膜21よりも大きくすることはない。

【0125】

さらに、第1実施形態と同様に、第1〜第3のゲート電極30a〜30c、フローティングゲート電極FG、コントロールゲート電極CG,第1、第2の電極33a、33b等を形成する。さらに、第2〜第5のPウェル13,14、22、23内にソース/ドレイン領域43a、43b、44a、44b、45a、45b、46a、46bを形成し、第1のPウェル13内に高不純物濃度拡散領域42を形成する。

【0126】

これにより、第1〜第3のn型MOSトランジスタT1〜T3、フラッシュメモリセルMC、第1、第2のコンデンサQ1、Q2を形成する。その後の工程は、第1実施形態と同様である。フラッシュメモリセルMCにおいて、コントロールゲート電極CGとフローティングゲート電極FGの間にはONO膜21が形成されている。また、第1のコンデンサQ1は、第1実施形態と同様に、第1、第2の電極33a、33bの間に誘電体膜33cとしてNO膜21aが形成される。

【0127】

以上の実施形態によれば、コントロールゲート電極CGとフローティングゲート電極FGの間に形成されるONO膜21を第1のコンデンサQ1の誘電体膜として適用するために、酸化膜20を選択的に除去してNO膜21aに変えている。また、ONO膜21のうち上側の酸化膜20は、図11Aに示したように、周辺トランジスタ領域Iに残されたシリコン酸化膜18、7と同時に除去される。

【0128】

このため、ONO膜21をNO膜21aに変更するための個別のエッチング工程を入れる必要はないので、スループットの低下を防止することができる。しかも、ONO膜21の上側の酸化膜20は、その下のシリコン窒化膜に対して選択的にエッチングされるので、自己整合的に上側の酸化膜20のエッチングが止まるのでエッチングの制御性に優れる。

【0129】

また、第1実施形態と同様に、NO膜21aを誘電体膜33cとして使用する第1のコンデンサQ1は、ONO膜21を使用する場合よりも単位面積当たりのコンデンサ容量を約25%増加させることができる。

【0130】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概

念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈され、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができると理解される。

【0131】

次に、本発明の実施形態について特徴を付記する。

(付記1)半導体基板の上方に第1の半導体膜を形成する工程と、第1領域の前記第1の半導体膜をエッチングする工程と、前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(付記2)半導体基板の上方に第1の半導体膜を形成する工程と、第1領域内の前記第1の半導体膜をエッチングする工程と、前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、前記マスクを除去する工程と、前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(付記3)前記第1領域はトランジスタ形成領域であり、前記第2領域はコンデンサ形成領域であり、前記第3領域はメモリセル形成領域であることを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4)前記第1絶縁膜、前記第1の誘電体膜及び前記第2の誘電体膜の上に第2の半導体膜を形成する工程と、前記メモリセル形成領域において、前記第2の半導体膜、前記第1の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第1の誘電体膜を挟むフローティングゲート電極とコントロールゲート電極を形成する工程と、前記コンデンサ形成領域において、前記第2の半導体膜、前記第2の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第2の誘電体膜を挟む第1、第2の電極を有するコンデンサを形成する工程と、前記第1トランジスタ形成領域において前記第2の半導体膜をパターニングすることによりMOSトランジスタのゲート電極を形成する工程と、有することを特徴とする付記3に記載の半導体装置の製造方法。

(付記5)前記第1の絶縁膜は、前記半導体基板の表面を熱酸化することにより形成されることを特徴とする付記1乃至付記4のいずれか1つに記載の半導体装置の製造方法。

(付記6)前記半導体基板の表面を熱酸化して前記第1の絶縁膜を形成すると同時に、前記第2の誘電体膜の前記窒化膜の表面を熱酸化し、前記第2の酸化膜よりも薄い窒化酸化膜を前記窒化膜の上に形成することを特徴とする付記1乃至付記5のいずれかに記載の半導体装置の製造方法。

(付記7)前記第1の絶縁膜は、前記第2領域内の前記第2酸化膜をエッチングする前に、前記半導体基板の表面を熱酸化することにより形成されることを特徴とする付記1又は付記3に記載の半導体装置の製造方法。

(付記8)前記第1の絶縁膜を前記半導体基板の第4領域にも形成する工程と、前記第4領域の前記第1の絶縁膜を除去した後に、前記半導体基板を熱酸化して前記第4領域に第2の絶縁膜を形成し、同時に前記第1領域の前記半導体基板の上の前記第1の絶縁膜の厚さを増やす工程と、を有することを特徴とする付記5に記載の半導体装置の製造方法。

(付記9)前記第1の誘電体膜を通して前記第1領域の前記半導体基板内に不純物をイオン注入し、第1の一導電型ウェルを形成する工程を有することを特徴とする付記1乃至付記8のいずれか1つに記載の半導体装置の製造方法。

(付記10)前記第1の半導体膜を形成する前に、前記半導体基板の上に第3の絶縁膜を形成する工程を有することを特徴とする付記1乃至付記9のいずれか1つに記載の半導体装置の製造方法。

(付記11)前記第2領域内の前記半導体基板の中に第2の一導電型ウェルを形成する工程と、前記一導電型ウェルと前記第1の半導体膜の間にコンデンサ用誘電体膜として第4の絶縁膜を形成する工程と、を有することを特徴とする付記1乃至付記10のいずれか1つに記載の半導体装置の製造方法。

【符号の説明】

【0132】

1 シリコン基板(半導体基板)

5 素子分離絶縁膜

7 シリコン酸化膜

9〜11、22、23 Pウェル

16 アモルファスシリコン膜

18 シリコン酸化膜

19 シリコン窒化膜

20 シリコン酸化膜

21 ONO膜

21a NO膜

25、26、27 ゲート絶縁膜

30 ポリシリコン膜

30a、30b、30c ゲート電極

33a 第1の電極

33b 第2の電極

33c 誘電体膜

33d コンタクトホール

FG フローティングゲート電極

CG コントロールゲート電極

Q1、Q2 コンデンサ

【特許請求の範囲】

【請求項1】

半導体基板の上方に第1の半導体膜を形成する工程と、

第1領域の前記第1の半導体膜をエッチングする工程と、

前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、

前記第1領域内の前記第1の誘電体膜をエッチングする工程と、

前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、

前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、

前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、

前記マスクを除去する工程と、

前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板の上方に第1の半導体膜を形成する工程と、

第1領域内の前記第1の半導体膜をエッチングする工程と、

前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、

前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、

前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、

前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、

前記マスクを除去する工程と、

前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項3】

前記第1領域はトランジスタ形成領域であり、前記第2領域はコンデンサ形成領域であり、前記第3領域はメモリセル形成領域であることを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1絶縁膜、前記第1の誘電体膜及び前記第2の誘電体膜の上に第2の半導体膜を形成する工程と、

前記メモリセル形成領域において、前記第2の半導体膜、前記第1の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第1の誘電体膜を挟むフローティングゲート電極とコントロールゲート電極を形成する工程と、

前記コンデンサ形成領域において、前記第2の半導体膜、前記第2の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第2の誘電体膜を挟む第1、第2の電極を有するコンデンサを形成する工程と、

前記第1トランジスタ形成領域において前記第2の半導体膜をパターニングすることによりMOSトランジスタのゲート電極を形成する工程と、

を有することを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記半導体基板の表面を熱酸化して前記第1の絶縁膜を形成すると同時に、前記第2の誘電体膜の前記窒化膜の表面を熱酸化し、前記第2の酸化膜よりも薄い窒化酸化膜を前記窒化膜の上に形成することを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板の上方に第1の半導体膜を形成する工程と、

第1領域の前記第1の半導体膜をエッチングする工程と、

前記第1領域の前記半導体基板の上方と第2領域及び第3領域の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、

前記第1領域内の前記第1の誘電体膜をエッチングする工程と、

前記第1領域内の前記半導体基板の上に第3酸化膜を形成する工程と、

前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、

前記マスクの前記開口部を通して、前記第1領域内の前記第3酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜を同時にエッチングすることにより、前記第1領域で前記半導体基板の表面を露出し、さらに前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、

前記マスクを除去する工程と、

前記半導体基板のうち前記第1領域の上に第1絶縁膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板の上方に第1の半導体膜を形成する工程と、

第1領域内の前記第1の半導体膜をエッチングする工程と、

前記第1領域内の前記半導体基板の上方と第2領域及び第3領域内の前記第1の半導体膜の上方に、第1酸化膜、窒化膜、第2酸化膜を順に積層し、複数層構造の第1の誘電体膜を形成する工程と、

前記第1領域内の前記第1の誘電体膜の前記第2酸化膜、前記窒化膜をエッチングし、前記第1酸化膜を残す工程と、

前記第1領域及び前記第2領域に開口部を有し、さらに前記第3領域内の前記第1の誘電体膜を覆う形状を有するマスクを前記半導体基板の上方に形成する工程と、

前記マスクの開口部を通して前記第1領域内の前記第1酸化膜と前記第2領域内の前記第1の誘電体膜の前記第2酸化膜をエッチングすることにより、前記第2領域内で薄層化された前記第1の誘電体膜を第2の誘電体膜として使用する工程と、

前記マスクを除去する工程と、

前記第1領域内の前記半導体基板の上に第1絶縁膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項3】

前記第1領域はトランジスタ形成領域であり、前記第2領域はコンデンサ形成領域であり、前記第3領域はメモリセル形成領域であることを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1絶縁膜、前記第1の誘電体膜及び前記第2の誘電体膜の上に第2の半導体膜を形成する工程と、

前記メモリセル形成領域において、前記第2の半導体膜、前記第1の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第1の誘電体膜を挟むフローティングゲート電極とコントロールゲート電極を形成する工程と、

前記コンデンサ形成領域において、前記第2の半導体膜、前記第2の誘電体膜及び前記第1の半導体膜をパターニングすることにより、前記第2の誘電体膜を挟む第1、第2の電極を有するコンデンサを形成する工程と、

前記第1トランジスタ形成領域において前記第2の半導体膜をパターニングすることによりMOSトランジスタのゲート電極を形成する工程と、

を有することを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記半導体基板の表面を熱酸化して前記第1の絶縁膜を形成すると同時に、前記第2の誘電体膜の前記窒化膜の表面を熱酸化し、前記第2の酸化膜よりも薄い窒化酸化膜を前記窒化膜の上に形成することを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【図1A】

【図1D】

【図1G】

【図1J】

【図1M】

【図1P】

【図1R】

【図1T】

【図1V】

【図1X】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11D】

【図1D】

【図1G】

【図1J】

【図1M】

【図1P】

【図1R】

【図1T】

【図1V】

【図1X】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11D】

【公開番号】特開2013−16598(P2013−16598A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−147634(P2011−147634)

【出願日】平成23年7月1日(2011.7.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年7月1日(2011.7.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]