半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、素子分離領域を形成する工程を含む半導体装置の製造方法に適用して有効な技術に関する。

【背景技術】

【0002】

半導体基板に溝を形成し、この溝に絶縁膜を埋め込むことで、素子分離領域が形成される。この素子分離領域で規定された活性領域に種々の半導体素子が形成されることにより、半導体装置が製造される。各活性領域同士は、素子分離領域によって電気的に分離することができる。

【0003】

特開2006−173260号公報(特許文献1)には、ウェットエッチング処理を行う前に半導体基板を除電する処理を行う技術が記載されている。

【0004】

特開2008−113028号公報(特許文献2)には、水素の標準電極電位よりも正電位である物質をシリコン表面に局所的に付着させ、前記シリコンに対する光を遮断して当該シリコンに生成される電子正孔対を抑制しつつ、当該シリコン表面のうち前記物質が付着する部分でHFと当該シリコンを酸化反応させて電子e−を生成し、当該電子e−を水素イオンH+と反応させる技術が記載されている。

【0005】

特開2009−49293号公報(特許文献3)に記載の技術は、基板12の上に第1の絶縁膜11を形成する工程(a)と、第1の絶縁膜11をウェットエッチングにより選択的に除去する工程(c)と、基板12における第1の絶縁膜11が除去された領域の上に第2の絶縁膜17を形成する工程(d)とを備えている。そして、工程(c)では、少なくともウェットエッチングを開始してから薬液が基板と接液するまでの期間において基板12の表面に可視光又は赤外光からなる照明光を照射している(ここで記載されている符号は特許文献3における符号に対応している)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−173260号公報

【特許文献2】特開2008−113028号公報

【特許文献3】特開2009−49293号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者の検討によれば、次のことが分かった。

【0008】

素子分離領域の形成工程について検討したところ、素子分離領域形成後に半導体基板にピット(窪み、穴)が発生しやすいことが分かった。

【0009】

素子分離領域を形成するには、まず、半導体基板の主面に酸化膜を形成してから、その酸化膜上に窒化シリコン膜を形成し、窒化シリコン膜、酸化膜および半導体基板に素子分離用の溝を形成する。それから、この溝を埋めるように酸化シリコン膜を形成してから、CMP処理により溝の外部の酸化シリコン膜を除去し、溝内に酸化シリコン膜を残す。そして、窒化シリコン膜を除去する。このようにして、溝に埋め込まれた酸化シリコン膜からなる素子分離領域が形成される。その後、半導体基板の主面の酸化膜をウェットエッチングで除去して半導体基板を露出させる。このような素子分離領域形成工程において、半導体基板の主面の酸化膜をウェットエッチングで除去して半導体基板を露出させたときに、半導体基板にピットが発生しやすいことが分かった。

【0010】

半導体基板にピットが発生した場合、そのピットを含む半導体チップ領域(半導体ウエハにおいて後で個々の半導体チップが取得される各領域を半導体チップ領域と称する)から取得された半導体チップ(半導体装置)の信頼性を低下させる虞がある。また、ピットを含む半導体チップ領域から取得された半導体チップを選別して除去する場合は、半導体装置の製造歩留まりを低下させ、コスト上昇の原因となる。

【0011】

本発明の目的は、半導体装置の信頼性を向上させることができる技術を提供することにある。

【0012】

また、本発明の目的は、半導体装置の製造歩留まりを向上させることができる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板の主面に第1絶縁膜を形成する工程、(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程を有している。更に、(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程を有している。そして、前記(f)工程では、前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングする。

【0016】

また、他の代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板の主面に第1絶縁膜を形成する工程、(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程を有している。更に、(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程を有している。そして、前記(f)工程では、前記半導体基板の主面に光を当てながら前記第1絶縁膜をウェットエッチングし、前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面の照度が、前記(f)工程における前記半導体基板の主面の照度よりも低くなるようにする。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

代表的な実施の形態によれば、半導体装置の信頼性を向上させることができる。

【0019】

また、半導体装置の製造コストを低減させることができる。

【図面の簡単な説明】

【0020】

【図1】本発明の一実施の形態である半導体装置の製造工程の一部を示す製造プロセスフロー図である。

【図2】本発明の一実施の形態である半導体装置の製造工程の一部を示す製造プロセスフロー図である。

【図3】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の要部断面図である。

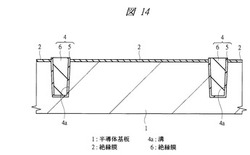

【図13】図12に続く半導体装置の製造工程中の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の要部断面図である。

【図18】図17に続く半導体装置の製造工程中の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の要部断面図である。

【図20】図19に続く半導体装置の製造工程中の要部断面図である。

【図21】図20に続く半導体装置の製造工程中の要部断面図である。

【図22】図21に続く半導体装置の製造工程中の要部断面図である。

【図23】図22に続く半導体装置の製造工程中の要部断面図である。

【図24】図23に続く半導体装置の製造工程中の要部断面図である。

【図25】図24に続く半導体装置の製造工程中の要部断面図である。

【図26】図25に続く半導体装置の製造工程中の要部断面図である。

【図27】図26に続く半導体装置の製造工程中の要部断面図である。

【図28】図27に続く半導体装置の製造工程中の要部断面図である。

【図29】図28に続く半導体装置の製造工程中の要部断面図である。

【図30】ステップS11の絶縁膜の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)の説明図である。

【図31】ステップS11の絶縁膜の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)の説明図である。

【図32】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図33】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図34】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図35】半導体ウエハの主面の電荷分布の説明図である。

【図36】半導体ウエハの主面の電荷分布の説明図である。

【図37】ピットの発生状況を示す説明図である。

【発明を実施するための形態】

【0021】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0022】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0023】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0024】

<半導体装置の製造工程>

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図1は、本発明の一実施の形態である半導体装置、例えばMISFET(Metal Insulator Semiconductor Field Effect Transistor)を有する半導体装置の製造工程の一部を示す製造プロセスフロー図である。図3〜図29は、本発明の一実施の形態である半導体装置、例えばMISFETを有する半導体装置の製造工程中の要部断面図である。

【0025】

まず、図3に示されるように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する(図1のステップS1)。次に、図4に示されるように、半導体基板1を酸化(好ましくは熱酸化)して半導体基板1の表面(主面)に絶縁膜(酸化膜)2を形成する(図1のステップS2)。次に、図5に示されるように、半導体基板1の主面(主面全面)上に、すなわち絶縁膜2上に、CVD(Chemical Vapor Deposition:化学気相成長)法(例えば熱CVD法)などにより、絶縁膜3を形成(堆積)する(図1のステップS3)。絶縁膜2は、好ましくは酸化シリコン膜からなり、絶縁膜3は好ましくは窒化シリコン膜からなる。絶縁膜2の厚みは、例えば5〜20nm程度とすることができ、絶縁膜3の厚みは、例えば100〜500nm程度とすることができる。

【0026】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜3上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図6に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR1を形成する。フォトレジストパターンPR1は、後述の溝4a形成予定領域に開口部を有している。

【0027】

次に、フォトレジストパターンPR1をエッチングマスクとして用いて、絶縁膜3、絶縁膜2および半導体基板1を順次ドライエッチング(プラズマドライエッチング)することにより、図7に示されるように、溝(素子分離用の溝)4aを形成する(図1のステップS4)。このステップS4では、プラズマドライエッチングによって溝4aを形成する。溝4aは、絶縁膜3、絶縁膜2および半導体基板1にかけて形成されている。すなわち、溝4aは、絶縁膜3および絶縁膜2を貫通し、溝4aの底部が半導体基板1の厚みの途中に位置するように形成されている。半導体基板1における溝4aの深さ(半導体基板1の表面から溝4aの底面までの深さ)は、例えば300〜700nm程度である。溝4aは、素子分離用の溝であり、すなわち後述する素子分離領域4を形成するための溝である。溝4aの形成後、フォトレジストパターンPR1は除去する。図7には、フォトレジストパターンPR1を除去した段階(状態)が示されている。

【0028】

ここで、プラズマドライエッチングとは、プラズマを利用したドライエッチングのことである。プラズマドライエッチングには、主にラジカルによってエッチングが進行する場合と、主にイオンによってエッチングが進行する場合と、ラジカルとイオンの両方によってエッチングが進行する場合とが含まれる。このため、主にラジカルよってエッチングが進行するプラズマエッチングだけでなく、主にイオンによってエッチングが進行する反応性イオンエッチング(Reactive Ion Etching:RIE)も、プラズマドライエッチングに含むものとする。

【0029】

次に、図8に示されるように、溝4aの内部(すなわち溝4aの底面および側壁)と絶縁膜3の表面とを酸化(好ましくは熱酸化)して絶縁膜5を形成する(図1のステップS5)。絶縁膜5は、酸化膜であり、溝4aの内部(すなわち溝4aの底面および側壁上)と絶縁膜3の表面上とに形成されるが、絶縁膜5のうち、溝4aの底面および側壁で露出する半導体基板1の露出面に形成された部分は、酸化シリコン膜からなり、絶縁膜3の表面に形成された部分は、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜5の厚みは、例えば5〜20nm程度とすることができる。

【0030】

次に、図9に示されるように、半導体基板1の主面(主面全面)上に、すなわち絶縁膜5上に、溝4a内を埋めるように、絶縁膜6を形成(堆積)する(図1のステップS6)。絶縁膜6は、好ましくは酸化シリコン膜からなる。絶縁膜6は、好ましくはプラズマCVDにより形成し、特に好ましくはHDP(High Density Plasma:高密度プラズマ)−CVD法により形成する。絶縁膜6は、溝4a内を埋めることができるような厚みに形成する。溝4aの深さにもよるが、絶縁膜6の厚みは500〜1000nm程度とすることができる。プラズマCVD法(特にHDP−CVD法)により絶縁膜6を成膜した場合、絶縁膜5は、絶縁膜6を堆積する際の半導体基板1へのダメージを防止する作用を備えている。絶縁膜6の形成後、スクラバ洗浄(例えば純水を使用したスクラバ洗浄)のような洗浄処理が行われる。

【0031】

次に、溝4aに埋め込んだ絶縁膜6を焼き締めるための熱処理(アニール処理)を行う。この熱処理は、半導体基板1を例えば400〜1200℃程度で熱処理することにより、行うことができる。

【0032】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜6上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図10に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR2を形成する。フォトレジストパターンPR2は、平面視で、溝4aを覆い(すなわち溝4aと重なり)、かつ溝4aが形成されていない領域を露出するようなパターン形状を有している。

【0033】

次に、フォトレジストパターンPR2をエッチングマスクとして用いて、絶縁膜6をドライエッチング(プラズマドライエッチング)することにより、フォトレジストパターンPR2から露出する部分の絶縁膜6(すなわち平面視で溝4aに重ならない領域の絶縁膜6)をエッチバックして厚みを薄くする(図1のステップS7)。このステップS7は、プラズマドライエッチングを用いることが好ましい。その後、フォトレジストパターンPR2をアッシング(プラズマアッシング)などにより除去し、更に、洗浄処理(例えば純水を使用した洗浄処理)が行われる。図11には、フォトレジストパターンPR2を除去した段階(状態)が示されている。ステップS7は、後で行うステップS8のCMP処理におけるディッシングなどを抑制または防止するために行われるが、それが気にならない場合は、ステップS7を省略することもできる。

【0034】

次に、絶縁膜6をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨する(図1のステップS8)。これにより、図12に示されるように、溝4aの外部の絶縁膜6が除去され、溝4a内に絶縁膜6が残される。また、このCMP処理の際に、絶縁膜3上の絶縁膜5も除去され、絶縁膜3の上面が露出される。また、ステップS8のCMP処理は、絶縁膜6,5(酸化シリコン膜)の研磨速度に比べて、絶縁膜3(窒化シリコン膜)の研磨速度が小さくなるような条件で行われるため、絶縁膜3はCMP処理のストッパ膜(または保護膜)として機能することができる。

【0035】

次に、図13に示されるように、溝4a内の絶縁膜6の上部(上面)をドライエッチング(プラズマドライエッチング)によってエッチバックすることにより、溝4a内の絶縁膜6の上面を後退させる(図1のステップS9)。このステップS9は、プラズマドライエッチングを用いることが好ましいが、絶縁膜6(酸化シリコン膜)のエッチング速度に比べて絶縁膜3(窒化シリコン膜)のエッチング速度が小さくなるようなエッチング条件で行われる。このため、ステップS9の前(かつステップS8の後)には、溝4a内の絶縁膜6の上面の高さ位置は、絶縁膜3の上面の高さ位置とほぼ同じであったものが、ステップS9の後(かつ後述のステップS10の前)には、溝4a内の絶縁膜6の上面の高さ位置は、絶縁膜3の上面の高さ位置よりも低くなる。但し、溝4a内の絶縁膜6の上面の高さ位置が、半導体基板1と絶縁膜2との界面の高さ位置よりも低くなる前に、ステップS9のドライエッチング(プラズマドライエッチング)を終了することが好ましい。図13には、溝4a内の絶縁膜6の上面の高さ位置が、絶縁膜2の上面の高さ位置と絶縁膜3の上面の高さ位置との間に位置する場合が示されている。

【0036】

次に、図14に示されるように、熱リン酸などの薬液(エッチング液)を用いたウェットエッチングにより絶縁膜3を除去する(図1のステップS10)。この際のウェットエッチングは、絶縁膜3(窒化シリコン膜)のエッチング速度に比べて絶縁膜6,5,2(酸化シリコン膜)のエッチング速度が小さくなるようなエッチング条件で行われる。このため、ステップS10では、絶縁膜3が選択的に除去されて、絶縁膜2の上面が露出される。

【0037】

次に、図15に示されるように、フッ酸などの薬液(エッチング液)を用いたウェットエッチングにより、絶縁膜2を除去する(図1のステップS11)。絶縁膜2を除去したことにより、半導体基板1の上面(表面、Si面)が露出される。すなわち、ステップS11では、絶縁膜2をウェットエッチングして除去することにより、半導体基板1のSi面が露出される。また、ステップS11のウェットエッチングは、絶縁膜2が除去されて半導体基板1の上面が露出される程度だけ行うため、溝4aの内部の絶縁膜6,5は、ほとんどエッチングされずに残存する。溝4aの内部に残存する絶縁膜5および絶縁膜6により、素子分離領域(素子分離)4が形成される。

【0038】

ステップS11を行う直前の段階で溝4aの内部に残存する絶縁膜5および絶縁膜6を素子分離領域4とみなすこともできるが、この場合、ステップS11直前における素子分離領域4の上面がステップS11でわずかにエッチングされたものが、ステップS11後の素子分離領域4となる。

【0039】

また、ステップS11では、半導体基板1の主面上(すなわち絶縁膜2上)にレジスト層(フォトレジスト層)が形成されていない状態で絶縁膜2をウェットエッチングするため、半導体基板1の主面全面で絶縁膜2がエッチングされて除去される。このため、ステップS11を行うと、素子分離領域4が形成されている領域以外の領域(すなわち活性領域)の半導体基板1の表面(Si面)が露出された状態となる。このステップS11の絶縁膜2の除去工程(ウェットエッチング工程)については、後でより詳細に説明する。

【0040】

このようにして、半導体基板1の溝4a内に埋め込まれた絶縁膜5,6からなる素子分離領域4が形成される。絶縁膜6に比べて絶縁膜5は薄いため、素子分離領域4は、主として溝4a内に埋め込まれた絶縁膜6により形成される。このように、素子分離領域4は、STI(Shallow Trench Isolation)法により形成される。素子分離領域4を形成したことで、半導体基板1においては、素子分離領域4によって活性領域が規定(画定)され、その活性領域に、以降の工程で種々の半導体素子(例えば後述するMISFETQ1,Q2など)が形成される。

【0041】

次に、図16に示されるように、半導体基板1の主面から所定の深さに渡ってウエル領域を形成する(図2のステップS12)。本実施の形態では、MISFETとしてnチャネル型のMISFETを形成する場合について説明するため、ここでは、ウエル領域としてp型ウエル(p型のウエル領域)PWを形成する。p型ウエルPWは、半導体基板1に対してホウ素(B)などのp型の不純物をイオン注入することによって形成することができる。pチャネル型のMISFETを形成する場合は、半導体基板1に対してリン(P)またはヒ素(As)などのn型の不純物をイオン注入することによって、n型のウエル領域(n型ウエル)を形成する。

【0042】

次に、図17に示されるように、半導体基板1の表面(すなわちp型ウエルPWの表面)上に、MISFETのゲート絶縁膜用の絶縁膜11を形成する(図2のステップS13)。絶縁膜11は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0043】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜11上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図18に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR3を形成する。

【0044】

次に、図19に示されるように、フォトレジストパターンPR3をエッチングマスクとして用いて、絶縁膜11をエッチングしてフォトレジストパターンPR3から露出する部分の絶縁膜11を選択的に除去する(図2のステップS14)。この際、フォトレジストパターンPR3に覆われた部分の絶縁膜11は除去されずに残存する。ステップS14のエッチングには、薬液(エッチング液)としてフッ酸などを用いたウェットエッチングを採用することができる。絶縁膜11が除去された領域では、半導体基板1の上面(表面、Si面)が露出する。

【0045】

ここで、高耐圧のMISFETが形成される予定領域(以下、高耐圧MIS領域1Aと称す)では、絶縁膜11が残され、一方、低耐圧のMISFETが形成される予定領域(以下、低耐圧MIS領域1Bと称す)では、絶縁膜11が除去されて半導体基板1の上面(すなわちSi面)が露出される。つまり、フォトレジストパターンPR3は、平面視で、高耐圧MIS領域1Aを覆い、かつ低耐圧MIS領域1Bを露出するようなパターン形状を有している。また、フォトレジストパターンPR3を用いた絶縁膜11のウェットエッチング(すなわちステップS14)を行う前に、アッシャーを用いたプラズマ処理などによりフォトレジストパターンPR3に対して表面処理(プラズマ表面処理)を行い、それによってウェットエッチング時の濡れ性向上(フォトレジストパターンPR3に対する濡れ性向上)を図ることもできる。

【0046】

次に、図20に示されるように、フォトレジストパターンPR3を除去する。フォトレジストパターンPR3の除去には、ウェット処理による除去を用い、例えばSPM(Sulfuric acid-Hydrogen Peroxide Mixture)液を用いたSPM洗浄を用いることができる。

【0047】

次に、上記ステップS14のウェットエッチング工程(フォトレジストパターンPR3をエッチングマスクとして絶縁膜11をウェットエッチングする工程)で絶縁膜11が除去された領域(すなわち低耐圧MIS領域1B)における半導体基板1の表面(すなわちp型ウエルPWの表面)上に、図21に示されるように、酸化(例えば熱酸化)によりMISFETのゲート絶縁膜用の絶縁膜12を形成する(図2のステップS15)。絶縁膜12は、例えば薄い酸化シリコン膜などからなる。絶縁膜12を形成する際に、絶縁膜11の厚みが厚くなる場合もあり得る。

【0048】

ステップS15で絶縁膜12を形成した段階(すなわち図21の段階)で絶縁膜12の厚みが絶縁膜11の厚みよりも薄くなるように、絶縁膜11と絶縁膜12との各形成時の厚みを制御する必要がある。このためには、ステップS13で絶縁膜11を形成した段階(図17の段階)の絶縁膜11の厚みを、ステップS15で絶縁膜12を形成した段階(図21の段階)の絶縁膜12の厚みよりも厚くすればよいが、絶縁膜12を(好ましくは熱酸化により)形成する際に絶縁膜11の厚みが厚くなる場合もあり得る。

【0049】

このようにして、図21に示されるように、低耐圧MIS領域1Bの半導体基板1(p型ウエルPW)の表面に絶縁膜12が形成され、高耐圧MIS領域1Aの半導体基板1(p型ウエルPW)の表面に絶縁膜12よりも厚い絶縁膜11が形成された状態が得られる。

【0050】

次に、図22に示されるように、半導体基板1の主面(主面全面)上に、ゲート電極用の導電体膜13を形成する(図2のステップS16)。導電体膜13は、例えば多結晶シリコン膜(ドープトポリシリコン膜)とすることができる。それから、半導体基板1の主面(主面全面)上に、すなわち導電体膜13上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR4を形成する。それから、フォトレジストパターンPR4をエッチングマスクとしたドライエッチング(プラズマドライエッチング)により導電体膜13をエッチングしてパターニングし、図23に示されるように、パターニングされた導電体膜13からなるゲート電極GEを形成する(図2のステップS17)。ゲート電極GEのうち、高耐圧のMISFET用のゲート電極GE1は、半導体基板1(p型ウエルPW)上に絶縁膜11を介して形成され、低耐圧のMISFET用のゲート電極GE2は、半導体基板1(p型ウエルPW)上に絶縁膜12を介して形成される。その後、フォトレジストパターンPR4は除去される。図23には、フォトレジストパターンPR4を除去した段階(状態)が示されている。ゲート電極GE1の下に絶縁膜11が残存し、ゲート電極GE2の下に絶縁膜12が残存するが、ゲート電極GE1,GE2で覆われない領域の絶縁膜11,12が層状に残存する場合もあり得る。

【0051】

次に、図24に示されるように、p型ウエルPWのゲート電極GEの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、n型のエクステンション領域(n−型半導体領域)EXを形成する(図2のステップS18)。エクステンション領域EXは、n型の半導体領域である。このイオン注入の際に、ゲート電極GEはイオン注入阻止マスクとして機能することができるため、p型ウエルPWにおけるゲート電極GEの直下の領域には、不純物はイオン注入されず、エクステンション領域EXは、ゲート電極GEの側壁に整合(自己整合)して形成される。

【0052】

次に、図25に示されるように、ゲート電極GEの側壁上に、側壁絶縁膜(絶縁膜)として、例えば酸化シリコンまたは窒化シリコンあるいはそれら絶縁膜の積層膜などからなるサイドウォールスペーサ(側壁スペーサ、側壁絶縁膜、サイドウォール)SPを形成する(図2のステップS19)。サイドウォールスペーサSPは、例えば、半導体基板1の主面(主面全面)上に酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜を堆積し、この酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0053】

サイドウォールスペーサSPの形成後、図26に示されるように、p型ウエルPWのゲート電極GEおよびサイドウォールスペーサSPの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、n型のソース・ドレイン領域(n+型半導体領域)SDを形成する(図2のステップS20)。ソース・ドレイン領域SDは、n型の半導体領域である。このイオン注入の際に、ゲート電極GEおよびその側壁上のサイドウォールスペーサSPはイオン注入阻止マスクとして機能することができるため、p型ウエルPWにおけるゲート電極GEの直下の領域とそのゲート電極GEの側壁上のサイドウォールスペーサSPの直下の領域とには、不純物は導入(イオン注入)されない。このため、ソース・ドレイン領域SDは、ゲート電極GEの側壁上のサイドウォールスペーサSPの側面(ゲート電極GEに接している側とは反対側の面)に整合(自己整合)して形成される。

【0054】

ソース・ドレイン領域SD形成用のイオン注入の後、導入した不純物の活性化のためのアニール処理を行う(図2のステップS21)。このアニール処理は、例えば、1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0055】

同じMISFET(同じゲート電極GEに対して)に対して形成されているエクステンション領域EXとソース・ドレイン領域SDとの対により、nチャネル型MISFETのLDD(Lightly doped Drain)構造のソースまたはドレインとして機能するn型の半導体領域が形成される。同じMISFET(同じゲート電極GE)に対して形成されているエクステンション領域EXとソース・ドレイン領域SDとの関係は、ソース・ドレイン領域SDとチャネル領域(ゲート電極GEの直下の領域)との間にエクステンション領域EXが介在し、ソース・ドレイン領域SDはエクステンション領域EXよりも、不純物濃度が高くかつ深さ(接合深さ)が深くなっている。

【0056】

このようにして、図26に示されるように、p型ウエルPWに、電界効果トランジスタとしてnチャネル型のMISFET(Metal Insulator Semiconductor Field Effect Transistor)Qn1,Q2が形成される。ゲート電極GE1をそのゲート電極とするMISFETQ1は、ゲート電極GE1の下に位置する絶縁膜11がゲート絶縁膜として機能し、ゲート電極GE2をそのゲート電極とするMISFETQ2は、ゲート電極GE2の下に位置する絶縁膜12がゲート絶縁膜として機能する。このため、MISFETQ1のゲート絶縁膜(ここでは絶縁膜11)の厚みは、MISFETQ2のゲート絶縁膜(ここでは絶縁膜12)の厚みよりも厚く、MISFETQ1の耐圧はMISFETQ2の耐圧より高くなっている。このため、MISFETQ1の動作電圧を、MISFETQ2の動作電圧よりも高くすることができる。MISFETQ1は高耐圧MIS領域1Aに形成され、MISFETQ2は低耐圧MIS領域1Bに形成される。

【0057】

なお、MISFETとしてnチャネル型MISFETを形成する場合について説明したが、nチャネル型MISFETの代わりにpチャネル型MISFETを形成することもでき、この場合、p型ウエルPW、エクステンション領域EXおよびソース・ドレイン領域SDの各導電型を逆にすればよい(すなわちp型ウエルPWをn型ウエルとし、エクステンション領域EXをp型とし、ソース・ドレイン領域SDをp型とすればよい)。また、nチャネル型MISFETとpチャネル型MISFETの両方を形成することもできる。

【0058】

また、図26において、高耐圧MIS領域1Aと低耐圧MIS領域1Bとの間(MISFETQ1が形成されている領域とMISFETQ2が形成されている領域との間)に素子分離領域4を設ける(配置する)こともできる。

【0059】

次に、サリサイド(Salicide:Self Aligned Silicide)技術により、ゲート電極GEおよびソース・ドレイン領域SDの表面(表層部分、上層部分)に、コバルトシリサイドまたはニッケルシリサイドなどからなる低抵抗の金属シリサイド層(図示せず)を形成することもできる。この金属シリサイド層は、ゲート電極GEおよびソース・ドレイン領域SDを覆うように例えばコバルト(Co)膜またはニッケル(Ni)膜などの金属膜を堆積して熱処理することにより、形成することができ、その後、未反応の金属膜は除去される。

【0060】

次に、図27に示されるように、半導体基板1の主面(主面全面)上に絶縁膜(層間絶縁膜)22を形成する。すなわち、ゲート電極GEおよびサイドウォールスペーサSPを覆うように、半導体基板1の主面上に絶縁膜22を形成する。絶縁膜22は、例えば、酸化シリコン膜の単体膜や、あるいは、窒化シリコン膜とそれよりも厚い酸化シリコン膜との積層膜などからなる。その後、絶縁膜22の表面(上面)をCMP法により研磨するなどして、絶縁膜22の上面を平坦化する。下地段差に起因して絶縁膜22の表面に凹凸形状が形成されていても、絶縁膜22の表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜を得ることができる。

【0061】

次に、絶縁膜22上に形成したフォトレジストパターン(図示せず)をエッチングマスクとして用いて、絶縁膜22をドライエッチングすることにより、図28に示されるように、絶縁膜22にコンタクトホール(貫通孔、孔)23を形成する。コンタクトホール23の底部では、半導体基板1の主面の一部、例えばソース・ドレイン領域SDの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)の一部や、ゲート電極GEの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)の一部などが露出される。

【0062】

次に、コンタクトホール23内に、タングステン(W)などからなる導電性のプラグ(接続用導体部)24を形成する。プラグ24を形成するには、例えば、コンタクトホール23の内部(底部および側壁上)を含む絶縁膜22上に、プラズマCVD法などによりバリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール23を埋めるように形成し、絶縁膜22上の不要な主導体膜およびバリア導体膜をCMP法またはエッチバック法などによって除去することにより、プラグ24を形成することができる。図面の簡略化のために、プラグ24は、主導体膜とバリア導体膜を一体化して示してある。プラグ24は、その底部で、ゲート電極GEまたはソース・ドレイン領域SDの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)などと接して、電気的に接続される。

【0063】

次に、図29に示されるように、プラグ24が埋め込まれた絶縁膜22上に、絶縁膜25を形成する。絶縁膜25は、複数の絶縁膜の積層膜で形成することもできる。

【0064】

次に、シングルダマシン法により第1層目の配線である配線M1を形成する。具体的には、次のようにして配線M1を形成することができる。まず、フォトレジストパターン(図示せず)をマスクとしたドライエッチング(プラズマドライエッチング)によって絶縁膜25の所定の領域に配線溝を形成した後、配線溝の底部および側壁上を含む絶縁膜25上にバリア導体膜(例えば窒化チタン膜、タンタル膜または窒化タンタル膜など)を形成する。続いて、CVD法またはスパッタリング法などによりバリア導体膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成して、銅めっき膜により配線溝の内部を埋め込む。それから、配線溝以外の領域の主導体膜(銅めっき膜およびシード層)とバリア導体膜をCMP法により除去して、配線溝に埋め込まれ銅を主導電材料とする第1層目の配線M1を形成する。図面の簡略化のために、配線M1は、バリア導体膜、シード層および銅めっき膜を一体化して示してある。

【0065】

配線M1は、プラグ24を介してゲート電極GEまたはソース・ドレイン領域SDなどと電気的に接続されている。その後、デュアルダマシン法により2層目の配線を形成するが、ここでは図示およびその説明は省略する。

【0066】

<ステップS11の絶縁膜2の除去工程について>

次に、上記ステップS11の絶縁膜2の除去工程(ウェットエッチング工程)について、より詳細に説明する。

【0067】

図30および図31は、ステップS11の絶縁膜2の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)31の説明図である。図30は、半導体製造装置31全体を模式的に示す平面図に対応し、図31は、半導体製造装置31における個々のエッチング用チャンバ33を模式的に示す断面図に対応している。

【0068】

図30の半導体製造装置31を用いてステップS11で絶縁膜2を除去する手順について、まず説明する。

【0069】

図30に示されるように、半導体製造装置31は、搬送室32、と搬送室32の周囲に配置された複数のエッチング用チャンバ33およびロードポート(ロードポート室)34とを有しており、いわゆるマルチチャンバタイプの半導体製造装置である。搬送室32とエッチング用チャンバ33との間と、搬送室32とロードポート(ロードポート室)34との間とは、開閉手段であるゲートバルブ(図示せず)などを介して連結されている。

【0070】

まず、フープ(図示せず)をロードポート(ロードポート室)34にドッキングした後、フープから半導体ウエハSWを取り出し、搬送室32に搬入する。半導体ウエハSWは、上記半導体基板1に対応するものである(すなわち半導体ウエハSWを上記半導体基板1とみなすことができる)。フープは半導体ウエハのバッチ搬送用の密閉収納容器であり、通常25枚、12枚、6枚等のバッチ単位で半導体ウエハを収納する。

【0071】

それから、搬送用ロボット35などによって半導体ウエハSWを、搬送室32を経てエッチング用チャンバ33内へ搬送する。そして、エッチング用チャンバ33内で、半導体ウエハSWから上記絶縁膜2を除去(ウェットエッチング)する処理(すなわち上記ステップS11の処理)を行う。

【0072】

本実施の形態では、半導体ウエハSWに光を当てる(光を照射する)ための光源として、照明装置(光源)36がエッチング用チャンバ33内に配置されている。照明装置36は、例えば蛍光灯などを用いることができる。照明装置36からの光を半導体ウエハSWに光を当てながら、半導体ウエハSWから上記絶縁膜2を除去(ウェットエッチング)する処理が行われる。

【0073】

エッチング用チャンバ33内で上記絶縁膜2を除去(ウェットエッチング)する処理が行われた後、半導体ウエハSWは搬送用ロボット35などによってエッチング用チャンバ33から搬送室32を経てロードポート(ロードポート室)34に搬送され、フープへ戻される。その後、半導体ウエハSWは、次の工程を行うための半導体製造装置に送られる。

【0074】

次に、ステップS11において、エッチング用チャンバ(エッチング装置)33内で行われる絶縁膜2の除去処理(ウェットエッチング処理)について、図31を参照しながら具体的に説明する。

【0075】

図31に示されるように、エッチング用チャンバ33内には、回転ステージ(ウエハ回転ステージ、スピンベース)41が配置されている。この回転ステージ41は、図示しない回転機構(例えばモータなど)によって高速で回転可能に構成された回転板であり、例えば半導体ウエハSWよりも大きな径を有している。エッチング用チャンバ33内に搬入された半導体ウエハSWは、この回転ステージ41上に載置(配置)され、図示しないチャック機構などによって回転ステージ41に保持される。この際、半導体ウエハSWは、絶縁膜2が形成された側の面である主面(表面、半導体素子形成側の主面)が上方を向き、主面とは反対側の面である裏面が下方(回転ステージ41に対向する側)を向くように、回転ステージ41上に配置されて固定される。図示しない回転機構によって回転ステージ41を回転させることで、回転ステージ41に保持された半導体ウエハSWも回転させることができる。

【0076】

回転ステージ41の上方に(例えば回転ステージ41に固定された半導体ウエハSWの主面の中央部上方に)ノズル42が配置され、このノズル42からエッチング液(洗浄液、エッチャント液、薬液)43を半導体ウエハSWの主面に向かって吐出(噴出、供給)し、半導体ウエハSWの主面にエッチング液43を供給できるように構成されている。エッチング液43は、半導体ウエハSWの主面に形成されている上記絶縁膜2をエッチング可能なエッチング液を用い、フッ酸(HF)の水溶液を好適に用いることができる。

【0077】

エッチング液43のフッ酸の濃度は、生産性に支障をきたさない範囲のエッチング時間で目的とするエッチング量を確保できるようにすればよく、例えば、5wt.%(5重量%以下程度の濃度とすることができる。

【0078】

半導体ウエハSWの主面に形成されている上記絶縁膜2を除去するには、絶縁膜2が形成されている半導体ウエハSWを、エッチング用チャンバ33内の回転ステージ41上に配置して固定してから(このとき、半導体ウエハSWにおいて、上記絶縁膜2が形成されている側の主面がノズル42側を向く)、回転ステージ41を回転させることによって、回転ステージ41に保持された半導体ウエハSWを回転させる。この際、回転ステージ41の回転の中心と半導体ウエハSWの主面の中心位置とをほぼ一致させることで、半導体ウエハSWの主面の中心位置を回転中心にして回転することが好ましい。

【0079】

半導体ウエハSWが回転した状態で、回転する半導体ウエハSWの主面に対して、ノズル42から半導体ウエハSWの主面の絶縁膜2をエッチングするためのエッチング液43を供給する。これにより、半導体ウエハSWの主面にノズル42からエッチング液43が供給され、このエッチング液43により、半導体ウエハSWの主面に形成されていた上記絶縁膜2がエッチング(ウェットエッチング)される。ノズル42から半導体ウエハSWの主面の中心部付近に供給されたエッチング液43は、半導体ウエハSWの回転によって、半導体ウエハSWの主面の中心部から外周部側に移動して、半導体ウエハSWの主面の全面にエッチング液43が行き渡り、半導体ウエハSWの主面の全面で、エッチング液43による絶縁膜2のエッチングが行われる。

【0080】

絶縁膜2のエッチングを停止するには、エッチング液用ノズル42から半導体ウエハSWの主面へのエッチング液43の供給を停止し、回転する半導体ウエハSWの主面(の中心部付近)へノズル42から純水などのリンス液(すすぎ液)を供給する。このリンス液が半導体ウエハSWの主面全体に行き渡ることで、半導体ウエハSWの主面のリンス処理(すすぎ処理)が行われ、半導体ウエハSWの主面からエッチング液43がリンス液とともに除去され、半導体ウエハSWの主面における絶縁膜2のエッチングが停止される。また、エッチング液43を半導体ウエハSWへ供給するノズルと、リンス液を半導体ウエハSWへ供給するノズルとを、同じノズル(ノズル42)で兼ねても、あるいは別々のノズルとしてもよい。

【0081】

本実施の形態では、絶縁膜2のウェットエッチング中の半導体ウエハSWの主面における照度を制御するために、上述のようにエッチング用チャンバ33に照明装置(光源)36が配置されている。照明装置36は、光44を発する光源として機能する。図31では、照明装置36が発する光44を矢印で模式的に示してある。照明装置36を設けるのは、照明装置36からの光44を半導体ウエハSWに当てる(照射する)ことで、絶縁膜2のエッチング中の半導体ウエハSWの照度を積極的に高くするためである。すなわち、エッチング液43を半導体ウエハSWの主面に供給して絶縁膜2のエッチングを行っている間、照明装置36によって半導体ウエハSWの主面を照らす(照明装置36からの光44を半導体ウエハSWの主面に当てる)ことにより、半導体ウエハSWの主面の照度を高くする。

【0082】

本実施の形態では、照明装置36からの光(照明装置36が発する光)を、半導体ウエハSWの主面に当てながら(照射しながら)、半導体ウエハSWの主面の絶縁膜2のエッチング(エッチング液43によるウェットエッチング)を行う。この際、半導体ウエハSWの主面の絶縁膜2のエッチング液43によるウェットエッチングの開始(半導体ウエハSWの主面にエッチング液43が接液した時点)から終了(リンス液によって半導体ウエハSWの主面からエッチング液43が除去された時点)まで、照明装置36からの光44を半導体ウエハSWの主面に当て続けるようにすることが好ましい。

【0083】

エッチング液43により絶縁膜2がウェットエッチングされる際に、照明装置36からの光44が半導体ウエハSWの主面全体に当たる(照射される)場合だけでなく、半導体ウエハSWの主面の一部に当たる(照射される)場合もあり得る。例えば、照明装置36から半導体ウエハSWの主面へ向かった光44の一部がノズル42で遮蔽されるなどして、照明装置36からの光44が半導体ウエハSWの主面全体ではなく、半導体ウエハSWの主面の一部に当たる(照射される)場合もあり得る。しかしながら、半導体ウエハSWは回転ステージ41とともに回転しているので、照明装置36からの光44が半導体ウエハSWの主面の一部に当たる(照射される)場合であっても、半導体ウエハSWの主面において光44が照射されている領域は、半導体ウエハSWの回転に伴い半導体ウエハSWの主面内を移動する。このため、絶縁膜2をエッチング液43でウェットエッチングしている間に、半導体ウエハSWの主面のいずれの領域も照明装置36からの光44が照射される期間を有することができる。逆に言えば、半導体ウエハSWの主面のいずれの領域も、絶縁膜2がエッチング液43でウェットエッチングされている間に照明装置36からの光44が照射される期間を有するように、半導体ウエハSWの主面の少なくとも一部に対して照明装置36からの光44を照射すればよい。つまり、半導体基板1(半導体ウエハSW)の主面が、絶縁膜2をウェットエッチングしている間に光44が全く照射されなかった領域を有さないようにすればよい。

【0084】

その理由は後述するが、本実施の形態では、半導体ウエハSWの主面の少なくとも一部(半導体ウエハSWの主面全面または主面の一部)に140ルクス以上の光を当てながら、絶縁膜2を(エッチング液43により)ウェットエッチングすることが好ましい。そして、半導体ウエハSWの主面のいずれの領域も、絶縁膜2を(エッチング液43により)ウェットエッチングしている間に140ルクス以上の光が照射されている期間を有するようにすることが、より好ましい。ここで、140ルクス以上の光とは、半導体ウエハSWの主面における照度が140ルクス以上であることに対応している。半導体ウエハSWの主面における照度は、光源(ここでは照明装置36)の明るさや、光源(ここでは照明装置36)から半導体ウエハSWの主面までの距離などにより制御することができる。

【0085】

<素子分離領域形成に伴う欠陥発生について>

次に、素子分離領域形成に伴う欠陥発生について説明する。

【0086】

図32〜図34は、絶縁膜2に相当する酸化膜102をウェットエッチングで除去したときに発生する欠陥の説明図である。

【0087】

図32〜図34において、酸化膜102は上記絶縁膜2に相当するものであり、溝104aは上記溝4aに相当するものであり、絶縁膜105は上記絶縁膜5に相当するものであり、絶縁膜106は上記絶縁膜6に相当するものであり、溝104a内に埋め込まれた絶縁膜105,106により形成された素子分離領域104は上記素子分離領域4に相当するものである。なお、図32は、上記ステップS11に相当する酸化膜102の除去工程(ウェットエッチング工程)を行う前の段階であり、図33は、上記ステップS11に相当する酸化膜102の除去工程(ウェットエッチング工程)を行った後の段階であり、図34は、酸化膜102の除去に伴って半導体基板1にピット(窪み、穴)51が形成された状態が示されている。

【0088】

図32の構造(状態)は、上記図14の構造(状態)を得るまでとほぼ同様の工程を行うことにより形成されている。図32の状態から、酸化膜102をフッ酸でウェットエッチングして除去することにより半導体基板1(のSi面)を露出させることで、上記図15に相当する図33の構造(状態)が得られるが、本発明者の解析によると、酸化膜102の除去に伴って図34のように半導体基板1にピット(窪み、穴)51が形成される場合がある。このピット51は、素子分離領域104で囲まれた活性領域において、酸化膜102をウェットエッチングして半導体基板1(のSi面)を露出させたときに発生する。

【0089】

このピット51の発生原因について、本発明者が検討したところ、素子分離領域104を形成する種々の工程に伴い酸化膜102に蓄えられた(チャージされた)電荷が主原因であることが分かった。酸化膜102をウェットエッチングするときに酸化膜102がエッチングの進行に伴って薄くなってくると、この電荷(酸化膜102に蓄えられた電荷)が半導体基板1側に放電してしまい、この放電によって半導体基板1にピット51が形成されることが分かった。

【0090】

半導体基板1にピット51が発生した場合、そのピット51を含む半導体チップ領域(半導体ウエハにおいて後で個々の半導体チップが取得される各領域を半導体チップ領域と称する)から取得された半導体チップ(半導体装置)の信頼性を低下させる虞がある。また、ピット51を含む半導体チップ領域から取得された半導体チップを選別して除去する場合は、半導体装置の製造歩留まりを低下させ、コスト上昇の原因となる。

【0091】

そこで、酸化膜102に電荷が蓄積される原因を調べたところ、素子分離領域104を形成するための種々の工程においてプラズマを用いる際に、半導体基板1の主面に形成されている絶縁膜にプラズマに起因した電荷が蓄積されることが、主原因であることが分かった。特に影響が大きいのは、素子分離用の溝104aを形成するためのプラズマドライエッチング(上記ステップS4に相当する工程)である。素子分離用の溝104aは深さが深いため、溝104aを形成するためのプラズマドライエッチングに要する時間が長く、溝104a形成のプラズマドライエッチングの際に、半導体基板1の主面に形成されている絶縁膜にプラズマに起因した電荷が蓄えられやすい(チャージされやすい)。溝104a形成時に半導体基板1の主面の絶縁膜に蓄えられた(チャージされた)電荷は、その後も除去されにくく、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。

【0092】

また、溝104a形成工程以外に、溝104aを埋める絶縁膜106(上記絶縁膜6に相当)を形成する工程(上記ステップS6に相当する工程)も、上記電荷蓄積への影響が大きい。これは、溝104aの深さが深いため、その溝104aを埋める絶縁膜106は溝104aを埋め込むことができるように厚く形成する必要があり、この厚い絶縁膜106を形成するのにプラズマCVD法を用いると、絶縁膜106形成時にプラズマに起因した電荷が蓄えられやすい(チャージされやすい)。絶縁膜106形成時に蓄えられた(チャージされた)電荷は、その後も除去されにくく、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。これは、絶縁膜106をプラズマCVD法で形成した場合に生じ得るが、特にプラズマ密度が高いHDP−CVD法により絶縁膜106を形成する場合に、より顕著に生じる。

【0093】

このように、溝104a形成工程と絶縁膜106形成工程とは、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。また、溝104a形成工程や絶縁膜106形成工程以外に、上記ステップS7,S9に相当するプラズマドライエッチング工程もプラズマを利用した処理であるため、これらの工程を行った場合は、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。また、プラズマ処理より影響は少ないが、酸化膜102を形成してから図32の構造を得るまでの間に行う種々の洗浄工程や、上記ステップS8に相当するCMP工程においても、静電気に起因した電荷の蓄積(チャージ)が発生し、これも図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。

【0094】

このように、酸化膜102を形成してから図32の構造を得るまでに、素子分離領域104を形成するための種々の工程で半導体基板1の主面に形成されている絶縁膜にチャージされた電荷は、酸化膜102を除去する直前の段階(図32の段階)では、酸化膜102にチャージされた状態となる。この電荷が、酸化膜102をウェットエッチングして半導体基板1を露出させる工程(図32から図33に移行する工程)において半導体基板1が露出する直前に酸化膜102の厚みが薄くなったときに、半導体基板1側に放電し、この放電によって半導体基板1にピット51が形成される。つまり、素子分離領域104を形成するための種々の工程で電荷がチャージされやすいことと、酸化膜102を形成してから酸化膜102をウェットエッチングして除去する(図32から図33に移行する工程)までの間に半導体基板1(のSi面)が露出されないこととにより、酸化膜102除去時に放電が起こりやすく、この放電によりピット51が形成されてしまう。素子分離領域104で囲まれた活性領域においては、酸化膜102に蓄えられていた電荷は逃げ場がないことから、酸化膜102をウェットエッチングしてその活性領域(のSi面)が露出する直前に、酸化膜102側から活性領域の半導体基板1(Si領域)側に電荷が放電して、ピット51が形成されるのである。また、酸化膜102のウェットエッチングにはフッ酸の水溶液のようにイオンを含む液体を用いるが、そのような液体を用いても、酸化膜102にチャージされている電荷を除去することは難しく、放電によりピット51が形成されてしまう。

【0095】

<本実施の形態の主要な特徴と効果>

そこで、本実施の形態では、ステップS11の絶縁膜2の除去(ウェットエッチング)工程において、照明装置36からの光44を半導体ウエハSWに当てる(照射する)ようにしている。すなわち、ステップS11では、半導体ウエハSWに照明装置36からの光44を当てながら(照射しながら)、絶縁膜2をウェットエッチングする。光44を半導体ウエハSWに当てるのは、光電効果によりSi基板(半導体基板1に対応するSi基板領域)で電荷(ここでは主として電子)を発生させてこれをSi基板側から絶縁膜2側に供給し、絶縁膜2に既に蓄えられていた電荷(主として正孔が蓄えられている)を中和させる(電子と正孔とを結合させて消滅させる)ためである。

【0096】

図35および図36は、ステップS11に相当する工程を行った半導体ウエハSWの主面の電荷分布の説明図である。図35は、本実施の形態とは異なり、照明装置36からの光44を半導体ウエハSWに当てずにステップS11(絶縁膜2のウェットエッチング)を行なった場合に対応し、図36は、本実施の形態のように、照明装置36からの光44を半導体ウエハSWに当てながらステップS11(絶縁膜2のウェットエッチング)を行なった場合に対応する。図35および図36において(a)で示されているのは、ステップS11を行ったときの半導体ウエハSWの主面における電荷分布(チャージされている電荷の分布)を等高線で示したものであり、等高線の数字が大きいほど、単位面積当たりの電荷の密度(チャージされている電荷の密度)が高いことを示している。また、図35および図36において(b)で示されているのは、(a)の分布をヒストグラム(度数分布)で示したものであり、(b)のヒストグラムの縦軸の数値は(a)の等高線の数値に対応し、(b)のヒストグラムの横軸は半導体ウエハSWの主面の全面積に占める割合(百分率表示)に対応している。なお、図35および図36の(a)の分布は、表面電荷測定装置により測定したものである。

【0097】

図35と図36を比べると分かるように、照明装置36からの光44を半導体ウエハSWに当てることにより、チャージされている電荷の量(密度)を低減することができる。これは、照明装置36からの光44による光電効果によってSi基板領域(半導体基板1に対応するSi基板領域)側から絶縁膜側に電荷(ここでは主として電子)が供給され、絶縁膜に蓄えられていた電荷(主としてホールが蓄えられている)を中和できたためと考えられる。

【0098】

図37は、上記ピット51の発生状況を示す説明図である。図37には、本実施の形態とは異なり、照明装置36からの光44を半導体ウエハSWに当てずに半導体ウエハSWの主面に形成された上記酸化膜102のウェットエッチング工程(上記図32から図33に移行する工程)を行なった場合に、発生した上記ピット51の分布が示されている。図37の半導体ウエハSWの主面において、黒い点で示されているのが、ピット51の発生位置であり、ピット51は半導体ウエハSWの主面において特定の位置に密集して発生しやすいことが、図37から分かる。図37と図35の(a)とを比べると分かるように、図37の半導体ウエハSWの主面においてピット51が密集して発生している領域は、図35の(a)の半導体ウエハSWの主面においてチャージされている電荷の密度が比較的高い領域と、かなり一致している(相関性が高い)。つまり、半導体ウエハSWの主面に形成された酸化膜102に高密度で電荷がチャージされている領域があると、その領域においてピット51が発生しやすいと考えられる。

【0099】

それに対して、本実施の形態では、照明装置36からの光44を半導体ウエハSWに当てながらステップS11(絶縁膜2のウェットエッチング)を行うことにより、半導体ウエハSWの主面の絶縁膜2にチャージされている電荷を光電効果によって中和して電荷密度を低減することができるため、基板領域におけるピット(上記ピット51に相当するもの)の発生を抑制または防止できる。本実施の形態の場合、図37において、ピット51はほぼ発生しなくなる。

【0100】

Siに光電効果を発生させるためには、1.1eV以上のエネルギーを与えればよい。光エネルギーは、次の式1

E=hν=h×c/λ ・・・(式1)

で表される。式1中のEはエネルギー、hはプランク定数、νは振動数、cは光の速さ、λは波長である。式1より、1.1eV以上のエネルギーを与えるには、1127nm以下の波長の光が必要であることが分かる。このため、ステップS11(絶縁膜2のウェットエッチング工程)において半導体ウエハSWに照射する光44は、1127nm以下の波長の光とすればよい。

【0101】

このように、本実施の形態は、ステップS11において、半導体ウエハSW(半導体基板1)に光(具体的には照明装置36からの光44)を当てながら(照射しながら)、絶縁膜2をウェットエッチングすることにより、上記ピット51の発生を抑制または防止している。この際、半導体ウエハSWに照射される光44は、140ルクス以上とすることが好ましい。ここで、140ルクス以上とは、半導体ウエハSWの主面における照度が140ルクス以上であることに対応している。半導体ウエハSWの主面における照度が低いと、光電効果が十分に得られないが、半導体ウエハSWに照射される光44を140ルクス以上とすることにより、光電効果によりSi基板(半導体基板1に対応するSi基板領域)で電荷(ここでは主として電子)を的確に発生させることができ、上記ピット51の発生を的確に防止できるようになる。

【0102】

また、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする(ステップS11を行う)ことがピット51発生抑制には重要であり、ステップS11の前に半導体ウエハSWに光を照射したとしても、絶縁膜2のウェットエッチング(ステップS11)中に半導体ウエハSWに光を当てないのであれば、ピット51発生抑制の効果は十分には得られない。これは、次に理由によるものである。

【0103】

すなわち、絶縁膜2が形成された半導体ウエハSWに光を照射した場合、光電効果を生じさせるには、光が絶縁膜2を通過してSi基板領域に到達する必要があるため、絶縁膜2の厚みが薄くなってきたときに光を照射することが有効である。このため、ステップS11の前に半導体ウエハSWに光を照射したときには、絶縁膜2の厚みが比較的厚いことにより、光電効果は限定的である。しかしながら、本実施の形態のようにステップS11で半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする場合には、光が照射されながらウェットエッチングが進行して絶縁膜2の厚みが薄くなっていくため、半導体ウエハSWのSi基板領域に光が到達しやすくなり、光電効果により電荷(ここでは主として電子)を効率よく発生させることができるようになる。このため、ピット51発生抑制の効果を的確に得ることができる。また、本実施の形態のようにステップS11で半導体ウエハSWの主面に光を当てながら絶縁膜2をウェットエッチングする場合、ウェットエッチングが進行して絶縁膜2の厚みが薄くなっていくと、絶縁膜2にチャージされている電荷密度(体積当たりの電荷密度)が徐々に大きくなっていき、そのときに光電効果による電荷(主として電子)が供給されることで、電子と正孔が結合して消滅しやすくなる。このため、ピット51発生抑制の効果を的確に得ることができる。

【0104】

本実施の形態のステップS11における半導体基板1(半導体ウエハSW)への光44の照射の仕方をまとめると以下のようになる。

【0105】

本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)の主面に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングするが、この際、半導体基板1(半導体ウエハSW)の主面の少なくとも一部に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。これにより、半導体基板1(半導体ウエハSW)の主面の光44が照射された領域において、上記ピット51の発生を抑制または防止することができる。

【0106】

また、本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)を回転させ、回転する半導体基板1(半導体ウエハSW)の主面の少なくとも一部に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。これにより、光44が半導体基板1(半導体ウエハSW)の主面の全体ではなく一部に照射される場合であっても、光44が照射されている領域は、半導体基板1(半導体ウエハSW)の回転に伴い半導体基板1(半導体ウエハSW)の主面内を移動することができ、半導体基板1(半導体ウエハSW)の主面において光44が照射される領域の実効的な面積を大きくすることができる。これにより、半導体基板1(半導体ウエハSW)の主面における、上記ピット51の発生を抑制または防止できる領域を大きくすることができる。

【0107】

また、本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)の主面のいずれの領域も、絶縁膜2をウェットエッチングしている間に光44(好ましくは140ルクス以上の光)が照射されている期間を有するようにすることが好ましい。すなわち、ステップS11において、半導体基板1(半導体ウエハSW)の主面が、絶縁膜2をウェットエッチングしている間に光44(好ましくは140ルクス以上の光)が全く照射されなかった領域を有さないようにすることが好ましい。これにより、半導体基板1(半導体ウエハSW)の主面の全領域において、上記ピット51の発生を抑制または防止できる効果を得られる。

【0108】

このように、本実施の形態では、ピット51の発生を抑制または防止できることで、半導体装置の信頼性を向上することができる。また、半導体装置の製造歩留まりを向上することができる。

【0109】

また、本実施の形態は、素子分離領域4を形成する種々の工程(特にプラズマを使用した工程)で電荷がチャージされやすいことに起因したピット51の発生を抑制または防止できる技術であるが、電荷のチャージに特に影響が大きいのは、素子分離用の溝4aを形成するためのプラズマドライエッチング工程であり、それ以外には、溝4aを埋める絶縁膜6を形成するプラズマCVD工程の影響も大きい。このため、本実施の形態は、素子分離用の溝4aをプラズマドライエッチングにより形成することと、溝4aを埋める絶縁膜6をプラズマCVD法により形成することの、少なくとも一方を満たしている場合に適用すれば、上記ピット51の発生抑制(防止)の効果を得られるが、両方を満たす場合に適用すれば、効果が最も大きい。

【0110】

<ステップS11と他のウェットエッチング工程との関係>

また、本実施の形態では、素子分離領域4形成に伴うピット51の発生を抑制または防止するために、ステップS11の絶縁膜2のウェットエッチング工程で半導体ウエハSWに光44を照射している。しかしながら、ステップS11(絶縁膜2除去工程)よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(エッチングマスクとして機能するフォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにする。これは、レジスト層(フォトレジスト層)は、光が照射されると変質し(例えば硬くなり)、後で除去しにくくなるためである。

【0111】

ステップS11では、半導体基板1(半導体ウエハSW)の主面にレジスト層(フォトレジスト層)を形成していない状態で絶縁膜2をウェットエッチングするため、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングしても、レジスト層自体が無いため、レジスト層(フォトレジスト層)に光が照射されることによる不具合は生じない。一方、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにすることで、レジスト層(フォトレジスト層)に光が照射されることによる不具合を抑制または防止できる。

【0112】

ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにしても、上記ピット51のようなものは発生しにくい。これは、ステップS11で絶縁膜2をウェットエッチングで除去して半導体基板1を露出させた段階で、半導体基板1の主面には素子分離領域4を除いて絶縁膜が形成されていない状態(電荷がチャージされた絶縁膜が無い状態)となり、その後の工程では、素子分離領域4形成時ほど半導体基板1(半導体ウエハSW)主面の絶縁膜に電荷がチャージされないためである。

【0113】

つまり、ステップS11で絶縁膜2を除去する工程は、ピット51が発生しやすい工程でかつレジスト層(フォトレジスト層)が形成されていない状態で行う工程であるため、ピット51の発生抑制(防止)のために、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。一方、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる工程は、ピット51が発生しにくい工程でかつレジスト層が形成された状態で行う工程であるため、レジスト層の変質を抑制するため、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにする。このように、半導体基板1(半導体ウエハSW)の主面上に形成された絶縁膜をウェットエッチングで除去して半導体基板1を露出させるという観点では同じ工程であっても、光を積極的に当てる場合(ステップS11)と当てない場合(ステップS11よりも後の工程でかつレジスト層が形成されている工程)とを使い分け、半導体装置の総合的な信頼性向上や製造歩留まり向上を図ることができる。

【0114】

ここで、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる工程を例示すると、上記ステップS14であり、前記絶縁膜及び前記レジスト層は、絶縁膜11およびフォトレジストパターンPR3にそれぞれ対応している。すなわち、上記ステップS14では、フォトレジストパターンPR3で覆われない領域(ここでは低耐圧MIS領域1B)の絶縁膜11がウェットエッチングによって除去されて半導体基板1の上面(すなわちSi面)が露出されるが、この際のウェットエッチングは、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないように行うのである。これは、ステップS14の絶縁膜11のウェットエッチングにおいては、半導体基板1(半導体ウエハSW)の主面における照度が100ルクス未満となるようにする、つまり、半導体基板1の主面が100ルクス以上の照度となる領域を有さないようにすることに対応している。これにより、絶縁膜11をウェットエッチングする際のフォトレジストパターンPR3の光による変質(例えば硬化)を抑制して、その後にフォトレジストパターンPR3を除去しやすくすることができ、フォトレジストパターンPR3の除去残りの発生を抑制または防止することができる。これにより、半導体装置の信頼性を向上することができる。また、半導体装置の製造歩留まりを向上することができる。また、ステップS14でウェットエッチングされる直前の絶縁膜11にチャージされている電荷は、ステップS11でウェットエッチングされる直前の絶縁膜2にチャージされている電荷よりもかなり少ないため、ステップS14で絶縁膜11をウェットエッチングする際に半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにしても、ピット51に相当するものの発生を抑制または防止することができる。

【0115】

また、上記のことを別の観点で見ると、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面の照度が、ステップS11における半導体基板1(半導体ウエハSW)の主面の照度よりも低くなるようにする。具体的には、上記ステップS14で絶縁膜11をウェットエッチングしているときの半導体基板1(半導体ウエハSW)の主面の照度を、上記ステップS11で絶縁膜2をウェットエッチングしているときの半導体基板1(半導体ウエハSW)の主面の照度よりも低くするのである。これにより、上記ピット51に相当するものの発生を抑制または防止できるという効果を得られるとともに、レジスト層の除去残りの発生を抑制または防止できるという効果を得られる。そして、ステップS11における半導体基板1(半導体ウエハSW)の主面の照度は140ルクス以上が好ましく、ステップS11工程の後において、半導体基板1の主面に絶縁膜と該絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には(具体的にはステップS14では)、半導体基板1(半導体ウエハSW)の主面の照度は100ルクス以下が好ましい。これにより、上記ピット51に相当するものの発生を抑制または防止できるという効果と、レジスト層の除去残りの発生を抑制または防止できるという効果とを更に向上させ、半導体装置の信頼性や製造歩留まりを、より的確に向上することが可能になる。

【0116】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0117】

本発明は、半導体装置の製造技術に適用して有効である。

【符号の説明】

【0118】

1 半導体基板

1A 高耐圧MIS領域

1B 低高耐圧MIS領域

2 絶縁膜

3 絶縁膜

4 素子分離領域

4a 溝

5 絶縁膜

6 絶縁膜

11 絶縁膜

12 絶縁膜

13 導電体膜

22 絶縁膜

23 コンタクトホール

24 プラグ

25 絶縁膜

31 半導体製造装置

32 搬送室

33 エッチング用チャンバ

34 ロードポート

35 搬送用ロボット

36 照明装置

41 回転ステージ

42 ノズル

43 エッチング液

51 ピット

102 酸化膜

104a 溝

105 絶縁膜

106 絶縁膜

EX エクステンション領域

GE,GE1,GE2 ゲート電極

M1 配線

PR1,PR2,PR3,PR4 フォトレジストパターン

Q1,Q2 MISFET

SD ソース・ドレイン領域

SP サイドウォールスペーサ

SW 半導体ウエハ

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、素子分離領域を形成する工程を含む半導体装置の製造方法に適用して有効な技術に関する。

【背景技術】

【0002】

半導体基板に溝を形成し、この溝に絶縁膜を埋め込むことで、素子分離領域が形成される。この素子分離領域で規定された活性領域に種々の半導体素子が形成されることにより、半導体装置が製造される。各活性領域同士は、素子分離領域によって電気的に分離することができる。

【0003】

特開2006−173260号公報(特許文献1)には、ウェットエッチング処理を行う前に半導体基板を除電する処理を行う技術が記載されている。

【0004】

特開2008−113028号公報(特許文献2)には、水素の標準電極電位よりも正電位である物質をシリコン表面に局所的に付着させ、前記シリコンに対する光を遮断して当該シリコンに生成される電子正孔対を抑制しつつ、当該シリコン表面のうち前記物質が付着する部分でHFと当該シリコンを酸化反応させて電子e−を生成し、当該電子e−を水素イオンH+と反応させる技術が記載されている。

【0005】

特開2009−49293号公報(特許文献3)に記載の技術は、基板12の上に第1の絶縁膜11を形成する工程(a)と、第1の絶縁膜11をウェットエッチングにより選択的に除去する工程(c)と、基板12における第1の絶縁膜11が除去された領域の上に第2の絶縁膜17を形成する工程(d)とを備えている。そして、工程(c)では、少なくともウェットエッチングを開始してから薬液が基板と接液するまでの期間において基板12の表面に可視光又は赤外光からなる照明光を照射している(ここで記載されている符号は特許文献3における符号に対応している)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−173260号公報

【特許文献2】特開2008−113028号公報

【特許文献3】特開2009−49293号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者の検討によれば、次のことが分かった。

【0008】

素子分離領域の形成工程について検討したところ、素子分離領域形成後に半導体基板にピット(窪み、穴)が発生しやすいことが分かった。

【0009】

素子分離領域を形成するには、まず、半導体基板の主面に酸化膜を形成してから、その酸化膜上に窒化シリコン膜を形成し、窒化シリコン膜、酸化膜および半導体基板に素子分離用の溝を形成する。それから、この溝を埋めるように酸化シリコン膜を形成してから、CMP処理により溝の外部の酸化シリコン膜を除去し、溝内に酸化シリコン膜を残す。そして、窒化シリコン膜を除去する。このようにして、溝に埋め込まれた酸化シリコン膜からなる素子分離領域が形成される。その後、半導体基板の主面の酸化膜をウェットエッチングで除去して半導体基板を露出させる。このような素子分離領域形成工程において、半導体基板の主面の酸化膜をウェットエッチングで除去して半導体基板を露出させたときに、半導体基板にピットが発生しやすいことが分かった。

【0010】

半導体基板にピットが発生した場合、そのピットを含む半導体チップ領域(半導体ウエハにおいて後で個々の半導体チップが取得される各領域を半導体チップ領域と称する)から取得された半導体チップ(半導体装置)の信頼性を低下させる虞がある。また、ピットを含む半導体チップ領域から取得された半導体チップを選別して除去する場合は、半導体装置の製造歩留まりを低下させ、コスト上昇の原因となる。

【0011】

本発明の目的は、半導体装置の信頼性を向上させることができる技術を提供することにある。

【0012】

また、本発明の目的は、半導体装置の製造歩留まりを向上させることができる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板の主面に第1絶縁膜を形成する工程、(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程を有している。更に、(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程を有している。そして、前記(f)工程では、前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングする。

【0016】

また、他の代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板の主面に第1絶縁膜を形成する工程、(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程を有している。更に、(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程を有している。そして、前記(f)工程では、前記半導体基板の主面に光を当てながら前記第1絶縁膜をウェットエッチングし、前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面の照度が、前記(f)工程における前記半導体基板の主面の照度よりも低くなるようにする。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

代表的な実施の形態によれば、半導体装置の信頼性を向上させることができる。

【0019】

また、半導体装置の製造コストを低減させることができる。

【図面の簡単な説明】

【0020】

【図1】本発明の一実施の形態である半導体装置の製造工程の一部を示す製造プロセスフロー図である。

【図2】本発明の一実施の形態である半導体装置の製造工程の一部を示す製造プロセスフロー図である。

【図3】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の要部断面図である。

【図13】図12に続く半導体装置の製造工程中の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の要部断面図である。

【図18】図17に続く半導体装置の製造工程中の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の要部断面図である。

【図20】図19に続く半導体装置の製造工程中の要部断面図である。

【図21】図20に続く半導体装置の製造工程中の要部断面図である。

【図22】図21に続く半導体装置の製造工程中の要部断面図である。

【図23】図22に続く半導体装置の製造工程中の要部断面図である。

【図24】図23に続く半導体装置の製造工程中の要部断面図である。

【図25】図24に続く半導体装置の製造工程中の要部断面図である。

【図26】図25に続く半導体装置の製造工程中の要部断面図である。

【図27】図26に続く半導体装置の製造工程中の要部断面図である。

【図28】図27に続く半導体装置の製造工程中の要部断面図である。

【図29】図28に続く半導体装置の製造工程中の要部断面図である。

【図30】ステップS11の絶縁膜の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)の説明図である。

【図31】ステップS11の絶縁膜の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)の説明図である。

【図32】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図33】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図34】半導体基板の主面の酸化膜をウェットエッチングで除去したときに発生する欠陥の説明図である。

【図35】半導体ウエハの主面の電荷分布の説明図である。

【図36】半導体ウエハの主面の電荷分布の説明図である。

【図37】ピットの発生状況を示す説明図である。

【発明を実施するための形態】

【0021】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0022】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0023】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0024】

<半導体装置の製造工程>

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図1は、本発明の一実施の形態である半導体装置、例えばMISFET(Metal Insulator Semiconductor Field Effect Transistor)を有する半導体装置の製造工程の一部を示す製造プロセスフロー図である。図3〜図29は、本発明の一実施の形態である半導体装置、例えばMISFETを有する半導体装置の製造工程中の要部断面図である。

【0025】

まず、図3に示されるように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する(図1のステップS1)。次に、図4に示されるように、半導体基板1を酸化(好ましくは熱酸化)して半導体基板1の表面(主面)に絶縁膜(酸化膜)2を形成する(図1のステップS2)。次に、図5に示されるように、半導体基板1の主面(主面全面)上に、すなわち絶縁膜2上に、CVD(Chemical Vapor Deposition:化学気相成長)法(例えば熱CVD法)などにより、絶縁膜3を形成(堆積)する(図1のステップS3)。絶縁膜2は、好ましくは酸化シリコン膜からなり、絶縁膜3は好ましくは窒化シリコン膜からなる。絶縁膜2の厚みは、例えば5〜20nm程度とすることができ、絶縁膜3の厚みは、例えば100〜500nm程度とすることができる。

【0026】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜3上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図6に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR1を形成する。フォトレジストパターンPR1は、後述の溝4a形成予定領域に開口部を有している。

【0027】

次に、フォトレジストパターンPR1をエッチングマスクとして用いて、絶縁膜3、絶縁膜2および半導体基板1を順次ドライエッチング(プラズマドライエッチング)することにより、図7に示されるように、溝(素子分離用の溝)4aを形成する(図1のステップS4)。このステップS4では、プラズマドライエッチングによって溝4aを形成する。溝4aは、絶縁膜3、絶縁膜2および半導体基板1にかけて形成されている。すなわち、溝4aは、絶縁膜3および絶縁膜2を貫通し、溝4aの底部が半導体基板1の厚みの途中に位置するように形成されている。半導体基板1における溝4aの深さ(半導体基板1の表面から溝4aの底面までの深さ)は、例えば300〜700nm程度である。溝4aは、素子分離用の溝であり、すなわち後述する素子分離領域4を形成するための溝である。溝4aの形成後、フォトレジストパターンPR1は除去する。図7には、フォトレジストパターンPR1を除去した段階(状態)が示されている。

【0028】

ここで、プラズマドライエッチングとは、プラズマを利用したドライエッチングのことである。プラズマドライエッチングには、主にラジカルによってエッチングが進行する場合と、主にイオンによってエッチングが進行する場合と、ラジカルとイオンの両方によってエッチングが進行する場合とが含まれる。このため、主にラジカルよってエッチングが進行するプラズマエッチングだけでなく、主にイオンによってエッチングが進行する反応性イオンエッチング(Reactive Ion Etching:RIE)も、プラズマドライエッチングに含むものとする。

【0029】

次に、図8に示されるように、溝4aの内部(すなわち溝4aの底面および側壁)と絶縁膜3の表面とを酸化(好ましくは熱酸化)して絶縁膜5を形成する(図1のステップS5)。絶縁膜5は、酸化膜であり、溝4aの内部(すなわち溝4aの底面および側壁上)と絶縁膜3の表面上とに形成されるが、絶縁膜5のうち、溝4aの底面および側壁で露出する半導体基板1の露出面に形成された部分は、酸化シリコン膜からなり、絶縁膜3の表面に形成された部分は、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜5の厚みは、例えば5〜20nm程度とすることができる。

【0030】

次に、図9に示されるように、半導体基板1の主面(主面全面)上に、すなわち絶縁膜5上に、溝4a内を埋めるように、絶縁膜6を形成(堆積)する(図1のステップS6)。絶縁膜6は、好ましくは酸化シリコン膜からなる。絶縁膜6は、好ましくはプラズマCVDにより形成し、特に好ましくはHDP(High Density Plasma:高密度プラズマ)−CVD法により形成する。絶縁膜6は、溝4a内を埋めることができるような厚みに形成する。溝4aの深さにもよるが、絶縁膜6の厚みは500〜1000nm程度とすることができる。プラズマCVD法(特にHDP−CVD法)により絶縁膜6を成膜した場合、絶縁膜5は、絶縁膜6を堆積する際の半導体基板1へのダメージを防止する作用を備えている。絶縁膜6の形成後、スクラバ洗浄(例えば純水を使用したスクラバ洗浄)のような洗浄処理が行われる。

【0031】

次に、溝4aに埋め込んだ絶縁膜6を焼き締めるための熱処理(アニール処理)を行う。この熱処理は、半導体基板1を例えば400〜1200℃程度で熱処理することにより、行うことができる。

【0032】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜6上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図10に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR2を形成する。フォトレジストパターンPR2は、平面視で、溝4aを覆い(すなわち溝4aと重なり)、かつ溝4aが形成されていない領域を露出するようなパターン形状を有している。

【0033】

次に、フォトレジストパターンPR2をエッチングマスクとして用いて、絶縁膜6をドライエッチング(プラズマドライエッチング)することにより、フォトレジストパターンPR2から露出する部分の絶縁膜6(すなわち平面視で溝4aに重ならない領域の絶縁膜6)をエッチバックして厚みを薄くする(図1のステップS7)。このステップS7は、プラズマドライエッチングを用いることが好ましい。その後、フォトレジストパターンPR2をアッシング(プラズマアッシング)などにより除去し、更に、洗浄処理(例えば純水を使用した洗浄処理)が行われる。図11には、フォトレジストパターンPR2を除去した段階(状態)が示されている。ステップS7は、後で行うステップS8のCMP処理におけるディッシングなどを抑制または防止するために行われるが、それが気にならない場合は、ステップS7を省略することもできる。

【0034】

次に、絶縁膜6をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨する(図1のステップS8)。これにより、図12に示されるように、溝4aの外部の絶縁膜6が除去され、溝4a内に絶縁膜6が残される。また、このCMP処理の際に、絶縁膜3上の絶縁膜5も除去され、絶縁膜3の上面が露出される。また、ステップS8のCMP処理は、絶縁膜6,5(酸化シリコン膜)の研磨速度に比べて、絶縁膜3(窒化シリコン膜)の研磨速度が小さくなるような条件で行われるため、絶縁膜3はCMP処理のストッパ膜(または保護膜)として機能することができる。

【0035】

次に、図13に示されるように、溝4a内の絶縁膜6の上部(上面)をドライエッチング(プラズマドライエッチング)によってエッチバックすることにより、溝4a内の絶縁膜6の上面を後退させる(図1のステップS9)。このステップS9は、プラズマドライエッチングを用いることが好ましいが、絶縁膜6(酸化シリコン膜)のエッチング速度に比べて絶縁膜3(窒化シリコン膜)のエッチング速度が小さくなるようなエッチング条件で行われる。このため、ステップS9の前(かつステップS8の後)には、溝4a内の絶縁膜6の上面の高さ位置は、絶縁膜3の上面の高さ位置とほぼ同じであったものが、ステップS9の後(かつ後述のステップS10の前)には、溝4a内の絶縁膜6の上面の高さ位置は、絶縁膜3の上面の高さ位置よりも低くなる。但し、溝4a内の絶縁膜6の上面の高さ位置が、半導体基板1と絶縁膜2との界面の高さ位置よりも低くなる前に、ステップS9のドライエッチング(プラズマドライエッチング)を終了することが好ましい。図13には、溝4a内の絶縁膜6の上面の高さ位置が、絶縁膜2の上面の高さ位置と絶縁膜3の上面の高さ位置との間に位置する場合が示されている。

【0036】

次に、図14に示されるように、熱リン酸などの薬液(エッチング液)を用いたウェットエッチングにより絶縁膜3を除去する(図1のステップS10)。この際のウェットエッチングは、絶縁膜3(窒化シリコン膜)のエッチング速度に比べて絶縁膜6,5,2(酸化シリコン膜)のエッチング速度が小さくなるようなエッチング条件で行われる。このため、ステップS10では、絶縁膜3が選択的に除去されて、絶縁膜2の上面が露出される。

【0037】

次に、図15に示されるように、フッ酸などの薬液(エッチング液)を用いたウェットエッチングにより、絶縁膜2を除去する(図1のステップS11)。絶縁膜2を除去したことにより、半導体基板1の上面(表面、Si面)が露出される。すなわち、ステップS11では、絶縁膜2をウェットエッチングして除去することにより、半導体基板1のSi面が露出される。また、ステップS11のウェットエッチングは、絶縁膜2が除去されて半導体基板1の上面が露出される程度だけ行うため、溝4aの内部の絶縁膜6,5は、ほとんどエッチングされずに残存する。溝4aの内部に残存する絶縁膜5および絶縁膜6により、素子分離領域(素子分離)4が形成される。

【0038】

ステップS11を行う直前の段階で溝4aの内部に残存する絶縁膜5および絶縁膜6を素子分離領域4とみなすこともできるが、この場合、ステップS11直前における素子分離領域4の上面がステップS11でわずかにエッチングされたものが、ステップS11後の素子分離領域4となる。

【0039】

また、ステップS11では、半導体基板1の主面上(すなわち絶縁膜2上)にレジスト層(フォトレジスト層)が形成されていない状態で絶縁膜2をウェットエッチングするため、半導体基板1の主面全面で絶縁膜2がエッチングされて除去される。このため、ステップS11を行うと、素子分離領域4が形成されている領域以外の領域(すなわち活性領域)の半導体基板1の表面(Si面)が露出された状態となる。このステップS11の絶縁膜2の除去工程(ウェットエッチング工程)については、後でより詳細に説明する。

【0040】

このようにして、半導体基板1の溝4a内に埋め込まれた絶縁膜5,6からなる素子分離領域4が形成される。絶縁膜6に比べて絶縁膜5は薄いため、素子分離領域4は、主として溝4a内に埋め込まれた絶縁膜6により形成される。このように、素子分離領域4は、STI(Shallow Trench Isolation)法により形成される。素子分離領域4を形成したことで、半導体基板1においては、素子分離領域4によって活性領域が規定(画定)され、その活性領域に、以降の工程で種々の半導体素子(例えば後述するMISFETQ1,Q2など)が形成される。

【0041】

次に、図16に示されるように、半導体基板1の主面から所定の深さに渡ってウエル領域を形成する(図2のステップS12)。本実施の形態では、MISFETとしてnチャネル型のMISFETを形成する場合について説明するため、ここでは、ウエル領域としてp型ウエル(p型のウエル領域)PWを形成する。p型ウエルPWは、半導体基板1に対してホウ素(B)などのp型の不純物をイオン注入することによって形成することができる。pチャネル型のMISFETを形成する場合は、半導体基板1に対してリン(P)またはヒ素(As)などのn型の不純物をイオン注入することによって、n型のウエル領域(n型ウエル)を形成する。

【0042】

次に、図17に示されるように、半導体基板1の表面(すなわちp型ウエルPWの表面)上に、MISFETのゲート絶縁膜用の絶縁膜11を形成する(図2のステップS13)。絶縁膜11は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0043】

次に、半導体基板1の主面(主面全面)上に、すなわち絶縁膜11上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、図18に示されるように、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR3を形成する。

【0044】

次に、図19に示されるように、フォトレジストパターンPR3をエッチングマスクとして用いて、絶縁膜11をエッチングしてフォトレジストパターンPR3から露出する部分の絶縁膜11を選択的に除去する(図2のステップS14)。この際、フォトレジストパターンPR3に覆われた部分の絶縁膜11は除去されずに残存する。ステップS14のエッチングには、薬液(エッチング液)としてフッ酸などを用いたウェットエッチングを採用することができる。絶縁膜11が除去された領域では、半導体基板1の上面(表面、Si面)が露出する。

【0045】

ここで、高耐圧のMISFETが形成される予定領域(以下、高耐圧MIS領域1Aと称す)では、絶縁膜11が残され、一方、低耐圧のMISFETが形成される予定領域(以下、低耐圧MIS領域1Bと称す)では、絶縁膜11が除去されて半導体基板1の上面(すなわちSi面)が露出される。つまり、フォトレジストパターンPR3は、平面視で、高耐圧MIS領域1Aを覆い、かつ低耐圧MIS領域1Bを露出するようなパターン形状を有している。また、フォトレジストパターンPR3を用いた絶縁膜11のウェットエッチング(すなわちステップS14)を行う前に、アッシャーを用いたプラズマ処理などによりフォトレジストパターンPR3に対して表面処理(プラズマ表面処理)を行い、それによってウェットエッチング時の濡れ性向上(フォトレジストパターンPR3に対する濡れ性向上)を図ることもできる。

【0046】

次に、図20に示されるように、フォトレジストパターンPR3を除去する。フォトレジストパターンPR3の除去には、ウェット処理による除去を用い、例えばSPM(Sulfuric acid-Hydrogen Peroxide Mixture)液を用いたSPM洗浄を用いることができる。

【0047】

次に、上記ステップS14のウェットエッチング工程(フォトレジストパターンPR3をエッチングマスクとして絶縁膜11をウェットエッチングする工程)で絶縁膜11が除去された領域(すなわち低耐圧MIS領域1B)における半導体基板1の表面(すなわちp型ウエルPWの表面)上に、図21に示されるように、酸化(例えば熱酸化)によりMISFETのゲート絶縁膜用の絶縁膜12を形成する(図2のステップS15)。絶縁膜12は、例えば薄い酸化シリコン膜などからなる。絶縁膜12を形成する際に、絶縁膜11の厚みが厚くなる場合もあり得る。

【0048】

ステップS15で絶縁膜12を形成した段階(すなわち図21の段階)で絶縁膜12の厚みが絶縁膜11の厚みよりも薄くなるように、絶縁膜11と絶縁膜12との各形成時の厚みを制御する必要がある。このためには、ステップS13で絶縁膜11を形成した段階(図17の段階)の絶縁膜11の厚みを、ステップS15で絶縁膜12を形成した段階(図21の段階)の絶縁膜12の厚みよりも厚くすればよいが、絶縁膜12を(好ましくは熱酸化により)形成する際に絶縁膜11の厚みが厚くなる場合もあり得る。

【0049】

このようにして、図21に示されるように、低耐圧MIS領域1Bの半導体基板1(p型ウエルPW)の表面に絶縁膜12が形成され、高耐圧MIS領域1Aの半導体基板1(p型ウエルPW)の表面に絶縁膜12よりも厚い絶縁膜11が形成された状態が得られる。

【0050】

次に、図22に示されるように、半導体基板1の主面(主面全面)上に、ゲート電極用の導電体膜13を形成する(図2のステップS16)。導電体膜13は、例えば多結晶シリコン膜(ドープトポリシリコン膜)とすることができる。それから、半導体基板1の主面(主面全面)上に、すなわち導電体膜13上に、フォトレジスト層を塗布してからこのフォトレジスト層を露光、現像することで、フォトレジストパターン(レジストパターン、レジスト層、マスク層)PR4を形成する。それから、フォトレジストパターンPR4をエッチングマスクとしたドライエッチング(プラズマドライエッチング)により導電体膜13をエッチングしてパターニングし、図23に示されるように、パターニングされた導電体膜13からなるゲート電極GEを形成する(図2のステップS17)。ゲート電極GEのうち、高耐圧のMISFET用のゲート電極GE1は、半導体基板1(p型ウエルPW)上に絶縁膜11を介して形成され、低耐圧のMISFET用のゲート電極GE2は、半導体基板1(p型ウエルPW)上に絶縁膜12を介して形成される。その後、フォトレジストパターンPR4は除去される。図23には、フォトレジストパターンPR4を除去した段階(状態)が示されている。ゲート電極GE1の下に絶縁膜11が残存し、ゲート電極GE2の下に絶縁膜12が残存するが、ゲート電極GE1,GE2で覆われない領域の絶縁膜11,12が層状に残存する場合もあり得る。

【0051】

次に、図24に示されるように、p型ウエルPWのゲート電極GEの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、n型のエクステンション領域(n−型半導体領域)EXを形成する(図2のステップS18)。エクステンション領域EXは、n型の半導体領域である。このイオン注入の際に、ゲート電極GEはイオン注入阻止マスクとして機能することができるため、p型ウエルPWにおけるゲート電極GEの直下の領域には、不純物はイオン注入されず、エクステンション領域EXは、ゲート電極GEの側壁に整合(自己整合)して形成される。

【0052】

次に、図25に示されるように、ゲート電極GEの側壁上に、側壁絶縁膜(絶縁膜)として、例えば酸化シリコンまたは窒化シリコンあるいはそれら絶縁膜の積層膜などからなるサイドウォールスペーサ(側壁スペーサ、側壁絶縁膜、サイドウォール)SPを形成する(図2のステップS19)。サイドウォールスペーサSPは、例えば、半導体基板1の主面(主面全面)上に酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜を堆積し、この酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0053】

サイドウォールスペーサSPの形成後、図26に示されるように、p型ウエルPWのゲート電極GEおよびサイドウォールスペーサSPの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、n型のソース・ドレイン領域(n+型半導体領域)SDを形成する(図2のステップS20)。ソース・ドレイン領域SDは、n型の半導体領域である。このイオン注入の際に、ゲート電極GEおよびその側壁上のサイドウォールスペーサSPはイオン注入阻止マスクとして機能することができるため、p型ウエルPWにおけるゲート電極GEの直下の領域とそのゲート電極GEの側壁上のサイドウォールスペーサSPの直下の領域とには、不純物は導入(イオン注入)されない。このため、ソース・ドレイン領域SDは、ゲート電極GEの側壁上のサイドウォールスペーサSPの側面(ゲート電極GEに接している側とは反対側の面)に整合(自己整合)して形成される。

【0054】

ソース・ドレイン領域SD形成用のイオン注入の後、導入した不純物の活性化のためのアニール処理を行う(図2のステップS21)。このアニール処理は、例えば、1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0055】

同じMISFET(同じゲート電極GEに対して)に対して形成されているエクステンション領域EXとソース・ドレイン領域SDとの対により、nチャネル型MISFETのLDD(Lightly doped Drain)構造のソースまたはドレインとして機能するn型の半導体領域が形成される。同じMISFET(同じゲート電極GE)に対して形成されているエクステンション領域EXとソース・ドレイン領域SDとの関係は、ソース・ドレイン領域SDとチャネル領域(ゲート電極GEの直下の領域)との間にエクステンション領域EXが介在し、ソース・ドレイン領域SDはエクステンション領域EXよりも、不純物濃度が高くかつ深さ(接合深さ)が深くなっている。

【0056】

このようにして、図26に示されるように、p型ウエルPWに、電界効果トランジスタとしてnチャネル型のMISFET(Metal Insulator Semiconductor Field Effect Transistor)Qn1,Q2が形成される。ゲート電極GE1をそのゲート電極とするMISFETQ1は、ゲート電極GE1の下に位置する絶縁膜11がゲート絶縁膜として機能し、ゲート電極GE2をそのゲート電極とするMISFETQ2は、ゲート電極GE2の下に位置する絶縁膜12がゲート絶縁膜として機能する。このため、MISFETQ1のゲート絶縁膜(ここでは絶縁膜11)の厚みは、MISFETQ2のゲート絶縁膜(ここでは絶縁膜12)の厚みよりも厚く、MISFETQ1の耐圧はMISFETQ2の耐圧より高くなっている。このため、MISFETQ1の動作電圧を、MISFETQ2の動作電圧よりも高くすることができる。MISFETQ1は高耐圧MIS領域1Aに形成され、MISFETQ2は低耐圧MIS領域1Bに形成される。

【0057】

なお、MISFETとしてnチャネル型MISFETを形成する場合について説明したが、nチャネル型MISFETの代わりにpチャネル型MISFETを形成することもでき、この場合、p型ウエルPW、エクステンション領域EXおよびソース・ドレイン領域SDの各導電型を逆にすればよい(すなわちp型ウエルPWをn型ウエルとし、エクステンション領域EXをp型とし、ソース・ドレイン領域SDをp型とすればよい)。また、nチャネル型MISFETとpチャネル型MISFETの両方を形成することもできる。

【0058】

また、図26において、高耐圧MIS領域1Aと低耐圧MIS領域1Bとの間(MISFETQ1が形成されている領域とMISFETQ2が形成されている領域との間)に素子分離領域4を設ける(配置する)こともできる。

【0059】

次に、サリサイド(Salicide:Self Aligned Silicide)技術により、ゲート電極GEおよびソース・ドレイン領域SDの表面(表層部分、上層部分)に、コバルトシリサイドまたはニッケルシリサイドなどからなる低抵抗の金属シリサイド層(図示せず)を形成することもできる。この金属シリサイド層は、ゲート電極GEおよびソース・ドレイン領域SDを覆うように例えばコバルト(Co)膜またはニッケル(Ni)膜などの金属膜を堆積して熱処理することにより、形成することができ、その後、未反応の金属膜は除去される。

【0060】

次に、図27に示されるように、半導体基板1の主面(主面全面)上に絶縁膜(層間絶縁膜)22を形成する。すなわち、ゲート電極GEおよびサイドウォールスペーサSPを覆うように、半導体基板1の主面上に絶縁膜22を形成する。絶縁膜22は、例えば、酸化シリコン膜の単体膜や、あるいは、窒化シリコン膜とそれよりも厚い酸化シリコン膜との積層膜などからなる。その後、絶縁膜22の表面(上面)をCMP法により研磨するなどして、絶縁膜22の上面を平坦化する。下地段差に起因して絶縁膜22の表面に凹凸形状が形成されていても、絶縁膜22の表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜を得ることができる。

【0061】

次に、絶縁膜22上に形成したフォトレジストパターン(図示せず)をエッチングマスクとして用いて、絶縁膜22をドライエッチングすることにより、図28に示されるように、絶縁膜22にコンタクトホール(貫通孔、孔)23を形成する。コンタクトホール23の底部では、半導体基板1の主面の一部、例えばソース・ドレイン領域SDの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)の一部や、ゲート電極GEの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)の一部などが露出される。

【0062】

次に、コンタクトホール23内に、タングステン(W)などからなる導電性のプラグ(接続用導体部)24を形成する。プラグ24を形成するには、例えば、コンタクトホール23の内部(底部および側壁上)を含む絶縁膜22上に、プラズマCVD法などによりバリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール23を埋めるように形成し、絶縁膜22上の不要な主導体膜およびバリア導体膜をCMP法またはエッチバック法などによって除去することにより、プラグ24を形成することができる。図面の簡略化のために、プラグ24は、主導体膜とバリア導体膜を一体化して示してある。プラグ24は、その底部で、ゲート電極GEまたはソース・ドレイン領域SDの表面(この表面に金属シリサイド層を形成している場合はその金属シリサイド層)などと接して、電気的に接続される。

【0063】

次に、図29に示されるように、プラグ24が埋め込まれた絶縁膜22上に、絶縁膜25を形成する。絶縁膜25は、複数の絶縁膜の積層膜で形成することもできる。

【0064】

次に、シングルダマシン法により第1層目の配線である配線M1を形成する。具体的には、次のようにして配線M1を形成することができる。まず、フォトレジストパターン(図示せず)をマスクとしたドライエッチング(プラズマドライエッチング)によって絶縁膜25の所定の領域に配線溝を形成した後、配線溝の底部および側壁上を含む絶縁膜25上にバリア導体膜(例えば窒化チタン膜、タンタル膜または窒化タンタル膜など)を形成する。続いて、CVD法またはスパッタリング法などによりバリア導体膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成して、銅めっき膜により配線溝の内部を埋め込む。それから、配線溝以外の領域の主導体膜(銅めっき膜およびシード層)とバリア導体膜をCMP法により除去して、配線溝に埋め込まれ銅を主導電材料とする第1層目の配線M1を形成する。図面の簡略化のために、配線M1は、バリア導体膜、シード層および銅めっき膜を一体化して示してある。

【0065】

配線M1は、プラグ24を介してゲート電極GEまたはソース・ドレイン領域SDなどと電気的に接続されている。その後、デュアルダマシン法により2層目の配線を形成するが、ここでは図示およびその説明は省略する。

【0066】

<ステップS11の絶縁膜2の除去工程について>

次に、上記ステップS11の絶縁膜2の除去工程(ウェットエッチング工程)について、より詳細に説明する。

【0067】

図30および図31は、ステップS11の絶縁膜2の除去工程(ウェットエッチング工程)で用いた半導体製造装置(エッチング装置)31の説明図である。図30は、半導体製造装置31全体を模式的に示す平面図に対応し、図31は、半導体製造装置31における個々のエッチング用チャンバ33を模式的に示す断面図に対応している。

【0068】

図30の半導体製造装置31を用いてステップS11で絶縁膜2を除去する手順について、まず説明する。

【0069】

図30に示されるように、半導体製造装置31は、搬送室32、と搬送室32の周囲に配置された複数のエッチング用チャンバ33およびロードポート(ロードポート室)34とを有しており、いわゆるマルチチャンバタイプの半導体製造装置である。搬送室32とエッチング用チャンバ33との間と、搬送室32とロードポート(ロードポート室)34との間とは、開閉手段であるゲートバルブ(図示せず)などを介して連結されている。

【0070】

まず、フープ(図示せず)をロードポート(ロードポート室)34にドッキングした後、フープから半導体ウエハSWを取り出し、搬送室32に搬入する。半導体ウエハSWは、上記半導体基板1に対応するものである(すなわち半導体ウエハSWを上記半導体基板1とみなすことができる)。フープは半導体ウエハのバッチ搬送用の密閉収納容器であり、通常25枚、12枚、6枚等のバッチ単位で半導体ウエハを収納する。

【0071】

それから、搬送用ロボット35などによって半導体ウエハSWを、搬送室32を経てエッチング用チャンバ33内へ搬送する。そして、エッチング用チャンバ33内で、半導体ウエハSWから上記絶縁膜2を除去(ウェットエッチング)する処理(すなわち上記ステップS11の処理)を行う。

【0072】

本実施の形態では、半導体ウエハSWに光を当てる(光を照射する)ための光源として、照明装置(光源)36がエッチング用チャンバ33内に配置されている。照明装置36は、例えば蛍光灯などを用いることができる。照明装置36からの光を半導体ウエハSWに光を当てながら、半導体ウエハSWから上記絶縁膜2を除去(ウェットエッチング)する処理が行われる。

【0073】

エッチング用チャンバ33内で上記絶縁膜2を除去(ウェットエッチング)する処理が行われた後、半導体ウエハSWは搬送用ロボット35などによってエッチング用チャンバ33から搬送室32を経てロードポート(ロードポート室)34に搬送され、フープへ戻される。その後、半導体ウエハSWは、次の工程を行うための半導体製造装置に送られる。

【0074】

次に、ステップS11において、エッチング用チャンバ(エッチング装置)33内で行われる絶縁膜2の除去処理(ウェットエッチング処理)について、図31を参照しながら具体的に説明する。

【0075】

図31に示されるように、エッチング用チャンバ33内には、回転ステージ(ウエハ回転ステージ、スピンベース)41が配置されている。この回転ステージ41は、図示しない回転機構(例えばモータなど)によって高速で回転可能に構成された回転板であり、例えば半導体ウエハSWよりも大きな径を有している。エッチング用チャンバ33内に搬入された半導体ウエハSWは、この回転ステージ41上に載置(配置)され、図示しないチャック機構などによって回転ステージ41に保持される。この際、半導体ウエハSWは、絶縁膜2が形成された側の面である主面(表面、半導体素子形成側の主面)が上方を向き、主面とは反対側の面である裏面が下方(回転ステージ41に対向する側)を向くように、回転ステージ41上に配置されて固定される。図示しない回転機構によって回転ステージ41を回転させることで、回転ステージ41に保持された半導体ウエハSWも回転させることができる。

【0076】

回転ステージ41の上方に(例えば回転ステージ41に固定された半導体ウエハSWの主面の中央部上方に)ノズル42が配置され、このノズル42からエッチング液(洗浄液、エッチャント液、薬液)43を半導体ウエハSWの主面に向かって吐出(噴出、供給)し、半導体ウエハSWの主面にエッチング液43を供給できるように構成されている。エッチング液43は、半導体ウエハSWの主面に形成されている上記絶縁膜2をエッチング可能なエッチング液を用い、フッ酸(HF)の水溶液を好適に用いることができる。

【0077】

エッチング液43のフッ酸の濃度は、生産性に支障をきたさない範囲のエッチング時間で目的とするエッチング量を確保できるようにすればよく、例えば、5wt.%(5重量%以下程度の濃度とすることができる。

【0078】

半導体ウエハSWの主面に形成されている上記絶縁膜2を除去するには、絶縁膜2が形成されている半導体ウエハSWを、エッチング用チャンバ33内の回転ステージ41上に配置して固定してから(このとき、半導体ウエハSWにおいて、上記絶縁膜2が形成されている側の主面がノズル42側を向く)、回転ステージ41を回転させることによって、回転ステージ41に保持された半導体ウエハSWを回転させる。この際、回転ステージ41の回転の中心と半導体ウエハSWの主面の中心位置とをほぼ一致させることで、半導体ウエハSWの主面の中心位置を回転中心にして回転することが好ましい。

【0079】

半導体ウエハSWが回転した状態で、回転する半導体ウエハSWの主面に対して、ノズル42から半導体ウエハSWの主面の絶縁膜2をエッチングするためのエッチング液43を供給する。これにより、半導体ウエハSWの主面にノズル42からエッチング液43が供給され、このエッチング液43により、半導体ウエハSWの主面に形成されていた上記絶縁膜2がエッチング(ウェットエッチング)される。ノズル42から半導体ウエハSWの主面の中心部付近に供給されたエッチング液43は、半導体ウエハSWの回転によって、半導体ウエハSWの主面の中心部から外周部側に移動して、半導体ウエハSWの主面の全面にエッチング液43が行き渡り、半導体ウエハSWの主面の全面で、エッチング液43による絶縁膜2のエッチングが行われる。

【0080】

絶縁膜2のエッチングを停止するには、エッチング液用ノズル42から半導体ウエハSWの主面へのエッチング液43の供給を停止し、回転する半導体ウエハSWの主面(の中心部付近)へノズル42から純水などのリンス液(すすぎ液)を供給する。このリンス液が半導体ウエハSWの主面全体に行き渡ることで、半導体ウエハSWの主面のリンス処理(すすぎ処理)が行われ、半導体ウエハSWの主面からエッチング液43がリンス液とともに除去され、半導体ウエハSWの主面における絶縁膜2のエッチングが停止される。また、エッチング液43を半導体ウエハSWへ供給するノズルと、リンス液を半導体ウエハSWへ供給するノズルとを、同じノズル(ノズル42)で兼ねても、あるいは別々のノズルとしてもよい。

【0081】

本実施の形態では、絶縁膜2のウェットエッチング中の半導体ウエハSWの主面における照度を制御するために、上述のようにエッチング用チャンバ33に照明装置(光源)36が配置されている。照明装置36は、光44を発する光源として機能する。図31では、照明装置36が発する光44を矢印で模式的に示してある。照明装置36を設けるのは、照明装置36からの光44を半導体ウエハSWに当てる(照射する)ことで、絶縁膜2のエッチング中の半導体ウエハSWの照度を積極的に高くするためである。すなわち、エッチング液43を半導体ウエハSWの主面に供給して絶縁膜2のエッチングを行っている間、照明装置36によって半導体ウエハSWの主面を照らす(照明装置36からの光44を半導体ウエハSWの主面に当てる)ことにより、半導体ウエハSWの主面の照度を高くする。

【0082】

本実施の形態では、照明装置36からの光(照明装置36が発する光)を、半導体ウエハSWの主面に当てながら(照射しながら)、半導体ウエハSWの主面の絶縁膜2のエッチング(エッチング液43によるウェットエッチング)を行う。この際、半導体ウエハSWの主面の絶縁膜2のエッチング液43によるウェットエッチングの開始(半導体ウエハSWの主面にエッチング液43が接液した時点)から終了(リンス液によって半導体ウエハSWの主面からエッチング液43が除去された時点)まで、照明装置36からの光44を半導体ウエハSWの主面に当て続けるようにすることが好ましい。

【0083】

エッチング液43により絶縁膜2がウェットエッチングされる際に、照明装置36からの光44が半導体ウエハSWの主面全体に当たる(照射される)場合だけでなく、半導体ウエハSWの主面の一部に当たる(照射される)場合もあり得る。例えば、照明装置36から半導体ウエハSWの主面へ向かった光44の一部がノズル42で遮蔽されるなどして、照明装置36からの光44が半導体ウエハSWの主面全体ではなく、半導体ウエハSWの主面の一部に当たる(照射される)場合もあり得る。しかしながら、半導体ウエハSWは回転ステージ41とともに回転しているので、照明装置36からの光44が半導体ウエハSWの主面の一部に当たる(照射される)場合であっても、半導体ウエハSWの主面において光44が照射されている領域は、半導体ウエハSWの回転に伴い半導体ウエハSWの主面内を移動する。このため、絶縁膜2をエッチング液43でウェットエッチングしている間に、半導体ウエハSWの主面のいずれの領域も照明装置36からの光44が照射される期間を有することができる。逆に言えば、半導体ウエハSWの主面のいずれの領域も、絶縁膜2がエッチング液43でウェットエッチングされている間に照明装置36からの光44が照射される期間を有するように、半導体ウエハSWの主面の少なくとも一部に対して照明装置36からの光44を照射すればよい。つまり、半導体基板1(半導体ウエハSW)の主面が、絶縁膜2をウェットエッチングしている間に光44が全く照射されなかった領域を有さないようにすればよい。

【0084】

その理由は後述するが、本実施の形態では、半導体ウエハSWの主面の少なくとも一部(半導体ウエハSWの主面全面または主面の一部)に140ルクス以上の光を当てながら、絶縁膜2を(エッチング液43により)ウェットエッチングすることが好ましい。そして、半導体ウエハSWの主面のいずれの領域も、絶縁膜2を(エッチング液43により)ウェットエッチングしている間に140ルクス以上の光が照射されている期間を有するようにすることが、より好ましい。ここで、140ルクス以上の光とは、半導体ウエハSWの主面における照度が140ルクス以上であることに対応している。半導体ウエハSWの主面における照度は、光源(ここでは照明装置36)の明るさや、光源(ここでは照明装置36)から半導体ウエハSWの主面までの距離などにより制御することができる。

【0085】

<素子分離領域形成に伴う欠陥発生について>

次に、素子分離領域形成に伴う欠陥発生について説明する。

【0086】

図32〜図34は、絶縁膜2に相当する酸化膜102をウェットエッチングで除去したときに発生する欠陥の説明図である。

【0087】

図32〜図34において、酸化膜102は上記絶縁膜2に相当するものであり、溝104aは上記溝4aに相当するものであり、絶縁膜105は上記絶縁膜5に相当するものであり、絶縁膜106は上記絶縁膜6に相当するものであり、溝104a内に埋め込まれた絶縁膜105,106により形成された素子分離領域104は上記素子分離領域4に相当するものである。なお、図32は、上記ステップS11に相当する酸化膜102の除去工程(ウェットエッチング工程)を行う前の段階であり、図33は、上記ステップS11に相当する酸化膜102の除去工程(ウェットエッチング工程)を行った後の段階であり、図34は、酸化膜102の除去に伴って半導体基板1にピット(窪み、穴)51が形成された状態が示されている。

【0088】

図32の構造(状態)は、上記図14の構造(状態)を得るまでとほぼ同様の工程を行うことにより形成されている。図32の状態から、酸化膜102をフッ酸でウェットエッチングして除去することにより半導体基板1(のSi面)を露出させることで、上記図15に相当する図33の構造(状態)が得られるが、本発明者の解析によると、酸化膜102の除去に伴って図34のように半導体基板1にピット(窪み、穴)51が形成される場合がある。このピット51は、素子分離領域104で囲まれた活性領域において、酸化膜102をウェットエッチングして半導体基板1(のSi面)を露出させたときに発生する。

【0089】

このピット51の発生原因について、本発明者が検討したところ、素子分離領域104を形成する種々の工程に伴い酸化膜102に蓄えられた(チャージされた)電荷が主原因であることが分かった。酸化膜102をウェットエッチングするときに酸化膜102がエッチングの進行に伴って薄くなってくると、この電荷(酸化膜102に蓄えられた電荷)が半導体基板1側に放電してしまい、この放電によって半導体基板1にピット51が形成されることが分かった。

【0090】

半導体基板1にピット51が発生した場合、そのピット51を含む半導体チップ領域(半導体ウエハにおいて後で個々の半導体チップが取得される各領域を半導体チップ領域と称する)から取得された半導体チップ(半導体装置)の信頼性を低下させる虞がある。また、ピット51を含む半導体チップ領域から取得された半導体チップを選別して除去する場合は、半導体装置の製造歩留まりを低下させ、コスト上昇の原因となる。

【0091】

そこで、酸化膜102に電荷が蓄積される原因を調べたところ、素子分離領域104を形成するための種々の工程においてプラズマを用いる際に、半導体基板1の主面に形成されている絶縁膜にプラズマに起因した電荷が蓄積されることが、主原因であることが分かった。特に影響が大きいのは、素子分離用の溝104aを形成するためのプラズマドライエッチング(上記ステップS4に相当する工程)である。素子分離用の溝104aは深さが深いため、溝104aを形成するためのプラズマドライエッチングに要する時間が長く、溝104a形成のプラズマドライエッチングの際に、半導体基板1の主面に形成されている絶縁膜にプラズマに起因した電荷が蓄えられやすい(チャージされやすい)。溝104a形成時に半導体基板1の主面の絶縁膜に蓄えられた(チャージされた)電荷は、その後も除去されにくく、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。

【0092】

また、溝104a形成工程以外に、溝104aを埋める絶縁膜106(上記絶縁膜6に相当)を形成する工程(上記ステップS6に相当する工程)も、上記電荷蓄積への影響が大きい。これは、溝104aの深さが深いため、その溝104aを埋める絶縁膜106は溝104aを埋め込むことができるように厚く形成する必要があり、この厚い絶縁膜106を形成するのにプラズマCVD法を用いると、絶縁膜106形成時にプラズマに起因した電荷が蓄えられやすい(チャージされやすい)。絶縁膜106形成時に蓄えられた(チャージされた)電荷は、その後も除去されにくく、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。これは、絶縁膜106をプラズマCVD法で形成した場合に生じ得るが、特にプラズマ密度が高いHDP−CVD法により絶縁膜106を形成する場合に、より顕著に生じる。

【0093】

このように、溝104a形成工程と絶縁膜106形成工程とは、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。また、溝104a形成工程や絶縁膜106形成工程以外に、上記ステップS7,S9に相当するプラズマドライエッチング工程もプラズマを利用した処理であるため、これらの工程を行った場合は、図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。また、プラズマ処理より影響は少ないが、酸化膜102を形成してから図32の構造を得るまでの間に行う種々の洗浄工程や、上記ステップS8に相当するCMP工程においても、静電気に起因した電荷の蓄積(チャージ)が発生し、これも図32の段階で酸化膜102に蓄えられている電荷を多くするように作用する。

【0094】

このように、酸化膜102を形成してから図32の構造を得るまでに、素子分離領域104を形成するための種々の工程で半導体基板1の主面に形成されている絶縁膜にチャージされた電荷は、酸化膜102を除去する直前の段階(図32の段階)では、酸化膜102にチャージされた状態となる。この電荷が、酸化膜102をウェットエッチングして半導体基板1を露出させる工程(図32から図33に移行する工程)において半導体基板1が露出する直前に酸化膜102の厚みが薄くなったときに、半導体基板1側に放電し、この放電によって半導体基板1にピット51が形成される。つまり、素子分離領域104を形成するための種々の工程で電荷がチャージされやすいことと、酸化膜102を形成してから酸化膜102をウェットエッチングして除去する(図32から図33に移行する工程)までの間に半導体基板1(のSi面)が露出されないこととにより、酸化膜102除去時に放電が起こりやすく、この放電によりピット51が形成されてしまう。素子分離領域104で囲まれた活性領域においては、酸化膜102に蓄えられていた電荷は逃げ場がないことから、酸化膜102をウェットエッチングしてその活性領域(のSi面)が露出する直前に、酸化膜102側から活性領域の半導体基板1(Si領域)側に電荷が放電して、ピット51が形成されるのである。また、酸化膜102のウェットエッチングにはフッ酸の水溶液のようにイオンを含む液体を用いるが、そのような液体を用いても、酸化膜102にチャージされている電荷を除去することは難しく、放電によりピット51が形成されてしまう。

【0095】

<本実施の形態の主要な特徴と効果>

そこで、本実施の形態では、ステップS11の絶縁膜2の除去(ウェットエッチング)工程において、照明装置36からの光44を半導体ウエハSWに当てる(照射する)ようにしている。すなわち、ステップS11では、半導体ウエハSWに照明装置36からの光44を当てながら(照射しながら)、絶縁膜2をウェットエッチングする。光44を半導体ウエハSWに当てるのは、光電効果によりSi基板(半導体基板1に対応するSi基板領域)で電荷(ここでは主として電子)を発生させてこれをSi基板側から絶縁膜2側に供給し、絶縁膜2に既に蓄えられていた電荷(主として正孔が蓄えられている)を中和させる(電子と正孔とを結合させて消滅させる)ためである。

【0096】

図35および図36は、ステップS11に相当する工程を行った半導体ウエハSWの主面の電荷分布の説明図である。図35は、本実施の形態とは異なり、照明装置36からの光44を半導体ウエハSWに当てずにステップS11(絶縁膜2のウェットエッチング)を行なった場合に対応し、図36は、本実施の形態のように、照明装置36からの光44を半導体ウエハSWに当てながらステップS11(絶縁膜2のウェットエッチング)を行なった場合に対応する。図35および図36において(a)で示されているのは、ステップS11を行ったときの半導体ウエハSWの主面における電荷分布(チャージされている電荷の分布)を等高線で示したものであり、等高線の数字が大きいほど、単位面積当たりの電荷の密度(チャージされている電荷の密度)が高いことを示している。また、図35および図36において(b)で示されているのは、(a)の分布をヒストグラム(度数分布)で示したものであり、(b)のヒストグラムの縦軸の数値は(a)の等高線の数値に対応し、(b)のヒストグラムの横軸は半導体ウエハSWの主面の全面積に占める割合(百分率表示)に対応している。なお、図35および図36の(a)の分布は、表面電荷測定装置により測定したものである。

【0097】

図35と図36を比べると分かるように、照明装置36からの光44を半導体ウエハSWに当てることにより、チャージされている電荷の量(密度)を低減することができる。これは、照明装置36からの光44による光電効果によってSi基板領域(半導体基板1に対応するSi基板領域)側から絶縁膜側に電荷(ここでは主として電子)が供給され、絶縁膜に蓄えられていた電荷(主としてホールが蓄えられている)を中和できたためと考えられる。

【0098】

図37は、上記ピット51の発生状況を示す説明図である。図37には、本実施の形態とは異なり、照明装置36からの光44を半導体ウエハSWに当てずに半導体ウエハSWの主面に形成された上記酸化膜102のウェットエッチング工程(上記図32から図33に移行する工程)を行なった場合に、発生した上記ピット51の分布が示されている。図37の半導体ウエハSWの主面において、黒い点で示されているのが、ピット51の発生位置であり、ピット51は半導体ウエハSWの主面において特定の位置に密集して発生しやすいことが、図37から分かる。図37と図35の(a)とを比べると分かるように、図37の半導体ウエハSWの主面においてピット51が密集して発生している領域は、図35の(a)の半導体ウエハSWの主面においてチャージされている電荷の密度が比較的高い領域と、かなり一致している(相関性が高い)。つまり、半導体ウエハSWの主面に形成された酸化膜102に高密度で電荷がチャージされている領域があると、その領域においてピット51が発生しやすいと考えられる。

【0099】

それに対して、本実施の形態では、照明装置36からの光44を半導体ウエハSWに当てながらステップS11(絶縁膜2のウェットエッチング)を行うことにより、半導体ウエハSWの主面の絶縁膜2にチャージされている電荷を光電効果によって中和して電荷密度を低減することができるため、基板領域におけるピット(上記ピット51に相当するもの)の発生を抑制または防止できる。本実施の形態の場合、図37において、ピット51はほぼ発生しなくなる。

【0100】

Siに光電効果を発生させるためには、1.1eV以上のエネルギーを与えればよい。光エネルギーは、次の式1

E=hν=h×c/λ ・・・(式1)

で表される。式1中のEはエネルギー、hはプランク定数、νは振動数、cは光の速さ、λは波長である。式1より、1.1eV以上のエネルギーを与えるには、1127nm以下の波長の光が必要であることが分かる。このため、ステップS11(絶縁膜2のウェットエッチング工程)において半導体ウエハSWに照射する光44は、1127nm以下の波長の光とすればよい。

【0101】

このように、本実施の形態は、ステップS11において、半導体ウエハSW(半導体基板1)に光(具体的には照明装置36からの光44)を当てながら(照射しながら)、絶縁膜2をウェットエッチングすることにより、上記ピット51の発生を抑制または防止している。この際、半導体ウエハSWに照射される光44は、140ルクス以上とすることが好ましい。ここで、140ルクス以上とは、半導体ウエハSWの主面における照度が140ルクス以上であることに対応している。半導体ウエハSWの主面における照度が低いと、光電効果が十分に得られないが、半導体ウエハSWに照射される光44を140ルクス以上とすることにより、光電効果によりSi基板(半導体基板1に対応するSi基板領域)で電荷(ここでは主として電子)を的確に発生させることができ、上記ピット51の発生を的確に防止できるようになる。

【0102】

また、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする(ステップS11を行う)ことがピット51発生抑制には重要であり、ステップS11の前に半導体ウエハSWに光を照射したとしても、絶縁膜2のウェットエッチング(ステップS11)中に半導体ウエハSWに光を当てないのであれば、ピット51発生抑制の効果は十分には得られない。これは、次に理由によるものである。

【0103】

すなわち、絶縁膜2が形成された半導体ウエハSWに光を照射した場合、光電効果を生じさせるには、光が絶縁膜2を通過してSi基板領域に到達する必要があるため、絶縁膜2の厚みが薄くなってきたときに光を照射することが有効である。このため、ステップS11の前に半導体ウエハSWに光を照射したときには、絶縁膜2の厚みが比較的厚いことにより、光電効果は限定的である。しかしながら、本実施の形態のようにステップS11で半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする場合には、光が照射されながらウェットエッチングが進行して絶縁膜2の厚みが薄くなっていくため、半導体ウエハSWのSi基板領域に光が到達しやすくなり、光電効果により電荷(ここでは主として電子)を効率よく発生させることができるようになる。このため、ピット51発生抑制の効果を的確に得ることができる。また、本実施の形態のようにステップS11で半導体ウエハSWの主面に光を当てながら絶縁膜2をウェットエッチングする場合、ウェットエッチングが進行して絶縁膜2の厚みが薄くなっていくと、絶縁膜2にチャージされている電荷密度(体積当たりの電荷密度)が徐々に大きくなっていき、そのときに光電効果による電荷(主として電子)が供給されることで、電子と正孔が結合して消滅しやすくなる。このため、ピット51発生抑制の効果を的確に得ることができる。

【0104】

本実施の形態のステップS11における半導体基板1(半導体ウエハSW)への光44の照射の仕方をまとめると以下のようになる。

【0105】

本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)の主面に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングするが、この際、半導体基板1(半導体ウエハSW)の主面の少なくとも一部に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。これにより、半導体基板1(半導体ウエハSW)の主面の光44が照射された領域において、上記ピット51の発生を抑制または防止することができる。

【0106】

また、本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)を回転させ、回転する半導体基板1(半導体ウエハSW)の主面の少なくとも一部に光44(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。これにより、光44が半導体基板1(半導体ウエハSW)の主面の全体ではなく一部に照射される場合であっても、光44が照射されている領域は、半導体基板1(半導体ウエハSW)の回転に伴い半導体基板1(半導体ウエハSW)の主面内を移動することができ、半導体基板1(半導体ウエハSW)の主面において光44が照射される領域の実効的な面積を大きくすることができる。これにより、半導体基板1(半導体ウエハSW)の主面における、上記ピット51の発生を抑制または防止できる領域を大きくすることができる。

【0107】

また、本実施の形態では、ステップS11において、半導体基板1(半導体ウエハSW)の主面のいずれの領域も、絶縁膜2をウェットエッチングしている間に光44(好ましくは140ルクス以上の光)が照射されている期間を有するようにすることが好ましい。すなわち、ステップS11において、半導体基板1(半導体ウエハSW)の主面が、絶縁膜2をウェットエッチングしている間に光44(好ましくは140ルクス以上の光)が全く照射されなかった領域を有さないようにすることが好ましい。これにより、半導体基板1(半導体ウエハSW)の主面の全領域において、上記ピット51の発生を抑制または防止できる効果を得られる。

【0108】

このように、本実施の形態では、ピット51の発生を抑制または防止できることで、半導体装置の信頼性を向上することができる。また、半導体装置の製造歩留まりを向上することができる。

【0109】

また、本実施の形態は、素子分離領域4を形成する種々の工程(特にプラズマを使用した工程)で電荷がチャージされやすいことに起因したピット51の発生を抑制または防止できる技術であるが、電荷のチャージに特に影響が大きいのは、素子分離用の溝4aを形成するためのプラズマドライエッチング工程であり、それ以外には、溝4aを埋める絶縁膜6を形成するプラズマCVD工程の影響も大きい。このため、本実施の形態は、素子分離用の溝4aをプラズマドライエッチングにより形成することと、溝4aを埋める絶縁膜6をプラズマCVD法により形成することの、少なくとも一方を満たしている場合に適用すれば、上記ピット51の発生抑制(防止)の効果を得られるが、両方を満たす場合に適用すれば、効果が最も大きい。

【0110】

<ステップS11と他のウェットエッチング工程との関係>

また、本実施の形態では、素子分離領域4形成に伴うピット51の発生を抑制または防止するために、ステップS11の絶縁膜2のウェットエッチング工程で半導体ウエハSWに光44を照射している。しかしながら、ステップS11(絶縁膜2除去工程)よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(エッチングマスクとして機能するフォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにする。これは、レジスト層(フォトレジスト層)は、光が照射されると変質し(例えば硬くなり)、後で除去しにくくなるためである。

【0111】

ステップS11では、半導体基板1(半導体ウエハSW)の主面にレジスト層(フォトレジスト層)を形成していない状態で絶縁膜2をウェットエッチングするため、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングしても、レジスト層自体が無いため、レジスト層(フォトレジスト層)に光が照射されることによる不具合は生じない。一方、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにすることで、レジスト層(フォトレジスト層)に光が照射されることによる不具合を抑制または防止できる。

【0112】

ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにしても、上記ピット51のようなものは発生しにくい。これは、ステップS11で絶縁膜2をウェットエッチングで除去して半導体基板1を露出させた段階で、半導体基板1の主面には素子分離領域4を除いて絶縁膜が形成されていない状態(電荷がチャージされた絶縁膜が無い状態)となり、その後の工程では、素子分離領域4形成時ほど半導体基板1(半導体ウエハSW)主面の絶縁膜に電荷がチャージされないためである。

【0113】

つまり、ステップS11で絶縁膜2を除去する工程は、ピット51が発生しやすい工程でかつレジスト層(フォトレジスト層)が形成されていない状態で行う工程であるため、ピット51の発生抑制(防止)のために、半導体ウエハSWの主面に光(好ましくは140ルクス以上の光)を当てながら絶縁膜2をウェットエッチングする。一方、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる工程は、ピット51が発生しにくい工程でかつレジスト層が形成された状態で行う工程であるため、レジスト層の変質を抑制するため、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにする。このように、半導体基板1(半導体ウエハSW)の主面上に形成された絶縁膜をウェットエッチングで除去して半導体基板1を露出させるという観点では同じ工程であっても、光を積極的に当てる場合(ステップS11)と当てない場合(ステップS11よりも後の工程でかつレジスト層が形成されている工程)とを使い分け、半導体装置の総合的な信頼性向上や製造歩留まり向上を図ることができる。

【0114】

ここで、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる工程を例示すると、上記ステップS14であり、前記絶縁膜及び前記レジスト層は、絶縁膜11およびフォトレジストパターンPR3にそれぞれ対応している。すなわち、上記ステップS14では、フォトレジストパターンPR3で覆われない領域(ここでは低耐圧MIS領域1B)の絶縁膜11がウェットエッチングによって除去されて半導体基板1の上面(すなわちSi面)が露出されるが、この際のウェットエッチングは、半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないように行うのである。これは、ステップS14の絶縁膜11のウェットエッチングにおいては、半導体基板1(半導体ウエハSW)の主面における照度が100ルクス未満となるようにする、つまり、半導体基板1の主面が100ルクス以上の照度となる領域を有さないようにすることに対応している。これにより、絶縁膜11をウェットエッチングする際のフォトレジストパターンPR3の光による変質(例えば硬化)を抑制して、その後にフォトレジストパターンPR3を除去しやすくすることができ、フォトレジストパターンPR3の除去残りの発生を抑制または防止することができる。これにより、半導体装置の信頼性を向上することができる。また、半導体装置の製造歩留まりを向上することができる。また、ステップS14でウェットエッチングされる直前の絶縁膜11にチャージされている電荷は、ステップS11でウェットエッチングされる直前の絶縁膜2にチャージされている電荷よりもかなり少ないため、ステップS14で絶縁膜11をウェットエッチングする際に半導体基板1(半導体ウエハSW)の主面に100ルクス以上の光が照射されないようにしても、ピット51に相当するものの発生を抑制または防止することができる。

【0115】

また、上記のことを別の観点で見ると、ステップS11よりも後において、半導体基板1(半導体ウエハSW)の主面に絶縁膜と該絶縁膜上のレジスト層(フォトレジスト層)とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には、半導体基板1(半導体ウエハSW)の主面の照度が、ステップS11における半導体基板1(半導体ウエハSW)の主面の照度よりも低くなるようにする。具体的には、上記ステップS14で絶縁膜11をウェットエッチングしているときの半導体基板1(半導体ウエハSW)の主面の照度を、上記ステップS11で絶縁膜2をウェットエッチングしているときの半導体基板1(半導体ウエハSW)の主面の照度よりも低くするのである。これにより、上記ピット51に相当するものの発生を抑制または防止できるという効果を得られるとともに、レジスト層の除去残りの発生を抑制または防止できるという効果を得られる。そして、ステップS11における半導体基板1(半導体ウエハSW)の主面の照度は140ルクス以上が好ましく、ステップS11工程の後において、半導体基板1の主面に絶縁膜と該絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って半導体基板1を露出させる際には(具体的にはステップS14では)、半導体基板1(半導体ウエハSW)の主面の照度は100ルクス以下が好ましい。これにより、上記ピット51に相当するものの発生を抑制または防止できるという効果と、レジスト層の除去残りの発生を抑制または防止できるという効果とを更に向上させ、半導体装置の信頼性や製造歩留まりを、より的確に向上することが可能になる。

【0116】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0117】

本発明は、半導体装置の製造技術に適用して有効である。

【符号の説明】

【0118】

1 半導体基板

1A 高耐圧MIS領域

1B 低高耐圧MIS領域

2 絶縁膜

3 絶縁膜

4 素子分離領域

4a 溝

5 絶縁膜

6 絶縁膜

11 絶縁膜

12 絶縁膜

13 導電体膜

22 絶縁膜

23 コンタクトホール

24 プラグ

25 絶縁膜

31 半導体製造装置

32 搬送室

33 エッチング用チャンバ

34 ロードポート

35 搬送用ロボット

36 照明装置

41 回転ステージ

42 ノズル

43 エッチング液

51 ピット

102 酸化膜

104a 溝

105 絶縁膜

106 絶縁膜

EX エクステンション領域

GE,GE1,GE2 ゲート電極

M1 配線

PR1,PR2,PR3,PR4 フォトレジストパターン

Q1,Q2 MISFET

SD ソース・ドレイン領域

SP サイドウォールスペーサ

SW 半導体ウエハ

【特許請求の範囲】

【請求項1】

(a)半導体基板を準備する工程、

(b)前記半導体基板の主面に第1絶縁膜を形成する工程、

(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、

(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程、

(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、

(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程、

を有し、

前記(f)工程では、前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記(f)工程では、回転する前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項3】

請求項2記載の半導体装置の製造方法において、

前記(f)工程では、回転する前記半導体基板の主面に前記第1絶縁膜をエッチングするためのエッチング液を供給して、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項4】

請求項3記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面のいずれの領域も、前記第1絶縁膜をウェットエッチングしている間に140ルクス以上の光が照射されている期間を有することを特徴とする半導体装置の製造方法。

【請求項5】

請求項4記載の半導体装置の製造方法において、

前記第1絶縁膜は、酸化膜であることを特徴とする半導体装置の製造方法。

【請求項6】

請求項5記載の半導体装置の製造方法において、

前記(b)工程では、熱酸化により前記第1絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項7】

請求項6記載の半導体装置の製造方法において、

前記(b)工程後で、前記(c)工程前に

(b1)前記第1絶縁膜上に第3絶縁膜を形成する工程、

を更に有し、

前記(c)工程では、前記第3絶縁膜、前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第3絶縁膜、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成し、

前記(e)工程後で、前記(f)工程前に、

(e1)前記第3絶縁膜を除去して前記第1絶縁膜を露出させる工程、

を更に有することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7記載の半導体装置の製造方法において、

前記第3絶縁膜は、窒化シリコン膜であることを特徴とする半導体装置の製造方法。

【請求項9】

請求項8記載の半導体装置の製造方法において、

前記(d)工程では、プラズマCVD法により前記第2絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項10】

請求項9記載の半導体装置の製造方法において、

前記(d)工程では、高密度プラズマCVD法により前記第2絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項11】

請求項10記載の半導体装置の製造方法において、

前記第2絶縁膜は、酸化シリコン膜であることを特徴とする半導体装置の製造方法。

【請求項12】

請求項11記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面上にレジスト層が形成されていない状態で、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項13】

請求項12記載の半導体装置の製造方法において、

前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面に100ルクス以上の光が照射されないようにすることを特徴とする半導体装置の製造方法。

【請求項14】

請求項13記載の半導体装置の製造方法において、

前記絶縁膜は、MISFETのゲート絶縁膜用の絶縁膜であることを特徴とする半導体装置の製造方法。

【請求項15】

(a)半導体基板を準備する工程、

(b)前記半導体基板の主面に第1絶縁膜を形成する工程、

(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、

(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程、

(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、

(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程、

を有し、

前記(f)工程では、前記半導体基板の主面に光を当てながら前記第1絶縁膜をウェットエッチングし、

前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面の照度が、前記(f)工程における前記半導体基板の主面の照度よりも低くなるようにすることを特徴とする半導体装置の製造方法。

【請求項16】

請求項15記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面上にレジスト層が形成されていない状態で、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項17】

請求項16記載の半導体装置の製造方法において、

前記絶縁膜は、MISFETのゲート絶縁膜用の絶縁膜であることを特徴とする半導体装置の製造方法。

【請求項1】

(a)半導体基板を準備する工程、

(b)前記半導体基板の主面に第1絶縁膜を形成する工程、

(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、

(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程、

(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、

(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程、

を有し、

前記(f)工程では、前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記(f)工程では、回転する前記半導体基板の主面の少なくとも一部に140ルクス以上の光を当てながら前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項3】

請求項2記載の半導体装置の製造方法において、

前記(f)工程では、回転する前記半導体基板の主面に前記第1絶縁膜をエッチングするためのエッチング液を供給して、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項4】

請求項3記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面のいずれの領域も、前記第1絶縁膜をウェットエッチングしている間に140ルクス以上の光が照射されている期間を有することを特徴とする半導体装置の製造方法。

【請求項5】

請求項4記載の半導体装置の製造方法において、

前記第1絶縁膜は、酸化膜であることを特徴とする半導体装置の製造方法。

【請求項6】

請求項5記載の半導体装置の製造方法において、

前記(b)工程では、熱酸化により前記第1絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項7】

請求項6記載の半導体装置の製造方法において、

前記(b)工程後で、前記(c)工程前に

(b1)前記第1絶縁膜上に第3絶縁膜を形成する工程、

を更に有し、

前記(c)工程では、前記第3絶縁膜、前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第3絶縁膜、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成し、

前記(e)工程後で、前記(f)工程前に、

(e1)前記第3絶縁膜を除去して前記第1絶縁膜を露出させる工程、

を更に有することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7記載の半導体装置の製造方法において、

前記第3絶縁膜は、窒化シリコン膜であることを特徴とする半導体装置の製造方法。

【請求項9】

請求項8記載の半導体装置の製造方法において、

前記(d)工程では、プラズマCVD法により前記第2絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項10】

請求項9記載の半導体装置の製造方法において、

前記(d)工程では、高密度プラズマCVD法により前記第2絶縁膜を形成することを特徴とする半導体装置の製造方法。

【請求項11】

請求項10記載の半導体装置の製造方法において、

前記第2絶縁膜は、酸化シリコン膜であることを特徴とする半導体装置の製造方法。

【請求項12】

請求項11記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面上にレジスト層が形成されていない状態で、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項13】

請求項12記載の半導体装置の製造方法において、

前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面に100ルクス以上の光が照射されないようにすることを特徴とする半導体装置の製造方法。

【請求項14】

請求項13記載の半導体装置の製造方法において、

前記絶縁膜は、MISFETのゲート絶縁膜用の絶縁膜であることを特徴とする半導体装置の製造方法。

【請求項15】

(a)半導体基板を準備する工程、

(b)前記半導体基板の主面に第1絶縁膜を形成する工程、

(c)前記第1絶縁膜および前記半導体基板をプラズマドライエッチングすることにより、前記第1絶縁膜および前記半導体基板に素子分離用の溝を形成する工程、

(d)前記溝を埋めるように、前記半導体基板の主面上に第2絶縁膜を形成する工程、

(e)CMP処理により前記溝の外部の前記第2絶縁膜を除去し、前記溝内に前記第2絶縁膜を残す工程、

(f)前記第1絶縁膜をウェットエッチングで除去して前記半導体基板を露出させる工程、

を有し、

前記(f)工程では、前記半導体基板の主面に光を当てながら前記第1絶縁膜をウェットエッチングし、

前記(f)工程の後において、前記半導体基板の主面に絶縁膜と前記絶縁膜上のレジスト層とが形成された状態で前記絶縁膜のウェットエッチングを行って前記半導体基板を露出させる際には、前記半導体基板の主面の照度が、前記(f)工程における前記半導体基板の主面の照度よりも低くなるようにすることを特徴とする半導体装置の製造方法。

【請求項16】

請求項15記載の半導体装置の製造方法において、

前記(f)工程では、前記半導体基板の主面上にレジスト層が形成されていない状態で、前記第1絶縁膜をウェットエッチングすることを特徴とする半導体装置の製造方法。

【請求項17】

請求項16記載の半導体装置の製造方法において、

前記絶縁膜は、MISFETのゲート絶縁膜用の絶縁膜であることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【公開番号】特開2013−16672(P2013−16672A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−148802(P2011−148802)

【出願日】平成23年7月5日(2011.7.5)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年7月5日(2011.7.5)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]