半導体装置の製造方法

【課題】高精細化に伴う、貫通孔の微細化とさらに高アスペクト化の貫通電極を有する半導体装置の製造方法を提案する。

【解決手段】半導体基板1の厚み方向に貫通する貫通電極4を有する半導体装置の製造方法であって、半導体基板1の第1の面1aから第1孔10を開口する第1の工程と、第1孔10を含む半導体基板1の第1の面1aに絶縁膜2を形成する第2の工程と、半導体基板1の第1の面1aと反対の面である第2の面1bから、少なくとも2つの第1孔10を含んで第1孔10へ貫通する第2孔11を開口する第3の工程と、第2孔11側よりスパッタ法によりシード層3を成膜する第4の工程と、シード層3に金属材料4aをメッキ法により半導体基板1の第1の面1aに達するまで第1孔10を埋める第5の工程と、半導体基板1の第2の面1bを第2孔11の深さ寸法より深く、厚み方向に研削する第6の工程と、を含む。

【解決手段】半導体基板1の厚み方向に貫通する貫通電極4を有する半導体装置の製造方法であって、半導体基板1の第1の面1aから第1孔10を開口する第1の工程と、第1孔10を含む半導体基板1の第1の面1aに絶縁膜2を形成する第2の工程と、半導体基板1の第1の面1aと反対の面である第2の面1bから、少なくとも2つの第1孔10を含んで第1孔10へ貫通する第2孔11を開口する第3の工程と、第2孔11側よりスパッタ法によりシード層3を成膜する第4の工程と、シード層3に金属材料4aをメッキ法により半導体基板1の第1の面1aに達するまで第1孔10を埋める第5の工程と、半導体基板1の第2の面1bを第2孔11の深さ寸法より深く、厚み方向に研削する第6の工程と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板への貫通電極を形成するプロセスを含む半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体素子を応用した製品は小型、薄型化が進んでおり、実装形態においても複数の半導体素子を積層する事で実装密度を高める手法が知られている。このような手法を実現させるために半導体素子の表面から裏面へ貫通孔を設ける貫通電極の形成技術が知られている。

例えば、特許文献1に記載されているように、貫通電極の導電電極をメッキ法により形成する際に、スパッタ法、真空蒸着法などでビアにシード層を形成し、その後、シード層にメッキ工程を実施する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−114568号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記シード層の形成に関しては次のような問題がある。

近年の微細化に伴い、シード層を形成する際に貫通孔が狭小化し、貫通電極として高アスペクト比化している。その為、貫通孔を形成するビア内へのシード層の成膜が困難となり電解メッキに必要なビア内へのシード層の付き回りが確保されず、貫通電極が形成できないという課題があった。

これを説明するために、図5に従来品のビアの断面図、図6に微細化された製品のビアの断面図を示す。図5、図6は製品の貫通電極形成時のシード層を形成した断面図である。

図5に示すように、半導体基板1にビア20が形成され、ビア20の内部には絶縁層2が形成される。そして、絶縁層2を覆って貫通電極を電解メッキにて形成する際のシード層3が形成されている。このように、ビア20の開口が大きい場合、シード層3は貫通電極を形成するビア20の底面まで成膜できている。

これに対してビアの開口が狭小化された場合、図6に示すように、ビア20に成膜されるシード層3が底面まで達することができず、メッキによる貫通電極の形成ができない。

【課題を解決するための手段】

【0005】

本発明は、上述の課題を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0006】

[適用例1]本適用例に係る半導体装置の製造方法は、半導体基板の厚み方向に貫通する貫通電極を有する半導体装置の製造方法であって、前記半導体基板の第1の面から第1孔を開口する第1の工程と、前記第1孔を含む前記半導体基板の前記第1の面に絶縁膜を形成する第2の工程と、前記半導体基板の前記第1の面と反対の面である第2の面から、少なくとも2つの前記第1孔を含んで前記第1孔へ貫通する第2孔を開口する第3の工程と、前記第2孔側よりスパッタ法によりシード層を成膜する第4の工程と、前記第1孔に前記シード層を用いてメッキ法により前記半導体基板の第1の面に達するまで金属材料を埋める第5の工程と、前記半導体基板の前記第2の面を前記第2孔の深さ寸法より深く、厚み方向に研削する第6の工程と、を含むことを特徴とする。

【0007】

本適用例によれば、第1孔の底面へのシード層の成膜を半導体基板の第2の面側より実施するため、第1孔の底面へのシード層の成膜が可能となり、微小化した貫通電極の第1孔内への電解メッキで金属材料の充填ができることになる。従って高精細化して微小化した貫通電極の製造方法を提供できる。また、半導体ウェハーを最終段階にて薄型化するため、貫通電極形成プロセス中でも既存の半導体ウェハーと同等に取り扱いが可能である。

【0008】

[適用例2]上記適用例に係る半導体装置の製造方法において、第4の工程で成膜される前記シード層は、前記半導体基板の前記第2の面及び、前記第2孔の孔内及び前記第1孔の前記第2孔側の孔内に成膜されることが好ましい。

【0009】

本適用例によれば、電解メッキにてメッキを成長させる際に第1孔の第2孔側からのみメッキが成長するため、第1孔内へのメッキの形成時のボイドの発生が抑制される効果を得ることができる。

【0010】

[適用例3]上記適用例に係る半導体装置の製造方法において、前記第1工程で開口される第1孔の大きさは、前記半導体基板の前記第1の面側と開口された孔の前記第2孔側まで同じ大きさ、または前記半導体基板の前記第1の面側より前記第2孔側の方が小さいことが好ましい。

【0011】

本適用例によれば、第1孔への第2孔側から成膜されたシード層は第1孔の第2孔側へ形成されるという効果が得られる。

【図面の簡単な説明】

【0012】

【図1】実施形態1の半導体装置の構成を示す断面図。

【図2】実施形態1の製造工程を示す工程図。

【図3】実施形態2の半導体装置の構成を示す断面図。

【図4】実施形態2の製造工程を示す工程図。

【図5】従来の貫通電極形成のシード層を形成する工程の断面図。

【図6】微小化した製品に従来のシード層形成の方式で実施した際の断面図。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の各図においては、各層や各部材を認識可能な程度の大きさにするため、各層や各部材の尺度を実際とは異ならせしめている。

【0014】

(実施形態1)

図1は本実施形態の半導体装置の構成を示す断面図である。

シリコンなどの半導体基板1には第1の面1aから第2の面1bへ貫通する第1孔10が設けられ、この第1孔10の内面には絶縁膜2が形成されている。絶縁膜2はSiO2膜にて形成され、半導体基板1の第1の面1aを覆い、第1孔10の内周面に連続して形成されている。

また、半導体基板1の第1孔10の絶縁膜2の上にはシード層3が設けられている。シード層3は半導体基板1の第2の面1b側から第1孔10の途中まで形成されている。シード層3の材料はCu、Auなどの金属膜が用いられる。

そして、第1孔10に金属材料としてCuが充填されて、半導体基板1の第1の面1aから第2の面1bにおよぶ貫通電極4が形成されている。

【0015】

第1孔10の開口された孔の径は、第1の面1a側の開口径をd1、第2の面1b側の開口径をd2とすると、d1≧d2、となる関係に形成されている。

なお、半導体基板1の第1の面1aまたは第2の面1bに集積回路などの回路を構成してもよい。

【0016】

次に上記の半導体装置の製造方法について説明する。

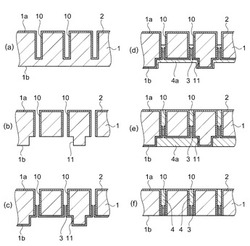

図2(a)〜図2(f)は、実施形態1に係る貫通電極の形成プロセスを示す工程図である。

【0017】

まず図2(a)に示すように、シリコンなどの半導体基板1の第1の面1aに第1孔10を形成し(第1の工程)、第1孔10の内面に絶縁膜2を成膜する(第2の工程)。第1孔10の深さは最終的に半導体基板1を薄型化するため、半導体基板1の最終厚み以上の深さでよい。ここでは半導体基板1の初期厚みを400μm、薄型後の厚みを100μm、第1孔10の深さを200μmとする。

第1孔10の形成方法はフォトレジストを使用しドライエッチングにより実施する。使用するガスはSF6、O2、C4F8、O2などを用いる。

第1孔10の開口径は10〜30μm程度とする。

絶縁膜2は無機材、有機材問わず絶縁性が確保できるものであればよい。

ここではSiO2をCVD法により成膜するものとする。

【0018】

次に図2(b)に示すように、半導体基板1の第2の面1bに第2孔11を第1孔10のドライエッチングと同様な手法により形成する(第3の工程)。

第2孔11の大きさは、2つ以上の第1孔10を含んで形成しており、ここでは2つの第1孔10を含んでいる。第2孔11の深さは半導体基板1の初期厚みから最終厚みを減じた深さ以下であり、かつ第1孔10まで貫通する深さとする。ここでは200μmとする。

【0019】

次に図2(c)に示すように、半導体基板の第2の面1bにシード層3を成膜する(第4の工程)。またシード層3の前に拡散防止層、密着層を形成してもよい。ここでは拡散防止層にTiW、シード層3にCuとし、いずれもスパッタ法により成膜を行い、それぞれの膜厚は100nm、300nmとする。

このとき、第1孔10の開口が狭いため、シード層3は第2の面1b側から第1の面1a側に向かう第1孔10の途中まで形成される。

【0020】

次に図2(d)、図2(e)に示すように、金属材料4aを電解メッキ法により第1孔10内に形成する(第5の工程)。ここではCuの電解メッキとする。

シード層3より半導体基板1の第2の面1b側より第1の面1aに向かいCuメッキが成長する。メッキの初期では、シード層3の周辺から金属材料4aが形成され、主に第1孔10の径方向に金属材料4aが充填される。そして、その後、第1孔10を第1の面1a側から第2の面1bへ向かって金属材料4aが充填される。

メッキ時間は第1孔10を全て充填するまでとする。

【0021】

次に図2(f)に示すように、半導体基板1の第1の面1aを研削もしくはCMP法により面精度を向上させる。

さらに、半導体基板1の第2の面1bを研削により薄型化し(第6の工程)、薄型と同時にシード層3、貫通電極4の分割を行う。ここでは最終厚みを100μmとした。

さらに必要により半導体基板1の第1の面1a、第2の面1bにバンプ形成、素子形成などを行ってもよい。

【0022】

以上述べたように、本実施形態1に係る半導体装置の製造方法によれば、以下の効果を得ることができる。

(1)第1孔10の底面へのシード層3の成膜を半導体基板1の第2の面1b側より実施するため、第1孔10の底面へのシード層3の成膜ができ、微小化した貫通電極4の形成が可能になり製品の高精細化、小型化が可能である。

(2)電解メッキにてメッキを成長させる際に第1孔10の第2孔11側からのみメッキが成長するため、第1孔10内へのメッキの形成時のボイドの発生が抑制される効果を得ることができる。

(3)第1工程に開口される第1孔10の大きさは、半導体基板1の第1の面1a側と開口された孔の第2孔11側まで同じ大きさ、または半導体基板1の第1の面1a側より第2孔11側の方が小さいことから、第1孔10への第2孔11側から成膜されたシード層3は第1孔10の第2孔11側へ形成されるという効果が得られる。

(4)高アスペクト比対応が可能であり貫通電極4の形成工程での薄型化するリスクを回避できる。

(5)シード層3のパターニングをなくす事ができるので既存の課題であるシード層のサイドエッチングの発生がなくなり配線幅も確保されるため、信頼性の向上にもつながる。

【0023】

(実施形態2)

図3は本実施形態の半導体装置の構成を示す断面図である。

本実施形態は電極パッドが形成された半導体基板に、この電極パッドを含んで貫通電極を形成している点が実施形態1と異なる。

なお、実施形態1と同一の構成部位については、同一の符号を使用する。

【0024】

シリコンなどの半導体基板1の第1の面1aにはSiO2膜からなる絶縁膜8が形成され、絶縁膜8の上に電極パッド5が形成されている。電極パッド5は例えばAl膜にて形成されている。そして、電極パッド5を含み第1の面1aから第2の面1bへ貫通する第1孔10が設けられている。

この第1孔10の内面には絶縁膜2が形成され、絶縁膜2はSiO2膜にて形成されている。

【0025】

また、半導体基板1の第1孔10の絶縁膜2の上にはシード層3が設けられている。シード層3は半導体基板1の第2の面1b側から第1孔10の途中まで形成されている。シード層3の材料はCu、Auなどの金属膜が用いられる。

そして、第1孔10に金属材料としてCuが充填されて、半導体基板1の第1の面1aから第2の面1bにおよぶ貫通電極4が形成されている。さらに、電極パッド5の上部に端子7が形成されている。

なお、端子7の上にバンプなどの接続手段を形成してもよい。

【0026】

次に上記の半導体装置の製造方法について説明する。

図4(a)〜図4(d)は、実施形態2に係る貫通電極の形成プロセスを示す工程図である。本実施形態に係る貫通電極の製造方法について、これらの図を参照して説明する。なお、実施形態1と同一の構成部位については、同一の符号を使用し、重複する説明は省略する。

【0027】

図4(a)に示すように、半導体基板1の第1の面1aに電極パッド5が形成されている。ここではアルミパッドとし実施形態1と同様に半導体基板1の第1の面1aに第1孔10を形成し(第1の工程)、その第1孔10に絶縁膜2を成膜する(第2の工程)。

電極パッド5表面の絶縁膜2はフォトレジにより開口を形成しドライエッチング法により除去する。

【0028】

次に図4(b)に示すように、実施形態1と同様に半導体基板1の第2の面1b側から第2孔11を形成(第3の工程)し、シード層3の形成を行う(第4の工程)。

【0029】

次に図4(c)に示すように、半導体基板1の第1の面1aの電極パッド5上にメッキ端子形成用のレジスト6を形成し、実施形態1と同様に貫通電極4を形成する(第5の工程)。

【0030】

次に図4(d)に示すように、半導体基板1の第1の面1aにレジスト6を除去し端子7を形成する。さらに半導体基板1の第2の面1b側を研削により実施形態1と同様に薄型化を行う(第6の工程)。

【0031】

以上述べたように、本実施形態2に係る半導体装置の製造方法によれば、以下の効果を得ることができる。

半導体基板1上へ配線パターンを形成してある基板においても貫通電極4を形成することが可能であり、製品形態の拡大化が図れる。

【符号の説明】

【0032】

1…半導体基板、1a…第1の面、1b…第2の面、2…絶縁膜、3…シード層、4…貫通電極、4a…金属材料、5…電極パッド、6…レジスト、7…端子、8…絶縁膜、10…第1孔、11…第2孔、20…ビア。

【技術分野】

【0001】

本発明は、半導体基板への貫通電極を形成するプロセスを含む半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体素子を応用した製品は小型、薄型化が進んでおり、実装形態においても複数の半導体素子を積層する事で実装密度を高める手法が知られている。このような手法を実現させるために半導体素子の表面から裏面へ貫通孔を設ける貫通電極の形成技術が知られている。

例えば、特許文献1に記載されているように、貫通電極の導電電極をメッキ法により形成する際に、スパッタ法、真空蒸着法などでビアにシード層を形成し、その後、シード層にメッキ工程を実施する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−114568号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記シード層の形成に関しては次のような問題がある。

近年の微細化に伴い、シード層を形成する際に貫通孔が狭小化し、貫通電極として高アスペクト比化している。その為、貫通孔を形成するビア内へのシード層の成膜が困難となり電解メッキに必要なビア内へのシード層の付き回りが確保されず、貫通電極が形成できないという課題があった。

これを説明するために、図5に従来品のビアの断面図、図6に微細化された製品のビアの断面図を示す。図5、図6は製品の貫通電極形成時のシード層を形成した断面図である。

図5に示すように、半導体基板1にビア20が形成され、ビア20の内部には絶縁層2が形成される。そして、絶縁層2を覆って貫通電極を電解メッキにて形成する際のシード層3が形成されている。このように、ビア20の開口が大きい場合、シード層3は貫通電極を形成するビア20の底面まで成膜できている。

これに対してビアの開口が狭小化された場合、図6に示すように、ビア20に成膜されるシード層3が底面まで達することができず、メッキによる貫通電極の形成ができない。

【課題を解決するための手段】

【0005】

本発明は、上述の課題を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0006】

[適用例1]本適用例に係る半導体装置の製造方法は、半導体基板の厚み方向に貫通する貫通電極を有する半導体装置の製造方法であって、前記半導体基板の第1の面から第1孔を開口する第1の工程と、前記第1孔を含む前記半導体基板の前記第1の面に絶縁膜を形成する第2の工程と、前記半導体基板の前記第1の面と反対の面である第2の面から、少なくとも2つの前記第1孔を含んで前記第1孔へ貫通する第2孔を開口する第3の工程と、前記第2孔側よりスパッタ法によりシード層を成膜する第4の工程と、前記第1孔に前記シード層を用いてメッキ法により前記半導体基板の第1の面に達するまで金属材料を埋める第5の工程と、前記半導体基板の前記第2の面を前記第2孔の深さ寸法より深く、厚み方向に研削する第6の工程と、を含むことを特徴とする。

【0007】

本適用例によれば、第1孔の底面へのシード層の成膜を半導体基板の第2の面側より実施するため、第1孔の底面へのシード層の成膜が可能となり、微小化した貫通電極の第1孔内への電解メッキで金属材料の充填ができることになる。従って高精細化して微小化した貫通電極の製造方法を提供できる。また、半導体ウェハーを最終段階にて薄型化するため、貫通電極形成プロセス中でも既存の半導体ウェハーと同等に取り扱いが可能である。

【0008】

[適用例2]上記適用例に係る半導体装置の製造方法において、第4の工程で成膜される前記シード層は、前記半導体基板の前記第2の面及び、前記第2孔の孔内及び前記第1孔の前記第2孔側の孔内に成膜されることが好ましい。

【0009】

本適用例によれば、電解メッキにてメッキを成長させる際に第1孔の第2孔側からのみメッキが成長するため、第1孔内へのメッキの形成時のボイドの発生が抑制される効果を得ることができる。

【0010】

[適用例3]上記適用例に係る半導体装置の製造方法において、前記第1工程で開口される第1孔の大きさは、前記半導体基板の前記第1の面側と開口された孔の前記第2孔側まで同じ大きさ、または前記半導体基板の前記第1の面側より前記第2孔側の方が小さいことが好ましい。

【0011】

本適用例によれば、第1孔への第2孔側から成膜されたシード層は第1孔の第2孔側へ形成されるという効果が得られる。

【図面の簡単な説明】

【0012】

【図1】実施形態1の半導体装置の構成を示す断面図。

【図2】実施形態1の製造工程を示す工程図。

【図3】実施形態2の半導体装置の構成を示す断面図。

【図4】実施形態2の製造工程を示す工程図。

【図5】従来の貫通電極形成のシード層を形成する工程の断面図。

【図6】微小化した製品に従来のシード層形成の方式で実施した際の断面図。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の各図においては、各層や各部材を認識可能な程度の大きさにするため、各層や各部材の尺度を実際とは異ならせしめている。

【0014】

(実施形態1)

図1は本実施形態の半導体装置の構成を示す断面図である。

シリコンなどの半導体基板1には第1の面1aから第2の面1bへ貫通する第1孔10が設けられ、この第1孔10の内面には絶縁膜2が形成されている。絶縁膜2はSiO2膜にて形成され、半導体基板1の第1の面1aを覆い、第1孔10の内周面に連続して形成されている。

また、半導体基板1の第1孔10の絶縁膜2の上にはシード層3が設けられている。シード層3は半導体基板1の第2の面1b側から第1孔10の途中まで形成されている。シード層3の材料はCu、Auなどの金属膜が用いられる。

そして、第1孔10に金属材料としてCuが充填されて、半導体基板1の第1の面1aから第2の面1bにおよぶ貫通電極4が形成されている。

【0015】

第1孔10の開口された孔の径は、第1の面1a側の開口径をd1、第2の面1b側の開口径をd2とすると、d1≧d2、となる関係に形成されている。

なお、半導体基板1の第1の面1aまたは第2の面1bに集積回路などの回路を構成してもよい。

【0016】

次に上記の半導体装置の製造方法について説明する。

図2(a)〜図2(f)は、実施形態1に係る貫通電極の形成プロセスを示す工程図である。

【0017】

まず図2(a)に示すように、シリコンなどの半導体基板1の第1の面1aに第1孔10を形成し(第1の工程)、第1孔10の内面に絶縁膜2を成膜する(第2の工程)。第1孔10の深さは最終的に半導体基板1を薄型化するため、半導体基板1の最終厚み以上の深さでよい。ここでは半導体基板1の初期厚みを400μm、薄型後の厚みを100μm、第1孔10の深さを200μmとする。

第1孔10の形成方法はフォトレジストを使用しドライエッチングにより実施する。使用するガスはSF6、O2、C4F8、O2などを用いる。

第1孔10の開口径は10〜30μm程度とする。

絶縁膜2は無機材、有機材問わず絶縁性が確保できるものであればよい。

ここではSiO2をCVD法により成膜するものとする。

【0018】

次に図2(b)に示すように、半導体基板1の第2の面1bに第2孔11を第1孔10のドライエッチングと同様な手法により形成する(第3の工程)。

第2孔11の大きさは、2つ以上の第1孔10を含んで形成しており、ここでは2つの第1孔10を含んでいる。第2孔11の深さは半導体基板1の初期厚みから最終厚みを減じた深さ以下であり、かつ第1孔10まで貫通する深さとする。ここでは200μmとする。

【0019】

次に図2(c)に示すように、半導体基板の第2の面1bにシード層3を成膜する(第4の工程)。またシード層3の前に拡散防止層、密着層を形成してもよい。ここでは拡散防止層にTiW、シード層3にCuとし、いずれもスパッタ法により成膜を行い、それぞれの膜厚は100nm、300nmとする。

このとき、第1孔10の開口が狭いため、シード層3は第2の面1b側から第1の面1a側に向かう第1孔10の途中まで形成される。

【0020】

次に図2(d)、図2(e)に示すように、金属材料4aを電解メッキ法により第1孔10内に形成する(第5の工程)。ここではCuの電解メッキとする。

シード層3より半導体基板1の第2の面1b側より第1の面1aに向かいCuメッキが成長する。メッキの初期では、シード層3の周辺から金属材料4aが形成され、主に第1孔10の径方向に金属材料4aが充填される。そして、その後、第1孔10を第1の面1a側から第2の面1bへ向かって金属材料4aが充填される。

メッキ時間は第1孔10を全て充填するまでとする。

【0021】

次に図2(f)に示すように、半導体基板1の第1の面1aを研削もしくはCMP法により面精度を向上させる。

さらに、半導体基板1の第2の面1bを研削により薄型化し(第6の工程)、薄型と同時にシード層3、貫通電極4の分割を行う。ここでは最終厚みを100μmとした。

さらに必要により半導体基板1の第1の面1a、第2の面1bにバンプ形成、素子形成などを行ってもよい。

【0022】

以上述べたように、本実施形態1に係る半導体装置の製造方法によれば、以下の効果を得ることができる。

(1)第1孔10の底面へのシード層3の成膜を半導体基板1の第2の面1b側より実施するため、第1孔10の底面へのシード層3の成膜ができ、微小化した貫通電極4の形成が可能になり製品の高精細化、小型化が可能である。

(2)電解メッキにてメッキを成長させる際に第1孔10の第2孔11側からのみメッキが成長するため、第1孔10内へのメッキの形成時のボイドの発生が抑制される効果を得ることができる。

(3)第1工程に開口される第1孔10の大きさは、半導体基板1の第1の面1a側と開口された孔の第2孔11側まで同じ大きさ、または半導体基板1の第1の面1a側より第2孔11側の方が小さいことから、第1孔10への第2孔11側から成膜されたシード層3は第1孔10の第2孔11側へ形成されるという効果が得られる。

(4)高アスペクト比対応が可能であり貫通電極4の形成工程での薄型化するリスクを回避できる。

(5)シード層3のパターニングをなくす事ができるので既存の課題であるシード層のサイドエッチングの発生がなくなり配線幅も確保されるため、信頼性の向上にもつながる。

【0023】

(実施形態2)

図3は本実施形態の半導体装置の構成を示す断面図である。

本実施形態は電極パッドが形成された半導体基板に、この電極パッドを含んで貫通電極を形成している点が実施形態1と異なる。

なお、実施形態1と同一の構成部位については、同一の符号を使用する。

【0024】

シリコンなどの半導体基板1の第1の面1aにはSiO2膜からなる絶縁膜8が形成され、絶縁膜8の上に電極パッド5が形成されている。電極パッド5は例えばAl膜にて形成されている。そして、電極パッド5を含み第1の面1aから第2の面1bへ貫通する第1孔10が設けられている。

この第1孔10の内面には絶縁膜2が形成され、絶縁膜2はSiO2膜にて形成されている。

【0025】

また、半導体基板1の第1孔10の絶縁膜2の上にはシード層3が設けられている。シード層3は半導体基板1の第2の面1b側から第1孔10の途中まで形成されている。シード層3の材料はCu、Auなどの金属膜が用いられる。

そして、第1孔10に金属材料としてCuが充填されて、半導体基板1の第1の面1aから第2の面1bにおよぶ貫通電極4が形成されている。さらに、電極パッド5の上部に端子7が形成されている。

なお、端子7の上にバンプなどの接続手段を形成してもよい。

【0026】

次に上記の半導体装置の製造方法について説明する。

図4(a)〜図4(d)は、実施形態2に係る貫通電極の形成プロセスを示す工程図である。本実施形態に係る貫通電極の製造方法について、これらの図を参照して説明する。なお、実施形態1と同一の構成部位については、同一の符号を使用し、重複する説明は省略する。

【0027】

図4(a)に示すように、半導体基板1の第1の面1aに電極パッド5が形成されている。ここではアルミパッドとし実施形態1と同様に半導体基板1の第1の面1aに第1孔10を形成し(第1の工程)、その第1孔10に絶縁膜2を成膜する(第2の工程)。

電極パッド5表面の絶縁膜2はフォトレジにより開口を形成しドライエッチング法により除去する。

【0028】

次に図4(b)に示すように、実施形態1と同様に半導体基板1の第2の面1b側から第2孔11を形成(第3の工程)し、シード層3の形成を行う(第4の工程)。

【0029】

次に図4(c)に示すように、半導体基板1の第1の面1aの電極パッド5上にメッキ端子形成用のレジスト6を形成し、実施形態1と同様に貫通電極4を形成する(第5の工程)。

【0030】

次に図4(d)に示すように、半導体基板1の第1の面1aにレジスト6を除去し端子7を形成する。さらに半導体基板1の第2の面1b側を研削により実施形態1と同様に薄型化を行う(第6の工程)。

【0031】

以上述べたように、本実施形態2に係る半導体装置の製造方法によれば、以下の効果を得ることができる。

半導体基板1上へ配線パターンを形成してある基板においても貫通電極4を形成することが可能であり、製品形態の拡大化が図れる。

【符号の説明】

【0032】

1…半導体基板、1a…第1の面、1b…第2の面、2…絶縁膜、3…シード層、4…貫通電極、4a…金属材料、5…電極パッド、6…レジスト、7…端子、8…絶縁膜、10…第1孔、11…第2孔、20…ビア。

【特許請求の範囲】

【請求項1】

半導体基板の厚み方向に貫通する貫通電極を有する半導体装置の製造方法であって、

前記半導体基板の第1の面から第1孔を開口する第1の工程と、

前記第1孔を含む前記半導体基板の前記第1の面に絶縁膜を形成する第2の工程と、

前記半導体基板の前記第1の面と反対の面である第2の面から、少なくとも2つの前記第1孔を含んで前記第1孔へ貫通する第2孔を開口する第3の工程と、

前記第2孔側よりスパッタ法によりシード層を成膜する第4の工程と、

前記シード層に金属材料をメッキ法により前記半導体基板の第1の面に達するまで前記第1孔を埋める第5の工程と、

前記半導体基板の前記第2の面を前記第2孔の深さ寸法より深く、厚み方向に研削する第6の工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第4の工程で成膜される前記シード層は、前記半導体基板の前記第2の面及び、前記第2孔の孔内及び前記第1孔の前記第2孔側の孔内に成膜することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の工程で開口される前記第1孔の大きさは、前記半導体基板の前記第1の面側と開口された孔の前記第2孔側まで同じ大きさ、または前記半導体基板の前記第1の面側より前記第2孔側の方が小さいことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項1】

半導体基板の厚み方向に貫通する貫通電極を有する半導体装置の製造方法であって、

前記半導体基板の第1の面から第1孔を開口する第1の工程と、

前記第1孔を含む前記半導体基板の前記第1の面に絶縁膜を形成する第2の工程と、

前記半導体基板の前記第1の面と反対の面である第2の面から、少なくとも2つの前記第1孔を含んで前記第1孔へ貫通する第2孔を開口する第3の工程と、

前記第2孔側よりスパッタ法によりシード層を成膜する第4の工程と、

前記シード層に金属材料をメッキ法により前記半導体基板の第1の面に達するまで前記第1孔を埋める第5の工程と、

前記半導体基板の前記第2の面を前記第2孔の深さ寸法より深く、厚み方向に研削する第6の工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第4の工程で成膜される前記シード層は、前記半導体基板の前記第2の面及び、前記第2孔の孔内及び前記第1孔の前記第2孔側の孔内に成膜することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の工程で開口される前記第1孔の大きさは、前記半導体基板の前記第1の面側と開口された孔の前記第2孔側まで同じ大きさ、または前記半導体基板の前記第1の面側より前記第2孔側の方が小さいことを特徴とする請求項1に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−21253(P2013−21253A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−155474(P2011−155474)

【出願日】平成23年7月14日(2011.7.14)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月14日(2011.7.14)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]