半導体装置の製造方法

【課題】 絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、凹部内に配線材料が埋め込まれた半導体装置の製造方法に関する。

【背景技術】

【0002】

マルチチップモジュール等の多層配線の形成に、一般的には、セミアディティブプロセスが適用される。以下、セミアディティブプロセスについて説明する。バリア膜上にシード膜を形成し、その上にレジスト膜を形成する。レジスト膜に、形成すべき配線パターンに整合する開口を形成する。この開口内を、無電解めっき法を用いて配線材料で埋め込む。その後、レジスト膜を除去する。さらに、めっきで形成された配線材料をエッチングマスクとして、シード膜及びバリア膜をエッチングする。これにより、シード膜及び配線材料からなる配線が形成される。配線の下には、バリア膜が配置される。この配線を覆うように、基板上に有機絶縁膜を形成する。

【0003】

配線が微細になると、特に配線幅が2μm以下になると、セミアディティブプロセスを適用して、安定して配線パターンを形成することが困難になる。微細な配線を形成するために、ダマシン法の適用が検討されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−85313号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

マルチチップモジュール等の多層配線の層間絶縁膜には、通常、有機絶縁膜が用いられる。有機絶縁膜に配線溝やビアホールを形成する際に、エッチングマスクとして無機材料からなるハードマスクが用いられる。ハードマスクと有機絶縁膜とのエッチング選択比を大きくする(ハードマスクを有機絶縁膜より高速にエッチングする)ことが困難である。このため、ハードマスクに開口を形成する際に、有機絶縁膜の表層部もエッチングされてしまう。このエッチングの深さは、面内でばらつきやすいため、配線溝等の深さのばらつきを小さくして、再現性よく配線溝を形成することが困難である。

【0006】

また、有機絶縁膜に配線溝等を形成する際に、等方性の高い条件でエッチングを行うと、配線溝の側壁がハードマスクの開口の縁から後退してしまう。逆に、異方性の高い条件でエッチングを行うと、配線溝の底面の外周部が過度にエッチングされてスパイク状の溝が形成される。このため、底面を平坦にすることが困難である。

【0007】

有機絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【課題を解決するための手段】

【0008】

本発明の一観点によると、

基板の上に、仮のパターンを形成する工程と、

前記仮のパターンを囲むように、前記基板の上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後、前記仮のパターンを除去する工程と、

前記仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する工程と、

前記シード膜の上に、配線材料を堆積させることにより、前記凹部を前記配線材料で埋め込む工程と

を有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

仮のパターンを除去することによって、層間絶縁膜に凹部が形成される。層間絶縁膜に対して、反応性イオンエッチング等による加工を行わないため、反応性イオンエッチングに起因して生じる種々の不都合を回避することができる。

【図面の簡単な説明】

【0010】

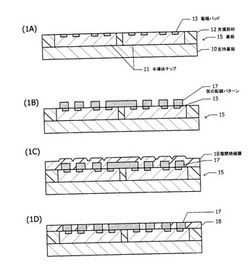

【図1−1】図1A〜図1Dは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図1−2】図1E〜図1Hは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図1−3】図1I〜図1Jは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図2−1】図2A〜図2Dは、実施例2による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図2−2】図2E〜図2Gは、実施例2による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図3】図3A〜図3Dは、実施例3による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−1】図4A〜図4Dは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−2】図4E〜図4Hは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−3】図4I〜図4Jは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図5】図5A〜図5Cは、実施例5による半導体装置の製造方法の製造途中段階における装置の断面図である。

【発明を実施するための形態】

【0011】

[実施例1]

図1A〜図1Jを参照して、実施例1による半導体装置の製造方法について説明する。

【0012】

図1Aに示すように、支持基板10の上面に、複数の半導体チップ11が搭載されている。半導体チップ11の間に、樹脂等の充填部材12が充填されている。半導体チップ11には、トランジスタ等の電子素子が形成されており、半導体チップ11の上面に、複数の電極パッド13が露出している。以下、支持基板10、半導体チップ11、及び充填部材12をまとめて。単に「基板」15ということとする。

【0013】

図1Bに示すように、基板15の上に、仮の配線パターン17を形成する。以下、仮の配線パターン17の形成方法について説明する。基板15の全面に、厚さ2μmのアルミニウム膜を、スパッタリング等により形成する。このアルミニウム膜を、例えば塩素系のガス(Cl2、BCl3、CCl4等)を用いた反応性イオンエッチングによりパターニングする。これにより、アルミニウムからなる仮の配線パターン17が形成される。

【0014】

なお、仮の配線パターン17に、アルミニウム以外の金属、例えばタングステン等の高融点金属を用いてもよいし、酸化シリコン等の無機絶縁材料を用いてもよい。仮の配線パターン17は、電極パッド13の上を通過する。一部の仮の配線パターン17は、複数の半導体チップ11に跨って、電極パッド13を相互に接続する。

【0015】

図1Cに示すように、仮の配線パターン17及び基板15の上に、有機絶縁材料からなる層間絶縁膜18を、塗布法により形成する。層間絶縁膜18は、仮の配線パターン17よりも厚くし、例えば3μmの厚さとする。層間絶縁膜18の有機絶縁材料の例として、ノボラック系樹脂、ポリイミド、フェノール樹脂、エポキシ樹脂、メチルシルスキオキサン等が挙げられる。

【0016】

図1Dに示すように、仮の配線パターン17が露出するまで、層間絶縁膜18に対して化学機械研磨(CMP)を施す。これにより、層間絶縁膜18の上面が平坦化される。図1C及び図1Dに示した工程で、仮の配線パターン17を囲むように、層間絶縁膜18が形成される。

【0017】

図1Eに示すように、仮の配線パターン17(図1D)を、薬液、例えば希硫酸、希塩酸等をもちいて除去する。仮の配線パターン17が占めていた領域に、配線溝(凹部)19が現れる。配線溝19の底面に、電極パッド13が露出する。電極パッド13には、仮の配線パターン17を除去するときに用いる薬液でエッチングされない導電材料、例えばCuが用いられる。

【0018】

仮の配線パターン17が酸化シリコンで形成される場合には、例えばフッ酸を用いて仮の配線パターン17を除去することができる。仮の配線パターン17がタングステンで形成される場合には、例えばフッ素ガスプラズマを用いて仮の配線パターン17を除去することができる。

【0019】

図1Fに示すように、配線溝19の側面と底面、及び層間絶縁膜18の上面に、バリア膜20を、スパッタリングにより形成する。バリア膜20には、例えば厚さ20nmのTi膜が用いられる。バリア膜20として、Tiの他に、TiB2、TiB、TiC、TiN、Zr、ZrB2、ZrB,ZrC、ZrN、Hf、HfB、HfC、HfN、V、VB2、VB、VC、VN、Nb、NbB2、NbB、NbC、NbN、Ta、TaB2、TaB、TaC、Ta4N5、Ta5N6、TaN、Ta2N、Cr、CrB2、Cr3C2、Cr2N、CrN、Mo、Mo2B3、MoB2、MoB、Mo2B、MoxCy、W、WxBy、WxCy、WxNy等を用いてもよい。

【0020】

バリア膜20の上に、シード膜21を、スパッタリングにより形成する。シード膜21には、例えば厚さ100nmのCu膜が用いられる。

【0021】

シード膜21の上に、めっき法を用いて配線材料23を堆積させる。配線材料23には、例えば厚さ2.5μmの銅(Cu)膜、または銅合金膜が用いられる。配線溝19が、配線材料23で埋め込まれる。

【0022】

平坦面上のバリア膜20が露出するまで、配線材料23及びシード膜21に化学機械研磨(CMP)を施す。さらに、露出したバリア膜20を、反応性イオンエッチングにより除去する。バリア膜20のエッチングには、例えば塩素系のガス、またはフッ素系のガスを用いることができる。これにより、配線溝19が形成されていない領域に、層間絶縁膜18が露出する。なお、反応性イオンエッチングによるバリア膜20のエッチングに代えて、CMPを用いてもよい。

【0023】

図1Gに、平坦面上のバリア膜20を除去した後の断面図を示す。配線溝19内に、シード膜21と配線材料23(図1F)とからなる配線25が残る。配線溝19の側面と底面には、バリア膜20が残る。

【0024】

図1Hに示すように、配線25の上面に、上部バリア膜26を形成する。上部バリア膜26には、例えばCoWP等が用いられる。上部バリア膜26の形成には、例えば無電解めっき法が用いられる。上部バリア膜26として、CoWPの他に、Co、CoP、CoW、CoB、CoWB、Ni、NiW、NiB、NiWP、NiWB等を用いてもよい。

【0025】

上部バリア膜26に代えて、銅のバリア機能を持つ絶縁材料、例えばSiN、SiC、SiOC等のバリア膜を用いてもよい。絶縁材料でバリア膜を形成する場合には、基板の全面にバリア膜が形成される。

【0026】

図1Iに示すように、層間絶縁膜18、配線25、上部バリア膜26の上に、コンタクトプラグ層を形成する。コンタクトプラグ層は、層間絶縁膜30、ビアホール31、バリア膜32、コンタクトプラグ33、及び上部バリア膜34を含む。層間絶縁膜30及びビアホール31の形成方法は、図1B〜図1Eに示した層間絶縁膜18及び配線溝19の形成方法と同一である。バリア膜32、コンタクトプラグ33、及び上部バリア膜34の形成方法は、図1F〜図1Hに示したバリア膜20、配線25、及び上部バリア膜26の形成方法と同一である。

【0027】

図1Jに示すように、層間絶縁膜30、コンタクトプラグ33、及び上部バリア膜34の上に、多層配線層を形成する。多層配線層の形成には、その下の配線25が配置される層、及びコンタクトプラグ33が配置される層の形成と同一の方法が適用される。

【0028】

多層配線層の上に、電極パッド40を形成する。電極パッド40が露出するように、多層配線層の表面を保護膜41で覆う。

【0029】

上記実施例1による方法では、有機絶縁材料からなる層間絶縁膜18に配線溝19(図1E)を形成する工程、及び層間絶縁膜30にビアホール31(図1I)を形成する工程が、有機絶縁材料に反応性イオンエッチングを適用する工程を含まない。このため、有機絶縁材料をエッチングする際に生じやすい深さのばらつき、横方向へのエッチングに起因する配線溝の幅の拡大、凹部の底面に形成されるスパイク状の溝の発生等を防止し、配線溝の深さの面内に関するばらつきを抑制することができる。これにより、配線の寸法精度を高めることができる。

【0030】

図1Hに示した段階で、層間絶縁膜18の表層部が除去されて、層間絶縁膜18の上面が配線25の上面よりも低くなる場合がある。ただし、図1Iに示した層間絶縁膜30を形成するための塗布工程において、低くなった層間絶縁膜18の上に層間絶縁膜30の材料が供給される。このように、層間絶縁膜18の上面が低くなっても、後の塗布工程で絶縁材料が補填されるため、問題は生じない。

【0031】

上記実施例1では、配線25(図1J)及びその上に形成される多層配線の基板15として、支持基板10の上に複数の半導体チップ11を搭載した基板を用いた。実施例1による方法は、単一の半導体チップの上に配線層を形成する工程にも適用可能である。この場合には、複数の半導体チップに分割する前のウエハ状態のときに、実施例1による方法で多層配線が形成される。

【0032】

[実施例2]

図2A〜図2Gを参照して、実施例2による半導体装置の製造方法について説明する。

【0033】

図2Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。基板15の上に、仮の配線パターン17を形成する。仮の配線パターン17の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0034】

仮の配線パターン17の側面と上面、及び基板15の露出した表面に、バリア膜50を形成する。バリア膜50には、例えば厚さ50nmのTiN膜が用いられる。バリア膜50の形成には、例えばスパッタリング、化学気相成長(CVD)等が適用される。

【0035】

図2Bに示すように、バリア膜50(図2A)を異方性エッチングすることにより、仮の配線パターン17の側面にのみバリア膜50を残す。この異方性エッチングには、たとえばCCl4等の塩素系のエッチングガスを用いることができる。異方性エッチング後、仮の配線パターン17の上面、及び基板15の上面が露出する。

【0036】

バリア膜50には、TiNの他に、銅の拡散を防止する他の導電性または絶縁性の材料を用いることができる。仮の配線パターン17として導電性の材料を用いる場合には、無電解めっき法により、仮の配線パターン17の側面と上面のみに、選択的にバリア膜50を堆積させることも可能である。無電解めっき法を適用する場合には、バリア膜50の材料として、上部バリア膜26(図1H)に用いることができる材料、例えばCoWP、NiP等を用いることができる。バリア膜50に用いることができる絶縁材料として、SiN、SiOC等が挙げられる。

【0037】

図2Cに示すように、仮の配線パターン17が形成されていない領域の基板15の上に、層間絶縁膜18を形成する。層間絶縁膜18の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。層間絶縁膜18を形成した後、仮の配線パターン17を除去する。

【0038】

図2Dに、仮の配線パターン17(図2C)を除去した後の断面図を示す。仮の配線パターン17が形成されていた領域に、配線溝19が現れる。配線溝19の側面には、バリア膜50が残っている。

【0039】

図2Eに示すように、配線溝19の底面と側面、及び層間絶縁膜18の上面に、バリア膜20を形成する。バリア膜20の上に、シード膜21を形成する。さらに、シード膜21の上に、配線材料23を堆積させる。バリア膜20及びシード膜21の形成方法は、図1Fに示したバリア膜20及びシード膜21の形成方法と同一である。配線材料23の堆積方法は、図1Fに示した配線材料23の堆積方法と同一である。

【0040】

図2Fに示すように、余分なバリア膜20、シード膜21、及び配線材料23を、CMPにより除去する。これらの除去方法は、図1Fの構造から図1Gの構造に至るまでの工程と同一である。配線溝19内に、シード膜21及び導電材料23からなる配線25が残る。配線25の側面及び底面に、バリア膜20が残存する。

【0041】

図2Gに示すように、配線25の上面に、上部バリア膜26を形成する。上部バリア膜26の形成方法は、図1Hに示した上部バリア膜26の形成方法と同一である。

【0042】

上記実施例1においては、配線25と層間絶縁膜18との間には、1層のバリア膜20(図1H)が配置されていた。実施例2においては、配線25と層間絶縁膜18との間に、バリア膜20に加えて、バリア膜50も配置されている。

【0043】

バリア膜20をスパッタリングで成膜する場合、配線溝19の側面に形成されるバリア膜20が、配線溝19の底面や層間絶縁膜18の上面に形成されるバリア膜20より薄くなりやすい。実施例2では、バリア膜20の薄い領域を、バリア膜50で補強することにより、銅の拡散防止機能を高め、より高い信頼性を確保することができる。

【0044】

[実施例3]

図3A〜図3Dを参照して、実施例3による半導体装置の製造方法について説明する。

【0045】

図3Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。

【0046】

基板15の上に、下地バリア膜55aを形成する。下地バリア膜55aは、例えば、厚さ20nmのTi膜と厚さ100nmのTiN膜とがこの順番に積層された2層構造を有する。下地バリア膜55aとして、その他に銅の拡散防止機能を有する高融点金属膜を用いてもよい。下地バリア膜55aの上に、厚さ2μmのアルミニウム膜17aを、例えばスパッタリングにより形成する。

【0047】

図3Bに示すように、アルミニウム膜17a(図3A)及び下地バリア膜55a(図3A)をパターニングすることにより、仮の配線パターン17及び下地バリア膜55を形成する。アルミニウム膜17a及び下地バリア膜55aのエッチングには、例えばCl2、BCl3、CCl4等の塩素系ガスを用いた反応性イオンエッチングを適用することができる。

【0048】

図3Cに示すように、仮の配線パターン17の側面と上面、及び仮の配線パターン17が形成されていない領域の基板15の上面に、バリア膜50を形成する。バリア膜50の形成方法は、図2Aに示したバリア膜50の形成方法と同一である。図2Aでは、基板15の上に仮の配線パターン17が直接形成されているが、図3Cでは、仮の配線パターン17と基板15との間に下地バリア膜55が配置されている。その他の点では、両者の構造は同一である。実施例3においても、実施例2の図2Bから図2Gまでの工程と同一の工程を実行する。

【0049】

図3Dに、これらの工程を実行した後の半導体装置の断面図を示す。実施例2では、配線25と基板15との間に、1層のバリア膜20のみが配置されていた。実施例3においては、配線25と基板15との間に、バリア膜20に加えて、下地バリア膜55も配置されている。このため、実施例2の構造に比べて、実施例3では、銅の拡散防止機能を高め、より高い信頼性を確保することができる。

【0050】

実施例3においては、配線25の下方に、2層のバリア膜20、55が配置され、側方にも2層のバリア膜20、50が配置されている。下地バリア膜55と、側方のバリア膜50とで十分な拡散防止機能が得られる場合には、バリア膜20の形成を省略してもよい。

【0051】

[実施例4]

図4A〜図4Jを参照して、実施例4による半導体装置の製造方法について説明する。

【0052】

図4Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。基板15の上に、仮のプラグパターン60を形成する。仮のプラグパターン60は、半導体チップ11の電極パッド13と重なる位置に形成される。仮のプラグパターン60の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0053】

図4Bに示すように、仮のプラグパターン60の側面に、バリア膜61を形成する。バリア膜61の形成方法は、図2A〜図2Bに示したバリア膜50の形成方法と同一である。

【0054】

図4Cに示すように、仮のプラグパターン60が形成されていない領域の基板15の上に、層間絶縁膜62を形成する。層間絶縁膜62の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。

【0055】

図4Dに示すように、層間絶縁膜62及び仮のプラグパターン60の上に、仮の配線パターン17を形成する。仮の配線パターン17は、仮のプラグパターン60の上を通過する。仮の配線パターン17の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0056】

図4Eに示すように、仮の配線パターン17の側面に、バリア膜50を形成する。バリア膜50の形成方法は、図2A〜図2Bに示したバリア膜50の形成方法と同一である。

【0057】

図4Fに示すように、仮の配線パターン17が形成されていない領域の層間絶縁膜62の上に、層間絶縁膜18を形成する。層間絶縁膜18の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。

【0058】

図4Gに示すように、仮の配線パターン17(図4F)及び仮のプラグパターン60(図4F)を除去する。仮の配線パターン17及び仮のプラグパターン60の除去方法は、図1Dに示した仮の配線パターン17の除去方法と同一である。仮のプラグパターン60が形成されていた領域にビアホール63が現れ、仮の配線パターン17が形成されていた領域に配線溝19が現れる。ビアホール63の側面には、バリア膜61が残存し、配線溝19の側面には、バリア膜50が残存する。

【0059】

図4Hに示すように、ビアホール63の側面と底面、配線溝19の側面と底面、及び層間絶縁膜18の上面に、バリア膜20を形成する。さらに、その上に、シード膜21を形成する。バリア膜20及びシード膜21の形成方法は、図1Fに示したバリア膜20及びシード膜21の形成方法と同一である。

【0060】

図4Iに示すように、シード膜21の上に、配線材料23を堆積させる。配線材料23の堆積方法は、図1Fに示した配線材料23の堆積方法と同一である。ビアホール63及び配線溝19が、配線材料23で埋め込まれる。

【0061】

図1Jに示すように、層間絶縁膜18の上面よりも上方に堆積している余分な配線材料23、シード膜21、バリア膜20を除去する。これらの膜の除去方法は、図1Gに示した工程において、図1Fの配線材料23、シード膜21、及びバリア膜20を除去した方法と同一である。

【0062】

ビアホール63及び配線溝19内に、シード膜21と配線材料23(図4I)とからなる配線25が残る。配線25は、基板15の面内方向に延びる配線部分と、半導体チップ11の電極パッド13に接続するためのコンタクトプラグとを含む。コンタクトプラグと配線とを異なる工程で形成する場合に比べて、工程数の削減を図ることができる。

【0063】

配線25と層間絶縁膜62との間に、2層のバリア膜20と61が配置され、配線25と層間絶縁膜18との間にも、2層のバリア膜20と50が配置されている。このため、銅の拡散防止機能を高め、信頼性の向上を図ることができる。

【0064】

実施例4によるコンタクトプラグ及び配線の形成方法は、図1Iに示した層間絶縁膜18及び配線25の上の多層配線の形成に適用することも可能である。

【0065】

[実施例5]

図5A〜図5Cを参照して、実施例5による半導体装置の製造方法について説明する。以下、図4A〜図4Jに示した実施例4との相違点にについて説明し、同一の構成については説明を省略する。

【0066】

図5Aに示すように、基板15の上に、下地バリア膜65及び仮のプラグパターン60を形成する。下地バリア膜65及び仮のプラグパターン60の形成方法は、図3A〜図3Bに示した下地バリア膜55及び仮の配線パターン17の形成方法と同一である。図5Aの構造を、図4Aに示した実施例4の構造と比較すると、実施例5では、仮のプラグパターン60の下に下地バリア膜65が配置されている。その他の点では、両者の構造は同一である。

【0067】

図5Bに、実施例4の図4Gに示した段階に対応する段階における装置の断面図を示す。実施例5では、図5Bに示すように、ビアホール63の底面に下地バリア膜65が残留している。その他の点では、両者の構造は同一である。

【0068】

図5Cに、実施例4の図4Jに示した段階に対応する段階における装置の断面図を示す。実施例4では、図4Jに示したように、配線25と基板15との間に、1層のバリア膜20が配置されていた。実施例5では、図5Cに示すように、配線25と基板15との間に、バリア膜20に加えて、下地バリア膜65も配置されている。このため、銅の拡散防止機能を高め、信頼性の向上を図ることができる。

【0069】

実施例4によるコンタクトプラグ及び配線の形成方法は、図1Iに示した層間絶縁膜18及び配線25の上の多層配線の形成に適用することも可能である。

【0070】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0071】

10 支持基板

11 半導体チップ

12 充填部材

13 電極パッド

15 基板

17 仮の配線パターン

18 層間絶縁膜

19 配線溝(凹部)

20 バリア膜

21 シード膜

23 配線材料

25 配線

26 上部バリア膜

30 層間絶縁膜

31 ビアホール

32 バリア膜

33 コンタクトプラグ

34 上部バリア膜

40 電極パッド

41 保護膜

50 バリア膜

55 下地バリア膜

60 仮のプラグパターン

61 バリア膜

62 層間絶縁膜

63 ビアホール

65 下地バリア膜

【技術分野】

【0001】

本発明は、凹部内に配線材料が埋め込まれた半導体装置の製造方法に関する。

【背景技術】

【0002】

マルチチップモジュール等の多層配線の形成に、一般的には、セミアディティブプロセスが適用される。以下、セミアディティブプロセスについて説明する。バリア膜上にシード膜を形成し、その上にレジスト膜を形成する。レジスト膜に、形成すべき配線パターンに整合する開口を形成する。この開口内を、無電解めっき法を用いて配線材料で埋め込む。その後、レジスト膜を除去する。さらに、めっきで形成された配線材料をエッチングマスクとして、シード膜及びバリア膜をエッチングする。これにより、シード膜及び配線材料からなる配線が形成される。配線の下には、バリア膜が配置される。この配線を覆うように、基板上に有機絶縁膜を形成する。

【0003】

配線が微細になると、特に配線幅が2μm以下になると、セミアディティブプロセスを適用して、安定して配線パターンを形成することが困難になる。微細な配線を形成するために、ダマシン法の適用が検討されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−85313号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

マルチチップモジュール等の多層配線の層間絶縁膜には、通常、有機絶縁膜が用いられる。有機絶縁膜に配線溝やビアホールを形成する際に、エッチングマスクとして無機材料からなるハードマスクが用いられる。ハードマスクと有機絶縁膜とのエッチング選択比を大きくする(ハードマスクを有機絶縁膜より高速にエッチングする)ことが困難である。このため、ハードマスクに開口を形成する際に、有機絶縁膜の表層部もエッチングされてしまう。このエッチングの深さは、面内でばらつきやすいため、配線溝等の深さのばらつきを小さくして、再現性よく配線溝を形成することが困難である。

【0006】

また、有機絶縁膜に配線溝等を形成する際に、等方性の高い条件でエッチングを行うと、配線溝の側壁がハードマスクの開口の縁から後退してしまう。逆に、異方性の高い条件でエッチングを行うと、配線溝の底面の外周部が過度にエッチングされてスパイク状の溝が形成される。このため、底面を平坦にすることが困難である。

【0007】

有機絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【課題を解決するための手段】

【0008】

本発明の一観点によると、

基板の上に、仮のパターンを形成する工程と、

前記仮のパターンを囲むように、前記基板の上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後、前記仮のパターンを除去する工程と、

前記仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する工程と、

前記シード膜の上に、配線材料を堆積させることにより、前記凹部を前記配線材料で埋め込む工程と

を有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

仮のパターンを除去することによって、層間絶縁膜に凹部が形成される。層間絶縁膜に対して、反応性イオンエッチング等による加工を行わないため、反応性イオンエッチングに起因して生じる種々の不都合を回避することができる。

【図面の簡単な説明】

【0010】

【図1−1】図1A〜図1Dは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図1−2】図1E〜図1Hは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図1−3】図1I〜図1Jは、実施例1による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図2−1】図2A〜図2Dは、実施例2による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図2−2】図2E〜図2Gは、実施例2による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図3】図3A〜図3Dは、実施例3による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−1】図4A〜図4Dは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−2】図4E〜図4Hは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図4−3】図4I〜図4Jは、実施例4による半導体装置の製造方法の製造途中段階における装置の断面図である。

【図5】図5A〜図5Cは、実施例5による半導体装置の製造方法の製造途中段階における装置の断面図である。

【発明を実施するための形態】

【0011】

[実施例1]

図1A〜図1Jを参照して、実施例1による半導体装置の製造方法について説明する。

【0012】

図1Aに示すように、支持基板10の上面に、複数の半導体チップ11が搭載されている。半導体チップ11の間に、樹脂等の充填部材12が充填されている。半導体チップ11には、トランジスタ等の電子素子が形成されており、半導体チップ11の上面に、複数の電極パッド13が露出している。以下、支持基板10、半導体チップ11、及び充填部材12をまとめて。単に「基板」15ということとする。

【0013】

図1Bに示すように、基板15の上に、仮の配線パターン17を形成する。以下、仮の配線パターン17の形成方法について説明する。基板15の全面に、厚さ2μmのアルミニウム膜を、スパッタリング等により形成する。このアルミニウム膜を、例えば塩素系のガス(Cl2、BCl3、CCl4等)を用いた反応性イオンエッチングによりパターニングする。これにより、アルミニウムからなる仮の配線パターン17が形成される。

【0014】

なお、仮の配線パターン17に、アルミニウム以外の金属、例えばタングステン等の高融点金属を用いてもよいし、酸化シリコン等の無機絶縁材料を用いてもよい。仮の配線パターン17は、電極パッド13の上を通過する。一部の仮の配線パターン17は、複数の半導体チップ11に跨って、電極パッド13を相互に接続する。

【0015】

図1Cに示すように、仮の配線パターン17及び基板15の上に、有機絶縁材料からなる層間絶縁膜18を、塗布法により形成する。層間絶縁膜18は、仮の配線パターン17よりも厚くし、例えば3μmの厚さとする。層間絶縁膜18の有機絶縁材料の例として、ノボラック系樹脂、ポリイミド、フェノール樹脂、エポキシ樹脂、メチルシルスキオキサン等が挙げられる。

【0016】

図1Dに示すように、仮の配線パターン17が露出するまで、層間絶縁膜18に対して化学機械研磨(CMP)を施す。これにより、層間絶縁膜18の上面が平坦化される。図1C及び図1Dに示した工程で、仮の配線パターン17を囲むように、層間絶縁膜18が形成される。

【0017】

図1Eに示すように、仮の配線パターン17(図1D)を、薬液、例えば希硫酸、希塩酸等をもちいて除去する。仮の配線パターン17が占めていた領域に、配線溝(凹部)19が現れる。配線溝19の底面に、電極パッド13が露出する。電極パッド13には、仮の配線パターン17を除去するときに用いる薬液でエッチングされない導電材料、例えばCuが用いられる。

【0018】

仮の配線パターン17が酸化シリコンで形成される場合には、例えばフッ酸を用いて仮の配線パターン17を除去することができる。仮の配線パターン17がタングステンで形成される場合には、例えばフッ素ガスプラズマを用いて仮の配線パターン17を除去することができる。

【0019】

図1Fに示すように、配線溝19の側面と底面、及び層間絶縁膜18の上面に、バリア膜20を、スパッタリングにより形成する。バリア膜20には、例えば厚さ20nmのTi膜が用いられる。バリア膜20として、Tiの他に、TiB2、TiB、TiC、TiN、Zr、ZrB2、ZrB,ZrC、ZrN、Hf、HfB、HfC、HfN、V、VB2、VB、VC、VN、Nb、NbB2、NbB、NbC、NbN、Ta、TaB2、TaB、TaC、Ta4N5、Ta5N6、TaN、Ta2N、Cr、CrB2、Cr3C2、Cr2N、CrN、Mo、Mo2B3、MoB2、MoB、Mo2B、MoxCy、W、WxBy、WxCy、WxNy等を用いてもよい。

【0020】

バリア膜20の上に、シード膜21を、スパッタリングにより形成する。シード膜21には、例えば厚さ100nmのCu膜が用いられる。

【0021】

シード膜21の上に、めっき法を用いて配線材料23を堆積させる。配線材料23には、例えば厚さ2.5μmの銅(Cu)膜、または銅合金膜が用いられる。配線溝19が、配線材料23で埋め込まれる。

【0022】

平坦面上のバリア膜20が露出するまで、配線材料23及びシード膜21に化学機械研磨(CMP)を施す。さらに、露出したバリア膜20を、反応性イオンエッチングにより除去する。バリア膜20のエッチングには、例えば塩素系のガス、またはフッ素系のガスを用いることができる。これにより、配線溝19が形成されていない領域に、層間絶縁膜18が露出する。なお、反応性イオンエッチングによるバリア膜20のエッチングに代えて、CMPを用いてもよい。

【0023】

図1Gに、平坦面上のバリア膜20を除去した後の断面図を示す。配線溝19内に、シード膜21と配線材料23(図1F)とからなる配線25が残る。配線溝19の側面と底面には、バリア膜20が残る。

【0024】

図1Hに示すように、配線25の上面に、上部バリア膜26を形成する。上部バリア膜26には、例えばCoWP等が用いられる。上部バリア膜26の形成には、例えば無電解めっき法が用いられる。上部バリア膜26として、CoWPの他に、Co、CoP、CoW、CoB、CoWB、Ni、NiW、NiB、NiWP、NiWB等を用いてもよい。

【0025】

上部バリア膜26に代えて、銅のバリア機能を持つ絶縁材料、例えばSiN、SiC、SiOC等のバリア膜を用いてもよい。絶縁材料でバリア膜を形成する場合には、基板の全面にバリア膜が形成される。

【0026】

図1Iに示すように、層間絶縁膜18、配線25、上部バリア膜26の上に、コンタクトプラグ層を形成する。コンタクトプラグ層は、層間絶縁膜30、ビアホール31、バリア膜32、コンタクトプラグ33、及び上部バリア膜34を含む。層間絶縁膜30及びビアホール31の形成方法は、図1B〜図1Eに示した層間絶縁膜18及び配線溝19の形成方法と同一である。バリア膜32、コンタクトプラグ33、及び上部バリア膜34の形成方法は、図1F〜図1Hに示したバリア膜20、配線25、及び上部バリア膜26の形成方法と同一である。

【0027】

図1Jに示すように、層間絶縁膜30、コンタクトプラグ33、及び上部バリア膜34の上に、多層配線層を形成する。多層配線層の形成には、その下の配線25が配置される層、及びコンタクトプラグ33が配置される層の形成と同一の方法が適用される。

【0028】

多層配線層の上に、電極パッド40を形成する。電極パッド40が露出するように、多層配線層の表面を保護膜41で覆う。

【0029】

上記実施例1による方法では、有機絶縁材料からなる層間絶縁膜18に配線溝19(図1E)を形成する工程、及び層間絶縁膜30にビアホール31(図1I)を形成する工程が、有機絶縁材料に反応性イオンエッチングを適用する工程を含まない。このため、有機絶縁材料をエッチングする際に生じやすい深さのばらつき、横方向へのエッチングに起因する配線溝の幅の拡大、凹部の底面に形成されるスパイク状の溝の発生等を防止し、配線溝の深さの面内に関するばらつきを抑制することができる。これにより、配線の寸法精度を高めることができる。

【0030】

図1Hに示した段階で、層間絶縁膜18の表層部が除去されて、層間絶縁膜18の上面が配線25の上面よりも低くなる場合がある。ただし、図1Iに示した層間絶縁膜30を形成するための塗布工程において、低くなった層間絶縁膜18の上に層間絶縁膜30の材料が供給される。このように、層間絶縁膜18の上面が低くなっても、後の塗布工程で絶縁材料が補填されるため、問題は生じない。

【0031】

上記実施例1では、配線25(図1J)及びその上に形成される多層配線の基板15として、支持基板10の上に複数の半導体チップ11を搭載した基板を用いた。実施例1による方法は、単一の半導体チップの上に配線層を形成する工程にも適用可能である。この場合には、複数の半導体チップに分割する前のウエハ状態のときに、実施例1による方法で多層配線が形成される。

【0032】

[実施例2]

図2A〜図2Gを参照して、実施例2による半導体装置の製造方法について説明する。

【0033】

図2Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。基板15の上に、仮の配線パターン17を形成する。仮の配線パターン17の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0034】

仮の配線パターン17の側面と上面、及び基板15の露出した表面に、バリア膜50を形成する。バリア膜50には、例えば厚さ50nmのTiN膜が用いられる。バリア膜50の形成には、例えばスパッタリング、化学気相成長(CVD)等が適用される。

【0035】

図2Bに示すように、バリア膜50(図2A)を異方性エッチングすることにより、仮の配線パターン17の側面にのみバリア膜50を残す。この異方性エッチングには、たとえばCCl4等の塩素系のエッチングガスを用いることができる。異方性エッチング後、仮の配線パターン17の上面、及び基板15の上面が露出する。

【0036】

バリア膜50には、TiNの他に、銅の拡散を防止する他の導電性または絶縁性の材料を用いることができる。仮の配線パターン17として導電性の材料を用いる場合には、無電解めっき法により、仮の配線パターン17の側面と上面のみに、選択的にバリア膜50を堆積させることも可能である。無電解めっき法を適用する場合には、バリア膜50の材料として、上部バリア膜26(図1H)に用いることができる材料、例えばCoWP、NiP等を用いることができる。バリア膜50に用いることができる絶縁材料として、SiN、SiOC等が挙げられる。

【0037】

図2Cに示すように、仮の配線パターン17が形成されていない領域の基板15の上に、層間絶縁膜18を形成する。層間絶縁膜18の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。層間絶縁膜18を形成した後、仮の配線パターン17を除去する。

【0038】

図2Dに、仮の配線パターン17(図2C)を除去した後の断面図を示す。仮の配線パターン17が形成されていた領域に、配線溝19が現れる。配線溝19の側面には、バリア膜50が残っている。

【0039】

図2Eに示すように、配線溝19の底面と側面、及び層間絶縁膜18の上面に、バリア膜20を形成する。バリア膜20の上に、シード膜21を形成する。さらに、シード膜21の上に、配線材料23を堆積させる。バリア膜20及びシード膜21の形成方法は、図1Fに示したバリア膜20及びシード膜21の形成方法と同一である。配線材料23の堆積方法は、図1Fに示した配線材料23の堆積方法と同一である。

【0040】

図2Fに示すように、余分なバリア膜20、シード膜21、及び配線材料23を、CMPにより除去する。これらの除去方法は、図1Fの構造から図1Gの構造に至るまでの工程と同一である。配線溝19内に、シード膜21及び導電材料23からなる配線25が残る。配線25の側面及び底面に、バリア膜20が残存する。

【0041】

図2Gに示すように、配線25の上面に、上部バリア膜26を形成する。上部バリア膜26の形成方法は、図1Hに示した上部バリア膜26の形成方法と同一である。

【0042】

上記実施例1においては、配線25と層間絶縁膜18との間には、1層のバリア膜20(図1H)が配置されていた。実施例2においては、配線25と層間絶縁膜18との間に、バリア膜20に加えて、バリア膜50も配置されている。

【0043】

バリア膜20をスパッタリングで成膜する場合、配線溝19の側面に形成されるバリア膜20が、配線溝19の底面や層間絶縁膜18の上面に形成されるバリア膜20より薄くなりやすい。実施例2では、バリア膜20の薄い領域を、バリア膜50で補強することにより、銅の拡散防止機能を高め、より高い信頼性を確保することができる。

【0044】

[実施例3]

図3A〜図3Dを参照して、実施例3による半導体装置の製造方法について説明する。

【0045】

図3Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。

【0046】

基板15の上に、下地バリア膜55aを形成する。下地バリア膜55aは、例えば、厚さ20nmのTi膜と厚さ100nmのTiN膜とがこの順番に積層された2層構造を有する。下地バリア膜55aとして、その他に銅の拡散防止機能を有する高融点金属膜を用いてもよい。下地バリア膜55aの上に、厚さ2μmのアルミニウム膜17aを、例えばスパッタリングにより形成する。

【0047】

図3Bに示すように、アルミニウム膜17a(図3A)及び下地バリア膜55a(図3A)をパターニングすることにより、仮の配線パターン17及び下地バリア膜55を形成する。アルミニウム膜17a及び下地バリア膜55aのエッチングには、例えばCl2、BCl3、CCl4等の塩素系ガスを用いた反応性イオンエッチングを適用することができる。

【0048】

図3Cに示すように、仮の配線パターン17の側面と上面、及び仮の配線パターン17が形成されていない領域の基板15の上面に、バリア膜50を形成する。バリア膜50の形成方法は、図2Aに示したバリア膜50の形成方法と同一である。図2Aでは、基板15の上に仮の配線パターン17が直接形成されているが、図3Cでは、仮の配線パターン17と基板15との間に下地バリア膜55が配置されている。その他の点では、両者の構造は同一である。実施例3においても、実施例2の図2Bから図2Gまでの工程と同一の工程を実行する。

【0049】

図3Dに、これらの工程を実行した後の半導体装置の断面図を示す。実施例2では、配線25と基板15との間に、1層のバリア膜20のみが配置されていた。実施例3においては、配線25と基板15との間に、バリア膜20に加えて、下地バリア膜55も配置されている。このため、実施例2の構造に比べて、実施例3では、銅の拡散防止機能を高め、より高い信頼性を確保することができる。

【0050】

実施例3においては、配線25の下方に、2層のバリア膜20、55が配置され、側方にも2層のバリア膜20、50が配置されている。下地バリア膜55と、側方のバリア膜50とで十分な拡散防止機能が得られる場合には、バリア膜20の形成を省略してもよい。

【0051】

[実施例4]

図4A〜図4Jを参照して、実施例4による半導体装置の製造方法について説明する。

【0052】

図4Aに示した基板15は、支持基板10、半導体チップ11、及び充填部材12を含み、実施例1で用いられた基板15(図1A)と同一の構造を有する。基板15の上に、仮のプラグパターン60を形成する。仮のプラグパターン60は、半導体チップ11の電極パッド13と重なる位置に形成される。仮のプラグパターン60の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0053】

図4Bに示すように、仮のプラグパターン60の側面に、バリア膜61を形成する。バリア膜61の形成方法は、図2A〜図2Bに示したバリア膜50の形成方法と同一である。

【0054】

図4Cに示すように、仮のプラグパターン60が形成されていない領域の基板15の上に、層間絶縁膜62を形成する。層間絶縁膜62の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。

【0055】

図4Dに示すように、層間絶縁膜62及び仮のプラグパターン60の上に、仮の配線パターン17を形成する。仮の配線パターン17は、仮のプラグパターン60の上を通過する。仮の配線パターン17の形成方法は、図1Bに示した仮の配線パターン17の形成方法と同一である。

【0056】

図4Eに示すように、仮の配線パターン17の側面に、バリア膜50を形成する。バリア膜50の形成方法は、図2A〜図2Bに示したバリア膜50の形成方法と同一である。

【0057】

図4Fに示すように、仮の配線パターン17が形成されていない領域の層間絶縁膜62の上に、層間絶縁膜18を形成する。層間絶縁膜18の形成方法は、図1C〜図1Dに示した層間絶縁膜18の形成方法と同一である。

【0058】

図4Gに示すように、仮の配線パターン17(図4F)及び仮のプラグパターン60(図4F)を除去する。仮の配線パターン17及び仮のプラグパターン60の除去方法は、図1Dに示した仮の配線パターン17の除去方法と同一である。仮のプラグパターン60が形成されていた領域にビアホール63が現れ、仮の配線パターン17が形成されていた領域に配線溝19が現れる。ビアホール63の側面には、バリア膜61が残存し、配線溝19の側面には、バリア膜50が残存する。

【0059】

図4Hに示すように、ビアホール63の側面と底面、配線溝19の側面と底面、及び層間絶縁膜18の上面に、バリア膜20を形成する。さらに、その上に、シード膜21を形成する。バリア膜20及びシード膜21の形成方法は、図1Fに示したバリア膜20及びシード膜21の形成方法と同一である。

【0060】

図4Iに示すように、シード膜21の上に、配線材料23を堆積させる。配線材料23の堆積方法は、図1Fに示した配線材料23の堆積方法と同一である。ビアホール63及び配線溝19が、配線材料23で埋め込まれる。

【0061】

図1Jに示すように、層間絶縁膜18の上面よりも上方に堆積している余分な配線材料23、シード膜21、バリア膜20を除去する。これらの膜の除去方法は、図1Gに示した工程において、図1Fの配線材料23、シード膜21、及びバリア膜20を除去した方法と同一である。

【0062】

ビアホール63及び配線溝19内に、シード膜21と配線材料23(図4I)とからなる配線25が残る。配線25は、基板15の面内方向に延びる配線部分と、半導体チップ11の電極パッド13に接続するためのコンタクトプラグとを含む。コンタクトプラグと配線とを異なる工程で形成する場合に比べて、工程数の削減を図ることができる。

【0063】

配線25と層間絶縁膜62との間に、2層のバリア膜20と61が配置され、配線25と層間絶縁膜18との間にも、2層のバリア膜20と50が配置されている。このため、銅の拡散防止機能を高め、信頼性の向上を図ることができる。

【0064】

実施例4によるコンタクトプラグ及び配線の形成方法は、図1Iに示した層間絶縁膜18及び配線25の上の多層配線の形成に適用することも可能である。

【0065】

[実施例5]

図5A〜図5Cを参照して、実施例5による半導体装置の製造方法について説明する。以下、図4A〜図4Jに示した実施例4との相違点にについて説明し、同一の構成については説明を省略する。

【0066】

図5Aに示すように、基板15の上に、下地バリア膜65及び仮のプラグパターン60を形成する。下地バリア膜65及び仮のプラグパターン60の形成方法は、図3A〜図3Bに示した下地バリア膜55及び仮の配線パターン17の形成方法と同一である。図5Aの構造を、図4Aに示した実施例4の構造と比較すると、実施例5では、仮のプラグパターン60の下に下地バリア膜65が配置されている。その他の点では、両者の構造は同一である。

【0067】

図5Bに、実施例4の図4Gに示した段階に対応する段階における装置の断面図を示す。実施例5では、図5Bに示すように、ビアホール63の底面に下地バリア膜65が残留している。その他の点では、両者の構造は同一である。

【0068】

図5Cに、実施例4の図4Jに示した段階に対応する段階における装置の断面図を示す。実施例4では、図4Jに示したように、配線25と基板15との間に、1層のバリア膜20が配置されていた。実施例5では、図5Cに示すように、配線25と基板15との間に、バリア膜20に加えて、下地バリア膜65も配置されている。このため、銅の拡散防止機能を高め、信頼性の向上を図ることができる。

【0069】

実施例4によるコンタクトプラグ及び配線の形成方法は、図1Iに示した層間絶縁膜18及び配線25の上の多層配線の形成に適用することも可能である。

【0070】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0071】

10 支持基板

11 半導体チップ

12 充填部材

13 電極パッド

15 基板

17 仮の配線パターン

18 層間絶縁膜

19 配線溝(凹部)

20 バリア膜

21 シード膜

23 配線材料

25 配線

26 上部バリア膜

30 層間絶縁膜

31 ビアホール

32 バリア膜

33 コンタクトプラグ

34 上部バリア膜

40 電極パッド

41 保護膜

50 バリア膜

55 下地バリア膜

60 仮のプラグパターン

61 バリア膜

62 層間絶縁膜

63 ビアホール

65 下地バリア膜

【特許請求の範囲】

【請求項1】

基板の上に、仮のパターンを形成する工程と、

前記仮のパターンを囲むように、前記基板の上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後、前記仮のパターンを除去する工程と、

前記仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する工程と、

前記シード膜の上に、配線材料を堆積させることにより、前記凹部を前記配線材料で埋め込む工程と

を有する半導体装置の製造方法。

【請求項2】

前記層間絶縁膜を形成する前に、前記仮のパターンの側面に、第2のバリア膜を形成する工程を、さらに有し、

前記仮のパターンを除去する工程において、前記第2のバリア膜は残す請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第2のバリア膜を形成する工程において、

前記仮のパターンの側面及び上面に、前記第2のバリア膜を形成した後、異方性の反応性イオンエッチングを施すことにより、前記仮のパターンの上面に形成された前記第2のバリア膜を除去し、前記パターンの側面には、前記第2のバリア膜を残す請求項2に記載の半導体装置の製造方法。

【請求項4】

前記仮のパターンを形成する前に、前記基板の上に下地バリア膜を形成する工程を、さらに有し、

前記仮のパターンは、前記下地バリア膜の上に形成し、

前記仮のパターンを形成した後、前記層間絶縁膜を形成する前に、前記仮のパターンが形成されていない領域の前記下地バリア膜を除去する工程を、さらに有する請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

基板の上に、仮のパターンを形成する工程と、

前記仮のパターンを囲むように、前記基板の上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後、前記仮のパターンを除去する工程と、

前記仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する工程と、

前記シード膜の上に、配線材料を堆積させることにより、前記凹部を前記配線材料で埋め込む工程と

を有する半導体装置の製造方法。

【請求項2】

前記層間絶縁膜を形成する前に、前記仮のパターンの側面に、第2のバリア膜を形成する工程を、さらに有し、

前記仮のパターンを除去する工程において、前記第2のバリア膜は残す請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第2のバリア膜を形成する工程において、

前記仮のパターンの側面及び上面に、前記第2のバリア膜を形成した後、異方性の反応性イオンエッチングを施すことにより、前記仮のパターンの上面に形成された前記第2のバリア膜を除去し、前記パターンの側面には、前記第2のバリア膜を残す請求項2に記載の半導体装置の製造方法。

【請求項4】

前記仮のパターンを形成する前に、前記基板の上に下地バリア膜を形成する工程を、さらに有し、

前記仮のパターンは、前記下地バリア膜の上に形成し、

前記仮のパターンを形成した後、前記層間絶縁膜を形成する前に、前記仮のパターンが形成されていない領域の前記下地バリア膜を除去する工程を、さらに有する請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【図1−1】

【図1−2】

【図1−3】

【図2−1】

【図2−2】

【図3】

【図4−1】

【図4−2】

【図4−3】

【図5】

【図1−2】

【図1−3】

【図2−1】

【図2−2】

【図3】

【図4−1】

【図4−2】

【図4−3】

【図5】

【公開番号】特開2013−26318(P2013−26318A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−157804(P2011−157804)

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]