半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ストレスマイグレーションに対して高い耐性を有する半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置は益々高集積化されつつあり、そのプロセスルールも微細化されつつある。そこで、半導体基板上に形成される下層配線層(アルミ配線)と上層配線層(アルミ配線)との接続を、層間絶縁膜に設けられた層間接続孔(ビアホール)に、タングステンプラグを埋設させることにより行う半導体装置が特許文献1に示されている。従来、こうしたビアホールは、イオナイズドスパッタリング法を用いて、主にアルミニウム合金系金属を埋め込むことにより導体化されてきた。しかしながら、微細化が進むとともに、イオナイズドスパッタリング法では、前述のアルミニウム合金系金属の埋め込みが不完全となり、不良の原因となっていた。そこで、そのような導通不良や配線寿命低下などの問題を回避するために、イオナイズドスパッタリング法に代えて、化学気相成長(CVD)法によって成膜されるタングステン膜が用いられるようになってきた。

【0003】

一方、特許文献2に示されるような薄膜抵抗体を有する半導体装置がある。この半導体装置は、下層接続層(特許文献1における下層配線層に相当)と、上層配線層と、これらを接続するためビアホールに設けられたプラグと、薄膜抵抗体と下層接続層との間に配置されたバリアメタル層と、を有する。このような構成の半導体装置においても、プロセスルールの微細化に伴い、プラグとして、アルミプラグに代わってタングステンプラグが用いられるようになってきている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−302752号公報

【特許文献2】特開2001−118844号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献2に示したような構成の半導体装置では、下層接続層として純粋なアルミニウム(Pure−Al)を用い、バリアメタル層としてTiW(チタンタングステン)を用いている。この下層接続層は、薄膜抵抗体と上層配線層とを接続するための金属層としてだけではなく、バリアメタル層をウェットエッチングするためのマスクとしての用途も兼ねる。このため、その構成材料として、ウェットエッチングの容易さから、不純物を含まないPure−Alが用いられる。

【0006】

このような構成では、上層配線層と下層接続層とを接続するプラグの構成材料として、タングステンを用いる場合、下層接続層の構成材料であるPure−Alと、タングステンプラグとが接続される構成となる。このため、アルミニウムおよびタングステンの線膨張係数差に起因するストレスマイグレーションにより、下層接続層とプラグとの界面にボイドが生じる虞がある。すなわち、プラグの接続箇所において、コンタクト抵抗が増加する、あるいは断線する等、半導体装置の信頼性低下が懸念される。

【0007】

本発明は、上記問題点に鑑みてなされたものであり、信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、請求項1に記載の半導体装置の製造方法は、

基板の一面上に薄膜抵抗体を成膜する第1成膜工程と、

薄膜抵抗体における基板との接触面と反対の面で面接触するように、接続層としての第1導体層を成膜する第2成膜工程と、

第1導体層上に、第1導体層のエッチングマスクとして、アルミニウムからなる第2導体層を所定の形状で成膜する第3成膜工程と、

第2導体層をエッチングマスクとして、第1導体層をエッチングして所定形状とするパターンニング工程と、

第2導体層を除去するマスク除去工程と、

薄膜抵抗体および第1導体層を覆うように、基板の一面上に層間絶縁膜を形成する第4成膜工程と、

層間絶縁膜を貫通して第1導体層に到達するビアホールを形成するビアホール形成工程と、

ビアホール内部にタングステンからなる導体を埋設して、タングステンプラグを形成するプラグ形成工程と、

タングステンプラグと接続するように、層間絶縁膜上に配線層を形成する配線工程と、

を備えることを特徴とする。

【0009】

本発明では、ビアホールの形成前に、アルミニウムからなり、第1導体層をエッチングする際のマスクとして用いられる第2導体層を除去する。そして、ビアホール形成工程にて、ビアホールを第1導体層に到達するように形成し、プラグ形成工程にて、ビアホール内部にタングステンからなる導体を埋設する。すなわち、アルミニウムからなる第2導体層を介することなく、配線層と、接続層としての第1導体層と、薄膜抵抗体とが電気的に導通する。したがって、アルミニウムとタングステンとの間の線膨張係数差に起因するストレスマイグレーションが発生することはなく、接続層におけるボイドの発生を抑制することができる。これにより、プラグとしてタングステンを用いることが必要とされる高集積化可能な半導体装置においても、接続信頼性を向上することができる。

【0010】

請求項2に記載のように、第1導体層はTiW(チタンタングステン)からなることが好ましい。

【0011】

薄膜抵抗体は極めて薄く形成されるため、ビアホールを薄膜抵抗体に到達して形成することは現実的ではない。このため、薄膜抵抗体と配線層を接続するための接続層として、第1導体層を用いる。TiWは、プラグとしてのタングステンと密着性に優れるため、第1導体層の構成材料として好適である。また、薄膜抵抗体と第2導体層とが直接接触すると、カーケンドール効果により、薄膜抵抗体と第2導体層との界面に合金を生じてしまい、薄膜抵抗体の抵抗値が変動してしまう虞がある。TiWは、エッチングしやすく、所定の形状に加工しやすいだけでなく、他の金属との間で合金化しにくいため、薄膜抵抗体と第2導体層との間のバリアメタルとして好適である。

【0012】

請求項3に記載のように、薄膜抵抗体はCrSi(クロムシリコン)系の薄膜であることが好ましい。

【0013】

CrSiは、抵抗値の温度依存性が小さく、温度変動の大きな箇所で利用することができる。また、レーザートリミング等の方法での形状の加工が容易であり、抵抗値を精密に決定できる。とくに、請求項2に記載のように、バリアメタルとしてTiWを用いる場合において、CrSiとTiWとは密着性に優れるため、半導体装置の接続信頼性を向上する効果も得られる。

【0014】

請求項4に記載のように、ビアホール形成工程の後、プラグ形成工程の前に、ビアホールの内壁にグルー膜を成膜するグルー膜形成工程を有することが好ましい。

【0015】

これによれば、ビアホールがその内壁にグルー膜を有することにより、プラグの構成材料であるタングステンが堆積しやすくなる。したがって、より効率的にプラグ形成工程を実施することができる。

【0016】

なお、請求項5に記載のように、グルー膜は、TiN(窒化チタン)からなることが好ましい。

【0017】

これによれば、プラグの構成材料であるタングステンが堆積しやすく、より効率的にビアホール内に埋設できることに加え、例えばアルミニウム系合金よりなる配線層との密着性に優れているため、半導体装置の接続信頼性を向上することができる。

【図面の簡単な説明】

【0018】

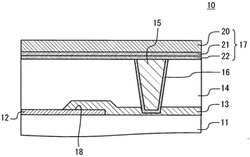

【図1】第1実施形態に係る半導体装置の概略を示す断面図である。

【図2】半導体装置の製造方法を示す断面図であり、(a)第1成膜工程、(b)第2成膜工程、(c)第3成膜工程、(d)パターンニング工程、(e)マスク除去工程、を示す。

【図3】半導体装置の製造方法を示す断面図であり、(a)第4成膜工程、(b)ビアホール形成工程、(c)グルー膜形成工程、(d)プラグ形成工程、(e)配線工程、を示す。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

【0020】

(第1実施形態)

最初に、図1を参照して、本実施形態に係る半導体装置10の構成について説明する。

【0021】

半導体装置10は、基板11と、薄膜抵抗体12と、接続層としての第1導体層13と、層間絶縁膜14と、タングステンプラグ15と、グルー膜16と、配線層17と、を有する。

【0022】

基板11は、一面にTEOS(オルトケイ酸テトラエチル)膜が形成されたシリコンなどからなる半導体基板(図示せず)であり、この半導体基板のTEOS形成面に薄膜抵抗体12と第1導体層13とが形成されている。

【0023】

薄膜抵抗体12は、基板11の一面上に成膜されている。本実施形態において、この薄膜抵抗体12は、抵抗値の温度依存性が小さく、安定した抵抗値を得られるCrSi(クロムシリコン)系の薄膜からなる。

【0024】

第1導体層13は、薄膜抵抗体12における基板11との接触面と反対の表面18の一部で面接触されつつ、基板11の一面上に成膜されている。本実施形態において、この第1導体層13は、他種金属と接触した場合に合金化しにくいTiW(チタンタングステン)からなる。

【0025】

層間絶縁膜14は、薄膜抵抗体12および第1導体層13を覆うように、基板11の一面上に形成されている。本実施形態において、この層間絶縁膜14はTEOS膜からなる。

【0026】

タングステンプラグ15は、タングステンからなり、層間絶縁膜14を貫通して設けられ、第1導体層13と配線層17とを電気的に接続している。

【0027】

グルー膜16は、層間絶縁膜14におけるタングステンプラグ15との対向面および第1導体層13におけるタングステンプラグ15との対向面に成膜されている。本実施形態において、グルー膜16はTiN(窒化チタン)からなる。

【0028】

配線層17は、層間絶縁膜14上に形成され、タングステンプラグ15を介して薄膜抵抗体12および第1導体層13と電気的に接続されている。具体的な構成として、配線層17は、主配線20と、主配線20に接してバリアメタルとして機能する第1バリアメタル層21と、第1バリアメタル層21と層間絶縁膜14、タングステンプラグ15およびグルー膜16の対向面に配置された第2バリアメタル層22とを有している。すなわち、層間絶縁膜14側から、第2バリアメタル層22、第1バリアメタル層21、主配線20の順で形成されている。主配線20の構成材料は、Cu(銅)を含むアルミニウム系合金である。また、第1バリアメタル層21は、TiNからなり、第2バリアメタル層22はチタンからなる。

【0029】

このように構成された本実施形態の半導体装置10では、配線層17が、図示しない外部回路と接続されることにより、薄膜抵抗体12が抵抗器として機能するようになっている。

【0030】

次に、図2および図3を参照して、本実施形態に係る半導体装置10の製造方法を以下に説明する。

【0031】

先ず、図2(a)に示すように、基板11の一面上に薄膜抵抗体12を形成する第1成膜工程を行う。具体的には、例えば、CrSi膜をイオナイズドスパッタリング(以降、単にスパッタリングという)により膜厚15nm程度成膜する。その後、フォトリソグラフィ処理によりパターンニングして薄膜抵抗体12を形成する。

【0032】

次いで、図2(b)に示すように、接続層としての第1導体層13を形成する第2成膜工程を行う。第1導体層13としては、TiW膜をスパッタリングにより膜厚120nm程度成膜する。この第1導体層13は、薄膜抵抗体12の表面18に面接触するように、基板11の一面全域に成膜する。

【0033】

次いで、図2(c)に示すように、第1導体層13をパターンニングするマスクとしての第2導体層19を形成する第3成膜工程を行う。第2導体層19としては、アルミニウムをスパッタリングにより膜厚200nm程度成膜する。その後、第2導体層19の表面の一部にフォトレジストを塗布してウェットエッチングを行い、第2導体層19を所定の形状とする。具体的には、薄膜抵抗体12の一部と第1導体層13と第2導体層19とが重畳するように形成する。なお、エッチング液としては、燐酸と硝酸との混合液を用いることができる。

【0034】

次いで、図2(d)に示すように、第2導体層19をエッチングマスクとして、第1導体層13をウェットエッチングによりパターンニングするパターンニング工程を行う。この工程におけるエッチング液として、水酸化アンモニウムと過酸化水素水との混合液を用いると、オーバーエッチを行っても、CrSiからなる薄膜抵抗体12をエッチオフすることがないため、確実にパターンニングを行うことができる。

【0035】

次いで、図2(e)に示すように、第2導体層19をウェットエッチングにより除去するマスク除去工程を行う。この工程においては、エッチング液として燐酸と硝酸との混合液を用いる。

【0036】

次いで、図3(a)に示すように、層間絶縁膜14を形成するための第4成膜工程を行う。層間絶縁膜14としては、TEOSを化学気相成長(CVD)法により、薄膜抵抗体12と第1導体層13とを覆うように、基板11の一面全域に成膜する。

【0037】

次いで、図3(b)に示すように、ビアホール23を形成するためのビアホール形成工程を行う。ビアホール23は、エッチング気体にC4F8(パーフルオロシクロブタン)のプラズマガスを用いたドライエッチングにより形成する。ビアホール23は、層間絶縁膜14を、層間絶縁膜14の基板11との接触面と反対の面側から第1導体層13に到達するまでエッチングして形成する。

【0038】

次いで、図3(c)に示すように、グルー膜16を形成するグルー膜形成工程を行う。グルー膜16としては、タングステンプラグ15との密着性に優れたTiNを、スパッタリングにより、層間絶縁膜14上に膜厚70nm程度成膜する。この工程により、ビアホール23の内壁にもグルー膜16が形成される。

【0039】

次いで、図3(d)に示すように、タングステンプラグ15を形成するためのプラグ形成工程を行う。まず、グルー膜16が形成された層間絶縁膜14上の全面に亘って、WF6(六フッ化タングステン)とSiH4(モノシラン)を用いた還元反応により、わずかにタングステン膜を成長させることで核形成を行う。続いて、WF6と水素の還元反応により、タングステンを堆積させる。この工程により、ビアホール23内にグルー膜16を介してタングステンプラグ15が形成される。また、層間絶縁膜14の表面上にも、グルー膜16を介してタングステン膜が形成される。その後、化学機械平坦化(CMP)により、層間絶縁膜14とタングステンプラグの一部が露出するように平坦化する。

【0040】

最後に、図3(e)に示すように、配線層17を形成する配線工程を行う。第2バリアメタル層22としてのチタン層を、平坦化された層間絶縁膜14、タングステンプラグ15の表面に露出した部分およびグルー膜16の表面に露出した一部の上に、スパッタリングにより成膜する。続いて、第1バリアメタル層21としてのTiN層を、第2バリアメタル層22の表面を被覆するようにスパッタリングにより成膜する。その後、主配線20としてのCuを含むアルミニウム系合金を、第1バリアメタル層21上に、スパッタリングにより成膜する。

【0041】

以上の工程を経て、本実施形態に係る半導体装置10を製造することができる。

【0042】

次に、本実施形態に係る半導体装置の製造方法を採用した場合の作用効果について説明する。

【0043】

本実施形態では、アルミニウムからなる第2導体層19を除去するマスク除去した後、ビアホール23を第1導体層13に到達するように形成し、次いで、タングステンプラグ15を形成する。すなわち、アルミニウムからなる第2導体層19を介することなく、配線層17、接続層としての第1導体層13ならびに薄膜抵抗体12が電気的に導通する。したがって、アルミニウムとタングステンとの間の線膨張係数差に起因するストレスマイグレーションが発生することはなく、接続層におけるボイドの発生を抑制することができる。これにより、プラグの構成材料としてタングステンを用いることが必要とされる高集積化可能な半導体装置10においても、接続信頼性を向上することができる。

【0044】

また、本実施形態では、薄膜抵抗体12としてCrSiを用いている。CrSiは、抵抗値の温度依存性が小さく、温度変動の大きな箇所で利用することができる。また、レーザートリミング等の方法での形状の加工が容易であり、抵抗値を精密に決定できる。

【0045】

また、本実施形態では、接続層としての第1導体層13に、TiWを用いている。TiWは、エッチングが容易で、所定の形状に加工しやすいことに加え、他の種類の金属と合金化しにくい。このため、薄膜抵抗体12の抵抗値を変動させることなく、第1導体層13に接続することができる。また、TiWは、CrSiとの密着性が高く、薄膜抵抗体12と第1導体層13との接続信頼性を向上することもできる。

【0046】

また、本実施形態では、ビアホール形成工程の後、プラグ形成工程の前に、ビアホール23の内壁にTiNからなるグルー膜16を成膜するグルー膜形成工程を有する。これによれば、ビアホール23がその内壁にグルー膜16を有することにより、タングステンプラグ15の構成材料であるであるタングステンが堆積しやすくなる。したがって、より効率的にプラグ形成工程を実施することができる。

【0047】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上述した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

【0048】

基板11としては、第1実施形態で示したような半導体基板上に形成されたTEOS膜以外に、半導体基板上に形成されたBPSG、LOCOS、SiO2、窒化膜などの絶縁膜の場合にも適用することができる。薄膜抵抗体12としては、第1実施形態で示したCrSi以外に、NiCrなどを用いることができる。第1導体層13としては、第1実施形態で示したTiW以外に、TiN、タングステンあるいはチタンを用いることができる。また、グルー膜16としては、第1実施形態で示したTiN以外に、チタンなどを用いることができる。なお、グルー膜16は、プラグ形成工程において、タングステンプラグ15の構成材料であるタングステンがビアホール23の内壁に堆積しやすくする機能を発揮するものである。このため、グルー膜16は必ずしも設ける必要はないが、グルー膜16を設けることにより、効率的にタングステンプラグ15をビアホール23内に埋設することができる。

【符号の説明】

【0049】

10・・・半導体装置

11・・・基板

12・・・薄膜抵抗体

13・・・第1導体層

14・・・層間絶縁膜

15・・・タングステンプラグ

16・・・グルー膜

17・・・配線層

20・・・主配線

21・・・第1バリアメタル層

22・・・第2バリアメタル層

【技術分野】

【0001】

本発明は、ストレスマイグレーションに対して高い耐性を有する半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置は益々高集積化されつつあり、そのプロセスルールも微細化されつつある。そこで、半導体基板上に形成される下層配線層(アルミ配線)と上層配線層(アルミ配線)との接続を、層間絶縁膜に設けられた層間接続孔(ビアホール)に、タングステンプラグを埋設させることにより行う半導体装置が特許文献1に示されている。従来、こうしたビアホールは、イオナイズドスパッタリング法を用いて、主にアルミニウム合金系金属を埋め込むことにより導体化されてきた。しかしながら、微細化が進むとともに、イオナイズドスパッタリング法では、前述のアルミニウム合金系金属の埋め込みが不完全となり、不良の原因となっていた。そこで、そのような導通不良や配線寿命低下などの問題を回避するために、イオナイズドスパッタリング法に代えて、化学気相成長(CVD)法によって成膜されるタングステン膜が用いられるようになってきた。

【0003】

一方、特許文献2に示されるような薄膜抵抗体を有する半導体装置がある。この半導体装置は、下層接続層(特許文献1における下層配線層に相当)と、上層配線層と、これらを接続するためビアホールに設けられたプラグと、薄膜抵抗体と下層接続層との間に配置されたバリアメタル層と、を有する。このような構成の半導体装置においても、プロセスルールの微細化に伴い、プラグとして、アルミプラグに代わってタングステンプラグが用いられるようになってきている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−302752号公報

【特許文献2】特開2001−118844号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献2に示したような構成の半導体装置では、下層接続層として純粋なアルミニウム(Pure−Al)を用い、バリアメタル層としてTiW(チタンタングステン)を用いている。この下層接続層は、薄膜抵抗体と上層配線層とを接続するための金属層としてだけではなく、バリアメタル層をウェットエッチングするためのマスクとしての用途も兼ねる。このため、その構成材料として、ウェットエッチングの容易さから、不純物を含まないPure−Alが用いられる。

【0006】

このような構成では、上層配線層と下層接続層とを接続するプラグの構成材料として、タングステンを用いる場合、下層接続層の構成材料であるPure−Alと、タングステンプラグとが接続される構成となる。このため、アルミニウムおよびタングステンの線膨張係数差に起因するストレスマイグレーションにより、下層接続層とプラグとの界面にボイドが生じる虞がある。すなわち、プラグの接続箇所において、コンタクト抵抗が増加する、あるいは断線する等、半導体装置の信頼性低下が懸念される。

【0007】

本発明は、上記問題点に鑑みてなされたものであり、信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、請求項1に記載の半導体装置の製造方法は、

基板の一面上に薄膜抵抗体を成膜する第1成膜工程と、

薄膜抵抗体における基板との接触面と反対の面で面接触するように、接続層としての第1導体層を成膜する第2成膜工程と、

第1導体層上に、第1導体層のエッチングマスクとして、アルミニウムからなる第2導体層を所定の形状で成膜する第3成膜工程と、

第2導体層をエッチングマスクとして、第1導体層をエッチングして所定形状とするパターンニング工程と、

第2導体層を除去するマスク除去工程と、

薄膜抵抗体および第1導体層を覆うように、基板の一面上に層間絶縁膜を形成する第4成膜工程と、

層間絶縁膜を貫通して第1導体層に到達するビアホールを形成するビアホール形成工程と、

ビアホール内部にタングステンからなる導体を埋設して、タングステンプラグを形成するプラグ形成工程と、

タングステンプラグと接続するように、層間絶縁膜上に配線層を形成する配線工程と、

を備えることを特徴とする。

【0009】

本発明では、ビアホールの形成前に、アルミニウムからなり、第1導体層をエッチングする際のマスクとして用いられる第2導体層を除去する。そして、ビアホール形成工程にて、ビアホールを第1導体層に到達するように形成し、プラグ形成工程にて、ビアホール内部にタングステンからなる導体を埋設する。すなわち、アルミニウムからなる第2導体層を介することなく、配線層と、接続層としての第1導体層と、薄膜抵抗体とが電気的に導通する。したがって、アルミニウムとタングステンとの間の線膨張係数差に起因するストレスマイグレーションが発生することはなく、接続層におけるボイドの発生を抑制することができる。これにより、プラグとしてタングステンを用いることが必要とされる高集積化可能な半導体装置においても、接続信頼性を向上することができる。

【0010】

請求項2に記載のように、第1導体層はTiW(チタンタングステン)からなることが好ましい。

【0011】

薄膜抵抗体は極めて薄く形成されるため、ビアホールを薄膜抵抗体に到達して形成することは現実的ではない。このため、薄膜抵抗体と配線層を接続するための接続層として、第1導体層を用いる。TiWは、プラグとしてのタングステンと密着性に優れるため、第1導体層の構成材料として好適である。また、薄膜抵抗体と第2導体層とが直接接触すると、カーケンドール効果により、薄膜抵抗体と第2導体層との界面に合金を生じてしまい、薄膜抵抗体の抵抗値が変動してしまう虞がある。TiWは、エッチングしやすく、所定の形状に加工しやすいだけでなく、他の金属との間で合金化しにくいため、薄膜抵抗体と第2導体層との間のバリアメタルとして好適である。

【0012】

請求項3に記載のように、薄膜抵抗体はCrSi(クロムシリコン)系の薄膜であることが好ましい。

【0013】

CrSiは、抵抗値の温度依存性が小さく、温度変動の大きな箇所で利用することができる。また、レーザートリミング等の方法での形状の加工が容易であり、抵抗値を精密に決定できる。とくに、請求項2に記載のように、バリアメタルとしてTiWを用いる場合において、CrSiとTiWとは密着性に優れるため、半導体装置の接続信頼性を向上する効果も得られる。

【0014】

請求項4に記載のように、ビアホール形成工程の後、プラグ形成工程の前に、ビアホールの内壁にグルー膜を成膜するグルー膜形成工程を有することが好ましい。

【0015】

これによれば、ビアホールがその内壁にグルー膜を有することにより、プラグの構成材料であるタングステンが堆積しやすくなる。したがって、より効率的にプラグ形成工程を実施することができる。

【0016】

なお、請求項5に記載のように、グルー膜は、TiN(窒化チタン)からなることが好ましい。

【0017】

これによれば、プラグの構成材料であるタングステンが堆積しやすく、より効率的にビアホール内に埋設できることに加え、例えばアルミニウム系合金よりなる配線層との密着性に優れているため、半導体装置の接続信頼性を向上することができる。

【図面の簡単な説明】

【0018】

【図1】第1実施形態に係る半導体装置の概略を示す断面図である。

【図2】半導体装置の製造方法を示す断面図であり、(a)第1成膜工程、(b)第2成膜工程、(c)第3成膜工程、(d)パターンニング工程、(e)マスク除去工程、を示す。

【図3】半導体装置の製造方法を示す断面図であり、(a)第4成膜工程、(b)ビアホール形成工程、(c)グルー膜形成工程、(d)プラグ形成工程、(e)配線工程、を示す。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

【0020】

(第1実施形態)

最初に、図1を参照して、本実施形態に係る半導体装置10の構成について説明する。

【0021】

半導体装置10は、基板11と、薄膜抵抗体12と、接続層としての第1導体層13と、層間絶縁膜14と、タングステンプラグ15と、グルー膜16と、配線層17と、を有する。

【0022】

基板11は、一面にTEOS(オルトケイ酸テトラエチル)膜が形成されたシリコンなどからなる半導体基板(図示せず)であり、この半導体基板のTEOS形成面に薄膜抵抗体12と第1導体層13とが形成されている。

【0023】

薄膜抵抗体12は、基板11の一面上に成膜されている。本実施形態において、この薄膜抵抗体12は、抵抗値の温度依存性が小さく、安定した抵抗値を得られるCrSi(クロムシリコン)系の薄膜からなる。

【0024】

第1導体層13は、薄膜抵抗体12における基板11との接触面と反対の表面18の一部で面接触されつつ、基板11の一面上に成膜されている。本実施形態において、この第1導体層13は、他種金属と接触した場合に合金化しにくいTiW(チタンタングステン)からなる。

【0025】

層間絶縁膜14は、薄膜抵抗体12および第1導体層13を覆うように、基板11の一面上に形成されている。本実施形態において、この層間絶縁膜14はTEOS膜からなる。

【0026】

タングステンプラグ15は、タングステンからなり、層間絶縁膜14を貫通して設けられ、第1導体層13と配線層17とを電気的に接続している。

【0027】

グルー膜16は、層間絶縁膜14におけるタングステンプラグ15との対向面および第1導体層13におけるタングステンプラグ15との対向面に成膜されている。本実施形態において、グルー膜16はTiN(窒化チタン)からなる。

【0028】

配線層17は、層間絶縁膜14上に形成され、タングステンプラグ15を介して薄膜抵抗体12および第1導体層13と電気的に接続されている。具体的な構成として、配線層17は、主配線20と、主配線20に接してバリアメタルとして機能する第1バリアメタル層21と、第1バリアメタル層21と層間絶縁膜14、タングステンプラグ15およびグルー膜16の対向面に配置された第2バリアメタル層22とを有している。すなわち、層間絶縁膜14側から、第2バリアメタル層22、第1バリアメタル層21、主配線20の順で形成されている。主配線20の構成材料は、Cu(銅)を含むアルミニウム系合金である。また、第1バリアメタル層21は、TiNからなり、第2バリアメタル層22はチタンからなる。

【0029】

このように構成された本実施形態の半導体装置10では、配線層17が、図示しない外部回路と接続されることにより、薄膜抵抗体12が抵抗器として機能するようになっている。

【0030】

次に、図2および図3を参照して、本実施形態に係る半導体装置10の製造方法を以下に説明する。

【0031】

先ず、図2(a)に示すように、基板11の一面上に薄膜抵抗体12を形成する第1成膜工程を行う。具体的には、例えば、CrSi膜をイオナイズドスパッタリング(以降、単にスパッタリングという)により膜厚15nm程度成膜する。その後、フォトリソグラフィ処理によりパターンニングして薄膜抵抗体12を形成する。

【0032】

次いで、図2(b)に示すように、接続層としての第1導体層13を形成する第2成膜工程を行う。第1導体層13としては、TiW膜をスパッタリングにより膜厚120nm程度成膜する。この第1導体層13は、薄膜抵抗体12の表面18に面接触するように、基板11の一面全域に成膜する。

【0033】

次いで、図2(c)に示すように、第1導体層13をパターンニングするマスクとしての第2導体層19を形成する第3成膜工程を行う。第2導体層19としては、アルミニウムをスパッタリングにより膜厚200nm程度成膜する。その後、第2導体層19の表面の一部にフォトレジストを塗布してウェットエッチングを行い、第2導体層19を所定の形状とする。具体的には、薄膜抵抗体12の一部と第1導体層13と第2導体層19とが重畳するように形成する。なお、エッチング液としては、燐酸と硝酸との混合液を用いることができる。

【0034】

次いで、図2(d)に示すように、第2導体層19をエッチングマスクとして、第1導体層13をウェットエッチングによりパターンニングするパターンニング工程を行う。この工程におけるエッチング液として、水酸化アンモニウムと過酸化水素水との混合液を用いると、オーバーエッチを行っても、CrSiからなる薄膜抵抗体12をエッチオフすることがないため、確実にパターンニングを行うことができる。

【0035】

次いで、図2(e)に示すように、第2導体層19をウェットエッチングにより除去するマスク除去工程を行う。この工程においては、エッチング液として燐酸と硝酸との混合液を用いる。

【0036】

次いで、図3(a)に示すように、層間絶縁膜14を形成するための第4成膜工程を行う。層間絶縁膜14としては、TEOSを化学気相成長(CVD)法により、薄膜抵抗体12と第1導体層13とを覆うように、基板11の一面全域に成膜する。

【0037】

次いで、図3(b)に示すように、ビアホール23を形成するためのビアホール形成工程を行う。ビアホール23は、エッチング気体にC4F8(パーフルオロシクロブタン)のプラズマガスを用いたドライエッチングにより形成する。ビアホール23は、層間絶縁膜14を、層間絶縁膜14の基板11との接触面と反対の面側から第1導体層13に到達するまでエッチングして形成する。

【0038】

次いで、図3(c)に示すように、グルー膜16を形成するグルー膜形成工程を行う。グルー膜16としては、タングステンプラグ15との密着性に優れたTiNを、スパッタリングにより、層間絶縁膜14上に膜厚70nm程度成膜する。この工程により、ビアホール23の内壁にもグルー膜16が形成される。

【0039】

次いで、図3(d)に示すように、タングステンプラグ15を形成するためのプラグ形成工程を行う。まず、グルー膜16が形成された層間絶縁膜14上の全面に亘って、WF6(六フッ化タングステン)とSiH4(モノシラン)を用いた還元反応により、わずかにタングステン膜を成長させることで核形成を行う。続いて、WF6と水素の還元反応により、タングステンを堆積させる。この工程により、ビアホール23内にグルー膜16を介してタングステンプラグ15が形成される。また、層間絶縁膜14の表面上にも、グルー膜16を介してタングステン膜が形成される。その後、化学機械平坦化(CMP)により、層間絶縁膜14とタングステンプラグの一部が露出するように平坦化する。

【0040】

最後に、図3(e)に示すように、配線層17を形成する配線工程を行う。第2バリアメタル層22としてのチタン層を、平坦化された層間絶縁膜14、タングステンプラグ15の表面に露出した部分およびグルー膜16の表面に露出した一部の上に、スパッタリングにより成膜する。続いて、第1バリアメタル層21としてのTiN層を、第2バリアメタル層22の表面を被覆するようにスパッタリングにより成膜する。その後、主配線20としてのCuを含むアルミニウム系合金を、第1バリアメタル層21上に、スパッタリングにより成膜する。

【0041】

以上の工程を経て、本実施形態に係る半導体装置10を製造することができる。

【0042】

次に、本実施形態に係る半導体装置の製造方法を採用した場合の作用効果について説明する。

【0043】

本実施形態では、アルミニウムからなる第2導体層19を除去するマスク除去した後、ビアホール23を第1導体層13に到達するように形成し、次いで、タングステンプラグ15を形成する。すなわち、アルミニウムからなる第2導体層19を介することなく、配線層17、接続層としての第1導体層13ならびに薄膜抵抗体12が電気的に導通する。したがって、アルミニウムとタングステンとの間の線膨張係数差に起因するストレスマイグレーションが発生することはなく、接続層におけるボイドの発生を抑制することができる。これにより、プラグの構成材料としてタングステンを用いることが必要とされる高集積化可能な半導体装置10においても、接続信頼性を向上することができる。

【0044】

また、本実施形態では、薄膜抵抗体12としてCrSiを用いている。CrSiは、抵抗値の温度依存性が小さく、温度変動の大きな箇所で利用することができる。また、レーザートリミング等の方法での形状の加工が容易であり、抵抗値を精密に決定できる。

【0045】

また、本実施形態では、接続層としての第1導体層13に、TiWを用いている。TiWは、エッチングが容易で、所定の形状に加工しやすいことに加え、他の種類の金属と合金化しにくい。このため、薄膜抵抗体12の抵抗値を変動させることなく、第1導体層13に接続することができる。また、TiWは、CrSiとの密着性が高く、薄膜抵抗体12と第1導体層13との接続信頼性を向上することもできる。

【0046】

また、本実施形態では、ビアホール形成工程の後、プラグ形成工程の前に、ビアホール23の内壁にTiNからなるグルー膜16を成膜するグルー膜形成工程を有する。これによれば、ビアホール23がその内壁にグルー膜16を有することにより、タングステンプラグ15の構成材料であるであるタングステンが堆積しやすくなる。したがって、より効率的にプラグ形成工程を実施することができる。

【0047】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上述した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

【0048】

基板11としては、第1実施形態で示したような半導体基板上に形成されたTEOS膜以外に、半導体基板上に形成されたBPSG、LOCOS、SiO2、窒化膜などの絶縁膜の場合にも適用することができる。薄膜抵抗体12としては、第1実施形態で示したCrSi以外に、NiCrなどを用いることができる。第1導体層13としては、第1実施形態で示したTiW以外に、TiN、タングステンあるいはチタンを用いることができる。また、グルー膜16としては、第1実施形態で示したTiN以外に、チタンなどを用いることができる。なお、グルー膜16は、プラグ形成工程において、タングステンプラグ15の構成材料であるタングステンがビアホール23の内壁に堆積しやすくする機能を発揮するものである。このため、グルー膜16は必ずしも設ける必要はないが、グルー膜16を設けることにより、効率的にタングステンプラグ15をビアホール23内に埋設することができる。

【符号の説明】

【0049】

10・・・半導体装置

11・・・基板

12・・・薄膜抵抗体

13・・・第1導体層

14・・・層間絶縁膜

15・・・タングステンプラグ

16・・・グルー膜

17・・・配線層

20・・・主配線

21・・・第1バリアメタル層

22・・・第2バリアメタル層

【特許請求の範囲】

【請求項1】

基板の一面上に薄膜抵抗体を成膜する第1成膜工程と、

前記薄膜抵抗体における前記基板との接触面と反対の面で面接触するように、接続層としての第1導体層を成膜する第2成膜工程と、

前記第1導体層上に、前記第1導体層のエッチングマスクとして、アルミニウムからなる第2導体層を所定の形状で成膜する第3成膜工程と、

前記第2導体層をエッチングマスクとして、前記第1導体層をエッチングして所定形状とするパターンニング工程と、

前記第2導体層を除去するマスク除去工程と、

前記薄膜抵抗体および前記第1導体層を覆うように、前記基板の一面上に層間絶縁膜を形成する第4成膜工程と、

前記層間絶縁膜を貫通して前記第1導体層に到達するビアホールを形成するビアホール形成工程と、

前記ビアホール内部にタングステンからなる導体を埋設して、タングステンプラグを形成するプラグ形成工程と、

前記タングステンプラグと接続するように、前記層間絶縁膜上に配線層を形成する配線工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記第1導体層はTiW(チタンタングステン)からなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記薄膜抵抗体はCrSi(クロムシリコン)系の薄膜であることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記ビアホール形成工程の後、前記プラグ形成工程の前に、前記ビアホールの内壁にグルー膜を成膜するグルー膜形成工程を有することを特徴とする請求項1〜3いずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記グルー膜はTiN(窒化チタン)からなることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項1】

基板の一面上に薄膜抵抗体を成膜する第1成膜工程と、

前記薄膜抵抗体における前記基板との接触面と反対の面で面接触するように、接続層としての第1導体層を成膜する第2成膜工程と、

前記第1導体層上に、前記第1導体層のエッチングマスクとして、アルミニウムからなる第2導体層を所定の形状で成膜する第3成膜工程と、

前記第2導体層をエッチングマスクとして、前記第1導体層をエッチングして所定形状とするパターンニング工程と、

前記第2導体層を除去するマスク除去工程と、

前記薄膜抵抗体および前記第1導体層を覆うように、前記基板の一面上に層間絶縁膜を形成する第4成膜工程と、

前記層間絶縁膜を貫通して前記第1導体層に到達するビアホールを形成するビアホール形成工程と、

前記ビアホール内部にタングステンからなる導体を埋設して、タングステンプラグを形成するプラグ形成工程と、

前記タングステンプラグと接続するように、前記層間絶縁膜上に配線層を形成する配線工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記第1導体層はTiW(チタンタングステン)からなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記薄膜抵抗体はCrSi(クロムシリコン)系の薄膜であることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記ビアホール形成工程の後、前記プラグ形成工程の前に、前記ビアホールの内壁にグルー膜を成膜するグルー膜形成工程を有することを特徴とする請求項1〜3いずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記グルー膜はTiN(窒化チタン)からなることを特徴とする請求項4に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−38195(P2013−38195A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−172469(P2011−172469)

【出願日】平成23年8月7日(2011.8.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月7日(2011.8.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]