半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

シリコンデバイスを含む半導体デバイスは、Mooreの法則で知られるスケーリング則の微細化によって集積化・低電力化が進められ、「3年で4倍の集積化を図る」というペースで開発が進められてきた。近年、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のゲート長は20nm以下となり、リソグラフィプロセスにおけるコストの高騰、およびデバイス寸法の物理的限界により、これまでのスケーリング則とは異なるアプローチでのデバイス性能の改善が求められている。リソグラフィプロセスにおけるコストの高騰には、製造装置およびマスクセットの価格の高騰が挙げられる。また、デバイス寸法の物理的限界には、動作限界および寸法ばらつき限界が挙げられる。

【0003】

近年、半導体装置の性能改善手法の一つとして、半導体装置内部に半導体素子以外の能動素子、例えば抵抗変化素子を、メモリあるいはスイッチとして設けることが行われている。

【0004】

このような抵抗変化素子としては、遷移金属酸化物を用いたRRAM(Resistance RAM [Random Access Memory])や、イオン伝導体を用いた固体電解質スイッチなどがある。イオン伝導体は、イオンが電界などの印加によって自由に動くことのできる固体である。その他にも、FRAM(Ferro Electric RAM)、MRAM(Magnetic RAM)、PRAM(Phase-change RAM)などの開発が進められている(非特許文献1)。

【0005】

このようなスイッチング素子は、MOSFETなどの半導体素子よりもサイズが小さいため、同じ機能を実現するための占有面積を小さくすることができ、ゲートの充放電や配線に起因する動作時の消費電力(Dynamic power)を小さくすることができる。さらに、SRAM(Static RAM)やDRAM(Dynamic RAM)は、電源がオフになると記憶状態が消去されてしまう揮発性素子であるのに対して、抵抗変化素子は、電源をオフにしても記憶状態が保持される不揮発性素子であるため、待機時の消費電力(Static power)も低減できる。

【0006】

加えて、固体電解質スイッチは、さらにオン抵抗が小さいという特徴を持っている。そのため、固体電解スイッチは、スイッチ自体を信号線に用いる、不揮発なプログラマブルロジックデバイスへの適用に有望であると考えられている(非特許文献2)。

【0007】

一方、特許文献1には、半導体装置の製造方法において、熱処理時の半導体基板(シリコン基板)の裏面側からの半導体構成原子(シリコン)の昇華を防止するために、半導体基板の表面側および裏面側を覆うように絶縁膜を形成し、半導体基板の表面側の絶縁膜をエッチング除去し、半導体基板の裏面側に絶縁膜が存在している状態で、半導体基板を熱処理することが記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−152920号公報

【非特許文献】

【0009】

【非特許文献1】R. Nebashi, et al., "A 90nm 12ns 32Mb 2T1MTJ MRAM", IEEE Solid-State Circuits Conference-Digest of Technical Papers, 8-12 Feb. 2009, pp.462-463,463a.

【非特許文献2】M. Tada, et al., "Nonvolatile Crossbar Switch Using TiOx/TaSiOy Solid-Electrolyte", IEEE Transactions on Electron Devices, vol. 57, no.8, pp.1987-1995 2010.

【発明の概要】

【発明が解決しようとする課題】

【0010】

近年、上記のRRAM、MRAM、PRAMに代表される抵抗変化素子には、通常のシリコン半導体プロセスに用いられていない重金属や貴金属(例えばFe、Ru、Mg)からなる膜が用いられている。このような膜は、半導体プロセスにおいて加工する際、通常は反応性ドライエッチング(Reactive Ion Etching:RIE)を用いて加工する。しかしながら、反応生成物の蒸気圧が低い場合、あるいは反応生成物が形成されない金属が含まれる場合、半導体素子を形成したシリコン基板の裏面やべベル(端面)部に成膜材料の金属が容易に付着する。シリコン基板に付着した金属は、プロセス中に発塵の原因になるとともに、後工程のプロセスにおける熱の印加によりシリコン基板中を拡散し、シリコン内に深い準位が形成され、ゲート絶縁膜を有するシリコン半導体素子の閾電圧の変化による誤動作や、ライフタイムの劣化による信頼性の低下を招く。また、金属が付着したままプロセス装置にて加熱を行った場合、昇華した金属が温度センサ等に付着し、プロセス装置の誤動作が発生しやすくなる。

【0011】

このような問題を解決するため、半導体素子形成領域以外のシリコン基板の裏面やべベル(端面)に成膜材料の金属が付着しないプロセス、あるいは付着しても容易に除去ができる手法が必要である。

【0012】

しかしながら、Ni、Pd、Co、Fe、Ptなどに代表される金属は薬液による除去が難しい。このような金属は、例えば王水(濃塩酸と濃硝酸との体積比3:1の混合液)などの洗浄力の強い薬液を用いると除去することができるが、付着金属の除去能力が高まる一方で母材であるシリコン基板裏面に荒れが生じ、先端微細半導体露光装置における焦点深度が不安定になる。

【0013】

一方、基板表面にシリコン窒化膜やシリコン酸化膜などの絶縁膜を形成し、絶縁膜表面に付着した金属をHPM(HCl、H2O2、H2Oを含む混合液)により除去したり、FPM(HF、H2O2、H2Oを含む混合液)により絶縁膜ごと付着した金属を除去(リフトオフ)したりする手法が知られている。しかしながら、この手法を半導体素子の形成された基板へ適用するためには、半導体素子の形成されていない面(基板の裏面)にのみに選択的に絶縁膜を形成する必要がある。

【0014】

基板の裏面にのみ絶縁膜を設けるためには、例えば特許文献1に記載されているように、熱CVD法を用いて基板の表裏面に同時に絶縁膜を成長した後、基板の表面側の絶縁膜を薬液により選択的に除去(ウェットエッチング)する手法がある。しかしながら、抵抗変化素子を半導体素子の上層側に形成するプロセスにおいては、半導体基板上に銅等の金属および層間絶縁膜を含む多層配線構造があらかじめ形成されているため、薬液による表面側絶縁膜を除去する際に、多層配線構造の金属および層間絶縁膜が劣化する。

【0015】

本発明の目的は、上述の問題を解決し、半導体装置の製造において基板の金属汚染を抑えることにある。

【課題を解決するための手段】

【0016】

本発明の一態様による半導体装置の製造方法は、半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、

前記半導体素子形成面に設けられた金属含有膜を加工する工程と、

前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む。

【0017】

本発明の他の態様による半導体製造装置は、上記の製造方法に用いられる製造装置であって、

減圧下で前記保護膜を形成するための成膜室と、

前記基板を載置するためのステージと、

前記成膜室へ前記基板を搬送するためのアームとを有し、

前記ステージは、基板搭載面に凹部を有し、該凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触できる形状を有し、

前記アームは、前記基板の裏面に接触し、該アームが回転することで該基板をフリップし、該基板の半導体素子形成面を前記ステージの基板搭載面に向けて載置する機構を備えていることを特徴とする。

【発明の効果】

【0018】

本発明によれば、半導体装置の製造において、半導体基板の金属汚染を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施形態における半導体製造装置の構成を説明するための概略図である。

【図2】本発明の実施形態における絶縁膜成長装置の構成を説明するための図である。

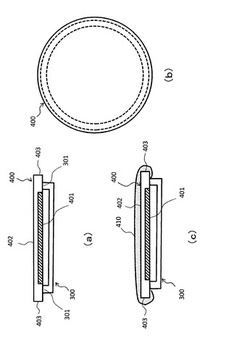

【図3】本発明の実施形態における凹型ステージの形状を説明するための図である。

【図4】本発明の実施形態における凹型ステージにシリコン基板を設置した状態、及び保護絶縁膜を成長した状態を説明するための図である。

【図5】本発明の実施形態における凹型ステージ上にシリコン基板を設置した状態、及び保護絶縁膜を成長した状態を説明するための図である。

【図6】本発明の実施形態における凹型ステージに設けられた真空チャックラインを説明するための図である。

【図7】本発明の実施形態における固体電解質スイッチ素子を説明するための断面図である。

【図8】本発明の実施形態におけるMRAM素子を説明するための断面図である。

【図9】本発明の実施形態における保護絶縁膜形成工程と保護絶縁膜除去工程とを含む工程フロー図である。

【図10】本発明の実施形態における、抵抗変化素子形成前の半導体素子が形成されたシリコン基板の断面図である。

【図11】本発明の実施形態における、抵抗変化素子と半導体素子が形成されたシリコン基板の断面図である。

【図12】図11に示す抵抗変化素子の拡大断面図である。

【発明を実施するための形態】

【0020】

本発明の一実施形態による半導体装置の製造方法は、半導体素子が形成された基板(例えばウェハ等の半導体基板)の、半導体素子形成面とは反対側の裏面および端部(べベル部)に保護膜を形成する工程と、半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程を含む。

【0021】

上記の金属含有膜の加工は、RIE等のドライエッチングにより行うことができる。

【0022】

上記の保護膜の除去工程においては、保護膜に付着した、前記金属含有膜に由来の金属成分とともに保護膜を除去することができる。

【0023】

本実施形態によれば、半導体素子の信頼性を高く維持したまま、抵抗変化素子を混載することができるようになり、半導体装置の高機能化および低電力化を図ることができる。

【0024】

上記の保護膜の形成は、400℃以下で行うことが好ましい。これにより、基板上にあらかじめ形成されている半導体素子や多層配線の熱に起因する劣化を抑えることができる。

【0025】

上記の保護膜の形成工程において、前記基板は、成膜ステージ(基板ステージ)上に、半導体素子形成面を成膜ステージの基板搭載面に向けて載置することができる。その際、成膜ステージは、基板搭載面に凹部を有し、この成膜ステージの基板搭載面の、前記凹部を囲む外周部が、前記基板の素子形成領域に接触しないようにその素子形成領域を囲む外周位置に接触することができる。以下、このような成膜ステージを「凹型ステージ」という。これにより、半導体素子形領域に保護膜が形成されることなく、基板の裏面および端部に選択的に保護膜を形成できる。また、素子形成領域がステージと直接接しないため、ステージからのパーティクルや金属汚染物質の付着が抑制できるとともに、スクラッチなどの機械的なダメージの発生を防止することができる。

【0026】

保護膜の形成においては、CVD法、プラズマCVD法、ALD法、プラズマALD法を用いることが好ましい。凹型ステージを用いた場合、半導体基板と凹型ステージとの接触面積が小さくなり、通常のステージに比べて基板の温度を高く維持しにくくなるが、これらの成膜方法を用いることにより、特に高密度プラズマ源を用いたプラズマCVD法やプラズマALD法を用いることにより、基板温度が低温であっても緻密な保護膜を形成できる。

【0027】

凹型ステージを用いた保護膜の形成においては、基板を、あらかじめ別のステージで所定の温度まで加熱した後に、凹型ステージへ搬送し、保護膜の形成を行うことが好ましい。その際、基板の裏面に接触する搬送アームによって基板を加熱ステージに搬送し、所定の温度に加熱し、その後、基板の裏面に接触させたアームによって加熱ステージから基板を取り出すことができる。

【0028】

凹型ステージ上へ基板を載置する際には、基板の裏面に接触しているアームを回転させることで基板をフリップし、半導体素子形成面が凹型ステージの凹みがある面(基板搭載面)に対向するように凹型ステージ上に載置し、この状態にて反応室(成膜室)内で保護膜を形成することが好ましい。

【0029】

前記保護膜として、シリコン酸化膜、シリコン窒素化膜、又はシリコン炭窒化膜を形成することができる。

【0030】

前記保護膜の除去は、薬液を用いた枚葉式スピン洗浄により実施することができる。

【0031】

本実施形態の製造方法は、前記金属含有膜が、Pt、Pd、Ni、Fe、Co、Ru、Mn、Mg、Ta、Ir、B、Ge、Te、Se、Sbから選ばれる少なくとも一種の金属を含む場合に、より効果的である。

【0032】

本実施形態の製造方法は、上記の金属含有膜の加工工程を含む、MRAM、PRAM、RRAM、FRAM、固体電解質スイッチ等の抵抗変化素子の形成工程を含む場合に、より効果的である。

【0033】

以下、本発明の好適な実施の形態についてさらに説明する。

【0034】

半導体素子の形成されたシリコン基板(ウェハ)上には、多層配線層と層間絶縁膜を含む多層配線構造を設けることができる。そして、この多層配線構造内に抵抗変化素子を設けることができる。

【0035】

本実施形態において、保護膜の形成は、抵抗変化素子の形成プロセスにおける金属含有膜のドライエッチング工程(以下「抵抗変化素子の加工工程」)の前に行う。

【0036】

保護膜の形成は、絶縁膜成長装置を用いて、例えば次のようにして行うことができる。

【0037】

絶縁膜成長装置は、基板ステージとして凹型ステージを備え、この凹型ステージは凹みがある面を上に向けて設置されている。シリコン基板は、この凹型ステージ上に、素子形成面と凹型ステージの凹みがある面とが対向するように(すなわち素子形成面を下に向けて、裏面を上に向けて)載置される。その際、凹型ステージの外周のみがシリコン基板と接触し、半導体素子形成領域は凹型ステージと接触しない。この状態で成膜処理を行うことにより、半導体素子形成領域には保護絶縁膜が形成されず、基板の裏面およびベベルに保護絶縁膜が形成される。

【0038】

凹型ステージ上へのシリコン基板の搬送は、シリコン基板の裏面に接触するアームによって行われ、アームを回転させることでシリコン基板をフリップし、半導体素子形成面を凹型ステージの凹みがある面に対向するように載置する。

【0039】

反応室に搬送されたシリコン基板の裏面およびベベル部に、例えばプラズマCVD法を用いて、保護絶縁膜を成長する。保護絶縁膜としては、シリコン酸化膜(SiO2)、シリコン窒化膜(SiN)、シリコン炭窒化膜(SiCN)などを用いることができる。保護絶縁膜を成長するための原料は、TEOS、SiH4、4MS、3MS、有機シラン、有機シロキサン、NH3などを用いることができる。保護絶縁膜の膜厚は10nm〜1μm程度の範囲に設定できる。保護絶縁膜の種類と膜厚は、付着する金属の種類や、濃度、洗浄液でのエッチングレート、付着金属のシリコン中の拡散係数、絶縁膜中の拡散係数などを考慮して適宜設定することができる。例えば、薬液でのエッチングレートを変えるために、絶縁膜はSiC膜や、SiOC膜等に変更しても良い。SiOC膜を形成する場合には有機シロキサン原料を用いることができる。

【0040】

本実施形態における抵抗変化素子は、例えば次のようにして形成することができる。

【0041】

まず、リソグラフィとドライエッチングを用いて、シリコン基板上の層間絶縁層に、シリコン基板上の半導体素子に電気的に接続するプラグを形成するためのスルーホールを形成する。このとき、加工される材料は通常の半導体プロセスに用いられている材料(Si、O、C、Nなどからなる材料)であるため、シリコン基板の裏面やべベル(端面)に汚染金属が付着することはない。

【0042】

つづいて、スルーホールを含むシリコン基板表面側の全面に、抵抗変化素子形成用の金属層および抵抗変化材料層を成長する。例えば固体電解質スイッチを形成する場合には、ポリマー固体電解質、Pt、Taの順に積層する。PtやTaがシリコン基板の表面の所定の範囲以外(すなわち、裏面やべベル(端面))に付着すると、汚染金属として続く工程において装置内に転写し、後続の処理される別のシリコン基板が汚染される。このように、抵抗変化素子形成用の金属層や抵抗変化材料層の形成時に、それらの材料が、シリコン基板の裏面やべベル(端面)にまわりこみ、汚染が発生するが、保護絶縁膜がシリコン基板の裏面およびべベル(端面)に形成されている場合には、汚染金属が直接シリコン基板に付着することはない。

【0043】

続いて、汚染金属を除去するため、裏面洗浄装置を用いて、例えばFPM洗浄により、保護絶縁膜ごと汚染金属を除去(リフトオフ洗浄)する。洗浄処理の条件は、形成した保護絶縁膜のエッチングレートと処理後の金属汚染レベルを確認しながら適宜設定することができる。

【0044】

その後、再び絶縁膜成長装置にて、シリコン基板の裏面およびべベル(端面)へ保護絶縁膜を形成する。

【0045】

つづいて、金属層および抵抗変化材料層を加工するためのリソグラフィを行う。その際、金属層および抵抗変化層の形成時にシリコン基板の裏面およびべベル(端面)に付着した汚染金属は、前述のリフトオフ洗浄により除去されているため、リソグラフィ装置内部に汚染金属が転写することはない。

【0046】

つづいて、金属層および抵抗変化材料層のドライエッチングを行う。例えばTaをエッチングする場合、Taは塩素系ガスを用いた反応性ドライエッチング(RIE)によって反応生成物を気化させてエッチングすることができるが、反応生成物の蒸気圧が低いため、ドライエッチング装置内に付着する。また、Ptをエッチングする場合には、反応生成物が発生しないため物理エッチングが行われ、大半が反応室中に飛散し、反応室内部に付着する。このように付着した汚染金属は、次にエッチングされるべく搬送された後続の処理される別のシリコン基板に転写する。このとき、保護絶縁膜をあらかじめ形成しておくことで、汚染金属が直接シリコン基板に付着することを防止できる。

【0047】

つづいて、ドライエッチング処理に起因する付着した汚染金属を保護絶縁膜とともに除去するため、裏面洗浄装置を用いてリフトオフ洗浄を行う。

【0048】

以上のプロセスによって、抵抗変化素子形成用の金属層や抵抗変化層の形成および加工に伴う、シリコン基板への汚染金属の直接の付着が防止され、また、後続の処理される別のシリコン基板の汚染も防止できる。そのため、抵抗変化素子の形成が完了し、リフトオフ洗浄により保護絶縁膜が除去された後は、通常の半導体製造プロセスを実施することができる。

【0049】

以上に説明したプロセスは、後に図9を用いて説明するプロセスのうち、図9(d)に示されるプロセスに相当する。本発明は、上述のプロセスに限定されるものではなく、本発明の他の実施形態によれば、例えば、図9(a)、図9(b)、図9(c)に示されるプロセスを含む製造方法を提供することができる。

【0050】

[半導体製造装置およびそれを用いた処理方法]

次に、絶縁膜成長装置を含む半導体製造装置およびそれを用いた処理方法について図面を用いて説明する。

【0051】

図1は、本実施形態に用いられる半導体製造装置の一構成例を模式的に示した図である。

【0052】

この装置は、複数の工程の処理が減圧下で実施可能なクラスタ型構造を有する。シリコン基板は、大気ロボット101によってカセットボックス100からロードロック室102に移される。その後、シリコン基板は熱処理を行うため、中央プラットフォーム室103に備えられた中央ハンドラ104によって加熱ステージモジュール105に移される。加熱ステージは、基板温度が200〜400℃の範囲の温度になるよう加熱されている。加熱により基板温度を上昇させるとともに、基板表面に付着した有機物などの除去を行うため、減圧下、不活性ガス雰囲気中で行うことが好ましい。

【0053】

つづいて、シリコン基板は、真空下で保護絶縁膜成長モジュール106に移されて、絶縁膜の成長が行われる。ここでシリコン基板は大気と接触すると大気中の成分が付着してしまうので、減圧下で基板を移送する。その際、中央プラットフォーム室103の圧力は加熱ステージモジュール105や保護絶縁膜成長モジュール106からのガス混入を防ぐため、加熱ステージモジュール105および保護絶縁膜成長モジュール106よりも高い圧力に設定することが好ましく、例えば500mTorr(66.66Pa)程度とすることが好ましい。

【0054】

図2は、本実施形態において保護絶縁膜の形成に使用するプラズマCVD装置の一構成例を示すブロック図である。

【0055】

図2に示すように、プラズマCVD装置は、反応室210、ガス供給部220、真空ポンプ230、および高周波(Radio Frequency:RF)電源240を有する。ガス供給部220は、ガス供給管222を介して反応室210と接続されている。真空ポンプ230は、ガス排出管236を介して反応室210と接続されている。そして、高周波電源240は、高周波ケーブル244を介して反応室210と接続されている。高周波ケーブル244には、マッチングボックス242が設けられている。

【0056】

反応室210内には、基板ステージ203およびシャワーヘッド205が設けられ、これらは互いに対向した状態で配置されている。基板ステージ203にはアース線207が接続されている。また、基板ステージ203にはヒータ(不図示)が設けられている。基板ステージ203は、半導体基板等の被成膜部材201を保持し、被成膜部材201を加熱する。シャワーヘッド205は、ガス供給管222が接続され、ガス供給管222を介して供給されるガスを被成膜部材201に噴射するガス噴出部として機能する。また、シャワーヘッド205には高周波ケーブル244が接続されている。

【0057】

ガス供給部220からガス供給管222を介してシャワーヘッド205に原料ガス等を供給すると共に、高周波電源240で作り出された高周波電力を高周波ケーブル244の途中に配置されたマッチングンボックス242により所定の周波数にしてシャワーヘッド5に供給する。これにより、基板ステージ203とシャワーヘッド205との間の空間のガスがプラズマ化される。

【0058】

ガス供給部220には、使用する原料ガスの種類数に対応する数の原料供給タンクと、添加ガス用のガス供給タンク(以下「ガス供給タンク」と称する)とが設けられている。図2は、ガス供給部220に、TEOS(テトラエトキシシラン)原料が充填された原料供給タンク211が設けられている場合を示している。TOES以外の液体原料として、他の有機シロキサン原料などを用いてもよい。

【0059】

原料供給タンク211には、流量制御部214および気化器219が設けられている。流量制御部214は、2つのバルブ218a、218bと、これらのバルブの間に設けられた流量制御器218とを有する。流量制御部214は配管212を介して気化器に接続されている。気化器219には、キャリアガスとして不活性ガス等を供給するタイプを用いても良い。気化器219は、原料供給タンク211から供給される液状原料を気化し反応室210に供給する。

【0060】

なお、図2に示すように、ガス供給管222にはクリーニングガス供給管228が接続されている。クリーニングガス供給管228には、リモートプラズマユニット224とバルブ226が設けられている。クリーニングガスとしては、NF3、O2、CxFy、それらの2種以上を含む混合ガスを用いることができる。

【0061】

また、各ガスが移送過程で液化するのを防止するために、配管212の周囲およびガス供給管222の周囲にヒータ(不図示)を設け、配管212およびガス供給管222をヒータ(不図示)で加温することもできる。これと同様な理由で、反応室210に供給されたガスの分子が励起される前に液化するのを防止するために、反応室210の周囲にもヒータ(不図示)を設け、反応室210を加温することもできる。

【0062】

次に、上記のプラズマCVD装置を用いた、保護絶縁膜の形成方法の手順を説明する。

【0063】

基板ステージ203上に被成膜部材201を配置した後、真空ポンプ230を動作させ、バルブ232を開いて反応室210を減圧し、反応室210内の初期真空度を数Torrにする(1Torr=約133Pa)。基板ステージ203は、被成膜部材201を加熱し、被成膜部材201の表面温度が所定の温度範囲になる。

【0064】

続いて、原料ガス(ここでは、TEOSの気体)とキャリアガスを混合させたガスを、ガス供給管222を介して反応室210に供給すると共に、高周波電源240およびマッチングボックス242を動作させて所定周波数の高周波電力を反応室210に供給する。

【0065】

反応室210での原料ガスの分圧は0.1〜3Torr(13.3〜400Pa)程度の範囲で維持されることが好ましい。また、真空ポンプ230の動作を制御することで、SiO2膜形成時の反応室10の雰囲気圧力を1〜6Torr(13.3〜800Pa)程度の範囲に維持することが好ましい。

【0066】

また、基板ステージ203の加熱により、被成膜部材201の表面温度は、100〜500℃の範囲で維持されることが好ましい。特に被成膜部材にあらかじめ形成された半導素子や多層配線を劣化させることのない温度として、一般的な多層銅配線の耐熱性限界を考慮して400℃以下で維持されることが好ましい。

【0067】

このような処理条件の下で、原料ガスであるTEOS原料、および酸素がプラズマによって励起され、活性化された状態の原料が酸素と反応し、被成膜部材201の表面に到達し、そこでSiO2膜が形成される。

【0068】

300mm成膜装置におけるTEOS原料を用いた代表的な成膜条件としては、TEOS=160sccm(standard cm3/min)、O2=200sccm、He=100sccm、反応室圧力400Pa、加熱ステージ温度300℃、RF−power=500Wを用いることができる。

【0069】

保護絶縁膜としてシリコン酸化膜を形成する場合には、通常、酸化ガスが用いられるが、シリコン窒化膜を形成する場合には、添加ガスとしてNH3を用いることができる。シリコン炭窒化膜(SiCN膜)を形成する場合には、4MS(テトラメチルシラン)や3MS(トリメチルシラン)を原料ガスとしてNH3を添加することが好ましい。

【0070】

なお、図2には、原料供給タンク211が1つの場合が示されているが、複数の原料供給タンクを設け、複数の種類の原料ガスを用いて保護絶縁膜を形成してもよい。使用する原料ガスは2種類に限らず、3種類以上であってもよい。

【0071】

また、基板ステージ203、真空ポンプ230、流量制御器218、高周波電源240、マッチングボックス242およびバルブ218a、218b、226に対する、上記保護絶縁膜の形成方法の手順に応じた動作指示内容を記述したプログラムを準備し、そのプログラムにしたがってマイクロコンピュータに処理を実行させることで、プラズマCVD装置を制御して保護絶縁膜を形成してもよい。

【0072】

保護絶縁膜の形成の際には、シリコン基板(被成膜部材201)をフリップ(上下反転)して、基板ステージ203に載置する。この基板ステージ203に凹型の専用ステージ(凹型ステージ)を用い、この凹型ステージの凹みがある面とシリコン基板の素子形成面とが対向するように、すなわち、シリコン基板の裏面(素子が形成されていない面)が上側を向くように載置される。このような状態で成膜を行うことにより、シリコン基板の素子形成領域に保護絶縁膜を形成することなく、シリコン基板の裏面およびべベル(端面)に保護絶縁膜を形成することができる。

【0073】

次に、凹型ステージについて説明する。

【0074】

図3に、凹型ステージの断面図(図3(a))及び上面図(図3(b))を示す。凹型ステージ300は、その基板搭載面に凹部を有し、この凹部を囲む外周部(すなわち枠状の凸部)が、載置された所定のシリコン基板(ウェハ)の素子形成領域を囲む外周位置に接する構造を有している。すなわち、シリコン基板を凹型ステージ上に載置した際に、シリコン基板の素子形成領域には凹型ステージが接しないように基板外周部のみに凹型ステージが接触できる構成となっている。シリコン基板として例えば300mmウェハを用いる場合、凹型ステージの寸法は、例えば、外径a=296mm、基板との接触部(凹部の外周部)301の幅c=3mm、凹部の深さ(枠状凸部の高さ)d=5mmとすることができる。凹型ステージ自体も適宜加熱されていることが好ましい。各部品の寸法については、搬送の誤差範囲、および成膜条件によるべベル(端面)への絶縁膜の回り込み状況などをみて適宜設定することができる。

【0075】

次に、図4及び図5を用いて、シリコン基板(ウェハ)の凹型ステージ上への配置について説明する。図4(a)及び図5(a)は断面図、図4(b)及び図5(b)は上面図を示す。図4(b)において、点線で示される円は、シリコン基板400と凹型ステージ300との接触位置の輪郭を示し、図5(b)において、点線で示される円は、シリコン基板400と凹型ステージ300との接触位置の内側の輪郭を示す。凹型ステージは、その外周が、図4に示すようにシリコン基板の外周に対して小さくてもよいし、図5に示すように大きくてもよい。

【0076】

保護絶縁膜形成前のシリコン基板(ウェハ)400は、表面に半導体素子形成領域401を有する。シリコン基板400は、凹型ステージの凹部がある面と半導体素子形成領域が対向するように配置され、凹型ステージの外周部と接触する。この状態で成膜を行うことにより、保護絶縁膜が、基板の裏面402及びベベル403に形成される。凹型ステージ300は、所定のシリコン基板400を載置した際に、シリコン基板の半導体素子形成領域401と凹型ステージの外周部(シリコン基板と接触する部分)301とが接触しないよう設計しておくことが好ましい。このとき、凹型ステージ上にあらかじめ絶縁膜を成長した後に、シリコン基板を搬送してもよい。清浄な絶縁膜で保護することで、接触面を介したシリコン基板への金属汚染の転写を防ぐことができる。

【0077】

図4(a)及び図5(a)に示す状態で成膜処理を行うと、それぞれ図4(c)及び図5(c)に示すように、保護絶縁膜410が、シリコン基板400の裏面402及びベベル403に形成される。その際、凹型ステージ300でカバーされている素子形成領域401には、保護絶縁膜は形成されない。保護絶縁膜が形成されたシリコン基板は凹型ステージが動作することで、中央ハンドラ104に吸着され、ロードロック室102に移され、ロードロック室102が大気解放された後に、大気圧ロボット101によってロードロック室102からカセットボックス100へ戻される。

【0078】

凹型ステージ上へのシリコン基板のチャック方法について図6を用いて説明する。図6(a)は断面図であり、図6(b)は上面図であり、図6(c)は図6(a)の点線で囲まれた部分の拡大図である。

【0079】

図6(a)、(c)に示すように、凹型ステージ300の外周部(シリコン基板400と接触する部分)に真空チャックライン600を設けることで、凹型ステージ上にシリコン基板を固定することができる。凹型ステージの外周部における真空チャック部601、602、603は、図6(b)に示すように設けることができるが、図に示される数および位置に限定されない。

【0080】

上記の説明では、シリコン基板の裏面およびべベル(端面)に保護絶縁膜の形成において、原料にTEOSを用い、成膜方法としてRF電源を用いたプラズマCVDの場合について詳しく述べたが、これらに限定されるものではない。金属汚染の拡散を防止するための保護絶縁膜としてはより緻密な膜が望ましいことから、基板温度が低い状態でもより緻密な絶縁膜の形成が可能な、HDPプラズマによるプラズマCVD法や、プラズマALD法などの成膜手法を用いることもできる。

【0081】

[固体電解質スイッチの形成方法]

次に、本実施形態における抵抗変化素子の形成方法として、固体電解質スイッチの場合を例に挙げて説明する。

【0082】

図7は、固体電解質スイッチの断面構造を示す模式図である。この固体電解質スイッチは、活性電極701、不活性電極702、およびそれらの間に挟まれた固体電解質(イオン電導層)703とを含む。このような構造を持つ固体電解質スイッチとしては、例えば、NanoBridge(登録商標)が挙げられる。

【0083】

活性電極701は、抵抗変化動作時に金属架橋を形成するための金属を供給する電極であり、Cu(銅)やAg(銀)などが用いられる。不活性電極702は、抵抗変化動作時に金属架橋が接続される電極であり、金属架橋とは化学反応を生じない電極であることが好ましく、Pt(白金)やRu(ルテニウム)が用いられる。固体電解質703は、イオン化された金属が移動し、内部に金属架橋を形成するための媒体であり、酸化タンタル、酸化ハフニウム、酸化ジルコニウム、酸化シリコン、有機ポリマー、およびこれらから選ばれる2種以上の混合物などを用いることができる。

【0084】

このような固体電解質スイッチは、活性電極用のCu、ポリマー固体電解質、不活性電極用のPtを用いた場合、例えば次のようにして形成することができる。

【0085】

不活性電極用のPtは、融点、沸点が高く、反応生成物を生成しないため除去が困難である。そのため、あらかじめ本実施形態による保護絶縁膜の形成方法により、シリコン基板の裏面およびべベル(端面)へ保護絶縁膜を形成する。

【0086】

活性電極用のCuは、半導体素子が設けられたシリコン基板上に設けられた銅配線を利用する。この銅配線上の絶縁膜にスルーホールを形成し、このスルーホールを含む表面上にポリマー固体電解質をプラズマCVD法で形成し、その上にスパッタリング法によりPt(10nm)を堆積する。このとき、スパッタリングチャンバにおいてエッジカットリングを搭載することで、基板裏面およびべベル(端面)への汚染金属の周り込みを回避した場合には、本実施形態による保護絶縁膜を形成しておかなくてもよい。ポリマー固体電解質は炭化水素から構成させる膜であり、SiOを含んでいても良い。

【0087】

つづいて、リソグラフィ技術及びドライエッチング技術により、Pt及びポリマー固体電解質を所定の形状にパターニングする。

【0088】

その後、スピン洗浄機によって裏面およびベベル上の保護絶縁膜を除去する。

【0089】

このように、抵抗変化素子の形成時に、本発明の実施形態による保護絶縁膜を形成しておくことで、金属のシリコン基板への直接の付着を防止することができる。

【0090】

[MRAMの形成方法]

次に、本実施形態における抵抗変化素子の形成方法として、MRAMの場合を例に挙げて説明する。

【0091】

図8は、MRAM記憶素子の断面構造を示す模式図である。この記憶素子(抵抗変化素子)は、下部磁性体層801、上部磁性体層802、およびそれらの間に挟まれたトンネル絶縁層803とを含む。

【0092】

下部磁性体層は、磁化方向が変更しない固定磁性層である。上部磁性層は、その磁化方向がセルのビット状態を変更し得るように切り替えられる自由磁化層である。上部磁性層の磁化が下部磁性層の磁化と並行な場合、セルの抵抗は低くなり、反平行な場合は高くなる。

【0093】

下部磁性体層801は、例えば、下から順にパーマロイ(Ni−Fe)で形成された初期磁性体層、Ir−Mnで形成された反強磁性体層、Co−Fe−Bで形成された固定強磁性層で形成される。典型的な初期磁性体層、反強磁性体層、および固定強磁性の厚さは、それぞれ、2nm、10nm、3nm程度を選択することができる。

【0094】

トンネル絶縁層803は、アルミナ(Al2O3)やマグネシア(MgO)などが用いられ、その厚さは1〜3nm程度に設定できる。

【0095】

上部磁性体層は、例えば、下から順にNi−Feで形成された自由磁性層、第一タンタル層、アルミ層、および第二タンタル層で形成することができる。

【0096】

これらの層の形成前に、本発明に実施形態による保護絶縁膜を形成しておく。

【0097】

これらの層を形成した後、リソグラフィ技術及びドライエッチング技術により所定の形状にパターニングする。

【0098】

その後、スピン洗浄機によって裏面およびベベル上の絶縁膜を除去する。

【0099】

このように、抵抗変化素子の形成時に、本発明の実施形態による保護絶縁膜を形成しておくことで、金属のシリコン基板への直接の付着を防止することができる。

【0100】

[保護絶縁膜の形成とリフトオフ洗浄を含むプロセス]

前述の通り、抵抗変化素子の成膜工程および加工(ドライエッチング)工程において、金属が、基板の裏面やべベル(端面)に付着する。この問題を解決するプロセス(保護絶縁膜の形成、リフトオフ洗浄工程)について、図9を用いてさらに説明する。図9は、保護絶縁膜の形成とリフトオフ洗浄を含む工程フロー図である。

【0101】

図9(a)は、抵抗変化素子の成膜工程における汚染金属の付着を、保護絶縁膜形成以外の方法(例えばスパッタリング時のエッジカットリングなど)で防止する場合の工程フローを示す。この工程フローにおいては、保護絶縁膜の形成を抵抗変化素子の成膜工程後に行う。つづいてリソグラフィとドライエッチングにより抵抗変化素子の加工工程を行い、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成とリフトオフ洗浄は各1回行うことになる。

【0102】

図9(b)の工程フローでは、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。そして、抵抗変化素子の成膜工程に引き続き、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成とリフトオフ洗浄は各1回行うことになる。

【0103】

図9(c)は、図9(b)と同様に、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。このとき、成膜時になんらかの金属付着防止対策を実施しない場合には、基板の裏面やべベル(端面)に金属が付着する。つづいて、基板の洗浄を行うことなく、保護絶縁膜を形成する。その際、基板に付着していた金属は保護絶縁膜の内部に捕獲される。つづいて、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成を2回、リフトオフ洗浄を1回行うことになる。

【0104】

図9(d)は、図9(b)及び図9(c)と同様に、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。引き続き、リフトオフにより保護絶縁膜を除去(リフトオフ洗浄)した後、再び保護絶縁膜を形成する。つづいて、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、抵抗変化素子の成膜工程に対して、保護絶縁膜形成とリフトオフ洗浄を各1回、抵抗変化素子の加工工程に対して、保護絶縁膜形成とリフトオフ洗浄を各1回行うことになる。このような工程フローによれば、基板を常にクリーンな状態に維持できる利点がある。

【0105】

リフトオフ洗浄については、枚葉スピン洗浄機とFPM洗浄液(0.1〜0.5%HF、0.1〜0.5%H2O2)を用いて、基板の裏面とべベル(端面)部の洗浄を行うことができる。回転する基板の表面上方より基板表面に乾燥窒素あるいは純水を吹き付けつつ、基板の裏面および基板裏面端部に洗浄液を噴射することで、基板外方向に向かう乾燥窒素または純水の流れにより洗浄液の基板表面への回り込みを防止ししながら裏面洗浄を行うことができる。洗浄後は純水を噴射することで基板に付着した薬液を除去することができる。FPMに加えて、半導体プロセスで一般に用いられている薬液、例えばHPM洗浄液(HCl/H2O2/H2O)、SPM洗浄液(H2SO4/H2O2)、FPM洗浄液(HF/H2O2/H2O)、DHF洗浄液(HF/H2O)、BHF洗浄液(HF/NH4F/H2O)などを適宜組み合わせても良い。

【0106】

各工程毎に基板裏面の金属汚染レベルをあらかじめ測定しておくことで、図9(a)〜(d)のいずれかの工程フロー、もしくはいずれかをベースにした工程フローを適用することで、工程数の増加を抑えた製造プロセスを提供することができる。

【実施例】

【0107】

以下、本発明について、実施例を挙げてさらに具体的に説明する。

【0108】

(実施例1)固体電解質スイッチを含む半導体装置の製造方法

本実施例では、抵抗変化素子として固体電解質スイッチを備えた半導体装置の製造方法について説明する。

【0109】

図10は、固体電解質スイッチ及び保護絶縁膜の形成前の、半導体素子が形成されたシリコン基板の断面模式図である。

【0110】

シリコン基板500上にMOSFET599が形成され、MOSFET599のゲート、ソース及びドレインはそれぞれTiN531で被覆されたタングステンプラグ532により、上層側の銅配線に接続されている。銅配線はCu534とCuを囲むTa/TaN533(積層バリアメタル)からなる。配線層間絶縁膜は比誘電率3以下のSiOCH膜513が用いられている。銅配線の上面には、保護膜としてプラズマCVDにより形成したSiCN膜514が設けられている。最上層の銅配線上には保護膜としてSiCN膜520が形成され、その上にスルーホール加工用のシリコン酸化膜520aが形成されている。

【0111】

ここで、基板の最表面はシリコン酸化膜520aによって被覆しているため、裏面スピン洗浄の際に、乾燥窒素や純水に暴露されても問題は生じない。

【0112】

つづいて本発明の実施形態による絶縁膜成長装置をもちいて、基板の裏面およびベベル(端面)に保護絶縁膜(シリコン酸化膜)(図示せず)を1μm成長した。このとき、半導体素子形成領域には保護絶縁膜が成長しないため、図10の断面構造に変化はない。

【0113】

つづいて、図11に、多層配線構造内に抵抗変化素子598が設けられたシリコン基板の断面図を示す。図12には、図11に示される抵抗変化素子598及びその周辺部の拡大図を示す。

【0114】

シリコン酸化膜520a上にリソグラフィとドライエッチングによってホールを形成し、このホールを含むシリコン基板全面に抵抗変化素子形成用の積層膜を形成する。図12に示す固体電解質スイッチを形成する場合、この積層膜の各層は、下からポリマー固体電解質591、Pt電極592、Ta電極593に対応する。Pt電極層及びTa電極層はスパッタリング法で形成し、膜厚はそれぞれ、10nm、25nmとした。このとき、スパッタリングにおけるエッジカットリングシールドの幅を5mmに設定し、基板の裏面及びベベル(端面)へのPt及びTaの付着を防いだ。

【0115】

つづいてリソグラフィとドライエッチングによって抵抗変化素子形成用の積層膜を加工した。例えば、ECRプラズマ源を用いたRIE装置を使用し、ソース/バイアス電力400W/200W、Ar=100sccm、反応室圧力0.3Pa、基板温度150℃に設定し、RIEを行い、有機ポリマー層についてはCF4=100sccmにてRIEを行った。

【0116】

その後、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。

【0117】

上記のRIEによる加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、リフトオフ洗浄しないで、全反射蛍光X線分析(TREX)を用いて基板裏面の金属汚染濃度を分析したところ、この基板の裏面から、Ptについて1×1016atom/cm2レベル以上の汚染が検出された。

【0118】

これに対し、上記の加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。その後、上記と同様にして基板裏面の金属汚染濃度を測定したところ、Ptについては検出下限以下であった。すなわち、本発明の実施形態にしたがって保護絶縁膜を形成し、リフトオフ洗浄を実施して保護絶縁膜を除去することで、抵抗変化素子の加工工程に起因する基板の金属汚染を防ぐことができることを確認した。

【0119】

(実施例2)MRAMを含む半導体装置の製造方法

本実施例では、抵抗変化素子としてTMR素子を用いたMRAMを備えた半導体装置の製造方法について説明する。本実施例は、抵抗変化素子の構成が異なること以外は実施例1と同様にして半導体装置を製造することができる。

【0120】

下部電極上に、Ta(10nm)/PtMn(10nm)/Co90Fe10(2.5nm)/Ru(0.85nm)/Co40Fe40B20(5nm)/MgO(2.5nm)/Co40Fe40B20(3nm)/Ta(10nm)/Ru(7nm)/NiFe(20nm)/Ta(5nm)をスパッタリング法で形成した。このとき、スパッタリングチャンバにおいてエッジカットリングを搭載することで、基板の裏面及びべベル(端面)への汚染金属の付着を回避できる。

【0121】

次に、上記の成膜工程を実施した後、下記の問題を回避するため、本発明の実施形態による絶縁膜成長装置を用いて、基板の裏面およびべベル(端面)上へ保護絶縁膜(SiO2)を形成した。その後、上記の成膜工程により形成された積層膜をリソグラフィとドライエッチングによって加工を行う。

【0122】

SiやAlなどの通常の半導体プロセスに用いられている材料は、それらの塩化物の融点、沸点が低く、高い蒸気圧を有するため、塩素系ガスを用いたRIEによって加工して素子形成を行うことができる。一方、強磁性体金属材料であるFe、Co、Niの塩化物は融点、沸点が高く、蒸気圧も低いため反応生成物の除去が困難である。一般に被加工物の温度を上げた昇温RIEや、CO/NH3混合ガスなどによるRIEが提案されているが、加工性は向上されつつあるものの、エッチング生成物の反応室内への再付着によるシリコン基板への転写が問題となっている。

【0123】

保護絶縁膜の形成後、リソグラフィとドライエッチングにより、所定の形状に前記積層膜を加工する。例えば、ECRプラズマ源を用いたRIE装置を使用し、ソース/バイアス電力800W/200W、CO=100sccm、NH3=100sccm、反応室圧力:0.5Pa、基板温度:室温に設定し、NiFe、CoFeBのRIEを行い、それ以外の層についてはCl2=120sccmにてRIEを行った。

【0124】

その後、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。

【0125】

上記のRIEによる加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、リフトオフ洗浄しないで、全反射蛍光X線分析(TREX)を用いて基板裏面の金属汚染濃度を分析したところ、この基板の裏面から、Feについて1×1016atom/cm2レベルの汚染が検出された。

【0126】

これに対し、上記の加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。その後、上記と同様にして基板裏面の金属汚染濃度を測定したところ、全ての評価金属について検出下限以下であった。すなわち、本発明の実施形態により保護絶縁膜を形成し、リフトオフ洗浄を実施して保護絶縁膜を除去することで、抵抗変化素子の加工工程に起因する基板の金属汚染を防ぐことができることを確認した。

【0127】

また、保護絶縁膜としてSiO2膜に代えてSiN膜を用いた場合にも同様の効果が得られることを確認した。

【0128】

以上の説明においては、好適な実施形態および実施例を挙げて本発明を説明したが、これら実施形態および実施例は、本発明を説明するためのものであって、これらに限定することを意味するものではない。半導体基板上に形成する抵抗変化素子の例として、固体電解質スイッチやMRAMについて説明したが、本発明はそれらに限定されるものではない。

【0129】

本発明は、半導体装置を形成する際に、基板の裏面やべベル(端面)への金属の付着・転写を防止することができ、金属の付着の防止が必要なプロセス、例えば、DRAM(Dynamic RAM)、FRAM(Ferro Electric RAM)、PRAM(Phase-change RAM)、RRAM(Resistive RAM)を有する半導体製品の製造方法、マイクロプロセッサなどの論理回路を有する半導体製品の製造方法へも適用することができる。また、本発明の基板の裏面に絶縁膜を成長できるという特徴を生かして、半導体装置に対する、電子回路装置、光回路装置、量子回路装置、マイクロマシン、MEMS(Micro Electro Mechanical Systems)などの製造にも適用することができる。

【0130】

以上、実施形態および実施例を参照して本発明を説明したが、本発明は上記実施形態および実施例に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更をすることができる。

【符号の説明】

【0131】

100 カセットボックス

101 大気ロボット

102 ロードロック室

103 中央プラットフォーム室

104 中央ハンドラ

105 加熱ステージモジュール

106 保護絶縁膜成長モジュール

201 被成膜部材

203 基板ステージ

205 シャワーヘッド

207 アース線

210 反応室

211 原料供給タンク

212 配管

214 流量制御部

218 流量制御器

218a、218b バルブ

219 気化器

220 ガス供給部

222 ガス供給管

224 リモートプラズマユニット

226 バルブ

228 クリーニングガス供給管

230 真空ポンプ

232 バルブ

236 ガス排出管

240 高周波電源

242 マッチングンボックス

244 高周波ケーブル

300 凹型ステージ

301 接触部

400 シリコン基板

401 半導体素子形成領域

402 基板裏面

403 ベベル

410 保護絶縁膜

500 シリコン基板

511、526 シリコン酸化膜

512、514、516、518、520、521、523 SiCN膜

513、515、517、519、524、525、522 SiOCH膜

520a シリコン酸化膜

520b SiN

526 シリコン酸化膜

527 シリコン酸窒化膜

531 TiN

532 タングステン

533、535、539、541、543、545、547、549 Ta/TaN

534、536、540、542、544、546、548 Cu

550 Al−Cu

591 ポリマー固体電解質

592 Ta

593 Pt

598 抵抗変化素子

599 MOSFET

600 真空チャックライン

601、602、603 真空チャック部

701 活性電極

702 不活性電極

703 固体電解質

801 下部磁性体層

802 上部磁性体層

803 トンネル絶縁層

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

シリコンデバイスを含む半導体デバイスは、Mooreの法則で知られるスケーリング則の微細化によって集積化・低電力化が進められ、「3年で4倍の集積化を図る」というペースで開発が進められてきた。近年、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のゲート長は20nm以下となり、リソグラフィプロセスにおけるコストの高騰、およびデバイス寸法の物理的限界により、これまでのスケーリング則とは異なるアプローチでのデバイス性能の改善が求められている。リソグラフィプロセスにおけるコストの高騰には、製造装置およびマスクセットの価格の高騰が挙げられる。また、デバイス寸法の物理的限界には、動作限界および寸法ばらつき限界が挙げられる。

【0003】

近年、半導体装置の性能改善手法の一つとして、半導体装置内部に半導体素子以外の能動素子、例えば抵抗変化素子を、メモリあるいはスイッチとして設けることが行われている。

【0004】

このような抵抗変化素子としては、遷移金属酸化物を用いたRRAM(Resistance RAM [Random Access Memory])や、イオン伝導体を用いた固体電解質スイッチなどがある。イオン伝導体は、イオンが電界などの印加によって自由に動くことのできる固体である。その他にも、FRAM(Ferro Electric RAM)、MRAM(Magnetic RAM)、PRAM(Phase-change RAM)などの開発が進められている(非特許文献1)。

【0005】

このようなスイッチング素子は、MOSFETなどの半導体素子よりもサイズが小さいため、同じ機能を実現するための占有面積を小さくすることができ、ゲートの充放電や配線に起因する動作時の消費電力(Dynamic power)を小さくすることができる。さらに、SRAM(Static RAM)やDRAM(Dynamic RAM)は、電源がオフになると記憶状態が消去されてしまう揮発性素子であるのに対して、抵抗変化素子は、電源をオフにしても記憶状態が保持される不揮発性素子であるため、待機時の消費電力(Static power)も低減できる。

【0006】

加えて、固体電解質スイッチは、さらにオン抵抗が小さいという特徴を持っている。そのため、固体電解スイッチは、スイッチ自体を信号線に用いる、不揮発なプログラマブルロジックデバイスへの適用に有望であると考えられている(非特許文献2)。

【0007】

一方、特許文献1には、半導体装置の製造方法において、熱処理時の半導体基板(シリコン基板)の裏面側からの半導体構成原子(シリコン)の昇華を防止するために、半導体基板の表面側および裏面側を覆うように絶縁膜を形成し、半導体基板の表面側の絶縁膜をエッチング除去し、半導体基板の裏面側に絶縁膜が存在している状態で、半導体基板を熱処理することが記載されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−152920号公報

【非特許文献】

【0009】

【非特許文献1】R. Nebashi, et al., "A 90nm 12ns 32Mb 2T1MTJ MRAM", IEEE Solid-State Circuits Conference-Digest of Technical Papers, 8-12 Feb. 2009, pp.462-463,463a.

【非特許文献2】M. Tada, et al., "Nonvolatile Crossbar Switch Using TiOx/TaSiOy Solid-Electrolyte", IEEE Transactions on Electron Devices, vol. 57, no.8, pp.1987-1995 2010.

【発明の概要】

【発明が解決しようとする課題】

【0010】

近年、上記のRRAM、MRAM、PRAMに代表される抵抗変化素子には、通常のシリコン半導体プロセスに用いられていない重金属や貴金属(例えばFe、Ru、Mg)からなる膜が用いられている。このような膜は、半導体プロセスにおいて加工する際、通常は反応性ドライエッチング(Reactive Ion Etching:RIE)を用いて加工する。しかしながら、反応生成物の蒸気圧が低い場合、あるいは反応生成物が形成されない金属が含まれる場合、半導体素子を形成したシリコン基板の裏面やべベル(端面)部に成膜材料の金属が容易に付着する。シリコン基板に付着した金属は、プロセス中に発塵の原因になるとともに、後工程のプロセスにおける熱の印加によりシリコン基板中を拡散し、シリコン内に深い準位が形成され、ゲート絶縁膜を有するシリコン半導体素子の閾電圧の変化による誤動作や、ライフタイムの劣化による信頼性の低下を招く。また、金属が付着したままプロセス装置にて加熱を行った場合、昇華した金属が温度センサ等に付着し、プロセス装置の誤動作が発生しやすくなる。

【0011】

このような問題を解決するため、半導体素子形成領域以外のシリコン基板の裏面やべベル(端面)に成膜材料の金属が付着しないプロセス、あるいは付着しても容易に除去ができる手法が必要である。

【0012】

しかしながら、Ni、Pd、Co、Fe、Ptなどに代表される金属は薬液による除去が難しい。このような金属は、例えば王水(濃塩酸と濃硝酸との体積比3:1の混合液)などの洗浄力の強い薬液を用いると除去することができるが、付着金属の除去能力が高まる一方で母材であるシリコン基板裏面に荒れが生じ、先端微細半導体露光装置における焦点深度が不安定になる。

【0013】

一方、基板表面にシリコン窒化膜やシリコン酸化膜などの絶縁膜を形成し、絶縁膜表面に付着した金属をHPM(HCl、H2O2、H2Oを含む混合液)により除去したり、FPM(HF、H2O2、H2Oを含む混合液)により絶縁膜ごと付着した金属を除去(リフトオフ)したりする手法が知られている。しかしながら、この手法を半導体素子の形成された基板へ適用するためには、半導体素子の形成されていない面(基板の裏面)にのみに選択的に絶縁膜を形成する必要がある。

【0014】

基板の裏面にのみ絶縁膜を設けるためには、例えば特許文献1に記載されているように、熱CVD法を用いて基板の表裏面に同時に絶縁膜を成長した後、基板の表面側の絶縁膜を薬液により選択的に除去(ウェットエッチング)する手法がある。しかしながら、抵抗変化素子を半導体素子の上層側に形成するプロセスにおいては、半導体基板上に銅等の金属および層間絶縁膜を含む多層配線構造があらかじめ形成されているため、薬液による表面側絶縁膜を除去する際に、多層配線構造の金属および層間絶縁膜が劣化する。

【0015】

本発明の目的は、上述の問題を解決し、半導体装置の製造において基板の金属汚染を抑えることにある。

【課題を解決するための手段】

【0016】

本発明の一態様による半導体装置の製造方法は、半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、

前記半導体素子形成面に設けられた金属含有膜を加工する工程と、

前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む。

【0017】

本発明の他の態様による半導体製造装置は、上記の製造方法に用いられる製造装置であって、

減圧下で前記保護膜を形成するための成膜室と、

前記基板を載置するためのステージと、

前記成膜室へ前記基板を搬送するためのアームとを有し、

前記ステージは、基板搭載面に凹部を有し、該凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触できる形状を有し、

前記アームは、前記基板の裏面に接触し、該アームが回転することで該基板をフリップし、該基板の半導体素子形成面を前記ステージの基板搭載面に向けて載置する機構を備えていることを特徴とする。

【発明の効果】

【0018】

本発明によれば、半導体装置の製造において、半導体基板の金属汚染を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施形態における半導体製造装置の構成を説明するための概略図である。

【図2】本発明の実施形態における絶縁膜成長装置の構成を説明するための図である。

【図3】本発明の実施形態における凹型ステージの形状を説明するための図である。

【図4】本発明の実施形態における凹型ステージにシリコン基板を設置した状態、及び保護絶縁膜を成長した状態を説明するための図である。

【図5】本発明の実施形態における凹型ステージ上にシリコン基板を設置した状態、及び保護絶縁膜を成長した状態を説明するための図である。

【図6】本発明の実施形態における凹型ステージに設けられた真空チャックラインを説明するための図である。

【図7】本発明の実施形態における固体電解質スイッチ素子を説明するための断面図である。

【図8】本発明の実施形態におけるMRAM素子を説明するための断面図である。

【図9】本発明の実施形態における保護絶縁膜形成工程と保護絶縁膜除去工程とを含む工程フロー図である。

【図10】本発明の実施形態における、抵抗変化素子形成前の半導体素子が形成されたシリコン基板の断面図である。

【図11】本発明の実施形態における、抵抗変化素子と半導体素子が形成されたシリコン基板の断面図である。

【図12】図11に示す抵抗変化素子の拡大断面図である。

【発明を実施するための形態】

【0020】

本発明の一実施形態による半導体装置の製造方法は、半導体素子が形成された基板(例えばウェハ等の半導体基板)の、半導体素子形成面とは反対側の裏面および端部(べベル部)に保護膜を形成する工程と、半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程を含む。

【0021】

上記の金属含有膜の加工は、RIE等のドライエッチングにより行うことができる。

【0022】

上記の保護膜の除去工程においては、保護膜に付着した、前記金属含有膜に由来の金属成分とともに保護膜を除去することができる。

【0023】

本実施形態によれば、半導体素子の信頼性を高く維持したまま、抵抗変化素子を混載することができるようになり、半導体装置の高機能化および低電力化を図ることができる。

【0024】

上記の保護膜の形成は、400℃以下で行うことが好ましい。これにより、基板上にあらかじめ形成されている半導体素子や多層配線の熱に起因する劣化を抑えることができる。

【0025】

上記の保護膜の形成工程において、前記基板は、成膜ステージ(基板ステージ)上に、半導体素子形成面を成膜ステージの基板搭載面に向けて載置することができる。その際、成膜ステージは、基板搭載面に凹部を有し、この成膜ステージの基板搭載面の、前記凹部を囲む外周部が、前記基板の素子形成領域に接触しないようにその素子形成領域を囲む外周位置に接触することができる。以下、このような成膜ステージを「凹型ステージ」という。これにより、半導体素子形領域に保護膜が形成されることなく、基板の裏面および端部に選択的に保護膜を形成できる。また、素子形成領域がステージと直接接しないため、ステージからのパーティクルや金属汚染物質の付着が抑制できるとともに、スクラッチなどの機械的なダメージの発生を防止することができる。

【0026】

保護膜の形成においては、CVD法、プラズマCVD法、ALD法、プラズマALD法を用いることが好ましい。凹型ステージを用いた場合、半導体基板と凹型ステージとの接触面積が小さくなり、通常のステージに比べて基板の温度を高く維持しにくくなるが、これらの成膜方法を用いることにより、特に高密度プラズマ源を用いたプラズマCVD法やプラズマALD法を用いることにより、基板温度が低温であっても緻密な保護膜を形成できる。

【0027】

凹型ステージを用いた保護膜の形成においては、基板を、あらかじめ別のステージで所定の温度まで加熱した後に、凹型ステージへ搬送し、保護膜の形成を行うことが好ましい。その際、基板の裏面に接触する搬送アームによって基板を加熱ステージに搬送し、所定の温度に加熱し、その後、基板の裏面に接触させたアームによって加熱ステージから基板を取り出すことができる。

【0028】

凹型ステージ上へ基板を載置する際には、基板の裏面に接触しているアームを回転させることで基板をフリップし、半導体素子形成面が凹型ステージの凹みがある面(基板搭載面)に対向するように凹型ステージ上に載置し、この状態にて反応室(成膜室)内で保護膜を形成することが好ましい。

【0029】

前記保護膜として、シリコン酸化膜、シリコン窒素化膜、又はシリコン炭窒化膜を形成することができる。

【0030】

前記保護膜の除去は、薬液を用いた枚葉式スピン洗浄により実施することができる。

【0031】

本実施形態の製造方法は、前記金属含有膜が、Pt、Pd、Ni、Fe、Co、Ru、Mn、Mg、Ta、Ir、B、Ge、Te、Se、Sbから選ばれる少なくとも一種の金属を含む場合に、より効果的である。

【0032】

本実施形態の製造方法は、上記の金属含有膜の加工工程を含む、MRAM、PRAM、RRAM、FRAM、固体電解質スイッチ等の抵抗変化素子の形成工程を含む場合に、より効果的である。

【0033】

以下、本発明の好適な実施の形態についてさらに説明する。

【0034】

半導体素子の形成されたシリコン基板(ウェハ)上には、多層配線層と層間絶縁膜を含む多層配線構造を設けることができる。そして、この多層配線構造内に抵抗変化素子を設けることができる。

【0035】

本実施形態において、保護膜の形成は、抵抗変化素子の形成プロセスにおける金属含有膜のドライエッチング工程(以下「抵抗変化素子の加工工程」)の前に行う。

【0036】

保護膜の形成は、絶縁膜成長装置を用いて、例えば次のようにして行うことができる。

【0037】

絶縁膜成長装置は、基板ステージとして凹型ステージを備え、この凹型ステージは凹みがある面を上に向けて設置されている。シリコン基板は、この凹型ステージ上に、素子形成面と凹型ステージの凹みがある面とが対向するように(すなわち素子形成面を下に向けて、裏面を上に向けて)載置される。その際、凹型ステージの外周のみがシリコン基板と接触し、半導体素子形成領域は凹型ステージと接触しない。この状態で成膜処理を行うことにより、半導体素子形成領域には保護絶縁膜が形成されず、基板の裏面およびベベルに保護絶縁膜が形成される。

【0038】

凹型ステージ上へのシリコン基板の搬送は、シリコン基板の裏面に接触するアームによって行われ、アームを回転させることでシリコン基板をフリップし、半導体素子形成面を凹型ステージの凹みがある面に対向するように載置する。

【0039】

反応室に搬送されたシリコン基板の裏面およびベベル部に、例えばプラズマCVD法を用いて、保護絶縁膜を成長する。保護絶縁膜としては、シリコン酸化膜(SiO2)、シリコン窒化膜(SiN)、シリコン炭窒化膜(SiCN)などを用いることができる。保護絶縁膜を成長するための原料は、TEOS、SiH4、4MS、3MS、有機シラン、有機シロキサン、NH3などを用いることができる。保護絶縁膜の膜厚は10nm〜1μm程度の範囲に設定できる。保護絶縁膜の種類と膜厚は、付着する金属の種類や、濃度、洗浄液でのエッチングレート、付着金属のシリコン中の拡散係数、絶縁膜中の拡散係数などを考慮して適宜設定することができる。例えば、薬液でのエッチングレートを変えるために、絶縁膜はSiC膜や、SiOC膜等に変更しても良い。SiOC膜を形成する場合には有機シロキサン原料を用いることができる。

【0040】

本実施形態における抵抗変化素子は、例えば次のようにして形成することができる。

【0041】

まず、リソグラフィとドライエッチングを用いて、シリコン基板上の層間絶縁層に、シリコン基板上の半導体素子に電気的に接続するプラグを形成するためのスルーホールを形成する。このとき、加工される材料は通常の半導体プロセスに用いられている材料(Si、O、C、Nなどからなる材料)であるため、シリコン基板の裏面やべベル(端面)に汚染金属が付着することはない。

【0042】

つづいて、スルーホールを含むシリコン基板表面側の全面に、抵抗変化素子形成用の金属層および抵抗変化材料層を成長する。例えば固体電解質スイッチを形成する場合には、ポリマー固体電解質、Pt、Taの順に積層する。PtやTaがシリコン基板の表面の所定の範囲以外(すなわち、裏面やべベル(端面))に付着すると、汚染金属として続く工程において装置内に転写し、後続の処理される別のシリコン基板が汚染される。このように、抵抗変化素子形成用の金属層や抵抗変化材料層の形成時に、それらの材料が、シリコン基板の裏面やべベル(端面)にまわりこみ、汚染が発生するが、保護絶縁膜がシリコン基板の裏面およびべベル(端面)に形成されている場合には、汚染金属が直接シリコン基板に付着することはない。

【0043】

続いて、汚染金属を除去するため、裏面洗浄装置を用いて、例えばFPM洗浄により、保護絶縁膜ごと汚染金属を除去(リフトオフ洗浄)する。洗浄処理の条件は、形成した保護絶縁膜のエッチングレートと処理後の金属汚染レベルを確認しながら適宜設定することができる。

【0044】

その後、再び絶縁膜成長装置にて、シリコン基板の裏面およびべベル(端面)へ保護絶縁膜を形成する。

【0045】

つづいて、金属層および抵抗変化材料層を加工するためのリソグラフィを行う。その際、金属層および抵抗変化層の形成時にシリコン基板の裏面およびべベル(端面)に付着した汚染金属は、前述のリフトオフ洗浄により除去されているため、リソグラフィ装置内部に汚染金属が転写することはない。

【0046】

つづいて、金属層および抵抗変化材料層のドライエッチングを行う。例えばTaをエッチングする場合、Taは塩素系ガスを用いた反応性ドライエッチング(RIE)によって反応生成物を気化させてエッチングすることができるが、反応生成物の蒸気圧が低いため、ドライエッチング装置内に付着する。また、Ptをエッチングする場合には、反応生成物が発生しないため物理エッチングが行われ、大半が反応室中に飛散し、反応室内部に付着する。このように付着した汚染金属は、次にエッチングされるべく搬送された後続の処理される別のシリコン基板に転写する。このとき、保護絶縁膜をあらかじめ形成しておくことで、汚染金属が直接シリコン基板に付着することを防止できる。

【0047】

つづいて、ドライエッチング処理に起因する付着した汚染金属を保護絶縁膜とともに除去するため、裏面洗浄装置を用いてリフトオフ洗浄を行う。

【0048】

以上のプロセスによって、抵抗変化素子形成用の金属層や抵抗変化層の形成および加工に伴う、シリコン基板への汚染金属の直接の付着が防止され、また、後続の処理される別のシリコン基板の汚染も防止できる。そのため、抵抗変化素子の形成が完了し、リフトオフ洗浄により保護絶縁膜が除去された後は、通常の半導体製造プロセスを実施することができる。

【0049】

以上に説明したプロセスは、後に図9を用いて説明するプロセスのうち、図9(d)に示されるプロセスに相当する。本発明は、上述のプロセスに限定されるものではなく、本発明の他の実施形態によれば、例えば、図9(a)、図9(b)、図9(c)に示されるプロセスを含む製造方法を提供することができる。

【0050】

[半導体製造装置およびそれを用いた処理方法]

次に、絶縁膜成長装置を含む半導体製造装置およびそれを用いた処理方法について図面を用いて説明する。

【0051】

図1は、本実施形態に用いられる半導体製造装置の一構成例を模式的に示した図である。

【0052】

この装置は、複数の工程の処理が減圧下で実施可能なクラスタ型構造を有する。シリコン基板は、大気ロボット101によってカセットボックス100からロードロック室102に移される。その後、シリコン基板は熱処理を行うため、中央プラットフォーム室103に備えられた中央ハンドラ104によって加熱ステージモジュール105に移される。加熱ステージは、基板温度が200〜400℃の範囲の温度になるよう加熱されている。加熱により基板温度を上昇させるとともに、基板表面に付着した有機物などの除去を行うため、減圧下、不活性ガス雰囲気中で行うことが好ましい。

【0053】

つづいて、シリコン基板は、真空下で保護絶縁膜成長モジュール106に移されて、絶縁膜の成長が行われる。ここでシリコン基板は大気と接触すると大気中の成分が付着してしまうので、減圧下で基板を移送する。その際、中央プラットフォーム室103の圧力は加熱ステージモジュール105や保護絶縁膜成長モジュール106からのガス混入を防ぐため、加熱ステージモジュール105および保護絶縁膜成長モジュール106よりも高い圧力に設定することが好ましく、例えば500mTorr(66.66Pa)程度とすることが好ましい。

【0054】

図2は、本実施形態において保護絶縁膜の形成に使用するプラズマCVD装置の一構成例を示すブロック図である。

【0055】

図2に示すように、プラズマCVD装置は、反応室210、ガス供給部220、真空ポンプ230、および高周波(Radio Frequency:RF)電源240を有する。ガス供給部220は、ガス供給管222を介して反応室210と接続されている。真空ポンプ230は、ガス排出管236を介して反応室210と接続されている。そして、高周波電源240は、高周波ケーブル244を介して反応室210と接続されている。高周波ケーブル244には、マッチングボックス242が設けられている。

【0056】

反応室210内には、基板ステージ203およびシャワーヘッド205が設けられ、これらは互いに対向した状態で配置されている。基板ステージ203にはアース線207が接続されている。また、基板ステージ203にはヒータ(不図示)が設けられている。基板ステージ203は、半導体基板等の被成膜部材201を保持し、被成膜部材201を加熱する。シャワーヘッド205は、ガス供給管222が接続され、ガス供給管222を介して供給されるガスを被成膜部材201に噴射するガス噴出部として機能する。また、シャワーヘッド205には高周波ケーブル244が接続されている。

【0057】

ガス供給部220からガス供給管222を介してシャワーヘッド205に原料ガス等を供給すると共に、高周波電源240で作り出された高周波電力を高周波ケーブル244の途中に配置されたマッチングンボックス242により所定の周波数にしてシャワーヘッド5に供給する。これにより、基板ステージ203とシャワーヘッド205との間の空間のガスがプラズマ化される。

【0058】

ガス供給部220には、使用する原料ガスの種類数に対応する数の原料供給タンクと、添加ガス用のガス供給タンク(以下「ガス供給タンク」と称する)とが設けられている。図2は、ガス供給部220に、TEOS(テトラエトキシシラン)原料が充填された原料供給タンク211が設けられている場合を示している。TOES以外の液体原料として、他の有機シロキサン原料などを用いてもよい。

【0059】

原料供給タンク211には、流量制御部214および気化器219が設けられている。流量制御部214は、2つのバルブ218a、218bと、これらのバルブの間に設けられた流量制御器218とを有する。流量制御部214は配管212を介して気化器に接続されている。気化器219には、キャリアガスとして不活性ガス等を供給するタイプを用いても良い。気化器219は、原料供給タンク211から供給される液状原料を気化し反応室210に供給する。

【0060】

なお、図2に示すように、ガス供給管222にはクリーニングガス供給管228が接続されている。クリーニングガス供給管228には、リモートプラズマユニット224とバルブ226が設けられている。クリーニングガスとしては、NF3、O2、CxFy、それらの2種以上を含む混合ガスを用いることができる。

【0061】

また、各ガスが移送過程で液化するのを防止するために、配管212の周囲およびガス供給管222の周囲にヒータ(不図示)を設け、配管212およびガス供給管222をヒータ(不図示)で加温することもできる。これと同様な理由で、反応室210に供給されたガスの分子が励起される前に液化するのを防止するために、反応室210の周囲にもヒータ(不図示)を設け、反応室210を加温することもできる。

【0062】

次に、上記のプラズマCVD装置を用いた、保護絶縁膜の形成方法の手順を説明する。

【0063】

基板ステージ203上に被成膜部材201を配置した後、真空ポンプ230を動作させ、バルブ232を開いて反応室210を減圧し、反応室210内の初期真空度を数Torrにする(1Torr=約133Pa)。基板ステージ203は、被成膜部材201を加熱し、被成膜部材201の表面温度が所定の温度範囲になる。

【0064】

続いて、原料ガス(ここでは、TEOSの気体)とキャリアガスを混合させたガスを、ガス供給管222を介して反応室210に供給すると共に、高周波電源240およびマッチングボックス242を動作させて所定周波数の高周波電力を反応室210に供給する。

【0065】

反応室210での原料ガスの分圧は0.1〜3Torr(13.3〜400Pa)程度の範囲で維持されることが好ましい。また、真空ポンプ230の動作を制御することで、SiO2膜形成時の反応室10の雰囲気圧力を1〜6Torr(13.3〜800Pa)程度の範囲に維持することが好ましい。

【0066】

また、基板ステージ203の加熱により、被成膜部材201の表面温度は、100〜500℃の範囲で維持されることが好ましい。特に被成膜部材にあらかじめ形成された半導素子や多層配線を劣化させることのない温度として、一般的な多層銅配線の耐熱性限界を考慮して400℃以下で維持されることが好ましい。

【0067】

このような処理条件の下で、原料ガスであるTEOS原料、および酸素がプラズマによって励起され、活性化された状態の原料が酸素と反応し、被成膜部材201の表面に到達し、そこでSiO2膜が形成される。

【0068】

300mm成膜装置におけるTEOS原料を用いた代表的な成膜条件としては、TEOS=160sccm(standard cm3/min)、O2=200sccm、He=100sccm、反応室圧力400Pa、加熱ステージ温度300℃、RF−power=500Wを用いることができる。

【0069】

保護絶縁膜としてシリコン酸化膜を形成する場合には、通常、酸化ガスが用いられるが、シリコン窒化膜を形成する場合には、添加ガスとしてNH3を用いることができる。シリコン炭窒化膜(SiCN膜)を形成する場合には、4MS(テトラメチルシラン)や3MS(トリメチルシラン)を原料ガスとしてNH3を添加することが好ましい。

【0070】

なお、図2には、原料供給タンク211が1つの場合が示されているが、複数の原料供給タンクを設け、複数の種類の原料ガスを用いて保護絶縁膜を形成してもよい。使用する原料ガスは2種類に限らず、3種類以上であってもよい。

【0071】

また、基板ステージ203、真空ポンプ230、流量制御器218、高周波電源240、マッチングボックス242およびバルブ218a、218b、226に対する、上記保護絶縁膜の形成方法の手順に応じた動作指示内容を記述したプログラムを準備し、そのプログラムにしたがってマイクロコンピュータに処理を実行させることで、プラズマCVD装置を制御して保護絶縁膜を形成してもよい。

【0072】

保護絶縁膜の形成の際には、シリコン基板(被成膜部材201)をフリップ(上下反転)して、基板ステージ203に載置する。この基板ステージ203に凹型の専用ステージ(凹型ステージ)を用い、この凹型ステージの凹みがある面とシリコン基板の素子形成面とが対向するように、すなわち、シリコン基板の裏面(素子が形成されていない面)が上側を向くように載置される。このような状態で成膜を行うことにより、シリコン基板の素子形成領域に保護絶縁膜を形成することなく、シリコン基板の裏面およびべベル(端面)に保護絶縁膜を形成することができる。

【0073】

次に、凹型ステージについて説明する。

【0074】

図3に、凹型ステージの断面図(図3(a))及び上面図(図3(b))を示す。凹型ステージ300は、その基板搭載面に凹部を有し、この凹部を囲む外周部(すなわち枠状の凸部)が、載置された所定のシリコン基板(ウェハ)の素子形成領域を囲む外周位置に接する構造を有している。すなわち、シリコン基板を凹型ステージ上に載置した際に、シリコン基板の素子形成領域には凹型ステージが接しないように基板外周部のみに凹型ステージが接触できる構成となっている。シリコン基板として例えば300mmウェハを用いる場合、凹型ステージの寸法は、例えば、外径a=296mm、基板との接触部(凹部の外周部)301の幅c=3mm、凹部の深さ(枠状凸部の高さ)d=5mmとすることができる。凹型ステージ自体も適宜加熱されていることが好ましい。各部品の寸法については、搬送の誤差範囲、および成膜条件によるべベル(端面)への絶縁膜の回り込み状況などをみて適宜設定することができる。

【0075】

次に、図4及び図5を用いて、シリコン基板(ウェハ)の凹型ステージ上への配置について説明する。図4(a)及び図5(a)は断面図、図4(b)及び図5(b)は上面図を示す。図4(b)において、点線で示される円は、シリコン基板400と凹型ステージ300との接触位置の輪郭を示し、図5(b)において、点線で示される円は、シリコン基板400と凹型ステージ300との接触位置の内側の輪郭を示す。凹型ステージは、その外周が、図4に示すようにシリコン基板の外周に対して小さくてもよいし、図5に示すように大きくてもよい。

【0076】

保護絶縁膜形成前のシリコン基板(ウェハ)400は、表面に半導体素子形成領域401を有する。シリコン基板400は、凹型ステージの凹部がある面と半導体素子形成領域が対向するように配置され、凹型ステージの外周部と接触する。この状態で成膜を行うことにより、保護絶縁膜が、基板の裏面402及びベベル403に形成される。凹型ステージ300は、所定のシリコン基板400を載置した際に、シリコン基板の半導体素子形成領域401と凹型ステージの外周部(シリコン基板と接触する部分)301とが接触しないよう設計しておくことが好ましい。このとき、凹型ステージ上にあらかじめ絶縁膜を成長した後に、シリコン基板を搬送してもよい。清浄な絶縁膜で保護することで、接触面を介したシリコン基板への金属汚染の転写を防ぐことができる。

【0077】

図4(a)及び図5(a)に示す状態で成膜処理を行うと、それぞれ図4(c)及び図5(c)に示すように、保護絶縁膜410が、シリコン基板400の裏面402及びベベル403に形成される。その際、凹型ステージ300でカバーされている素子形成領域401には、保護絶縁膜は形成されない。保護絶縁膜が形成されたシリコン基板は凹型ステージが動作することで、中央ハンドラ104に吸着され、ロードロック室102に移され、ロードロック室102が大気解放された後に、大気圧ロボット101によってロードロック室102からカセットボックス100へ戻される。

【0078】

凹型ステージ上へのシリコン基板のチャック方法について図6を用いて説明する。図6(a)は断面図であり、図6(b)は上面図であり、図6(c)は図6(a)の点線で囲まれた部分の拡大図である。

【0079】

図6(a)、(c)に示すように、凹型ステージ300の外周部(シリコン基板400と接触する部分)に真空チャックライン600を設けることで、凹型ステージ上にシリコン基板を固定することができる。凹型ステージの外周部における真空チャック部601、602、603は、図6(b)に示すように設けることができるが、図に示される数および位置に限定されない。

【0080】

上記の説明では、シリコン基板の裏面およびべベル(端面)に保護絶縁膜の形成において、原料にTEOSを用い、成膜方法としてRF電源を用いたプラズマCVDの場合について詳しく述べたが、これらに限定されるものではない。金属汚染の拡散を防止するための保護絶縁膜としてはより緻密な膜が望ましいことから、基板温度が低い状態でもより緻密な絶縁膜の形成が可能な、HDPプラズマによるプラズマCVD法や、プラズマALD法などの成膜手法を用いることもできる。

【0081】

[固体電解質スイッチの形成方法]

次に、本実施形態における抵抗変化素子の形成方法として、固体電解質スイッチの場合を例に挙げて説明する。

【0082】

図7は、固体電解質スイッチの断面構造を示す模式図である。この固体電解質スイッチは、活性電極701、不活性電極702、およびそれらの間に挟まれた固体電解質(イオン電導層)703とを含む。このような構造を持つ固体電解質スイッチとしては、例えば、NanoBridge(登録商標)が挙げられる。

【0083】

活性電極701は、抵抗変化動作時に金属架橋を形成するための金属を供給する電極であり、Cu(銅)やAg(銀)などが用いられる。不活性電極702は、抵抗変化動作時に金属架橋が接続される電極であり、金属架橋とは化学反応を生じない電極であることが好ましく、Pt(白金)やRu(ルテニウム)が用いられる。固体電解質703は、イオン化された金属が移動し、内部に金属架橋を形成するための媒体であり、酸化タンタル、酸化ハフニウム、酸化ジルコニウム、酸化シリコン、有機ポリマー、およびこれらから選ばれる2種以上の混合物などを用いることができる。

【0084】

このような固体電解質スイッチは、活性電極用のCu、ポリマー固体電解質、不活性電極用のPtを用いた場合、例えば次のようにして形成することができる。

【0085】

不活性電極用のPtは、融点、沸点が高く、反応生成物を生成しないため除去が困難である。そのため、あらかじめ本実施形態による保護絶縁膜の形成方法により、シリコン基板の裏面およびべベル(端面)へ保護絶縁膜を形成する。

【0086】

活性電極用のCuは、半導体素子が設けられたシリコン基板上に設けられた銅配線を利用する。この銅配線上の絶縁膜にスルーホールを形成し、このスルーホールを含む表面上にポリマー固体電解質をプラズマCVD法で形成し、その上にスパッタリング法によりPt(10nm)を堆積する。このとき、スパッタリングチャンバにおいてエッジカットリングを搭載することで、基板裏面およびべベル(端面)への汚染金属の周り込みを回避した場合には、本実施形態による保護絶縁膜を形成しておかなくてもよい。ポリマー固体電解質は炭化水素から構成させる膜であり、SiOを含んでいても良い。

【0087】

つづいて、リソグラフィ技術及びドライエッチング技術により、Pt及びポリマー固体電解質を所定の形状にパターニングする。

【0088】

その後、スピン洗浄機によって裏面およびベベル上の保護絶縁膜を除去する。

【0089】

このように、抵抗変化素子の形成時に、本発明の実施形態による保護絶縁膜を形成しておくことで、金属のシリコン基板への直接の付着を防止することができる。

【0090】

[MRAMの形成方法]

次に、本実施形態における抵抗変化素子の形成方法として、MRAMの場合を例に挙げて説明する。

【0091】

図8は、MRAM記憶素子の断面構造を示す模式図である。この記憶素子(抵抗変化素子)は、下部磁性体層801、上部磁性体層802、およびそれらの間に挟まれたトンネル絶縁層803とを含む。

【0092】

下部磁性体層は、磁化方向が変更しない固定磁性層である。上部磁性層は、その磁化方向がセルのビット状態を変更し得るように切り替えられる自由磁化層である。上部磁性層の磁化が下部磁性層の磁化と並行な場合、セルの抵抗は低くなり、反平行な場合は高くなる。

【0093】

下部磁性体層801は、例えば、下から順にパーマロイ(Ni−Fe)で形成された初期磁性体層、Ir−Mnで形成された反強磁性体層、Co−Fe−Bで形成された固定強磁性層で形成される。典型的な初期磁性体層、反強磁性体層、および固定強磁性の厚さは、それぞれ、2nm、10nm、3nm程度を選択することができる。

【0094】

トンネル絶縁層803は、アルミナ(Al2O3)やマグネシア(MgO)などが用いられ、その厚さは1〜3nm程度に設定できる。

【0095】

上部磁性体層は、例えば、下から順にNi−Feで形成された自由磁性層、第一タンタル層、アルミ層、および第二タンタル層で形成することができる。

【0096】

これらの層の形成前に、本発明に実施形態による保護絶縁膜を形成しておく。

【0097】

これらの層を形成した後、リソグラフィ技術及びドライエッチング技術により所定の形状にパターニングする。

【0098】

その後、スピン洗浄機によって裏面およびベベル上の絶縁膜を除去する。

【0099】

このように、抵抗変化素子の形成時に、本発明の実施形態による保護絶縁膜を形成しておくことで、金属のシリコン基板への直接の付着を防止することができる。

【0100】

[保護絶縁膜の形成とリフトオフ洗浄を含むプロセス]

前述の通り、抵抗変化素子の成膜工程および加工(ドライエッチング)工程において、金属が、基板の裏面やべベル(端面)に付着する。この問題を解決するプロセス(保護絶縁膜の形成、リフトオフ洗浄工程)について、図9を用いてさらに説明する。図9は、保護絶縁膜の形成とリフトオフ洗浄を含む工程フロー図である。

【0101】

図9(a)は、抵抗変化素子の成膜工程における汚染金属の付着を、保護絶縁膜形成以外の方法(例えばスパッタリング時のエッジカットリングなど)で防止する場合の工程フローを示す。この工程フローにおいては、保護絶縁膜の形成を抵抗変化素子の成膜工程後に行う。つづいてリソグラフィとドライエッチングにより抵抗変化素子の加工工程を行い、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成とリフトオフ洗浄は各1回行うことになる。

【0102】

図9(b)の工程フローでは、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。そして、抵抗変化素子の成膜工程に引き続き、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成とリフトオフ洗浄は各1回行うことになる。

【0103】

図9(c)は、図9(b)と同様に、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。このとき、成膜時になんらかの金属付着防止対策を実施しない場合には、基板の裏面やべベル(端面)に金属が付着する。つづいて、基板の洗浄を行うことなく、保護絶縁膜を形成する。その際、基板に付着していた金属は保護絶縁膜の内部に捕獲される。つづいて、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、保護絶縁膜形成を2回、リフトオフ洗浄を1回行うことになる。

【0104】

図9(d)は、図9(b)及び図9(c)と同様に、保護絶縁膜を形成した後に抵抗変化素子の成膜工程を実施する。引き続き、リフトオフにより保護絶縁膜を除去(リフトオフ洗浄)した後、再び保護絶縁膜を形成する。つづいて、抵抗変化素子の加工工程を実施し、その後リフトオフによる保護絶縁膜の除去(リフトオフ洗浄)を行う。この場合、抵抗変化素子の成膜工程に対して、保護絶縁膜形成とリフトオフ洗浄を各1回、抵抗変化素子の加工工程に対して、保護絶縁膜形成とリフトオフ洗浄を各1回行うことになる。このような工程フローによれば、基板を常にクリーンな状態に維持できる利点がある。

【0105】

リフトオフ洗浄については、枚葉スピン洗浄機とFPM洗浄液(0.1〜0.5%HF、0.1〜0.5%H2O2)を用いて、基板の裏面とべベル(端面)部の洗浄を行うことができる。回転する基板の表面上方より基板表面に乾燥窒素あるいは純水を吹き付けつつ、基板の裏面および基板裏面端部に洗浄液を噴射することで、基板外方向に向かう乾燥窒素または純水の流れにより洗浄液の基板表面への回り込みを防止ししながら裏面洗浄を行うことができる。洗浄後は純水を噴射することで基板に付着した薬液を除去することができる。FPMに加えて、半導体プロセスで一般に用いられている薬液、例えばHPM洗浄液(HCl/H2O2/H2O)、SPM洗浄液(H2SO4/H2O2)、FPM洗浄液(HF/H2O2/H2O)、DHF洗浄液(HF/H2O)、BHF洗浄液(HF/NH4F/H2O)などを適宜組み合わせても良い。

【0106】

各工程毎に基板裏面の金属汚染レベルをあらかじめ測定しておくことで、図9(a)〜(d)のいずれかの工程フロー、もしくはいずれかをベースにした工程フローを適用することで、工程数の増加を抑えた製造プロセスを提供することができる。

【実施例】

【0107】

以下、本発明について、実施例を挙げてさらに具体的に説明する。

【0108】

(実施例1)固体電解質スイッチを含む半導体装置の製造方法

本実施例では、抵抗変化素子として固体電解質スイッチを備えた半導体装置の製造方法について説明する。

【0109】

図10は、固体電解質スイッチ及び保護絶縁膜の形成前の、半導体素子が形成されたシリコン基板の断面模式図である。

【0110】

シリコン基板500上にMOSFET599が形成され、MOSFET599のゲート、ソース及びドレインはそれぞれTiN531で被覆されたタングステンプラグ532により、上層側の銅配線に接続されている。銅配線はCu534とCuを囲むTa/TaN533(積層バリアメタル)からなる。配線層間絶縁膜は比誘電率3以下のSiOCH膜513が用いられている。銅配線の上面には、保護膜としてプラズマCVDにより形成したSiCN膜514が設けられている。最上層の銅配線上には保護膜としてSiCN膜520が形成され、その上にスルーホール加工用のシリコン酸化膜520aが形成されている。

【0111】

ここで、基板の最表面はシリコン酸化膜520aによって被覆しているため、裏面スピン洗浄の際に、乾燥窒素や純水に暴露されても問題は生じない。

【0112】

つづいて本発明の実施形態による絶縁膜成長装置をもちいて、基板の裏面およびベベル(端面)に保護絶縁膜(シリコン酸化膜)(図示せず)を1μm成長した。このとき、半導体素子形成領域には保護絶縁膜が成長しないため、図10の断面構造に変化はない。

【0113】

つづいて、図11に、多層配線構造内に抵抗変化素子598が設けられたシリコン基板の断面図を示す。図12には、図11に示される抵抗変化素子598及びその周辺部の拡大図を示す。

【0114】

シリコン酸化膜520a上にリソグラフィとドライエッチングによってホールを形成し、このホールを含むシリコン基板全面に抵抗変化素子形成用の積層膜を形成する。図12に示す固体電解質スイッチを形成する場合、この積層膜の各層は、下からポリマー固体電解質591、Pt電極592、Ta電極593に対応する。Pt電極層及びTa電極層はスパッタリング法で形成し、膜厚はそれぞれ、10nm、25nmとした。このとき、スパッタリングにおけるエッジカットリングシールドの幅を5mmに設定し、基板の裏面及びベベル(端面)へのPt及びTaの付着を防いだ。

【0115】

つづいてリソグラフィとドライエッチングによって抵抗変化素子形成用の積層膜を加工した。例えば、ECRプラズマ源を用いたRIE装置を使用し、ソース/バイアス電力400W/200W、Ar=100sccm、反応室圧力0.3Pa、基板温度150℃に設定し、RIEを行い、有機ポリマー層についてはCF4=100sccmにてRIEを行った。

【0116】

その後、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。

【0117】

上記のRIEによる加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、リフトオフ洗浄しないで、全反射蛍光X線分析(TREX)を用いて基板裏面の金属汚染濃度を分析したところ、この基板の裏面から、Ptについて1×1016atom/cm2レベル以上の汚染が検出された。

【0118】

これに対し、上記の加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。その後、上記と同様にして基板裏面の金属汚染濃度を測定したところ、Ptについては検出下限以下であった。すなわち、本発明の実施形態にしたがって保護絶縁膜を形成し、リフトオフ洗浄を実施して保護絶縁膜を除去することで、抵抗変化素子の加工工程に起因する基板の金属汚染を防ぐことができることを確認した。

【0119】

(実施例2)MRAMを含む半導体装置の製造方法

本実施例では、抵抗変化素子としてTMR素子を用いたMRAMを備えた半導体装置の製造方法について説明する。本実施例は、抵抗変化素子の構成が異なること以外は実施例1と同様にして半導体装置を製造することができる。

【0120】

下部電極上に、Ta(10nm)/PtMn(10nm)/Co90Fe10(2.5nm)/Ru(0.85nm)/Co40Fe40B20(5nm)/MgO(2.5nm)/Co40Fe40B20(3nm)/Ta(10nm)/Ru(7nm)/NiFe(20nm)/Ta(5nm)をスパッタリング法で形成した。このとき、スパッタリングチャンバにおいてエッジカットリングを搭載することで、基板の裏面及びべベル(端面)への汚染金属の付着を回避できる。

【0121】

次に、上記の成膜工程を実施した後、下記の問題を回避するため、本発明の実施形態による絶縁膜成長装置を用いて、基板の裏面およびべベル(端面)上へ保護絶縁膜(SiO2)を形成した。その後、上記の成膜工程により形成された積層膜をリソグラフィとドライエッチングによって加工を行う。

【0122】

SiやAlなどの通常の半導体プロセスに用いられている材料は、それらの塩化物の融点、沸点が低く、高い蒸気圧を有するため、塩素系ガスを用いたRIEによって加工して素子形成を行うことができる。一方、強磁性体金属材料であるFe、Co、Niの塩化物は融点、沸点が高く、蒸気圧も低いため反応生成物の除去が困難である。一般に被加工物の温度を上げた昇温RIEや、CO/NH3混合ガスなどによるRIEが提案されているが、加工性は向上されつつあるものの、エッチング生成物の反応室内への再付着によるシリコン基板への転写が問題となっている。

【0123】

保護絶縁膜の形成後、リソグラフィとドライエッチングにより、所定の形状に前記積層膜を加工する。例えば、ECRプラズマ源を用いたRIE装置を使用し、ソース/バイアス電力800W/200W、CO=100sccm、NH3=100sccm、反応室圧力:0.5Pa、基板温度:室温に設定し、NiFe、CoFeBのRIEを行い、それ以外の層についてはCl2=120sccmにてRIEを行った。

【0124】

その後、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。

【0125】

上記のRIEによる加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、リフトオフ洗浄しないで、全反射蛍光X線分析(TREX)を用いて基板裏面の金属汚染濃度を分析したところ、この基板の裏面から、Feについて1×1016atom/cm2レベルの汚染が検出された。

【0126】

これに対し、上記の加工処理後に、後続の別の基板(ウェハ)を反応室へ搬送し、この搬送作業以外の作業をすることなしに反応室から取り出した基板について、FPMを用いたリフトオフ洗浄を実施し、保護絶縁膜を除去した。その後、上記と同様にして基板裏面の金属汚染濃度を測定したところ、全ての評価金属について検出下限以下であった。すなわち、本発明の実施形態により保護絶縁膜を形成し、リフトオフ洗浄を実施して保護絶縁膜を除去することで、抵抗変化素子の加工工程に起因する基板の金属汚染を防ぐことができることを確認した。

【0127】

また、保護絶縁膜としてSiO2膜に代えてSiN膜を用いた場合にも同様の効果が得られることを確認した。

【0128】

以上の説明においては、好適な実施形態および実施例を挙げて本発明を説明したが、これら実施形態および実施例は、本発明を説明するためのものであって、これらに限定することを意味するものではない。半導体基板上に形成する抵抗変化素子の例として、固体電解質スイッチやMRAMについて説明したが、本発明はそれらに限定されるものではない。

【0129】

本発明は、半導体装置を形成する際に、基板の裏面やべベル(端面)への金属の付着・転写を防止することができ、金属の付着の防止が必要なプロセス、例えば、DRAM(Dynamic RAM)、FRAM(Ferro Electric RAM)、PRAM(Phase-change RAM)、RRAM(Resistive RAM)を有する半導体製品の製造方法、マイクロプロセッサなどの論理回路を有する半導体製品の製造方法へも適用することができる。また、本発明の基板の裏面に絶縁膜を成長できるという特徴を生かして、半導体装置に対する、電子回路装置、光回路装置、量子回路装置、マイクロマシン、MEMS(Micro Electro Mechanical Systems)などの製造にも適用することができる。

【0130】

以上、実施形態および実施例を参照して本発明を説明したが、本発明は上記実施形態および実施例に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更をすることができる。

【符号の説明】

【0131】

100 カセットボックス

101 大気ロボット

102 ロードロック室

103 中央プラットフォーム室

104 中央ハンドラ

105 加熱ステージモジュール

106 保護絶縁膜成長モジュール

201 被成膜部材

203 基板ステージ

205 シャワーヘッド

207 アース線

210 反応室

211 原料供給タンク

212 配管

214 流量制御部

218 流量制御器

218a、218b バルブ

219 気化器

220 ガス供給部

222 ガス供給管

224 リモートプラズマユニット

226 バルブ

228 クリーニングガス供給管

230 真空ポンプ

232 バルブ

236 ガス排出管

240 高周波電源

242 マッチングンボックス

244 高周波ケーブル

300 凹型ステージ

301 接触部

400 シリコン基板

401 半導体素子形成領域

402 基板裏面

403 ベベル

410 保護絶縁膜

500 シリコン基板

511、526 シリコン酸化膜

512、514、516、518、520、521、523 SiCN膜

513、515、517、519、524、525、522 SiOCH膜

520a シリコン酸化膜

520b SiN

526 シリコン酸化膜

527 シリコン酸窒化膜

531 TiN

532 タングステン

533、535、539、541、543、545、547、549 Ta/TaN

534、536、540、542、544、546、548 Cu

550 Al−Cu

591 ポリマー固体電解質

592 Ta

593 Pt

598 抵抗変化素子

599 MOSFET

600 真空チャックライン

601、602、603 真空チャック部

701 活性電極

702 不活性電極

703 固体電解質

801 下部磁性体層

802 上部磁性体層

803 トンネル絶縁層

【特許請求の範囲】

【請求項1】

半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、

前記半導体素子形成面に設けられた金属含有膜を加工する工程と、

前記金属含有膜の加工後に前記保護膜を除去する工程と、

を含む半導体装置の製造方法。

【請求項2】

前記金属含有膜の加工工程において、

前記金属含有膜はドライエッチングにより加工され、

前記保護膜の除去工程において、

前記保護膜に付着した、前記金属含有膜に由来の金属成分とともに前記保護膜を除去する、請求項1に記載の製造方法。

【請求項3】

前記保護膜の形成工程において、

前記基板は、成膜ステージ上に、半導体素子形成面を該成膜ステージの基板搭載面に向けて載置され、

前記成膜ステージは、基板搭載面に凹部を有し、

前記成膜ステージの基板搭載面の、前記凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触している状態で前記保護膜の成膜を行う、請求項1又は2に記載の製造方法。

【請求項4】

前記基板は、加熱ステージ上で所定の温度に加熱されたのち、前記成膜ステージ上へ搬送されて保護膜の成膜が行われる、請求項3に記載の製造方法。

【請求項5】

前記保護膜の形成工程において、

400℃以下で、CVD法、プラズマCVD法、ALD法、又はプラズマALD法によって成膜を行う、請求項1から4のいずれか一項に記載の製造方法。

【請求項6】

前記保護膜として、シリコン酸化膜、シリコン窒素化膜、又はシリコン炭窒化膜を形成する、請求項1から5のいずれか一項に記載の製造方法。

【請求項7】

前記保護膜の除去工程において、

薬液を用いた枚葉式スピン洗浄により前記保護膜を除去する、請求項1から6のいずれか一項に記載の製造方法。

【請求項8】

前記金属含有膜は、Pt、Pd、Ni、Fe、Co、Ru、Mn、Mg、Ta、Ir、B、Ge、Te、Se、Sbから選ばれる少なくとも一種の金属を含む、請求項1から7のいずれか一項に記載の製造方法。

【請求項9】

抵抗変化素子を形成する工程を有し、

この抵抗変化素子の形成工程は、前記金属含有膜を加工する工程を含む、請求項1から8のいずれか一項に記載の製造方法。

【請求項10】

前記抵抗変化素子として、MRAM、PRAM、RRAM、FRAM、又は固体電解質スイッチを形成する、請求項9に記載の製造方法。

【請求項11】

前記保護膜として第1の保護膜と第2の保護膜を形成し、

前記金属含有膜を形成する前に前記第1の保護膜を形成し、

前記金属含有膜の形成後に前記第1の保護膜上に前記第2の保護膜を形成し、

前記金属含有膜の加工後に前記第1の保護膜および前記第2の保護膜を除去する、請求項1から10のいずれか一項に記載の製造方法。

【請求項12】

前記保護膜として第1の保護膜と第2の保護膜を形成し、

前記金属含有膜を形成する前に前記第1の保護膜を形成し、

前記金属含有膜の形成後に前記第1の保護膜を除去し、

前記第1保護膜を除去した後に前記第2の保護膜を形成し、

前記金属含有膜の加工後に前記第2の保護膜を除去する、請求項1から10のいずれか一項に記載の製造方法。

【請求項13】

請求項1から12のいずれか一項に記載の製造方法に用いられる製造装置であって、

減圧下で前記保護膜を形成するための成膜室と、

前記基板を載置するためのステージと、

前記成膜室へ前記基板を搬送するためのアームとを有し、

前記ステージは、基板搭載面に凹部を有し、該凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触できる形状を有し、

前記アームは、前記基板の裏面に接触し、該アームが回転することで該基板をフリップし、該基板の半導体素子形成面を前記ステージの基板搭載面に向けて載置する機構を備えていることを特徴とする半導体製造装置。

【請求項1】

半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、

前記半導体素子形成面に設けられた金属含有膜を加工する工程と、

前記金属含有膜の加工後に前記保護膜を除去する工程と、

を含む半導体装置の製造方法。

【請求項2】

前記金属含有膜の加工工程において、

前記金属含有膜はドライエッチングにより加工され、

前記保護膜の除去工程において、

前記保護膜に付着した、前記金属含有膜に由来の金属成分とともに前記保護膜を除去する、請求項1に記載の製造方法。

【請求項3】

前記保護膜の形成工程において、

前記基板は、成膜ステージ上に、半導体素子形成面を該成膜ステージの基板搭載面に向けて載置され、

前記成膜ステージは、基板搭載面に凹部を有し、

前記成膜ステージの基板搭載面の、前記凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触している状態で前記保護膜の成膜を行う、請求項1又は2に記載の製造方法。

【請求項4】

前記基板は、加熱ステージ上で所定の温度に加熱されたのち、前記成膜ステージ上へ搬送されて保護膜の成膜が行われる、請求項3に記載の製造方法。

【請求項5】

前記保護膜の形成工程において、

400℃以下で、CVD法、プラズマCVD法、ALD法、又はプラズマALD法によって成膜を行う、請求項1から4のいずれか一項に記載の製造方法。

【請求項6】

前記保護膜として、シリコン酸化膜、シリコン窒素化膜、又はシリコン炭窒化膜を形成する、請求項1から5のいずれか一項に記載の製造方法。

【請求項7】

前記保護膜の除去工程において、

薬液を用いた枚葉式スピン洗浄により前記保護膜を除去する、請求項1から6のいずれか一項に記載の製造方法。

【請求項8】

前記金属含有膜は、Pt、Pd、Ni、Fe、Co、Ru、Mn、Mg、Ta、Ir、B、Ge、Te、Se、Sbから選ばれる少なくとも一種の金属を含む、請求項1から7のいずれか一項に記載の製造方法。

【請求項9】

抵抗変化素子を形成する工程を有し、

この抵抗変化素子の形成工程は、前記金属含有膜を加工する工程を含む、請求項1から8のいずれか一項に記載の製造方法。

【請求項10】

前記抵抗変化素子として、MRAM、PRAM、RRAM、FRAM、又は固体電解質スイッチを形成する、請求項9に記載の製造方法。

【請求項11】

前記保護膜として第1の保護膜と第2の保護膜を形成し、

前記金属含有膜を形成する前に前記第1の保護膜を形成し、

前記金属含有膜の形成後に前記第1の保護膜上に前記第2の保護膜を形成し、

前記金属含有膜の加工後に前記第1の保護膜および前記第2の保護膜を除去する、請求項1から10のいずれか一項に記載の製造方法。

【請求項12】

前記保護膜として第1の保護膜と第2の保護膜を形成し、

前記金属含有膜を形成する前に前記第1の保護膜を形成し、

前記金属含有膜の形成後に前記第1の保護膜を除去し、

前記第1保護膜を除去した後に前記第2の保護膜を形成し、

前記金属含有膜の加工後に前記第2の保護膜を除去する、請求項1から10のいずれか一項に記載の製造方法。

【請求項13】

請求項1から12のいずれか一項に記載の製造方法に用いられる製造装置であって、

減圧下で前記保護膜を形成するための成膜室と、

前記基板を載置するためのステージと、

前記成膜室へ前記基板を搬送するためのアームとを有し、

前記ステージは、基板搭載面に凹部を有し、該凹部を囲む外周部が、前記基板の素子形成領域に接触しないように該素子形成領域を囲む外周位置に接触できる形状を有し、

前記アームは、前記基板の裏面に接触し、該アームが回転することで該基板をフリップし、該基板の半導体素子形成面を前記ステージの基板搭載面に向けて載置する機構を備えていることを特徴とする半導体製造装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−4736(P2013−4736A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−134284(P2011−134284)

【出願日】平成23年6月16日(2011.6.16)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

2.FRAM

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度経済産業省産業技術研究開発委託費「低炭素社会を実現する超低電圧デバイスプロジェクト」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月16日(2011.6.16)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

2.FRAM

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度経済産業省産業技術研究開発委託費「低炭素社会を実現する超低電圧デバイスプロジェクト」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]