半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造工程において、種々の洗浄技術が用いられている(例えば特許文献1参照)。洗浄処理として、例えば、希フッ化水素酸水溶液(DHF)処理や、アンモニア過酸化水素水混合水溶液(APM)処理や、塩酸過酸化水素水混合水溶液(HPM)処理が挙げられる。なお、例えばDHF処理は、洗浄のみを目的として行われるわけではなく、例えば酸化シリコン膜を所望領域で除去するような場合にも用いられる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−53050号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0006】

H2O2の導入と同時かそれよりも遅く温水が導入される。これにより、H2O2の導入なしにシリコンが温水に曝される場合に比べて、シリコンのエッチングが抑制される。

【図面の簡単な説明】

【0007】

【図1】図1は、DHF処理、APM処理、及びHPM処理についてまとめた表である。

【図2】図2は、DHF処理、APM処理、及びHPM処理を行う処理装置を示す概略図である。

【図3】図3は、比較例の処理フローと、処理液温度とH2O2濃度及びHCl濃度を示すグラフである。

【図4】図4A〜図4Cは、比較例の処理を施したウエハのTEM写真である。

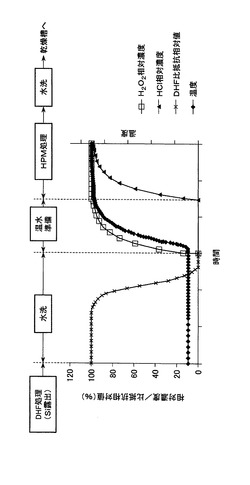

【図5】図5は、実施例の処理フローと、処理液温度とH2O2濃度及びHCl濃度と比抵抗とを示すグラフである。

【図6】図6Aは、DHF処理時のウエハのTEM写真であり、図6Bは、実施例の処理を施したウエハのTEM写真であり、図6Cは、比較例の処理を施したウエハのTEM写真である。

【図7−1】図7AM及び図7ATは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−2】図7B1〜図7B3は、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−3】図7CM及び図7CTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−4】図7DM及び図7DTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−5】図7EM及び図7ETは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−6】図7FM及び図7FTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−7】図7GM及び図7GTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−8】図7HM及び図7HTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−9】図7I1及び図7I2は、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−10】図7JM及び図7JTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−11】図7KM及び図7KTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−12】図7LM及び図7LTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−13】図7MM及び図7MTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−14】図7NM及び図7NTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−15】図7OM及び図7OTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−16】図7PM及び図7PTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−17】図7QM及び図7QTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−18】図7RM及び図7RTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−19】図7SM及び図7STは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−20】図7TM及び図7TTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−21】図7UM及び図7UTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−22】図7VM及び図7VTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−23】図7WM及び図7WTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−24】図7XMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−25】図7XTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−26】図7YMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図8】図8は、消去状態におけるフラッシュメモリセルトランジスタの閾値電圧とそのばらつきを、実施例及び比較例のフラッシュメモリについて示したグラフである。

【図9】他の実施例の処理工程の一部を示すフローである。

【発明を実施するための形態】

【0008】

まず、半導体装置製造工程において用いられる、希フッ化水素酸水溶液(DHF)処理、アンモニア過酸化水素水混合水溶液(APM)処理、及び塩酸過酸化水素水混合水溶液(HPM)処理について説明する。

【0009】

図1は、DHF処理、APM処理、及びHPM処理についてまとめた表である。DHF処理は、薬液として水(H2O)にフッ化水素酸(HF)を混合した希フッ化水素酸水溶液(DHF)を用い、酸化膜除去や金属除去を目的として行われる。通常、処理温度は室温であり、エッチングレートの制御等の必要に応じ、室温より高温の処理温度とすることもある。室温とは、例えば24℃〜26℃(例えば25℃)である。なお、DHF処理では、酸化還元電位の高い金属(例えばCu等)の除去は難しい。

【0010】

APM処理は、薬液として水(H2O)に過酸化水素水(H2O2)及びアンモニア水(NH4OH)を混合したアンモニア過酸化水素水混合水溶液(APM)を用い、例えばパーティクル除去を目的として行われる。処理温度は、除去性能を向上させるために室温より高温が好ましく、例えば40℃〜80℃である。

【0011】

HPM処理は、薬液として水(H2O)に過酸化水素水(H2O2)及び塩化水素酸(HCl)を混合した塩酸過酸化水素水混合水溶液(HPM)を用い、例えば金属除去を目的として行われる。処理温度は、除去性能を向上させるために室温より高温が好ましく、例えば60℃〜80℃である。

【0012】

図2は、DHF処理、APM処理、及びHPM処理を行う処理装置を示す概略図である。この処理装置は、1つの槽でDHF処理、APM処理、及びHPM処理を行うことができるワンバス処理装置である。

【0013】

槽101内に、処理対象物であるウエハ102が載置される。槽101内に供給される水または薬液を、まとめて処理液103と呼ぶ。槽101は、処理液103が、下側から導入され、上側から排出される構造となっている。槽101に導入される処理液103の種類を切り替えることにより、槽101内の処理液103を置換することができる。これにより、槽101内にウエハ102を載置したまま、DHF処理、APM処理、及びHPM処理のうちの任意の処理を行うことができる。

【0014】

複数の処理(例えばDHF処理とHPM処理)を順次行う場合であっても、処理開始から処理終了まで、ウエハ102は処理液103中に浸かった状態が保たれる。これにより、処理中の大気曝露に起因するパーティクル付着、汚染が抑制される。例えば、各処理を別々の処理槽で行う水洗槽渡り処理の場合(例えば、DHF処理をDHF処理槽で行い、水洗槽を介した後、HPM処理をHPM処理槽で行う場合)、処理槽間の移動時の大気曝露に起因して、ウエハへのパーティクル付着等が起こりやすい。

【0015】

主供給管104を通って、槽101に処理液103が導入される。主供給管104に、HF供給管105、HCl供給管106、H2O2供給管107、NH4OH供給管108、及び、室温水・温水供給管109が、それぞれ、バルブ105a〜109aを介して接続されている。各バルブ105a〜108aの開閉により、HF、HCl、H2O2、及びNH4OHの供給開始と供給停止が制御される。バルブ109aの開閉により、室温水または温水の供給開始と供給停止が制御される。

【0016】

室温水・温水供給管109に、室温水供給管110及び温水供給管111が、それぞれ、バルブ110a及び111aを介して接続されている。H2O源から室温の水が、室温水供給管110または温水供給管111に供給される。温水供給管111は、所望温度の温水が得られるように水を加熱する温水ユニット111bを備え、温水ユニット111bよりH2O源側に配置されたバルブ111cを介して、H2O源に接続されている。

【0017】

槽101へ室温水を供給するときは、バルブ110aを開とし、バルブ111a及びバルブ111cを閉とする。槽101へ温水を供給するときは、バルブ110aを閉とし、バルブ111a及びバルブ111cを開とする。

【0018】

半導体装置の製造工程で用いられる純水は、微粒子個数、金属濃度、有機物濃度、溶存酸素量等が管理されている。溶存酸素は、シリコン上の自然酸化膜成長抑制等のために、低く抑えることが好ましい。純水の溶存酸素量は、半導体装置製造工場受け入れ時は例えば2ppm〜3ppmであり、その後の脱気により、製造工程で使用される際には例えば2ppb以下にされている。

【0019】

次に、比較例による処理について説明する。比較例の処理では、APM処理とDHF処理とHPM処理とが順次行われる。比較例のAPM処理、DHF処理、及びHPM処理は、例えば、MOSトランジスタ製造における、シャロートレンチアイソレーション(STI)による素子分離絶縁膜の形成工程で行われる。以下、さらに詳しく説明する。

【0020】

図7AM及び図7ATは、シリコン基板1に、素子分離絶縁膜の埋め込まれる素子分離溝4が形成された状態を示す概略断面図である。シリコン基板1上に、熱酸化で酸化シリコン膜(初期酸化膜)2が形成され、初期酸化膜2上に、窒化膜(アイソレーション窒化膜)3が成膜され、アイソレーション窒化膜3が、素子分離溝4の形成領域上で開口する形状にパターニングされる。アイソレーション窒化膜3をマスクとして、初期酸化膜2とシリコン基板1とがエッチングされて、素子分離溝4が形成される。

【0021】

図7B1〜図7B3は、素子分離溝4近傍の拡大断面図を示す。図7B1は、素子分離溝4が形成された時点を示す。素子分離溝4の縁を画定している、シリコン基板1の角部1Cは、アクティブ領域端部となる。アクティブ領域端部の角部1Cが尖っていると、角部1Cで、MOSトランジスタ駆動時に電界集中が生じやすい。なお以後、角部1Cを、「素子分離溝の角部」と表現することもある。

【0022】

次に、図7B2に示すように、DHF処理が行われる。DHF処理により、初期酸化膜2の端部を後退させ、角部1Cの上面部分を露出させる。

【0023】

次に、図7B3に示すように、角部1Cを熱酸化して、酸化シリコン膜5を形成する。この熱酸化により、角部1Cが丸められる。角部1Cを丸めることにより、上述の電界集中を抑制できる。その後、素子分離溝4に素子分離絶縁膜が埋め込まれる。

【0024】

DHF処理に伴い、自然酸化膜等も除去されることにより、基板1のシリコン表面が露出した部分が生じる。露出したシリコン表面は疎水性でパーティクルを寄せ付けやすい。また、DHF処理のみでは除去できない金属もある。ここでは、図7B2に示すDHF処理の後、図7B3に示す熱酸化の前の洗浄として、HPM処理を行う。なお、図7B1に示す素子分離溝4形成の後、図7B2に示すDHF処理の前の洗浄として、APM処理を行う。

【0025】

図3の上側部分に、比較例の処理フローを示す。(APM処理の後、)DHF処理が行われる。DHF処理により、基板のシリコン表面が露出する。DHF処理後、槽内に室温水を導入し、処理液を室温水に置換して、水洗を行う。室温水での水洗後、槽内に温水を導入し、温水を使用するHPM処理を準備する(温水準備)。温水準備後、槽内に過酸化水素水と塩化水素酸とを投入して、HPM処理を行う。HPM処理後、槽内に室温水を導入し、処理液を室温水に置換して、水洗を行う。その後、ウエハを乾燥槽へ移し、乾燥を行う。

【0026】

図3の下側部分に、温水準備及びHPM処理の期間における、槽内の処理液温度と、処理液のH2O2濃度及びHCl濃度を示す。H2O2濃度及びHCl濃度は、それぞれ、HPM処理工程での目標濃度を100%とした相対濃度で示す。

【0027】

温水準備工程において、槽内に温水を導入することにより、水温が上昇する。槽内の水温がHPM処理の目標温度に達したら、槽内にH2O2及びHClが投入されて、HPM処理が開始される。

【0028】

比較例の処理によって生じた問題について説明する。図4A〜図4Cは、比較例の処理を施したウエハの透過型電子顕微鏡(TEM)写真である。

【0029】

図4Aは、図7B1に対応し、シリコン基板に素子分離溝が形成された時点の写真である。中央下側の台形状の領域が、シリコン基板であり、その脇の領域が素子分離溝である。シリコン基板上に、初期酸化膜を介して、アイソレーション窒化膜が形成されている。

【0030】

図4Bは、図7B2に対応し、APM処理の後のDHF処理により、初期酸化膜の端部が後退した時点の写真である。

【0031】

図4Cは、DHF処理の後、HPM処理を行った時点の写真である。素子分離溝の角部を、図4Cに、破線で囲んで示す。上述のように、角部は、HPM処理の後の熱酸化によって丸められる。角部の丸め形状は、この熱酸化工程で制御したい。このため、この熱酸化の前までは、素子分離溝を形成した時点での角部形状がそのまま維持されていることが好ましい。

【0032】

図4Bに示すように、DHF処理後までは、素子分離溝形成時とほぼ同様な角部形状が維持されている。しかし、図4Cに示すように、HPM処理後は、角部がエッチングされて丸まってしまっている。熱酸化まで角部形状をそのまま維持したいという観点からは、このようなエッチングは好ましくない。

【0033】

本願発明者は、素子分離溝の角部がエッチングされた原因について考察した。図3に示したように、比較例の方法では、DHF処理の後、水洗及び温水準備を経て、HPM処理が行われる。HPM処理は、薬液がH2O2やHClを含んでおり酸性である。処理液が酸性の下では、シリコンは固体として存在する方がイオンとして存在するよりも安定であり、シリコンのエッチングが抑制されると考えられる。従って、水洗工程及び温水準備工程において、つまり水によって、シリコンがエッチングされている可能性が高い。特に、室温水より高温(例えば30℃以上)の温水によるエッチングが起こりやすいと考えられる。

【0034】

次に、本発明の実施例による処理について説明する。上記比較例と同様に、例えば、MOSトランジスタ製造の素子分離絶縁膜形成工程において、APM処理、DHF処理、及びHPM処理が行われる。

【0035】

図5の上側部分に、実施例の処理フローを示す。図5の下側部分に、水洗、温水準備、及びHPM処理の期間における、槽内の処理液温度と、処理液のH2O2濃度及びHCl濃度を示す。また、水洗期間における処理液の比抵抗を示す。H2O2濃度及びHCl濃度は、比較例の説明と同様に相対濃度で示す。処理液の比抵抗は、DHF処理完了時を100%、水洗完了時を0%とした相対値で示す。

【0036】

本実施例の処理フローについて説明する。(APM処理の後、)DHF処理が行われる。DHF処理に伴って、基板のシリコン表面が露出する。DHF処理後、水洗を行う。水洗工程において、室温水が槽内に導入され、DHF処理の薬液(希フッ酸)が槽内から排出され、処理液が室温水に置換される。水洗工程で、処理液が水に置換されたかどうかは、例えば比抵抗により判定される。処理液の比抵抗が、純水の比抵抗(約18.3MΩ・cm)に達したら、処理液が水に置換されたと判定される。

【0037】

水洗後、温水準備が行われる。実施例の温水準備工程では、槽内に温水を導入するとともに、予め、HPM処理で用いられるH2O2も導入する。水洗工程で処理液が室温水に置換された後に、槽内へのH2O2導入が開始される。温水の導入開始時点は、H2O2の導入開始時点と同時かそれよりも遅く設定されている。

【0038】

処理液温度がHPM処理の目標温度に達したら、槽内へのHCl導入が開始されて、HPM処理が開始される。HPM処理後の水洗及びその後の乾燥は、比較例と同様である。

【0039】

実施例の処理では、H2O2が温水準備工程で処理液に投入される。これにより、DHF処理で露出したシリコン表面上に、薄い酸化膜が形成されて、温水によるシリコンのエッチングが抑制されると考えられる。

【0040】

なお、溶存酸素の有無に関わらず、水によるシリコンのエッチングは生じると考えられるが、水中の溶存酸素量の低い方が、エッチングは生じやすいようである。エッチングの生じやすい溶存酸素量の目安を挙げるならば、例えば80ppb以下である。溶存酸素量の少ない純水中で、シリコンの構造的に安定な面(例えば(111)面)が出るようにエッチングが進みやすくなるようであり、比較例のTEM像において、素子分離溝幅はほぼそのままで角部が斜めに削れているのは、溶存酸素の少ない純水中で安定面が出ようとしているということと理解できる。

【0041】

シリコンのエッチング抑制の観点からは、処理液温度が上昇した時点で、処理液中にH2O2が含まれていることが望ましい。H2O2の投入と同時かそれより遅く温水を導入することにより、温度上昇時において確実に、処理液中にH2O2が含まれるようにできる。

【0042】

なお、温水に比べればエッチングレートは遅いが、室温水でもシリコンのエッチングはある程度起こると考えられる。このため、DHF処理後の水洗途中からH2O2を投入すればよいようにも思われる。しかし、水洗途中に、希フッ酸が処理液に残った状態でH2O2が投入されると、H2O2によるシリコン酸化と、希フッ酸による酸化シリコンのエッチングとが繰り返されて、シリコンが過度にエッチングされてしまうこととなる。このため、H2O2投入は、希フッ酸が排出された後に開始することが望ましい。

【0043】

図6A〜図6Cは、ウエハのTEM写真である。図6Aは、DHF処理時点の写真である。図6Bは、実施例のHPM処理後の写真である。比較のため、図6Cとして、比較例のHPM処理後の写真(図4Cと同一)を並べる。実施例の処理により、HPM処理後において、素子分離溝の角部のエッチングが抑制されていることがわかる。

【0044】

次に、実施例の処理を応用した、半導体装置の製造方法について説明する。図7AM、図7AT〜図7YMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。本応用例では、フラッシュメモリセルトランジスタと周辺トランジスタとが同時形成される。フラッシュメモリセルトランジスタ領域の概略断面図に「M」を付し、周辺トランジスタ領域の概略断面図に「T」を付す。

【0045】

フラッシュメモリセルトランジスタ領域の概略断面図は、ゲート幅方向(x方向)と、ゲート長方向(y方向)とをまとめて示す。本応用例では、フラッシュメモリをn型MOSトランジスタで形成する。

【0046】

周辺トランジスタとして、ワードライン制御回路等に使用され、比較的高電圧(例えば10V)で駆動される高電圧MOSトランジスタと、ロジック回路やビットラインデコーダ等に使用され、比較的低電圧(例えば1.8V)で駆動される低電圧MOSトランジスタとが形成される。本応用例では、周辺トランジスタ領域に、10V駆動n型トランジスタ、10V駆動p型トランジスタ、トリプルウェルを持つ1.8V駆動n型トランジスタ、1.8V駆動n型トランジスタ、及び1.8V駆動p型トランジスタが形成される。

【0047】

図7AM及び図7ATを参照する。シリコン基板1として、例えばp型シリコン基板を用意する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(初期酸化膜)2を形成する。初期酸化膜2上に、例えば、化学気相堆積(CVD)により窒化シリコン膜(アイソレーション窒化膜)3を厚さ110nm程度堆積する。

【0048】

レジストパターンを用いたエッチングでアイソレーション窒化膜3をパターニングし、アイソレーション窒化膜3をマスクとして、初期酸化膜2及びシリコン基板1をエッチングする。シリコン基板1のエッチングにより、素子分離溝4が形成される。素子分離溝4の深さは、例えば300nm程度である。

【0049】

図7B1〜図7B3を参照する。図7B1〜図7B3は、素子分離溝4近傍の拡大断面図を示す。図7B1は、素子分離溝4が形成された時点を示す。素子分離溝4の形成後、APM処理で洗浄を行う。

【0050】

図7B2に示すように、APM処理後、DHF処理を行って、初期酸化膜2の端部を後退させ、素子分離溝4の角部1Cの上面部分を露出させる。DHF処理後、上記実施例の方法により、HPM処理で洗浄を行う。実施例のHPM処理により、角部1Cの不要なエッチング、つまり、角部1Cが不要に丸められることを抑制して、HPM処理を行うことができる。

【0051】

図7B3に示すように、HPM処理後、シリコン基板1の表面を熱酸化して、例えば厚さ5nm程度の酸化シリコン膜5を形成する。素子分離膜4の内面上と、DHF処理で露出した基板1の上面上とに、酸化シリコン膜5が形成される。この熱酸化に伴い、角部1Cが丸められる。角部1Cを丸めることにより、上述のように、MOSトランジスタ駆動時の電界集中を抑制できる。

【0052】

図7CM及び図7CTを参照する。図7CM及び図7CTは、酸化シリコン膜5が形成された状態を、ウエハ全体について示す。

【0053】

図7DM及び図7DTを参照する。素子分離溝4を埋め込んでアイソレーション窒化膜3上に、例えば高密度プラズマ(HDP)CVDにより、酸化シリコン膜6を堆積する。

【0054】

図7EM及び図7ETを参照する。酸化シリコン膜6の上部を、化学機械研磨(CMP)で除去して、アイソレーション窒化膜3を露出させる。これにより、各素子分離溝4に埋め込まれた素子分離絶縁膜6が形成される。

【0055】

図7FM及び図7FTを参照する。アイソレーション窒化膜3が、リン酸ボイルを用いたウエットエッチングにより除去される。初期酸化膜2が、DHF処理により除去される。

【0056】

図7GM及び図7GTを参照する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(犠牲酸化膜)7を形成する。

【0057】

図7HM及び図7HTを参照する。レジストパターンを適宜用いて、フラッシュメモリセル領域及び周辺トランジスタ領域に、ウェル形成やチャネルドーピングの不純物注入を行なう。フラッシュメモリセル領域全面と、10V駆動n型トランジスタ領域とに、高濃度p型ウェルHPWを形成する。なお、フラッシュメモリはp型MOSトランジスタで形成することもでき、その場合には、フラッシュメモリセル領域に高濃度n型ウェルが形成される。

【0058】

フラッシュメモリセル領域全面と、10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域とに、埋め込みn型ウェルENWを形成する。

【0059】

10V駆動p型トランジスタ領域と、10V駆動n型トランジスタ領域の縁部と、トリプルウェル上の1.8V駆動n型トランジスタ領域の縁部とに、高濃度n型ウェルHNWを形成する。

【0060】

図7I1及び図7I2を参照する。図7I1及び図7I2は、素子分離絶縁膜6近傍の拡大断面図を示す。図7I1は、図7HM及び図7HTを参照して説明した不純物注入工程が終了した時点を示す。APM処理で洗浄を行う。

【0061】

図7I2に示すように、APM処理後、DHF処理を行って、犠牲酸化膜7を除去する。なお、同時に素子分離絶縁膜6の酸化シリコン膜もエッチングされる。犠牲酸化膜7を確実に除去するために、犠牲酸化膜7の膜厚に対しややオーバーエッチングとなるようにエッチングを行う。このエッチングに起因して、素子分離溝の角部1Cが露出する。

【0062】

DHF処理後、実施例の方法により、HPM処理で洗浄を行う。ここでのHPM処理も、図7B2を参照して説明したHPM処理と同様に、角部1Cが露出した状態で行われる。これに起因して、角部1Cの不要なエッチングが懸念される。実施例のHPM処理により、角部1Cの不要なエッチングが抑制される。

【0063】

図7JM及び図7JTを参照する。図7JM及び図7JTは、犠牲酸化膜7が除去された状態を、ウエハ全体について示す。不純物注入でダメージを受けた犠牲酸化膜7が除去され、後の工程で、新たにトンネル酸化膜が形成される。

【0064】

図7KM及び図7KTを参照する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(トンネル酸化膜)8を形成する。トンネル酸化膜8上に、例えば、CVDによりポリシリコンを厚さ90nm堆積して、フラッシュメモリセルトランジスタのフローティングゲートとなる導電膜9を形成する。

【0065】

図7LM及び図7LTを参照する。レジストパターンを用いた異方性エッチング(ドライエッチング)で導電膜9をパターニングする。フラッシュメモリセル領域では、導電膜9がゲート幅方向(x方向)に分割される。周辺トランジスタ領域では、導電膜9が全面で除去される。

【0066】

次に、ウエハ全面上に例えばCVDで酸化シリコン膜を厚さ5nm堆積し、この酸化シリコン膜上に例えばCVDで窒化シリコン膜を厚さ8nm堆積し、この窒化シリコン膜を熱酸化し例えば厚さ5nm程度の酸窒化シリコン膜を形成して、ONO膜10を形成する。

【0067】

さらに、レジストパターンを適宜用いて、周辺トランジスタ領域に、ウェル形成やチャネルドーピングの不純物注入を行なう。トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、低濃度p型ウェルLPWが形成される。トリプルウェルを持つ1.8V駆動n型トランジスタ領域では、埋め込みn型ウェルENWと高濃度n型ウェルHNWとで低濃度p型ウェルLPWが囲まれたトリプルウェルが形成される。1.8V駆動p型トランジスタ領域に、低濃度n型ウェルLNWが形成される。

【0068】

図7MM及び図7MTを参照する。フラッシュメモリセル領域を覆うレジストパターンを用いたエッチングにより、周辺トランジスタ領域で、ONO膜10及びトンネル酸化膜8を除去する。ONO膜10の酸窒化シリコン膜及び窒化シリコン膜が、異方性ドライエッチングで除去される。レジストの残った状態で、さらに、ONO膜10の酸化シリコン膜とトンネル酸化膜8とが、等方性ウエットエッチングで除去される。なお最後に、ウエットエッチングでレジスト剥離が行われる。

【0069】

図7NM及び図7NTを参照する。周辺トランジスタ領域のシリコン基板1上に、熱酸化により、例えば厚さ9nmの酸化シリコン膜11を形成する。

【0070】

図7OM及び図7OTを参照する。レジストパターンを用いたウエットエッチングにより、酸化シリコン膜11を、低電圧トランジスタ(トリプルウェルを持つ1.8V駆動n型トランジスタ、1.8V駆動n型トランジスタ、及び1.8V駆動p型トランジスタ)の形成領域で除去し、高電圧トランジスタ(10V駆動n型トランジスタ、及び10V駆動p型トランジスタ)の形成領域で残す。酸化シリコン膜11除去のウエットエッチングには、例えばDHF処理が用いられる。

【0071】

そして、低電圧トランジスタ形成領域のシリコン基板1上に、熱酸化により、例えば厚さ3nmの酸化シリコン膜(ゲート酸化膜)11Lを形成する。この熱酸化により、高電圧トランジスタ形成領域では、酸化シリコン膜11が成長し、例えば厚さ16nmの酸化シリコン膜(ゲート酸化膜)11Hが形成される。

【0072】

図7PM及び図7PTを参照する。フラッシュメモリセル領域のONO膜10と、周辺トランジスタ領域のゲート酸化膜11H及び11Lとを覆って、例えば、CVDによりポリシリコンを厚さ100nm堆積して、メモリセルトランジスタのコントロールゲート電極及び周辺トランジスタのゲート電極となる導電膜12を形成する。導電膜12上に、例えば、CVDで窒化膜を厚さ30nm堆積して、反射防止膜13を形成する。

【0073】

図7QM及び図7QTを参照する。レジストパターンを用いたエッチングにより、反射防止膜13、導電膜12、ONO膜10、及び導電膜9をパターニングして、フラッシュメモリセル領域のゲート電極を形成する。

【0074】

図7RM及び図7RTを参照する。ゲート電極をマスクとしフラッシュメモリセル領域にn型不純物を注入して、フラッシュメモリセルトランジスタのソースドレイン領域14を形成する。なお、フラッシュメモリセルをp型MOSトランジスタで形成する場合は、p型不純物注入により、ソースドレイン領域が形成される。

【0075】

図7SM及び図7STを参照する。フラッシュメモリセル領域のゲート電極側壁を熱酸化して、酸化シリコン膜15を形成する。その後、ウエハ全面上に、例えば、CVDで窒化シリコン膜を厚さ50nm堆積する。この窒化シリコン膜を異方性エッチングして、フラッシュメモリセルトランジスタのゲート電極側壁上に、サイドウォール絶縁膜16を形成する。なお、このエッチングにより、反射防止膜13も除去される。

【0076】

図7TM及び図7TTを参照する。レジストパターンを用いたエッチングで導電膜12をパターニングして、周辺トランジスタ領域のゲート電極を形成する。レジストパターン、及び各トランジスタのゲート電極をマスクとして、周辺トランジスタ領域に、LDD領域17を形成する不純物注入を行なう。

【0077】

10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、n型不純物が注入される。10V駆動p型トランジスタ領域と、1.8V駆動p型トランジスタ領域とに、p型不純物が注入される。

【0078】

図7UM及び図7UTを参照する。ウエハ全面上に、例えば、CVDで酸化シリコン膜を厚さ100nm堆積する。この酸化シリコン膜を異方性エッチングでエッチングして、フラッシュメモリセルトランジスタのゲート電極側壁上、及び周辺トランジスタのゲート電極側壁上に、サイドウォール絶縁膜18を形成する。なお、このエッチングにより、フラッシュメモリセル領域におけるサイドウォール絶縁膜18の外側部分のトンネル酸化膜8、及び、周辺トランジスタ領域におけるサイドウォール絶縁膜18の外側部分のゲート酸化膜11H及び11Lも除去される。

【0079】

さらに、レジストパターン、各トランジスタのゲート電極、及びサイドウォール絶縁膜18をマスクとして、周辺トランジスタ領域に、ソースドレイン領域19を形成する不純物注入を行なう。10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、n型不純物が注入される。10V駆動p型トランジスタ領域と、1.8V駆動p型トランジスタ領域とに、p型不純物が注入される。

【0080】

図7VM及び図7VTを参照する。フラッシュメモリセル領域及び周辺トランジスタ領域において、ゲート電極12上、及びソースドレイン領域14、19上に、例えばコバルトシリサイドにより、シリサイド層20を形成する。

【0081】

図7WM及び図7WTを参照する。ウエハ全面上に、例えば、CVDで窒化シリコン膜を厚さ30nm堆積して、エッチングストッパ膜21を形成する。エッチングストッパ膜21上に、例えば、CVDでボロンリンシリケートガラス(BPSG)を厚さ1600nm堆積して、層間絶縁膜22を形成する。

【0082】

図7XM及び図7XTを参照する。レジストパターンを用い層間絶縁膜22及びエッチングストッパ膜21をエッチングして、フラッシュメモリセルトランジスタのソースドレイン領域14上に配置されたシリサイド層20を露出するコンタクトホールや、周辺トランジスタのソースドレイン領域19上に配置されたシリサイド層20を露出するコンタクトホール等を形成する。エッチングストッパ膜21は、コンタクトホール形成のエッチングにおいて、エッチングストッパとして用いられる。

【0083】

コンタクトホールの内面を覆って層間絶縁膜22上に、例えば、チタン膜を厚さ30nm堆積し、チタン膜上に窒化チタン膜を厚さ20nm堆積し、窒化チタン膜上にタングステン膜を厚さ300nm形成する。層間絶縁膜22上の不要なタングステン膜、窒化チタン膜、及びチタン膜をCMPで除去して、導電プラグ23が形成される。

【0084】

層間絶縁膜22上に、例えば、チタン膜を厚さ60nm堆積し、このチタン膜上に窒化チタン膜を厚さ30nm堆積し、この窒化チタン膜上にアルミニウム膜を厚さ360nm堆積し、アルミニウム膜上にチタン膜を厚さ5nm堆積し、このチタン膜上に窒化チタン膜を厚さ70nm形成する。レジストパターンを用いたエッチングにより、この積層金属膜をパターニングして、第1メタル配線24を形成する。

【0085】

図7YMを参照する。さらに、上層の配線構造を形成する。上層の配線構造は、代表としてフラッシュメモリセル領域を示す。第1メタル配線24を覆って層間絶縁膜22上に、例えば、HDPCVDにより酸化シリコンを厚さ720nm堆積して、層間絶縁膜25を形成する。層間絶縁膜25上に、例えば、CVDによりテトラエトキシシラン(TEOS)を厚さ1100nm堆積して、層間絶縁膜26を形成する。層間絶縁膜26の上部を、CMPで平坦化する。

【0086】

その後、レジストパターンを用い層間絶縁膜26及び25をエッチングして、第1メタル配線24を露出するコンタクトホールを形成する。コンタクトホールの内面を覆って層間絶縁膜26上に、例えば、チタン膜を厚さ10nm堆積し、チタン膜上に窒化チタン膜を厚さ7nm堆積し、窒化チタン膜上にタングステン膜を厚さ300nm形成する。層間絶縁膜26上の不要なタングステン膜、窒化チタン膜、及びチタン膜をCMPで除去して、導電プラグ27が形成される。層間絶縁膜26上に、第1メタル配線24と同様にして、第2メタル配線28を形成する。

【0087】

以後、同様な工程を繰り返すことにより、多層配線構造が形成される。図7YMに示す例では、配線として第5メタル配線29までが形成される。第5メタル配線29上に、HDPCVDで形成した酸化シリコンによる層間絶縁膜30が形成され、層間絶縁膜30上に、例えば、CVDにより窒化シリコンが厚さ1000nm堆積されて、カバー絶縁膜31が形成される。このようにして、応用例による半導体装置が形成される。

【0088】

以上説明したように、応用例の半導体装置製造工程では、素子分離溝の角部を丸める熱酸化の前処理として、APM処理、DHF処理、及びHPM処理が順次行われる(図7B1〜図7B3参照)。また、フラッシュメモリセルトランジスタのトンネル酸化膜を形成する熱酸化の前処理として、APM処理、DHF処理、及びHPM処理が順次行われる(図7I1及び図7I2参照)。DHF処理後に行われるHPM処理に、実施例の方法を適用することにより、シリコンの不要なエッチングを抑制することができ、特に、素子分離溝の角部形状の制御性向上が図られる。

【0089】

次に、実施例の処理の適用による、フラッシュメモリセルトランジスタの電気特性改善効果について説明する。上記応用例と同様にして、フラッシュメモリセルトランジスタを作製した。ただし、素子分離溝角部の熱酸化の前処理として行うHPM処理は、比較例の方法を用いた。トンネル酸化膜形成の熱酸化の前処理として行うHPM処理に、実施例の方法を用いた。このように作製されたサンプルを、実施例のフラッシュメモリと呼ぶこととする。

【0090】

各々フラッシュメモリセルトランジスタが多数形成されたウエハを、複数枚作製した。フラッシュメモリは、p型MOSトランジスタを用いて形成した。チャネル注入条件を振って、3種類の異なるチャネル条件のサンプルを作製した。

【0091】

比較例のフラッシュメモリとして、素子分離溝角部の熱酸化の前処理として行うHPM処理、及び、トンネル酸化膜形成の熱酸化の前処理として行うHPM処理の両方とも、比較例の方法を用いたサンプルを作製した。

【0092】

なお、このフラッシュメモリは、以下のように動作する。書き込み時は、例えば、ゲート電圧10V、ソース電圧1.8V、ドレイン電圧0V、及び基板電圧5Vを印加する。これにより、ドレイン端の強電界によりバンド間遷移を起こした電子が、ドレイン近傍の空乏層で加速され、フローティングゲートに注入される。つまり、ドレインから電子がバンドトゥバンドトンネリング(BTBT)によりフローティングゲートに蓄えられる。p型MOSトランジスタであるが、電子がフローティングゲートに蓄積される。消去時は、例えば、ゲート電圧−15.5V、ソース電圧0V、ドレイン電圧0V、及び基板電圧0Vを印加して、フローティングゲートに蓄えられた電子を、基板側に引き抜く。

【0093】

図8は、消去状態におけるフラッシュメモリトランジスタの閾値電圧(イレースVth)とそのばらつきを、実施例及び比較例のフラッシュメモリについて示したグラフである。各プロットは、1枚のウエハを示し、ウエハ内に多数形成されたフラッシュメモリセルトランジスタのイレースVthの、平均値が横軸上に、分散が縦軸上に示されている。実施例の結果が丸で、比較例の結果が菱形でプロットされている。

【0094】

実施例は比較例に比べて、分散が減少している。すなわち、ウエハ内に形成された複数のフラッシュメモリにおける、イレースVthのばらつきが減少している。このような、電気特性のばらつき減少は、実施例の処理により、素子分離溝の角部形状の制御性が向上し、フラッシュメモリごとの角部形状のばらつきが減少したためと解釈することができる。

【0095】

なお、上記実施例の処理では、処理液温度がHPM処理の目標温度に達してから、HClの投入を開始した。HCl投入開始時点は、H2O2の投入開始時点より後であれば、処理液温度がHPM処理の目標温度に達した時点以後に限定されないであろう。なお、HClを投入した時点で、HPM処理の薬液となるが、処理能力を高めるために、HPM処理の目標温度まで処理液温度を上昇させることが好ましい。

【0096】

なお、上記実施例の処理では、H2O2の投入と同時かそれより遅く温水を導入したが、図9に示すように、他の実施例として、温水の導入開始後に、H2O2を投入する方法も可能であろう。この場合、シリコンがエッチングされやすいような高い水温(例えば30℃以上)に達する前に、H2O2の投入を開始することが好ましい。

【0097】

実施例でのH2O2濃度を算出してみると、目標温度に達した時点で2.4wt%、30℃で1.2wt%であった。そこで、濃度の目安を挙げるならば、シリコンがエッチングされやすいような高い水温(例えば30℃以上)に達する前に、例えば、H2O2濃度が1.2wt%以上となっていることが好ましく、2.4wt%以上となっていることがさらに好ましい。

【0098】

なお、上記実施例の処理では、DHF処理後にHPM処理を行った。ここで、DHF処理後にAPM処理を行う場合について考える。APM処理の薬液は、H2O2がHPM処理と共通であり、HPM処理のHClの替わりにNH4OHを用いるものと捉えることができる。

【0099】

比較例のHPM処理について考察したのと同様に、温水を準備してからH2O2とNH4OHとを投入するAPM処理では、温水によりシリコンがエッチングされやすい。APM処理においても、H2O2投入と同時かそれより遅く温水を導入することにより、温水によるシリコンエッチングを抑制できる。

【0100】

NH4OH投入は、例えば、処理液温度がAPM処理の目標温度に到達後開始することができるが、HPM処理でのHCl投入と同様に、H2O2の投入開始時点より後であればよいであろう。また、APM処理の場合も、HPM処理について考察したのと同様に、温水導入後にH2O2を投入する方法も可能であろう。

【0101】

なお、上記応用例の半導体装置製造工程では、素子分離溝角部の熱酸化の前処理、または、トンネル酸化膜形成の熱酸化の前処理として、最初にAPM処理、次にDHF処理、最後にHPF処理を行った。これらの前処理は、例えば、最初にDHF処理を行い、次にAPM処理を行い、最後にHPM処理を行うようにすることもできる。この場合は、DHF処理にAPM処理が続くこととなる。

【0102】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0103】

以上説明した実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程と

を有する半導体装置の製造方法。

(付記2)

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する付記1に記載の半導体装置の製造方法。

(付記3)

前記槽内の処理液の温度が目標温度に到達後、HClまたはNH4OHを導入する付記2に記載の半導体装置の製造方法。

(付記4)

前記目標温度は60℃〜80℃の範囲の温度であり、前記槽内にHClを導入する付記3に記載の半導体装置の製造方法。

(付記5)

前記目標温度は40℃〜80℃の範囲の温度であり、前記槽内にNH4OHを導入する付記3に記載の半導体装置の製造方法。

(付記6)

前記水の温度は、24℃〜26℃の範囲である付記1〜5のいずれか1つに記載の半導体装置の製造方法。

(付記7)

前記水及び前記温水の溶存酸素量は、80ppb以下である付記1〜6のいずれか1つに記載の半導体装置の製造方法。

(付記8)

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板上に酸化シリコン膜を形成し、前記酸化シリコン膜上にマスクパターンを形成し、前記マスクパターンの開口内で前記酸化シリコン膜と前記シリコン基板をエッチングして、前記シリコン基板に素子分離溝を形成する工程を有する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記9)

前記希フッ酸処理する工程は、前記酸化シリコン膜の端部を後退させ、

さらに、

前記酸化シリコン膜の端部を後退させた後、前記素子分離溝の内面に、熱酸化により酸化シリコン膜を成長させる工程を有する付記8に記載の半導体装置の製造方法。

(付記10)

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板に素子分離溝を形成し、前記素子分離溝内に酸化シリコン膜を埋め込み、前記素子分離溝の外側の前記シリコン基板上に酸化シリコン膜を形成する工程を有する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記11)

前記希フッ酸処理する工程の前、前記シリコン基板上に酸化シリコン膜を形成する工程の後、さらに、

前記シリコン基板上の酸化シリコン膜を通して、前記酸化シリコン基板に不純物を注入する工程を有する付記10に記載の半導体装置の製造方法。

(付記12)

前記希フッ酸処理する工程は、前記シリコン基板上の前記酸化シリコン膜を除去し、

さらに、

前記シリコン基板上の前記酸化シリコン膜を除去した後、前記シリコン基板上に、熱酸化により酸化シリコン膜を成長させる工程を有する付記10または11に記載の半導体装置の製造方法。

(付記13)

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、前記槽内に前記水よりも温度の高い温水を導入するとともに、前記槽内の水温が30℃に達する前に、前記槽内にH2O2を導入する工程と

を有する半導体装置の製造方法。

(付記14)

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する付記13に記載の半導体装置の製造方法。

(付記15)

前記水の温度は、24℃〜26℃の範囲である付記13または14に記載の半導体装置の製造方法。

【符号の説明】

【0104】

101 槽

102 ウエハ

103 処理液

104 主供給管

105 HF供給管

106 HCl供給管

107 H2O2供給管

108 NH4OH供給管

109 室温水・温水供給管

110 室温水供給管

111 温水供給管

105a〜111a、111c バルブ

111b 温水ユニット

1 シリコン基板

2 初期酸化膜

3 アイソレーション窒化膜

4 素子分離溝

5 酸化シリコン膜

6 素子分離絶縁膜

7 犠牲酸化膜

8 トンネル酸化膜

9 導電膜(フローティングゲート)

10 ONO膜

11 酸化シリコン膜

11H、11L ゲート酸化膜

12 導電膜(コントロールゲート電極、周辺トランジスタのゲート電極)

13 反射防止膜

14 メモリセルトランジスタのソースドレイン領域

15 酸化シリコン膜

16 サイドウォール絶縁膜

17 周辺トランジスタのLDD領域

18 サイドウォール絶縁膜

19 周辺トランジスタのソースドレイン領域

20 シリサイド層

21 エッチングストッパ膜

22、25、26、30 層間絶縁膜

23、27 導電プラグ

24、28、29 メタル配線

31 カバー絶縁膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造工程において、種々の洗浄技術が用いられている(例えば特許文献1参照)。洗浄処理として、例えば、希フッ化水素酸水溶液(DHF)処理や、アンモニア過酸化水素水混合水溶液(APM)処理や、塩酸過酸化水素水混合水溶液(HPM)処理が挙げられる。なお、例えばDHF処理は、洗浄のみを目的として行われるわけではなく、例えば酸化シリコン膜を所望領域で除去するような場合にも用いられる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−53050号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0006】

H2O2の導入と同時かそれよりも遅く温水が導入される。これにより、H2O2の導入なしにシリコンが温水に曝される場合に比べて、シリコンのエッチングが抑制される。

【図面の簡単な説明】

【0007】

【図1】図1は、DHF処理、APM処理、及びHPM処理についてまとめた表である。

【図2】図2は、DHF処理、APM処理、及びHPM処理を行う処理装置を示す概略図である。

【図3】図3は、比較例の処理フローと、処理液温度とH2O2濃度及びHCl濃度を示すグラフである。

【図4】図4A〜図4Cは、比較例の処理を施したウエハのTEM写真である。

【図5】図5は、実施例の処理フローと、処理液温度とH2O2濃度及びHCl濃度と比抵抗とを示すグラフである。

【図6】図6Aは、DHF処理時のウエハのTEM写真であり、図6Bは、実施例の処理を施したウエハのTEM写真であり、図6Cは、比較例の処理を施したウエハのTEM写真である。

【図7−1】図7AM及び図7ATは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−2】図7B1〜図7B3は、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−3】図7CM及び図7CTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−4】図7DM及び図7DTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−5】図7EM及び図7ETは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−6】図7FM及び図7FTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−7】図7GM及び図7GTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−8】図7HM及び図7HTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−9】図7I1及び図7I2は、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−10】図7JM及び図7JTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−11】図7KM及び図7KTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−12】図7LM及び図7LTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−13】図7MM及び図7MTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−14】図7NM及び図7NTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−15】図7OM及び図7OTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−16】図7PM及び図7PTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−17】図7QM及び図7QTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−18】図7RM及び図7RTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−19】図7SM及び図7STは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−20】図7TM及び図7TTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−21】図7UM及び図7UTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−22】図7VM及び図7VTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−23】図7WM及び図7WTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−24】図7XMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−25】図7XTは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−26】図7YMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図8】図8は、消去状態におけるフラッシュメモリセルトランジスタの閾値電圧とそのばらつきを、実施例及び比較例のフラッシュメモリについて示したグラフである。

【図9】他の実施例の処理工程の一部を示すフローである。

【発明を実施するための形態】

【0008】

まず、半導体装置製造工程において用いられる、希フッ化水素酸水溶液(DHF)処理、アンモニア過酸化水素水混合水溶液(APM)処理、及び塩酸過酸化水素水混合水溶液(HPM)処理について説明する。

【0009】

図1は、DHF処理、APM処理、及びHPM処理についてまとめた表である。DHF処理は、薬液として水(H2O)にフッ化水素酸(HF)を混合した希フッ化水素酸水溶液(DHF)を用い、酸化膜除去や金属除去を目的として行われる。通常、処理温度は室温であり、エッチングレートの制御等の必要に応じ、室温より高温の処理温度とすることもある。室温とは、例えば24℃〜26℃(例えば25℃)である。なお、DHF処理では、酸化還元電位の高い金属(例えばCu等)の除去は難しい。

【0010】

APM処理は、薬液として水(H2O)に過酸化水素水(H2O2)及びアンモニア水(NH4OH)を混合したアンモニア過酸化水素水混合水溶液(APM)を用い、例えばパーティクル除去を目的として行われる。処理温度は、除去性能を向上させるために室温より高温が好ましく、例えば40℃〜80℃である。

【0011】

HPM処理は、薬液として水(H2O)に過酸化水素水(H2O2)及び塩化水素酸(HCl)を混合した塩酸過酸化水素水混合水溶液(HPM)を用い、例えば金属除去を目的として行われる。処理温度は、除去性能を向上させるために室温より高温が好ましく、例えば60℃〜80℃である。

【0012】

図2は、DHF処理、APM処理、及びHPM処理を行う処理装置を示す概略図である。この処理装置は、1つの槽でDHF処理、APM処理、及びHPM処理を行うことができるワンバス処理装置である。

【0013】

槽101内に、処理対象物であるウエハ102が載置される。槽101内に供給される水または薬液を、まとめて処理液103と呼ぶ。槽101は、処理液103が、下側から導入され、上側から排出される構造となっている。槽101に導入される処理液103の種類を切り替えることにより、槽101内の処理液103を置換することができる。これにより、槽101内にウエハ102を載置したまま、DHF処理、APM処理、及びHPM処理のうちの任意の処理を行うことができる。

【0014】

複数の処理(例えばDHF処理とHPM処理)を順次行う場合であっても、処理開始から処理終了まで、ウエハ102は処理液103中に浸かった状態が保たれる。これにより、処理中の大気曝露に起因するパーティクル付着、汚染が抑制される。例えば、各処理を別々の処理槽で行う水洗槽渡り処理の場合(例えば、DHF処理をDHF処理槽で行い、水洗槽を介した後、HPM処理をHPM処理槽で行う場合)、処理槽間の移動時の大気曝露に起因して、ウエハへのパーティクル付着等が起こりやすい。

【0015】

主供給管104を通って、槽101に処理液103が導入される。主供給管104に、HF供給管105、HCl供給管106、H2O2供給管107、NH4OH供給管108、及び、室温水・温水供給管109が、それぞれ、バルブ105a〜109aを介して接続されている。各バルブ105a〜108aの開閉により、HF、HCl、H2O2、及びNH4OHの供給開始と供給停止が制御される。バルブ109aの開閉により、室温水または温水の供給開始と供給停止が制御される。

【0016】

室温水・温水供給管109に、室温水供給管110及び温水供給管111が、それぞれ、バルブ110a及び111aを介して接続されている。H2O源から室温の水が、室温水供給管110または温水供給管111に供給される。温水供給管111は、所望温度の温水が得られるように水を加熱する温水ユニット111bを備え、温水ユニット111bよりH2O源側に配置されたバルブ111cを介して、H2O源に接続されている。

【0017】

槽101へ室温水を供給するときは、バルブ110aを開とし、バルブ111a及びバルブ111cを閉とする。槽101へ温水を供給するときは、バルブ110aを閉とし、バルブ111a及びバルブ111cを開とする。

【0018】

半導体装置の製造工程で用いられる純水は、微粒子個数、金属濃度、有機物濃度、溶存酸素量等が管理されている。溶存酸素は、シリコン上の自然酸化膜成長抑制等のために、低く抑えることが好ましい。純水の溶存酸素量は、半導体装置製造工場受け入れ時は例えば2ppm〜3ppmであり、その後の脱気により、製造工程で使用される際には例えば2ppb以下にされている。

【0019】

次に、比較例による処理について説明する。比較例の処理では、APM処理とDHF処理とHPM処理とが順次行われる。比較例のAPM処理、DHF処理、及びHPM処理は、例えば、MOSトランジスタ製造における、シャロートレンチアイソレーション(STI)による素子分離絶縁膜の形成工程で行われる。以下、さらに詳しく説明する。

【0020】

図7AM及び図7ATは、シリコン基板1に、素子分離絶縁膜の埋め込まれる素子分離溝4が形成された状態を示す概略断面図である。シリコン基板1上に、熱酸化で酸化シリコン膜(初期酸化膜)2が形成され、初期酸化膜2上に、窒化膜(アイソレーション窒化膜)3が成膜され、アイソレーション窒化膜3が、素子分離溝4の形成領域上で開口する形状にパターニングされる。アイソレーション窒化膜3をマスクとして、初期酸化膜2とシリコン基板1とがエッチングされて、素子分離溝4が形成される。

【0021】

図7B1〜図7B3は、素子分離溝4近傍の拡大断面図を示す。図7B1は、素子分離溝4が形成された時点を示す。素子分離溝4の縁を画定している、シリコン基板1の角部1Cは、アクティブ領域端部となる。アクティブ領域端部の角部1Cが尖っていると、角部1Cで、MOSトランジスタ駆動時に電界集中が生じやすい。なお以後、角部1Cを、「素子分離溝の角部」と表現することもある。

【0022】

次に、図7B2に示すように、DHF処理が行われる。DHF処理により、初期酸化膜2の端部を後退させ、角部1Cの上面部分を露出させる。

【0023】

次に、図7B3に示すように、角部1Cを熱酸化して、酸化シリコン膜5を形成する。この熱酸化により、角部1Cが丸められる。角部1Cを丸めることにより、上述の電界集中を抑制できる。その後、素子分離溝4に素子分離絶縁膜が埋め込まれる。

【0024】

DHF処理に伴い、自然酸化膜等も除去されることにより、基板1のシリコン表面が露出した部分が生じる。露出したシリコン表面は疎水性でパーティクルを寄せ付けやすい。また、DHF処理のみでは除去できない金属もある。ここでは、図7B2に示すDHF処理の後、図7B3に示す熱酸化の前の洗浄として、HPM処理を行う。なお、図7B1に示す素子分離溝4形成の後、図7B2に示すDHF処理の前の洗浄として、APM処理を行う。

【0025】

図3の上側部分に、比較例の処理フローを示す。(APM処理の後、)DHF処理が行われる。DHF処理により、基板のシリコン表面が露出する。DHF処理後、槽内に室温水を導入し、処理液を室温水に置換して、水洗を行う。室温水での水洗後、槽内に温水を導入し、温水を使用するHPM処理を準備する(温水準備)。温水準備後、槽内に過酸化水素水と塩化水素酸とを投入して、HPM処理を行う。HPM処理後、槽内に室温水を導入し、処理液を室温水に置換して、水洗を行う。その後、ウエハを乾燥槽へ移し、乾燥を行う。

【0026】

図3の下側部分に、温水準備及びHPM処理の期間における、槽内の処理液温度と、処理液のH2O2濃度及びHCl濃度を示す。H2O2濃度及びHCl濃度は、それぞれ、HPM処理工程での目標濃度を100%とした相対濃度で示す。

【0027】

温水準備工程において、槽内に温水を導入することにより、水温が上昇する。槽内の水温がHPM処理の目標温度に達したら、槽内にH2O2及びHClが投入されて、HPM処理が開始される。

【0028】

比較例の処理によって生じた問題について説明する。図4A〜図4Cは、比較例の処理を施したウエハの透過型電子顕微鏡(TEM)写真である。

【0029】

図4Aは、図7B1に対応し、シリコン基板に素子分離溝が形成された時点の写真である。中央下側の台形状の領域が、シリコン基板であり、その脇の領域が素子分離溝である。シリコン基板上に、初期酸化膜を介して、アイソレーション窒化膜が形成されている。

【0030】

図4Bは、図7B2に対応し、APM処理の後のDHF処理により、初期酸化膜の端部が後退した時点の写真である。

【0031】

図4Cは、DHF処理の後、HPM処理を行った時点の写真である。素子分離溝の角部を、図4Cに、破線で囲んで示す。上述のように、角部は、HPM処理の後の熱酸化によって丸められる。角部の丸め形状は、この熱酸化工程で制御したい。このため、この熱酸化の前までは、素子分離溝を形成した時点での角部形状がそのまま維持されていることが好ましい。

【0032】

図4Bに示すように、DHF処理後までは、素子分離溝形成時とほぼ同様な角部形状が維持されている。しかし、図4Cに示すように、HPM処理後は、角部がエッチングされて丸まってしまっている。熱酸化まで角部形状をそのまま維持したいという観点からは、このようなエッチングは好ましくない。

【0033】

本願発明者は、素子分離溝の角部がエッチングされた原因について考察した。図3に示したように、比較例の方法では、DHF処理の後、水洗及び温水準備を経て、HPM処理が行われる。HPM処理は、薬液がH2O2やHClを含んでおり酸性である。処理液が酸性の下では、シリコンは固体として存在する方がイオンとして存在するよりも安定であり、シリコンのエッチングが抑制されると考えられる。従って、水洗工程及び温水準備工程において、つまり水によって、シリコンがエッチングされている可能性が高い。特に、室温水より高温(例えば30℃以上)の温水によるエッチングが起こりやすいと考えられる。

【0034】

次に、本発明の実施例による処理について説明する。上記比較例と同様に、例えば、MOSトランジスタ製造の素子分離絶縁膜形成工程において、APM処理、DHF処理、及びHPM処理が行われる。

【0035】

図5の上側部分に、実施例の処理フローを示す。図5の下側部分に、水洗、温水準備、及びHPM処理の期間における、槽内の処理液温度と、処理液のH2O2濃度及びHCl濃度を示す。また、水洗期間における処理液の比抵抗を示す。H2O2濃度及びHCl濃度は、比較例の説明と同様に相対濃度で示す。処理液の比抵抗は、DHF処理完了時を100%、水洗完了時を0%とした相対値で示す。

【0036】

本実施例の処理フローについて説明する。(APM処理の後、)DHF処理が行われる。DHF処理に伴って、基板のシリコン表面が露出する。DHF処理後、水洗を行う。水洗工程において、室温水が槽内に導入され、DHF処理の薬液(希フッ酸)が槽内から排出され、処理液が室温水に置換される。水洗工程で、処理液が水に置換されたかどうかは、例えば比抵抗により判定される。処理液の比抵抗が、純水の比抵抗(約18.3MΩ・cm)に達したら、処理液が水に置換されたと判定される。

【0037】

水洗後、温水準備が行われる。実施例の温水準備工程では、槽内に温水を導入するとともに、予め、HPM処理で用いられるH2O2も導入する。水洗工程で処理液が室温水に置換された後に、槽内へのH2O2導入が開始される。温水の導入開始時点は、H2O2の導入開始時点と同時かそれよりも遅く設定されている。

【0038】

処理液温度がHPM処理の目標温度に達したら、槽内へのHCl導入が開始されて、HPM処理が開始される。HPM処理後の水洗及びその後の乾燥は、比較例と同様である。

【0039】

実施例の処理では、H2O2が温水準備工程で処理液に投入される。これにより、DHF処理で露出したシリコン表面上に、薄い酸化膜が形成されて、温水によるシリコンのエッチングが抑制されると考えられる。

【0040】

なお、溶存酸素の有無に関わらず、水によるシリコンのエッチングは生じると考えられるが、水中の溶存酸素量の低い方が、エッチングは生じやすいようである。エッチングの生じやすい溶存酸素量の目安を挙げるならば、例えば80ppb以下である。溶存酸素量の少ない純水中で、シリコンの構造的に安定な面(例えば(111)面)が出るようにエッチングが進みやすくなるようであり、比較例のTEM像において、素子分離溝幅はほぼそのままで角部が斜めに削れているのは、溶存酸素の少ない純水中で安定面が出ようとしているということと理解できる。

【0041】

シリコンのエッチング抑制の観点からは、処理液温度が上昇した時点で、処理液中にH2O2が含まれていることが望ましい。H2O2の投入と同時かそれより遅く温水を導入することにより、温度上昇時において確実に、処理液中にH2O2が含まれるようにできる。

【0042】

なお、温水に比べればエッチングレートは遅いが、室温水でもシリコンのエッチングはある程度起こると考えられる。このため、DHF処理後の水洗途中からH2O2を投入すればよいようにも思われる。しかし、水洗途中に、希フッ酸が処理液に残った状態でH2O2が投入されると、H2O2によるシリコン酸化と、希フッ酸による酸化シリコンのエッチングとが繰り返されて、シリコンが過度にエッチングされてしまうこととなる。このため、H2O2投入は、希フッ酸が排出された後に開始することが望ましい。

【0043】

図6A〜図6Cは、ウエハのTEM写真である。図6Aは、DHF処理時点の写真である。図6Bは、実施例のHPM処理後の写真である。比較のため、図6Cとして、比較例のHPM処理後の写真(図4Cと同一)を並べる。実施例の処理により、HPM処理後において、素子分離溝の角部のエッチングが抑制されていることがわかる。

【0044】

次に、実施例の処理を応用した、半導体装置の製造方法について説明する。図7AM、図7AT〜図7YMは、応用例による半導体装置の製造方法の主要工程を示す概略断面図である。本応用例では、フラッシュメモリセルトランジスタと周辺トランジスタとが同時形成される。フラッシュメモリセルトランジスタ領域の概略断面図に「M」を付し、周辺トランジスタ領域の概略断面図に「T」を付す。

【0045】

フラッシュメモリセルトランジスタ領域の概略断面図は、ゲート幅方向(x方向)と、ゲート長方向(y方向)とをまとめて示す。本応用例では、フラッシュメモリをn型MOSトランジスタで形成する。

【0046】

周辺トランジスタとして、ワードライン制御回路等に使用され、比較的高電圧(例えば10V)で駆動される高電圧MOSトランジスタと、ロジック回路やビットラインデコーダ等に使用され、比較的低電圧(例えば1.8V)で駆動される低電圧MOSトランジスタとが形成される。本応用例では、周辺トランジスタ領域に、10V駆動n型トランジスタ、10V駆動p型トランジスタ、トリプルウェルを持つ1.8V駆動n型トランジスタ、1.8V駆動n型トランジスタ、及び1.8V駆動p型トランジスタが形成される。

【0047】

図7AM及び図7ATを参照する。シリコン基板1として、例えばp型シリコン基板を用意する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(初期酸化膜)2を形成する。初期酸化膜2上に、例えば、化学気相堆積(CVD)により窒化シリコン膜(アイソレーション窒化膜)3を厚さ110nm程度堆積する。

【0048】

レジストパターンを用いたエッチングでアイソレーション窒化膜3をパターニングし、アイソレーション窒化膜3をマスクとして、初期酸化膜2及びシリコン基板1をエッチングする。シリコン基板1のエッチングにより、素子分離溝4が形成される。素子分離溝4の深さは、例えば300nm程度である。

【0049】

図7B1〜図7B3を参照する。図7B1〜図7B3は、素子分離溝4近傍の拡大断面図を示す。図7B1は、素子分離溝4が形成された時点を示す。素子分離溝4の形成後、APM処理で洗浄を行う。

【0050】

図7B2に示すように、APM処理後、DHF処理を行って、初期酸化膜2の端部を後退させ、素子分離溝4の角部1Cの上面部分を露出させる。DHF処理後、上記実施例の方法により、HPM処理で洗浄を行う。実施例のHPM処理により、角部1Cの不要なエッチング、つまり、角部1Cが不要に丸められることを抑制して、HPM処理を行うことができる。

【0051】

図7B3に示すように、HPM処理後、シリコン基板1の表面を熱酸化して、例えば厚さ5nm程度の酸化シリコン膜5を形成する。素子分離膜4の内面上と、DHF処理で露出した基板1の上面上とに、酸化シリコン膜5が形成される。この熱酸化に伴い、角部1Cが丸められる。角部1Cを丸めることにより、上述のように、MOSトランジスタ駆動時の電界集中を抑制できる。

【0052】

図7CM及び図7CTを参照する。図7CM及び図7CTは、酸化シリコン膜5が形成された状態を、ウエハ全体について示す。

【0053】

図7DM及び図7DTを参照する。素子分離溝4を埋め込んでアイソレーション窒化膜3上に、例えば高密度プラズマ(HDP)CVDにより、酸化シリコン膜6を堆積する。

【0054】

図7EM及び図7ETを参照する。酸化シリコン膜6の上部を、化学機械研磨(CMP)で除去して、アイソレーション窒化膜3を露出させる。これにより、各素子分離溝4に埋め込まれた素子分離絶縁膜6が形成される。

【0055】

図7FM及び図7FTを参照する。アイソレーション窒化膜3が、リン酸ボイルを用いたウエットエッチングにより除去される。初期酸化膜2が、DHF処理により除去される。

【0056】

図7GM及び図7GTを参照する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(犠牲酸化膜)7を形成する。

【0057】

図7HM及び図7HTを参照する。レジストパターンを適宜用いて、フラッシュメモリセル領域及び周辺トランジスタ領域に、ウェル形成やチャネルドーピングの不純物注入を行なう。フラッシュメモリセル領域全面と、10V駆動n型トランジスタ領域とに、高濃度p型ウェルHPWを形成する。なお、フラッシュメモリはp型MOSトランジスタで形成することもでき、その場合には、フラッシュメモリセル領域に高濃度n型ウェルが形成される。

【0058】

フラッシュメモリセル領域全面と、10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域とに、埋め込みn型ウェルENWを形成する。

【0059】

10V駆動p型トランジスタ領域と、10V駆動n型トランジスタ領域の縁部と、トリプルウェル上の1.8V駆動n型トランジスタ領域の縁部とに、高濃度n型ウェルHNWを形成する。

【0060】

図7I1及び図7I2を参照する。図7I1及び図7I2は、素子分離絶縁膜6近傍の拡大断面図を示す。図7I1は、図7HM及び図7HTを参照して説明した不純物注入工程が終了した時点を示す。APM処理で洗浄を行う。

【0061】

図7I2に示すように、APM処理後、DHF処理を行って、犠牲酸化膜7を除去する。なお、同時に素子分離絶縁膜6の酸化シリコン膜もエッチングされる。犠牲酸化膜7を確実に除去するために、犠牲酸化膜7の膜厚に対しややオーバーエッチングとなるようにエッチングを行う。このエッチングに起因して、素子分離溝の角部1Cが露出する。

【0062】

DHF処理後、実施例の方法により、HPM処理で洗浄を行う。ここでのHPM処理も、図7B2を参照して説明したHPM処理と同様に、角部1Cが露出した状態で行われる。これに起因して、角部1Cの不要なエッチングが懸念される。実施例のHPM処理により、角部1Cの不要なエッチングが抑制される。

【0063】

図7JM及び図7JTを参照する。図7JM及び図7JTは、犠牲酸化膜7が除去された状態を、ウエハ全体について示す。不純物注入でダメージを受けた犠牲酸化膜7が除去され、後の工程で、新たにトンネル酸化膜が形成される。

【0064】

図7KM及び図7KTを参照する。シリコン基板1上に、熱酸化により、例えば厚さ10nm程度の酸化シリコン膜(トンネル酸化膜)8を形成する。トンネル酸化膜8上に、例えば、CVDによりポリシリコンを厚さ90nm堆積して、フラッシュメモリセルトランジスタのフローティングゲートとなる導電膜9を形成する。

【0065】

図7LM及び図7LTを参照する。レジストパターンを用いた異方性エッチング(ドライエッチング)で導電膜9をパターニングする。フラッシュメモリセル領域では、導電膜9がゲート幅方向(x方向)に分割される。周辺トランジスタ領域では、導電膜9が全面で除去される。

【0066】

次に、ウエハ全面上に例えばCVDで酸化シリコン膜を厚さ5nm堆積し、この酸化シリコン膜上に例えばCVDで窒化シリコン膜を厚さ8nm堆積し、この窒化シリコン膜を熱酸化し例えば厚さ5nm程度の酸窒化シリコン膜を形成して、ONO膜10を形成する。

【0067】

さらに、レジストパターンを適宜用いて、周辺トランジスタ領域に、ウェル形成やチャネルドーピングの不純物注入を行なう。トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、低濃度p型ウェルLPWが形成される。トリプルウェルを持つ1.8V駆動n型トランジスタ領域では、埋め込みn型ウェルENWと高濃度n型ウェルHNWとで低濃度p型ウェルLPWが囲まれたトリプルウェルが形成される。1.8V駆動p型トランジスタ領域に、低濃度n型ウェルLNWが形成される。

【0068】

図7MM及び図7MTを参照する。フラッシュメモリセル領域を覆うレジストパターンを用いたエッチングにより、周辺トランジスタ領域で、ONO膜10及びトンネル酸化膜8を除去する。ONO膜10の酸窒化シリコン膜及び窒化シリコン膜が、異方性ドライエッチングで除去される。レジストの残った状態で、さらに、ONO膜10の酸化シリコン膜とトンネル酸化膜8とが、等方性ウエットエッチングで除去される。なお最後に、ウエットエッチングでレジスト剥離が行われる。

【0069】

図7NM及び図7NTを参照する。周辺トランジスタ領域のシリコン基板1上に、熱酸化により、例えば厚さ9nmの酸化シリコン膜11を形成する。

【0070】

図7OM及び図7OTを参照する。レジストパターンを用いたウエットエッチングにより、酸化シリコン膜11を、低電圧トランジスタ(トリプルウェルを持つ1.8V駆動n型トランジスタ、1.8V駆動n型トランジスタ、及び1.8V駆動p型トランジスタ)の形成領域で除去し、高電圧トランジスタ(10V駆動n型トランジスタ、及び10V駆動p型トランジスタ)の形成領域で残す。酸化シリコン膜11除去のウエットエッチングには、例えばDHF処理が用いられる。

【0071】

そして、低電圧トランジスタ形成領域のシリコン基板1上に、熱酸化により、例えば厚さ3nmの酸化シリコン膜(ゲート酸化膜)11Lを形成する。この熱酸化により、高電圧トランジスタ形成領域では、酸化シリコン膜11が成長し、例えば厚さ16nmの酸化シリコン膜(ゲート酸化膜)11Hが形成される。

【0072】

図7PM及び図7PTを参照する。フラッシュメモリセル領域のONO膜10と、周辺トランジスタ領域のゲート酸化膜11H及び11Lとを覆って、例えば、CVDによりポリシリコンを厚さ100nm堆積して、メモリセルトランジスタのコントロールゲート電極及び周辺トランジスタのゲート電極となる導電膜12を形成する。導電膜12上に、例えば、CVDで窒化膜を厚さ30nm堆積して、反射防止膜13を形成する。

【0073】

図7QM及び図7QTを参照する。レジストパターンを用いたエッチングにより、反射防止膜13、導電膜12、ONO膜10、及び導電膜9をパターニングして、フラッシュメモリセル領域のゲート電極を形成する。

【0074】

図7RM及び図7RTを参照する。ゲート電極をマスクとしフラッシュメモリセル領域にn型不純物を注入して、フラッシュメモリセルトランジスタのソースドレイン領域14を形成する。なお、フラッシュメモリセルをp型MOSトランジスタで形成する場合は、p型不純物注入により、ソースドレイン領域が形成される。

【0075】

図7SM及び図7STを参照する。フラッシュメモリセル領域のゲート電極側壁を熱酸化して、酸化シリコン膜15を形成する。その後、ウエハ全面上に、例えば、CVDで窒化シリコン膜を厚さ50nm堆積する。この窒化シリコン膜を異方性エッチングして、フラッシュメモリセルトランジスタのゲート電極側壁上に、サイドウォール絶縁膜16を形成する。なお、このエッチングにより、反射防止膜13も除去される。

【0076】

図7TM及び図7TTを参照する。レジストパターンを用いたエッチングで導電膜12をパターニングして、周辺トランジスタ領域のゲート電極を形成する。レジストパターン、及び各トランジスタのゲート電極をマスクとして、周辺トランジスタ領域に、LDD領域17を形成する不純物注入を行なう。

【0077】

10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、n型不純物が注入される。10V駆動p型トランジスタ領域と、1.8V駆動p型トランジスタ領域とに、p型不純物が注入される。

【0078】

図7UM及び図7UTを参照する。ウエハ全面上に、例えば、CVDで酸化シリコン膜を厚さ100nm堆積する。この酸化シリコン膜を異方性エッチングでエッチングして、フラッシュメモリセルトランジスタのゲート電極側壁上、及び周辺トランジスタのゲート電極側壁上に、サイドウォール絶縁膜18を形成する。なお、このエッチングにより、フラッシュメモリセル領域におけるサイドウォール絶縁膜18の外側部分のトンネル酸化膜8、及び、周辺トランジスタ領域におけるサイドウォール絶縁膜18の外側部分のゲート酸化膜11H及び11Lも除去される。

【0079】

さらに、レジストパターン、各トランジスタのゲート電極、及びサイドウォール絶縁膜18をマスクとして、周辺トランジスタ領域に、ソースドレイン領域19を形成する不純物注入を行なう。10V駆動n型トランジスタ領域と、トリプルウェルを持つ1.8V駆動n型トランジスタ領域と、1.8V駆動n型トランジスタ領域とに、n型不純物が注入される。10V駆動p型トランジスタ領域と、1.8V駆動p型トランジスタ領域とに、p型不純物が注入される。

【0080】

図7VM及び図7VTを参照する。フラッシュメモリセル領域及び周辺トランジスタ領域において、ゲート電極12上、及びソースドレイン領域14、19上に、例えばコバルトシリサイドにより、シリサイド層20を形成する。

【0081】

図7WM及び図7WTを参照する。ウエハ全面上に、例えば、CVDで窒化シリコン膜を厚さ30nm堆積して、エッチングストッパ膜21を形成する。エッチングストッパ膜21上に、例えば、CVDでボロンリンシリケートガラス(BPSG)を厚さ1600nm堆積して、層間絶縁膜22を形成する。

【0082】

図7XM及び図7XTを参照する。レジストパターンを用い層間絶縁膜22及びエッチングストッパ膜21をエッチングして、フラッシュメモリセルトランジスタのソースドレイン領域14上に配置されたシリサイド層20を露出するコンタクトホールや、周辺トランジスタのソースドレイン領域19上に配置されたシリサイド層20を露出するコンタクトホール等を形成する。エッチングストッパ膜21は、コンタクトホール形成のエッチングにおいて、エッチングストッパとして用いられる。

【0083】

コンタクトホールの内面を覆って層間絶縁膜22上に、例えば、チタン膜を厚さ30nm堆積し、チタン膜上に窒化チタン膜を厚さ20nm堆積し、窒化チタン膜上にタングステン膜を厚さ300nm形成する。層間絶縁膜22上の不要なタングステン膜、窒化チタン膜、及びチタン膜をCMPで除去して、導電プラグ23が形成される。

【0084】

層間絶縁膜22上に、例えば、チタン膜を厚さ60nm堆積し、このチタン膜上に窒化チタン膜を厚さ30nm堆積し、この窒化チタン膜上にアルミニウム膜を厚さ360nm堆積し、アルミニウム膜上にチタン膜を厚さ5nm堆積し、このチタン膜上に窒化チタン膜を厚さ70nm形成する。レジストパターンを用いたエッチングにより、この積層金属膜をパターニングして、第1メタル配線24を形成する。

【0085】

図7YMを参照する。さらに、上層の配線構造を形成する。上層の配線構造は、代表としてフラッシュメモリセル領域を示す。第1メタル配線24を覆って層間絶縁膜22上に、例えば、HDPCVDにより酸化シリコンを厚さ720nm堆積して、層間絶縁膜25を形成する。層間絶縁膜25上に、例えば、CVDによりテトラエトキシシラン(TEOS)を厚さ1100nm堆積して、層間絶縁膜26を形成する。層間絶縁膜26の上部を、CMPで平坦化する。

【0086】

その後、レジストパターンを用い層間絶縁膜26及び25をエッチングして、第1メタル配線24を露出するコンタクトホールを形成する。コンタクトホールの内面を覆って層間絶縁膜26上に、例えば、チタン膜を厚さ10nm堆積し、チタン膜上に窒化チタン膜を厚さ7nm堆積し、窒化チタン膜上にタングステン膜を厚さ300nm形成する。層間絶縁膜26上の不要なタングステン膜、窒化チタン膜、及びチタン膜をCMPで除去して、導電プラグ27が形成される。層間絶縁膜26上に、第1メタル配線24と同様にして、第2メタル配線28を形成する。

【0087】

以後、同様な工程を繰り返すことにより、多層配線構造が形成される。図7YMに示す例では、配線として第5メタル配線29までが形成される。第5メタル配線29上に、HDPCVDで形成した酸化シリコンによる層間絶縁膜30が形成され、層間絶縁膜30上に、例えば、CVDにより窒化シリコンが厚さ1000nm堆積されて、カバー絶縁膜31が形成される。このようにして、応用例による半導体装置が形成される。

【0088】

以上説明したように、応用例の半導体装置製造工程では、素子分離溝の角部を丸める熱酸化の前処理として、APM処理、DHF処理、及びHPM処理が順次行われる(図7B1〜図7B3参照)。また、フラッシュメモリセルトランジスタのトンネル酸化膜を形成する熱酸化の前処理として、APM処理、DHF処理、及びHPM処理が順次行われる(図7I1及び図7I2参照)。DHF処理後に行われるHPM処理に、実施例の方法を適用することにより、シリコンの不要なエッチングを抑制することができ、特に、素子分離溝の角部形状の制御性向上が図られる。

【0089】

次に、実施例の処理の適用による、フラッシュメモリセルトランジスタの電気特性改善効果について説明する。上記応用例と同様にして、フラッシュメモリセルトランジスタを作製した。ただし、素子分離溝角部の熱酸化の前処理として行うHPM処理は、比較例の方法を用いた。トンネル酸化膜形成の熱酸化の前処理として行うHPM処理に、実施例の方法を用いた。このように作製されたサンプルを、実施例のフラッシュメモリと呼ぶこととする。

【0090】

各々フラッシュメモリセルトランジスタが多数形成されたウエハを、複数枚作製した。フラッシュメモリは、p型MOSトランジスタを用いて形成した。チャネル注入条件を振って、3種類の異なるチャネル条件のサンプルを作製した。

【0091】

比較例のフラッシュメモリとして、素子分離溝角部の熱酸化の前処理として行うHPM処理、及び、トンネル酸化膜形成の熱酸化の前処理として行うHPM処理の両方とも、比較例の方法を用いたサンプルを作製した。

【0092】

なお、このフラッシュメモリは、以下のように動作する。書き込み時は、例えば、ゲート電圧10V、ソース電圧1.8V、ドレイン電圧0V、及び基板電圧5Vを印加する。これにより、ドレイン端の強電界によりバンド間遷移を起こした電子が、ドレイン近傍の空乏層で加速され、フローティングゲートに注入される。つまり、ドレインから電子がバンドトゥバンドトンネリング(BTBT)によりフローティングゲートに蓄えられる。p型MOSトランジスタであるが、電子がフローティングゲートに蓄積される。消去時は、例えば、ゲート電圧−15.5V、ソース電圧0V、ドレイン電圧0V、及び基板電圧0Vを印加して、フローティングゲートに蓄えられた電子を、基板側に引き抜く。

【0093】

図8は、消去状態におけるフラッシュメモリトランジスタの閾値電圧(イレースVth)とそのばらつきを、実施例及び比較例のフラッシュメモリについて示したグラフである。各プロットは、1枚のウエハを示し、ウエハ内に多数形成されたフラッシュメモリセルトランジスタのイレースVthの、平均値が横軸上に、分散が縦軸上に示されている。実施例の結果が丸で、比較例の結果が菱形でプロットされている。

【0094】

実施例は比較例に比べて、分散が減少している。すなわち、ウエハ内に形成された複数のフラッシュメモリにおける、イレースVthのばらつきが減少している。このような、電気特性のばらつき減少は、実施例の処理により、素子分離溝の角部形状の制御性が向上し、フラッシュメモリごとの角部形状のばらつきが減少したためと解釈することができる。

【0095】

なお、上記実施例の処理では、処理液温度がHPM処理の目標温度に達してから、HClの投入を開始した。HCl投入開始時点は、H2O2の投入開始時点より後であれば、処理液温度がHPM処理の目標温度に達した時点以後に限定されないであろう。なお、HClを投入した時点で、HPM処理の薬液となるが、処理能力を高めるために、HPM処理の目標温度まで処理液温度を上昇させることが好ましい。

【0096】

なお、上記実施例の処理では、H2O2の投入と同時かそれより遅く温水を導入したが、図9に示すように、他の実施例として、温水の導入開始後に、H2O2を投入する方法も可能であろう。この場合、シリコンがエッチングされやすいような高い水温(例えば30℃以上)に達する前に、H2O2の投入を開始することが好ましい。

【0097】

実施例でのH2O2濃度を算出してみると、目標温度に達した時点で2.4wt%、30℃で1.2wt%であった。そこで、濃度の目安を挙げるならば、シリコンがエッチングされやすいような高い水温(例えば30℃以上)に達する前に、例えば、H2O2濃度が1.2wt%以上となっていることが好ましく、2.4wt%以上となっていることがさらに好ましい。

【0098】

なお、上記実施例の処理では、DHF処理後にHPM処理を行った。ここで、DHF処理後にAPM処理を行う場合について考える。APM処理の薬液は、H2O2がHPM処理と共通であり、HPM処理のHClの替わりにNH4OHを用いるものと捉えることができる。

【0099】

比較例のHPM処理について考察したのと同様に、温水を準備してからH2O2とNH4OHとを投入するAPM処理では、温水によりシリコンがエッチングされやすい。APM処理においても、H2O2投入と同時かそれより遅く温水を導入することにより、温水によるシリコンエッチングを抑制できる。

【0100】

NH4OH投入は、例えば、処理液温度がAPM処理の目標温度に到達後開始することができるが、HPM処理でのHCl投入と同様に、H2O2の投入開始時点より後であればよいであろう。また、APM処理の場合も、HPM処理について考察したのと同様に、温水導入後にH2O2を投入する方法も可能であろう。

【0101】

なお、上記応用例の半導体装置製造工程では、素子分離溝角部の熱酸化の前処理、または、トンネル酸化膜形成の熱酸化の前処理として、最初にAPM処理、次にDHF処理、最後にHPF処理を行った。これらの前処理は、例えば、最初にDHF処理を行い、次にAPM処理を行い、最後にHPM処理を行うようにすることもできる。この場合は、DHF処理にAPM処理が続くこととなる。

【0102】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0103】

以上説明した実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程と

を有する半導体装置の製造方法。

(付記2)

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する付記1に記載の半導体装置の製造方法。

(付記3)

前記槽内の処理液の温度が目標温度に到達後、HClまたはNH4OHを導入する付記2に記載の半導体装置の製造方法。

(付記4)

前記目標温度は60℃〜80℃の範囲の温度であり、前記槽内にHClを導入する付記3に記載の半導体装置の製造方法。

(付記5)

前記目標温度は40℃〜80℃の範囲の温度であり、前記槽内にNH4OHを導入する付記3に記載の半導体装置の製造方法。

(付記6)

前記水の温度は、24℃〜26℃の範囲である付記1〜5のいずれか1つに記載の半導体装置の製造方法。

(付記7)

前記水及び前記温水の溶存酸素量は、80ppb以下である付記1〜6のいずれか1つに記載の半導体装置の製造方法。

(付記8)

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板上に酸化シリコン膜を形成し、前記酸化シリコン膜上にマスクパターンを形成し、前記マスクパターンの開口内で前記酸化シリコン膜と前記シリコン基板をエッチングして、前記シリコン基板に素子分離溝を形成する工程を有する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記9)

前記希フッ酸処理する工程は、前記酸化シリコン膜の端部を後退させ、

さらに、

前記酸化シリコン膜の端部を後退させた後、前記素子分離溝の内面に、熱酸化により酸化シリコン膜を成長させる工程を有する付記8に記載の半導体装置の製造方法。

(付記10)

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板に素子分離溝を形成し、前記素子分離溝内に酸化シリコン膜を埋め込み、前記素子分離溝の外側の前記シリコン基板上に酸化シリコン膜を形成する工程を有する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記11)

前記希フッ酸処理する工程の前、前記シリコン基板上に酸化シリコン膜を形成する工程の後、さらに、

前記シリコン基板上の酸化シリコン膜を通して、前記酸化シリコン基板に不純物を注入する工程を有する付記10に記載の半導体装置の製造方法。

(付記12)

前記希フッ酸処理する工程は、前記シリコン基板上の前記酸化シリコン膜を除去し、

さらに、

前記シリコン基板上の前記酸化シリコン膜を除去した後、前記シリコン基板上に、熱酸化により酸化シリコン膜を成長させる工程を有する付記10または11に記載の半導体装置の製造方法。

(付記13)

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、前記槽内に前記水よりも温度の高い温水を導入するとともに、前記槽内の水温が30℃に達する前に、前記槽内にH2O2を導入する工程と

を有する半導体装置の製造方法。

(付記14)

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する付記13に記載の半導体装置の製造方法。

(付記15)

前記水の温度は、24℃〜26℃の範囲である付記13または14に記載の半導体装置の製造方法。

【符号の説明】

【0104】

101 槽

102 ウエハ

103 処理液

104 主供給管

105 HF供給管

106 HCl供給管

107 H2O2供給管

108 NH4OH供給管

109 室温水・温水供給管

110 室温水供給管

111 温水供給管

105a〜111a、111c バルブ

111b 温水ユニット

1 シリコン基板

2 初期酸化膜

3 アイソレーション窒化膜

4 素子分離溝

5 酸化シリコン膜

6 素子分離絶縁膜

7 犠牲酸化膜

8 トンネル酸化膜

9 導電膜(フローティングゲート)

10 ONO膜

11 酸化シリコン膜

11H、11L ゲート酸化膜

12 導電膜(コントロールゲート電極、周辺トランジスタのゲート電極)

13 反射防止膜

14 メモリセルトランジスタのソースドレイン領域

15 酸化シリコン膜

16 サイドウォール絶縁膜

17 周辺トランジスタのLDD領域

18 サイドウォール絶縁膜

19 周辺トランジスタのソースドレイン領域

20 シリサイド層

21 エッチングストッパ膜

22、25、26、30 層間絶縁膜

23、27 導電プラグ

24、28、29 メタル配線

31 カバー絶縁膜

【特許請求の範囲】

【請求項1】

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程と

を有する半導体装置の製造方法。

【請求項2】

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する請求項1に記載の半導体装置の製造方法。

【請求項3】

前記槽内の処理液の温度が目標温度に到達後、HClまたはNH4OHを導入する請求項2に記載の半導体装置の製造方法。

【請求項4】

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板上に酸化シリコン膜を形成し、前記酸化シリコン膜上にマスクパターンを形成し、前記マスクパターンの開口内で前記酸化シリコン膜と前記シリコン基板をエッチングして、前記シリコン基板に素子分離溝を形成する工程を有する請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記希フッ酸処理する工程は、前記酸化シリコン膜の端部を後退させ、

さらに、

前記酸化シリコン膜の端部を後退させた後、前記素子分離溝の内面に、熱酸化により酸化シリコン膜を成長させる工程を有する請求項4に記載の半導体装置の製造方法。

【請求項6】

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板に素子分離溝を形成し、前記素子分離溝内に酸化シリコン膜を埋め込み、前記素子分離溝の外側の前記シリコン基板上に酸化シリコン膜を形成する工程を有する請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記希フッ酸処理する工程は、前記シリコン基板上の前記酸化シリコン膜を除去し、

さらに、

前記シリコン基板上の前記酸化シリコン膜を除去した後、前記シリコン基板上に、熱酸化により酸化シリコン膜を成長させる工程を有する請求項6に記載の半導体装置の製造方法。

【請求項8】

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、前記槽内に前記水よりも温度の高い温水を導入するとともに、前記槽内の水温が30℃に達する前に、前記槽内にH2O2を導入する工程と

を有する半導体装置の製造方法。

【請求項9】

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する請求項8に記載の半導体装置の製造方法。

【請求項1】

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、前記槽内に、H2O2と、前記水よりも温度の高い温水とを導入する工程と

を有する半導体装置の製造方法。

【請求項2】

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する請求項1に記載の半導体装置の製造方法。

【請求項3】

前記槽内の処理液の温度が目標温度に到達後、HClまたはNH4OHを導入する請求項2に記載の半導体装置の製造方法。

【請求項4】

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板上に酸化シリコン膜を形成し、前記酸化シリコン膜上にマスクパターンを形成し、前記マスクパターンの開口内で前記酸化シリコン膜と前記シリコン基板をエッチングして、前記シリコン基板に素子分離溝を形成する工程を有する請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記希フッ酸処理する工程は、前記酸化シリコン膜の端部を後退させ、

さらに、

前記酸化シリコン膜の端部を後退させた後、前記素子分離溝の内面に、熱酸化により酸化シリコン膜を成長させる工程を有する請求項4に記載の半導体装置の製造方法。

【請求項6】

前記希フッ酸処理する工程の前に、さらに、

前記シリコン基板に素子分離溝を形成し、前記素子分離溝内に酸化シリコン膜を埋め込み、前記素子分離溝の外側の前記シリコン基板上に酸化シリコン膜を形成する工程を有する請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記希フッ酸処理する工程は、前記シリコン基板上の前記酸化シリコン膜を除去し、

さらに、

前記シリコン基板上の前記酸化シリコン膜を除去した後、前記シリコン基板上に、熱酸化により酸化シリコン膜を成長させる工程を有する請求項6に記載の半導体装置の製造方法。

【請求項8】

槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、

前記槽内に水を導入して、前記槽内から希フッ酸を排出する工程と、

前記槽内から希フッ酸が排出された後、前記槽内に前記水よりも温度の高い温水を導入するとともに、前記槽内の水温が30℃に達する前に、前記槽内にH2O2を導入する工程と

を有する半導体装置の製造方法。

【請求項9】

さらに、

前記H2O2の導入時点より後に、前記槽内に、HClまたはNH4OHを導入する請求項8に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図5】

【図7−1】

【図7−2】

【図7−3】

【図7−4】

【図7−5】

【図7−6】

【図7−7】

【図7−8】

【図7−9】

【図7−10】

【図7−11】

【図7−12】

【図7−13】

【図7−14】

【図7−15】

【図7−16】

【図7−17】

【図7−18】

【図7−19】

【図7−20】

【図7−21】

【図7−22】

【図7−23】

【図7−24】

【図7−25】

【図7−26】

【図8】

【図9】

【図4】

【図6】

【図2】

【図3】

【図5】

【図7−1】

【図7−2】

【図7−3】

【図7−4】

【図7−5】

【図7−6】

【図7−7】

【図7−8】

【図7−9】

【図7−10】

【図7−11】

【図7−12】

【図7−13】

【図7−14】

【図7−15】

【図7−16】

【図7−17】

【図7−18】

【図7−19】

【図7−20】

【図7−21】

【図7−22】

【図7−23】

【図7−24】

【図7−25】

【図7−26】

【図8】

【図9】

【図4】

【図6】

【公開番号】特開2013−4812(P2013−4812A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−135617(P2011−135617)

【出願日】平成23年6月17日(2011.6.17)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月17日(2011.6.17)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]