半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、IC(Integrated Circuit)チップを積層した3次元ICが注目されている。3次元ICのチップ間(または、ICチップとパッケージ基板の間)は、ICチップを貫通する電極(以下、貫通電極と呼ぶ)によって接続される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−228320号公報

【特許文献2】特開2010−21352号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、ICチップの配線は、ダマシン法により形成される。ダマシン法では、まず層間絶縁膜に配線溝を形成し、この配線溝の内部および層間絶縁膜上に導電材(例えば、Cu)を形成する。その後、層間絶縁膜上の導電材を化学的機械研磨(Chemical Mechanical Polishing)により除去して、配線溝に埋設された埋設配線を形成する。

【0005】

この化学的機械研磨は導電材が除去された後も一定期間継続され、層間絶縁膜の上部が一定量除去される。この時、貫通電極の膜内形成領域(層間絶縁膜内の形成領域)と埋設配線が形成された配線領域の撥水性(または、研磨レート)の違いによって、研磨面に窪みが発生する。この窪みの上に層間絶縁膜を形成し次層の埋設配線を形成すると、埋設配線間のショートが起き易くなるという問題が生じる。

【課題を解決するための手段】

【0006】

上記の問題を解決するために、本製造方法の一観点によれば、半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する半導体装置の製造方法が提供される。

【発明の効果】

【0007】

開示の製造方法によれば、貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが抑制される。

【図面の簡単な説明】

【0008】

【図1】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図2】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図3】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図4】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図5】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図6】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図7】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図8】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図9】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図10】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図11】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図12】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図13】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図14】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図15】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図16】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図17】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

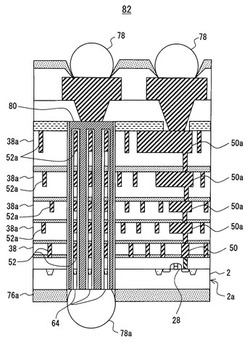

【図18】貫通電極領域にダミーSTI溝を設けない場合の問題を説明する工程断面図である。

【図19】貫通電極領域の上にダミー凹部を設けない場合の問題を説明する工程断面図である。

【図20】貫通電極領域の上にダミー凹部を設けない場合の問題を説明する工程断面図である。

【図21】貫通電極領域の上にダミー凹部を設けない場合の別の問題を説明する工程断面図である。

【図22】貫通電極領域の上にダミー凹部を設けない場合の別の問題を説明する工程断面図である。

【図23】貫通電極領域上のダミー埋設導電部を、配線ルールにしたがって形成した場合の問題を説明する図である。

【図24】凹部およびダミー凹部が設けられた層間絶縁膜の平面図である。

【図25】凹部およびダミー凹部が設けられた層間絶縁膜の平面図である。

【図26】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図27】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図28】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図29】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図30】バリアメタル用研磨剤の研磨レートを説明する図である。

【発明を実施するための形態】

【0009】

以下、図面にしたがって本発明の実施の形態について説明する。但し、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。尚、図面が異なっても対応する部分には同一の符号を付し、その説明を省略する。

【0010】

(実施の形態1)

図1乃至17は、実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【0011】

(1)素子分離絶縁膜および半導体素子の形成工程

(i)STI溝およびダミーSTI溝の形成工程(図1(a)〜図1(c))

まず、ウエハ状の基板(素子未形成基板)2を用意する。基板2は、例えばSi基板又はSOI(Silicon on Insulator)基板である。

【0012】

図1(a)に示しように、基板2には、半導体素子が形成される素子形成領域10と貫通電極が形成される貫通電極領域12とが、予め設定されている。貫通電極領域12には、基板2が除去されて空洞が形成される除去領域24と、除去領域24以外の非除去領域26が設定されている。尚、素子形成領域10は、基板2の表面内の領域である。貫通電極領域12は、基板2の表面から内部に至る領域である。この貫通電極領域12内に、後述する貫通電極の一部が形成される。図1には、水平方向(基板表面に平行な方向)に対する素子形成領域10の設定範囲が矢印で示されている。貫通電極領域12についても、同様である。

【0013】

図1(a)に示すように、基板2の表面に、例えばCVD(Chemical Vapor Deposition)法により厚さ30〜150nmの研磨ストッパー膜(例えば、SiN膜)4を形成する。

【0014】

更に、研磨ストッパー膜4の上に、図1(b)に示すように、レジスト膜(例えば、フォトレジスト膜;以下同様)8を形成する。このレジスト膜8に、例えばフォトリソグラフィ技術を用いて、STI(Shallow Trench Isolation)溝に対応する開口部6aおよびダミーSTI溝に対応する開口部6bを設ける。

【0015】

STI溝は、素子形成領域10に設けられる素子分離絶縁膜用の基板凹部(基板表面の凹部)である。一方、ダミーSTI溝は、貫通電極領域12の非除去領域26に設けられる基板凹部である。

【0016】

次に、レジスト膜8をマスクとし、CF4ガスを反応ガスとして研磨ストッパー膜4および基板2をドライエッチングする。その後、レジスト膜8を、例えばアッシングにより除去する。

【0017】

このドライエッチングにより、図1(c)に示すように、素子形成領域10にSTI溝14を形成する。更に、貫通電極領域12の非除去領域26に、ダミーSTI溝16を形成する。STI溝14およびダミーSTI溝16は、基板2の凹部(基板凹部)である。

【0018】

尚、ダミーSTI溝16は、素子形成領域10に形成してもよい。むしろ、STI溝の形成密度が低い素子形成領域10には、ダミーSTI溝16を形成することが好ましい。

【0019】

(ii)埋設絶縁膜およびダミー埋設絶縁膜の形成工程(図1(d)〜図2(b))

まず、図1(d)に示すように、研磨ストッパー膜4の上、基板凹部14の内部、およびダミー基板凹部16の内部に、例えばHDP(High Density Plasma)−CVD法により絶縁膜18(以下、埋め込み絶縁膜と呼ぶ)を堆積する。埋め込み絶縁膜18は、例えば厚さ300〜1000nmのSiO2膜である。

【0020】

次に、図2(a)に示すように、化学的機械研磨(以下、CMPと呼ぶ)により、研磨ストッパー膜4が露出するまで埋め込み絶縁膜18を研磨して、STI溝14の内部に埋設絶縁膜20を形成すると共に、ダミーSTI溝16の内部にダミー埋設絶縁膜22を形成する。

【0021】

研磨法としては、例えばロータリ式研磨法を用いることができる(後述する他のCMPについても同様)。研磨剤(研磨スラリ)としては、ヒュームドシリカ等の砥粒にph調整剤(例えば、水酸化カリウムや水酸化アンモニウム)を加えたSTI用研磨剤を用いることができる。砥粒は、コロイダルシリカまたは酸化セリウムであっても良い。また、平坦性を向上させるため、研磨剤に界面活性剤を添加しても良い。

【0022】

このようなSTI用研磨剤としては、キャボットマイクロエレクトロニクス社製のSS−25シリーズ(商品名)、DAナノマテリアルズ社製のSTI−2100(商品名)、日立化成社製のHS−8005シリーズ、同じく日立化成社製のHS−9000シリーズ(商品名)などがある。

【0023】

次に、図2(b)に示すように、リン酸等のエッチング液を用いて、研磨ストッパー膜4を除去する。このウェットエッチングにより、基板2の表面が露出する。この時、埋設絶縁膜20とダミー埋設絶縁膜22は、研磨ストッパー膜4の厚さ分、基板表面から突出する。

【0024】

(iii)半導体素子の形成工程(図2(c))

次に、図2(c)に示すように、埋設絶縁膜20で囲われた領域に、MOS(Metal Oxide Semiconductor)トランジスタ等の半導体素子28を形成する。この半導体素子28は、埋設絶縁膜20により他の半導体素子から電気的に分離される。すなわち、埋設絶縁膜20は、素子分離絶縁膜である。

【0025】

一方、図2(c)に示すように、ダミー埋設絶縁膜22で囲われた領域に、半導体素子は形成されない。すなわちダミー埋設絶縁膜22は、素子分離絶縁膜としては機能しない。

【0026】

以上の工程により、半導体素子28を有する素子領域10aと貫通電極が形成される貫通電極領域12とを有する基板2aが形成される。

【0027】

尚、図面が複雑になるので、図2(c)の左端側の埋設絶縁膜20に対応する半導体素子は省略されている。しかし、実際には、この領域にも、半導体素子は形成される(以下の図面でも、同様)。

【0028】

―リーク電流の防止―

図2(b)に示すように、研磨ストッパー膜4を除去した直後の埋設絶縁膜20およびダミー埋設絶縁膜22は、基板2の表面から突出する突出部30a、30bを有している。この突出部は、半導体素子28を形成する工程(例えば、ゲート酸化膜の除去工程)で徐々にエッチングされ、図2(c)に示すように、基板表面と略同じ高さになる。

【0029】

埋め込み絶縁膜18の膜厚や研磨レートは、基板に平行な面内である程度ばらついている。このため、研磨ストッパー膜4上に埋め込み絶縁膜18が残留しないように、研磨ストッパー膜4が露出した後も、一定期間研磨は継続される。

【0030】

図2(a)に示すように、素子形成領域10の研磨ストッパー膜4は、部分的に埋設絶縁膜20で置換される。埋設絶縁膜20を形成する埋め込み絶縁膜18は、研磨ストッパー膜4より研磨され易い。このため、素子形成領域10上の研磨ストッパー膜4は、無垢の研磨ストッパー膜(埋設絶縁膜20で部分的に置換されていない研磨ストッパー膜)より研磨され易い。

【0031】

貫通電極領域12上の研磨ストッパー膜4も、ダミー埋設絶縁膜22で部分的に置換される。ダミー埋設絶縁膜22も埋め込み絶縁膜18で形成されるので、貫通電極領域12上の研磨ストッパー膜4も研磨され易い。

【0032】

このため実施の形態1によれば、素子形成領域10上の研磨ストッパー膜4は、埋設絶縁膜20で部分的に置換されてはいるが、略均一に研磨される。

【0033】

図18は、貫通電極領域12にダミーSTI溝16を設けない場合の問題を説明する工程断面図である。図18(a)〜(d)は、それぞれ図1(d)〜図2(c)に対応している。図18(a)は、STI溝14が形成された基板の2上に、埋め込み絶縁膜18が形成された状態を示している。

【0034】

図18(a)に示すように、貫通電極領域12にダミーSTI溝が設けられないと、素子形成領域10上の研磨ストッパー膜4だけが研磨され易くなる。

【0035】

このため、図18(b)に示すように、素子形成領域10上の研磨ストッパー膜4は、貫通電極領域12上の研磨ストッパー膜4より深く研磨される。この時、埋設絶縁膜20の頂上も研磨される。

【0036】

素子形成領域10上の研磨ストッパー膜4および埋設絶縁膜20の研磨深さは、貫通電極領域12から遠ざかるほど深くなる。したがって、図18(c)に示すように、研磨ストップ膜4の頂上は、貫通電極領域12から遠ざかるほど低くなる。

【0037】

この様な基板2に半導体素子28を形成すると、埋設絶縁膜20は徐々にエッチングされ、貫通電極領域12から離れた埋設絶縁膜20aの頂上は基板表面より低くなる。この様な埋設絶縁膜20aで囲われた領域に半導体素子(例えば、MOSトランジスタ)を形成すると、例えば閾値が低くなりリーク電流が増加する。

【0038】

しかし、実施の形態1によれば、上述したように素子形成領域10上の研磨ストッパー膜4は略均一に研磨されるので、このような問題は生じない。

【0039】

(2)コンタクトプラグの形成工程(図2(d))

次に、図2(d)に示すように、半導体素子28、埋設絶縁膜20、およびダミー埋設絶縁膜22を覆うように、基板2aの表面に例えば厚さ300nm〜1000nmの絶縁膜(以下、下部絶縁膜と呼ぶ)32を堆積する。下部絶縁膜32は、例えばCVD法により形成されるSiO2膜である。

【0040】

この下部絶縁膜32に半導体素子28に達するコンタクトホールを形成し、形成したコンタクトホール内にコンタクトプラグ34を形成する。コンタクトプラグ34は、例えば窒化チタニウム(TiN)膜とタングステン(W)膜を順次コンタクトホール内および下部絶縁膜32上に堆積し、その後下部絶縁膜32上のWを除去することで形成される。

【0041】

(3)多層配線部の形成工程(図2(d)〜図9)

(I)埋設導電部およびダミー埋設導電部の形成工程

(i)層間絶縁膜の形成工程(図2(d)〜図3(a))

まず、図2(d)に示すように、下部絶縁膜32およびコンタクトプラグ34の上に、例えばCVDにより、厚さ10〜200nm程度のエッチングストッパー膜36を形成する。エッチングストッパー膜36は、例えば、炭化シリコン(SiC)膜、炭窒化シリコン(SiCN)膜、窒化シリコン(SiN)膜等である。

【0042】

図3(a)に示すように、このエッチングストッパー膜36の上に、厚さ10nm〜1000nmの層間絶縁膜38を形成する。すなわち、半導体素子28を有する基板2aの上に層間絶縁膜38を形成する。

【0043】

層間絶縁膜38は、例えば、CVD、PE−CVD(Plasma enhanced CVD)、および回転塗布法などにより形成される低誘電率絶縁膜(比誘電率が3.0以下の絶縁膜)である。大部分の低誘電率絶縁膜は、疎水性の絶縁膜(例えば、有機官能基を有する絶縁膜)である。したがって、特に断らない限り、低誘電率絶縁膜とは、疎水性の低誘電率絶縁膜を意味するものとする。また、層間絶縁膜は、特に断らない限り、疎水性の低誘電率絶縁膜で形成されるものとする(実施の形態2においても同じ)。

【0044】

低誘電率絶縁膜は、例えば有機シランまたは有機シロキサンを含む原料から形成することができる。例えば、低誘電率絶縁膜は、メチルシラン、ジメチルシラン、トリメチルシラン、テトラメチルシラン、フェニルシラン、メチルフェニルシラン、エチルシラン、またはジエチルシランを含む原料から形成することができる。

【0045】

または、低誘電率絶縁膜は、シクロヘキシルシラン、テトラエトキシシラン、ジメチルジエトキシシラン、ジメチルジメトキシシラン、ジメチルエトキシシラン、メチルジエトキシシラン、又はトリエトキシシランを含む原料から形成することができる。

【0046】

または、低誘電率絶縁膜は、トリメチルフェノキシシラン、フェノキシシラン、ジエトキシシラン、ジアセトキシメチルシラン、メチルトリエトキシシラン、またはジ−tert−ブチルシランを含む原料から形成することができる。

【0047】

または、低誘電率絶縁膜は、tert−ブチルシラン、1,3,5,7−テトラメチルシクロテトラシロキサン、またはオクタメチルシクロテトラシロキサンを含む原料から形成することができる。

【0048】

または、層間絶縁膜38は、ヘキサメチルシクロトリシロキサン、ヘキサメチルジシロキサン、1,1,2,2−テトラメチルジシロキサン、またはオクタメチルトリシロキサンを含む原料から形成することができる。

【0049】

または、低誘電率絶縁膜は、これらの物質(メチルシラン〜オクタメチルトリシロキサン)を複数含む原料により形成することができる。低誘電率絶縁膜の原料には、誘電率を下げるため、ポロジェンが含有させても良い。

【0050】

回転塗布法に用いる原料としては、JSR社製のLKD(商品名)、ダウケミカル社製のポーラスSilK(商品名)、ULVAC社製または三井化学社製のスケーラブルポーラスシリカなどある。

【0051】

CVD法に用いる原料としては、AMAT社製のBlack Diamond(商品名)、ASM社製のAurora(商品名)、ノベラス社製のCORAL(商品名)などがある。

【0052】

(ii)凹部(配線溝)およびダミー凹部の形成工程(図3(a)〜図4(b))

まず、図3(a)に示すように、層間絶縁膜38の上に、厚さ10nm〜150nmのハードマスク用の絶縁膜(例えば、SiO2)膜40を堆積する。ハードマスク用絶縁膜40としては、炭化シリコン(SiC)膜、炭酸化シリコン(SiOC)膜、炭窒化シリコン(SiCN)膜、窒化シリコン(SiN)膜などの絶縁膜または金属膜を用いてよい(以下、同様)。これらの絶縁膜は、例えば、CVD、PE−CVD、またはPVD(Physical Vapor Deposition)により形成される。

【0053】

図3(b)に示すように、ハードマスク用絶縁膜40の上に、配線溝用凹部に対応する開口部45aおよびダミー凹部に対応する開口部45bを有するレジスト膜8aを形成する。

【0054】

次に、図4(a)に示すように、レジスト膜8aをマスクとして、絶縁膜40をエッチングし、ハードマスク42を形成する。

【0055】

このハードマスク42を用いて、図4(b)に示すように、層間絶縁膜38およびエッチングストッパー膜36をドライエッチングして、素子領域10aの上の層間絶縁膜39aに配線溝用の凹部44およびダミー凹部46を形成する。一方、貫通電極領域12の上の層間絶縁膜39bには、このドライエッチングによりダミー凹部46を形成する。

【0056】

ハードマスク42および層間絶縁膜38は、例えばCF4ガスを反応ガスとしてドライエッチングされる。エッチングストッパー膜36は、例えばCF4ガスとO2ガスの混合ガスを反応ガスとしてドライエッチングされる。その後、レジスト膜8aおよびハードマスク42を除去する。レジスト膜8aは、例えばアッシングにより除去する。

【0057】

後述するように、凹部(配線溝)44には、配線が形成される。一方、素子領域10a上のダミー凹部46には、素子領域10a上の研磨むらを抑制するため、ダミー埋設導電部が形成される。この素子領域10a上のダミー埋設導電部の形成位置は、所定の配線ルールに従って決定される。

【0058】

一方、貫通電極領域12上のダミー凹部46は、図4(b)に示すように、貫通電極領域内の非除去領域26の上に形成される。

【0059】

尚、図4(b)に示す例では、ダミー凹部46は、素子領域10a上の層間絶縁膜39aおよび貫通電極領域12層間絶縁膜39bの両方に形成される。但し、配線密度が高く研磨むらが生じ難い場合等には、素子領域10aの上には、ダミー凹部46を形成しなくてもよい。

【0060】

このように、ダミー凹部46は、素子領域10aと貫通電極領域12のうち少なくても貫通電極領域12の上の層間絶縁膜39bに形成される。

【0061】

(iii)埋設導電部(配線)およびダミー埋設導電部の埋め込み工程(図5)

まず、バリアメタル(図示せず)およびシード膜(図示せず)を、層間絶縁膜38の上、凹部44の内壁、およびダミー凹部46の内壁に順次堆積する。但し、層間絶縁膜38上には、ハードマスク42を介して、バリアメタルおよびシード膜を堆積する。バリアメタルは、例えば厚さ1nm〜30nmの窒化タンタル(TaN)膜である。

【0062】

バリアメタルおよびシード膜は、例えばスパッタ法によって堆積される(以下、同様)。尚、バリアメタルは、導電材の拡散防止のために設けられる。

【0063】

バリアメタルとしては、Ti、Ni、Co、Zr、Cr、Pd、Mn、Ag、Al、Sn、Ta、Re、W、Pt、V、Ru、Auのいずれか1つの金属又は複数の金属の混合物(合金を含む)またはその窒化物が好ましい。シード膜は、例えば、厚さ1nm〜100nmの銅膜である。

【0064】

このシード膜を給電部として、図5(a)に示すように、層間絶縁膜38の上、凹部44の内部、およびダミー凹部46の内部に、例えば厚さ1.2μm程度の導電材48を形成する。但し、層間絶縁膜38の上には、ハードマスク42、バリアメタル、及びシード膜を介して、導電材48を形成する。また、凹部44の内部およびダミー凹部46の内部には、バリアメタル及びシード膜を介して導電材48を形成する。尚、「層間絶縁膜38の上」とは、層間絶縁膜38の外表面上のことである。以下の説明でも、同様である。

【0065】

導電材48は、例えば銅(Cu)である。或いは、導電材48は、Ti、Ni、Co、Zr、Cr、Pd、Mn、Ag、Al、Sn、Ta、Re、W、Pt、V、Ru、Au、Si、Ge、C、S、O、Cl、P、B、H、Hf、F、Nのうち何れか1つ又は複数の元素がCuに混入したもの(合金を含む)でも良い。これらの元素は、シード膜に混入させてもよい。

【0066】

次に、導電材48、バリアメタル、ハードマスク42、および層間絶縁膜38の上部を、例えばCMPで一定量研磨して、図5(b)に示すように、凹部44の内部に埋設導電部(導電部)50を形成する。また、この研磨により、ダミー埋設導電部52をダミー凹部46の内部に形成する。この研磨では層間絶縁膜38も研磨され、所定の厚さ(例えば、20nm〜100nm)を有する埋設導電部50が形成される。尚、ハードマスク42は、バリアメタルを堆積する前、例えば研磨により除去してもよい。

【0067】

以上の研磨工程では、2種類の研磨剤が用いられる。最初に用いる研磨剤は、導電材48を研磨する研磨剤である。2番目に用いる研磨剤は、バリアメタル、ハードマスク42、(凹部44およびダミー凹部46内部の)導電材48、および層間絶縁膜38の上部を研磨する研磨剤である。

【0068】

最初に用いる研磨剤としては、例えば導電材を選択的に研磨する導電材用研磨剤を用いることができる。導電材用研磨剤は、例えば、コロイダルシリカ等の砥粒に加工液を加えることで、導電材(例えば、Cu)に対する研磨レートを大きくした研磨剤である。更に、導電材用研磨剤は、砥粒サイズ(例えば、50nm程度)を小さくすることで、バリアメタル等に対する研磨レートを小さくした研磨剤である。この様に加工水と小サイズ砥粒を組み合わせることで、導電材の選択的研磨が実現される。因みに、STI用研磨剤の砥粒の粒径は、200nm程度である。

【0069】

導電材用研磨剤の砥粒としては、コロイダルシリカ以外にも、フュームドシリカ、セリウム、アルミナ、炭化珪素などの粒子を用いることができる。加工液は、例えば、分散剤、酸化剤、防食剤、キレート剤などを混合した薬液である。酸化剤は、例えば過硫酸アンモニウムや過酸化水素水である。防食剤は、例えばベンゾトリアゾール(BTA)である。キレート剤は、例えばクエン酸、リンゴ酸、キナルジン酸、オレイン酸である。

【0070】

このような導電材用研磨剤では、酸化剤によって導電材(例えば、Cu)が酸化され、水溶性の物質(例えば、Cu錯体)に変化する。この物質が研磨液に溶けだすことで、導電材が高いレートで研磨される。

【0071】

導電材用研磨剤としては、日立化成社製のHS−H635(商品名)、日立化成社製のHS−C930(商品名)、JSR社製のCMS74シリーズ(商品名)、JSR社製のCMS75シリーズ等がある。

【0072】

2番目の研磨剤は、バリアメタル等(バリアメタル、ハードマスク用絶縁膜40、および導電材48)に対する研磨レートが、低誘電率絶縁膜(層間絶縁膜38)に対する研磨レートより大きい研磨剤である。更に、2番目の研磨剤は、バリアメタル、ハードマスク用絶縁膜40、および導電材48それぞれに対して、同程度の研磨レートを有する研磨剤である。

【0073】

2番目の研磨剤としては、例えば、STI用研磨剤に加工液を少量加えた研磨剤(以下、バリアメタル用研磨剤と呼ぶ)を用いることができる。バリアメタル用研磨剤に含まれる加工水は、導電材用研磨剤の加工水と同様、導電材(例えば、Cu)に作用して、導電材に対する研磨レートを高くする薬液である。

【0074】

ここで、バリアメタル用研磨剤の研磨レートに関して少し説明する。

【0075】

まず、バリアメタル用研磨剤のバリアメタル等に対する研磨レートと低誘電率絶縁膜に対する研磨レートを比較する。

【0076】

バリアメタル用研磨剤は、STI用研磨剤と同様、薬剤(ph剤、酸化剤等)が添加された水溶液(例えば、加工水)中に砥粒を分散させたスラリである。したがって、バリアメタル用研磨剤は、疎水性の低誘電率絶縁膜によってはじかれる。一方、バリアメタル用研磨剤は、親水性のハードマスク用絶縁膜40には濡れ易い。このため、バリアメタル用研磨剤のハードマスク用絶縁膜40に対する研磨レートは、(バリアメタル用研磨剤の)低誘電率絶縁膜に対する研磨レートより大きい。バリアメタルおよび導電材に対する研磨レートも同様に、低誘電率絶縁膜に対する研磨レートより大きい。

【0077】

すなわち、バリメタル研磨剤は、バリアメタル等(バリアメタル、ハードマスク用絶縁膜40、および導電材48)に対する研磨レートが、低誘電率絶縁膜(層間絶縁膜38)に対する研磨レートより大きい研磨剤である。

【0078】

次に、バリアメタル、ハードマスク用絶縁膜40、および導電材48それぞれに対する研磨レートを比較する。図30は、バリアメタル用研磨剤の研磨レートを説明する図である。横軸は、研磨対象物である。縦軸は、研磨レートである。

【0079】

バリアメタル用研磨剤の砥粒サイズは、導電材用研磨剤の砥粒サイズより大きい(例えば、バリアメタル用研磨剤の砥粒サイズは、STI用研磨剤と同程度に大きい。)。このため、バリアメタル用研磨剤の対ハードマスク研磨レート100(ハードマスク用絶縁膜に対する研磨レート)は、導電材用研磨剤の対ハードマスク研磨レート102より大きい。

【0080】

バリアメタル用研磨剤に添加される加工水は、導電材用研磨剤に添加される加工水より低濃度である。したがって、バリアメタル用研磨剤の対導電材研磨レート104は、導電材用研磨剤の対導電材用研磨レート106より小さい。

【0081】

ところで、導電材用研磨剤の対導電材研磨レート106は、導電材用研磨剤の対ハードマスク研磨レート102より大きい。したがって、導電材用研磨剤の研磨レート102,106に対する大小関係108を考慮すれば容易に推定されるように、バリアメタル用研磨剤は、ハードマスク(すなわち、ハードマスク用絶縁膜40)および導電材48それぞれに対して、同程度の研磨レート100,104を有している。

【0082】

ところで、バリアメタル用研磨剤に添加される加工水は、バリアメタルにも作用する。この加工水の作用により、対バリアメタル研磨レートは、対ハードマスク研磨レートと同程度になる。したがって、バリアメタル用研磨剤は、バリアメタルに対しても、導電材48と同程度の研磨レートを有している。但し、対バリアメタル研磨レートは、対ハードマスク研磨レートより大きくてもよい。バリアメタルは極めて薄いので、対バリアメタル研磨レートが対ハードマスク研磨レートより大きくても、研磨面は平坦に保たれる。

【0083】

このようなバリアメタル用研磨剤としては、日立化成社製のT605−8(商品名)、JSR社製のCMS8201/8252(商品名)、JSR社製のCMS8501/8552(商品名)などがある。

【0084】

尚、バリアメタル用研磨剤に改質剤(または界面活性剤)を添加することで、低誘電率絶縁膜を親水性することが提案されている。しかし、このような研磨剤を用いると低誘電率絶縁膜の吸水性が高まり、その結果、低誘電率絶縁膜の誘電率が高くなってしまう。したがって、バリアメタル用研磨剤に改質剤等を添加した研磨剤は、2番目の研磨剤としては好ましくない。

【0085】

(II)「埋設導電部およびダミー埋設導電部の形成工程」の繰り返し(図6〜図9)

(I)で説明した「埋設導電部およびダミー埋設導電部の形成工程」(以下、埋設導電部の形成工程と呼ぶ)と略同じ工程を繰り返すことで、図9に示す多層配線部54を形成する。

【0086】

1層目の配線層53aは、(I)の工程で形成される配線層である。一方、2層目以降の配線層53は、(I)の工程とは異なり、直前に形成した埋設導電部(配線)に接続するコンタクトプラグを形成した後、埋設導電部およびダミー埋設導電部を形成することで製造される。これ以外の点では、1層目の配線層53aの形成工程と2層目以降の配線層53の形成工程は略同じである。

【0087】

以下、1層目の埋設導電部53aの形成工程と2層目以降の埋設導電部53の形成工程の相違点について説明する。尚、1層目の埋設導電部53aの形成工程と共通する部分については、説明を省略する。

【0088】

2層目の埋設導電部53bの形成工程では、図6(a)に示すように、1層目の層間絶縁膜38の上に、エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用絶縁膜40aを、1層目の埋設導電部53aの形成工程と略同じ手順で形成する。エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用絶縁膜40aの組成およびサイズは、1層目のものと略同じである。但し膜厚は、1層目のものよりも厚くしてもよい。

【0089】

次に、ハードマスク用絶縁膜40aの上に、コンタクトプラグに対応する開口部56を有するレジスト膜8bを形成する。このコンタクトプラグは、一層目の埋設導電部(配線)50に接続するプラグである。

【0090】

このレジスト膜8bをマスクとして、図6(b)に示すように絶縁膜40aをドライエッチングし、ハードマスク42aを形成する。このハードマスク42aを用いて、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aを順次ドライエッチングし、1層目の配線50に達するコンタクトホール58を形成する。その後、レジスト8bをアッシングにより除去する。

【0091】

次に、図7(a)に示すように、ハードマスク42aの上に、2層目の凹部(配線溝)に対応する開口部45cおよび2層目のダミー凹部に対応する開口部45dを有するレジスト膜8cを形成する。

【0092】

このレジスト膜8cをマスクとして、ハードマスク42aをドライエッチングして、ハードマスク42aに新たな開口部を形成する。

【0093】

この新たな開口部を有するハードマスク42aを用い、図7(b)に示すように、2層目の層間絶縁膜38aをドライエッチングして、素子領域10a上の層間絶縁膜39cに凹部(配線溝)44aおよびダミー凹部46aを形成する。更に、このドライエッチングにより、(貫通電極領域12内の)非除去領域26上の層間絶縁膜39dに、ダミー凹部46aが形成される。その後、ハードマスク42a上に残っているレジスト膜8cを、アッシングにより除去する。

【0094】

1層目の凹部(配線溝)44とは異なり、2層目の凹部(配線溝)44aは、層間絶縁膜38aを貫通せずに、層間絶縁膜38aの内部に留まっている。ダミー凹部46aについても、同様である。コンタクトホール58の上部は、上記ドライエッチングにより、凹部(配線溝)44aに吸収される。一方、コンタクトホール58aの下部により、凹部(配線溝)44aは1層目の埋設導電部(配線)50に連結される。

【0095】

図7(b)に示す例では、ダミー凹部46aは、素子領域10aの上の層間絶縁膜39cおよび貫通電極領域12上の層間絶縁膜39dの両方に形成される。しかし、凹部(配線溝)44aの密度が高い場合等には、1層目の配線層53aと同様、素子領域10aの上にダミー凹部46aは形成しなくてもよい。

【0096】

次に、層間絶縁膜38aの上、凹部44aの内部、コンタクトホール58aの内部、およびダミー凹部46aの内部に、導電材48aを形成する(図8(a)参照)。但し、層間絶縁膜38aの上には、ハードマスク42aを介して導電材48aを形成する。

【0097】

その後、導電材48aを研磨し、図8(b)にように、2層目の埋設導電部50aおよびダミー埋設導電部52aを形成する。導電材48aの形成工程および研磨工程は、1層目の埋設導電部の形成工程および研磨工程と略同じである。

【0098】

以上の工程により、埋設導電部50a、ダミー埋設導電部52a、およびコンタクトプラグ34aを有する2層目の配線層53bが形成される。

【0099】

3層目以降の配線層53も、2層目の配線層53bと略同じ工程により形成される。このような工程により、複数の配線層53,53aを有する多層配線部54が形成される。

【0100】

―配線間の短絡防止―

図19及び20は、貫通電極領域12の上にダミー凹部46を設けない場合の問題を説明する工程断面図である。

【0101】

図19(a)に示すように、貫通電極領域12の上にダミー凹部を設けずに、層間絶縁膜38の上に導電材48を形成した場合を考える。尚、図19(a)では、層間絶縁膜38上のハードマスクは省略されている。

【0102】

この状態で導電材48が研磨され層間絶縁膜38の表面が露出すると、図19(b)に示すように、貫通電極領域12の上には、親水性の導電材(例えば、Cu)を有さない層間絶縁膜(以下、貫通領域絶縁膜と呼ぶ)39eが出現する。一方、素子領域10aの上には、導電材(埋設導電部50およびダミー埋設導電部52)を有する層間絶縁膜39f(以下、素子領域絶縁膜と呼ぶ)が出現する。

【0103】

素子領域絶縁膜39fの表面には、親水性の導電材が表面に露出している。したがって、素子領域絶縁膜39fは、水に濡れ易い。一方は、貫通領域絶縁膜39eは、疎水性の低誘電率絶縁膜で膜全体が形成されているので、水をはじき易い。

【0104】

このため、導電材48の研磨が終了し層間絶縁膜38の研磨が開始すると、貫通領域絶縁膜39eの周囲に、研磨剤の淀みが発生する。その結果、貫通領域絶縁膜39eの周囲で研磨が促進され、貫通領域絶縁膜39eの周りに窪み60が生成される。

【0105】

その後、図20(a)に示すように、窪み60の上に次の層間絶縁膜38cを形成すると、窪み60が次の層間絶縁膜38cに転写されて、別の窪み60aが発生する。

【0106】

この窪み60aを有する層間絶縁膜38cに埋設導電部(配線)50,50bを形成すると、図20(b)に示すように、一部の導電材48bが研磨されずに、窪み60aに残留する。

【0107】

この窪み60aに配線50b(埋設導電部)が形成されると、残留した導電材48bによって配線50bが接続されショートする。

【0108】

一方、実施の形態1では、貫通電極領域12上の層間絶縁膜38にも、親水性の導電材(ダミー埋設部52)が形成される。したがって、実施の形態1によれば、研磨剤の淀みが発生しないので、配線同士がショートすることはない。

【0109】

図21及び22は、貫通電極領域12の上にダミー凹部46を設けない場合の別の問題を説明する工程断面図である。

【0110】

図19及び20を参照して説明した問題は、層間絶縁膜が疎水性の低誘電率絶縁膜で形成されている場合に生じる問題である。図21及び22では、層間絶縁膜が親水性の絶縁膜で形成されている場合に生じる問題を説明する。尚、親水性の絶縁膜としては、有機官能基を有さない多孔質無機二酸化ケイ素(SiO2)等がある。

【0111】

図21(a)に示すように、貫通電極領域12の上にダミー凹部を設けずに、層間絶縁膜38の上に導電材48を形成した場合を考える。尚、図21(a)でも、層間絶縁膜38上のハードマスクは省略されている。

【0112】

導電材48の研磨が終了し層間絶縁膜38の研磨が開始すると、貫通電極領域12の上に、導電材(ダミー埋設導電部52)を有さない貫通領域絶縁膜39eが出現する。一方、素子領域10aの上には、導電材(埋設導電部50およびダミー埋設導電部52)を有する素子領域絶縁膜39fが出現する(図21(b)参照)。

【0113】

図21及び22の場合、層間絶縁膜38も親水性の絶縁膜で形成されているので、貫通領域絶縁膜39eおよび素子領域絶縁膜39fは共に、水をはじかない。このため、図19及び20の場合とは異なり、研磨剤の淀みは発生しない。

【0114】

しかし、図21(b)に示すように、層間絶縁膜38が研磨されると、素子領域絶縁膜39fに弧状の窪み60bが発生する。

【0115】

この窪み60bの上に次の層間絶縁膜38dを形成すると、図22(a)に示すように、次の層間絶縁膜38dにも窪み60cが発生する。このような層間絶縁膜38dに埋設導電部(配線)50を形成すると、窪み60cの底に残留した導電材48cにより、配線間がショートがする(図22(b)参照)。

【0116】

しかし、この場合も、貫通電極領域12上の絶縁膜38にダミー埋設導電部を形成することで、窪み60bの発生が抑制され、配線間のショートも起きない。したがって、層間絶縁膜38は親水性であってもよい。

【0117】

親水性の層間絶縁膜に窪み60bが発生することは、実験により確認されている。このような窪み60bは、配線(埋設導電部)を形成する導電材が層間絶縁膜より柔らかいために発生すると考えられる。

【0118】

Cu等の導電材は、層間絶縁膜より柔らかい。このため研磨圧力に対して導電材が発生する反発力(反作用)は、層間絶縁膜が発生する反発力より小さい。したがって、層間絶縁膜に導電材が埋設されていると、層間絶縁膜に加わる研磨圧力が増加し、層間絶縁膜が研磨され易くなる。その結果、窪み60bが発生する。

【0119】

(4)貫通電極の形成工程(図10〜図16)

まず、図10に示すように、多層配線部54の上にハードマスク用絶縁膜40bを形成する。ハードマスク用絶縁膜40bは、多層配線部54の形成に用いた絶縁膜40,40aと略同じものである。

【0120】

このハードマスク用絶縁膜40bの上に、貫通電極領域12の上に開口部6cを有するレジスト膜8dを形成する。このレジスト膜8dをマスクとして、絶縁膜40bをドライエッチングして、貫通電極領域12の上で開口するハードマスク42bを形成する。

【0121】

このハードマスク42bを用いて、貫通電極領域12の上の層間絶縁膜38,38a、エッチングストッパー膜36,36a、下部絶縁膜32、および貫通電極領域(基板2の一部)12をドライエッチングして、図11に示すように、基板2の内部に至る貫通電極ホール(孔)62を形成する。

【0122】

ハードマスク42b、層間絶縁膜38,38a、下部絶縁膜32、および基板2(貫通電極領域12)は、例えばCF4ガスを反応ガスとするドライエッチングにより除去する。エッチングストッパー膜36,36aは、例えばCF4ガスとO2ガスの混合ガスを反応ガスとするドライエッチングにより除去する。その後、レジスト膜8dを、アッシングにより除去する。

【0123】

ダミー埋設導電部52,52aを形成する導電材は、このようなドライエッチングでは除去されない。このため貫通ホール62の内部には、図11に示すように、ダミー埋設導電部52aの下側にピラー(支柱)状のエッチング残部64が形成される。

【0124】

次に、図12に示すように、貫通ホール62の内壁、エッチング残部64、及びハードマスク42bを覆う絶縁膜66を、例えばCVDにより堆積する。絶縁膜66は、例えば厚さ100nm〜200nmのSiO2膜である。絶縁膜66は、例えばSiC膜、SiCN膜、またはSiN膜であってもよい。

【0125】

この絶縁膜66の上に、厚さ50〜300nmのバリアメタル、厚さ1nm〜100nmのシード膜、厚さ10μm程度の導電材(第2導電材)を順次形成して、貫通ホール62を導電材で埋め込む。その後、図13に示すように、導電材、ハードマスク42b上の絶縁膜66、およびハードマスク42bの上部を研磨して、貫通ホール62内に埋設された導電材68を形成する。

【0126】

バリアメタル、シード膜、および導電材の組成および形成方法は、埋設導電部50およびダミー埋設導電部52と略同じである。また、導電材の研磨法も、埋設導電部50およびダミー埋設導電部52と略同じである。但し、予めウェットエッチングによりハードマスク42b上の導電材を1μm程度まで薄くしてから、導電材を研磨する。

【0127】

次に、図14に示すように、ハードマスク42bの上に、貫通ホール内の導電材68および最上層の埋設導電部50a(配線)の上で開口する上部絶縁膜70を形成する。

【0128】

上部絶縁膜70の開口部には、貫通ホール内の導電材68および埋設導電部50a(配線)それぞれに接続する電極72を形成する。電極72は、例えばアルミニウム(Al)電極である。電極72と上部絶縁膜70間には、バリアメタル(図示せず)が形成される。

【0129】

次に、図15に示すように、上部絶縁膜70の上に、電極72の上で開口する最上部絶縁膜74を形成する。最上部絶縁膜74と上部絶縁膜70の間には、SiN膜(図示せず)等を形成してもよい。

【0130】

上部絶縁膜70および最上部絶縁膜74は、例えばCVDおよびフォトリソグラフィ技術により形成される。上部絶縁膜70および最上部絶縁膜74は、例えばSiO2である。

【0131】

図15に示すように、最上部絶縁膜74の上には、電極72の上で開口するポリイミド膜76を形成する。その後、このポリイミド膜76の開口部に、電極72に接続する半田バンプ78を形成する。

【0132】

次に、基板2の裏面(素子領域10aの反対側の基板面)を、貫通ホール内に埋設された導電材68が露出するまで、例えば機械的に研磨する。これにより、図16に示すように、基板2および多層配線部54を貫通する貫通電極80が形成される。

【0133】

尚、貫通電極80は貫通ホールの内壁に形成された絶縁膜66により、基板2から絶縁される。

【0134】

(5)裏面側バンプの形成工程等(図17)

その後、図17に示すように、基板2の裏面に、貫通電極80の下側で開口するポリイミド膜76aを形成する。このポリイミド膜76aの開口部に、貫通電極80に接続する半田バンプ78aを形成する。最後に、半導体素子28および多層配線部54などが形成された基板2を分割して、半導体装置82を完成する。

【0135】

この半導体装置82は、図17に示すように、半導体素子28を有する基板2aと、基板2a上に積層された複数の層間絶縁膜38,38aとを有している。半導体装置82は、更に、複数の層間絶縁膜38,38aそれぞれに埋設された複数の埋設導電部50,50aと、基板2aおよび複数の層間絶縁膜38,38aを貫通する貫通電極80とを有している。

【0136】

そして、貫通電極80は、基板2aの一部、複数の層間絶縁膜38,38a、および複数の埋設導電部50,50aに対応するダミー埋設導電部52,52aを順次積層して得られる柱状の積層部(エッチング残部64)を有している。

【0137】

尚、埋設導電部50,50aおよび埋設導電部50,50aの対応するダミー埋設導電部は同じ工程で形成されるで、略同じ厚さ(したがって、所定の厚さ)を有している。ここで、半導体装置82は、例えば、半田バンプ78aにより裏面側でパッケージ基板に搭載される。一方、半導体装置82の表面側には、別の半導体装置(ICチップ;図示せず)が積層される。

【0138】

この時、半導体装置82の貫通電極80は、表面側の別の半導体装置の電極に接続される。この別の半導体装置には、貫通電極80を介して、パッケージ基板から電源電圧や信号が供給される。或いは、別の半導体装置の信号が、半導体装置82の貫通電極80を介して、パッケージ基板に出力される。

【0139】

貫通電極80を有する半導体装置を複数積層すれば、3層以上のスタックドICを形成することができる。この場合、半導体装置間の信号の送受信は、貫通電極80を介して行われる。

【0140】

―貫通電極の貫通性―

上述したように、素子領域10a上のダミー埋設導電部52の位置は、配線層53,53aごとに定められる配線ルールによって決定される。このため、ダミー埋設導電部52,52aは、配線層ごとに異なった位置(基板2に平行な面内の位置)に形成される。

【0141】

図23は、貫通電極領域12上のダミー埋設導電部52,52aを、配線ルールにしたがって形成した場合の問題を説明する図である。この場合、ダミー埋設導電部52,52aは配線層53,53aごとに異なった位置に形成される。このため、図23に示すように、ピラー状のエッチング残部64aが、貫通ホール62内に無秩序に林立する。

【0142】

このため、基板2に近づくほど貫通ホール62の開口率が小さくなり、最悪の場合、貫通ホール62がエッチング残部64aによって塞がれてしまう。このような貫通ホール62に導電材を形成しても、貫通性の良い貫通電極(すなわち、低抵抗の貫通電極)は形成できない。

【0143】

一方、実施の形態1では、予め設定された非除去領域26の上にダミー埋設導電部52,52aが形成されるので、図16に示すように、貫通電極80の貫通性は良好である。したがって、貫通電極80の抵抗は低くなる。

【0144】

ダミー埋設導電部52,52aは、貫通電極領域12内の非除去領域26(図7(b)参照)の上に形成される。したがって、貫通電極領域12内における非除去領域26の割合が小さいほど、貫通性は良くなる。

【0145】

例えば、非除去領域26の横断面(基板2に平行な断面)の総面積は、貫通電極領域12の横断面の面積の0.4倍以下が好ましい。尚、「非除去領域26の横断面の総面積」とは、全ての非除去領域26の横断面の面積の和を意味する。

【0146】

但し、非除去領域26の割合が小さくなり過ぎると、素子領域10a上で層間絶縁膜38,38aが窪んで配線間のショートが起きやすくなる。したがって、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.1倍以上が好ましい。

【0147】

すなわち、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.4倍以下0.1倍以上が好ましい。更に好ましくは、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.3倍以下0.2倍以上である。

【0148】

同様に、貫通電極80の積層部(エッチング残部64)の横断面の総面積は、貫通電極80の横断面の面積の0.4倍以下0.1倍以上が好ましい。更に好ましくは、貫通電極80の積層部(エッチング残部64)の横断面の総面積は、貫通電極80の横断面の面積の0.3倍以下0.2倍以上である。

【0149】

貫通電極領域12の上に形成されるダミー凹部の平面形状(基板2に平行な断面の形状)およびサイズが配線層ごとに異なると、最もサイズの大きなダミー凹部または最も細長いダミー凹部によって貫通電極ホール62の開口率が制限される。したがって、貫通電極領域12上のダミー凹部52,52aの平面形状は、所定の形状および所定サイズ(例えば、非除去領域26の平面形状およびサイズ)を有することが好ましい。この場合、積層部64内のダミー埋設導電部の基板に平行な断面も、所定の形状および所定のサイズを有する。

【0150】

尚、ダミー基板凹部内のダミー埋設絶縁膜22(図2(c)参照)は、例えば基板用のドライエッチングで除去することができる。しかし、ダミー埋設絶縁膜22と基板2のエッチングレートが異なるので、ダミー埋設絶縁膜22(またはその一部)が除去領域24(図1(a)参照)に形成されると、貫通ホール62の形状に乱れが生じる。

【0151】

したがって、「(1)素子分離絶縁膜および半導体素子の形成工程」で説明したように、ダミー埋設絶縁膜22も非除去領域26に形成することが好ましい。但し、基板2とダミー埋設絶縁膜22のエッチングレートの差が小さい場合等には、ダミー埋設絶縁膜22(またはその一部)を除去領域24に形成してもよい。

【0152】

―ダミー凹部の平面形状―

図24及び25は、凹部44およびダミー凹部46が設けられた層間絶縁膜38,38aの平面図である。図24及び25には、層間絶縁膜38,38aの下方に位置する貫通電極領域12が破線で示されている。

【0153】

図24(a)に示す例では、ダミー凹部46の平面形状は正方形である。したがって、ダミー凹部46は、四角柱状の孔(ホール)である。図24(a)に示す例では、このようなダミー凹部46が、格子状に配列されている。一方、凹部44は、縦長の配線溝である。

【0154】

図24(b)に示す例では、四角柱状のダミー凹部46の列が、上下スライドしている。

【0155】

図25(a)に示す例では、貫通電極領域12上のダミー凹部46の平面形状は、長方形である。したがって、貫通電極領域12上のダミー凹部46は溝である。このような場合、エッチング残部64の横断面が大きくなり、エッチング残部64の強度は大きくなる。

【0156】

図25(b)に示す例では、貫通電極領域12上のダミー凹部46は45°回転している。

【0157】

この様に、ダミー凹部46の形状および配置には、種々のバリエーションが存在する。一方、ダミー凹部46の1辺は、CMPの特性等を考慮すると、0.1μm〜1.0μm程度が好ましい(ダミー凹部46の平面形状が矩形の場合)。

【0158】

実施の形態1では、貫通電極領域12上のダミー凹部46は、非除去領域26(図7(b)参照)の上に設けられる。しかし、貫通電極領域12上のダミー凹部46が少数の場合等には、非除去領域26を設定せずに、ダミー凹部46を貫通電極領域12内の任意の位置に形成してもよい。

【0159】

(実施の形態2)

図26乃至29は、実施の形態2の半導体装置82aの製造方法を説明する工程断面図である。

【0160】

実施の形態1では、図7に示すようにコンタクトホール58の形成後、凹部44a(配線溝)とダミー凹部46aを同時に形成する。一方、実施の形態2では、コンタクトホール58aと同時にダミー凹部46aを形成し、その後凹部44a(配線溝)を形成する。その他の工程は、実施の形態1の製造方法と略同じである。したがって、実施の形態1と共通する部分については、説明を省略する。

【0161】

まず、図26(a)に示すように、実施の形態1の工程にしたがって、1層目の配線層53aまで形成する。更に、実施の形態1の工程にしたがって、1層目の配線層53aの上に、エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用の絶縁膜40aを形成する。

【0162】

次に、ハードマスク用絶縁膜40aの上に、2層目のダミー凹部に対応する開口部45dとコンタクトプラグに対応する開口部56を有するレジスト膜8eを形成する。このコンタクトプラグは、一層目の配線50に接続するプラグである。

【0163】

このレジスト膜8eをマスクとして、図26(b)に示すように絶縁膜40aをドライエッチングし、ハードマスク42cを形成する。次に、ハードマスク42cを用いて、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aをドライエッチングして、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aを貫通する、ダミー凹部46bおよびコンタクトホール58を形成する。

【0164】

次に、図27(a)に示すように、ハードマスク42cの上に、2層目の凹部(配線溝)に対応する開口部45cを有するレジスト膜8fを形成する。

【0165】

次に、図27(b)に示すように、レジスト膜8fをマスクとして、ハードマスク42cをドライエッチングし、新たな開口部を形成する。

【0166】

このハードマスク42cを用い、図27(b)に示すように、2層目の層間絶縁膜38aをドライエッチングして、凹部(配線溝)44aを形成する。その後、レジスト膜8fを除去する。

【0167】

以上の工程により、図28に示すように、2層目の層間絶縁膜38aに、ダミー凹部46b、凹部(配線溝)44a、コンタクトホール58aが形成される。

【0168】

その後、実施の形態1と同じ手順により、埋設導電部とダミー埋設導電部を形成し、更に3層目以降の配線層等を形成する。これにより、図29に示すに、実施の形態2の半導体装置82aが形成される。

【0169】

図29に示すように、実施の形態2の半導体装置82aでは、ダミー埋設導電部52bが配線層53を貫通している。その他の点は、実施の形態1の半導体装置82と略同じである。

【0170】

以上のように、実施の形態の形態1及び2では、ダミー基板凹部は細長い平面形状を有する凹部すなわち溝(ダミーSTI溝)である。しかし、ダミー基板凹部は、等方的な平面形状を有する凹部すなわち孔であってもよい。同様に、基板凹部も孔であってもよい。

【0171】

また、実施の形態1及び2では、素子領域上の凹部は溝(配線溝)である。しかし、素子領域上の凹部は孔(例えば、コンタクトホール)であってもよい。この場合、埋設導電部は、例えばコンタクトプラグになる。

【0172】

また、実施の形態の形態1及び2の半導体素子28は、MOSトランジスタである。しかし、半導体素子28は、他の素子(例えば、バイポーラトランジスタ、光検出器など)であってもよい。

【0173】

以上の実施の形態1及び2に関し、更に以下の付記を開示する。

【0174】

(付記1)

半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、

前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、

前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、

前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、

前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、

前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する

半導体装置の製造方法。

【0175】

(付記2)

付記1に記載の半導体装置の製造方法において、

前記貫通電極領域は、前記第1絶縁膜および前記基板が除去される除去領域と前記除去領域以外の非除去領域とを有し、

前記貫通電極領域上の前記ダミー凹部は、前記非除去領域上に形成されることを

特徴とする半導体装置の製造方法。

【0176】

(付記3)

付記1又は2に記載の半導体装置の製造方法において、

前記半導体素子が形成される素子形成領域と前記貫通電極領域とを有する素子未形成基板の表面に、研磨ストッパー膜を形成し、

前記素子形成領域に基板凹部を形成し、前記貫通電極領域にダミー基板凹部を形成し、

前記研磨ストッパー膜上、前記基板凹部内、および前記ダミー基板凹部内に第2絶縁膜を形成し、

前記研磨ストッパー膜が露出するまで前記第2絶縁膜を研磨して、前記基板凹部内に素子分離絶縁膜を形成すると共に前記ダミー基板凹部内にダミー素子分離絶縁膜を形成し、

前記素子形成領域内の前記素子分離絶縁膜で囲われた領域に前記半導体素子を形成して、前記素子領域と前記貫通電極領域とを有する前記基板を形成し、

前記貫通電極領域の前記ダミー基板凹部は、前記非除去領域に形成されることを

特徴とする半導体装置の製造方法。

【0177】

(付記4)

付記1乃至3に記載の半導体装置の製造方法において、

前記ダミー凹部または前記ダミー基板凹部は、溝または孔であることを

特徴とする半導体装置の製造方法。

【0178】

(付記5)

付記1乃至4のいずれか1項に記載の半導体装置の製造方法において、

前記ダミー凹部の前記基板に平行な断面は、所定の形状および所定のサイズを有することを

特徴とする半導体装置の製造方法。

【0179】

(付記6)

付記1乃至5のいずれか1項に記載の半導体装置において、

前記第1絶縁膜は、疎水性の絶縁膜であることを

特徴とする半導体装置の製造方法。

【0180】

(付記7)

付記6に記載の半導体装置の製造方法において、

前記第1絶縁膜は、有機官能基を有することを

特徴とする半導体装置の製造方法。

【0181】

(付記8)

付記1乃至7のいずれか1項に記載の半導体装置の製造方法において、

前記非除去領域の横断面の総面積は、前記貫通電極領域の横断面の面積の0.4倍以下0.1倍以上であることを

特徴とする半導体装置の製造方法。

【0182】

(付記9)

半導体素子を有する基板と、

前記基板上に積層された複数の絶縁膜と、

前記複数の絶縁膜それぞれに形成された複数の導電部と、

前記基板および前記複数の絶縁膜を貫通する貫通電極とを有し、

前記貫通電極は、前記基板、前記複数の絶縁膜、および前記導電部に対応するダミー導電部を積層して得られる柱状の積層部を有する

半導体装置。

【符号の説明】

【0183】

2・・・素子未形成基板

4・・・研磨ストッパー膜

10・・・素子形成領域

10a・・・素子領域

12・・・貫通電極領域

14・・・STI溝(基板凹部)

16・・・ダミーSTI溝(ダミー基板凹部)

18・・・埋め込み絶縁膜

20・・・埋設絶縁膜

22・・・ダミー埋設絶縁膜

24・・・除去領域

26・・・非除去領域

28・・・半導体素子

38・・・層間絶縁膜(絶縁膜)

44・・・凹部

46・・・ダミー凹部

48・・・導電材

50・・・埋設導電部

52・・・ダミー埋設導電部

54・・・多層配線部

62・・・貫通ホール(貫通電極ホール)

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、IC(Integrated Circuit)チップを積層した3次元ICが注目されている。3次元ICのチップ間(または、ICチップとパッケージ基板の間)は、ICチップを貫通する電極(以下、貫通電極と呼ぶ)によって接続される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−228320号公報

【特許文献2】特開2010−21352号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、ICチップの配線は、ダマシン法により形成される。ダマシン法では、まず層間絶縁膜に配線溝を形成し、この配線溝の内部および層間絶縁膜上に導電材(例えば、Cu)を形成する。その後、層間絶縁膜上の導電材を化学的機械研磨(Chemical Mechanical Polishing)により除去して、配線溝に埋設された埋設配線を形成する。

【0005】

この化学的機械研磨は導電材が除去された後も一定期間継続され、層間絶縁膜の上部が一定量除去される。この時、貫通電極の膜内形成領域(層間絶縁膜内の形成領域)と埋設配線が形成された配線領域の撥水性(または、研磨レート)の違いによって、研磨面に窪みが発生する。この窪みの上に層間絶縁膜を形成し次層の埋設配線を形成すると、埋設配線間のショートが起き易くなるという問題が生じる。

【課題を解決するための手段】

【0006】

上記の問題を解決するために、本製造方法の一観点によれば、半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する半導体装置の製造方法が提供される。

【発明の効果】

【0007】

開示の製造方法によれば、貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが抑制される。

【図面の簡単な説明】

【0008】

【図1】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図2】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図3】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図4】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図5】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図6】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図7】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図8】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図9】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図10】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図11】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図12】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図13】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図14】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図15】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図16】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図17】実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【図18】貫通電極領域にダミーSTI溝を設けない場合の問題を説明する工程断面図である。

【図19】貫通電極領域の上にダミー凹部を設けない場合の問題を説明する工程断面図である。

【図20】貫通電極領域の上にダミー凹部を設けない場合の問題を説明する工程断面図である。

【図21】貫通電極領域の上にダミー凹部を設けない場合の別の問題を説明する工程断面図である。

【図22】貫通電極領域の上にダミー凹部を設けない場合の別の問題を説明する工程断面図である。

【図23】貫通電極領域上のダミー埋設導電部を、配線ルールにしたがって形成した場合の問題を説明する図である。

【図24】凹部およびダミー凹部が設けられた層間絶縁膜の平面図である。

【図25】凹部およびダミー凹部が設けられた層間絶縁膜の平面図である。

【図26】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図27】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図28】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図29】実施の形態2の半導体装置の製造方法を説明する工程断面図である。

【図30】バリアメタル用研磨剤の研磨レートを説明する図である。

【発明を実施するための形態】

【0009】

以下、図面にしたがって本発明の実施の形態について説明する。但し、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。尚、図面が異なっても対応する部分には同一の符号を付し、その説明を省略する。

【0010】

(実施の形態1)

図1乃至17は、実施の形態1の半導体装置の製造方法を説明する工程断面図である。

【0011】

(1)素子分離絶縁膜および半導体素子の形成工程

(i)STI溝およびダミーSTI溝の形成工程(図1(a)〜図1(c))

まず、ウエハ状の基板(素子未形成基板)2を用意する。基板2は、例えばSi基板又はSOI(Silicon on Insulator)基板である。

【0012】

図1(a)に示しように、基板2には、半導体素子が形成される素子形成領域10と貫通電極が形成される貫通電極領域12とが、予め設定されている。貫通電極領域12には、基板2が除去されて空洞が形成される除去領域24と、除去領域24以外の非除去領域26が設定されている。尚、素子形成領域10は、基板2の表面内の領域である。貫通電極領域12は、基板2の表面から内部に至る領域である。この貫通電極領域12内に、後述する貫通電極の一部が形成される。図1には、水平方向(基板表面に平行な方向)に対する素子形成領域10の設定範囲が矢印で示されている。貫通電極領域12についても、同様である。

【0013】

図1(a)に示すように、基板2の表面に、例えばCVD(Chemical Vapor Deposition)法により厚さ30〜150nmの研磨ストッパー膜(例えば、SiN膜)4を形成する。

【0014】

更に、研磨ストッパー膜4の上に、図1(b)に示すように、レジスト膜(例えば、フォトレジスト膜;以下同様)8を形成する。このレジスト膜8に、例えばフォトリソグラフィ技術を用いて、STI(Shallow Trench Isolation)溝に対応する開口部6aおよびダミーSTI溝に対応する開口部6bを設ける。

【0015】

STI溝は、素子形成領域10に設けられる素子分離絶縁膜用の基板凹部(基板表面の凹部)である。一方、ダミーSTI溝は、貫通電極領域12の非除去領域26に設けられる基板凹部である。

【0016】

次に、レジスト膜8をマスクとし、CF4ガスを反応ガスとして研磨ストッパー膜4および基板2をドライエッチングする。その後、レジスト膜8を、例えばアッシングにより除去する。

【0017】

このドライエッチングにより、図1(c)に示すように、素子形成領域10にSTI溝14を形成する。更に、貫通電極領域12の非除去領域26に、ダミーSTI溝16を形成する。STI溝14およびダミーSTI溝16は、基板2の凹部(基板凹部)である。

【0018】

尚、ダミーSTI溝16は、素子形成領域10に形成してもよい。むしろ、STI溝の形成密度が低い素子形成領域10には、ダミーSTI溝16を形成することが好ましい。

【0019】

(ii)埋設絶縁膜およびダミー埋設絶縁膜の形成工程(図1(d)〜図2(b))

まず、図1(d)に示すように、研磨ストッパー膜4の上、基板凹部14の内部、およびダミー基板凹部16の内部に、例えばHDP(High Density Plasma)−CVD法により絶縁膜18(以下、埋め込み絶縁膜と呼ぶ)を堆積する。埋め込み絶縁膜18は、例えば厚さ300〜1000nmのSiO2膜である。

【0020】

次に、図2(a)に示すように、化学的機械研磨(以下、CMPと呼ぶ)により、研磨ストッパー膜4が露出するまで埋め込み絶縁膜18を研磨して、STI溝14の内部に埋設絶縁膜20を形成すると共に、ダミーSTI溝16の内部にダミー埋設絶縁膜22を形成する。

【0021】

研磨法としては、例えばロータリ式研磨法を用いることができる(後述する他のCMPについても同様)。研磨剤(研磨スラリ)としては、ヒュームドシリカ等の砥粒にph調整剤(例えば、水酸化カリウムや水酸化アンモニウム)を加えたSTI用研磨剤を用いることができる。砥粒は、コロイダルシリカまたは酸化セリウムであっても良い。また、平坦性を向上させるため、研磨剤に界面活性剤を添加しても良い。

【0022】

このようなSTI用研磨剤としては、キャボットマイクロエレクトロニクス社製のSS−25シリーズ(商品名)、DAナノマテリアルズ社製のSTI−2100(商品名)、日立化成社製のHS−8005シリーズ、同じく日立化成社製のHS−9000シリーズ(商品名)などがある。

【0023】

次に、図2(b)に示すように、リン酸等のエッチング液を用いて、研磨ストッパー膜4を除去する。このウェットエッチングにより、基板2の表面が露出する。この時、埋設絶縁膜20とダミー埋設絶縁膜22は、研磨ストッパー膜4の厚さ分、基板表面から突出する。

【0024】

(iii)半導体素子の形成工程(図2(c))

次に、図2(c)に示すように、埋設絶縁膜20で囲われた領域に、MOS(Metal Oxide Semiconductor)トランジスタ等の半導体素子28を形成する。この半導体素子28は、埋設絶縁膜20により他の半導体素子から電気的に分離される。すなわち、埋設絶縁膜20は、素子分離絶縁膜である。

【0025】

一方、図2(c)に示すように、ダミー埋設絶縁膜22で囲われた領域に、半導体素子は形成されない。すなわちダミー埋設絶縁膜22は、素子分離絶縁膜としては機能しない。

【0026】

以上の工程により、半導体素子28を有する素子領域10aと貫通電極が形成される貫通電極領域12とを有する基板2aが形成される。

【0027】

尚、図面が複雑になるので、図2(c)の左端側の埋設絶縁膜20に対応する半導体素子は省略されている。しかし、実際には、この領域にも、半導体素子は形成される(以下の図面でも、同様)。

【0028】

―リーク電流の防止―

図2(b)に示すように、研磨ストッパー膜4を除去した直後の埋設絶縁膜20およびダミー埋設絶縁膜22は、基板2の表面から突出する突出部30a、30bを有している。この突出部は、半導体素子28を形成する工程(例えば、ゲート酸化膜の除去工程)で徐々にエッチングされ、図2(c)に示すように、基板表面と略同じ高さになる。

【0029】

埋め込み絶縁膜18の膜厚や研磨レートは、基板に平行な面内である程度ばらついている。このため、研磨ストッパー膜4上に埋め込み絶縁膜18が残留しないように、研磨ストッパー膜4が露出した後も、一定期間研磨は継続される。

【0030】

図2(a)に示すように、素子形成領域10の研磨ストッパー膜4は、部分的に埋設絶縁膜20で置換される。埋設絶縁膜20を形成する埋め込み絶縁膜18は、研磨ストッパー膜4より研磨され易い。このため、素子形成領域10上の研磨ストッパー膜4は、無垢の研磨ストッパー膜(埋設絶縁膜20で部分的に置換されていない研磨ストッパー膜)より研磨され易い。

【0031】

貫通電極領域12上の研磨ストッパー膜4も、ダミー埋設絶縁膜22で部分的に置換される。ダミー埋設絶縁膜22も埋め込み絶縁膜18で形成されるので、貫通電極領域12上の研磨ストッパー膜4も研磨され易い。

【0032】

このため実施の形態1によれば、素子形成領域10上の研磨ストッパー膜4は、埋設絶縁膜20で部分的に置換されてはいるが、略均一に研磨される。

【0033】

図18は、貫通電極領域12にダミーSTI溝16を設けない場合の問題を説明する工程断面図である。図18(a)〜(d)は、それぞれ図1(d)〜図2(c)に対応している。図18(a)は、STI溝14が形成された基板の2上に、埋め込み絶縁膜18が形成された状態を示している。

【0034】

図18(a)に示すように、貫通電極領域12にダミーSTI溝が設けられないと、素子形成領域10上の研磨ストッパー膜4だけが研磨され易くなる。

【0035】

このため、図18(b)に示すように、素子形成領域10上の研磨ストッパー膜4は、貫通電極領域12上の研磨ストッパー膜4より深く研磨される。この時、埋設絶縁膜20の頂上も研磨される。

【0036】

素子形成領域10上の研磨ストッパー膜4および埋設絶縁膜20の研磨深さは、貫通電極領域12から遠ざかるほど深くなる。したがって、図18(c)に示すように、研磨ストップ膜4の頂上は、貫通電極領域12から遠ざかるほど低くなる。

【0037】

この様な基板2に半導体素子28を形成すると、埋設絶縁膜20は徐々にエッチングされ、貫通電極領域12から離れた埋設絶縁膜20aの頂上は基板表面より低くなる。この様な埋設絶縁膜20aで囲われた領域に半導体素子(例えば、MOSトランジスタ)を形成すると、例えば閾値が低くなりリーク電流が増加する。

【0038】

しかし、実施の形態1によれば、上述したように素子形成領域10上の研磨ストッパー膜4は略均一に研磨されるので、このような問題は生じない。

【0039】

(2)コンタクトプラグの形成工程(図2(d))

次に、図2(d)に示すように、半導体素子28、埋設絶縁膜20、およびダミー埋設絶縁膜22を覆うように、基板2aの表面に例えば厚さ300nm〜1000nmの絶縁膜(以下、下部絶縁膜と呼ぶ)32を堆積する。下部絶縁膜32は、例えばCVD法により形成されるSiO2膜である。

【0040】

この下部絶縁膜32に半導体素子28に達するコンタクトホールを形成し、形成したコンタクトホール内にコンタクトプラグ34を形成する。コンタクトプラグ34は、例えば窒化チタニウム(TiN)膜とタングステン(W)膜を順次コンタクトホール内および下部絶縁膜32上に堆積し、その後下部絶縁膜32上のWを除去することで形成される。

【0041】

(3)多層配線部の形成工程(図2(d)〜図9)

(I)埋設導電部およびダミー埋設導電部の形成工程

(i)層間絶縁膜の形成工程(図2(d)〜図3(a))

まず、図2(d)に示すように、下部絶縁膜32およびコンタクトプラグ34の上に、例えばCVDにより、厚さ10〜200nm程度のエッチングストッパー膜36を形成する。エッチングストッパー膜36は、例えば、炭化シリコン(SiC)膜、炭窒化シリコン(SiCN)膜、窒化シリコン(SiN)膜等である。

【0042】

図3(a)に示すように、このエッチングストッパー膜36の上に、厚さ10nm〜1000nmの層間絶縁膜38を形成する。すなわち、半導体素子28を有する基板2aの上に層間絶縁膜38を形成する。

【0043】

層間絶縁膜38は、例えば、CVD、PE−CVD(Plasma enhanced CVD)、および回転塗布法などにより形成される低誘電率絶縁膜(比誘電率が3.0以下の絶縁膜)である。大部分の低誘電率絶縁膜は、疎水性の絶縁膜(例えば、有機官能基を有する絶縁膜)である。したがって、特に断らない限り、低誘電率絶縁膜とは、疎水性の低誘電率絶縁膜を意味するものとする。また、層間絶縁膜は、特に断らない限り、疎水性の低誘電率絶縁膜で形成されるものとする(実施の形態2においても同じ)。

【0044】

低誘電率絶縁膜は、例えば有機シランまたは有機シロキサンを含む原料から形成することができる。例えば、低誘電率絶縁膜は、メチルシラン、ジメチルシラン、トリメチルシラン、テトラメチルシラン、フェニルシラン、メチルフェニルシラン、エチルシラン、またはジエチルシランを含む原料から形成することができる。

【0045】

または、低誘電率絶縁膜は、シクロヘキシルシラン、テトラエトキシシラン、ジメチルジエトキシシラン、ジメチルジメトキシシラン、ジメチルエトキシシラン、メチルジエトキシシラン、又はトリエトキシシランを含む原料から形成することができる。

【0046】

または、低誘電率絶縁膜は、トリメチルフェノキシシラン、フェノキシシラン、ジエトキシシラン、ジアセトキシメチルシラン、メチルトリエトキシシラン、またはジ−tert−ブチルシランを含む原料から形成することができる。

【0047】

または、低誘電率絶縁膜は、tert−ブチルシラン、1,3,5,7−テトラメチルシクロテトラシロキサン、またはオクタメチルシクロテトラシロキサンを含む原料から形成することができる。

【0048】

または、層間絶縁膜38は、ヘキサメチルシクロトリシロキサン、ヘキサメチルジシロキサン、1,1,2,2−テトラメチルジシロキサン、またはオクタメチルトリシロキサンを含む原料から形成することができる。

【0049】

または、低誘電率絶縁膜は、これらの物質(メチルシラン〜オクタメチルトリシロキサン)を複数含む原料により形成することができる。低誘電率絶縁膜の原料には、誘電率を下げるため、ポロジェンが含有させても良い。

【0050】

回転塗布法に用いる原料としては、JSR社製のLKD(商品名)、ダウケミカル社製のポーラスSilK(商品名)、ULVAC社製または三井化学社製のスケーラブルポーラスシリカなどある。

【0051】

CVD法に用いる原料としては、AMAT社製のBlack Diamond(商品名)、ASM社製のAurora(商品名)、ノベラス社製のCORAL(商品名)などがある。

【0052】

(ii)凹部(配線溝)およびダミー凹部の形成工程(図3(a)〜図4(b))

まず、図3(a)に示すように、層間絶縁膜38の上に、厚さ10nm〜150nmのハードマスク用の絶縁膜(例えば、SiO2)膜40を堆積する。ハードマスク用絶縁膜40としては、炭化シリコン(SiC)膜、炭酸化シリコン(SiOC)膜、炭窒化シリコン(SiCN)膜、窒化シリコン(SiN)膜などの絶縁膜または金属膜を用いてよい(以下、同様)。これらの絶縁膜は、例えば、CVD、PE−CVD、またはPVD(Physical Vapor Deposition)により形成される。

【0053】

図3(b)に示すように、ハードマスク用絶縁膜40の上に、配線溝用凹部に対応する開口部45aおよびダミー凹部に対応する開口部45bを有するレジスト膜8aを形成する。

【0054】

次に、図4(a)に示すように、レジスト膜8aをマスクとして、絶縁膜40をエッチングし、ハードマスク42を形成する。

【0055】

このハードマスク42を用いて、図4(b)に示すように、層間絶縁膜38およびエッチングストッパー膜36をドライエッチングして、素子領域10aの上の層間絶縁膜39aに配線溝用の凹部44およびダミー凹部46を形成する。一方、貫通電極領域12の上の層間絶縁膜39bには、このドライエッチングによりダミー凹部46を形成する。

【0056】

ハードマスク42および層間絶縁膜38は、例えばCF4ガスを反応ガスとしてドライエッチングされる。エッチングストッパー膜36は、例えばCF4ガスとO2ガスの混合ガスを反応ガスとしてドライエッチングされる。その後、レジスト膜8aおよびハードマスク42を除去する。レジスト膜8aは、例えばアッシングにより除去する。

【0057】

後述するように、凹部(配線溝)44には、配線が形成される。一方、素子領域10a上のダミー凹部46には、素子領域10a上の研磨むらを抑制するため、ダミー埋設導電部が形成される。この素子領域10a上のダミー埋設導電部の形成位置は、所定の配線ルールに従って決定される。

【0058】

一方、貫通電極領域12上のダミー凹部46は、図4(b)に示すように、貫通電極領域内の非除去領域26の上に形成される。

【0059】

尚、図4(b)に示す例では、ダミー凹部46は、素子領域10a上の層間絶縁膜39aおよび貫通電極領域12層間絶縁膜39bの両方に形成される。但し、配線密度が高く研磨むらが生じ難い場合等には、素子領域10aの上には、ダミー凹部46を形成しなくてもよい。

【0060】

このように、ダミー凹部46は、素子領域10aと貫通電極領域12のうち少なくても貫通電極領域12の上の層間絶縁膜39bに形成される。

【0061】

(iii)埋設導電部(配線)およびダミー埋設導電部の埋め込み工程(図5)

まず、バリアメタル(図示せず)およびシード膜(図示せず)を、層間絶縁膜38の上、凹部44の内壁、およびダミー凹部46の内壁に順次堆積する。但し、層間絶縁膜38上には、ハードマスク42を介して、バリアメタルおよびシード膜を堆積する。バリアメタルは、例えば厚さ1nm〜30nmの窒化タンタル(TaN)膜である。

【0062】

バリアメタルおよびシード膜は、例えばスパッタ法によって堆積される(以下、同様)。尚、バリアメタルは、導電材の拡散防止のために設けられる。

【0063】

バリアメタルとしては、Ti、Ni、Co、Zr、Cr、Pd、Mn、Ag、Al、Sn、Ta、Re、W、Pt、V、Ru、Auのいずれか1つの金属又は複数の金属の混合物(合金を含む)またはその窒化物が好ましい。シード膜は、例えば、厚さ1nm〜100nmの銅膜である。

【0064】

このシード膜を給電部として、図5(a)に示すように、層間絶縁膜38の上、凹部44の内部、およびダミー凹部46の内部に、例えば厚さ1.2μm程度の導電材48を形成する。但し、層間絶縁膜38の上には、ハードマスク42、バリアメタル、及びシード膜を介して、導電材48を形成する。また、凹部44の内部およびダミー凹部46の内部には、バリアメタル及びシード膜を介して導電材48を形成する。尚、「層間絶縁膜38の上」とは、層間絶縁膜38の外表面上のことである。以下の説明でも、同様である。

【0065】

導電材48は、例えば銅(Cu)である。或いは、導電材48は、Ti、Ni、Co、Zr、Cr、Pd、Mn、Ag、Al、Sn、Ta、Re、W、Pt、V、Ru、Au、Si、Ge、C、S、O、Cl、P、B、H、Hf、F、Nのうち何れか1つ又は複数の元素がCuに混入したもの(合金を含む)でも良い。これらの元素は、シード膜に混入させてもよい。

【0066】

次に、導電材48、バリアメタル、ハードマスク42、および層間絶縁膜38の上部を、例えばCMPで一定量研磨して、図5(b)に示すように、凹部44の内部に埋設導電部(導電部)50を形成する。また、この研磨により、ダミー埋設導電部52をダミー凹部46の内部に形成する。この研磨では層間絶縁膜38も研磨され、所定の厚さ(例えば、20nm〜100nm)を有する埋設導電部50が形成される。尚、ハードマスク42は、バリアメタルを堆積する前、例えば研磨により除去してもよい。

【0067】

以上の研磨工程では、2種類の研磨剤が用いられる。最初に用いる研磨剤は、導電材48を研磨する研磨剤である。2番目に用いる研磨剤は、バリアメタル、ハードマスク42、(凹部44およびダミー凹部46内部の)導電材48、および層間絶縁膜38の上部を研磨する研磨剤である。

【0068】

最初に用いる研磨剤としては、例えば導電材を選択的に研磨する導電材用研磨剤を用いることができる。導電材用研磨剤は、例えば、コロイダルシリカ等の砥粒に加工液を加えることで、導電材(例えば、Cu)に対する研磨レートを大きくした研磨剤である。更に、導電材用研磨剤は、砥粒サイズ(例えば、50nm程度)を小さくすることで、バリアメタル等に対する研磨レートを小さくした研磨剤である。この様に加工水と小サイズ砥粒を組み合わせることで、導電材の選択的研磨が実現される。因みに、STI用研磨剤の砥粒の粒径は、200nm程度である。

【0069】

導電材用研磨剤の砥粒としては、コロイダルシリカ以外にも、フュームドシリカ、セリウム、アルミナ、炭化珪素などの粒子を用いることができる。加工液は、例えば、分散剤、酸化剤、防食剤、キレート剤などを混合した薬液である。酸化剤は、例えば過硫酸アンモニウムや過酸化水素水である。防食剤は、例えばベンゾトリアゾール(BTA)である。キレート剤は、例えばクエン酸、リンゴ酸、キナルジン酸、オレイン酸である。

【0070】

このような導電材用研磨剤では、酸化剤によって導電材(例えば、Cu)が酸化され、水溶性の物質(例えば、Cu錯体)に変化する。この物質が研磨液に溶けだすことで、導電材が高いレートで研磨される。

【0071】

導電材用研磨剤としては、日立化成社製のHS−H635(商品名)、日立化成社製のHS−C930(商品名)、JSR社製のCMS74シリーズ(商品名)、JSR社製のCMS75シリーズ等がある。

【0072】

2番目の研磨剤は、バリアメタル等(バリアメタル、ハードマスク用絶縁膜40、および導電材48)に対する研磨レートが、低誘電率絶縁膜(層間絶縁膜38)に対する研磨レートより大きい研磨剤である。更に、2番目の研磨剤は、バリアメタル、ハードマスク用絶縁膜40、および導電材48それぞれに対して、同程度の研磨レートを有する研磨剤である。

【0073】

2番目の研磨剤としては、例えば、STI用研磨剤に加工液を少量加えた研磨剤(以下、バリアメタル用研磨剤と呼ぶ)を用いることができる。バリアメタル用研磨剤に含まれる加工水は、導電材用研磨剤の加工水と同様、導電材(例えば、Cu)に作用して、導電材に対する研磨レートを高くする薬液である。

【0074】

ここで、バリアメタル用研磨剤の研磨レートに関して少し説明する。

【0075】

まず、バリアメタル用研磨剤のバリアメタル等に対する研磨レートと低誘電率絶縁膜に対する研磨レートを比較する。

【0076】

バリアメタル用研磨剤は、STI用研磨剤と同様、薬剤(ph剤、酸化剤等)が添加された水溶液(例えば、加工水)中に砥粒を分散させたスラリである。したがって、バリアメタル用研磨剤は、疎水性の低誘電率絶縁膜によってはじかれる。一方、バリアメタル用研磨剤は、親水性のハードマスク用絶縁膜40には濡れ易い。このため、バリアメタル用研磨剤のハードマスク用絶縁膜40に対する研磨レートは、(バリアメタル用研磨剤の)低誘電率絶縁膜に対する研磨レートより大きい。バリアメタルおよび導電材に対する研磨レートも同様に、低誘電率絶縁膜に対する研磨レートより大きい。

【0077】

すなわち、バリメタル研磨剤は、バリアメタル等(バリアメタル、ハードマスク用絶縁膜40、および導電材48)に対する研磨レートが、低誘電率絶縁膜(層間絶縁膜38)に対する研磨レートより大きい研磨剤である。

【0078】

次に、バリアメタル、ハードマスク用絶縁膜40、および導電材48それぞれに対する研磨レートを比較する。図30は、バリアメタル用研磨剤の研磨レートを説明する図である。横軸は、研磨対象物である。縦軸は、研磨レートである。

【0079】

バリアメタル用研磨剤の砥粒サイズは、導電材用研磨剤の砥粒サイズより大きい(例えば、バリアメタル用研磨剤の砥粒サイズは、STI用研磨剤と同程度に大きい。)。このため、バリアメタル用研磨剤の対ハードマスク研磨レート100(ハードマスク用絶縁膜に対する研磨レート)は、導電材用研磨剤の対ハードマスク研磨レート102より大きい。

【0080】

バリアメタル用研磨剤に添加される加工水は、導電材用研磨剤に添加される加工水より低濃度である。したがって、バリアメタル用研磨剤の対導電材研磨レート104は、導電材用研磨剤の対導電材用研磨レート106より小さい。

【0081】

ところで、導電材用研磨剤の対導電材研磨レート106は、導電材用研磨剤の対ハードマスク研磨レート102より大きい。したがって、導電材用研磨剤の研磨レート102,106に対する大小関係108を考慮すれば容易に推定されるように、バリアメタル用研磨剤は、ハードマスク(すなわち、ハードマスク用絶縁膜40)および導電材48それぞれに対して、同程度の研磨レート100,104を有している。

【0082】

ところで、バリアメタル用研磨剤に添加される加工水は、バリアメタルにも作用する。この加工水の作用により、対バリアメタル研磨レートは、対ハードマスク研磨レートと同程度になる。したがって、バリアメタル用研磨剤は、バリアメタルに対しても、導電材48と同程度の研磨レートを有している。但し、対バリアメタル研磨レートは、対ハードマスク研磨レートより大きくてもよい。バリアメタルは極めて薄いので、対バリアメタル研磨レートが対ハードマスク研磨レートより大きくても、研磨面は平坦に保たれる。

【0083】

このようなバリアメタル用研磨剤としては、日立化成社製のT605−8(商品名)、JSR社製のCMS8201/8252(商品名)、JSR社製のCMS8501/8552(商品名)などがある。

【0084】

尚、バリアメタル用研磨剤に改質剤(または界面活性剤)を添加することで、低誘電率絶縁膜を親水性することが提案されている。しかし、このような研磨剤を用いると低誘電率絶縁膜の吸水性が高まり、その結果、低誘電率絶縁膜の誘電率が高くなってしまう。したがって、バリアメタル用研磨剤に改質剤等を添加した研磨剤は、2番目の研磨剤としては好ましくない。

【0085】

(II)「埋設導電部およびダミー埋設導電部の形成工程」の繰り返し(図6〜図9)

(I)で説明した「埋設導電部およびダミー埋設導電部の形成工程」(以下、埋設導電部の形成工程と呼ぶ)と略同じ工程を繰り返すことで、図9に示す多層配線部54を形成する。

【0086】

1層目の配線層53aは、(I)の工程で形成される配線層である。一方、2層目以降の配線層53は、(I)の工程とは異なり、直前に形成した埋設導電部(配線)に接続するコンタクトプラグを形成した後、埋設導電部およびダミー埋設導電部を形成することで製造される。これ以外の点では、1層目の配線層53aの形成工程と2層目以降の配線層53の形成工程は略同じである。

【0087】

以下、1層目の埋設導電部53aの形成工程と2層目以降の埋設導電部53の形成工程の相違点について説明する。尚、1層目の埋設導電部53aの形成工程と共通する部分については、説明を省略する。

【0088】

2層目の埋設導電部53bの形成工程では、図6(a)に示すように、1層目の層間絶縁膜38の上に、エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用絶縁膜40aを、1層目の埋設導電部53aの形成工程と略同じ手順で形成する。エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用絶縁膜40aの組成およびサイズは、1層目のものと略同じである。但し膜厚は、1層目のものよりも厚くしてもよい。

【0089】

次に、ハードマスク用絶縁膜40aの上に、コンタクトプラグに対応する開口部56を有するレジスト膜8bを形成する。このコンタクトプラグは、一層目の埋設導電部(配線)50に接続するプラグである。

【0090】

このレジスト膜8bをマスクとして、図6(b)に示すように絶縁膜40aをドライエッチングし、ハードマスク42aを形成する。このハードマスク42aを用いて、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aを順次ドライエッチングし、1層目の配線50に達するコンタクトホール58を形成する。その後、レジスト8bをアッシングにより除去する。

【0091】

次に、図7(a)に示すように、ハードマスク42aの上に、2層目の凹部(配線溝)に対応する開口部45cおよび2層目のダミー凹部に対応する開口部45dを有するレジスト膜8cを形成する。

【0092】

このレジスト膜8cをマスクとして、ハードマスク42aをドライエッチングして、ハードマスク42aに新たな開口部を形成する。

【0093】

この新たな開口部を有するハードマスク42aを用い、図7(b)に示すように、2層目の層間絶縁膜38aをドライエッチングして、素子領域10a上の層間絶縁膜39cに凹部(配線溝)44aおよびダミー凹部46aを形成する。更に、このドライエッチングにより、(貫通電極領域12内の)非除去領域26上の層間絶縁膜39dに、ダミー凹部46aが形成される。その後、ハードマスク42a上に残っているレジスト膜8cを、アッシングにより除去する。

【0094】

1層目の凹部(配線溝)44とは異なり、2層目の凹部(配線溝)44aは、層間絶縁膜38aを貫通せずに、層間絶縁膜38aの内部に留まっている。ダミー凹部46aについても、同様である。コンタクトホール58の上部は、上記ドライエッチングにより、凹部(配線溝)44aに吸収される。一方、コンタクトホール58aの下部により、凹部(配線溝)44aは1層目の埋設導電部(配線)50に連結される。

【0095】

図7(b)に示す例では、ダミー凹部46aは、素子領域10aの上の層間絶縁膜39cおよび貫通電極領域12上の層間絶縁膜39dの両方に形成される。しかし、凹部(配線溝)44aの密度が高い場合等には、1層目の配線層53aと同様、素子領域10aの上にダミー凹部46aは形成しなくてもよい。

【0096】

次に、層間絶縁膜38aの上、凹部44aの内部、コンタクトホール58aの内部、およびダミー凹部46aの内部に、導電材48aを形成する(図8(a)参照)。但し、層間絶縁膜38aの上には、ハードマスク42aを介して導電材48aを形成する。

【0097】

その後、導電材48aを研磨し、図8(b)にように、2層目の埋設導電部50aおよびダミー埋設導電部52aを形成する。導電材48aの形成工程および研磨工程は、1層目の埋設導電部の形成工程および研磨工程と略同じである。

【0098】

以上の工程により、埋設導電部50a、ダミー埋設導電部52a、およびコンタクトプラグ34aを有する2層目の配線層53bが形成される。

【0099】

3層目以降の配線層53も、2層目の配線層53bと略同じ工程により形成される。このような工程により、複数の配線層53,53aを有する多層配線部54が形成される。

【0100】

―配線間の短絡防止―

図19及び20は、貫通電極領域12の上にダミー凹部46を設けない場合の問題を説明する工程断面図である。

【0101】

図19(a)に示すように、貫通電極領域12の上にダミー凹部を設けずに、層間絶縁膜38の上に導電材48を形成した場合を考える。尚、図19(a)では、層間絶縁膜38上のハードマスクは省略されている。

【0102】

この状態で導電材48が研磨され層間絶縁膜38の表面が露出すると、図19(b)に示すように、貫通電極領域12の上には、親水性の導電材(例えば、Cu)を有さない層間絶縁膜(以下、貫通領域絶縁膜と呼ぶ)39eが出現する。一方、素子領域10aの上には、導電材(埋設導電部50およびダミー埋設導電部52)を有する層間絶縁膜39f(以下、素子領域絶縁膜と呼ぶ)が出現する。

【0103】

素子領域絶縁膜39fの表面には、親水性の導電材が表面に露出している。したがって、素子領域絶縁膜39fは、水に濡れ易い。一方は、貫通領域絶縁膜39eは、疎水性の低誘電率絶縁膜で膜全体が形成されているので、水をはじき易い。

【0104】

このため、導電材48の研磨が終了し層間絶縁膜38の研磨が開始すると、貫通領域絶縁膜39eの周囲に、研磨剤の淀みが発生する。その結果、貫通領域絶縁膜39eの周囲で研磨が促進され、貫通領域絶縁膜39eの周りに窪み60が生成される。

【0105】

その後、図20(a)に示すように、窪み60の上に次の層間絶縁膜38cを形成すると、窪み60が次の層間絶縁膜38cに転写されて、別の窪み60aが発生する。

【0106】

この窪み60aを有する層間絶縁膜38cに埋設導電部(配線)50,50bを形成すると、図20(b)に示すように、一部の導電材48bが研磨されずに、窪み60aに残留する。

【0107】

この窪み60aに配線50b(埋設導電部)が形成されると、残留した導電材48bによって配線50bが接続されショートする。

【0108】

一方、実施の形態1では、貫通電極領域12上の層間絶縁膜38にも、親水性の導電材(ダミー埋設部52)が形成される。したがって、実施の形態1によれば、研磨剤の淀みが発生しないので、配線同士がショートすることはない。

【0109】

図21及び22は、貫通電極領域12の上にダミー凹部46を設けない場合の別の問題を説明する工程断面図である。

【0110】

図19及び20を参照して説明した問題は、層間絶縁膜が疎水性の低誘電率絶縁膜で形成されている場合に生じる問題である。図21及び22では、層間絶縁膜が親水性の絶縁膜で形成されている場合に生じる問題を説明する。尚、親水性の絶縁膜としては、有機官能基を有さない多孔質無機二酸化ケイ素(SiO2)等がある。

【0111】

図21(a)に示すように、貫通電極領域12の上にダミー凹部を設けずに、層間絶縁膜38の上に導電材48を形成した場合を考える。尚、図21(a)でも、層間絶縁膜38上のハードマスクは省略されている。

【0112】

導電材48の研磨が終了し層間絶縁膜38の研磨が開始すると、貫通電極領域12の上に、導電材(ダミー埋設導電部52)を有さない貫通領域絶縁膜39eが出現する。一方、素子領域10aの上には、導電材(埋設導電部50およびダミー埋設導電部52)を有する素子領域絶縁膜39fが出現する(図21(b)参照)。

【0113】

図21及び22の場合、層間絶縁膜38も親水性の絶縁膜で形成されているので、貫通領域絶縁膜39eおよび素子領域絶縁膜39fは共に、水をはじかない。このため、図19及び20の場合とは異なり、研磨剤の淀みは発生しない。

【0114】

しかし、図21(b)に示すように、層間絶縁膜38が研磨されると、素子領域絶縁膜39fに弧状の窪み60bが発生する。

【0115】

この窪み60bの上に次の層間絶縁膜38dを形成すると、図22(a)に示すように、次の層間絶縁膜38dにも窪み60cが発生する。このような層間絶縁膜38dに埋設導電部(配線)50を形成すると、窪み60cの底に残留した導電材48cにより、配線間がショートがする(図22(b)参照)。

【0116】

しかし、この場合も、貫通電極領域12上の絶縁膜38にダミー埋設導電部を形成することで、窪み60bの発生が抑制され、配線間のショートも起きない。したがって、層間絶縁膜38は親水性であってもよい。

【0117】

親水性の層間絶縁膜に窪み60bが発生することは、実験により確認されている。このような窪み60bは、配線(埋設導電部)を形成する導電材が層間絶縁膜より柔らかいために発生すると考えられる。

【0118】

Cu等の導電材は、層間絶縁膜より柔らかい。このため研磨圧力に対して導電材が発生する反発力(反作用)は、層間絶縁膜が発生する反発力より小さい。したがって、層間絶縁膜に導電材が埋設されていると、層間絶縁膜に加わる研磨圧力が増加し、層間絶縁膜が研磨され易くなる。その結果、窪み60bが発生する。

【0119】

(4)貫通電極の形成工程(図10〜図16)

まず、図10に示すように、多層配線部54の上にハードマスク用絶縁膜40bを形成する。ハードマスク用絶縁膜40bは、多層配線部54の形成に用いた絶縁膜40,40aと略同じものである。

【0120】

このハードマスク用絶縁膜40bの上に、貫通電極領域12の上に開口部6cを有するレジスト膜8dを形成する。このレジスト膜8dをマスクとして、絶縁膜40bをドライエッチングして、貫通電極領域12の上で開口するハードマスク42bを形成する。

【0121】

このハードマスク42bを用いて、貫通電極領域12の上の層間絶縁膜38,38a、エッチングストッパー膜36,36a、下部絶縁膜32、および貫通電極領域(基板2の一部)12をドライエッチングして、図11に示すように、基板2の内部に至る貫通電極ホール(孔)62を形成する。

【0122】

ハードマスク42b、層間絶縁膜38,38a、下部絶縁膜32、および基板2(貫通電極領域12)は、例えばCF4ガスを反応ガスとするドライエッチングにより除去する。エッチングストッパー膜36,36aは、例えばCF4ガスとO2ガスの混合ガスを反応ガスとするドライエッチングにより除去する。その後、レジスト膜8dを、アッシングにより除去する。

【0123】

ダミー埋設導電部52,52aを形成する導電材は、このようなドライエッチングでは除去されない。このため貫通ホール62の内部には、図11に示すように、ダミー埋設導電部52aの下側にピラー(支柱)状のエッチング残部64が形成される。

【0124】

次に、図12に示すように、貫通ホール62の内壁、エッチング残部64、及びハードマスク42bを覆う絶縁膜66を、例えばCVDにより堆積する。絶縁膜66は、例えば厚さ100nm〜200nmのSiO2膜である。絶縁膜66は、例えばSiC膜、SiCN膜、またはSiN膜であってもよい。

【0125】

この絶縁膜66の上に、厚さ50〜300nmのバリアメタル、厚さ1nm〜100nmのシード膜、厚さ10μm程度の導電材(第2導電材)を順次形成して、貫通ホール62を導電材で埋め込む。その後、図13に示すように、導電材、ハードマスク42b上の絶縁膜66、およびハードマスク42bの上部を研磨して、貫通ホール62内に埋設された導電材68を形成する。

【0126】

バリアメタル、シード膜、および導電材の組成および形成方法は、埋設導電部50およびダミー埋設導電部52と略同じである。また、導電材の研磨法も、埋設導電部50およびダミー埋設導電部52と略同じである。但し、予めウェットエッチングによりハードマスク42b上の導電材を1μm程度まで薄くしてから、導電材を研磨する。

【0127】

次に、図14に示すように、ハードマスク42bの上に、貫通ホール内の導電材68および最上層の埋設導電部50a(配線)の上で開口する上部絶縁膜70を形成する。

【0128】

上部絶縁膜70の開口部には、貫通ホール内の導電材68および埋設導電部50a(配線)それぞれに接続する電極72を形成する。電極72は、例えばアルミニウム(Al)電極である。電極72と上部絶縁膜70間には、バリアメタル(図示せず)が形成される。

【0129】

次に、図15に示すように、上部絶縁膜70の上に、電極72の上で開口する最上部絶縁膜74を形成する。最上部絶縁膜74と上部絶縁膜70の間には、SiN膜(図示せず)等を形成してもよい。

【0130】

上部絶縁膜70および最上部絶縁膜74は、例えばCVDおよびフォトリソグラフィ技術により形成される。上部絶縁膜70および最上部絶縁膜74は、例えばSiO2である。

【0131】

図15に示すように、最上部絶縁膜74の上には、電極72の上で開口するポリイミド膜76を形成する。その後、このポリイミド膜76の開口部に、電極72に接続する半田バンプ78を形成する。

【0132】

次に、基板2の裏面(素子領域10aの反対側の基板面)を、貫通ホール内に埋設された導電材68が露出するまで、例えば機械的に研磨する。これにより、図16に示すように、基板2および多層配線部54を貫通する貫通電極80が形成される。

【0133】

尚、貫通電極80は貫通ホールの内壁に形成された絶縁膜66により、基板2から絶縁される。

【0134】

(5)裏面側バンプの形成工程等(図17)

その後、図17に示すように、基板2の裏面に、貫通電極80の下側で開口するポリイミド膜76aを形成する。このポリイミド膜76aの開口部に、貫通電極80に接続する半田バンプ78aを形成する。最後に、半導体素子28および多層配線部54などが形成された基板2を分割して、半導体装置82を完成する。

【0135】

この半導体装置82は、図17に示すように、半導体素子28を有する基板2aと、基板2a上に積層された複数の層間絶縁膜38,38aとを有している。半導体装置82は、更に、複数の層間絶縁膜38,38aそれぞれに埋設された複数の埋設導電部50,50aと、基板2aおよび複数の層間絶縁膜38,38aを貫通する貫通電極80とを有している。

【0136】

そして、貫通電極80は、基板2aの一部、複数の層間絶縁膜38,38a、および複数の埋設導電部50,50aに対応するダミー埋設導電部52,52aを順次積層して得られる柱状の積層部(エッチング残部64)を有している。

【0137】

尚、埋設導電部50,50aおよび埋設導電部50,50aの対応するダミー埋設導電部は同じ工程で形成されるで、略同じ厚さ(したがって、所定の厚さ)を有している。ここで、半導体装置82は、例えば、半田バンプ78aにより裏面側でパッケージ基板に搭載される。一方、半導体装置82の表面側には、別の半導体装置(ICチップ;図示せず)が積層される。

【0138】

この時、半導体装置82の貫通電極80は、表面側の別の半導体装置の電極に接続される。この別の半導体装置には、貫通電極80を介して、パッケージ基板から電源電圧や信号が供給される。或いは、別の半導体装置の信号が、半導体装置82の貫通電極80を介して、パッケージ基板に出力される。

【0139】

貫通電極80を有する半導体装置を複数積層すれば、3層以上のスタックドICを形成することができる。この場合、半導体装置間の信号の送受信は、貫通電極80を介して行われる。

【0140】

―貫通電極の貫通性―

上述したように、素子領域10a上のダミー埋設導電部52の位置は、配線層53,53aごとに定められる配線ルールによって決定される。このため、ダミー埋設導電部52,52aは、配線層ごとに異なった位置(基板2に平行な面内の位置)に形成される。

【0141】

図23は、貫通電極領域12上のダミー埋設導電部52,52aを、配線ルールにしたがって形成した場合の問題を説明する図である。この場合、ダミー埋設導電部52,52aは配線層53,53aごとに異なった位置に形成される。このため、図23に示すように、ピラー状のエッチング残部64aが、貫通ホール62内に無秩序に林立する。

【0142】

このため、基板2に近づくほど貫通ホール62の開口率が小さくなり、最悪の場合、貫通ホール62がエッチング残部64aによって塞がれてしまう。このような貫通ホール62に導電材を形成しても、貫通性の良い貫通電極(すなわち、低抵抗の貫通電極)は形成できない。

【0143】

一方、実施の形態1では、予め設定された非除去領域26の上にダミー埋設導電部52,52aが形成されるので、図16に示すように、貫通電極80の貫通性は良好である。したがって、貫通電極80の抵抗は低くなる。

【0144】

ダミー埋設導電部52,52aは、貫通電極領域12内の非除去領域26(図7(b)参照)の上に形成される。したがって、貫通電極領域12内における非除去領域26の割合が小さいほど、貫通性は良くなる。

【0145】

例えば、非除去領域26の横断面(基板2に平行な断面)の総面積は、貫通電極領域12の横断面の面積の0.4倍以下が好ましい。尚、「非除去領域26の横断面の総面積」とは、全ての非除去領域26の横断面の面積の和を意味する。

【0146】

但し、非除去領域26の割合が小さくなり過ぎると、素子領域10a上で層間絶縁膜38,38aが窪んで配線間のショートが起きやすくなる。したがって、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.1倍以上が好ましい。

【0147】

すなわち、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.4倍以下0.1倍以上が好ましい。更に好ましくは、非除去領域26の横断面の総面積は、貫通電極領域12の横断面の面積の0.3倍以下0.2倍以上である。

【0148】

同様に、貫通電極80の積層部(エッチング残部64)の横断面の総面積は、貫通電極80の横断面の面積の0.4倍以下0.1倍以上が好ましい。更に好ましくは、貫通電極80の積層部(エッチング残部64)の横断面の総面積は、貫通電極80の横断面の面積の0.3倍以下0.2倍以上である。

【0149】

貫通電極領域12の上に形成されるダミー凹部の平面形状(基板2に平行な断面の形状)およびサイズが配線層ごとに異なると、最もサイズの大きなダミー凹部または最も細長いダミー凹部によって貫通電極ホール62の開口率が制限される。したがって、貫通電極領域12上のダミー凹部52,52aの平面形状は、所定の形状および所定サイズ(例えば、非除去領域26の平面形状およびサイズ)を有することが好ましい。この場合、積層部64内のダミー埋設導電部の基板に平行な断面も、所定の形状および所定のサイズを有する。

【0150】

尚、ダミー基板凹部内のダミー埋設絶縁膜22(図2(c)参照)は、例えば基板用のドライエッチングで除去することができる。しかし、ダミー埋設絶縁膜22と基板2のエッチングレートが異なるので、ダミー埋設絶縁膜22(またはその一部)が除去領域24(図1(a)参照)に形成されると、貫通ホール62の形状に乱れが生じる。

【0151】

したがって、「(1)素子分離絶縁膜および半導体素子の形成工程」で説明したように、ダミー埋設絶縁膜22も非除去領域26に形成することが好ましい。但し、基板2とダミー埋設絶縁膜22のエッチングレートの差が小さい場合等には、ダミー埋設絶縁膜22(またはその一部)を除去領域24に形成してもよい。

【0152】

―ダミー凹部の平面形状―

図24及び25は、凹部44およびダミー凹部46が設けられた層間絶縁膜38,38aの平面図である。図24及び25には、層間絶縁膜38,38aの下方に位置する貫通電極領域12が破線で示されている。

【0153】

図24(a)に示す例では、ダミー凹部46の平面形状は正方形である。したがって、ダミー凹部46は、四角柱状の孔(ホール)である。図24(a)に示す例では、このようなダミー凹部46が、格子状に配列されている。一方、凹部44は、縦長の配線溝である。

【0154】

図24(b)に示す例では、四角柱状のダミー凹部46の列が、上下スライドしている。

【0155】

図25(a)に示す例では、貫通電極領域12上のダミー凹部46の平面形状は、長方形である。したがって、貫通電極領域12上のダミー凹部46は溝である。このような場合、エッチング残部64の横断面が大きくなり、エッチング残部64の強度は大きくなる。

【0156】

図25(b)に示す例では、貫通電極領域12上のダミー凹部46は45°回転している。

【0157】

この様に、ダミー凹部46の形状および配置には、種々のバリエーションが存在する。一方、ダミー凹部46の1辺は、CMPの特性等を考慮すると、0.1μm〜1.0μm程度が好ましい(ダミー凹部46の平面形状が矩形の場合)。

【0158】

実施の形態1では、貫通電極領域12上のダミー凹部46は、非除去領域26(図7(b)参照)の上に設けられる。しかし、貫通電極領域12上のダミー凹部46が少数の場合等には、非除去領域26を設定せずに、ダミー凹部46を貫通電極領域12内の任意の位置に形成してもよい。

【0159】

(実施の形態2)

図26乃至29は、実施の形態2の半導体装置82aの製造方法を説明する工程断面図である。

【0160】

実施の形態1では、図7に示すようにコンタクトホール58の形成後、凹部44a(配線溝)とダミー凹部46aを同時に形成する。一方、実施の形態2では、コンタクトホール58aと同時にダミー凹部46aを形成し、その後凹部44a(配線溝)を形成する。その他の工程は、実施の形態1の製造方法と略同じである。したがって、実施の形態1と共通する部分については、説明を省略する。

【0161】

まず、図26(a)に示すように、実施の形態1の工程にしたがって、1層目の配線層53aまで形成する。更に、実施の形態1の工程にしたがって、1層目の配線層53aの上に、エッチングストッパー膜36a、層間絶縁膜38a、およびハードマスク用の絶縁膜40aを形成する。

【0162】

次に、ハードマスク用絶縁膜40aの上に、2層目のダミー凹部に対応する開口部45dとコンタクトプラグに対応する開口部56を有するレジスト膜8eを形成する。このコンタクトプラグは、一層目の配線50に接続するプラグである。

【0163】

このレジスト膜8eをマスクとして、図26(b)に示すように絶縁膜40aをドライエッチングし、ハードマスク42cを形成する。次に、ハードマスク42cを用いて、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aをドライエッチングして、2層目の層間絶縁膜38aおよびエッチングストッパー膜36aを貫通する、ダミー凹部46bおよびコンタクトホール58を形成する。

【0164】

次に、図27(a)に示すように、ハードマスク42cの上に、2層目の凹部(配線溝)に対応する開口部45cを有するレジスト膜8fを形成する。

【0165】

次に、図27(b)に示すように、レジスト膜8fをマスクとして、ハードマスク42cをドライエッチングし、新たな開口部を形成する。

【0166】

このハードマスク42cを用い、図27(b)に示すように、2層目の層間絶縁膜38aをドライエッチングして、凹部(配線溝)44aを形成する。その後、レジスト膜8fを除去する。

【0167】

以上の工程により、図28に示すように、2層目の層間絶縁膜38aに、ダミー凹部46b、凹部(配線溝)44a、コンタクトホール58aが形成される。

【0168】

その後、実施の形態1と同じ手順により、埋設導電部とダミー埋設導電部を形成し、更に3層目以降の配線層等を形成する。これにより、図29に示すに、実施の形態2の半導体装置82aが形成される。

【0169】

図29に示すように、実施の形態2の半導体装置82aでは、ダミー埋設導電部52bが配線層53を貫通している。その他の点は、実施の形態1の半導体装置82と略同じである。

【0170】

以上のように、実施の形態の形態1及び2では、ダミー基板凹部は細長い平面形状を有する凹部すなわち溝(ダミーSTI溝)である。しかし、ダミー基板凹部は、等方的な平面形状を有する凹部すなわち孔であってもよい。同様に、基板凹部も孔であってもよい。

【0171】

また、実施の形態1及び2では、素子領域上の凹部は溝(配線溝)である。しかし、素子領域上の凹部は孔(例えば、コンタクトホール)であってもよい。この場合、埋設導電部は、例えばコンタクトプラグになる。

【0172】

また、実施の形態の形態1及び2の半導体素子28は、MOSトランジスタである。しかし、半導体素子28は、他の素子(例えば、バイポーラトランジスタ、光検出器など)であってもよい。

【0173】

以上の実施の形態1及び2に関し、更に以下の付記を開示する。

【0174】

(付記1)

半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、

前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、

前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、

前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、

前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、

前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する

半導体装置の製造方法。

【0175】

(付記2)

付記1に記載の半導体装置の製造方法において、

前記貫通電極領域は、前記第1絶縁膜および前記基板が除去される除去領域と前記除去領域以外の非除去領域とを有し、

前記貫通電極領域上の前記ダミー凹部は、前記非除去領域上に形成されることを

特徴とする半導体装置の製造方法。

【0176】

(付記3)

付記1又は2に記載の半導体装置の製造方法において、

前記半導体素子が形成される素子形成領域と前記貫通電極領域とを有する素子未形成基板の表面に、研磨ストッパー膜を形成し、

前記素子形成領域に基板凹部を形成し、前記貫通電極領域にダミー基板凹部を形成し、

前記研磨ストッパー膜上、前記基板凹部内、および前記ダミー基板凹部内に第2絶縁膜を形成し、

前記研磨ストッパー膜が露出するまで前記第2絶縁膜を研磨して、前記基板凹部内に素子分離絶縁膜を形成すると共に前記ダミー基板凹部内にダミー素子分離絶縁膜を形成し、

前記素子形成領域内の前記素子分離絶縁膜で囲われた領域に前記半導体素子を形成して、前記素子領域と前記貫通電極領域とを有する前記基板を形成し、

前記貫通電極領域の前記ダミー基板凹部は、前記非除去領域に形成されることを

特徴とする半導体装置の製造方法。

【0177】

(付記4)

付記1乃至3に記載の半導体装置の製造方法において、

前記ダミー凹部または前記ダミー基板凹部は、溝または孔であることを

特徴とする半導体装置の製造方法。

【0178】

(付記5)

付記1乃至4のいずれか1項に記載の半導体装置の製造方法において、

前記ダミー凹部の前記基板に平行な断面は、所定の形状および所定のサイズを有することを

特徴とする半導体装置の製造方法。

【0179】

(付記6)

付記1乃至5のいずれか1項に記載の半導体装置において、

前記第1絶縁膜は、疎水性の絶縁膜であることを

特徴とする半導体装置の製造方法。

【0180】

(付記7)

付記6に記載の半導体装置の製造方法において、

前記第1絶縁膜は、有機官能基を有することを

特徴とする半導体装置の製造方法。

【0181】

(付記8)

付記1乃至7のいずれか1項に記載の半導体装置の製造方法において、

前記非除去領域の横断面の総面積は、前記貫通電極領域の横断面の面積の0.4倍以下0.1倍以上であることを

特徴とする半導体装置の製造方法。

【0182】

(付記9)

半導体素子を有する基板と、

前記基板上に積層された複数の絶縁膜と、

前記複数の絶縁膜それぞれに形成された複数の導電部と、

前記基板および前記複数の絶縁膜を貫通する貫通電極とを有し、

前記貫通電極は、前記基板、前記複数の絶縁膜、および前記導電部に対応するダミー導電部を積層して得られる柱状の積層部を有する

半導体装置。

【符号の説明】

【0183】

2・・・素子未形成基板

4・・・研磨ストッパー膜

10・・・素子形成領域

10a・・・素子領域

12・・・貫通電極領域

14・・・STI溝(基板凹部)

16・・・ダミーSTI溝(ダミー基板凹部)

18・・・埋め込み絶縁膜

20・・・埋設絶縁膜

22・・・ダミー埋設絶縁膜

24・・・除去領域

26・・・非除去領域

28・・・半導体素子

38・・・層間絶縁膜(絶縁膜)

44・・・凹部

46・・・ダミー凹部

48・・・導電材

50・・・埋設導電部

52・・・ダミー埋設導電部

54・・・多層配線部

62・・・貫通ホール(貫通電極ホール)

【特許請求の範囲】

【請求項1】

半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、

前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、

前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、

前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、

前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、

前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する

半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記貫通電極領域は、前記第1絶縁膜および前記基板が除去される除去領域と前記除去領域以外の非除去領域とを有し、

前記貫通電極領域上の前記ダミー凹部は、前記非除去領域上に形成されることを

特徴とする半導体装置の製造方法。

【請求項3】

請求項1又は2に記載の半導体装置の製造方法において、

前記半導体素子が形成される素子形成領域と前記貫通電極領域とを有する素子未形成基板の表面に、研磨ストッパー膜を形成し、

前記素子形成領域に基板凹部を形成し、前記貫通電極領域にダミー基板凹部を形成し、

前記研磨ストッパー膜上、前記基板凹部内、および前記ダミー基板凹部内に第2絶縁膜を形成し、

前記研磨ストッパー膜が露出するまで前記第2絶縁膜を研磨して、前記基板凹部内に素子分離絶縁膜を形成すると共に前記ダミー基板凹部内にダミー素子分離絶縁膜を形成し、

前記素子形成領域内の前記素子分離絶縁膜で囲われた領域に前記半導体素子を形成して、前記素子領域と前記貫通電極領域とを有する前記基板を形成し、

前記貫通電極領域の前記ダミー基板凹部は、前記非除去領域に形成されることを

特徴とする半導体装置の製造方法。

【請求項4】

請求項1乃至3のいずれか1項に記載の半導体装置において、

前記第1絶縁膜は、疎水性の絶縁膜であることを

特徴とする半導体装置の製造方法。

【請求項5】

半導体素子を有する基板と、

前記基板上に積層された複数の絶縁膜と、

前記複数の絶縁膜それぞれに形成された複数の導電部と、

前記基板および前記複数の絶縁膜を貫通する貫通電極とを有し、

前記貫通電極は、前記基板、前記複数の絶縁膜、および前記導電部に対応するダミー導電部を積層して得られる柱状の積層部を有する

半導体装置。

【請求項1】

半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、

前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、

前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、

前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、

前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、

前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成する

半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記貫通電極領域は、前記第1絶縁膜および前記基板が除去される除去領域と前記除去領域以外の非除去領域とを有し、

前記貫通電極領域上の前記ダミー凹部は、前記非除去領域上に形成されることを

特徴とする半導体装置の製造方法。

【請求項3】

請求項1又は2に記載の半導体装置の製造方法において、

前記半導体素子が形成される素子形成領域と前記貫通電極領域とを有する素子未形成基板の表面に、研磨ストッパー膜を形成し、

前記素子形成領域に基板凹部を形成し、前記貫通電極領域にダミー基板凹部を形成し、

前記研磨ストッパー膜上、前記基板凹部内、および前記ダミー基板凹部内に第2絶縁膜を形成し、

前記研磨ストッパー膜が露出するまで前記第2絶縁膜を研磨して、前記基板凹部内に素子分離絶縁膜を形成すると共に前記ダミー基板凹部内にダミー素子分離絶縁膜を形成し、

前記素子形成領域内の前記素子分離絶縁膜で囲われた領域に前記半導体素子を形成して、前記素子領域と前記貫通電極領域とを有する前記基板を形成し、

前記貫通電極領域の前記ダミー基板凹部は、前記非除去領域に形成されることを

特徴とする半導体装置の製造方法。

【請求項4】

請求項1乃至3のいずれか1項に記載の半導体装置において、

前記第1絶縁膜は、疎水性の絶縁膜であることを

特徴とする半導体装置の製造方法。

【請求項5】

半導体素子を有する基板と、

前記基板上に積層された複数の絶縁膜と、

前記複数の絶縁膜それぞれに形成された複数の導電部と、

前記基板および前記複数の絶縁膜を貫通する貫通電極とを有し、

前記貫通電極は、前記基板、前記複数の絶縁膜、および前記導電部に対応するダミー導電部を積層して得られる柱状の積層部を有する

半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2013−65615(P2013−65615A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−202047(P2011−202047)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]