半導体装置の製造方法

【課題】周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に、第2絶縁膜26から離間する第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有する半導体装置の製造方法による。

【解決手段】第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に、第2絶縁膜26から離間する第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有する半導体装置の製造方法による。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

電源を切っても記憶を保持できるフラッシュメモリは、携帯電話のようなモバイル機器に使用されるほか、ロジック回路と混載してFPGA(Field Programmable Gate Array)にも使用されている。特に、後者のようにフラッシュメモリをロジック回路と混載する場合には、メモリセルとロジック回路のそれぞれの製造プロセスを互いにうまく利用しあい、製品として出荷するロジック混載メモリに不具合が発生しないようにする必要がある。

【0003】

そのロジック混載メモリでは、製品の出荷前に、フラッシュメモリを構成するトンネル絶縁膜の耐圧をモニターする場合がある。但し、トンネル絶縁膜は、フローティングゲートの下に形成されているため、その上下から電圧を与えて耐圧をモニターするには、コントロールゲートを介さないでフローティングゲートに導電性プラグを直接コンタクトさせ、その導電性プラグと半導体基板との間に試験電圧を印加する必要がある。

【0004】

そのため、上記のロジック混載メモリでは、フローティングゲートにコンタクトする導電性プラグの形成プロセスを、周辺ロジック回路の製造プロセスにいかにして組み入れるかが重要となる。

【0005】

以下の特許文献1〜10には、本発明に関連する様々なロジック混載メモリが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平6−97457号公報

【特許文献2】特開2003−158242号公報

【特許文献3】特開平11−219595号公報

【特許文献4】特開2004−55763号公報

【特許文献5】特開平10−56161号公報

【特許文献6】特開平11−31799号公報

【特許文献7】特開平10−189954号公報

【特許文献8】特開2003−37169号公報

【特許文献9】特開2003−100887号公報

【特許文献10】特開2003−124356号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明の一観点によれば、半導体基板の第1領域上にコンタクト領域を一部に有する第1絶縁膜を形成する工程と、前記第1絶縁膜上に第1導電体を形成する工程と、前記第1導電体上に第2絶縁膜を形成する工程と、前記第1導電体の前記コンタクト領域上の前記第2絶縁膜を除去することにより、前記第2絶縁膜に開口を形成する工程と、前記第2絶縁膜の上に第2導電膜を形成する工程と、前記第1導電体の前記コンタクト領域上の前記第2導電膜を除去し、該第2導電膜を第2導電体とする工程と、前記第2導電体を覆う第3絶縁膜を形成する工程と、前記コンタクト領域上であって、前記開口の内側の前記第3絶縁膜に、前記第2絶縁膜から離間する第1ホールを形成する工程と、前記コンタクト領域と電気的に接続される導電性プラグを前記第1ホール内に形成する工程とを有する半導体装置の製造方法が提供される。

【0009】

その半導体装置の製造方法では、前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第2領域にも形成し、前記第2導電膜を形成する工程において、前記第2領域の前記第1絶縁膜上にも該第2導電膜を形成し、前記第2導電膜を前記第2導電体とする工程において、前記第2領域の該第2導電膜をパターニングしてコントロールゲートとし、前記コンタクト領域上の前記第2絶縁膜を除去する工程において、該第2絶縁膜を前記コントロールゲートの下に中間絶縁膜として残し、前記第1導電体を形成する工程において、該第1導電体と同じ材料で構成されるフローティングゲートを前記中間絶縁膜の下に形成し、前記フローティングゲートの側方の前記半導体基板に第1、第2ソース/ドレイン領域を形成して、該第1、第2ソース/ドレイン領域、前記第1絶縁膜、前記フローティングゲート、前記中間絶縁膜、及び前記コントロールゲートでフラッシュメモリセルを構成する工程を更に有するのが好ましい。

【0010】

更に、このようにフラッシュメモリセルを形成する場合には、前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第3領域にも形成するのが好ましい。そして、前記第2絶縁膜を形成する工程において、該第2絶縁膜を前記第3領域の前記第1絶縁膜上にも形成し、前記第1、第2絶縁膜をスルー膜として使用しながら前記第3領域の前記半導体基板に不純物を注入する工程を有するのが好ましい。

【0011】

このようにスルー膜として使用した第1、第2絶縁膜は、上記の不純物を注入後、コンタクト領域上の第2絶縁膜を除去する工程において除去してよい。

【0012】

これによれば、不純物注入のスルー膜として使用した後に不要となった第2絶縁膜を第3領域において除去する工程が、コンタクト領域上の第2絶縁膜を除去する工程を兼ねる。そのため、本発明では、余計なマスク工程を追加せずにコンタクト領域の上方の第2絶縁膜を選択的に除去できる。

【0013】

更に、このように第2絶縁膜を除去する工程では、第1領域では第2絶縁膜のみを除去するのに対し、第3領域では第1絶縁膜と第2絶縁膜の二層を除去するので、第3領域のエッチング量が第1領域におけるそれよりも多くなる。そのため、この工程におけるエッチング量を第3領域のそれに合わせることで、第1領域における第2絶縁膜を完全に除去しながら、第3領域における第1、第2絶縁膜の過剰なエッチングを防止してその下の素子分離絶縁膜等に削れが発生するのを防ぐことができる。

【発明の効果】

【0014】

本発明によれば、不純物注入のスルー膜として使用した後に不要となった第2絶縁膜を第3領域において除去する工程が、コンタクト領域上の第2絶縁膜を除去する工程を兼ねので、余計なマスク工程を追加せずにコンタクト領域の上方の第2絶縁膜を選択的に除去できる。

【0015】

更に、その第2絶縁膜を除去する工程では、第3領域のエッチング量が第2領域のエッチング量よりも大きくなるので、全体のエッチング量を第3領域のそれに合わせることで、第2領域における第2絶縁膜を完全に除去しつつ、第3領域における過剰なエッチングによって素子分離絶縁膜等が削れるのを防ぐことができる。

【図面の簡単な説明】

【0016】

【図1】図1は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その1)である。

【図2】図2は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その2)である。

【図3】図3は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その3)である。

【図4】図4は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その4)である。

【図5】図5は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第2例)の製造途中の断面図(その1)である。

【図6】図6は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第2例)の製造途中の断面図(その2)である。

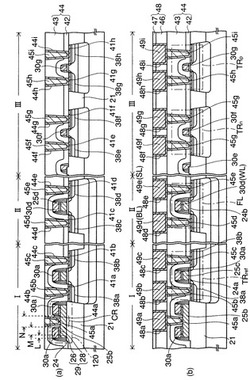

【図7】図7(a)、(b)は、仮想的な半導体装置(第3例)の製造途中の断面図である

【図8】図8は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図9】図9は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図10】図10は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図11】図11は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図12】図12は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図13】図13は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図14】図14は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図15】図15は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図16】図16は、本発明の第1実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図17】図17は、本発明の第1実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図18】図18は、本発明の第1実施形態に係る半導体装置の等価回路の一例を示す図である。

【図19】図19は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図20】図20は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図21】図21は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図22】図22は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図23】図23は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図24】図24は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図25】図25は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その3)である。

【図26】図26は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図27】図27は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図28】図28は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図29】図29は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図30】図30は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図31】図31は、本発明の第3実施形態に係る半導体装置の製造途中の平面図である。

【図32】図32は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図33】図33は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図34】図34は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図35】図35は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図36】図36は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図37】図37は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図38】図38は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図39】図39は、本発明の第5実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図40】図40は、本発明の第5実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図41】図41は、本発明の第5実施形態において、反射防止膜の厚さによってAs-イオンがどの程度ブロックされるのかを調査して得られたグラフである。

【図42】図42は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図43】図43は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図44】図44は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図45】図45は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図46】図46は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図47】図47は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図48】図48は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図49】図49は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図50】図50は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その9)である。

【図51】図51は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その10)である。

【図52】図52は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その11)である。

【図53】図53は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その12)である。

【図54】図54は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その13)である。

【図55】図55は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その14)である。

【図56】図56は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その15)である。

【図57】図57は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その16)である。

【図58】図58は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その17)である。

【図59】図59は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その18)である。

【図60】図60は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その19)である。

【図61】図61は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その20)である。

【図62】図62は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その21)である。

【図63】図63は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その22)である。

【図64】図64は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その23)である。

【図65】図65は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その24)である。

【図66】図66は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その25)である。

【図67】図67は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図68】図68は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図69】図69は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その3)である。

【発明を実施するための形態】

【0017】

(1)予備的事項の説明

本発明の実施の形態の前に、予備的事項について説明する。

【0018】

(i)第1例

図1〜図4は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図である。

【0019】

最初に、図1(a)に示す断面構造を得るまでの工程について説明する。

【0020】

まず、シリコン基板1にSTI(Shallow Trench Isolation)用の素子分離溝1aを形成した後、その溝1a内に二酸化シリコン膜を素子分離絶縁膜2として埋め込む。次いで、シリコン基板1の表面を熱酸化して第1熱酸化膜3を形成した後、全面に第1ポリシリコン膜4を形成してそれをパターニングし、第1周辺回路領域Iとセル領域IIのみにポリシリコン膜4を残す。その後に、全面にONO膜5を形成する。

【0021】

続いて、図1(b)に示すように、第2周辺回路領域III上の第1熱酸化膜3とONO膜5とをエッチングして除去する。そして、第2周辺回路領域IIIのシリコン基板1の表面を熱酸化して第2熱酸化膜7を形成した後、全面に第2ポリシリコン膜6を形成する。

【0022】

次に、図2(a)に示すように、第2ポリシリコン膜6の上に第1レジストパターン9を形成する。そして、その第1レジストパターン9をマスクにして、第1周辺回路領域Iとセル領域IIにおける各膜4〜6をエッチングする。これにより、セル領域IIには、ポリシリコンよりなるフローティングゲート4bとコントロールゲート6bが残されることになる。また、第1周辺回路領域Iには、ポリシリコンよりなる第1、第2導電体4a、6aが残される。

【0023】

この後に、第1レジストパターン9は除去される。

【0024】

次に、図2(b)に示すように、第2導電体6aが露出する第2レジストパターン10をセル領域IIと第2周辺回路領域IIIに形成する。そして、その第2レジストパターン10をマスクにして第2ポリシリコン膜6をエッチングすることにより、第2周辺回路領域IIにゲート電極6cを形成すると共に、第1周辺回路領域Iの第2導電体6aを除去し、ONO膜5を露出させる。

【0025】

続いて、図3(a)に示す断面構造を得るまでの工程について説明する。

【0026】

まず、フローティングゲート4bとゲート電極6cとをマスクにしてシリコン基板1にn型不純物をイオン注入することにより、各ゲート4b、6cの側方のシリコン基板1に第1〜第4ソース/ドレインエクステンション11a〜11dを形成する。次に、全面に酸化シリコン膜等の絶縁膜を形成した後、それをエッチバックして各ゲート4b、6cと第1導電体4aのそれぞれの横に絶縁性サイドウォール14aとして残す。そのエッチバックの際、第1、第2熱酸化膜3、7はパターニングされてそれぞれトンネル絶縁膜3a、ゲート絶縁膜7aとなる。

【0027】

そして、その絶縁性サイドウォール14aをマスクにして、シリコン基板1にn型不純物を再びイオン注入することにより、第1〜第4n型ソース/ドレイン領域12a〜12dをシリコン基板1に形成する。

【0028】

次いで、その第1〜第4n型不純物拡散領域12a〜12d上に第1〜第4シリサイド層13a〜13dを形成した後、全面にカバー絶縁膜15と層間絶縁膜16とを順に形成する。

【0029】

ここまでの工程により、第2周辺回路領域IIIには、第1、第2n型不純物拡散領域12a、12bとゲート電極6cとで構成される周辺トランジスタTRが形成され、セル領域IIには、第1、第2不純物拡散領域12a、12b、トンネル絶縁膜3a、フローティングゲート4b、中間絶縁膜5b、及びコントロールゲート6bで構成されるフラッシュメモリセルFLが形成されたことになる。

【0030】

一方、第1周辺回路領域Iにおける第1導電体4aは、不図示の参照トランジスタのゲート電極を兼ねている。その参照トランジスタは、フラッシュメモリセルFLのトンネル絶縁膜3aと同じプロセスで形成されたゲート絶縁膜を有しているので、参照トランジスタの耐圧を調べることで、フラッシュメモリセルFLのトンネル絶縁膜3aの耐圧を調べることができる。

【0031】

次に、図3(b)に示すように、カバー絶縁膜15と層間絶縁膜16とをパターニングして、第1〜第4シリサイド層13a〜13dに至る深さの第1〜第4ホール16a〜16dを形成すると共に、第1導電体4aの上に第5ホール16eを形成する。

【0032】

これらのホール16a〜16eは、最初にカバー絶縁膜15をエッチングストッパ膜として使用しながら層間絶縁膜16をエッチングし、次にエッチングガスを変えてカバー絶縁膜15をエッチングすることにより形成される。

【0033】

また、これらのホールのうち、第1〜第4ホール16a〜16dのコンタクト構造は、ボーダレスコンタクトと呼ばれる。ボーダレスコンタクトでは、各ホール16a〜16dが多少位置ずれしてその一部が素子分離絶縁膜2に重なっても、素子分離絶縁膜2とカバー絶縁膜15とのエッチング速度の違いによって、ホール形成時における素子分離絶縁膜2のエッチング量を抑えている。

【0034】

一方、第5ホール16eは、第1導電体4aとのコンタクトをとり、参照トランジスタにゲート電圧を印加するために形成されるものなので、その底部に第1導電体4aが露出しなければならない。ところが、第1〜第4ホール16a〜16dの形成が、カバー絶縁膜15のエッチング終了と同時に完了するのに対し、第5ホール16eを形成するには、カバー絶縁膜15の下のONO膜5をもエッチングしなければならない。

【0035】

そのため、ホールのエッチング時間を第1〜第4ホール16a〜16dのエッチング時間に合わせると、図示のように、第5ホール16eのエッチング量が不足してホール16eが未開口となり、その下に第1導電体4aが露出しない。

【0036】

従って、第5ホール16eを開口させるには、第1〜第4ホール16a〜16dの形成に必要なエッチング時間に加え、第5ホール16eが貫通するONO膜5のエッチング時間の分だけ余計にエッチングを行わなければならない。

【0037】

但し、このように長時間エッチングを行っても、第1〜第4ホール16a〜16dと第1〜第4シリサイド層13a〜13dとが位置ずれを起こしていなければ特に問題は無い。

【0038】

しかし、それらの間に位置ずれが発生していると、図4の点線円内に示されるように、例えば第3ホール16cの下の素子分離絶縁膜2がエッチングされてしまい、第3ホール16cにシリコン基板1が露出してしまう。こうなると、第3ホール16c内に埋め込まれる第3導電性プラグ19cとシリコン基板1とが短絡してしまい、第3n型ソース/ドレイン領域12cの電位を導電性プラグ19cでコントロールできなくなってしまう。このような不都合は、第3導電性プラグ19cだけでなく、第1、第2、第4ホール16a、16c、16dに形成される第1、第2、第4導電性プラグ19a、19c、19dによっても発生し得る。

【0039】

(ii)第2例

上記した第1例の不都合を解消するため、以下のような方法も考えられる。

【0040】

図5、図6は、仮想的な半導体装置(第2例)の製造途中の断面図である。

【0041】

まず、第1例で示した図2(b)の工程を終了した後に、図5(a)に示すように、フローティングゲート4bとゲート電極6cとをマスクにしてシリコン基板1にn型不純物をイオン注入することにより、各ゲート4b、6cの側方のシリコン基板1に第1〜第4ソース/ドレインエクステンション11a〜11dを形成する。

【0042】

次に、図5(b)に示すように、全面に酸化シリコン等の絶縁膜14を形成する。

【0043】

続いて、図6(a)に示すように、絶縁膜14をエッチバックして各ゲート4b、6cと第1導電体4aのそれぞれの横に絶縁性サイドウォール14aとして残す。本例では、更にエッチングを進めて、第1導電体1上のONO膜5をもエッチングして除去する。

【0044】

続いて、絶縁性サイドウォール14aをマスクにして、シリコン基板1にn型不純物を再びイオン注入することにより、第1〜第4n型ソース/ドレイン領域12a〜12dをシリコン基板1に形成する。

【0045】

その後に、各n型ソース/ドレイン領域12a〜12dの上に第1〜第4シリサイド層13a〜13dを形成する。

【0046】

この後は、第1例で説明した図3〜図4の工程を行うことにより、層間絶縁膜16に第1〜第5ホール16a〜16dを形成し、図6(b)に示す断面構造を得る。

【0047】

以上説明した第2例では、図6(a)に示したように、エッチバックにより絶縁性サイドウォール14aを形成する際にONO膜5も同時に除去し、第1導電体4aの表面を露出させる。そのため、第1〜第4ホール16a〜16dを過剰にエッチングしなくても第5ホール16eの下に第1導電体4aの表面が露出する。

【0048】

しかし、図6(a)に示すエッチバック工程では、絶縁性サイドウォール14aの形成に本来必要なエッチング時間よりも長くエッチングを行うため、素子分離絶縁膜2がエッチングされその上面がシリコン基板1のそれよりも下がってしまう。その結果、図6(b)の点線Xのように、第3n型ソース/ドレイン領域12cとシリコン基板1のそれぞれの側面が素子分離溝1aの側壁に表出する。従って、第3ホール16cが位置ずれを起こすと、第1例と同様に、第3ホール16c内に形成される第3導電性プラグ19cとシリコン基板1とがショートしてしまう。

【0049】

(iii)第3例

上記した第1例と第2例の他に、以下のような方法も考えられる。

【0050】

図7(a)、(b)は、仮想的な半導体装置(第3例)の製造途中の断面図である。

【0051】

まず、第1例で示した図2(a)の工程の後に、図7(a)に示すように、コントロールゲート6b上と第2ポリシリコン膜6上とに、第2導電体6aが露出する第2レジストパターン10を形成する。

【0052】

次に、図7(b)に示すように、第2レジストパターン10をマスクにし、第2ポリシリコン膜6をエッチングしてゲート電極6cを形成すると共に、第2導電体6aとONO膜5とをエッチングして除去し、第1導電体4aを露出させる。その後に、第2レジストパターン10を除去する。

【0053】

この後は、第1例で説明した図3、図4の工程が行われる。

【0054】

第3例では、ゲート電極6cのパターニング時にONO膜5をエッチングして除去するが、そのエッチングによって素子分離絶縁膜2の上面がシリコン基板1の上面よりも下がるので、やはり第2例と同じような不都合が発生してしまう。また、第2周辺回路領域IIIのゲート絶縁膜が薄いと、ONO膜をエッチングする際にソース/ドレイン形成予定領域のシリコン基板1の表面がRIE等のエッチング雰囲気に長時間曝されて汚染したり、シリコン基板1が掘られたりする不都合が生じる。

【0055】

上記した第1〜第3例では、第1導電体4a上のONO膜5の除去の仕方がそれぞれ異なるが、いずれの例でもONO膜を除去しようとすると第1〜第4ホール16a〜16d内で導電性プラグとシリコン基板1とのショートが発生する。これを防ぐために、ONO膜5を除去するための専用のフォトリソグラフィ工程を追加することも考えられるが、これでは工程数が多くなり、半導体装置の生産性が悪化してしまう。

【0056】

本願発明者は、このような第1〜第3例の不都合を解消するため、次のような本発明の実施の形態に想到した。

【0057】

(2)第1実施形態

図8〜図15は、本発明の第1実施形態に係る半導体装置の製造途中の断面図であり、図16、図17はその平面図である。

【0058】

本実施形態では、FPGA等のロジック混載メモリが作製される。

【0059】

最初に、図8(a)に示す断面構造を得るまでの工程について説明する。

【0060】

まず、第1周辺回路領域(第1領域)I、セル領域(第2領域)II、及び第2周辺回路領域(第3領域)IIIが画定されたp型シリコン基板(半導体基板)20にSTI用の素子分離溝20aを形成した後、その素子分離溝20a内に酸化シリコンを素子分離絶縁膜21として埋め込む。

【0061】

次いで、シリコン基板20の表面を熱酸化して犠牲酸化膜(不図示)を形成し、その犠牲酸化膜をスルー膜として使用しながらシリコン基板20にn型不純物としてP+イオンをイオン注入して、シリコン基板20の深部に第1nウエル17aを形成する。そのイオン注入の条件としては、例えば加速エネルギ2MeV、ドーズ量2×1013cm-3が採用される。

【0062】

続いて、1回目の条件を加速エネルギ400KeV及びドーズ量1.5×1013cm-3とし、2回目の条件を加速エネルギ100KeV及びドーズ量2×1012cm-3のとするイオン注入により、シリコン基板20にp型不純物のB+イオンを注入して、上記の第1nウエル17aよりも浅い部分のシリコン基板20に第1pウエル17bを形成する。

【0063】

更に、加速エネルギ40KeV、ドーズ量6×1013cm-3の条件でシリコン基板20にB+イオンをイオン注入することにより、セル領域IIに後で形成されるフラッシュメモリセルの閾値電圧を制御するためのセル用不純物拡散領域17cを形成する。

【0064】

その後、第2周辺回路領域IIIにおいてもイオン注入を行い、図示のような第2nウエル22と第2pウエル23とを形成する。これらのウエルのうち、第2nウエル22のイオン注入は二回に分けて行われ、1回目の条件としてはP+イオンの加速エネルギ600KeV、ドーズ量1.5×1013cm-3が採用され、2回目の条件としては加速エネルギ240KeV、ドーズ量6.0×1012cm-3が採用される。また、第2pウエル23も2回のイオン注入により形成され、1回目の条件としてはB+イオンの加速エネルギ400KeV、ドーズ量1.5×1013cm-3が採用され、2回目の条件としては加速エネルギ100KeV、ドーズ量8×1012cm-3が採用される。

【0065】

なお、上記のn型不純物とp型不純物の打ち分けは不図示のレジストパターンを用いて行われ、イオン注入が終了した後にそのレジストパターンは除去される。

【0066】

その後、イオン注入のスルー膜として使用した犠牲酸化膜をフッ酸溶液によって除去してシリコン基板20の清浄面を露出させた後、ArとO2との混合雰囲気中、温度900℃〜1050℃の条件でその清浄面を熱酸化する。これにより、シリコン基板20の各領域I〜IIIには、厚さ約10nmの熱酸化膜が第1絶縁膜24として形成される。

【0067】

次に、図8(b)に示す断面構造を得るまでの工程について説明する。

【0068】

まず、SiH4(シラン)とPH3(ホスフィン)とを反応ガスとして使用する減圧CVD(Chemical Vapor Deposition)法により、第1絶縁膜24の上に第1導電膜25としてポリシリコン膜を約90nmの厚さに形成する。そのポリシリコン膜には、反応ガス中のPH3により、リンがin-situでドープされることになる。

【0069】

続いて、フォトリソグラフィによりその第1導電膜25をパターニングして第2周辺回路領域III上から除去する。なお、セル領域IIにおける第1導電膜25は、このパターニングによりワードライン方向に直行した帯状となる。

【0070】

次に、第1導電膜25上と、第2周辺回路領域III上の第1絶縁膜24上とに、減圧CVD法を用いて酸化シリコン膜と窒化シリコン膜とをこの順にそれぞれ厚さ5nm、10nmに形成する。更に、O2雰囲気中において、基板温度約950℃、加熱時間約90分間の条件で窒化シリコン膜の表面を酸化し、窒化シリコン膜の表面に約30nmの酸化シリコン膜を形成する。これにより、酸化シリコン膜、窒化シリコン膜、及び酸化シリコン膜をこの順に積層してなるONO膜が第2絶縁膜26として全面に形成されたことになる。

【0071】

その第2絶縁膜26を構成するONO膜は、低温で形成しても酸化シリコン膜と比較してリーク電流が小さい。そのため、フラッシュメモリセルのフローティングゲートとコントロールゲートの間の中間絶縁膜としてこの第2絶縁膜26を使用することで、フローティングゲートに蓄積された電荷がコントロールゲート側に逃げ難くなり、フラッシュメモリセルに書き込まれた情報を長時間にわたって保持することができる。

【0072】

このような第2絶縁膜26を形成した後、加速エネルギを150KeV、ドーズ量を3×1012cm-3とする条件を採用して、第1、第2絶縁膜24、26をスルー膜として使用しながらn型不純物のAs-イオンをシリコン基板20にイオン注入してn型不純物拡散領域22aを形成する。そのn型不純物拡散領域22aは、後で形成されるp型MOSトランジスタの閾値電圧を調節する役割を担う。

【0073】

更に、第1、第2絶縁膜24、26をスルー膜として使用しながら、加速エネルギ30KeV、ドーズ量5×1012cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入する。これにより、第2周辺回路領域IIIには、p型MOSトランジスタの閾値電圧を調節するためのp型不純物拡散領域23aが形成される。

【0074】

なお、このような不純物拡散領域22a、23aのイオン注入では、不図示のレジストパターンによってn型不純物とp型不純物の打ち分けが行われる。

【0075】

続いて、図9(a)に示すように、第2絶縁膜26の上に第1レジストパターン27を形成する。その第1レジストパターン27には、後で導電性プラグと接続される第1導電膜25のコンタクト領域CRの上に第1窓27aを有すると共に、第2周辺回路領域IIIの上に第2窓27bを有する。そして、この第1レジストパターン27をマスクとして使用しながら、CH3とO2との混合ガスをエッチングガスとするプラズマエッチングにより、第1レジストパターン27で覆われていない領域の第2絶縁膜26をエッチングし、その第2絶縁膜26を構成する最上層の酸化シリコン膜と窒化シリコン膜とをエッチングする。次いで、第1レジストパターン27をマスクにして、HF溶液により第2絶縁膜26の最下層の酸化シリコン膜をウエットエッチングして除去する。

【0076】

これにより、コンタクト領域CRにおける第1導電膜25と、第2周辺回路領域IIIのシリコン基板20が露出すると共に、コンタクト領域CRを除いた領域のみに第2絶縁膜が残る。

【0077】

続いて、酸素アッシングによって第1レジストパターン27を除去した後、ウエット処理によりシリコン基板20の表面を洗浄する。

【0078】

次に、図9(b)に示す断面構造を得るまでの工程について説明する。

【0079】

まず、酸素雰囲気中で基板温度を約850℃とする酸化条件を採用して、第2絶縁膜26で覆われていない部分のシリコンを熱酸化する。これにより、ポリシリコンよりなる第1導電膜25上において第2絶縁膜26が除去されていた部分と、第2周辺回路領域IIIのシリコン基板20のそれぞれの表面に、厚さ約2.2nmの熱酸化膜が第3絶縁膜28として形成される。その第3絶縁膜28は第2絶縁膜26と隣接して形成され、これらの第2、第3絶縁膜26、28により絶縁体29が構成される。なお、図9(b)には明示しないが、コンタクト領域CR上の絶縁体29の厚さは他の領域に比べて著しく薄い。

【0080】

その後に、SiH4を反応ガスとして使用する減圧CVD法により、各絶縁膜26、28の上に、厚さ約180nmのノンドープのポリシリコン膜を第2導電膜30として形成する。

【0081】

次に、図10(a)に示す断面構造を得るまでの工程について説明する。

【0082】

まず、第2導電膜30上にフォトレジストを塗布し、それを露光、現像することにより、第2レジストパターン18を形成する。次に、この第2レジストパターン18をエッチングマスクとして使用して第1、第2導電膜25、30、及び絶縁体29をパターニングする。そのパターニングはプラズマエッチングチャンバ内で行われ、ポリシリコンよりなる第1、第2導電膜25、30のエッチングガスとしてはCl2とO2との混合ガスが使用され、ONO膜で構成される第2絶縁膜26のエッチングガスとしてはCH3とO2との混合ガスが使用される。

【0083】

このようなパターニングの結果、第2導電膜30を第2周辺回路領域IIIに残しながら、第1周辺回路領域I上の第1、第2導電膜25、30が、コンタクト領域CRを含む領域においてそれぞれ第1、第2導電体25a、30aとされる。そして、セル領域II上では、第1、第2導電膜25、30と絶縁体29とがそれぞれフローティングゲート25d、コントロールゲート30d、中間絶縁膜29dとされる。

【0084】

この後に、第2レジストパターン30は除去される。

【0085】

図16は、この工程を終了後の平面図であり、先の図10(a)は、図16のA−A線に沿う断面図に相当する。これに示されるように、第1導電体25aは、素子分離絶縁膜21上のパッド部25bと第1絶縁膜24上のゲート部25cとで構成される。

【0086】

次いで、図10(b)に示すように、第1導電体25aのパッド部25bと第2導電膜30とを覆い、且つゲート部25cとフローティングゲート25dとが露出する第3窓31aを備えた第3レジストパターン31を各領域I〜IIIに形成する。そして、この第3窓31aを通じてn型不純物のAsを加速エネルギ50KeV、ドーズ量6×1014cm-3の条件でシリコン基板20にイオン注入することにより、フローティングゲート25dとゲート部25cのそれぞれの側方のシリコン基板20に第1〜第4n型ソース/ドレインエクステンション32a〜32dを形成する。

【0087】

その後に、第3レジストパターン31を除去する。

【0088】

次に、図11(a)に示すように、フローティングゲート25dとコントロールゲート30dの側面を酸化して熱酸化膜(不図示)を形成した後、窒化シリコン膜を全面に形成してそれをエッチバックし、第2導電体30aとフローティングゲート25dのそれぞれの側面に第1絶縁性サイドウォール33として残す。

【0089】

次に、図11(b)に示すように、各領域I〜IIIの上に第4レジストパターン34を形成する。その第4レジストパターン34は、パッド部25bのコンタクト領域CR上に第4窓34aを有すると共に、第2周辺回路領域III上においてゲート電極形状を有する。そして、Cl2とO2との混合ガスをエッチングガスとして採用し、この第4レジストパターン34をマスクにしながら第2導電体30aと第2導電膜30とをプラズマエッチングすることにより、コンタクト領域CR上の第2導電体30aを除去して第1開口30bを形成すると共に、第2周辺回路領域III上に第1、第2ゲート電極30f、30gを形成する。また、このエッチングでは、素子分離絶縁膜21上に延在していた第2導電膜30がパターニングされて配線30eとなる。

【0090】

この後に、第4レジストパターン34を除去する。

【0091】

次に、図12(a)に示すように、第1ゲート電極30fの側方の第3絶縁膜28が露出する大きさの第5窓35aを備えた第5レジストパターン35を各領域I〜IIIの上に形成する。そして、その第5レジストパターン35をマスクにしてチルト角0°、加速エネルギ0.5KeV、及びドーズ量3.5×1014cm-3の条件でB+をシリコン基板20にイオン注入する。その後に、第5窓35aを通じてチルト角28°、加速エネルギ80KeV、及びドーズ量7.0×1012cm-3の条件でAs+を四方向からシリコン基板20にイオン注入することにより、第1ゲート電極30fの側方のシリコン基板20に第5、第6n型ソース/ドレインエクステンション32e、32fを形成する。その後に、第5レジストパターン35は除去される。

【0092】

続いて、図12(b)に示すように、第2ゲート電極30gの側方の第3絶縁膜28が露出する大きさの第6窓36aを備えた第6レジストパターン36を各領域I〜IIIの上に形成する。

【0093】

そして、その第6レジストパターン36をマスクにしてチルト角0°、加速エネルギ3.0KeV、及びドーズ量1.0×1015cm-3の条件でAs+をシリコン基板20にイオン注入する。その後に、第6窓36aを通じてチルト角28°、加速エネルギ35KeV、及びドーズ量1.0×1013cm-3の条件でBF2をシリコン基板20にイオン注入することにより、第2ゲート電極30gの側方のシリコン基板20に第1、第2p型ソース/ドレインエクステンション32g、32hを形成する。その後に、第6レジストパターン36は除去される。

【0094】

次に、図13(a)に示す断面構造を得るまでの工程について説明する。

【0095】

まず、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックして、第2導電体30a、コントロールゲート30d、配線30e、及び第1、第2ゲート電極30f、30gのそれぞれの側面に第2絶縁性サイドウォール37を形成する。そして、そのエッチバックを更に進めることにより、第2絶縁性サイドウォール37をマスクにしながら、パッド部25b上で絶縁体29を構成している第3絶縁膜28をエッチングし、第1開口30bよりも直径が小さな第2開口29aを形成する。

【0096】

また、このエッチバックにより、第2絶縁性サイドウォール37がマスクとなって第1絶縁膜24がパターニングされ、その第1絶縁膜24がゲート部25cとフローティングゲート25dのそれぞれの下にゲート絶縁膜24a及びトンネル絶縁膜24bとして残る。

【0097】

更に、第2周辺回路領域IIIでは、第3絶縁膜28がパターニングされて第1、第2ゲート30f、30gの下にゲート絶縁膜28a、28bとして残る。

【0098】

続いて、図13(b)に示すように、シリコン基板20上にNMOS形成領域が露出する第7レジストパターン39を形成し、このレジストパターン39をマスクにしながら加速エネルギ10KeV、ドーズ量6×1015cm-3の条件でP+をシリコン基板20にイオン注入する。これにより、ゲート部25c、フローティングゲート25d、第1ゲート電極30fのそれぞれの側方のシリコン基板20に、第1〜第6n型ソース/ドレイン領域38a〜38fが形成される。また、このイオン注入では、第2導電体30a、コントロールゲート30d、第1ゲート電極30fにもn型不純物が導入され、これらがn型化される。

【0099】

その結果、第1周辺回路領域Iでは、ゲート部25c、ゲート絶縁膜24a、及び第1、第2n型ソース/ドレイン領域38a、38bで構成される参照トランジスタTRrefが形成される。一方、セル領域IIでは、コントロールゲート30d、中間絶縁膜29d、フローティングゲート25d、トンネル絶縁膜24b、及び第3、第4n型ソース/ドレイン領域38c、38dで構成されるフラッシュメモリセルFLが形成される。そして、第2周辺回路領域IIIでは、第1ゲート電極30f、ゲート絶縁膜28a、及び第5、第6n型ソース/ドレイン領域38e、38fで構成されるn型MOSトランジスタTRnが形成される。

【0100】

この後に、第7レジストパターン39は除去される。

【0101】

次いで、図14(a)に示すように、第1周辺回路領域I、セル領域II、及びn型MOSトランジスタTRnを第8レジストパターン40で覆う。そして、加速エネルギ5KeV、ドーズ量4×1015cm-3のイオン注入条件を採用して、第2ゲート電極30gの側方のシリコン基板20にp型不純物としてB+を導入することにより、第1、第2p型ソース/ドレイン領域38g、38hを形成する。これにより、n型MOSトランジスタTRnの隣の第2周辺回路領域IIIには、第2ゲート電極30g、ゲート絶縁膜28b、及び第1、第2p型ソース/ドレイン領域38g、38hで構成されるp型MOSトランジスタTRpが形成される。

【0102】

そのp型MOSトランジスタTRpは、n型MOSトランジスタTRnと共にセンスアンプ等のロジック回路を構成する。

【0103】

そのイオン注入が終了した後、第8レジストパターン40を除去する。

【0104】

次に、図14(b)に示す断面構造を得るまでの工程について説明する。

【0105】

まず、スパッタ法により全面にコバルト膜を厚さ約8nmに形成した後、そのコバルト膜をアニールしてシリコンと反応させる。そして、素子分離絶縁膜21等の上の未反応のコバルト膜をウエットエッチングして除去し、シリコン基板20の表層に第1〜第8コバルトシリサイド層41a〜41hを形成する。

【0106】

続いて、CVD法によりシリコン窒化膜を厚さ約50nmに形成し、それをエッチングストッパ膜42とする。次いで、そのエッチングストッパ膜42の上にCVD法により第4絶縁膜43として酸化シリコン膜を形成し、エッチングストッパ膜42と第4絶縁膜43とを第1層間絶縁膜44とする。なお、その第4絶縁膜43の厚さは、シリコン基板20の平坦面上で約1000nmである。

【0107】

続いて、CMP(Chemical Mechanical Polishing)法により第1層間絶縁膜44の上面を研磨して平坦化する。その後に、フォトリソグラフィにより第1層間絶縁膜44をパターニングして第1〜第9ホール44a〜44iを形成する。これらのホールのうち、第1ホール44aは、パッド部25bのコンタクト領域CR上に位置しており、第1、第2開口30b、29aの内側に形成される。また、残りの第2〜第9ホール44b〜44iは、それぞれ第1〜第8コバルトシリサイド層41a〜41hの上に形成される。そして、上記の第1ホール44aの下にはONO膜で構成される第2絶縁膜26が形成されていないため、第2周辺回路領域IIIにおける第4〜第9ホール44a〜44iを形成するのと同じ条件で第1ホール44aを形成することにより、パッド部25bの表面を露出させることができる。

【0108】

次に、図15(a)に示す断面構造を得るまでの工程について説明する。

【0109】

まず、第1〜第9ホール44a〜44i内と第1層間絶縁膜44上とに、スパッタ法によりTi(チタン)膜とTiN(窒化チタン)膜とをこの順に形成し、それらをグルー膜とする。そして、六フッ化タングステンを反応ガスとして使用するCVD法により、そのグルー膜の上にW(タングステン)膜を形成して第1〜第9ホール44a〜44i内を完全に埋め込む。そして、第1層間絶縁膜44の上面に形成された余分なW膜とグルー膜とをCMP法により除去し、それらを第1〜第9ホール44a〜44i内に第1〜第9導電性プラグ45a〜45iとして残す。

【0110】

これらの導電性プラグのうち、第2〜第9導電性プラグ45b〜45iは、第1〜第8コバルトシリサイド層41a〜41hを介してソース/ドレイン領域38a〜38hと電気的に接続される。

【0111】

一方、第1導電性プラグ45aは、第1導電体25bのコンタクト領域CRと電気的に接続される。

【0112】

また、同図に示されるように、絶縁体29を構成する第2絶縁膜26は、第3絶縁膜28よりもコンタクト領域CRから離れる構造となる。

【0113】

次に、図15(b)に示す断面構造を得るまでの工程について説明する。

【0114】

最初に、塗布型の低誘電率絶縁膜46を全面に形成した後、低誘電率絶縁膜46が吸湿するのを防ぐ酸化シリコン膜をカバー絶縁膜47としてその上に形成し、低誘電率絶縁膜46とカバー絶縁膜47とを第2層間絶縁膜48とする。

【0115】

次いで、フォトリソグラフィによりその第2層間絶縁膜48をパターニングして、各プラグ45a〜45iの上に第1〜第9配線溝48a〜48iを形成する。なお、このフォトリソグラフィにおいて、酸化シリコンよりなるカバー絶縁膜47のプラズマエッチングにはCH3とO2との混合ガスがエッチングガスとして使用され、低誘電率絶縁膜46のプラズマエッチングにはO2ガスがエッチングガスとして使用される。

【0116】

その後、スパッタ法により全面にCu(銅)膜をシード層として形成し、このシード層に給電を行うことによりシード層上に電解銅めっき膜を形成し、その銅めっき膜により各配線溝48a〜48iを完全に埋め込む。その後に、CMP法を用いて、第2層間絶縁膜48の上に形成された余分なシード層と銅めっき膜とを除去し、それらを各配線溝48a〜48iの中に第1〜第9銅配線49a〜49iとして残す。

【0117】

各銅配線49a〜49iの機能は特に限定されないが、フラッシュメモリセルFLの上の第4、第5銅配線49d、49eは、例えばNAND型フラッシュメモリのビットライン(BL)とソースライン(SL)として機能する。また、コントロールゲート30dはワードライン(WL)として機能する。

【0118】

図17は、この工程を終了後の平面図であり、先の図15(b)は、図17のB−B線に沿う断面図に相当する。但し、図17では、各層の平面レイアウトを見やすくするために、第1〜第9銅配線49a〜49iと第2層間絶縁膜28とを省略してある。

【0119】

これに示されるように、第2導電体30aは、第1導電体25aのゲート部25cの上方からパッド部25bのコンタクト領域CRの外側に延在するように形成される。また、その第2導電体30aは、絶縁膜に囲まれており、電気的にはフローティングの状態となる。

【0120】

以上により、本実施形態に係る半導体装置の基本構造が完成した。

【0121】

その半導体装置は、図15(a)に示すように、シリコン基板20上に第1絶縁膜24、第1導電体25a、第2絶縁膜26、及び第2導電体30aが順に形成された第1の部分Lを有する。更に、その半導体装置は、第1導電体25aと第2導電体30a、又は第1導電体25aと第2絶縁膜26のいずれか一方が積層された第2の部分Mと、第2絶縁膜26と第2導電体30aのいずれもが積層されない第3の部分Nとを有する。そして、これら第1〜第3の部分L〜Nを一体的に有してなる積層構造体120がその半導体装置に形成されたことになる。

【0122】

また、半導体装置には、図15(b)に示したように参照トランジスタTRrefが形成されるが、この参照トランジスタTRrefの機能は特に限定されない。例えば、参照トランジスタTRrefは、工場から出荷する前に、フラッシュメモリセルFLのトンネル絶縁膜24bの耐圧を調べる場合に使用される。これを行うには、第2、第3導電性プラグ45b、45cを介して第1、第2n型ソース/ドレイン領域38a、38bに所定の電圧を印加した状態で、第1導電性プラグ45aを介してゲート部25cの電位を高めていく。そして、ゲート絶縁膜24aがブレイクダウンを起こしてゲート部25cに電子が注入されると、第1導電性プラグ45aに電流が流れるので、その電流を検出することにより、ゲート絶縁膜24aと同じプロセスによって形成されたフラッシュメモリセルFLのトンネル絶縁膜24bの耐圧を調べることができる。

【0123】

或いは、図18に示すように、センスアンプS/Aに入力される参照電流Irefを生成するために上記の参照トランジスタTRrefを用いてもよい。この場合は、参照トランジスタTRrefのゲート部25cにゲート電圧Vgとして2V程度の電圧を印加する共に、そのソース−ドレイン間に約0.5V程度の電圧を印加する。これにより、参照トランジスタTRrefのソース−ドレイン間に参照電流Irefが流れ、それがセンスアンプS/Aに入力される。そして、センスアンプS/Aでは、この参照電流Irefと、フラッシュメモリセルFLの読み出し電流IBLとの大小が比較され、フラッシュメモリセルFLに1と0のどちらの情報が書き込まれているのかが判断される。

【0124】

参照トランジスタTRrefは、フラッシュメモリセルFLと同じ温度特性を持っているので、例えば周囲の温度が上昇して読み出し電流IBLの大きさが小さくなった場合、参照電流Irefの大きさも小さくなるため、各電流IBL、Irefの差が温度に大きく影響されない。従って、周囲の温度が変化しても、センスアンプS/Aにおける各電流IBL、Irefの大小の判断に誤りが発生し難くなり、フラッシュメモリセルFLの読み出し動作を正確に行うことができる。

【0125】

上記した本実施形態によれば、図8(b)に示したように、第1絶縁膜24とONOよりなる第2絶縁膜26とをスルー膜として使用しながら、イオン注入により、第2周辺回路領域IIIに閾値調整用のn型不純物拡散領域22aとp型不純物拡散領域23aとを形成する。そして、図9(a)に示したように、そのイオン注入が終了してスルー膜としての役割を終えた第1、第2絶縁膜24、26を第2周辺回路領域III上で除去するのと同時に、第1周辺回路領域Iのコンタクト領域CR上の第2絶縁膜26も除去する。そのため、本実施形態では、コンタクト領域CR上の第2絶縁膜26を除去するための専用のマスク工程が不要となり、工程数の増大を抑えながら、コンタクト領域CR上の第2絶縁膜26を選択的に除去することが可能となる。

【0126】

しかも、図9(a)のエッチング工程では、第1周辺回路領域Iでは第2絶縁膜26のみを除去するのに対し、第2周辺回路領域IIIでは第1、第2絶縁膜24、26の二層を除去するので、第2周辺回路領域IIIのエッチング量が第1周辺回路領域Iにおけるそれよりも多くなる。そのため、この工程におけるエッチング量を第2周辺回路領域IIIのそれに合わせることで、第1周辺回路領域Iにおける第2絶縁膜26を完全に除去しながら、第2周辺回路領域IIIにおいて第1、第2絶縁膜24、26が過剰にエッチングされるのを防ぐことができる。従って、本発明の予備的事項で説明した第1〜第3例のような素子分離絶縁膜21の削れが第2周辺回路領域IIIにおいて発生しないので、素子分離絶縁膜21の削れに伴う導電性プラグ45f〜45iとシリコン基板20とのショートを防ぐことができ、不良となる半導体装置の数を減らして生産性を高めることが可能となる。

【0127】

(3)第2実施形態

第1実施形態では、第1導電体25aをゲートとするトランジスタを形成したが、第1導電体25aと第2導電体30aとを電極とするキャパシタを形成することもできる。本実施形態では、フラッシュメモリセルの制御用の高電圧を発生するためのポンピングキャパシタに上記の第1導電体を用いる。

【0128】

図19〜図22は、本発明の第2実施形態に係る半導体装置の製造途中の断面図であり、図23〜図25はその平面図である。これらの図において、第1実施形態で説明した要素については第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0129】

最初に、図19(a)に示す断面構造を得るまでの工程について説明する。

【0130】

まず、第1実施形態の図10(a)で説明したように、第2レジストパターン18をエッチングマスクとして使用して第1、第2導電膜25、30、及び絶縁体29をパターニングする。但し、本実施形態では、図19(a)に示されるように、そのパターニングによって形成された第1周辺回路領域I上の第1導電体25aには第1実施形態のようなゲート部25bは形成されない。

【0131】

図23は、このパターニングを終了した時点での平面図であり、上の図19(a)は図23のC−C線に沿う断面図に相当する。これに示されるように、第1導電体25aは、キャパシタ下部電極形状の矩形にパターニングされる。

【0132】

次に、図19(b)に示すように、第3レジストパターン31の第3窓31aを通じてAsを加速エネルギ50KeV、ドーズ量6×1014cm-3の条件でシリコン基板20にイオン注入することにより、フローティングゲート25dの側方のシリコン基板20に第2、第3n型ソース/ドレインエクステンション32c、32dを形成する。その後に、第3レジストパターン31は除去される。

【0133】

続いて、図20(a)に示すように、窒化シリコン膜を全面に形成した後、それをエッチバックして、第1導電体30aとフローティングゲート25dのそれぞれの側面に第1絶縁性サイドウォール33として残す。

【0134】

次いで、図20(b)に示すように、各領域I〜IIIの上に第4レジストパターン34を形成し、この第4レジストパターン34をマスクにして第2導電体30aと第2導電膜30とをプラズマエッチングする。これにより、コンタクト領域CR上の第2導電体30aに第1開口30bが形成されると共に、第2導電体30aがキャパシタ上部電極形状の矩形にパターニングされる。また、第2周辺回路領域IIIでは、第2導電膜30がパターニングされて第1、第2ゲート電極30f、30gと配線30eとが形成される。

【0135】

この後に、第4レジストパターン34を除去する。

【0136】

図24は、この工程を終了した時点での平面図であり、上の図20(b)は図24のD−D線に沿う断面図に相当する。

【0137】

次に、図21(a)に示される断面構造を得るまでの工程について説明する。

【0138】

まず、第1実施形態の図12(a)、(b)で説明した工程を行うことにより、第1、第2ゲート電極30f、30gの側方のシリコン基板20に、それぞれ第5、第6n型ソース/ドレインエクステンション32e、32fと第1、第2p型ソース/ドレインエクステンション32g、32hとを形成する。そして、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックして、第2導電体30a、コントロールゲート30d、配線30e、及び第1、第2ゲート電極30f、30gのそれぞれの側面に第2絶縁性サイドウォール37を形成する。

【0139】

そして、このエッチバックの後に若干のオーバーエッチングを行うことにより、第1開口30b下の酸化シリコンよりなる第3絶縁膜28を除去して第2開口29aを形成し、その第2開口29aからコンタクト領域CRを露出させる。なお、このエッチバックは、ONO膜で構成される第2絶縁膜26が残存する程度に行われるので、周辺回路領域の素子分離絶縁膜21が大きく減少するといった不都合は生じない。

【0140】

また、このようなエッチバックの結果、フローティングゲート25d下の第1絶縁膜24がパターニングされてトンネル絶縁膜24bになると共に、第1、第2ゲート電極30f、30g下の第3絶縁膜28がパターニングされてゲート絶縁膜28a、28bとなる。

【0141】

その後に、第1実施形態で説明した図13(b)、図14(a)のイオン注入工程を行うことにより、図21(b)に示すように、フローティングゲート25dと第1、第2ゲート電極30f、30gの側方のシリコン基板20に、第3〜第6n型ソース/ドレイン領域38c〜38fと第1、第2p型ソース/ドレイン領域38g、38hを形成する。

【0142】

次に、第1実施形態で説明した図14(b)、図15(a)の工程を行うことにより、図22の断面図のようなフラッシュメモリセルFL、n型MOSトランジスタTRn、及びp型MOSトランジスタTRpの基本構造を完成させる。そして、図22に示されるように、第2導電体30aに至る深さの第10ホール44jを形成し、その中に第2導電体30aと電気的に接続される第10導電性プラグ45jを形成する。

【0143】

図25は、この工程を終了した時点での平面図であり、上の図21は図25のE−E線に沿う断面図に相当する。

【0144】

この後は、第1実施形態の図15(b)で説明したのと同様の工程を行うことにより、第2層間絶縁層と銅配線とを形成して、本実施形態に係る半導体装置の基本構造を完成させる。

【0145】

その半導体装置は、図22に示されるように、第1、第2導電体25a、30aの間で絶縁体29を構成する第2絶縁膜26がキャパシタ誘電体膜として機能し、これら第1、第2導電体25a、30aと第2絶縁膜26によってキャパシタQが構成される。

【0146】

そのキャパシタQの機能は特に限定されないが、1.2Vの電源電圧を昇圧して10Vの高電圧を発生する昇圧回路内のポンピングキャパシタとしてキャパシタQを使用するのが好ましい。このようにして得られた高電圧は、例えば、フラッシュメモリセルFLに書き込み又は消去を行う際にコントロールゲート30dに印加され、それによりトンネル絶縁膜24bを介してフローティングゲート25dに電子が注入、又は引き抜かれる。

【0147】

また、このキャパシタQでは、第2開口29aの直径を第1開口30bのそれよりも小さくしたので、点線円内に示すように、第1開口30bの側面と第1導電体25aとの間に第2絶縁膜26が張り出した構造となる。そのような構造によれば、第1導電体25aと第2導電体30aとの間に常に第2絶縁膜26が存在するので、第2絶縁膜26を介してキャパシタQの耐圧が劣化することはない。

【0148】

以上説明した本実施形態によれば、第1実施形態で図8(b)、図9(a)を参照して説明したように、トランジスタの閾値調整用の不純物領域22a、23bをイオン注入で形成する際にスルー膜として使用した第1、第2絶縁膜24、26を除去するのと同時に、第1周辺回路Iのコンタクト領域I上のONO膜よりなる第2絶縁膜26を除去する。そのため、マスク工程を追加せずにコンタクト領域CR上の第2絶縁膜を選択的に除去することが可能となると共に、本発明の予備的事項で説明した第1〜第3例のような素子分離絶縁膜21のエッチングが発生しない。

【0149】

(4)第3実施形態

本実施形態は、第1実施形態で説明した第1導電体25aを抵抗素子として使用するものである。

【0150】

図26〜図30は、本発明の第3実施形態に係る半導体装置の製造途中の断面図であり、図31はその平面図である。これらの図において、第1実施形態で説明した要素については第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0151】

最初に、図26(a)に示す断面構造を得るまでの工程について説明する。

【0152】

まず、第1実施形態の図8(b)の工程を行った後、図26(a)に示すように、第1導電膜25の二つのコンタクト領域CRのそれぞれの上に第1窓27aを備えた第1レジストパターン27を第2絶縁膜26の上に形成する。そして、その第1レジストパターン27をマスクにするフォトリソグラフィにより、コンタクト領域CR上の第2絶縁膜26を除去すると共に、第2周辺回路領域III上の第1、第2絶縁膜24、26とを除去する。その後に、第1レジストパターン27を除去する。

【0153】

次に、図26(b)に示すように、第1実施形態と同様の酸化条件を採用して第2絶縁膜26で覆われていない部分のシリコンを熱酸化し、それにより形成された熱酸化膜を第3絶縁膜28とする。そして、その第3絶縁膜28と第2絶縁膜26とで構成される絶縁体29の上に第2導電膜30としてポリシリコン膜を形成する。

【0154】

続いて、図27(a)に示すように、フォトリソグラフィにより第1、第2導電膜25、30と絶縁体29とをパターニングして、第1周辺回路領域Iにおいてエッチングされずに残存する第1、第2導電膜25、30を第1、第2導電体25a、30aとすると共に、セル領域IIの第1、第2導電膜25、30と絶縁体29をそれぞれフローティングゲート25d、コントロールゲート30d、及び中間絶縁膜29dとする。

【0155】

次いで、図27(b)に示すように、第3レジストパターン31の第3窓31aを通じてシリコン基板20にn型不純物をイオン注入して、フローティングゲート25dの側方のシリコン基板20に第2、第3n型ソース/ドレインエクステンション32c、32dを形成する。

【0156】

その後に、第3レジストパターン31を除去する。

【0157】

次に、図28(a)に示すように、窒化シリコン膜を全面に形成した後、それをエッチバックして、第2導電体30aとフローティングゲート25dのそれぞれの側面に第1絶縁性サイドウォール33として残す。

【0158】

続いて、図28(b)に示すように、第1導電体25aの二つのコンタクト領域CRに対応する二つの第4窓34aを備えた第4レジストパターン34をエッチングマスクとして用いながら、第2導電体30aと第2導電膜30とをエッチングする。これにより、第2導電膜30がパターニングされてコンタクト領域CRの上に第1開口30bが形成されると共に、第2周辺回路領域IIIの上の第2導電膜30がパターニングされて第1、第2ゲート電極30f、30gが形成される。更に、素子分離絶縁膜21上に延在していた第2導電膜30もパターニングされて配線30eとなる。

【0159】

その後、このパターニングに使用した第4レジストパターン34は除去される。

【0160】

次いで、図29(a)に示すように、第1、第2ゲート電極30f、30gの側方のシリコン基板20に、それぞれ第5、第6n型ソース/ドレインエクステンション32e、32fと第1、第2p型ソース/ドレインエクステンション32g、32hとを形成する。

【0161】

そして、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックして、第2導電体30a、コントロールゲート30d、配線30e、及び第1、第2ゲート電極30f、30gのそれぞれの側面に第2絶縁性サイドウォール37を形成する。

【0162】

また、このようなエッチバックの結果、フローティングゲート25d下の第1絶縁膜24がパターニングされてトンネル絶縁膜24bになると共に、第1、第2ゲート電極30f、30g下の第3絶縁膜28がパターニングされてゲート絶縁膜28a、28bとなる。更に、第1導電体25aのコンタクトCR上の第3絶縁膜28が除去されて第1開口30bよりも小さな第2開口29aが形成され、その第2開口29aにコンタクト領域CRが露出する。

【0163】

続いて、図29(b)に示すように、フローティングゲート25dと第1、第2ゲート電極30f、30gの側方のシリコン基板20に、第3〜第6n型ソース/ドレイン領域38c〜38fと第1、第2p型ソース/ドレイン領域38g、38hを形成する。

【0164】

次に、第1実施形態で説明した図14(b)、図15(a)の工程を行うことにより、図30に示すように、第1層間絶縁膜44に第1、第4〜第9ホール44a、44d〜44iを形成した後、各ホールの中に第1、第4〜第9導電性プラグ45a、45d〜45iを形成する。

【0165】

ここまでの工程により、フラッシュメモリセルFL、n型MOSトランジスタTRn、及びp型MOSトランジスタTRpの基本構造が図示のように完成したことになる。

【0166】

図31は、この工程を終了した時点での平面図であり、上の図30は図31のF−F線に沿う断面図に相当する。

【0167】

この後は、第1実施形態の図15(b)で説明したのと同様の工程を行うことにより、第2層間絶縁層と銅配線とを形成して、本実施形態に係る半導体装置の基本構造を完成させる。

【0168】

その半導体装置では、図30に示されるように、第1導電体25aの上に第1ホール44aが間隔をおいて二つ形成されると共に、各第1ホール44aのそれぞれに第1導電性プラグ45aが形成される。そして、これら二つの第1導電性プラグ45aを端子とし、第1導電体25aを抵抗体とする抵抗素子Rが図示のように形成される。

【0169】

その抵抗素子Rの機能は特に限定されず、ロジック回路に必要とされる任意の抵抗として用いてよい。

【0170】

ところで、第2絶縁膜26の上の第2導電体30aは、電気的にフローティングとなっており、上記の抵抗素子Rと電気的に接続されるものではないが、第1開口30bの近くで第1導電体25aと短絡すると、第1導電体25aを流れるべき電流が第2導電体30aに流れ込んで抵抗素子Rの抵抗値が設計よりも増える恐れがある。

【0171】

その点に鑑み、本実施形態では、第2開口29aの直径を第1開口30bのそれよりも小さくした。これによれば、点線円内に示すように、第1開口30bの側面と第1導電体25aとの間に第2絶縁膜26が張り出した構造となるので、第2実施形態と同様に第1導電体25aと第2導電体30aとの短絡が生じることはない。その結果、第1、第2導電体25a、30a同士の短絡に伴う抵抗素子Rの抵抗値のばらつきを抑制でき、その抵抗値を設計通りにすることができる。

【0172】

また、上記した本実施形態では、第1実施形態で図8(b)、図9(a)を参照して説明したように、トランジスタの閾値調整用の不純物領域22a、23bをイオン注入で形成する際にスルー膜として使用した第1、第2絶縁膜24、26を除去するのと同時に、第1周辺回路Iのコンタクト領域I上のONO膜よりなる第2絶縁膜26を除去する。そのため、工程数の増大を招かずにコンタクト領域CR上の第2絶縁膜を選択的に除去することが可能となる。

【0173】

更に、第1実施形態と同様に、第1、第2絶縁膜24、26を除去する工程では、第2周辺回路領域IIIのエッチング量の方が第1周辺回路領域Iのそれよりも多い。従って、この工程のエッチング量を第2周辺回路領域IIIにおけるそれに合わせることで、コンタクト領域CR上での第2絶縁膜26を完全に除去しながら、第2周辺回路領域IIIにおけるエッチングが過剰になるのを防止することができ、第2周辺回路領域IIIの素子分離絶縁膜21がエッチングされるのを防ぐことができる。

【0174】

(5)第4実施形態

第1実施形態では、第1周辺回路領域Iに第2導電体30aを残存させたが、これを途中で除去するようにしたのが本実施形態である。

【0175】

図32〜図38は、本発明の第4実施形態に係る半導体装置の製造途中の断面図である。これらの図において、第1実施形態で説明した要素については第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0176】

まず、第1実施形態で説明した図9(a)の工程を行うことにより、図32(a)に示すように、第2絶縁膜26をパターニングする。但し、第1実施形態では、コンタクト領域CR以外の第1周辺回路領域Iにもパターニング後の第2絶縁膜26を残していたが、本実施形態では、パターニングによりセル領域IIにのみ第2絶縁膜26を残す。

【0177】

次いで、図32(b)に示すように、第1実施形態と同じ酸化条件を採用して、第1周辺回路領域I上のポリシリコンよりなる第1導電体25と第2周辺回路領域III上のシリコン基板20とを熱酸化する。そして、これにより形成された熱酸化膜を第3絶縁膜28とし、その第3絶縁膜28と第2絶縁膜26とを絶縁体29とする。

【0178】

その後に、第1実施形態の図10(a)と同じ工程を行うことにより、図33(a)に示すように、第1導電膜25、絶縁体29、及び第2導電体30のそれぞれをパターニングする。その結果、第1周辺回路領域Iには、第1導電体25a、絶縁体29を構成する第2絶縁膜28、及び第2導電体30aの積層体が形成される。そして、セル領域II上には、後でフラッシュメモリセルを構成することになるフローティングゲート25d、中間絶縁膜29d、及びコントロールゲート30dの積層体が形成されることになる。

【0179】

次に、図33(b)に示すように、第1実施形態の図10(b)と同じようにして、第3レジストパターン31の第3窓31aを通じてシリコン基板20にn型不純物をイオン注入する。そのイオン注入により、フローティングゲート25dとゲート部25cのそれぞれの側方のシリコン基板20に、第1〜第4n型ソース/ドレインエクステンション32a〜32dが形成される。その後に、第3レジストパターン31を除去する。

【0180】

続いて、図34(a)に示すように、全面に窒化シリコン膜を形成した後、その窒化シリコン膜をエッチバックして、第2導電体30bとフローティングゲート25dのそれぞれの側面に第1絶縁性サイドウォール33として残す。

【0181】

次に、図34(b)に示す断面構造を得るまでの工程について説明する。

【0182】

まず、各領域I〜IIIの上に第4レジストパターン34を形成する。その第4レジストパターン34は、セル領域IIを覆うと共に、第2周辺回路領域III上においてゲート電極形状を有する。一方、第1周辺回路領域Iは、その第4レジストパターン34で覆われずに露出する。

【0183】

次いで、Cl2とO2との混合ガスをエッチングガスとして採用し、第4レジストパターン34をマスクにしながら、第1周辺回路領域Iの第2導電体30aと第2周辺回路領域IIの第2導電膜30とをプラズマエッチングする。その結果、第1周辺回路領域Iでは、第2導電体30aの全てが除去されて第2絶縁膜28が露出すると共に、第1絶縁性サイドウォール33が第2絶縁膜28の上面よりも突出し、その側面33aが露出した構造が得られる。そして、第2周辺回路領域IIIでは、第2導電膜30がパターニングされて第1、第2ゲート電極30f、30gとなる。

【0184】

この後に、第4レジストパターン34を除去する。

【0185】

続いて、図35(a)に示すように、第5レジストパターン35の第5窓35aを通じてn型不純物をシリコン20にイオン注入して、第1ゲート電極30fの側方のシリコン基板20に第5、第6n型ソース/ドレインエクステンション32e、32fを形成する。その後に、第5レジストパターン35は除去される。

【0186】

次いで、図35(b)に示すように、第6レジストパターン36の第6窓36aを通じてp型不純物をシリコン20にイオン注入することにより、第2ゲート電極30gの側方のシリコン基板20に第1、第2p型ソース/ドレインエクステンション32g、32hを形成する。その後に、第6レジストパターン36は除去される。

【0187】

次に、図36(a)に示す断面構造を得るまでの工程について説明する。

【0188】

まず、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックすることにより、点線円内に示されるように、第2導電体30a(図34(a)参照)が除去されて露出していた第1絶縁性サイドウォール33の側面33aと第2絶縁膜28の上とに第2絶縁性サイドウォール37を形成する。その第2絶縁性サイドウォール37は、コントロールゲート30d、及び第1、第2ゲート電極30f、30gのそれぞれの側面にも形成される。

【0189】

そして、更にそのエッチバックを進めて、第2絶縁性サイドウォール37をマスクにしながら、パッド部25b上で絶縁体29を構成している第3絶縁膜28をエッチングする。これにより、パッド部25bの第3絶縁膜28がパターニングされて第3開口29bが形成され、点線円内に示すように、第2絶縁性サイドウォール37の曲面状の側面37aがその第3開口29bの側面に連続した構造が得られる。

【0190】

また、このエッチバックでは、第2絶縁性サイドウォール37がマスクとなって第1絶縁膜24がパターニングされ、その第1絶縁膜24がゲート部25cとフローティングゲート25dのそれぞれの下にゲート絶縁膜24a及びトンネル絶縁膜24bとして残る。

【0191】

更に、第2周辺回路領域IIIでは、第3絶縁膜28がパターニングされて第1、第2ゲート30f、30gの下にゲート絶縁膜28a、28bとして残る。

【0192】

続いて、第1実施形態で説明した図13(b)の工程と同様に、図36(b)に示すように、第7レジストパターン39をマスクとするイオン注入により、ゲート部25c、フローティングゲート25d、第1ゲート電極30fのそれぞれの側方のシリコン基板20に第1〜第6n型ソース/ドレイン領域38a〜38fを形成する。その後に、第7レジストパターン39を除去する。

【0193】

この工程により、第1実施形態と同様に、参照トランジスタTRref、フラッシュメモリセルFL、及びn型MOSトランジスタTRnの基本構造が完成したことになる。

【0194】

次に、第1実施形態で説明した図14(a)の工程と同様に、図37(a)に示すように、第8レジストパターン40をマスクとするイオン注入により第2ゲート電極30gの側方のシリコン基板20に第1、第2p型ソース/ドレイン領域38g、38hを形成する。そのイオン注入が終了した後、第8レジストパターン40は除去される。そして、この工程により、第2周辺回路領域IIIには、第1実施形態で説明したp型MOSトランジスタTRnの基本構造が完成する。

【0195】

続いて、第1実施形態の図14(b)の工程を行うことにより、図37(b)に示すように、各ソース/ドレイン領域38a〜38hの表層に第1〜第8コバルトシリサイド層41a〜41hを形成し、更にその上の第1層間絶縁膜44をパターニングして第1〜第9ホール44a〜44iを形成する。

【0196】

次いで、第1実施形態の図15(a)の工程を行うことにより、図38に示すように、各ソース/ドレイン領域38a〜38hと電気的に接続される第1〜第9導電性プラグ45a〜45iを第1〜第9ホール44a〜44iの中に形成する。

【0197】

この後は、第2層間絶縁膜と銅配線の形成工程を行うが、これらの工程は第1実施形態と同様なので、その説明は省略する。

【0198】

以上説明した本実施形態によれば、第1〜第3実施形態で説明した理由により、図32(a)に示した工程において、余分なマスク工程を追加しないでコンタクト領域CR上の第2絶縁膜26を除去できると共に、その第2絶縁膜26を除去する際に素子分離絶縁膜21がエッチングされるのを防ぐことができる。

【0199】

更に、本実施形態では、図34(b)に示した工程において、第1周辺回路領域Iを覆わないように第4レジストパターン34を形成し、第1周辺回路領域I上の第2導電体30aをエッチングして除去するようにした。これによれば、第1実施形態の図11(b)の工程のように第4レジストパターン34に第4窓34aを形成しないので、その第4窓34aと第2導電体30aとのアライメントを考慮する必要が無く、第4レジストパターン34の位置合わせ精度を緩和することができる。更に、第4窓34aを形成しない分だけ第4レジストパターン34の形状が単純化されるので、第4レジストパターン34を形成するのに必要な露光データが第1実施形態よりも少なくなり、その露光データを作成する手間を減らすことができる。

【0200】

(6)第5実施形態

図39、図40は、本発明の第5実施形態に係る半導体装置の製造途中の断面図である。これらの図において、第1実施形態で説明した要素については第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0201】

最初に、図39(a)に示す断面構造を得るまでの工程について説明する。

【0202】

まず、第1実施形態の図9(b)の工程を行うことにより、図39(a)に示すように、第2、第3絶縁膜26、28の上に厚さ約180nmのポリシリコン膜を第2導電膜30として形成する。

【0203】

その後、本実施形態では、第1、第2導電膜25、30のパターニングの際に露光光の反射を防止する反射防止膜50として70nm以上の厚さの窒化シリコン膜を形成する。

【0204】

次に、図39(b)に示すように、反射防止膜50の上に第2レジストパターン18を形成し、この第2レジストパターン18をマスクにして、反射防止膜50、第1、第2導電膜25、30、及び絶縁体29をエッチングする。そのエッチングでは、ポリシリコンよりなる第1、第2導電膜25、30のエッチングガスとしてCl2とO2との混合ガスが使用される。また、窒化シリコン膜よりなる反射防止膜50とONO膜よりなる第2絶縁膜26のエッチングガスとしてはCH3とO2との混合ガスが使用される。

【0205】

このようなエッチングの結果、第1周辺回路領域I上の第1、第2導電膜25、30がそれぞれ第1、第2導電体25a、30aとされ、セル領域II上の第1、第2導電膜25、30と絶縁体29とがそれぞれフローティングゲート25d、コントロールゲート30d、中間絶縁膜29dとされる。

【0206】

この後に、第2レジストパターン18は除去される。

【0207】

続いて、図40(a)に示すように、70nm以上の厚い反射防止膜50をマスクにし、その反射防止膜50によってコントロールゲート30dと第2周辺回路領域IIIの第2導電膜30にイオンが注入されるのを防ぎながら、n型不純物のAsを加速エネルギ50KeV、ドーズ量6×1015cm-3の条件でシリコン基板20にイオン注入する。それにより、フローティングゲート25dとゲート部25cのそれぞれの側方のシリコン基板20には、第1〜第4n型ソース/ドレインエクステンション32a〜32dが形成される。

【0208】

この後は、第1実施形態で説明した図11(a)〜図15(b)と同じ工程を行うことにより、本実施形態に係る半導体装置の基本構造を完成させる。

【0209】

以上説明した本実施形態では、図39(a)で説明したように、コントロールゲート30d上の反射防止膜50が70nm以上の厚みを有するので、第1〜第4n型ソース/ドレインエクステンション32a〜32dをイオン注入で形成する際、反射防止膜50でイオンをブロックすることができる。そのため、そのイオン注入の際、第2導電膜30にn型不純物が注入されるのを防止するために第1実施形態で形成した第3レジストパターン31(図10(b)参照)が不要となるので、その第3レジストパターンの形成工程の分だけ工程を簡略化することが可能となる。

【0210】

図41は、窒化シリコン膜よりなる反射防止膜50の厚さによって、As-イオンがどの程度ブロックされるのかを調査して得られたグラフである。特に、この調査では、図14(a)の工程で低抵抗化のために第2ゲート電極30gにイオン注入されたB+の濃度と、図40のイオン注入工程で反射防止膜50を通り抜けて第2ゲート電極30gに注入されたAs-との比の百分率を求めた。図41の縦軸はその百分率を表す。

【0211】

図41に示されるように、窒化シリコン膜よりなる反射防止膜50の厚さを70nm以上とすることで、殆ど全てのAs-が反射防止膜50によってブロックされるのが理解される。

【0212】

(7)第6実施形態

図42〜図66は、本発明の第6実施形態に係る半導体装置の製造途中の断面図であり、図67〜図69はその平面図である。

【0213】

本実施形態では、第1実施形態と同様にFPGA等のロジック混載メモリが作製されるが、第1実施形態よりもトランジスタを大幅に多く形成するので、ロジック混載メモリの機能も大幅に向上させることができる。

【0214】

最初に、図42に示す断面構造を得るまでの工程について説明する。

【0215】

まず、第1、第2周辺回路領域I、IIIとセル領域IIとが画定されたシリコン基板60にSTI用の溝60aを形成し、その溝60a内に素子分離絶縁膜61として酸化シリコンを形成する。その後に、シリコン基板60の全面を熱酸化して厚さ約10nmの熱酸化膜を形成し、それを犠牲絶縁膜59とする。

【0216】

なお、シリコン基板60の第2周辺回路領域IIIは、高電圧トランジスタ形成領域IIIH、中電圧トランジスタ形成領域IIIM、及び低電圧トランジスタ形成領域IIILに更に細分される。

【0217】

次に、図43に示すように、高電圧トランジスタ形成領域IIIHにおいてn型MOSトランジスタが形成される領域とセル領域IIとが露出する第1窓62aを備えた第1レジストパターン62を犠牲絶縁膜59の上に形成する。その第1窓62aには、第1周辺回路領域Iの一部も露出する。そして、その第1窓62aを通じてn型不純物のP+イオンをシリコン基板60にイオン注入し、シリコン基板60の深部に第1nウエル63を形成する。そのイオン注入の条件は特に限定されないが、本実施形態では加速エネルギ2MeV、ドーズ量2×1013cm-3を採用する。

【0218】

この後に、第1レジストパターン62を除去する。

【0219】

次いで、図44に示すように、犠牲絶縁膜59の上にフォトレジストを塗布し、それを露光、現像することにより第2レジストパターン58を形成する。その第2レジストパターン58は、高電圧トランジスタ形成領域IIIHにおいてn型MOSトランジスタが形成される領域とセル領域IIとが露出する第2窓58aを有する。第1周辺回路領域Iの一部もその第2窓58aから露出する。

【0220】

また、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILにおいてn型MOSトランジスタが形成される領域上の第2レジストパターン58にはそれぞれ第3、第4窓58b、58cが形成される。

【0221】

そして、このような第2レジストパターン58をマスクにして、1回目の条件を加速エネルギ400KeV及びドーズ量1.5×1013cm-3とし、2回目の条件を加速エネルギ100KeV、ドーズ量2×1012cm-3とするイオン注入でシリコン基板60にp型不純物のB+イオンを注入することにより、第1〜第3pウエル64〜66を形成する。

【0222】

高電圧トランジスタ形成領域IIIHには、閾値電圧の高いn型MOSトランジスタと閾値電圧の低いn型MOSトランジスタとが形成されるが、後者の閾値電圧が上記の第1pウエル64によって制御される。

【0223】

この後に、第2レジストパターン58を除去する。

【0224】

次に、図45に示すように、高電圧トランジスタ形成領域IIIHにおいて閾値電圧の高いn型MOSトランジスタが形成される領域上に第5窓67aを有する第3レジストパターン67を各領域I〜IIIの上に形成する。その第3レジストパターン67は、第5窓67aの他に、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILにおいてn型MOSトランジスタが形成される領域上に第6、第7窓67b、67cが形成される。

【0225】

そして、この第3レジストパターン67をマスクにして、加速エネルギ100KeV、ドーズ量6×1012cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入することにより、第4〜第6pウエル68〜70を形成する。

【0226】

これらのウエルのうち、第4pウエル68は、高電圧トランジスタ形成領域IIIHに後で形成される閾値電圧の高いn型MOSトランジスタの閾値電圧を制御するものである。一方、第5、第6pウエル69、70は、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILに後で形成されるn型MOSトランジスタのチャネルストップ層としての機能を有する。

【0227】

その後に、第3レジストパターン67を除去する。

【0228】

続いて、図46に示すように、各領域IIIH、IIIM、及びIIILにおいてp型MOSトランジスタが形成される領域上に第8〜第10窓71a〜71cを有する第4レジストパターン71を各領域I〜III上に形成する。

【0229】

そして、この第4レジストパターン71をマスクにして、1回目の条件を加速エネルギ600KeV及びドーズ量1.5×1013cm-3とし、2回目の条件を加速エネルギ240KeV、ドーズ量3×1012cm-3とするイオン注入により、シリコン基板60にn型不純物のP+イオンを注入して第2〜第4nウエル72〜74を形成する。

【0230】

高電圧トランジスタ形成領域IIIHには、閾値電圧の高いp型MOSトランジスタと閾値電圧の低いp型MOSトランジスタとが形成されるが、後者の閾値電圧が上記の第2pウエル72によって制御される。

【0231】

この後に、第4レジストパターン71を除去する。

【0232】

次いで、図47に示すように、高電圧トランジスタ形成領域IIIHにおいて閾値電圧の高いp型MOSトランジスタが形成される領域上に第11窓75aを有する第5レジストパターン75を各領域I〜IIIの上に形成する。その第5レジストパターン75には、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILにおいてp型MOSトランジスタが形成される領域上に第12、第13窓75b、75cが形成される。

【0233】

そして、この第5レジストパターン75をマスクにして、加速エネルギ240KeV、ドーズ量6.5×1012cm-3の条件でシリコン基板60にn型不純物のP+イオンをイオン注入することにより、第5〜第7nウエル76〜78を形成する。

【0234】

これらのウエルのうち、第5nウエル76は、高電圧トランジスタ形成領域IIIHに後で形成される閾値電圧の高いp型MOSトランジスタの閾値電圧を制御するものである。一方、第6、第7nウエル77、78は、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILに後で形成されるp型MOSトランジスタのチャネルストップ層としての機能を有する。

【0235】

この後に、第5レジストパターン75を除去する。

【0236】

続いて、図48に示すように、第1周辺回路領域Iとセル領域II上に第14窓79aを備えた第6レジストパターン79を各領域I〜III上に形成する。そして、その第6レジストパターン79をマスクにして、加速エネルギ40KeV、ドーズ量6×1013cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入することにより、第1p型不純物拡散領域80を形成する。その第1p型不純物拡散領域80は、セル領域IIに後で形成されるフラッシュメモリセルの閾値電圧を制御する役割を担う。

【0237】

この後に、第6レジストパターン79を除去する。

【0238】

次に、図49に示す断面構造を得るまでの工程について説明する。

【0239】

まず、フッ酸溶液によるウエットエッチングで犠牲絶縁膜59を除去し、シリコン基板60の清浄面を露出させる。そして、ArとO2との混合雰囲気において基板温度を900℃〜1050℃とする熱処理条件でシリコン基板60の表面に熱酸化膜を厚さ約10nmに形成し、それを第1絶縁膜81とする。その第1絶縁膜81は、後でフラッシュメモリセルのトンネル絶縁膜となる。

【0240】

次に、図50に示す断面構造を得るまでの工程について説明する。

【0241】

まず、SiH4とPH3とを反応ガスとして使用する減圧CVD法により、第1絶縁膜81の上に、in-situでリンがドープされたポリシリコン膜を厚さ約90nmに形成し、それを第1導電膜82とする。次いで、フォトリソグラフィによりその第1導電膜82をパターニングして第2周辺回路領域IIIから除去する。なお、セル領域IIにおける第1導電膜82は、このパターニングによりワードライン方向に直行した帯状となる。

【0242】

次に、第1導電膜82上と、第2周辺回路領域III上の第1絶縁膜81上とに、減圧CVD法を用いて酸化シリコン膜と窒化シリコン膜とをこの順にそれぞれ厚さ5nm、10nmに形成する。更に、O2雰囲気中において、基板温度約950℃で窒化シリコン膜の表面を酸化し、その表面に約30nmの酸化シリコン膜を形成する。これにより、酸化シリコン膜、窒化シリコン膜、及び酸化シリコン膜をこの順に積層してなるONO膜が第2絶縁膜83として全面に形成される。

【0243】

なお、ONO膜中の窒化シリコン膜を酸化する際の熱処理や、図49で説明した第1絶縁膜81を形成する際の熱処理により、シリコン基板60に形成されていたウエル中の不純物が約0.1〜0.2μm以上拡散し、ウエルの不純物分布がブロードとなる。

【0244】

続いて、図51に示すように、中電圧トランジスタ形成領域IIIMにおいてn型MOSトランジスタが形成される領域上に第15窓84aを備えた第7レジストパターン84を各領域I〜III上に形成する。そして、その第7レジストパターン84をマスクにし、第1、第2絶縁膜81、83をスルー膜にしながら、加速エネルギ30KeV、ドーズ量5×1012cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入する。これにより、中電圧トランジスタ形成領域IIIMには、n型MOSトランジスタの閾値電圧を調節するための第2p型不純物拡散領域85が形成されたことになる。

【0245】

その後に、第7レジストパターン84を除去する。

【0246】

次に、図52に示すように、今度は中電圧トランジスタ形成領域IIIMにおいてp型MOSトランジスタが形成される領域上に第16窓86aを備えた第8レジストパターン86を各領域I〜III上に形成する。更に、その第8レジストパターン86をマスクにし、第1、第2絶縁膜81、83をスルー膜にしながら、加速エネルギ150KeV、ドーズ量3×1012cm-3の条件でシリコン基板60にn型不純物のAs-イオンをイオン注入する。これにより、中電圧トランジスタ形成領域IIIMには、p型MOSトランジスタの閾値電圧を調節するための第1n型不純物拡散領域87が形成されたことになる。

【0247】

その後に、第7レジストパターン84を除去する。

【0248】

次いで、図53に示すように、第2絶縁膜83の上にフォトレジストを塗布し、それを露光、現像することにより、低電圧トランジスタ形成領域IIILの上に第17窓88aを備えた第9レジストパターン88を形成する。

【0249】

低電圧トランジスタ形成領域IIILには、高閾値電圧と低閾値電圧の二つのn型MOSトランジスタと、高閾値電圧と低閾値電圧の二つのp型MOSトランジスタとが後で形成されるが、上記した第17窓88aは、そのうちの高閾値電圧のn型MOSトランジスタが形成される領域の上に形成される。

【0250】

そして、第1、第2絶縁膜81、83をスルー膜にしながら、第17窓88aを通じて加速エネルギ10KeV、ドーズ量5×1012cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入する。これにより、低電圧トランジスタ形成領域IIILには、高閾値電圧のn型MOSトランジスタの閾値電圧調節用の第3p型不純物拡散領域89が形成されたことになる。

【0251】

その後に、第9レジストパターン88は除去される。

【0252】

続いて、図54に示すように、低電圧トランジスタ形成領域IIILにおいて高閾値電圧のp型MOSトランジスタが形成される領域上に第18窓90aを備えた第10レジストパターン90を各領域I〜IIIの上に形成する。その後、第1、第2絶縁膜81、83をスルー膜にしながら、第17窓90aを通じて加速エネルギ100KeV、ドーズ量5×1012cm-3の条件でシリコン基板60にn型不純物のAs-イオンをイオン注入して、高閾値電圧のp型MOSトランジスタの閾値電圧調節用の第2n型不純物拡散領域91を形成する。

【0253】

このイオン注入を終了後、第10レジストパターン90を除去する。

【0254】

ここまでの工程により、第2周辺回路領域IIIにおけるトランジスタの閾値電圧を制御するための拡散領域85、87、89、91の形成が終了したので、これらの拡散領域をイオン注入で形成する際にスルー膜として使用した第2周辺回路領域IIIの第1、第2絶縁膜81、83はこれ以降の工程では不要となる。

【0255】

そこで、次の図55に示す工程では、その第2周辺回路領域IIIの第1、第2絶縁膜81、83を除去する。これを行うには、図55に示すように、セル領域IIを覆う第11レジストパターン92を第2絶縁膜83の上に形成する。第1周辺回路領域Iにおける第1導電膜82のコンタクト領域CRと、第2周辺回路IIIは、その第11レジストパターン92に覆われずに露出する。

【0256】

次いで、第11レジストパターン92をマスクとして使用しながら、CH3とO2との混合ガスをエッチングガスとするプラズマエッチングと、その後のHF溶液によるウエットエッチングにより、コンタクト領域CR上の第2絶縁膜83と、第2周辺回路IIIの第1、第2絶縁膜81、83とをエッチングして除去する。これにより、コンタクト領域CR以外の領域のみに第2絶縁膜83が残ると共に、第2周辺回路領域IIIのシリコン基板60が露出することになる。

【0257】

続いて、酸素アッシングによって第11レジストパターン92を除去した後、ウエット処理によりシリコン基板60の表面を洗浄する。

【0258】

次に、図56に示す断面構造を得るまでの工程について説明する。

【0259】

まず、基板温度を850℃とする酸化条件を採用し、第2周辺回路領域IIIに露出しているシリコン基板60の表面を13nmの厚さだけ熱酸化して、それにより形成された熱酸化膜を第3絶縁膜94とする。この熱酸化では、第2絶縁膜83で覆われずに露出している第1導電膜82のコンタクト領域CR上にも熱酸化膜よりなる第3絶縁膜94が形成される。

【0260】

次いで、セル領域IIと高電圧トランジスタ形成領域IIIHの上に第12レジストパターン93を形成する。そして、この第12レジストパターン93をマスクとして使用しながら、HF溶液を用いたウエットエッチングにより、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIIL上の第3絶縁膜94をエッチングして除去する。また、このエッチングでは、第1導電膜82のコンタクト領域CR上の熱酸化膜よりなる第3絶縁膜94もエッチングされ、それによりコンタクト領域CRが露出する。

【0261】

その後に、第12レジストパターン93を除去する。

【0262】

次に、図57に示す断面構造を得るまでの工程について説明する。

【0263】

まず、酸素雰囲気中で基板温度を約850℃とする酸化条件を採用し、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILにおいて露出しているシリコン基板60の表面を約6nmの厚さだけ熱酸化して、それにより形成された熱酸化膜を第4絶縁膜96とする。その第4絶縁膜96は、先の第3絶縁膜94と同様に、第1導電膜82のコンタクト領域CR上にも形成される。

【0264】

続いて、セル領域II、高電圧トランジスタ形成領域IIIH、及び中電圧トランジスタ形成領域IIIMの上に第13レジストパターン95を形成する。そして、この第13レジストパターン95をマスクとして使用しながら、HF溶液を用いたウエットエッチングにより、コンタクト領域CR上と低電圧トランジスタ形成領域IIIL上の第4絶縁膜96をエッチングして除去する。

【0265】

その後に、第13レジストパターン95を除去する。

【0266】

次に、図58に示す断面構造を得るまでの工程について説明する。

【0267】

まず、酸素雰囲気中で基板温度を約850℃とする酸化条件を採用して、第2〜第4絶縁膜83、94、96で覆われていない部分のシリコンを約2.2nmの厚さだけ熱酸化する。これにより、ポリシリコンよりなる第1導電膜82のコンタクト領域CRと、低電圧トランジスタ形成領域IIILのシリコン60のそれぞれの表面に、厚さ約2.2nmの熱酸化膜が第5絶縁膜97として形成される。その第5絶縁膜97は第2絶縁膜83と隣接して形成され、これらの第2、第5絶縁膜83、97により絶縁体99が構成される。なお、このようにしてコンタクト領域CRに形成された第5絶縁膜97の厚さは第2絶縁膜83よりも格段に薄くなる。

【0268】

また、第5絶縁膜97を熱酸化によって形成した結果、第3絶縁膜94と第4絶縁膜96の最終的な厚さはそれぞれ16nm及び7nmとなる。

【0269】

その後に、SiH4を反応ガスとして使用する減圧CVD法により、厚さ約180nmのノンドープのポリシリコン膜を第2導電膜100として全面に形成する。

【0270】

次に、図59に示す断面構造を得るまでの工程について説明する。

【0271】

まず、第2導電膜100上にフォトレジストを塗布し、それを露光、現像することにより、第14レジストパターン101を形成する。次に、この第14レジストパターン101をエッチングマスクとして使用して第1、第2導電膜82、100、及び絶縁体99をパターニングする。そのパターニングはプラズマエッチングチャンバ内で行われ、ポリシリコンよりなる第1、第2導電膜82、100のエッチングガスとしてはCl2とO2との混合ガスが使用され、絶縁体99を構成するONO膜よりなる第2絶縁膜83のエッチングガスとしてはCH3とO2との混合ガスが使用される。

【0272】

このようなパターニングの結果、第2導電膜100を第2周辺回路領域IIIに残しながら、第1周辺回路領域I上の第1、第2導電膜82、100がそれぞれ第1、第2導電体82a、100aとされ、セル領域II上の第1、第2導電膜82、100と絶縁体29とがそれぞれフローティングゲート82d、コントロールゲート100d、中間絶縁膜99dとされる。

【0273】

この後に、第14レジストパターン101は除去される。

【0274】

図67は、この工程を終了後の平面図であり、上の図59は、図67のG−G線に沿う断面図に相当する。但し、図67では、構成を見易くするために、第1周辺回路領域Iにおける第2導電体100aを省くと共に、第2周辺回路領域IIIを省略している。

【0275】

図67に示されるように、第1導電体82aはパッド部82bとゲート部82cとで構成される。

【0276】

次に、図60に示す断面構造を得るまでの工程について説明する。

【0277】

まず、フローティングゲート82dとコントロールゲート100dのそれぞれの側面を熱酸化することにより、これらの側面に極薄い熱酸化膜(不図示)を形成する。その熱酸化膜は、最終的に形成されるフラッシュメモリセルのリテンション特性を向上させる役割を担う。

【0278】

その後に、第2導電体100a、コントロールゲート100d、及び第2導電膜100を覆う不図示のレジストパターンを形成し、そのレジストパターンをマスクにしてシリコン基板60にn型不純物としてAs+をイオン注入する。そのイオン注入の条件は特に限定されないが、本実施形態では例えば加速エネルギ50KeV、ドーズ量6.0×1014cm-3が採用される。そのようなイオン注入の結果、第1導電体82aとフローティングゲート82dのそれぞれの側方には、第2〜第4n型ソース/ドレインエクステンション102b〜102dが形成されることになる。

【0279】

その後に、上記のレジストパターンを除去し、フローティングゲート82dとコントロールゲート100dの側面を再度熱酸化し、不図示の熱酸化膜を形成する。

【0280】

次に、図61に示すように、窒化シリコン膜を全面に形成した後、それをエッチバックして、第2導電体100aとフローティングゲート82dのそれぞれの側面に第1絶縁性サイドウォール103として残す。

【0281】

次に、図62に示すように、フォトリソグラフィにより第1周辺回路領域I上の第2導電体100aと第2周辺回路領域III上の第2導電膜100とをパターニングする。これにより、コンタクト領域CR上の第2導電体100aが除去されて第1開口100bが形成されると共に、第2周辺回路領域IIIでは、パターニングされた第2導電膜100よりなる第1〜10ゲート電極100e〜100nが形成される。

【0282】

続いて、図63に示すように、第1〜10ゲート電極100e〜100nと不図示のレジストパターンとをマスクにしながらシリコン基板60にAs等のn型不純物をイオン注入することにより、図示のような第5〜第14n型ソース/ドレインエクステンション102e〜102nを形成する。また、これと同様にB等のp型不純物をシリコン基板60にイオン注入することにより、図示のような第1〜第10p型ソース/ドレインエクステンション102p〜102yを形成する。なお、上記のイオン注入におけるn型不純物とp型不純物との打ち分けは、不図示のレジストパターンを用いて行われ、イオン注入が終了後にそのレジストパターンは除去される。

【0283】

次に、図64に示す断面構造を得るまでの工程について説明する。

【0284】

まず、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックして、第2導電体100a、コントロールゲート100d、及び第1〜10ゲート電極100e〜100nの側面に第2絶縁性サイドウォール104を形成する。そして、そのエッチバックの後にオーバーエッチを行うことにより、第2絶縁性サイドウォール104をマスクにしながら、パッド部25b上で絶縁体99を構成している第5絶縁膜97をエッチングする。これにより、第1開口100bよりも直径が小さな第2開口99aが絶縁体99に形成されると共に、その第2開口99aからコンタクト領域CRが露出し、第2周辺回路領域IIのシリコン基板60が露出する。

【0285】

また、このエッチバックにより、第2絶縁性サイドウォール104がマスクとなって第1絶縁膜81がパターニングされ、その第1絶縁膜81が第1導電体82aとフローティングゲート82dのそれぞれの下にゲート絶縁膜81a及びトンネル絶縁膜81bとして残る。

【0286】

更に、第2周辺回路領域IIIでは、第1〜10ゲート電極100e〜100nがマスクとなって第3〜第5絶縁膜94、96、97がパターニングされ、これらの絶縁膜がゲート絶縁膜94a〜94d、96a、96b、97a〜97dとして残される。

【0287】

その後、第2絶縁性サイドウォール104、コントロールゲート100d、及び第1〜10ゲート電極100e〜100nをマスクとするイオン注入により、図示のような第1〜第14n型ソース/ドレイン領域105a〜105nと、第1〜第10p型ソース/ドレイン領域105p〜105yとを形成する。このイオン注入におけるn型不純物とp型不純物との打ち分けは、不図示のレジストパターンを用いて行われ、イオン注入が終了後にそのレジストパターンは除去される。

【0288】

ここまでの工程により、高電圧トランジスタ形成領域IIIHと低電圧トランジスタ形成領域IIILのそれぞれには、センスアンプ等のロジック回路を構成するn型MOSトランジスタTRn(Low Vth)、TRn(High Vth)と、p型MOSトランジスタTRp(Low Vth)、TRp(High Vth)とが形成される。各トランジスタに付されたLow VthとHigh Vthは、そのトランジスタの閾値電圧の高低を示すものである。

【0289】

このように閾値電圧が高いものと低いものとを混在させると、閾値電圧が低いトランジスタを使用することで回路を高速に動作させることができるとともに、スタンバイ時にはその閾値電圧が低いトランジスタをオフ状態にし、代わりに閾値電圧が高いトランジスタを使用することで、スタンバイ中に発生するリーク電流を抑制することができる。

【0290】

また、上記のトランジスタのうち、高電圧トランジスタ形成領域IIIHに形成されるものは、ゲート電極に印加される電圧が5Vの高電圧トランジスタとなり、低電圧トランジスタ形成領域IIILに形成されるものは1.2Vの低電圧トランジスタとなる。

【0291】

そして、中電圧トランジスタ形成領域IIIMには、ゲート電極への印加電圧が共に2.5Vのn型MOSトランジスタTRnとp型MOSトランジスタTRpとが図示のように形成される。

【0292】

一方、セル領域IIでは、コントロールゲート100d、中間絶縁膜99d、フローティングゲート82d、トンネル絶縁膜81b、及び第3、第4n型ソース/ドレイン領域105c、105dで構成されるフラッシュメモリセルFLが形成される。

【0293】

図68は、この工程を終了後の平面図であり、先の図64は、図68のH−H線に沿う断面図に相当する。但し、図68では、構成を見易くするために、第2周辺回路領域IIIを省略している。

【0294】

図68に示されるように、第1導電体82aのゲート部82cの側方のシリコン基板60には第1n型ソース/ドレイン領域105aが形成されている。そして、第1、第2n型ソース/ドレイン領域105a、105b、ゲート絶縁膜81a(図64参照)、及びゲート部82cにより参照トランジスタTRrefが構成される。

【0295】

次に、図65に示す断面構造を得るまでの工程について説明する。

【0296】

まず、スパッタ法により全面にコバルト膜を厚さ約8nmに形成した後、そのコバルト膜をアニールしてシリコンと反応させる。そして、素子分離絶縁膜61等の上の未反応のコバルト膜をウエットエッチングして除去し、シリコン基板60の表層にコバルトシリサイド層106b〜106yを形成する。

【0297】

続いて、CVD法によりシリコン窒化膜を厚さ約50nmに形成し、それをエッチングストッパ膜107とする。次いで、そのエッチングストッパ膜107の上にCVD法により第6絶縁膜108として酸化シリコン膜を形成し、エッチングストッパ膜107と第6絶縁膜108とを第1層間絶縁膜109とする。その第6絶縁膜108は、シリコン基板60の平坦面上で約1μmの厚さを有する。

【0298】

続いて、CMP法により第1層間絶縁膜109の上面を研磨して平坦化する。その後に、フォトリソグラフィにより第1層間絶縁膜109をパターニングして、第1、第3〜25ホール109a、109c〜109yを形成する。これらのホールのうち、第1ホール109aは、第1導電体82aのコンタクト領域CR上に位置しており、第1、第2開口100b、99aの内側に形成される。また、残りの第3〜第25ホール100c〜100yは、それぞれコバルトシリサイド層106b〜106yの上に形成される。

【0299】

更に、第1、第3〜25ホール109a、100c〜100y内と第1層間絶縁膜109上とに、スパッタ法によりTi膜とTiN膜とをこの順に形成し、それらをグルー膜とする。そして、六フッ化タングステンを反応ガスとして使用するCVD法により、そのグルー膜の上にW膜を形成して第1、第3〜25ホール109a、100c〜100y内を完全に埋め込む。そして、第1層間絶縁膜109の上面に形成された余分なW膜とグルー膜とをCMP法により除去し、それらを第1、第3〜25ホール109a、100c〜100y内に第1、第3〜25導電性プラグ110a、110c〜110yとして残す。

【0300】

次に、図66に示す断面構造を得るまでの工程について説明する。

【0301】

最初に、塗布型の低誘電率絶縁膜111を全面に形成した後、その上にカバー絶縁膜112として酸化シリコン膜を形成し、低誘電率絶縁膜111とカバー絶縁膜112とを第2層間絶縁膜113とする。

【0302】

次いで、フォトリソグラフィによりその第2層間絶縁膜113をパターニングして、配線溝113aを形成する。

【0303】

その後、スパッタ法により全面にCu膜をシード層として形成し、このシード層に給電を行うことによりシード層上に電解銅めっき膜を形成し、その銅めっき膜により各配線溝113aを完全に埋め込む。その後に、CMP法を用いて、第2層間絶縁膜113の上に形成された余分なシード層と銅めっき膜とを除去し、それらを各配線溝113aの中に銅配線114として残す。

【0304】

図69は、この工程を終了後の平面図であり、先の図67は、図69のJ−J線に沿う断面図に相当する。但し、図69では、各層の平面レイアウトを見やすくするために、第2周辺回路領域IIIを省くと共に、銅配線114と第2層間絶縁膜113とを省略してある。

【0305】

これに示されるように、第1導電体82aのゲート部82cの側方のシリコン基板20には、第2n型ソース/ドレイン領域が形成されており、その上に第2導電性プラグが電気的に接続されている。その第2導電性プラグは、第2層間絶縁膜に形成された第2ホール内に形成されており、残りの第1、第3〜25導電性プラグ110a、110c〜110yと同じプロセスによって形成される。

【0306】

以上により、本実施形態に係る半導体装置の基本構造が完成した。

【0307】

その半導体装置の製造方法によれば、図51〜図54に示したように、第2絶縁膜83をスルー膜にしながら、中電圧トランジスタ形成領域IIIMと低電圧トランジスタ形成領域IIILのそれぞれに閾値電圧調節用のウエル85、87、89、91を形成する。そして、図55に示したように、そのイオン注入が終了してスルー膜としての役割を終えた第2絶縁膜83を第2周辺回路領域IIで除去するのと同時に、第1導電体82aのコンタクト領域CR上の第2絶縁膜83も除去する。このように、本実施形態では、スルー膜の除去工程が、コンタクト領域CR上の第2絶縁膜83の除去工程を兼ねるので、余計なマスク工程を追加すること無しに、コンタクト領域CR上の第2絶縁膜83を除去することが可能となる。

【0308】

以下に、本発明の特徴を付記する。

【0309】

(付記1) 半導体基板の第1領域上に第1絶縁膜、第1導電体、第2絶縁膜、及び第2導電体が順に形成された第1の部分と、

前記半導体基板上に前記第1導電体と前記第2導電体、又は前記第1導電体と前記第2絶縁膜のいずれか一方が積層された第2の部分と、

前記半導体基板上に前記第2絶縁膜と前記第2導電体のいずれもが積層されない第3の部分と、

を一体的に有する積層構造体と、

前記積層構造体を覆い、前記第3の部分の一部において前記積層構造体の前記第1導電体のコンタクト領域が露出するホールを備えた第3絶縁膜と、

を有することを特徴とする半導体装置。

【0310】

(付記2) 前記第1絶縁膜は酸化シリコン膜であることを特徴とする付記1に記載の半導体装置。

【0311】

(付記3) 前記第2絶縁膜はONO膜であることを特徴とする付記1に記載の半導体装置。

【0312】

(付記4) 前記半導体基板の第2領域上に順に形成されたトンネル絶縁膜、前記第1導電体と同じ材料で構成されるフローティングゲート、前記第2絶縁膜と同じ材料で構成される中間絶縁膜、及び前記第2導電体と同じ材料で構成されるコントロールゲートと、前記フローティングゲートの側方の前記半導体基板に形成された第1、第2ソース/ドレイン領域とで構成されるフラッシュメモリセルを有することを特徴とする付記1に記載の半導体装置。

【0313】

(付記5) 前記第1導電体は、前記コンタクト領域に形成されたパッド部と、該パッド部に繋がるゲート部とで構成され、

前記ゲート部の側方の前記半導体基板に第3、第4ソース/ドレイン領域が形成されて、

前記第1絶縁膜、前記ゲート部、及び前記第3、第4ソース/ドレイン領域によりトランジスタが構成されることを特徴とする付記1に記載の半導体装置。

【0314】

(付記6) 前記パッド部の前記コンタクト領域上の前記第2導電体に第1開口が形成されると共に、前記第1開口の内側の前記パッド部上に第2開口を備えた酸化シリコン膜が形成されて、前記ホールが前記第1、第2開口の内側に形成されたことを特徴とする付記5に記載の半導体装置。

【0315】

(付記7) 前記第2導電体は電気的にフローティング状態であることを特徴とする付記1に記載の半導体装置。

【0316】

(付記8) 前記第1導電体、前記第2絶縁膜、及び前記第2導電体によりキャパシタが構成されたことを特徴とする付記1に記載の半導体装置。

【0317】

(付記9) 前記ホールが間隔をおいて二つ形成されると共に、該ホールのそれぞれに前記コンタクト領域と電気的に接続された導電性プラグが形成されて、該二つの導電性プラグと前記第1導電体とにより抵抗素子が構成されることを特徴とする付記4に記載の半導体装置。

【0318】

(付記10) 半導体基板と、

前記半導体基板の第1領域上に順に形成された第1絶縁膜及び第1導電体と、

前記第1導電体上のコンタクト領域を除く領域に形成された絶縁体と、

前記第1導電体と前記絶縁体とを覆い、前記コンタクト領域の上にホールを備えた層間絶縁膜と、

前記ホール内に形成され、前記第1導電体のコンタクト領域と電気的に接続された導電性プラグと、

を有することを特徴とする半導体装置。

【0319】

(付記11) 半導体基板の第1領域上に第1絶縁膜を形成する工程と、

前記第1絶縁膜上に第1導電体を形成する工程と、

前記第1導電体上に第2絶縁膜を形成する工程と、

前記第1導電体のコンタクト領域上の前記第2絶縁膜を除去する工程と、

前記第2絶縁膜の上に第2導電膜を形成する工程と、

前記第1導電体のコンタクト領域上の前記第2導電膜を除去し、該第2導電膜を第2導電体とする工程と、

前記第2導電体を覆う第3絶縁膜を形成する工程と、

前記コンタクト領域上の前記第3絶縁膜に第1ホールを形成する工程と、

前記コンタクト領域と電気的に接続される第1導電性プラグを前記第1ホール内に形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0320】

(付記12) 前記第2絶縁膜としてONO膜を形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0321】

(付記13) 前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第2領域にも形成し、

前記第2導電膜を形成する工程において、前記第2領域の前記第1絶縁膜上にも該第2導電膜を形成し、

前記第2導電膜を前記第2導電体とする工程において、前記第2領域の該第2導電膜をパターニングしてコントロールゲートとし、

前記コンタクト領域上の前記第2絶縁膜を除去する工程において、該第2絶縁膜を前記コントロールゲートの下に中間絶縁膜として残し、

前記第1導電体を形成する工程において、該第1導電体と同じ材料で構成されるフローティングゲートを前記中間絶縁膜の下に形成し、

前記フローティングゲートの側方の前記半導体基板に第1、第2ソース/ドレイン領域を形成して、該第1、第2ソース/ドレイン領域、前記第1絶縁膜、前記フローティングゲート、前記中間絶縁膜、及び前記コントロールゲートでフラッシュメモリセルを構成する工程を更に有することを特徴とする付記11に記載の半導体装置の製造方法。

【0322】

(付記14) 前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第3領域にも形成すると共に、

前記第2絶縁膜を形成する工程において、該第2絶縁膜を前記第3領域の前記第1絶縁膜上にも形成し、

前記第1、第2絶縁膜をスルー膜として使用しながら、前記第3領域の前記半導体基板に不純物を注入する工程を有することを特徴とする付記13に記載の半導体装置の製造方法。

【0323】

(付記15) 前記不純物を注入した後、前記コンタクト領域上の前記第2絶縁膜を除去する工程において、前記第3領域の前記第1、第2絶縁膜を除去する工程と、

前記第1、第2絶縁膜を除去後、前記第3領域の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、

前記ゲート電極の側方の前記半導体基板に第3、第4ソース/ドレイン領域を形成して、前記ゲート絶縁膜、前記ゲート電極、及び前記第3、第4ソース/ドレイン領域により第1トランジスタを構成する工程とを有することを特徴とする付記14に記載の半導体装置の製造方法。

【0324】

(付記16) 前記不純物を注入する工程は、前記第1トランジスタの閾値電圧を調節する不純物拡散領域をイオン注入で形成する工程であることを特徴とする付記15に記載の半導体装置の製造方法。

【0325】

(付記17) 前記第1、第3領域は周辺回路領域であり、前記第2領域はセル領域であることを特徴とする付記16に記載の半導体装置の製造方法。

【0326】

(付記18) 前記第1導電体のコンタクト領域上の前記第2導電膜を除去する工程は、該第2導電膜の上に70nm以上の厚さの反射防止膜を形成する工程と、該反射防止膜の上にレジストパターンを形成する工程と、前記レジストパターンをマスクにして前記反射防止膜と前記第2導電膜とをパターニングすることにより、前記第2導電体、前記コントロールゲート、及び前記ゲート電極を形成する工程と、前記レジストパターンを除去する工程とを有し、

前記第1、第2ソース/ドレイン領域を形成する工程は、イオン注入用のレジストパターンを形成せずに、前記反射防止膜をマスクにして前記半導体基板に不純物を注入して行われることを特徴とする付記13に記載の半導体装置の製造方法。

【0327】

(付記19) 前記反射防止膜として窒化シリコン膜を使用することを特徴とする付記18に記載の半導体装置の製造方法。

【0328】

(付記20) 前記コントロールゲートを形成した後に、前記第2導電体と前記フローティングゲートのそれぞれの側面に第1絶縁性サイドウォールを形成する工程を有し、

前記コンタクト領域上の前記第2導電膜を除去する工程において、該第2導電膜の全てを除去し、

前記第2導電膜の除去によって露出した前記第1絶縁性サイドウォールの側面に第2絶縁性サイドウォールを形成する工程を有することを特徴とする付記13に記載の半導体装置の製造方法。

【0329】

(付記21) 前記第1導電体を形成する工程において該第1導電体にパッド部とゲート部とを形成し、

前記ゲート部の側方の前記半導体基板に第5、第6ソース/ドレイン領域を形成して、前記第1絶縁膜、前記ゲート部、及び前記第5、第6ソース/ドレイン領域により第2トランジスタを構成する工程を有することを特徴とする付記11に記載の半導体装置の製造方法。

【0330】

(付記22) 前記第3絶縁膜をパターニングすることにより、前記第2導電体に至る深さの第2ホールを前記第1ホールから離して形成する工程と、

前記第2導電体と電気的に接続される第2導電性プラグを前記第2ホールの中に形成し、前記第1導電体、前記第2絶縁膜、及び前記第2絶縁膜でキャパシタを構成する工程とを有することを特徴とする付記11に記載の半導体装置の製造方法。

【0331】

(付記23) 前記第1ホールを形成する工程において、該第1ホールを間隔を置いて二つ形成し、

前記第1導電性プラグを形成する工程において、前記第1ホールのそれぞれに該第1導電性プラグを形成して、前記二つの第1導電性プラグと前記第1導電体で抵抗素子を構成することを特徴とする付記11に記載の半導体装置の製造方法。

【符号の説明】

【0332】

1、20、60…シリコン基板、1a、20a、60a…素子分離溝、2、21、61…素子分離絶縁膜、3…第1熱酸化膜、4…第1ポリシリコン膜、4a…第1導電体、4b…フローティングゲート、5…ONO膜、5b…中間絶縁膜、6…第2ポリシリコン膜、6a…第2導電体、6c…ゲート電極、7…第2熱酸化膜、10…第2レジストパターン、11a〜11d…第1〜第4ソース/ドレインエクステンション、12a〜12d…第1〜第4n型ソース/ドレイン領域、13a〜13d…第1〜第4シリサイド層、14…絶縁膜、14a…絶縁性サイドウォール、15…カバー絶縁膜、16…層間絶縁膜、16a〜16e…第1〜第5ホール、18…第2レジストパターン、19a〜19e…第1〜第5導電性プラグ、22…nウエル、22a…n型不純物拡散領域、23…pウエル、23a…p型不純物拡散領域、24…第1絶縁膜、25…第1導電膜、25a…第1導電体、25b…パッド部、25c…ゲート部、25d…フローティングゲート、26…第2絶縁膜、27…第1レジストパターン、27a…第1窓、27b…第2窓、28…第3絶縁膜、29…絶縁体、29a…第2開口、29b…第3開口、29d…中間絶縁膜、30…第2導電膜、30a…第2導電体、30b…第1開口、30d…コントロールゲート、30e…配線、31…第3レジストパターン、31a…第3窓、32a〜32f…第1〜第6n型ソース/ドレインエクステンション、32g、32h…第1、第2p型ソース/ドレインエクステンション、33…第1絶縁性サイドウォール、34…第4レジストパターン、34a…第4窓、35…第5レジストパターン、35a…第5窓、36…第6レジストパターン、36a…第6窓、37…第2絶縁性サイドウォール、38a〜38f…第1〜第6n型ソース/ドレイン領域、38g、38h…第1、第2p型ソース/ドレイン領域、39…第7レジストパターン、40…第8レジストパターン、41a〜41h…第1〜第8コバルトシリサイド層、42…エッチングストッパ層、43…第4絶縁膜、44…第1層間絶縁膜、44a〜44i…第1〜第9ホール、45a〜45i…第1〜第9導電性プラグ、46…低誘電率絶縁膜、47…カバー絶縁膜、48…第2層間絶縁膜、48a〜48i…第1〜第9配線溝、49a〜49i…第1〜第9銅配線、50…反射防止膜、58…第2レジストパターン、59…犠牲絶縁膜、62…第1レジストパターン、62a…第1窓、63…第1nウエル、64〜66…第1〜第3pウエル、67…第3レジストパターン、67a〜67c…第5〜第7窓、68〜70…第4〜第6pウエル、71…第4レジストパターン、71a〜71c…第8〜第10窓、72〜74…第2〜第4nウエル、75…第5レジストパターン、75a〜75c…第11〜第13窓、76〜78…第5〜第7nウエル、79…第6レジストパターン79、79a…第14窓、80…第1p型不純物拡散領域、81…第1絶縁膜、82…第1導電膜、82a…第1導電体、82b…パッド部、82c…ゲート部、82d…フローティングゲート、83…第2絶縁膜、84…第7レジストパターン、84a…第15窓、85…第2p型不純物拡散領域、86…第8レジストパターン、86a…第16窓、87…第1n型不純物拡散領域、88…第9レジストパターン、88a…第17窓、89…第3p型不純物拡散領域、90…第10レジストパターン、90a…第18窓、91…第2n型不純物拡散領域、92…第11レジストパターン、93…第12レジストパターン、94…第3絶縁膜、95…第13レジストパターン、96…第4絶縁膜、97…第5絶縁膜、99…絶縁体、99d…中間絶縁膜、100…第2導電膜、100a…第2導電体、100d…コントロールゲート、100e〜100n…第1〜10ゲート電極、101…第14レジストパターン、102b〜102n…第2〜第14n型ソース/ドレインエクステンション、102p〜102y…第1〜第10p型ソース/ドレインエクステンション、103…第1絶縁性サイドウォール、104…第2絶縁性サイドウォール、105a〜105n…第1〜第14n型ソース/ドレイン領域、105p〜105y…第1〜第10p型ソース/ドレイン領域、107…エッチングストッパ膜、108…第6絶縁膜、109…第1層間絶縁膜、109a〜109y…第1〜第25ホール、110a〜110y…第1〜第25導電性プラグ、111…低誘電率絶縁膜、112…カバー絶縁膜、113…第2層間絶縁膜、113a…配線溝、114…銅配線、120…積層構造体。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

電源を切っても記憶を保持できるフラッシュメモリは、携帯電話のようなモバイル機器に使用されるほか、ロジック回路と混載してFPGA(Field Programmable Gate Array)にも使用されている。特に、後者のようにフラッシュメモリをロジック回路と混載する場合には、メモリセルとロジック回路のそれぞれの製造プロセスを互いにうまく利用しあい、製品として出荷するロジック混載メモリに不具合が発生しないようにする必要がある。

【0003】

そのロジック混載メモリでは、製品の出荷前に、フラッシュメモリを構成するトンネル絶縁膜の耐圧をモニターする場合がある。但し、トンネル絶縁膜は、フローティングゲートの下に形成されているため、その上下から電圧を与えて耐圧をモニターするには、コントロールゲートを介さないでフローティングゲートに導電性プラグを直接コンタクトさせ、その導電性プラグと半導体基板との間に試験電圧を印加する必要がある。

【0004】

そのため、上記のロジック混載メモリでは、フローティングゲートにコンタクトする導電性プラグの形成プロセスを、周辺ロジック回路の製造プロセスにいかにして組み入れるかが重要となる。

【0005】

以下の特許文献1〜10には、本発明に関連する様々なロジック混載メモリが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平6−97457号公報

【特許文献2】特開2003−158242号公報

【特許文献3】特開平11−219595号公報

【特許文献4】特開2004−55763号公報

【特許文献5】特開平10−56161号公報

【特許文献6】特開平11−31799号公報

【特許文献7】特開平10−189954号公報

【特許文献8】特開2003−37169号公報

【特許文献9】特開2003−100887号公報

【特許文献10】特開2003−124356号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明の一観点によれば、半導体基板の第1領域上にコンタクト領域を一部に有する第1絶縁膜を形成する工程と、前記第1絶縁膜上に第1導電体を形成する工程と、前記第1導電体上に第2絶縁膜を形成する工程と、前記第1導電体の前記コンタクト領域上の前記第2絶縁膜を除去することにより、前記第2絶縁膜に開口を形成する工程と、前記第2絶縁膜の上に第2導電膜を形成する工程と、前記第1導電体の前記コンタクト領域上の前記第2導電膜を除去し、該第2導電膜を第2導電体とする工程と、前記第2導電体を覆う第3絶縁膜を形成する工程と、前記コンタクト領域上であって、前記開口の内側の前記第3絶縁膜に、前記第2絶縁膜から離間する第1ホールを形成する工程と、前記コンタクト領域と電気的に接続される導電性プラグを前記第1ホール内に形成する工程とを有する半導体装置の製造方法が提供される。

【0009】

その半導体装置の製造方法では、前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第2領域にも形成し、前記第2導電膜を形成する工程において、前記第2領域の前記第1絶縁膜上にも該第2導電膜を形成し、前記第2導電膜を前記第2導電体とする工程において、前記第2領域の該第2導電膜をパターニングしてコントロールゲートとし、前記コンタクト領域上の前記第2絶縁膜を除去する工程において、該第2絶縁膜を前記コントロールゲートの下に中間絶縁膜として残し、前記第1導電体を形成する工程において、該第1導電体と同じ材料で構成されるフローティングゲートを前記中間絶縁膜の下に形成し、前記フローティングゲートの側方の前記半導体基板に第1、第2ソース/ドレイン領域を形成して、該第1、第2ソース/ドレイン領域、前記第1絶縁膜、前記フローティングゲート、前記中間絶縁膜、及び前記コントロールゲートでフラッシュメモリセルを構成する工程を更に有するのが好ましい。

【0010】

更に、このようにフラッシュメモリセルを形成する場合には、前記第1絶縁膜を形成する工程において、該第1絶縁膜を前記半導体基板の第3領域にも形成するのが好ましい。そして、前記第2絶縁膜を形成する工程において、該第2絶縁膜を前記第3領域の前記第1絶縁膜上にも形成し、前記第1、第2絶縁膜をスルー膜として使用しながら前記第3領域の前記半導体基板に不純物を注入する工程を有するのが好ましい。

【0011】

このようにスルー膜として使用した第1、第2絶縁膜は、上記の不純物を注入後、コンタクト領域上の第2絶縁膜を除去する工程において除去してよい。

【0012】

これによれば、不純物注入のスルー膜として使用した後に不要となった第2絶縁膜を第3領域において除去する工程が、コンタクト領域上の第2絶縁膜を除去する工程を兼ねる。そのため、本発明では、余計なマスク工程を追加せずにコンタクト領域の上方の第2絶縁膜を選択的に除去できる。

【0013】

更に、このように第2絶縁膜を除去する工程では、第1領域では第2絶縁膜のみを除去するのに対し、第3領域では第1絶縁膜と第2絶縁膜の二層を除去するので、第3領域のエッチング量が第1領域におけるそれよりも多くなる。そのため、この工程におけるエッチング量を第3領域のそれに合わせることで、第1領域における第2絶縁膜を完全に除去しながら、第3領域における第1、第2絶縁膜の過剰なエッチングを防止してその下の素子分離絶縁膜等に削れが発生するのを防ぐことができる。

【発明の効果】

【0014】

本発明によれば、不純物注入のスルー膜として使用した後に不要となった第2絶縁膜を第3領域において除去する工程が、コンタクト領域上の第2絶縁膜を除去する工程を兼ねので、余計なマスク工程を追加せずにコンタクト領域の上方の第2絶縁膜を選択的に除去できる。

【0015】

更に、その第2絶縁膜を除去する工程では、第3領域のエッチング量が第2領域のエッチング量よりも大きくなるので、全体のエッチング量を第3領域のそれに合わせることで、第2領域における第2絶縁膜を完全に除去しつつ、第3領域における過剰なエッチングによって素子分離絶縁膜等が削れるのを防ぐことができる。

【図面の簡単な説明】

【0016】

【図1】図1は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その1)である。

【図2】図2は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その2)である。

【図3】図3は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その3)である。

【図4】図4は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図(その4)である。

【図5】図5は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第2例)の製造途中の断面図(その1)である。

【図6】図6は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第2例)の製造途中の断面図(その2)である。

【図7】図7(a)、(b)は、仮想的な半導体装置(第3例)の製造途中の断面図である

【図8】図8は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図9】図9は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図10】図10は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図11】図11は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図12】図12は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図13】図13は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図14】図14は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図15】図15は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図16】図16は、本発明の第1実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図17】図17は、本発明の第1実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図18】図18は、本発明の第1実施形態に係る半導体装置の等価回路の一例を示す図である。

【図19】図19は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図20】図20は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図21】図21は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図22】図22は、本発明の第2実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図23】図23は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図24】図24は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図25】図25は、本発明の第2実施形態に係る半導体装置の製造途中の平面図(その3)である。

【図26】図26は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図27】図27は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図28】図28は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図29】図29は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図30】図30は、本発明の第3実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図31】図31は、本発明の第3実施形態に係る半導体装置の製造途中の平面図である。

【図32】図32は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図33】図33は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図34】図34は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図35】図35は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図36】図36は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図37】図37は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図38】図38は、本発明の第4実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図39】図39は、本発明の第5実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図40】図40は、本発明の第5実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図41】図41は、本発明の第5実施形態において、反射防止膜の厚さによってAs-イオンがどの程度ブロックされるのかを調査して得られたグラフである。

【図42】図42は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図43】図43は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図44】図44は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図45】図45は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図46】図46は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図47】図47は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図48】図48は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図49】図49は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図50】図50は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その9)である。

【図51】図51は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その10)である。

【図52】図52は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その11)である。

【図53】図53は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その12)である。

【図54】図54は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その13)である。

【図55】図55は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その14)である。

【図56】図56は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その15)である。

【図57】図57は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その16)である。

【図58】図58は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その17)である。

【図59】図59は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その18)である。

【図60】図60は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その19)である。

【図61】図61は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その20)である。

【図62】図62は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その21)である。

【図63】図63は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その22)である。

【図64】図64は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その23)である。

【図65】図65は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その24)である。

【図66】図66は、本発明の第6実施形態に係る半導体装置の製造途中の断面図(その25)である。

【図67】図67は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その1)である。

【図68】図68は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その2)である。

【図69】図69は、本発明の第6実施形態に係る半導体装置の製造途中の平面図(その3)である。

【発明を実施するための形態】

【0017】

(1)予備的事項の説明

本発明の実施の形態の前に、予備的事項について説明する。

【0018】

(i)第1例

図1〜図4は、フラッシュメモリとロジック回路とを混載してなる仮想的な半導体装置(第1例)の製造途中の断面図である。

【0019】

最初に、図1(a)に示す断面構造を得るまでの工程について説明する。

【0020】

まず、シリコン基板1にSTI(Shallow Trench Isolation)用の素子分離溝1aを形成した後、その溝1a内に二酸化シリコン膜を素子分離絶縁膜2として埋め込む。次いで、シリコン基板1の表面を熱酸化して第1熱酸化膜3を形成した後、全面に第1ポリシリコン膜4を形成してそれをパターニングし、第1周辺回路領域Iとセル領域IIのみにポリシリコン膜4を残す。その後に、全面にONO膜5を形成する。

【0021】

続いて、図1(b)に示すように、第2周辺回路領域III上の第1熱酸化膜3とONO膜5とをエッチングして除去する。そして、第2周辺回路領域IIIのシリコン基板1の表面を熱酸化して第2熱酸化膜7を形成した後、全面に第2ポリシリコン膜6を形成する。

【0022】

次に、図2(a)に示すように、第2ポリシリコン膜6の上に第1レジストパターン9を形成する。そして、その第1レジストパターン9をマスクにして、第1周辺回路領域Iとセル領域IIにおける各膜4〜6をエッチングする。これにより、セル領域IIには、ポリシリコンよりなるフローティングゲート4bとコントロールゲート6bが残されることになる。また、第1周辺回路領域Iには、ポリシリコンよりなる第1、第2導電体4a、6aが残される。

【0023】

この後に、第1レジストパターン9は除去される。

【0024】

次に、図2(b)に示すように、第2導電体6aが露出する第2レジストパターン10をセル領域IIと第2周辺回路領域IIIに形成する。そして、その第2レジストパターン10をマスクにして第2ポリシリコン膜6をエッチングすることにより、第2周辺回路領域IIにゲート電極6cを形成すると共に、第1周辺回路領域Iの第2導電体6aを除去し、ONO膜5を露出させる。

【0025】

続いて、図3(a)に示す断面構造を得るまでの工程について説明する。

【0026】

まず、フローティングゲート4bとゲート電極6cとをマスクにしてシリコン基板1にn型不純物をイオン注入することにより、各ゲート4b、6cの側方のシリコン基板1に第1〜第4ソース/ドレインエクステンション11a〜11dを形成する。次に、全面に酸化シリコン膜等の絶縁膜を形成した後、それをエッチバックして各ゲート4b、6cと第1導電体4aのそれぞれの横に絶縁性サイドウォール14aとして残す。そのエッチバックの際、第1、第2熱酸化膜3、7はパターニングされてそれぞれトンネル絶縁膜3a、ゲート絶縁膜7aとなる。

【0027】

そして、その絶縁性サイドウォール14aをマスクにして、シリコン基板1にn型不純物を再びイオン注入することにより、第1〜第4n型ソース/ドレイン領域12a〜12dをシリコン基板1に形成する。

【0028】

次いで、その第1〜第4n型不純物拡散領域12a〜12d上に第1〜第4シリサイド層13a〜13dを形成した後、全面にカバー絶縁膜15と層間絶縁膜16とを順に形成する。

【0029】

ここまでの工程により、第2周辺回路領域IIIには、第1、第2n型不純物拡散領域12a、12bとゲート電極6cとで構成される周辺トランジスタTRが形成され、セル領域IIには、第1、第2不純物拡散領域12a、12b、トンネル絶縁膜3a、フローティングゲート4b、中間絶縁膜5b、及びコントロールゲート6bで構成されるフラッシュメモリセルFLが形成されたことになる。

【0030】

一方、第1周辺回路領域Iにおける第1導電体4aは、不図示の参照トランジスタのゲート電極を兼ねている。その参照トランジスタは、フラッシュメモリセルFLのトンネル絶縁膜3aと同じプロセスで形成されたゲート絶縁膜を有しているので、参照トランジスタの耐圧を調べることで、フラッシュメモリセルFLのトンネル絶縁膜3aの耐圧を調べることができる。

【0031】

次に、図3(b)に示すように、カバー絶縁膜15と層間絶縁膜16とをパターニングして、第1〜第4シリサイド層13a〜13dに至る深さの第1〜第4ホール16a〜16dを形成すると共に、第1導電体4aの上に第5ホール16eを形成する。

【0032】

これらのホール16a〜16eは、最初にカバー絶縁膜15をエッチングストッパ膜として使用しながら層間絶縁膜16をエッチングし、次にエッチングガスを変えてカバー絶縁膜15をエッチングすることにより形成される。

【0033】

また、これらのホールのうち、第1〜第4ホール16a〜16dのコンタクト構造は、ボーダレスコンタクトと呼ばれる。ボーダレスコンタクトでは、各ホール16a〜16dが多少位置ずれしてその一部が素子分離絶縁膜2に重なっても、素子分離絶縁膜2とカバー絶縁膜15とのエッチング速度の違いによって、ホール形成時における素子分離絶縁膜2のエッチング量を抑えている。

【0034】

一方、第5ホール16eは、第1導電体4aとのコンタクトをとり、参照トランジスタにゲート電圧を印加するために形成されるものなので、その底部に第1導電体4aが露出しなければならない。ところが、第1〜第4ホール16a〜16dの形成が、カバー絶縁膜15のエッチング終了と同時に完了するのに対し、第5ホール16eを形成するには、カバー絶縁膜15の下のONO膜5をもエッチングしなければならない。

【0035】

そのため、ホールのエッチング時間を第1〜第4ホール16a〜16dのエッチング時間に合わせると、図示のように、第5ホール16eのエッチング量が不足してホール16eが未開口となり、その下に第1導電体4aが露出しない。

【0036】

従って、第5ホール16eを開口させるには、第1〜第4ホール16a〜16dの形成に必要なエッチング時間に加え、第5ホール16eが貫通するONO膜5のエッチング時間の分だけ余計にエッチングを行わなければならない。

【0037】

但し、このように長時間エッチングを行っても、第1〜第4ホール16a〜16dと第1〜第4シリサイド層13a〜13dとが位置ずれを起こしていなければ特に問題は無い。

【0038】

しかし、それらの間に位置ずれが発生していると、図4の点線円内に示されるように、例えば第3ホール16cの下の素子分離絶縁膜2がエッチングされてしまい、第3ホール16cにシリコン基板1が露出してしまう。こうなると、第3ホール16c内に埋め込まれる第3導電性プラグ19cとシリコン基板1とが短絡してしまい、第3n型ソース/ドレイン領域12cの電位を導電性プラグ19cでコントロールできなくなってしまう。このような不都合は、第3導電性プラグ19cだけでなく、第1、第2、第4ホール16a、16c、16dに形成される第1、第2、第4導電性プラグ19a、19c、19dによっても発生し得る。

【0039】

(ii)第2例

上記した第1例の不都合を解消するため、以下のような方法も考えられる。

【0040】

図5、図6は、仮想的な半導体装置(第2例)の製造途中の断面図である。

【0041】

まず、第1例で示した図2(b)の工程を終了した後に、図5(a)に示すように、フローティングゲート4bとゲート電極6cとをマスクにしてシリコン基板1にn型不純物をイオン注入することにより、各ゲート4b、6cの側方のシリコン基板1に第1〜第4ソース/ドレインエクステンション11a〜11dを形成する。

【0042】

次に、図5(b)に示すように、全面に酸化シリコン等の絶縁膜14を形成する。

【0043】

続いて、図6(a)に示すように、絶縁膜14をエッチバックして各ゲート4b、6cと第1導電体4aのそれぞれの横に絶縁性サイドウォール14aとして残す。本例では、更にエッチングを進めて、第1導電体1上のONO膜5をもエッチングして除去する。

【0044】

続いて、絶縁性サイドウォール14aをマスクにして、シリコン基板1にn型不純物を再びイオン注入することにより、第1〜第4n型ソース/ドレイン領域12a〜12dをシリコン基板1に形成する。

【0045】

その後に、各n型ソース/ドレイン領域12a〜12dの上に第1〜第4シリサイド層13a〜13dを形成する。

【0046】

この後は、第1例で説明した図3〜図4の工程を行うことにより、層間絶縁膜16に第1〜第5ホール16a〜16dを形成し、図6(b)に示す断面構造を得る。

【0047】

以上説明した第2例では、図6(a)に示したように、エッチバックにより絶縁性サイドウォール14aを形成する際にONO膜5も同時に除去し、第1導電体4aの表面を露出させる。そのため、第1〜第4ホール16a〜16dを過剰にエッチングしなくても第5ホール16eの下に第1導電体4aの表面が露出する。

【0048】

しかし、図6(a)に示すエッチバック工程では、絶縁性サイドウォール14aの形成に本来必要なエッチング時間よりも長くエッチングを行うため、素子分離絶縁膜2がエッチングされその上面がシリコン基板1のそれよりも下がってしまう。その結果、図6(b)の点線Xのように、第3n型ソース/ドレイン領域12cとシリコン基板1のそれぞれの側面が素子分離溝1aの側壁に表出する。従って、第3ホール16cが位置ずれを起こすと、第1例と同様に、第3ホール16c内に形成される第3導電性プラグ19cとシリコン基板1とがショートしてしまう。

【0049】

(iii)第3例

上記した第1例と第2例の他に、以下のような方法も考えられる。

【0050】

図7(a)、(b)は、仮想的な半導体装置(第3例)の製造途中の断面図である。

【0051】

まず、第1例で示した図2(a)の工程の後に、図7(a)に示すように、コントロールゲート6b上と第2ポリシリコン膜6上とに、第2導電体6aが露出する第2レジストパターン10を形成する。

【0052】

次に、図7(b)に示すように、第2レジストパターン10をマスクにし、第2ポリシリコン膜6をエッチングしてゲート電極6cを形成すると共に、第2導電体6aとONO膜5とをエッチングして除去し、第1導電体4aを露出させる。その後に、第2レジストパターン10を除去する。

【0053】

この後は、第1例で説明した図3、図4の工程が行われる。

【0054】

第3例では、ゲート電極6cのパターニング時にONO膜5をエッチングして除去するが、そのエッチングによって素子分離絶縁膜2の上面がシリコン基板1の上面よりも下がるので、やはり第2例と同じような不都合が発生してしまう。また、第2周辺回路領域IIIのゲート絶縁膜が薄いと、ONO膜をエッチングする際にソース/ドレイン形成予定領域のシリコン基板1の表面がRIE等のエッチング雰囲気に長時間曝されて汚染したり、シリコン基板1が掘られたりする不都合が生じる。

【0055】

上記した第1〜第3例では、第1導電体4a上のONO膜5の除去の仕方がそれぞれ異なるが、いずれの例でもONO膜を除去しようとすると第1〜第4ホール16a〜16d内で導電性プラグとシリコン基板1とのショートが発生する。これを防ぐために、ONO膜5を除去するための専用のフォトリソグラフィ工程を追加することも考えられるが、これでは工程数が多くなり、半導体装置の生産性が悪化してしまう。

【0056】

本願発明者は、このような第1〜第3例の不都合を解消するため、次のような本発明の実施の形態に想到した。

【0057】

(2)第1実施形態

図8〜図15は、本発明の第1実施形態に係る半導体装置の製造途中の断面図であり、図16、図17はその平面図である。

【0058】

本実施形態では、FPGA等のロジック混載メモリが作製される。

【0059】

最初に、図8(a)に示す断面構造を得るまでの工程について説明する。

【0060】

まず、第1周辺回路領域(第1領域)I、セル領域(第2領域)II、及び第2周辺回路領域(第3領域)IIIが画定されたp型シリコン基板(半導体基板)20にSTI用の素子分離溝20aを形成した後、その素子分離溝20a内に酸化シリコンを素子分離絶縁膜21として埋め込む。

【0061】

次いで、シリコン基板20の表面を熱酸化して犠牲酸化膜(不図示)を形成し、その犠牲酸化膜をスルー膜として使用しながらシリコン基板20にn型不純物としてP+イオンをイオン注入して、シリコン基板20の深部に第1nウエル17aを形成する。そのイオン注入の条件としては、例えば加速エネルギ2MeV、ドーズ量2×1013cm-3が採用される。

【0062】

続いて、1回目の条件を加速エネルギ400KeV及びドーズ量1.5×1013cm-3とし、2回目の条件を加速エネルギ100KeV及びドーズ量2×1012cm-3のとするイオン注入により、シリコン基板20にp型不純物のB+イオンを注入して、上記の第1nウエル17aよりも浅い部分のシリコン基板20に第1pウエル17bを形成する。

【0063】

更に、加速エネルギ40KeV、ドーズ量6×1013cm-3の条件でシリコン基板20にB+イオンをイオン注入することにより、セル領域IIに後で形成されるフラッシュメモリセルの閾値電圧を制御するためのセル用不純物拡散領域17cを形成する。

【0064】

その後、第2周辺回路領域IIIにおいてもイオン注入を行い、図示のような第2nウエル22と第2pウエル23とを形成する。これらのウエルのうち、第2nウエル22のイオン注入は二回に分けて行われ、1回目の条件としてはP+イオンの加速エネルギ600KeV、ドーズ量1.5×1013cm-3が採用され、2回目の条件としては加速エネルギ240KeV、ドーズ量6.0×1012cm-3が採用される。また、第2pウエル23も2回のイオン注入により形成され、1回目の条件としてはB+イオンの加速エネルギ400KeV、ドーズ量1.5×1013cm-3が採用され、2回目の条件としては加速エネルギ100KeV、ドーズ量8×1012cm-3が採用される。

【0065】

なお、上記のn型不純物とp型不純物の打ち分けは不図示のレジストパターンを用いて行われ、イオン注入が終了した後にそのレジストパターンは除去される。

【0066】

その後、イオン注入のスルー膜として使用した犠牲酸化膜をフッ酸溶液によって除去してシリコン基板20の清浄面を露出させた後、ArとO2との混合雰囲気中、温度900℃〜1050℃の条件でその清浄面を熱酸化する。これにより、シリコン基板20の各領域I〜IIIには、厚さ約10nmの熱酸化膜が第1絶縁膜24として形成される。

【0067】

次に、図8(b)に示す断面構造を得るまでの工程について説明する。

【0068】

まず、SiH4(シラン)とPH3(ホスフィン)とを反応ガスとして使用する減圧CVD(Chemical Vapor Deposition)法により、第1絶縁膜24の上に第1導電膜25としてポリシリコン膜を約90nmの厚さに形成する。そのポリシリコン膜には、反応ガス中のPH3により、リンがin-situでドープされることになる。

【0069】

続いて、フォトリソグラフィによりその第1導電膜25をパターニングして第2周辺回路領域III上から除去する。なお、セル領域IIにおける第1導電膜25は、このパターニングによりワードライン方向に直行した帯状となる。

【0070】

次に、第1導電膜25上と、第2周辺回路領域III上の第1絶縁膜24上とに、減圧CVD法を用いて酸化シリコン膜と窒化シリコン膜とをこの順にそれぞれ厚さ5nm、10nmに形成する。更に、O2雰囲気中において、基板温度約950℃、加熱時間約90分間の条件で窒化シリコン膜の表面を酸化し、窒化シリコン膜の表面に約30nmの酸化シリコン膜を形成する。これにより、酸化シリコン膜、窒化シリコン膜、及び酸化シリコン膜をこの順に積層してなるONO膜が第2絶縁膜26として全面に形成されたことになる。

【0071】

その第2絶縁膜26を構成するONO膜は、低温で形成しても酸化シリコン膜と比較してリーク電流が小さい。そのため、フラッシュメモリセルのフローティングゲートとコントロールゲートの間の中間絶縁膜としてこの第2絶縁膜26を使用することで、フローティングゲートに蓄積された電荷がコントロールゲート側に逃げ難くなり、フラッシュメモリセルに書き込まれた情報を長時間にわたって保持することができる。

【0072】

このような第2絶縁膜26を形成した後、加速エネルギを150KeV、ドーズ量を3×1012cm-3とする条件を採用して、第1、第2絶縁膜24、26をスルー膜として使用しながらn型不純物のAs-イオンをシリコン基板20にイオン注入してn型不純物拡散領域22aを形成する。そのn型不純物拡散領域22aは、後で形成されるp型MOSトランジスタの閾値電圧を調節する役割を担う。

【0073】

更に、第1、第2絶縁膜24、26をスルー膜として使用しながら、加速エネルギ30KeV、ドーズ量5×1012cm-3の条件でシリコン基板60にp型不純物のB+イオンをイオン注入する。これにより、第2周辺回路領域IIIには、p型MOSトランジスタの閾値電圧を調節するためのp型不純物拡散領域23aが形成される。

【0074】

なお、このような不純物拡散領域22a、23aのイオン注入では、不図示のレジストパターンによってn型不純物とp型不純物の打ち分けが行われる。

【0075】

続いて、図9(a)に示すように、第2絶縁膜26の上に第1レジストパターン27を形成する。その第1レジストパターン27には、後で導電性プラグと接続される第1導電膜25のコンタクト領域CRの上に第1窓27aを有すると共に、第2周辺回路領域IIIの上に第2窓27bを有する。そして、この第1レジストパターン27をマスクとして使用しながら、CH3とO2との混合ガスをエッチングガスとするプラズマエッチングにより、第1レジストパターン27で覆われていない領域の第2絶縁膜26をエッチングし、その第2絶縁膜26を構成する最上層の酸化シリコン膜と窒化シリコン膜とをエッチングする。次いで、第1レジストパターン27をマスクにして、HF溶液により第2絶縁膜26の最下層の酸化シリコン膜をウエットエッチングして除去する。

【0076】

これにより、コンタクト領域CRにおける第1導電膜25と、第2周辺回路領域IIIのシリコン基板20が露出すると共に、コンタクト領域CRを除いた領域のみに第2絶縁膜が残る。

【0077】

続いて、酸素アッシングによって第1レジストパターン27を除去した後、ウエット処理によりシリコン基板20の表面を洗浄する。

【0078】

次に、図9(b)に示す断面構造を得るまでの工程について説明する。

【0079】

まず、酸素雰囲気中で基板温度を約850℃とする酸化条件を採用して、第2絶縁膜26で覆われていない部分のシリコンを熱酸化する。これにより、ポリシリコンよりなる第1導電膜25上において第2絶縁膜26が除去されていた部分と、第2周辺回路領域IIIのシリコン基板20のそれぞれの表面に、厚さ約2.2nmの熱酸化膜が第3絶縁膜28として形成される。その第3絶縁膜28は第2絶縁膜26と隣接して形成され、これらの第2、第3絶縁膜26、28により絶縁体29が構成される。なお、図9(b)には明示しないが、コンタクト領域CR上の絶縁体29の厚さは他の領域に比べて著しく薄い。

【0080】

その後に、SiH4を反応ガスとして使用する減圧CVD法により、各絶縁膜26、28の上に、厚さ約180nmのノンドープのポリシリコン膜を第2導電膜30として形成する。

【0081】

次に、図10(a)に示す断面構造を得るまでの工程について説明する。

【0082】

まず、第2導電膜30上にフォトレジストを塗布し、それを露光、現像することにより、第2レジストパターン18を形成する。次に、この第2レジストパターン18をエッチングマスクとして使用して第1、第2導電膜25、30、及び絶縁体29をパターニングする。そのパターニングはプラズマエッチングチャンバ内で行われ、ポリシリコンよりなる第1、第2導電膜25、30のエッチングガスとしてはCl2とO2との混合ガスが使用され、ONO膜で構成される第2絶縁膜26のエッチングガスとしてはCH3とO2との混合ガスが使用される。

【0083】

このようなパターニングの結果、第2導電膜30を第2周辺回路領域IIIに残しながら、第1周辺回路領域I上の第1、第2導電膜25、30が、コンタクト領域CRを含む領域においてそれぞれ第1、第2導電体25a、30aとされる。そして、セル領域II上では、第1、第2導電膜25、30と絶縁体29とがそれぞれフローティングゲート25d、コントロールゲート30d、中間絶縁膜29dとされる。

【0084】

この後に、第2レジストパターン30は除去される。

【0085】

図16は、この工程を終了後の平面図であり、先の図10(a)は、図16のA−A線に沿う断面図に相当する。これに示されるように、第1導電体25aは、素子分離絶縁膜21上のパッド部25bと第1絶縁膜24上のゲート部25cとで構成される。

【0086】

次いで、図10(b)に示すように、第1導電体25aのパッド部25bと第2導電膜30とを覆い、且つゲート部25cとフローティングゲート25dとが露出する第3窓31aを備えた第3レジストパターン31を各領域I〜IIIに形成する。そして、この第3窓31aを通じてn型不純物のAsを加速エネルギ50KeV、ドーズ量6×1014cm-3の条件でシリコン基板20にイオン注入することにより、フローティングゲート25dとゲート部25cのそれぞれの側方のシリコン基板20に第1〜第4n型ソース/ドレインエクステンション32a〜32dを形成する。

【0087】

その後に、第3レジストパターン31を除去する。

【0088】

次に、図11(a)に示すように、フローティングゲート25dとコントロールゲート30dの側面を酸化して熱酸化膜(不図示)を形成した後、窒化シリコン膜を全面に形成してそれをエッチバックし、第2導電体30aとフローティングゲート25dのそれぞれの側面に第1絶縁性サイドウォール33として残す。

【0089】

次に、図11(b)に示すように、各領域I〜IIIの上に第4レジストパターン34を形成する。その第4レジストパターン34は、パッド部25bのコンタクト領域CR上に第4窓34aを有すると共に、第2周辺回路領域III上においてゲート電極形状を有する。そして、Cl2とO2との混合ガスをエッチングガスとして採用し、この第4レジストパターン34をマスクにしながら第2導電体30aと第2導電膜30とをプラズマエッチングすることにより、コンタクト領域CR上の第2導電体30aを除去して第1開口30bを形成すると共に、第2周辺回路領域III上に第1、第2ゲート電極30f、30gを形成する。また、このエッチングでは、素子分離絶縁膜21上に延在していた第2導電膜30がパターニングされて配線30eとなる。

【0090】

この後に、第4レジストパターン34を除去する。

【0091】

次に、図12(a)に示すように、第1ゲート電極30fの側方の第3絶縁膜28が露出する大きさの第5窓35aを備えた第5レジストパターン35を各領域I〜IIIの上に形成する。そして、その第5レジストパターン35をマスクにしてチルト角0°、加速エネルギ0.5KeV、及びドーズ量3.5×1014cm-3の条件でB+をシリコン基板20にイオン注入する。その後に、第5窓35aを通じてチルト角28°、加速エネルギ80KeV、及びドーズ量7.0×1012cm-3の条件でAs+を四方向からシリコン基板20にイオン注入することにより、第1ゲート電極30fの側方のシリコン基板20に第5、第6n型ソース/ドレインエクステンション32e、32fを形成する。その後に、第5レジストパターン35は除去される。

【0092】

続いて、図12(b)に示すように、第2ゲート電極30gの側方の第3絶縁膜28が露出する大きさの第6窓36aを備えた第6レジストパターン36を各領域I〜IIIの上に形成する。

【0093】

そして、その第6レジストパターン36をマスクにしてチルト角0°、加速エネルギ3.0KeV、及びドーズ量1.0×1015cm-3の条件でAs+をシリコン基板20にイオン注入する。その後に、第6窓36aを通じてチルト角28°、加速エネルギ35KeV、及びドーズ量1.0×1013cm-3の条件でBF2をシリコン基板20にイオン注入することにより、第2ゲート電極30gの側方のシリコン基板20に第1、第2p型ソース/ドレインエクステンション32g、32hを形成する。その後に、第6レジストパターン36は除去される。

【0094】

次に、図13(a)に示す断面構造を得るまでの工程について説明する。

【0095】

まず、CVD法により全面に酸化シリコン膜を形成した後、その酸化シリコン膜をエッチバックして、第2導電体30a、コントロールゲート30d、配線30e、及び第1、第2ゲート電極30f、30gのそれぞれの側面に第2絶縁性サイドウォール37を形成する。そして、そのエッチバックを更に進めることにより、第2絶縁性サイドウォール37をマスクにしながら、パッド部25b上で絶縁体29を構成している第3絶縁膜28をエッチングし、第1開口30bよりも直径が小さな第2開口29aを形成する。

【0096】

また、このエッチバックにより、第2絶縁性サイドウォール37がマスクとなって第1絶縁膜24がパターニングされ、その第1絶縁膜24がゲート部25cとフローティングゲート25dのそれぞれの下にゲート絶縁膜24a及びトンネル絶縁膜24bとして残る。

【0097】

更に、第2周辺回路領域IIIでは、第3絶縁膜28がパターニングされて第1、第2ゲート30f、30gの下にゲート絶縁膜28a、28bとして残る。

【0098】

続いて、図13(b)に示すように、シリコン基板20上にNMOS形成領域が露出する第7レジストパターン39を形成し、このレジストパターン39をマスクにしながら加速エネルギ10KeV、ドーズ量6×1015cm-3の条件でP+をシリコン基板20にイオン注入する。これにより、ゲート部25c、フローティングゲート25d、第1ゲート電極30fのそれぞれの側方のシリコン基板20に、第1〜第6n型ソース/ドレイン領域38a〜38fが形成される。また、このイオン注入では、第2導電体30a、コントロールゲート30d、第1ゲート電極30fにもn型不純物が導入され、これらがn型化される。

【0099】

その結果、第1周辺回路領域Iでは、ゲート部25c、ゲート絶縁膜24a、及び第1、第2n型ソース/ドレイン領域38a、38bで構成される参照トランジスタTRrefが形成される。一方、セル領域IIでは、コントロールゲート30d、中間絶縁膜29d、フローティングゲート25d、トンネル絶縁膜24b、及び第3、第4n型ソース/ドレイン領域38c、38dで構成されるフラッシュメモリセルFLが形成される。そして、第2周辺回路領域IIIでは、第1ゲート電極30f、ゲート絶縁膜28a、及び第5、第6n型ソース/ドレイン領域38e、38fで構成されるn型MOSトランジスタTRnが形成される。

【0100】

この後に、第7レジストパターン39は除去される。

【0101】

次いで、図14(a)に示すように、第1周辺回路領域I、セル領域II、及びn型MOSトランジスタTRnを第8レジストパターン40で覆う。そして、加速エネルギ5KeV、ドーズ量4×1015cm-3のイオン注入条件を採用して、第2ゲート電極30gの側方のシリコン基板20にp型不純物としてB+を導入することにより、第1、第2p型ソース/ドレイン領域38g、38hを形成する。これにより、n型MOSトランジスタTRnの隣の第2周辺回路領域IIIには、第2ゲート電極30g、ゲート絶縁膜28b、及び第1、第2p型ソース/ドレイン領域38g、38hで構成されるp型MOSトランジスタTRpが形成される。

【0102】

そのp型MOSトランジスタTRpは、n型MOSトランジスタTRnと共にセンスアンプ等のロジック回路を構成する。

【0103】

そのイオン注入が終了した後、第8レジストパターン40を除去する。

【0104】

次に、図14(b)に示す断面構造を得るまでの工程について説明する。

【0105】

まず、スパッタ法により全面にコバルト膜を厚さ約8nmに形成した後、そのコバルト膜をアニールしてシリコンと反応させる。そして、素子分離絶縁膜21等の上の未反応のコバルト膜をウエットエッチングして除去し、シリコン基板20の表層に第1〜第8コバルトシリサイド層41a〜41hを形成する。

【0106】

続いて、CVD法によりシリコン窒化膜を厚さ約50nmに形成し、それをエッチングストッパ膜42とする。次いで、そのエッチングストッパ膜42の上にCVD法により第4絶縁膜43として酸化シリコン膜を形成し、エッチングストッパ膜42と第4絶縁膜43とを第1層間絶縁膜44とする。なお、その第4絶縁膜43の厚さは、シリコン基板20の平坦面上で約1000nmである。

【0107】

続いて、CMP(Chemical Mechanical Polishing)法により第1層間絶縁膜44の上面を研磨して平坦化する。その後に、フォトリソグラフィにより第1層間絶縁膜44をパターニングして第1〜第9ホール44a〜44iを形成する。これらのホールのうち、第1ホール44aは、パッド部25bのコンタクト領域CR上に位置しており、第1、第2開口30b、29aの内側に形成される。また、残りの第2〜第9ホール44b〜44iは、それぞれ第1〜第8コバルトシリサイド層41a〜41hの上に形成される。そして、上記の第1ホール44aの下にはONO膜で構成される第2絶縁膜26が形成されていないため、第2周辺回路領域IIIにおける第4〜第9ホール44a〜44iを形成するのと同じ条件で第1ホール44aを形成することにより、パッド部25bの表面を露出させることができる。

【0108】

次に、図15(a)に示す断面構造を得るまでの工程について説明する。

【0109】