半導体装置の製造方法

【課題】一連の露光工程を含む半導体装置の製造において、縦横比が可変な露光装置と縦横比が固定の露光装置を使い分けることにより、半導体装置の製造費用を低減させる。

【解決手段】半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。

【解決手段】半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に半導体装置の製造に係り、特に露光技術に関する。

【背景技術】

【0002】

半導体装置の高速化の要求に伴い、今日では半導体ウェハなどの被露光基板表面に形成されるパタ―ンは非常に微細化している。また今日では、半導体装置の多機能化の要求に伴い、被露光基板上に多数のパタ―ンを重ねて露光する必要が生じている。このような非常に微細なパタ―ンを多数重ねて露光する場合には、被合わせ層におけるパタ―ンと合わせ層におけるパタ―ンとの間に高精度の位置合わせが重要になる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平6−104156号公報

【特許文献2】特開2009−231564号公報

【特許文献3】特開平10−172878号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

複数の層を重ねて半導体装置を製造する際、通常は、被位置合わせ層とその上に形成される位置あわせ層との間で位置合わせをすればことが足りる。順次行われるこのような位置合わせの結果、最下層のパタ―ンと最上層のパタ―ンとの間で大きな位置ずれが生じても、通常は問題にはならない。

【0005】

ところで一般的な半導体装置、例えば多層配線構造を有する半導体装置では、下層の配線パタ―ンの方が微細でパタ―ン密度も高く、上層の配線パタ―ンに移行するにつれて配線パタ―ンの設計ルールが緩くなり、またパタ―ン密度もより粗になる傾向がある。このような微細なパターンの露光には通常、スキャナとよばれる、レチクル上のパタ―ンを一方向に走査し、かつ被処理基板Wを逆方向に走査しながら露光をスリット状の部分部分に分けて行う縮小投影露光装置が使われることが多い。

【0006】

しかしスキャナは高価であり、またスキャナを使って露光を行った場合には、露光のスループットが低くなるため、例えば多層配線構造の上層の配線パタ―ンを形成する場合などは、レチクル上のパタ―ンを一括して露光できるステッパとよばれる縮小投影露光装置を使い、露光のスループットを上げたいという要求が存在する。

【0007】

ところがスキャナでは露光がスリット状の部分部分にわけて、かつレチクルおよび被処理基板をそれぞれの方向に送りながら行われるため、被処理基板のプロセス工程上における伸縮に対応して、伸縮したショットに対応して、当該レチクル上のパターンの当該被処理基板上への投影に際して、当該レチクルパターンの縦横比を変化させることができ、また半導体装置全体で見るとパタ―ンの縦横比が、露光装置の制御機構の精度に起因した位置ずれにより、下層と上層で変化することがある。これに対し、ステッパではレチクル上のパタ―ンが一括して露光されるため、縦横比は、光学系の誤差を除けば通常は1:1に原理的に固定されており、変化することがない。

【0008】

そこで一連のパタ―ンがスキャナを使って順次露光され形成されている被処理基板上に、ステッパを使って上層パタ―ンを重ねて露光しようとすると、縦横比の誤差の累積により、露光位置合わせが出来なくなる場合が生じることがある。このような場合には、前記一連の下層パタ―ンが形成されている被処理基板を破棄する以外に方法がない。

【課題を解決するための手段】

【0009】

一の側面によれば半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。

【発明の効果】

【0010】

本発明によれば、一連の露光工程を含む半導体装置の製造の際に、縦横比が可変なスキャナなどの露光装置と縦横比が固定のステッパなどの露光装置使い分けることが可能となり、半導体装置の製造費用を低減させることができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態で製造される半導体装置の例を示す断面図である。

【図2A】図1の半導体装置において形成されるアラインメントマークの例を示す断面図である。

【図2B】図1の半導体装置において形成される位置ずれ検出マークの例を示す断面図である。

【図3】半導体装置に形成されたアラインメントマークと位置ずれ検出マークを示す平面図である。

【図4】図1の半導体装置の位置合わせ系列を示す工程図である。

【図5】本実施形態で使われる縦横比が可変な縮小投影露光装置の例を示す図である。

【図6A】被処理基板上に生じる露光パタ―ンの歪みの例を示す平面図である。

【図6B】被処理基板上に生じる露光パタ―ンの歪みの別の例を示す平面図である。

【図7】被処理基板上における露光パタ―ンの基本的な位置ずれの例を示す平面図である。

【図8】本実施形態による露光プロセスを示すフローチャートである。

【図9】被処理基板上に重畳して形成された露光パタ―ンの位置ずれの例を示す平面図である。

【図10】図9の状態から位置合わせを行った場合の、被処理基板上に重畳して形成された露光パタ―ンの例を示す平面図である。

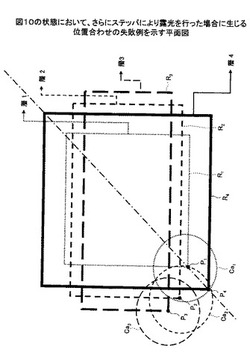

【図11】図10の状態において、さらにステッパにより露光を行った場合に生じる位置合わせの失敗例を示す平面図である。

【図12】図11の状態に対して行われる縦横比の調整を説明するための平面図である。

【図13】図12において縦横比調整後の状態を示す平面図である。

【図14】係数kあるいはk1,k2の決定方法の概略を示すグラフである。

【図15A】本実施形態における位置合わせ系列の例を示す図である。

【図15B】図15Aの位置合わせ系列に対応する位置合わせ結果を比較対照例と比較して示す表の図である。

【図16】図8において、前記図12の縦横比の調整に係る部分を示すフローチャートである。

【図17】本発明の考え方を説明する図である。

【発明を実施するための形態】

【0012】

[第1の実施形態]

図1は、第1の実施形態により製造される、シリコン基板11上に形成されたトランジスタTrを含む半導体装置10を示す断面図である。図1の半導体装置10の例では、前記トランジスタTr上に層間絶縁膜15〜19が積層されている。

【0013】

図1を参照するに、前記シリコン基板11中には素子分離領域11Iにより素子領域11Aが画成されており、前記シリコン基板11上にはゲート絶縁膜12を介してゲート電極13が形成されている。

【0014】

前記素子領域11Aでは前記シリコン基板11中、前記ゲート電極13の第1の側および第2の側に、n型あるいはp型の拡散領域よりなるソースエクステンション領域11aとドレインエクステンション領域11bが形成され、さらにゲート電極13の前記第1の側では、ゲート電極13直下のチャネル領域11chから見て側壁絶縁膜13Aの外側にn+型あるいはp+型の拡散領域よりなるソース領域が、また前記ゲート電極13の前記第2の側では前記チャネル領域11chから見て側壁絶縁膜13Bの外側に、n+型あるいはp+型の拡散領域よりなるドレイン領域が形成されている。

【0015】

前記ゲート電極13は絶縁膜14により覆われ、前記絶縁膜14中には前記ソース領域11aにコンタクトして第1のビアプラグ14Aが、また前記ドレイン領域11bにコンタクトして第2のビアプラグ14Bが形成されている。

【0016】

さらに前記絶縁膜14上には、前記層間絶縁膜15〜19を積層した多層配線構造20が形成されている。

【0017】

図示の例では前記層間絶縁膜15は第1層の配線パタ―ン15L,15Mおよび第1層のビアプラグ15Cを含み、前記配線パタ―ン15Lはビアプラグ14Bに、配線パタ―ン15Mはビアプラグ14Aに電気的に接続されている。またビアプラグ15Cは配線パタ―ン15Lに整合し、かつ前記配線パタ―ン15Lに電気的に接続されている。

【0018】

さらに前記層間絶縁膜16は第2層の配線パタ―ン16Lおよび第2層のビアプラグ16Cを含み、前記配線パタ―ン16Lは前記ビアプラグ15Cに整合し、かつ前記ビアプラグ15Cに電気的に接続される一方、ビアプラグ16Cにも整合し、かつ前記ビアプラグ16Cに電気的に接続されている。

【0019】

さらに前記層間絶縁膜17は第3層の配線パタ―ン17Lおよび第3層のビアプラグ17Cを含み、前記配線パタ―ン17Lはその下のビアプラグ16Cに整合し、かつ前記ビアプラグ16Cに電気的に接続される一方、前記ビアプラグ17Cにも整合し、かつ前記ビアプラグ17Cに電気的に接続されている。

【0020】

さらに前記層間絶縁膜18は第4層の配線パタ―ン18Lおよび第4層のビアプラグ18Cを含み、前記配線パタ―ン18Lはその下のビアプラグ17Cに整合し、かつ電気的に接続される一方、前記ビアプラグ18Cにも整合し、かつ電気的に接続されている。

【0021】

さらに前記層間絶縁膜19は第5層の配線パタ―ン19Lおよび第5層のビアプラグ19Cを含み、前記配線パタ―ン19Lはその下のビアプラグ18Cに整合し、かつ電気的に接続される一方、前記ビアプラグ19Cにも整合し、かつ電気的に接続されている。

【0022】

ただし本発明は、図1に示したような、各層の配線パタ―ンおよびビアプラグが基板に垂直な方向に整列している場合に限定されるものではなく、前記多層配線構造20中に様々な回路パターンが形成されている場合をも含むものである。

【0023】

このような多層配線構造20をフォトリソグラフィにより形成する際には、第1層の配線パタ―ン15Lに第1層のビアプラグ15Cを位置合わせし、さらに第1層のビアプラグ15Cに第2層の配線パタ―ン16Lを位置合わせし、前記第2層の配線パタ―ン16Lに第2層のビアプラグ16Cを位置合わせし・・・という一連の位置合わせ工程が必要になる。

【0024】

図2Aは、このような層間絶縁膜15〜19中に形成され、フォトリソグラフィ工程の際に配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの位置合わせに使われるアラインメントマークALの例を、また図2Bは、前記層間絶縁膜15〜19中に形成され、同じくフォトリソグラフィ工程の際に配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの位置ずれの検出に使われる位置ずれ検出マークDvの例を示す断面図である。

【0025】

図2Aを参照するに、アラインメントマークALは前記層間絶縁膜15〜19中に、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cの各々に対応して、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cと同時に形成されており、前記アラインメントマークALは、フォトリソグラフィ工程の際にx軸方向への位置検出に使われるマークALxとy軸方向への位置検出に使われるマークALyより構成されている。マークALxとマークALyとは対をなしており、配線パタ―ン15L,ビアプラグ15C,配線パタ―ン16L,ビアプラグ16C・・・に対応して、位置をずらしながら形成されている。例えば前記マークALxのx軸方向への繰り返しを検出し、その中央の位置をもって、マークALxのx座標値を読み取ることが可能であり、また前記マークALyのy軸方向への繰り返しを検出し、その中央の位置をもって、マークALyのy座標値を読み取ることができる。

【0026】

これに対し図2Bを参照するに位置ずれ検出マークDvも前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cの各々に対応して、前記層間絶縁膜15〜19中に前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cと同時に形成されており、各々の位置ずれ検出マークDvは、合わせパタ―ンDvUと被合わせパタ―ンDvLとにより構成されている。

【0027】

例えば図示の例では、合わせパタ―ンDvUが、その下の破線で示した被合わせパタ―ンDvL'に、前記基板11に垂直方向から見た場合に含まれるように形成されており、その結果、フォトリソグラフィ工程による前記配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの形成の際、前記合わせパタ―ンDvUと被合わせパタ―ンDvL'との、前記基板11に垂直方向から見た位置関係をもとに、合わせパタ―ンDvUの被合わせパタ―ンDvL'に対する位置ずれ、従って例えばビアプラグ15Cの配線パタ―ン15Lに対する位置ずれなどが検出される。

【0028】

位置ずれ検出マークDvも、配線パタ―ン15L,ビアプラグ15C,配線パタ―ン16L,ビアプラグ16C・・・に対応して、位置をずらしながら、任意の配線パタ―ンあるいはビアプラグ、例えばビアプラグ15C、に対応する合わせマークDvUに対して一つ下のビアプラグあるいは配線パタ―ン、例えば15L、に対応する被合わせマークDvL'が重なるように、また前記合わせマークDvUと同じ層で隣接する被合わせマークDvLに対しては、一つ上の配線パタ―ンあるいはビアプラグ、例えば配線パタ―ン16L、の合わせマークDvUが重なるように形成されている。

【0029】

このようなアラインメントマークALおよび位置ずれ検出マークDvを使うことにより前記ビアプラグ15Cが前記配線パタ―ン15Lに位置合わせされ、前記配線パタ―ン16Lが前記ビアプラグ15Cに位置合わせされ、前記ビアプラグ16Cが前記配線パタ―ン16Lに位置合わせされ、前記配線パタ―ン17Lが前記ビアプラグ16Cに位置合わせされ、前記ビアプラグ17Cが前記配線パタ―ン17Lに位置合わせされ、前記配線パタ―ン18Lが前記ビアプラグ17Cに位置合わせされ、前記ビアプラグ18Cが前記配線パタ―ン18Lに位置合わせされ、前記配線パタ―ン19Lが前記ビアプラグ18Cに位置合わせされ、前記ビアプラグ19Cが前記配線パタ―ン19Lに位置合わせされる。

【0030】

これに伴い、図2Aおよび図2Bに示すように、前記層間絶縁膜15〜19中にはそれぞれの配線パタ―ンおよびビアプラグのためのアラインメントマークALおよび位置ずれ検出マークDvが、位置をずらしながら順次形成されることになる。

【0031】

図3は、このようにして形成された図1の半導体装置10における多層配線構造20を基板11に垂直な方向から見た平面図である。

【0032】

図3を参照するに、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cが形成される「露光ショット」と表記した半導体パタ―ン形成領域を囲んで、図示の例では四隅A〜Dに、前記アラインメントマークALおよび位置ずれ検出マークDvがそれぞれ形成されている。前記図2A,2Bに示したように、前記アラインメントマークALおよび位置ずれ検出マークDvは、前記各々の隅A〜Dにおいて順次ずらして形成されているため、図3の平面図では一列に整列して見え、前記層間絶縁膜15〜19を透かしてそれぞれのアラインメントマークALおよび位置ずれ検出マークDvを読み取ることが可能である。

【0033】

図4は、このようなアラインメントマークALおよび位置ずれ検出マークDvにより検出された位置ずれに基づいて行われる、図1の半導体装置10をフォトリソグラフィにより製造する際の位置合わせ系列の例を示す工程図である。

【0034】

図4を参照するに、ステップ1において素子分離領域11I(ISO)が形成され、ステップ2において前記素子分離領域11Iに対してゲート電極13(Gate)が、位置合わせの後、露光により形成されたレジストパターンをマスクに、ドライエッチングにより形成される。さらにステップ3において前記ステップ2と平行して、イオン注入マスクが位置合わせされ、前記シリコン基板11の所定領域に第1回目のイオン注入(ii)が実行される。これにより、例えば前記シリコン基板11中にソースエクステンション領域11aおよびドレインエクステンション領域11bが形成される。

【0035】

前記ステップ2および3の後、ステップ4において、例えば図1の例ではビアプラグ14A,14Bを含む配線層C1を形成するためのマスク位置合わせが、前記ゲート電極13のパタ―ンに対して行われ、またこれに平行してステップ5において、前記ゲート電極13に対して次のイオン注入マスクが位置合わせされ、前記シリコン基板11の所定領域に第2回目のイオン注入(ii)が実行され、前記ソース領域およびドレイン領域11c,11dが形成される。

【0036】

さらにステップ6において、図1の半導体装置10の例では配線パタ―ン15L,15Mに対応する配線層L1のパターニングのためのマスク位置合わせがなされ、さらに対応して形成された金属膜をパターニングすることにより、配線パタ―ン15L,15Mを含む配線層L1が形成される。

【0037】

さらにステップ7において例えば前記ビアプラグ15Cを含む配線層C2のパターニングのためのマスク位置合わせがなされ、引き続き前記配線層C2のパターニングが行われる。

【0038】

さらにステップ8において、図1の半導体装置10の例では配線パタ―ン16Lを含む配線層L2のパターニングのためのマスク位置合わせがなされ、さらに対応する金属膜をパターニングすることにより、前記配線層L2のパターニングが行われる。

【0039】

さらにステップ9において例えば前記ビアプラグ16Cを含むビアプラグC3のパターニングのためのマスク位置合わせがなされ、引き続き、前記配線層C3のパターニングが行われる。

【0040】

さらにステップ10において図1の半導体装置10の例では配線パタ―ン17Lを含む配線層L3のパターニングのためのマスク位置合わせがなされ、さらに対応する金属膜をパターニングすることにより、配線層L3のパターニングが行われる。

【0041】

さらにこのような工程を繰り返すことにより、前記図1の半導体装置10が得られる。

【0042】

図5は、本実施形態で使われる縮小投影露光装置30の例を示す。

【0043】

図5を参照するに縮小投影露光装置30はいわゆるスキャナであり、光源31と、被処理基板Wを保持して移動させるウェハ走査ステージ32を含み、前記光源31とウェハ走査ステージ32の間には、第1の実施形態による露光マスク34を担持するレチクル走査ステージ33が設けられている。

【0044】

前記光源31は、例えばエキシマレーザなど、深紫外(DUV)波長の露光ビームを発生する光源であり、前記光源31から出射した露光ビームはミラー35で反射された後、コリメートレンズ系36により前記レチクル走査ステージ33上の露光マスク34に平行光ビームとして照射される。

【0045】

このようにして前記露光マスク34に照射された露光ビームは前記露光マスク34を通過する際に露光マスク14のレチクルが保持している所望の半導体装置の露光パタ―ンに従って整型され、前記レチクル走査ステージ33とウェハ走査ステージ32の間に設けられた投影レンズ系37により、前記被処理基板Wの表面に集束され、前記被処理基板W上のレジスト膜が所望の露光パタ―ンに従ってスリット状に露光される。

【0046】

前記縮小投影露光装置30はスキャナであるため、前記レチクル走査ステージ13が図5中の矢印Aの方向に移動され、また前記被処理基板Wが矢印Bの方向に移動され、前記レチクル上の露光パタ―ン全体の露光がなされる。このようなスキャナを使った場合、前記矢印Aおよび矢印Bの方向への走査速度により、前記被処理基板W上に露光されるパタ―ンにおいて縦横比を変化させることができる。具体的には、図5中の水平方向の投影倍率に関しては、X方向のレチクル上のパターンのウェハ上への投影倍率を、投影レンズ系内のレンズ倍率制御機構によって変化させることが可能であり、図5中の垂直方向の投影倍率は、レチクルの走査スピードとウェハの走査速度の差を利用して変化させることが可能であり、その結果X方向とY方向の相対的な倍率差を変化させることが可能となっている。

【0047】

図6Aは、前記スキャナ30を使って被処理基板W上に素子分離領域11Iを形成した後、さらにゲート電極13を重畳して露光した場合の位置ずれ、ないし歪みの例を、また図6Bは、ゲート電極13上にビアプラグ14A,14Bを重畳して露光した場合の位置ずれ、ないし歪みの例を示す。図6Aおよび図6B中、実線の四角形は被処理基板W上の正規の四角形(正方形)を、破線は露光の際に位置ずれが生じて歪んだ四角形を示している。また前記四角形の各稜点の矢印は、それぞれの稜点の変位を示しているが、前記縮小投影露光装置30がスキャナであるため、変位の方向および変位量は様々であるのがわかる。

【0048】

このような位置ずれ成分には、x軸方向の並進ズレ成分である「Shift_X」、y軸方向の並進ズレ成分である「Shift_Y」、ウェハ全体のx軸方向に関する倍率ズレ成分である「wafer_mag_X」、ウェハ全体のy軸方向に関する倍率ズレ成分である「wafer_mag_Y」、ウェハ全体のx軸方向への回転ズレ成分である「wafer_rot_X」、ウェハ全体のy軸方向への回転ズレ成分である「wafer_rot_Y」、さらにx軸方向へのショットの倍率ズレ成分である「shot_mag_X」、y軸方向へのショットの倍率ズレ成分である「shot_mag_Y」、x軸方向へのショットの回転ズレ成分である「shot_rot_X」、およびy軸方向へのショットの回転ズレ成分である「shot_rot_Y」が含まれる。

【0049】

数学的に示せば、x方向の位置ずれ量は、

(Xmi+Xci)×wafer_mag_X + (Ymi+Yci)×wafer_rot_Y + shot_mag_X×Xmi+ shot_rot_Y ×Ymi+ Shift_X)+εx

であり、

y方向の位置ずれ量は、

(Ymi+Yci)×wafer_mag_Y + (Xmi+Xci)×wafer_rot_X + shot_mag_Y×Ymi+ shot_rot_X ×Xmi+ Shift_Y+εy)

である。

【0050】

ここで、Xciは、ウェハ内のi番目の位置ずれ計測の属するショットのショット中心座標をウェハ中心を原点(0, 0)とした際のウェハ内座標位置であり、Xmiは、同様にウェハ内のi番目の位置ずれ計測位置を、その属するショットの中心座標であるXciを原点(0, 0)にした際のショット内座標位置である。また、εx, εyはそれぞれ、x方向、y方向の非線形位置ずれ成分である。

【0051】

図7は、上記位置ずれ成分「Shift_X」,「Shift_Y」,「wafer_mag_X」,「wafer_mag_Y」,「wafer_rot_X」,「wafer_rot_Y」,「shot_mag_X」,「shot_mag_Y」,「shot_rot_X」、および「shot_rot_Y」の例を示す平面図である。

【0052】

図7中、破線は正規のパタ―ンを、実線はそれぞれの位置ずれが生じた状態を示している。

【0053】

図7を参照するに位置ずれ成分「Shift_X」,「Shift_Y」は、それぞれx軸方向およびy軸方向への平行移動に対応しており、「wafer_mag_X」,「wafer_mag_Y」は、それぞれウェハ全体としてのx軸方向およびy軸方向への倍率のずれに対応しており、「wafer_rot_X」,「wafer_rot_Y」は、それぞれウェハ全体としてのx軸方向およびy軸方向への変形に対応しており、「wafer_rot_X」,「wafer_rot_Y」を組みあわせることで、ウェハ全体の回転を表すことができる。

【0054】

さらに図7において「shot_mag_X」,「shot_mag_Y」は、個々のショットにおけるx軸方向およびy軸方向への倍率のずれに対応し、「shot_rot_X」および「shot_rot_Y」は、個々のショットにおけるx軸方向およびy軸方向への変形に対応している。「shot_rot_X」,「shot_rot_Y」を組みあわせることで、当該ショットの回転を表すことができる。例えば、「shot_mag_X」,「shot_mag_Y」の符号を時計周りを+に取った場合、「(shot_mag_X+shot_mag_Y)/2」がショットの回転に該当する。

【0055】

このような露光装置における位置ずれについては、図6A,図6Bに矢印で示した各位置ずれ成分のロット単位の処理履歴:つまりロット単位で、その中の数枚のウェハに対して位置ずれ計測を行い、その計測データの解析結果を、ロットの位置ずれの出来栄えを表す尺度、としてデータベースに登録されており、例えば図4のようなフォトリソグラフィ工程を実行する際には、予想される位置ずれを前記データベースより読み出し、補正を行ってから露光を実行することがなされている。

【0056】

図8は、このような露光工程の例を示すフローチャートである。

【0057】

図8を参照するに、ステップ11においてあるロットの被処理基板Wが入来すると、ステップ12において、前記縮小投影露光装置30は前記データベースを参照して、そのロットについて最適な補正量を決定する。このような補正量には、図6A,6Bに示した各成分についての位置ずれ補正値の他に、最適な線幅を得るための最適な露光量の補正値が含まれる。このような最適補正量の決定は、それ以前のロットについての最適補正量の変化を、例えば移動平均を計算して外挿すること、などによりなされる。

【0058】

次にステップ13において前記最適補正量を使って補正した露光データにより被処理基板Wを露光し、レジストパターンを現像する。

【0059】

さらにステップ14において、現像により得られたレジストパターンを、顕微鏡を使って検査し、実際の位置ずれの値を求める。より具体的には、顕微鏡で観察される位置ずれ計測用の被合わせマークと合わせマークの重なり具合(位置ずれ量)を画像処理によって求める。

【0060】

さらにステップ15において、前記ステップ14で求められた実際の位置ずれの値が許容範囲内に収まっているか否かを判定し、収まっている場合(YES)ならばステップ16の線幅検査に進み、線幅を求める。

【0061】

さらにステップ17において、前記ステップ16で求められた線幅が許容範囲内である(YES)と判定されると、ステップ18で次の工程に進む。

【0062】

一方、前記ステップ15において位置ずれが許容範囲を超えている(NO)と判定された場合にはステップ19において、先にステップ13で形成されたレジストパターンが除去され、さらにステップ20において、前記ステップ14で求められた真の位置ずれの値を元に、前記ステップ12で求められた補正値が修正され、再びステップ13に戻り、前記修正された補正値を使って露光および現像が行われる。また同時にステップ12で使われたデータベースが、最新の位置ずれ補正値により更新される。

【0063】

同様にステップ17で露光線幅が許容範囲を超える(NO)と判定された場合にも、ステップ19において既存のレジストパターンは除去され、さらにステップ20において前記ステップ16で求められた真の露光線幅の値を元に、前記ステップ12で求められた露光量の最適補正値が修正され、再びステップ13に戻り、前記修正された補正値を使って、露光および現像が行われる。また同時にステップ12で使われたデータベースが、最新の露光量により更新される。

【0064】

図9は、前記図5のスキャナ30を使って、被処理基板W上に、層1〜層3まで、同一の矩形パタ―ンを重畳露光した際の位置ずれおよび位置合わせを説明する平面図である。

【0065】

図9を参照するに、最初に非露光基板W上に層1の露光および現像がなされ、前記露光および現像の結果得られたレジストパターンをマスクとしたエッチングにより、前記被処理基板W上には例えば点線で示した矩形パタ―ンR1が形成される。

【0066】

次に破線で示した層2の露光が、前記層1の露光で形成された矩形パタ―ンR1に重畳して実行される。

【0067】

図示の例では層2の露光で形成される矩形パタ―ンR2は、層1の露光で形成される矩形(正方形)パタ―ンR1と同一のパタ―ンであり、露光の際の位置ずれが生じていなければ、矩形パタ―ンR2は矩形パタ―ンR1と一致するはずのものであるが、図9では実際は、前記矩形パタ―ンR2は横長に変形されている。このような位置ずれないしパタ―ンの変形は、例えば図5のスキャナ30における光学系の誤差の他、レチクル走査ステージ13の走査速度やウェハ走査ステージ32のずれなどに起因して生じており、x軸方向およびy軸方向への倍率のずれの結果生じるものである。層3の矩形パタ―ンR3も同様である。なお図9において前記層1〜層3の矩形パタ―ンR1〜R3の中心は、位置合わせされているものとする。すなわち図9では、実際にはウェハ内のショット毎に、当該中心位置はずれているが、ショットの倍率による位置ずれの影響を分かりやすく示すために当該中心位置はずれていないものとして表現している。

【0068】

図9中、各矩形パタ―ンの右下稜点P1,P2,P3に付した円Ca1,Ca2,Ca3は位置合わせ許容誤差範囲を示しており、例えば層1の矩形パタ―ンR1の左下稜点P1の円Ca1内に層2の矩形パタ―ンR2の左下稜点P2が入っていれば、層1と層2の位置ずれは許容範囲にあると考えられる。層1と層2の中心が一致しており、左右上下対象であり、そのコーナー(最大位置ずれ量が発生する場所)が位置ずれ許容範囲であれば層1と層2のすべてのパターンについて許容範囲にあるということである。

【0069】

図9の例では、前記稜点P2は前記円Ca1内に入っており、矩形パタ―ンR1と矩形パタ―ンR2とは許容範囲内で位置合わせされているが、矩形パタ―ンR3では稜点P3が矩形パタ―ンR2の許容範囲Ca2を外れていることがわかる。

【0070】

そこでこのような場合、通常は前記矩形パタ―ンR3を露光する際のx軸方向およびy軸方向への倍率ShotMag_XおよびShotMag_Yを、図9中に矢印Δ1で示すように前記矩形パタ―ンR3の稜点P3が前記円Ca2内に入るように補正する。なお前記図9において、また以後の説明においても、前記Shift_X,Shift_Y,wafer_mag_X,wafer_mag_Y,wafer_rot_Xおよびwafer_rot_Yの各成分については、すでに補正がなされているものとする。

【0071】

図10は、このような補正を行って形成した矩形パタ―ンR1〜R3を示す平面図である。

【0072】

図10を参照するに、前記図9に示した矢印Δ1の補正の結果、前記稜点P3は前記稜点P2における許容範囲円Ca2内に収まっているのがわかる。

【0073】

このように、縮小投影露光装置としてスキャナを使っている限り、相前後して露光される二つの層の間で位置ずれを許容範囲内に維持することにより、所望の半導体装置を製造することが可能であるが、一方、多層配線構造の上層に形成される配線パタ―ンあるいはビアプラグパタ―ンについては、パタ―ン幅が下層の微細な配線パタ―ンに比較して広いので、より露光スループットの高いステッパを使って露光を行いたい要望がある。

【0074】

しかしステッパでは、露光装置の図示および構成についての説明は省略するが、倍率の縦横比が通常は1:1に固定されていて、x軸方向への倍率ShotMag_Xとy軸方向への倍率ShotMag_Yを別々に変化させることはできず、図9,図10に示した位置ずれ補正方法は使えない。

【0075】

図11は、層1〜層3においてスキャナ30を使い、前記図10に示す矩形パタ―ンR1〜R3を形成した後、ステッパを使って層4の矩形パタ―ンR4を形成した本実施例の比較例を示す平面図である。

【0076】

図11を参照するに、図示の例では図10に示す矩形パタ―ンR1〜R3に矩形パタ―ンR4が重畳して露光されているが、パタ―ンR4の右下稜点P4が、円Ca3で示す、その直下の矩形パタ―ンR3の位置ずれ許容範囲から大きく外れていることがわかる。

【0077】

矩形パタ―ンR4を露光する縮小投影露光装置はステッパであるため、縦横の倍率は別々に変化させることはできず、このため倍率を調整しても、前記稜点P4は図中に一点鎖線で示す線の上を移動することしかできない。

【0078】

このため、図11のような状態が生じると、矩形パタ―ンR4の矩形パタ―ンR3に対する位置合わせは失敗したことになる。

【0079】

これに対し本実施形態では前記層1を基準層とし、図12に示すように、層3における矩形パタ―ンR3の稜点P3を、Δ2で表したベクトルに従って、基準層1の稜点P1の近傍の×で示した位置P3'に移動させ、前記矩形パタ―ンR3の縦横比を、図13に示すように、基準層1における矩形パタ―ンR1の縦横比に近づけている。ここで図13は、前記図12の調整の結果得られた矩形パタ―ンR3を、前記矩形パタ―ンR1,R2,R4に重畳して示している図である。

【0080】

このように矩形パタ―ンR3を基準層1における矩形パタ―ンR1に対して補正しておくことにより、縦横比の調整後においても稜点P3は矩形パタ―ンR2の位置ずれ許容範囲円Ca2の内側になお含まれ、かつ矩形パタ―ンR4の稜点P4が矩形パタ―ンR3の位置ずれ許容範囲円Ca3の内側に含まれるようにすることができる。

【0081】

以下、本発明の考え方を、図17を参照しながらより具体的に説明する。

【0082】

図17における稜点P1,P2,P3は図12の矩形パタ―ンR1の稜点P1,矩形パタ―ンR2の稜点P2,矩形パタ―ンR3の稜点P3にそれぞれ対応するものであるが、本願発明では稜点P3の位置ずれパラメータの決定にあたって、まず、過去の稜点P3と稜点P2の位置ずれの最適解を基に、当該最適解の移動平均等を用いた手法を適用する。ここで、最適解とは、例えばShiftXを例に取れば、設定したShiftX(set)に対して実際に得られた位置ずれをShiftXをShiftX(result)として、ShiftXが0であるべき最適ShiftX(optimum)は、

ShiftX(optimum) = ShiftX(set)−ShiftX(result)

の関係を満たすものと定義される。ここでは、位置ずれがXnmである場合、−Xnmの設定することで位置ずれが0nmになるように最適解の符号を定義している。

【0083】

一般には、このような過去のロット単位あるいはウェハ単位の最適解に対して、移動平均あるいは加重移動平均をとることによって、次に露光すべきロットの最適解を予測する手法が用いられている。ただし、ここでいう従来使われている最適解とは、あくまでも被合わせ層と合わせ層に関する最適解であり、それ以外の層に対しては問題としていない。

【0084】

これに対し本願発明は、このように稜点P3−P2に関する最適解の予測値として過去のロットの最適解の移動平均あるいは加重移動平均を出発点として用いるが、当該最適解の予測値に対して、これから露光すべきロットの過去の履歴、すなわち当該ロットの稜点P2−P1間の位置ずれ(本件では倍率のみを取り扱う)をもさらに考慮するものである。

【0085】

図17では、稜点P3に対して、移動平均等で求めた最適予測値の結果倍率ShiftX(result),ShiftY(result) がずれているわけであるが、本願発明では、その最適予測値に対して、kΔ1の補正を行い、稜点P3を其の分だけ、基準層1の矩形パタ―ンR1の稜点P1に近づける。ここで図17におけるベクトルΔ1は、基準層1に対して層2を、過去のデータベースに基づいて最適化した場合の稜点P1に対する稜点P2のずれを示しており、理想的に最適化された場合にはゼロになるべきものであるが、最適化を過去のデータベースに基づいて行っているため、ゼロにはなっておらず、ベクトルΔ1だけのずれが発生している。

【0086】

このような状況で、さらに層3を層2に対して過去のデータベースに基づいて最適化した後、さらに層1に対して調整を行おうとすると、まず矩形パタ―ンR3を矩形パタ―ンR2に対して最適化した場合の稜点P3の位置の計算値、ないし予測値が得られるので、このようにして得られた稜点P3の位置を出発点として、これを基準層1の稜点P1の位置に近づける調整を行う。

【0087】

図示の例では、稜点P3は稜点P2に対して大きくベクトルΔ2だけずれているため、一見すると、このような調整では、稜点P1に対する稜点P2のずれに対応するベクトルΔ1を前記稜点P3に対しても適用し、稜点P3をベクトルΔ1だけ移動させるのが妥当に考えられるかも知れない。しかし例えば実際の稜点P3が最適化の結果、稜点P2に一致している場合も考えられ、そのような場合には稜点P3は上記Δ1の補正分だけ稜点P2から稜点P1の方向にずれることになるため(図17中のベクトルkΔ1')、稜点P2に対する稜点P3の位置合わせ、すなわち層2に対する層3の最適化に対しては、図17中にベクトルΔ2'で示すように稜点P2を行き過ぎてしまい、逆に不利な補正となってしまうことがある。図17の状態では、まだ層3の露光はなされていないので、稜点P3の実際の位置はわかっていない。

【0088】

このように本発明では、層2と層3のみについてみると不利になるような補正をしてまでも、以降の層におけるスキャナとステッパの倍率差の調整が可能となるように層3の倍率補正をしているわけである。このため本発明では、図17に示すように層2に対して最適化された層3の矩形パタ―ンR3の稜点P3を基準層1の稜点P1に近づける調整を行う際に、ベクトルΔ1に例えば値が1/2の係数kを乗じて、倍率の予測値ShotMagX(予測値) ,ShotMagY(予測値)を、以下の式より求める。

ShotMagX(予測値) = ShotMagX(最適解予測値)+ k(ShotMagX(P2)−ShotMagX(P1)) (式1)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k(ShotMagY(P2)−ShotMagY(P1)) (式2)

なお図17においても各層1,2,3において矩形パタ―ンR1,R2,R3の中心は一致させられており、従って図17における各点の移動は倍率ShotMagX,ShotMagYの変化に対応していることに注意すべきである。

【0089】

層1は基準層であるので、ShotMagX(P1)、ShotMagY(P1)は0となり、層3の調整後の稜点P3の予測値ShotMagX(P3)(予測値),ShotMagY(P3)(予測値)は、次式

ShotMagX(P3)(予測値) = ShotMagX(P3)(最適解予測値)+ k(ShotMagX(P2)) (式3)

ShotMagY(P3)(予測値) = ShotMagY(P3)(最適解予測値)+ k(ShotMagY(P2)) (式4)

より求められる。なお上記ShotMagX(P2)、ShotMagY(P2) は、層1に対する層2の倍率ずれを意味している。

【0090】

ここで、倍率差が基準層から乖離するのを積極的に抑えることを目的として上式を、

ShotMagX(予測値) = ShotMagX(最適解予測値)− k(ShotMagX(P2)−ShotMagY(P2)) (式5)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k(ShotMagX(P2)−ShotMagY(P2)) (式6)

としてもよい。

また 汎用的な補正式としては、X方向倍率とY方向倍率の違いに対応して、

ShotMagX(予測値) = ShotMagX(最適解予測値)− k1×ShotMagX(P2) +k2×ShotMagY(P2) (式7)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k1×ShotMagX(P2)−K2×ShotMagY(P2) (式8)

とすると良い。

【0091】

ここで前記係数k、あるいはk1,k2は、上記の式による補正の結果、補正後の位置ずれの頻度分布が、図14の曲線Aで示すように平均して位置ずれゼロになるように、あるいは曲線Bで示すように位置ずれがゼロでなくても、所定の許容範囲に入るように選定される。なおここで「所定許容範囲」とは、前記縦横比補正後においても全ての層1〜4においてパタ―ンR1〜R4が位置合わせ許容誤差範囲であることを意味している。例えば図13の例では、前記縦横比の調整を行った後において、前記稜点P3'は、前記矩形パタ―ンR2の位置合わせ許容範囲円Ca2の内側に位置していなければならない。これに対し、前記係数k、あるいはk1,k2が大きすぎるなど不適切な場合には、曲線Cで示すように補正後に所定の許容範囲を超える位置ずれが生じることがある。

【0092】

前記係数k、あるいは係数k1,k2がゼロであると上記縦横比の補正はなされないことになるが、このような縦横比の補正が必要である限り、前記係数kあるいは係数k1,k2は0より大きな値をとる。先の図17の例ではk=1/2となっている。上記の説明から前記係数k,k1,k2は1.0以下となることが多いと考えられるが、1.0以下に限定されるものではなく、1.0を超える値をとることもありうる。

【0093】

以上の説明では、層1および層2を、スキャナを使った位置合わせ、および露光により形成し、さらにその後、層3を層2に対してスキャナを使って位置合わせする際、ステッパによる層4の形成に鑑み、前記層1を基準層として、これに縦横比を合わせた後、露光をしている。

【0094】

図15Aは、このような露光の繰り返しによる、先の図1と同様な多層配線構造形成の例を示す工程図である。

【0095】

図15Aを参照するに、まず基準層となる配線層L1が第1層として露光・現像、およびパターニングにより形成され、この配線層L1に対してビアプラグを含む配線層C2が第2層としてスキャナを使って位置合わせされ、引き続き露光・現像およびパターニングされる。この工程では位置合わせされる配線層L1が基準層であるため、それ以上の調整は必要ない。

【0096】

次に前記配線層C2のビアプラグパタ―ンに対して配線層L2層が第3層として、再びスキャナを使って位置合わせされる。その際、本実施形態では、前記配線層L2が、前記配線層C2のみならず、記基準層L1に対しても、スキャナを使って位置合わせをされ、これにより縦横比が、先に図11,12で説明したように調整される。

【0097】

さらに前記配線層L2が形成された後、これに対し配線層C3が第4層として、再びスキャナを使って位置合わせされる。その際、本実施形態では、前記配線層C3のビアプラグパタ―ンが、前記配線層L2のみならず、記基準層L1に対しても位置合わせされ、縦横比が先に図12,13で説明したように調整される。

【0098】

図15Aの工程では、このような一連の位置合わせ工程が、スキャナを使って繰り返し実行され、配線層L5がその下の配線層C5に第9層として位置合わせして形成される。さらに前記配線層L5が形成されると、今度はステッパを使って、前記配線層L5上に配線層C6が第10層として形成される。

【0099】

このような一連の位置合わせ工程を行った場合、最終的な配線層C6の前記基準層L1に対する相対位置ずれRP(L1−C6)は、上下層間で行われる各々の位置合わせ工程での相対位置ずれRP(C2−L1),RP(L2−C2),RP(C3−L2),RP(L3−C3)・・・の総和として、以下のように表される。

【0100】

RP(L1−C6)=RP(C2−L1)+RP(L2−C2)+RP(C3−L2)+RP(L3−C3)+RP(C4−L3)+RP(L4−C4)+RP(C5−L4)+RP(L5−C5)+RP(C6−L5) (式9)

ただしRP(C2−L1)は配線層C2と配線層L1との間の相対位置ずれ量、RP(L2−C2)は配線層L2と配線層C2の間の相対位置ずれ量、RP(C3−L2)は配線層C3と配線層L2の間の相対位置ずれ量・・・である。

【0101】

本実施形態では、このような相対位置ずれ量RP(C2−L1),RP(L2−C2),RP(C3−L2),RP(L3−C3)・・・を、品種毎、工程毎、ロット毎に計算し、データベース化しておく。

【0102】

図15Bは、かかる予測補正を行った場合において生じる位置ずれの具体例を、比較対照例と比較して示す表の図である。ただし図中の数値の単位はppmである。

【0103】

まず比較対照例で見ると、「L1基準位置ずれ」の欄における「ShotMagX」,「ShotMagY」の値は、それぞれ「位置ずれ結果」の欄の位置合わせ「L1−C2」,「C2−L2」,「L2−C3」・・・における「ShotMagX」あるいは「ShotMagY」の値を順次総和したものになっており、上式(9)に対応している。ここで「位置ずれ結果」の欄における倍率差、すなわち合わせ層と被合わせ層との間での位置合わせに伴う倍率差に注目すると、「位置ずれ結果」における値は絶対値で1.70を超えていないが、「L1基準位置ずれ」における値は、ステッパによるC6層の露光直前において3.15に達しているのがわかる。これは前記図10で説明した、位置合わせが失敗した例に対応している。

【0104】

これに対し前記図15Bの表における「本発明の効果」を注目すると、位置合わせ「L1−C2」,「C2−L2」,「L2−C3」・・・の各々において、合わせ層と被合わせ層との位置合わせの他に、基準層L1に対する位置合わせをも行っている結果、「位置ずれ予測」の欄における倍率差は、比較対照例の場合と比べてやや増大しているが、基準層L1に対する「L1基準位置ずれ予測」の欄における倍率差の値は、ステッパによる層C6の露光直前においても−0.64に過ぎず、ステッパによる位置合わせが可能な範囲に維持されていることがわかる。

【0105】

このような露光を行うため、本実施形態では前記図8のフローチャートにおいて、ステップ12の「当該ロットの補正値の決定」を、図16に示すフローチャートに従って実行する。

【0106】

図16を参照するに、前記ステップ12は、被合わせ層に対する合わせ層の中心を合わせる中心合わせステップ12Aと、前記ステップ12Aの後、当該ロット、例えばロットi、の当該ウェハにおける当該被合わせ層に対する当該合わせ層の位置ずれを、過去の位置ずれデータから例えば移動平均などにより予測し、位置合わせ補正値の予測値 ShotMagX(最適解予測値),ShotMagY(最適解予測値)を取得するステップ12Bと、当該ロットiの当該被合わせ層に対する当該合わせ層の位置合わせの際の相対位置ずれ量Δ1、ないしShotMagX(P2)−ShotMagX(P1),ShotMagY(P2)−ShotMagY(P1)をデータベースより取得し、前記ステップ12Bで取得された予測値ShotMagX(最適解予測値),ShotMagY(最適解予測値)を、前記相対位置ずれ量Δ1を使って、例えば式(1),(2)、あるいは式(3),(4)、あるいは式(5),(6)、あるいは式(7),(8)により補正し、基準層に対する位置合わせ補正値の縦横比を調整するステップ12Cと、を含んでいる。

【0107】

なお本実施形態による位置合わせは、図15Aに示したような直列的な層L1〜C6までの位置合わせに限定されるものではなく、先に図4で説明したようなステップS1〜ステップS10の位置合わせなど、他の位置合わせ系列に対しても適用可能である。

【0108】

さらに以上の説明においては、縦横比のずれが最も少なくなる最初の層L1を基準層として使ったが、基準層は最初の層L1に限定されるものではなく、例えば最初の層L1を露光した後、次の層C1を露光する前に、前記層L1のパタ―ンの座標絶対値を露光装置により読み取り、読み取った座標絶対値をもとに、仮想的な基準層を設定することも可能である。このように前記基準層L1は、最初に被処理基板上に露光されるパタ―ンに限定されるものではない。このような仮想的な基準層では、縦横比を、スキャナで露光されるパタ―ンの縦横比(1:1)に合わせて設定することができる。

【0109】

被処理基板上に最初に露光される層L1が基準層である場合には、前記層L1においては図16のステップ12Cは不必要でありスキップすることができるが、基準層が上に述べた例のように仮想的な基準層として露光装置に保持されている場合には、最初の層L1を露光する段階から、かかる仮想的な基準層を使ってパタ―ンの縦横比を調整することができる。

【0110】

また経験上、各層における縦横比の基準層からのずれが小さいことが知られている場合には、前記図15のステップS12Cの工程は、ステッパにおいて露光される層の直前の層に対してのみ実行することで、全体の露光処理スループットを向上させることができる。

【0111】

さらにステッパによる露光の後で、必要に応じてスキャナを使った露光を行っても構わない。すなわち本実施形態において、ステッパにより露光される層が半導体装置の最上層であるとは限らないことに注意すべきである。

【0112】

本実施形態による半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。その際前記第2の縦横比は、前記第1の縦横比よりも前記第2の露光装置の縦横比に近いことに注意すべきである。

【0113】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0114】

10 半導体装置

11 シリコン基板

11A 素子領域

11a ソースエクステンション領域

11b ドレインエクステンション領域

11c ソース領域

11d ドレイン領域

11I 素子分離領域

12 ゲート絶縁膜

13 ゲート電極

13A,13B 側壁絶縁膜

14,15,16,17,18,19 層間絶縁膜

14A,14B,15C,16C,17C,18C,19C ビアプラグ

15L,15M,16L,17L,18L,19L 配線パタ―ン

20 多層配線構造

30 縮小投影露光装置(スキャナ)

31 光源

32 ウェハ走査ステージ

33 レチクル走査ステージ

34 レチクル

35 ミラー

36 コリメートレンズ系

37 投影レンズ系

AL アラインメントマーク

Dv 位置ずれ検出マーク

L1,C2,L2,C3,L3,C4,L4,C5,L5,C6 配線層

W 被処理基板

【技術分野】

【0001】

本発明は一般に半導体装置の製造に係り、特に露光技術に関する。

【背景技術】

【0002】

半導体装置の高速化の要求に伴い、今日では半導体ウェハなどの被露光基板表面に形成されるパタ―ンは非常に微細化している。また今日では、半導体装置の多機能化の要求に伴い、被露光基板上に多数のパタ―ンを重ねて露光する必要が生じている。このような非常に微細なパタ―ンを多数重ねて露光する場合には、被合わせ層におけるパタ―ンと合わせ層におけるパタ―ンとの間に高精度の位置合わせが重要になる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平6−104156号公報

【特許文献2】特開2009−231564号公報

【特許文献3】特開平10−172878号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

複数の層を重ねて半導体装置を製造する際、通常は、被位置合わせ層とその上に形成される位置あわせ層との間で位置合わせをすればことが足りる。順次行われるこのような位置合わせの結果、最下層のパタ―ンと最上層のパタ―ンとの間で大きな位置ずれが生じても、通常は問題にはならない。

【0005】

ところで一般的な半導体装置、例えば多層配線構造を有する半導体装置では、下層の配線パタ―ンの方が微細でパタ―ン密度も高く、上層の配線パタ―ンに移行するにつれて配線パタ―ンの設計ルールが緩くなり、またパタ―ン密度もより粗になる傾向がある。このような微細なパターンの露光には通常、スキャナとよばれる、レチクル上のパタ―ンを一方向に走査し、かつ被処理基板Wを逆方向に走査しながら露光をスリット状の部分部分に分けて行う縮小投影露光装置が使われることが多い。

【0006】

しかしスキャナは高価であり、またスキャナを使って露光を行った場合には、露光のスループットが低くなるため、例えば多層配線構造の上層の配線パタ―ンを形成する場合などは、レチクル上のパタ―ンを一括して露光できるステッパとよばれる縮小投影露光装置を使い、露光のスループットを上げたいという要求が存在する。

【0007】

ところがスキャナでは露光がスリット状の部分部分にわけて、かつレチクルおよび被処理基板をそれぞれの方向に送りながら行われるため、被処理基板のプロセス工程上における伸縮に対応して、伸縮したショットに対応して、当該レチクル上のパターンの当該被処理基板上への投影に際して、当該レチクルパターンの縦横比を変化させることができ、また半導体装置全体で見るとパタ―ンの縦横比が、露光装置の制御機構の精度に起因した位置ずれにより、下層と上層で変化することがある。これに対し、ステッパではレチクル上のパタ―ンが一括して露光されるため、縦横比は、光学系の誤差を除けば通常は1:1に原理的に固定されており、変化することがない。

【0008】

そこで一連のパタ―ンがスキャナを使って順次露光され形成されている被処理基板上に、ステッパを使って上層パタ―ンを重ねて露光しようとすると、縦横比の誤差の累積により、露光位置合わせが出来なくなる場合が生じることがある。このような場合には、前記一連の下層パタ―ンが形成されている被処理基板を破棄する以外に方法がない。

【課題を解決するための手段】

【0009】

一の側面によれば半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。

【発明の効果】

【0010】

本発明によれば、一連の露光工程を含む半導体装置の製造の際に、縦横比が可変なスキャナなどの露光装置と縦横比が固定のステッパなどの露光装置使い分けることが可能となり、半導体装置の製造費用を低減させることができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態で製造される半導体装置の例を示す断面図である。

【図2A】図1の半導体装置において形成されるアラインメントマークの例を示す断面図である。

【図2B】図1の半導体装置において形成される位置ずれ検出マークの例を示す断面図である。

【図3】半導体装置に形成されたアラインメントマークと位置ずれ検出マークを示す平面図である。

【図4】図1の半導体装置の位置合わせ系列を示す工程図である。

【図5】本実施形態で使われる縦横比が可変な縮小投影露光装置の例を示す図である。

【図6A】被処理基板上に生じる露光パタ―ンの歪みの例を示す平面図である。

【図6B】被処理基板上に生じる露光パタ―ンの歪みの別の例を示す平面図である。

【図7】被処理基板上における露光パタ―ンの基本的な位置ずれの例を示す平面図である。

【図8】本実施形態による露光プロセスを示すフローチャートである。

【図9】被処理基板上に重畳して形成された露光パタ―ンの位置ずれの例を示す平面図である。

【図10】図9の状態から位置合わせを行った場合の、被処理基板上に重畳して形成された露光パタ―ンの例を示す平面図である。

【図11】図10の状態において、さらにステッパにより露光を行った場合に生じる位置合わせの失敗例を示す平面図である。

【図12】図11の状態に対して行われる縦横比の調整を説明するための平面図である。

【図13】図12において縦横比調整後の状態を示す平面図である。

【図14】係数kあるいはk1,k2の決定方法の概略を示すグラフである。

【図15A】本実施形態における位置合わせ系列の例を示す図である。

【図15B】図15Aの位置合わせ系列に対応する位置合わせ結果を比較対照例と比較して示す表の図である。

【図16】図8において、前記図12の縦横比の調整に係る部分を示すフローチャートである。

【図17】本発明の考え方を説明する図である。

【発明を実施するための形態】

【0012】

[第1の実施形態]

図1は、第1の実施形態により製造される、シリコン基板11上に形成されたトランジスタTrを含む半導体装置10を示す断面図である。図1の半導体装置10の例では、前記トランジスタTr上に層間絶縁膜15〜19が積層されている。

【0013】

図1を参照するに、前記シリコン基板11中には素子分離領域11Iにより素子領域11Aが画成されており、前記シリコン基板11上にはゲート絶縁膜12を介してゲート電極13が形成されている。

【0014】

前記素子領域11Aでは前記シリコン基板11中、前記ゲート電極13の第1の側および第2の側に、n型あるいはp型の拡散領域よりなるソースエクステンション領域11aとドレインエクステンション領域11bが形成され、さらにゲート電極13の前記第1の側では、ゲート電極13直下のチャネル領域11chから見て側壁絶縁膜13Aの外側にn+型あるいはp+型の拡散領域よりなるソース領域が、また前記ゲート電極13の前記第2の側では前記チャネル領域11chから見て側壁絶縁膜13Bの外側に、n+型あるいはp+型の拡散領域よりなるドレイン領域が形成されている。

【0015】

前記ゲート電極13は絶縁膜14により覆われ、前記絶縁膜14中には前記ソース領域11aにコンタクトして第1のビアプラグ14Aが、また前記ドレイン領域11bにコンタクトして第2のビアプラグ14Bが形成されている。

【0016】

さらに前記絶縁膜14上には、前記層間絶縁膜15〜19を積層した多層配線構造20が形成されている。

【0017】

図示の例では前記層間絶縁膜15は第1層の配線パタ―ン15L,15Mおよび第1層のビアプラグ15Cを含み、前記配線パタ―ン15Lはビアプラグ14Bに、配線パタ―ン15Mはビアプラグ14Aに電気的に接続されている。またビアプラグ15Cは配線パタ―ン15Lに整合し、かつ前記配線パタ―ン15Lに電気的に接続されている。

【0018】

さらに前記層間絶縁膜16は第2層の配線パタ―ン16Lおよび第2層のビアプラグ16Cを含み、前記配線パタ―ン16Lは前記ビアプラグ15Cに整合し、かつ前記ビアプラグ15Cに電気的に接続される一方、ビアプラグ16Cにも整合し、かつ前記ビアプラグ16Cに電気的に接続されている。

【0019】

さらに前記層間絶縁膜17は第3層の配線パタ―ン17Lおよび第3層のビアプラグ17Cを含み、前記配線パタ―ン17Lはその下のビアプラグ16Cに整合し、かつ前記ビアプラグ16Cに電気的に接続される一方、前記ビアプラグ17Cにも整合し、かつ前記ビアプラグ17Cに電気的に接続されている。

【0020】

さらに前記層間絶縁膜18は第4層の配線パタ―ン18Lおよび第4層のビアプラグ18Cを含み、前記配線パタ―ン18Lはその下のビアプラグ17Cに整合し、かつ電気的に接続される一方、前記ビアプラグ18Cにも整合し、かつ電気的に接続されている。

【0021】

さらに前記層間絶縁膜19は第5層の配線パタ―ン19Lおよび第5層のビアプラグ19Cを含み、前記配線パタ―ン19Lはその下のビアプラグ18Cに整合し、かつ電気的に接続される一方、前記ビアプラグ19Cにも整合し、かつ電気的に接続されている。

【0022】

ただし本発明は、図1に示したような、各層の配線パタ―ンおよびビアプラグが基板に垂直な方向に整列している場合に限定されるものではなく、前記多層配線構造20中に様々な回路パターンが形成されている場合をも含むものである。

【0023】

このような多層配線構造20をフォトリソグラフィにより形成する際には、第1層の配線パタ―ン15Lに第1層のビアプラグ15Cを位置合わせし、さらに第1層のビアプラグ15Cに第2層の配線パタ―ン16Lを位置合わせし、前記第2層の配線パタ―ン16Lに第2層のビアプラグ16Cを位置合わせし・・・という一連の位置合わせ工程が必要になる。

【0024】

図2Aは、このような層間絶縁膜15〜19中に形成され、フォトリソグラフィ工程の際に配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの位置合わせに使われるアラインメントマークALの例を、また図2Bは、前記層間絶縁膜15〜19中に形成され、同じくフォトリソグラフィ工程の際に配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの位置ずれの検出に使われる位置ずれ検出マークDvの例を示す断面図である。

【0025】

図2Aを参照するに、アラインメントマークALは前記層間絶縁膜15〜19中に、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cの各々に対応して、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cと同時に形成されており、前記アラインメントマークALは、フォトリソグラフィ工程の際にx軸方向への位置検出に使われるマークALxとy軸方向への位置検出に使われるマークALyより構成されている。マークALxとマークALyとは対をなしており、配線パタ―ン15L,ビアプラグ15C,配線パタ―ン16L,ビアプラグ16C・・・に対応して、位置をずらしながら形成されている。例えば前記マークALxのx軸方向への繰り返しを検出し、その中央の位置をもって、マークALxのx座標値を読み取ることが可能であり、また前記マークALyのy軸方向への繰り返しを検出し、その中央の位置をもって、マークALyのy座標値を読み取ることができる。

【0026】

これに対し図2Bを参照するに位置ずれ検出マークDvも前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cの各々に対応して、前記層間絶縁膜15〜19中に前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cと同時に形成されており、各々の位置ずれ検出マークDvは、合わせパタ―ンDvUと被合わせパタ―ンDvLとにより構成されている。

【0027】

例えば図示の例では、合わせパタ―ンDvUが、その下の破線で示した被合わせパタ―ンDvL'に、前記基板11に垂直方向から見た場合に含まれるように形成されており、その結果、フォトリソグラフィ工程による前記配線パタ―ン15L〜19L,ビアプラグパタ―ン15C〜19Cの形成の際、前記合わせパタ―ンDvUと被合わせパタ―ンDvL'との、前記基板11に垂直方向から見た位置関係をもとに、合わせパタ―ンDvUの被合わせパタ―ンDvL'に対する位置ずれ、従って例えばビアプラグ15Cの配線パタ―ン15Lに対する位置ずれなどが検出される。

【0028】

位置ずれ検出マークDvも、配線パタ―ン15L,ビアプラグ15C,配線パタ―ン16L,ビアプラグ16C・・・に対応して、位置をずらしながら、任意の配線パタ―ンあるいはビアプラグ、例えばビアプラグ15C、に対応する合わせマークDvUに対して一つ下のビアプラグあるいは配線パタ―ン、例えば15L、に対応する被合わせマークDvL'が重なるように、また前記合わせマークDvUと同じ層で隣接する被合わせマークDvLに対しては、一つ上の配線パタ―ンあるいはビアプラグ、例えば配線パタ―ン16L、の合わせマークDvUが重なるように形成されている。

【0029】

このようなアラインメントマークALおよび位置ずれ検出マークDvを使うことにより前記ビアプラグ15Cが前記配線パタ―ン15Lに位置合わせされ、前記配線パタ―ン16Lが前記ビアプラグ15Cに位置合わせされ、前記ビアプラグ16Cが前記配線パタ―ン16Lに位置合わせされ、前記配線パタ―ン17Lが前記ビアプラグ16Cに位置合わせされ、前記ビアプラグ17Cが前記配線パタ―ン17Lに位置合わせされ、前記配線パタ―ン18Lが前記ビアプラグ17Cに位置合わせされ、前記ビアプラグ18Cが前記配線パタ―ン18Lに位置合わせされ、前記配線パタ―ン19Lが前記ビアプラグ18Cに位置合わせされ、前記ビアプラグ19Cが前記配線パタ―ン19Lに位置合わせされる。

【0030】

これに伴い、図2Aおよび図2Bに示すように、前記層間絶縁膜15〜19中にはそれぞれの配線パタ―ンおよびビアプラグのためのアラインメントマークALおよび位置ずれ検出マークDvが、位置をずらしながら順次形成されることになる。

【0031】

図3は、このようにして形成された図1の半導体装置10における多層配線構造20を基板11に垂直な方向から見た平面図である。

【0032】

図3を参照するに、前記配線パタ―ン15L〜19Lおよびビアプラグ15C〜19Cが形成される「露光ショット」と表記した半導体パタ―ン形成領域を囲んで、図示の例では四隅A〜Dに、前記アラインメントマークALおよび位置ずれ検出マークDvがそれぞれ形成されている。前記図2A,2Bに示したように、前記アラインメントマークALおよび位置ずれ検出マークDvは、前記各々の隅A〜Dにおいて順次ずらして形成されているため、図3の平面図では一列に整列して見え、前記層間絶縁膜15〜19を透かしてそれぞれのアラインメントマークALおよび位置ずれ検出マークDvを読み取ることが可能である。

【0033】

図4は、このようなアラインメントマークALおよび位置ずれ検出マークDvにより検出された位置ずれに基づいて行われる、図1の半導体装置10をフォトリソグラフィにより製造する際の位置合わせ系列の例を示す工程図である。

【0034】

図4を参照するに、ステップ1において素子分離領域11I(ISO)が形成され、ステップ2において前記素子分離領域11Iに対してゲート電極13(Gate)が、位置合わせの後、露光により形成されたレジストパターンをマスクに、ドライエッチングにより形成される。さらにステップ3において前記ステップ2と平行して、イオン注入マスクが位置合わせされ、前記シリコン基板11の所定領域に第1回目のイオン注入(ii)が実行される。これにより、例えば前記シリコン基板11中にソースエクステンション領域11aおよびドレインエクステンション領域11bが形成される。

【0035】

前記ステップ2および3の後、ステップ4において、例えば図1の例ではビアプラグ14A,14Bを含む配線層C1を形成するためのマスク位置合わせが、前記ゲート電極13のパタ―ンに対して行われ、またこれに平行してステップ5において、前記ゲート電極13に対して次のイオン注入マスクが位置合わせされ、前記シリコン基板11の所定領域に第2回目のイオン注入(ii)が実行され、前記ソース領域およびドレイン領域11c,11dが形成される。

【0036】

さらにステップ6において、図1の半導体装置10の例では配線パタ―ン15L,15Mに対応する配線層L1のパターニングのためのマスク位置合わせがなされ、さらに対応して形成された金属膜をパターニングすることにより、配線パタ―ン15L,15Mを含む配線層L1が形成される。

【0037】

さらにステップ7において例えば前記ビアプラグ15Cを含む配線層C2のパターニングのためのマスク位置合わせがなされ、引き続き前記配線層C2のパターニングが行われる。

【0038】

さらにステップ8において、図1の半導体装置10の例では配線パタ―ン16Lを含む配線層L2のパターニングのためのマスク位置合わせがなされ、さらに対応する金属膜をパターニングすることにより、前記配線層L2のパターニングが行われる。

【0039】

さらにステップ9において例えば前記ビアプラグ16Cを含むビアプラグC3のパターニングのためのマスク位置合わせがなされ、引き続き、前記配線層C3のパターニングが行われる。

【0040】

さらにステップ10において図1の半導体装置10の例では配線パタ―ン17Lを含む配線層L3のパターニングのためのマスク位置合わせがなされ、さらに対応する金属膜をパターニングすることにより、配線層L3のパターニングが行われる。

【0041】

さらにこのような工程を繰り返すことにより、前記図1の半導体装置10が得られる。

【0042】

図5は、本実施形態で使われる縮小投影露光装置30の例を示す。

【0043】

図5を参照するに縮小投影露光装置30はいわゆるスキャナであり、光源31と、被処理基板Wを保持して移動させるウェハ走査ステージ32を含み、前記光源31とウェハ走査ステージ32の間には、第1の実施形態による露光マスク34を担持するレチクル走査ステージ33が設けられている。

【0044】

前記光源31は、例えばエキシマレーザなど、深紫外(DUV)波長の露光ビームを発生する光源であり、前記光源31から出射した露光ビームはミラー35で反射された後、コリメートレンズ系36により前記レチクル走査ステージ33上の露光マスク34に平行光ビームとして照射される。

【0045】

このようにして前記露光マスク34に照射された露光ビームは前記露光マスク34を通過する際に露光マスク14のレチクルが保持している所望の半導体装置の露光パタ―ンに従って整型され、前記レチクル走査ステージ33とウェハ走査ステージ32の間に設けられた投影レンズ系37により、前記被処理基板Wの表面に集束され、前記被処理基板W上のレジスト膜が所望の露光パタ―ンに従ってスリット状に露光される。

【0046】

前記縮小投影露光装置30はスキャナであるため、前記レチクル走査ステージ13が図5中の矢印Aの方向に移動され、また前記被処理基板Wが矢印Bの方向に移動され、前記レチクル上の露光パタ―ン全体の露光がなされる。このようなスキャナを使った場合、前記矢印Aおよび矢印Bの方向への走査速度により、前記被処理基板W上に露光されるパタ―ンにおいて縦横比を変化させることができる。具体的には、図5中の水平方向の投影倍率に関しては、X方向のレチクル上のパターンのウェハ上への投影倍率を、投影レンズ系内のレンズ倍率制御機構によって変化させることが可能であり、図5中の垂直方向の投影倍率は、レチクルの走査スピードとウェハの走査速度の差を利用して変化させることが可能であり、その結果X方向とY方向の相対的な倍率差を変化させることが可能となっている。

【0047】

図6Aは、前記スキャナ30を使って被処理基板W上に素子分離領域11Iを形成した後、さらにゲート電極13を重畳して露光した場合の位置ずれ、ないし歪みの例を、また図6Bは、ゲート電極13上にビアプラグ14A,14Bを重畳して露光した場合の位置ずれ、ないし歪みの例を示す。図6Aおよび図6B中、実線の四角形は被処理基板W上の正規の四角形(正方形)を、破線は露光の際に位置ずれが生じて歪んだ四角形を示している。また前記四角形の各稜点の矢印は、それぞれの稜点の変位を示しているが、前記縮小投影露光装置30がスキャナであるため、変位の方向および変位量は様々であるのがわかる。

【0048】

このような位置ずれ成分には、x軸方向の並進ズレ成分である「Shift_X」、y軸方向の並進ズレ成分である「Shift_Y」、ウェハ全体のx軸方向に関する倍率ズレ成分である「wafer_mag_X」、ウェハ全体のy軸方向に関する倍率ズレ成分である「wafer_mag_Y」、ウェハ全体のx軸方向への回転ズレ成分である「wafer_rot_X」、ウェハ全体のy軸方向への回転ズレ成分である「wafer_rot_Y」、さらにx軸方向へのショットの倍率ズレ成分である「shot_mag_X」、y軸方向へのショットの倍率ズレ成分である「shot_mag_Y」、x軸方向へのショットの回転ズレ成分である「shot_rot_X」、およびy軸方向へのショットの回転ズレ成分である「shot_rot_Y」が含まれる。

【0049】

数学的に示せば、x方向の位置ずれ量は、

(Xmi+Xci)×wafer_mag_X + (Ymi+Yci)×wafer_rot_Y + shot_mag_X×Xmi+ shot_rot_Y ×Ymi+ Shift_X)+εx

であり、

y方向の位置ずれ量は、

(Ymi+Yci)×wafer_mag_Y + (Xmi+Xci)×wafer_rot_X + shot_mag_Y×Ymi+ shot_rot_X ×Xmi+ Shift_Y+εy)

である。

【0050】

ここで、Xciは、ウェハ内のi番目の位置ずれ計測の属するショットのショット中心座標をウェハ中心を原点(0, 0)とした際のウェハ内座標位置であり、Xmiは、同様にウェハ内のi番目の位置ずれ計測位置を、その属するショットの中心座標であるXciを原点(0, 0)にした際のショット内座標位置である。また、εx, εyはそれぞれ、x方向、y方向の非線形位置ずれ成分である。

【0051】

図7は、上記位置ずれ成分「Shift_X」,「Shift_Y」,「wafer_mag_X」,「wafer_mag_Y」,「wafer_rot_X」,「wafer_rot_Y」,「shot_mag_X」,「shot_mag_Y」,「shot_rot_X」、および「shot_rot_Y」の例を示す平面図である。

【0052】

図7中、破線は正規のパタ―ンを、実線はそれぞれの位置ずれが生じた状態を示している。

【0053】

図7を参照するに位置ずれ成分「Shift_X」,「Shift_Y」は、それぞれx軸方向およびy軸方向への平行移動に対応しており、「wafer_mag_X」,「wafer_mag_Y」は、それぞれウェハ全体としてのx軸方向およびy軸方向への倍率のずれに対応しており、「wafer_rot_X」,「wafer_rot_Y」は、それぞれウェハ全体としてのx軸方向およびy軸方向への変形に対応しており、「wafer_rot_X」,「wafer_rot_Y」を組みあわせることで、ウェハ全体の回転を表すことができる。

【0054】

さらに図7において「shot_mag_X」,「shot_mag_Y」は、個々のショットにおけるx軸方向およびy軸方向への倍率のずれに対応し、「shot_rot_X」および「shot_rot_Y」は、個々のショットにおけるx軸方向およびy軸方向への変形に対応している。「shot_rot_X」,「shot_rot_Y」を組みあわせることで、当該ショットの回転を表すことができる。例えば、「shot_mag_X」,「shot_mag_Y」の符号を時計周りを+に取った場合、「(shot_mag_X+shot_mag_Y)/2」がショットの回転に該当する。

【0055】

このような露光装置における位置ずれについては、図6A,図6Bに矢印で示した各位置ずれ成分のロット単位の処理履歴:つまりロット単位で、その中の数枚のウェハに対して位置ずれ計測を行い、その計測データの解析結果を、ロットの位置ずれの出来栄えを表す尺度、としてデータベースに登録されており、例えば図4のようなフォトリソグラフィ工程を実行する際には、予想される位置ずれを前記データベースより読み出し、補正を行ってから露光を実行することがなされている。

【0056】

図8は、このような露光工程の例を示すフローチャートである。

【0057】

図8を参照するに、ステップ11においてあるロットの被処理基板Wが入来すると、ステップ12において、前記縮小投影露光装置30は前記データベースを参照して、そのロットについて最適な補正量を決定する。このような補正量には、図6A,6Bに示した各成分についての位置ずれ補正値の他に、最適な線幅を得るための最適な露光量の補正値が含まれる。このような最適補正量の決定は、それ以前のロットについての最適補正量の変化を、例えば移動平均を計算して外挿すること、などによりなされる。

【0058】

次にステップ13において前記最適補正量を使って補正した露光データにより被処理基板Wを露光し、レジストパターンを現像する。

【0059】

さらにステップ14において、現像により得られたレジストパターンを、顕微鏡を使って検査し、実際の位置ずれの値を求める。より具体的には、顕微鏡で観察される位置ずれ計測用の被合わせマークと合わせマークの重なり具合(位置ずれ量)を画像処理によって求める。

【0060】

さらにステップ15において、前記ステップ14で求められた実際の位置ずれの値が許容範囲内に収まっているか否かを判定し、収まっている場合(YES)ならばステップ16の線幅検査に進み、線幅を求める。

【0061】

さらにステップ17において、前記ステップ16で求められた線幅が許容範囲内である(YES)と判定されると、ステップ18で次の工程に進む。

【0062】

一方、前記ステップ15において位置ずれが許容範囲を超えている(NO)と判定された場合にはステップ19において、先にステップ13で形成されたレジストパターンが除去され、さらにステップ20において、前記ステップ14で求められた真の位置ずれの値を元に、前記ステップ12で求められた補正値が修正され、再びステップ13に戻り、前記修正された補正値を使って露光および現像が行われる。また同時にステップ12で使われたデータベースが、最新の位置ずれ補正値により更新される。

【0063】

同様にステップ17で露光線幅が許容範囲を超える(NO)と判定された場合にも、ステップ19において既存のレジストパターンは除去され、さらにステップ20において前記ステップ16で求められた真の露光線幅の値を元に、前記ステップ12で求められた露光量の最適補正値が修正され、再びステップ13に戻り、前記修正された補正値を使って、露光および現像が行われる。また同時にステップ12で使われたデータベースが、最新の露光量により更新される。

【0064】

図9は、前記図5のスキャナ30を使って、被処理基板W上に、層1〜層3まで、同一の矩形パタ―ンを重畳露光した際の位置ずれおよび位置合わせを説明する平面図である。

【0065】

図9を参照するに、最初に非露光基板W上に層1の露光および現像がなされ、前記露光および現像の結果得られたレジストパターンをマスクとしたエッチングにより、前記被処理基板W上には例えば点線で示した矩形パタ―ンR1が形成される。

【0066】

次に破線で示した層2の露光が、前記層1の露光で形成された矩形パタ―ンR1に重畳して実行される。

【0067】

図示の例では層2の露光で形成される矩形パタ―ンR2は、層1の露光で形成される矩形(正方形)パタ―ンR1と同一のパタ―ンであり、露光の際の位置ずれが生じていなければ、矩形パタ―ンR2は矩形パタ―ンR1と一致するはずのものであるが、図9では実際は、前記矩形パタ―ンR2は横長に変形されている。このような位置ずれないしパタ―ンの変形は、例えば図5のスキャナ30における光学系の誤差の他、レチクル走査ステージ13の走査速度やウェハ走査ステージ32のずれなどに起因して生じており、x軸方向およびy軸方向への倍率のずれの結果生じるものである。層3の矩形パタ―ンR3も同様である。なお図9において前記層1〜層3の矩形パタ―ンR1〜R3の中心は、位置合わせされているものとする。すなわち図9では、実際にはウェハ内のショット毎に、当該中心位置はずれているが、ショットの倍率による位置ずれの影響を分かりやすく示すために当該中心位置はずれていないものとして表現している。

【0068】

図9中、各矩形パタ―ンの右下稜点P1,P2,P3に付した円Ca1,Ca2,Ca3は位置合わせ許容誤差範囲を示しており、例えば層1の矩形パタ―ンR1の左下稜点P1の円Ca1内に層2の矩形パタ―ンR2の左下稜点P2が入っていれば、層1と層2の位置ずれは許容範囲にあると考えられる。層1と層2の中心が一致しており、左右上下対象であり、そのコーナー(最大位置ずれ量が発生する場所)が位置ずれ許容範囲であれば層1と層2のすべてのパターンについて許容範囲にあるということである。

【0069】

図9の例では、前記稜点P2は前記円Ca1内に入っており、矩形パタ―ンR1と矩形パタ―ンR2とは許容範囲内で位置合わせされているが、矩形パタ―ンR3では稜点P3が矩形パタ―ンR2の許容範囲Ca2を外れていることがわかる。

【0070】

そこでこのような場合、通常は前記矩形パタ―ンR3を露光する際のx軸方向およびy軸方向への倍率ShotMag_XおよびShotMag_Yを、図9中に矢印Δ1で示すように前記矩形パタ―ンR3の稜点P3が前記円Ca2内に入るように補正する。なお前記図9において、また以後の説明においても、前記Shift_X,Shift_Y,wafer_mag_X,wafer_mag_Y,wafer_rot_Xおよびwafer_rot_Yの各成分については、すでに補正がなされているものとする。

【0071】

図10は、このような補正を行って形成した矩形パタ―ンR1〜R3を示す平面図である。

【0072】

図10を参照するに、前記図9に示した矢印Δ1の補正の結果、前記稜点P3は前記稜点P2における許容範囲円Ca2内に収まっているのがわかる。

【0073】

このように、縮小投影露光装置としてスキャナを使っている限り、相前後して露光される二つの層の間で位置ずれを許容範囲内に維持することにより、所望の半導体装置を製造することが可能であるが、一方、多層配線構造の上層に形成される配線パタ―ンあるいはビアプラグパタ―ンについては、パタ―ン幅が下層の微細な配線パタ―ンに比較して広いので、より露光スループットの高いステッパを使って露光を行いたい要望がある。

【0074】

しかしステッパでは、露光装置の図示および構成についての説明は省略するが、倍率の縦横比が通常は1:1に固定されていて、x軸方向への倍率ShotMag_Xとy軸方向への倍率ShotMag_Yを別々に変化させることはできず、図9,図10に示した位置ずれ補正方法は使えない。

【0075】

図11は、層1〜層3においてスキャナ30を使い、前記図10に示す矩形パタ―ンR1〜R3を形成した後、ステッパを使って層4の矩形パタ―ンR4を形成した本実施例の比較例を示す平面図である。

【0076】

図11を参照するに、図示の例では図10に示す矩形パタ―ンR1〜R3に矩形パタ―ンR4が重畳して露光されているが、パタ―ンR4の右下稜点P4が、円Ca3で示す、その直下の矩形パタ―ンR3の位置ずれ許容範囲から大きく外れていることがわかる。

【0077】

矩形パタ―ンR4を露光する縮小投影露光装置はステッパであるため、縦横の倍率は別々に変化させることはできず、このため倍率を調整しても、前記稜点P4は図中に一点鎖線で示す線の上を移動することしかできない。

【0078】

このため、図11のような状態が生じると、矩形パタ―ンR4の矩形パタ―ンR3に対する位置合わせは失敗したことになる。

【0079】

これに対し本実施形態では前記層1を基準層とし、図12に示すように、層3における矩形パタ―ンR3の稜点P3を、Δ2で表したベクトルに従って、基準層1の稜点P1の近傍の×で示した位置P3'に移動させ、前記矩形パタ―ンR3の縦横比を、図13に示すように、基準層1における矩形パタ―ンR1の縦横比に近づけている。ここで図13は、前記図12の調整の結果得られた矩形パタ―ンR3を、前記矩形パタ―ンR1,R2,R4に重畳して示している図である。

【0080】

このように矩形パタ―ンR3を基準層1における矩形パタ―ンR1に対して補正しておくことにより、縦横比の調整後においても稜点P3は矩形パタ―ンR2の位置ずれ許容範囲円Ca2の内側になお含まれ、かつ矩形パタ―ンR4の稜点P4が矩形パタ―ンR3の位置ずれ許容範囲円Ca3の内側に含まれるようにすることができる。

【0081】

以下、本発明の考え方を、図17を参照しながらより具体的に説明する。

【0082】

図17における稜点P1,P2,P3は図12の矩形パタ―ンR1の稜点P1,矩形パタ―ンR2の稜点P2,矩形パタ―ンR3の稜点P3にそれぞれ対応するものであるが、本願発明では稜点P3の位置ずれパラメータの決定にあたって、まず、過去の稜点P3と稜点P2の位置ずれの最適解を基に、当該最適解の移動平均等を用いた手法を適用する。ここで、最適解とは、例えばShiftXを例に取れば、設定したShiftX(set)に対して実際に得られた位置ずれをShiftXをShiftX(result)として、ShiftXが0であるべき最適ShiftX(optimum)は、

ShiftX(optimum) = ShiftX(set)−ShiftX(result)

の関係を満たすものと定義される。ここでは、位置ずれがXnmである場合、−Xnmの設定することで位置ずれが0nmになるように最適解の符号を定義している。

【0083】

一般には、このような過去のロット単位あるいはウェハ単位の最適解に対して、移動平均あるいは加重移動平均をとることによって、次に露光すべきロットの最適解を予測する手法が用いられている。ただし、ここでいう従来使われている最適解とは、あくまでも被合わせ層と合わせ層に関する最適解であり、それ以外の層に対しては問題としていない。

【0084】

これに対し本願発明は、このように稜点P3−P2に関する最適解の予測値として過去のロットの最適解の移動平均あるいは加重移動平均を出発点として用いるが、当該最適解の予測値に対して、これから露光すべきロットの過去の履歴、すなわち当該ロットの稜点P2−P1間の位置ずれ(本件では倍率のみを取り扱う)をもさらに考慮するものである。

【0085】

図17では、稜点P3に対して、移動平均等で求めた最適予測値の結果倍率ShiftX(result),ShiftY(result) がずれているわけであるが、本願発明では、その最適予測値に対して、kΔ1の補正を行い、稜点P3を其の分だけ、基準層1の矩形パタ―ンR1の稜点P1に近づける。ここで図17におけるベクトルΔ1は、基準層1に対して層2を、過去のデータベースに基づいて最適化した場合の稜点P1に対する稜点P2のずれを示しており、理想的に最適化された場合にはゼロになるべきものであるが、最適化を過去のデータベースに基づいて行っているため、ゼロにはなっておらず、ベクトルΔ1だけのずれが発生している。

【0086】

このような状況で、さらに層3を層2に対して過去のデータベースに基づいて最適化した後、さらに層1に対して調整を行おうとすると、まず矩形パタ―ンR3を矩形パタ―ンR2に対して最適化した場合の稜点P3の位置の計算値、ないし予測値が得られるので、このようにして得られた稜点P3の位置を出発点として、これを基準層1の稜点P1の位置に近づける調整を行う。

【0087】

図示の例では、稜点P3は稜点P2に対して大きくベクトルΔ2だけずれているため、一見すると、このような調整では、稜点P1に対する稜点P2のずれに対応するベクトルΔ1を前記稜点P3に対しても適用し、稜点P3をベクトルΔ1だけ移動させるのが妥当に考えられるかも知れない。しかし例えば実際の稜点P3が最適化の結果、稜点P2に一致している場合も考えられ、そのような場合には稜点P3は上記Δ1の補正分だけ稜点P2から稜点P1の方向にずれることになるため(図17中のベクトルkΔ1')、稜点P2に対する稜点P3の位置合わせ、すなわち層2に対する層3の最適化に対しては、図17中にベクトルΔ2'で示すように稜点P2を行き過ぎてしまい、逆に不利な補正となってしまうことがある。図17の状態では、まだ層3の露光はなされていないので、稜点P3の実際の位置はわかっていない。

【0088】

このように本発明では、層2と層3のみについてみると不利になるような補正をしてまでも、以降の層におけるスキャナとステッパの倍率差の調整が可能となるように層3の倍率補正をしているわけである。このため本発明では、図17に示すように層2に対して最適化された層3の矩形パタ―ンR3の稜点P3を基準層1の稜点P1に近づける調整を行う際に、ベクトルΔ1に例えば値が1/2の係数kを乗じて、倍率の予測値ShotMagX(予測値) ,ShotMagY(予測値)を、以下の式より求める。

ShotMagX(予測値) = ShotMagX(最適解予測値)+ k(ShotMagX(P2)−ShotMagX(P1)) (式1)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k(ShotMagY(P2)−ShotMagY(P1)) (式2)

なお図17においても各層1,2,3において矩形パタ―ンR1,R2,R3の中心は一致させられており、従って図17における各点の移動は倍率ShotMagX,ShotMagYの変化に対応していることに注意すべきである。

【0089】

層1は基準層であるので、ShotMagX(P1)、ShotMagY(P1)は0となり、層3の調整後の稜点P3の予測値ShotMagX(P3)(予測値),ShotMagY(P3)(予測値)は、次式

ShotMagX(P3)(予測値) = ShotMagX(P3)(最適解予測値)+ k(ShotMagX(P2)) (式3)

ShotMagY(P3)(予測値) = ShotMagY(P3)(最適解予測値)+ k(ShotMagY(P2)) (式4)

より求められる。なお上記ShotMagX(P2)、ShotMagY(P2) は、層1に対する層2の倍率ずれを意味している。

【0090】

ここで、倍率差が基準層から乖離するのを積極的に抑えることを目的として上式を、

ShotMagX(予測値) = ShotMagX(最適解予測値)− k(ShotMagX(P2)−ShotMagY(P2)) (式5)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k(ShotMagX(P2)−ShotMagY(P2)) (式6)

としてもよい。

また 汎用的な補正式としては、X方向倍率とY方向倍率の違いに対応して、

ShotMagX(予測値) = ShotMagX(最適解予測値)− k1×ShotMagX(P2) +k2×ShotMagY(P2) (式7)

ShotMagY(予測値) = ShotMagY(最適解予測値)+ k1×ShotMagX(P2)−K2×ShotMagY(P2) (式8)

とすると良い。

【0091】

ここで前記係数k、あるいはk1,k2は、上記の式による補正の結果、補正後の位置ずれの頻度分布が、図14の曲線Aで示すように平均して位置ずれゼロになるように、あるいは曲線Bで示すように位置ずれがゼロでなくても、所定の許容範囲に入るように選定される。なおここで「所定許容範囲」とは、前記縦横比補正後においても全ての層1〜4においてパタ―ンR1〜R4が位置合わせ許容誤差範囲であることを意味している。例えば図13の例では、前記縦横比の調整を行った後において、前記稜点P3'は、前記矩形パタ―ンR2の位置合わせ許容範囲円Ca2の内側に位置していなければならない。これに対し、前記係数k、あるいはk1,k2が大きすぎるなど不適切な場合には、曲線Cで示すように補正後に所定の許容範囲を超える位置ずれが生じることがある。

【0092】

前記係数k、あるいは係数k1,k2がゼロであると上記縦横比の補正はなされないことになるが、このような縦横比の補正が必要である限り、前記係数kあるいは係数k1,k2は0より大きな値をとる。先の図17の例ではk=1/2となっている。上記の説明から前記係数k,k1,k2は1.0以下となることが多いと考えられるが、1.0以下に限定されるものではなく、1.0を超える値をとることもありうる。

【0093】

以上の説明では、層1および層2を、スキャナを使った位置合わせ、および露光により形成し、さらにその後、層3を層2に対してスキャナを使って位置合わせする際、ステッパによる層4の形成に鑑み、前記層1を基準層として、これに縦横比を合わせた後、露光をしている。

【0094】

図15Aは、このような露光の繰り返しによる、先の図1と同様な多層配線構造形成の例を示す工程図である。

【0095】

図15Aを参照するに、まず基準層となる配線層L1が第1層として露光・現像、およびパターニングにより形成され、この配線層L1に対してビアプラグを含む配線層C2が第2層としてスキャナを使って位置合わせされ、引き続き露光・現像およびパターニングされる。この工程では位置合わせされる配線層L1が基準層であるため、それ以上の調整は必要ない。

【0096】

次に前記配線層C2のビアプラグパタ―ンに対して配線層L2層が第3層として、再びスキャナを使って位置合わせされる。その際、本実施形態では、前記配線層L2が、前記配線層C2のみならず、記基準層L1に対しても、スキャナを使って位置合わせをされ、これにより縦横比が、先に図11,12で説明したように調整される。

【0097】

さらに前記配線層L2が形成された後、これに対し配線層C3が第4層として、再びスキャナを使って位置合わせされる。その際、本実施形態では、前記配線層C3のビアプラグパタ―ンが、前記配線層L2のみならず、記基準層L1に対しても位置合わせされ、縦横比が先に図12,13で説明したように調整される。

【0098】

図15Aの工程では、このような一連の位置合わせ工程が、スキャナを使って繰り返し実行され、配線層L5がその下の配線層C5に第9層として位置合わせして形成される。さらに前記配線層L5が形成されると、今度はステッパを使って、前記配線層L5上に配線層C6が第10層として形成される。

【0099】

このような一連の位置合わせ工程を行った場合、最終的な配線層C6の前記基準層L1に対する相対位置ずれRP(L1−C6)は、上下層間で行われる各々の位置合わせ工程での相対位置ずれRP(C2−L1),RP(L2−C2),RP(C3−L2),RP(L3−C3)・・・の総和として、以下のように表される。

【0100】

RP(L1−C6)=RP(C2−L1)+RP(L2−C2)+RP(C3−L2)+RP(L3−C3)+RP(C4−L3)+RP(L4−C4)+RP(C5−L4)+RP(L5−C5)+RP(C6−L5) (式9)

ただしRP(C2−L1)は配線層C2と配線層L1との間の相対位置ずれ量、RP(L2−C2)は配線層L2と配線層C2の間の相対位置ずれ量、RP(C3−L2)は配線層C3と配線層L2の間の相対位置ずれ量・・・である。

【0101】

本実施形態では、このような相対位置ずれ量RP(C2−L1),RP(L2−C2),RP(C3−L2),RP(L3−C3)・・・を、品種毎、工程毎、ロット毎に計算し、データベース化しておく。

【0102】

図15Bは、かかる予測補正を行った場合において生じる位置ずれの具体例を、比較対照例と比較して示す表の図である。ただし図中の数値の単位はppmである。

【0103】

まず比較対照例で見ると、「L1基準位置ずれ」の欄における「ShotMagX」,「ShotMagY」の値は、それぞれ「位置ずれ結果」の欄の位置合わせ「L1−C2」,「C2−L2」,「L2−C3」・・・における「ShotMagX」あるいは「ShotMagY」の値を順次総和したものになっており、上式(9)に対応している。ここで「位置ずれ結果」の欄における倍率差、すなわち合わせ層と被合わせ層との間での位置合わせに伴う倍率差に注目すると、「位置ずれ結果」における値は絶対値で1.70を超えていないが、「L1基準位置ずれ」における値は、ステッパによるC6層の露光直前において3.15に達しているのがわかる。これは前記図10で説明した、位置合わせが失敗した例に対応している。

【0104】

これに対し前記図15Bの表における「本発明の効果」を注目すると、位置合わせ「L1−C2」,「C2−L2」,「L2−C3」・・・の各々において、合わせ層と被合わせ層との位置合わせの他に、基準層L1に対する位置合わせをも行っている結果、「位置ずれ予測」の欄における倍率差は、比較対照例の場合と比べてやや増大しているが、基準層L1に対する「L1基準位置ずれ予測」の欄における倍率差の値は、ステッパによる層C6の露光直前においても−0.64に過ぎず、ステッパによる位置合わせが可能な範囲に維持されていることがわかる。

【0105】

このような露光を行うため、本実施形態では前記図8のフローチャートにおいて、ステップ12の「当該ロットの補正値の決定」を、図16に示すフローチャートに従って実行する。

【0106】

図16を参照するに、前記ステップ12は、被合わせ層に対する合わせ層の中心を合わせる中心合わせステップ12Aと、前記ステップ12Aの後、当該ロット、例えばロットi、の当該ウェハにおける当該被合わせ層に対する当該合わせ層の位置ずれを、過去の位置ずれデータから例えば移動平均などにより予測し、位置合わせ補正値の予測値 ShotMagX(最適解予測値),ShotMagY(最適解予測値)を取得するステップ12Bと、当該ロットiの当該被合わせ層に対する当該合わせ層の位置合わせの際の相対位置ずれ量Δ1、ないしShotMagX(P2)−ShotMagX(P1),ShotMagY(P2)−ShotMagY(P1)をデータベースより取得し、前記ステップ12Bで取得された予測値ShotMagX(最適解予測値),ShotMagY(最適解予測値)を、前記相対位置ずれ量Δ1を使って、例えば式(1),(2)、あるいは式(3),(4)、あるいは式(5),(6)、あるいは式(7),(8)により補正し、基準層に対する位置合わせ補正値の縦横比を調整するステップ12Cと、を含んでいる。

【0107】

なお本実施形態による位置合わせは、図15Aに示したような直列的な層L1〜C6までの位置合わせに限定されるものではなく、先に図4で説明したようなステップS1〜ステップS10の位置合わせなど、他の位置合わせ系列に対しても適用可能である。

【0108】

さらに以上の説明においては、縦横比のずれが最も少なくなる最初の層L1を基準層として使ったが、基準層は最初の層L1に限定されるものではなく、例えば最初の層L1を露光した後、次の層C1を露光する前に、前記層L1のパタ―ンの座標絶対値を露光装置により読み取り、読み取った座標絶対値をもとに、仮想的な基準層を設定することも可能である。このように前記基準層L1は、最初に被処理基板上に露光されるパタ―ンに限定されるものではない。このような仮想的な基準層では、縦横比を、スキャナで露光されるパタ―ンの縦横比(1:1)に合わせて設定することができる。

【0109】

被処理基板上に最初に露光される層L1が基準層である場合には、前記層L1においては図16のステップ12Cは不必要でありスキップすることができるが、基準層が上に述べた例のように仮想的な基準層として露光装置に保持されている場合には、最初の層L1を露光する段階から、かかる仮想的な基準層を使ってパタ―ンの縦横比を調整することができる。

【0110】

また経験上、各層における縦横比の基準層からのずれが小さいことが知られている場合には、前記図15のステップS12Cの工程は、ステッパにおいて露光される層の直前の層に対してのみ実行することで、全体の露光処理スループットを向上させることができる。

【0111】

さらにステッパによる露光の後で、必要に応じてスキャナを使った露光を行っても構わない。すなわち本実施形態において、ステッパにより露光される層が半導体装置の最上層であるとは限らないことに注意すべきである。

【0112】

本実施形態による半導体装置の製造方法は、縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、を含み、前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含む。その際前記第2の縦横比は、前記第1の縦横比よりも前記第2の露光装置の縦横比に近いことに注意すべきである。

【0113】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0114】

10 半導体装置

11 シリコン基板

11A 素子領域

11a ソースエクステンション領域

11b ドレインエクステンション領域

11c ソース領域

11d ドレイン領域

11I 素子分離領域

12 ゲート絶縁膜

13 ゲート電極

13A,13B 側壁絶縁膜

14,15,16,17,18,19 層間絶縁膜

14A,14B,15C,16C,17C,18C,19C ビアプラグ

15L,15M,16L,17L,18L,19L 配線パタ―ン

20 多層配線構造

30 縮小投影露光装置(スキャナ)

31 光源

32 ウェハ走査ステージ

33 レチクル走査ステージ

34 レチクル

35 ミラー

36 コリメートレンズ系

37 投影レンズ系

AL アラインメントマーク

Dv 位置ずれ検出マーク

L1,C2,L2,C3,L3,C4,L4,C5,L5,C6 配線層

W 被処理基板

【特許請求の範囲】

【請求項1】

露光領域の縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、

露光領域の縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、

を含み、

前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第2の縦横比は、前記第1の縦横比よりも前記第2の露光装置の縦横比に近いことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記基準層は、前記被処理基板上に最初に形成されるパタ―ンを含む層であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記基準層は、前記被処理基板上に最初に形成されるパタ―ンをもとに設定されることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記第1の工程に先立って、前記被処理基板上に前記第1の露光装置により複数の層を、それぞれ下側の層に対して上側の層を順次合わせ層と被合わせ層として位置合わせすることにより形成する工程を繰り返し含み、

前記繰り返される工程の各々において、前記合わせ層を被合わせ層に位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、縦横比を調整する工程を含むことを特徴とする請求項1〜4のうち、いずれか一項記載の半導体装置の製造方法。

【請求項1】

露光領域の縦横比が可変な第1の露光装置により、被処理基板上において合わせ層を被合わせ層に対して位置合わせして露光する第1の工程と、

露光領域の縦横比が固定された第2の露光装置により、前記合わせ層に次の合わせ層を位置合わせして露光する第2の工程と、

を含み、

前記第1の工程では、前記合わせ層を被合わせ層に、第1の縦横比で位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、前記第1の縦横比を第2の縦横比に調整する工程を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第2の縦横比は、前記第1の縦横比よりも前記第2の露光装置の縦横比に近いことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記基準層は、前記被処理基板上に最初に形成されるパタ―ンを含む層であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記基準層は、前記被処理基板上に最初に形成されるパタ―ンをもとに設定されることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記第1の工程に先立って、前記被処理基板上に前記第1の露光装置により複数の層を、それぞれ下側の層に対して上側の層を順次合わせ層と被合わせ層として位置合わせすることにより形成する工程を繰り返し含み、

前記繰り返される工程の各々において、前記合わせ層を被合わせ層に位置合わせした後、前記合わせ層を基準層に対して位置合わせすることにより、縦横比を調整する工程を含むことを特徴とする請求項1〜4のうち、いずれか一項記載の半導体装置の製造方法。

【図1】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15A】

【図15B】

【図16】

【図17】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15A】

【図15B】

【図16】

【図17】

【公開番号】特開2013−77653(P2013−77653A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−215680(P2011−215680)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]