半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関するもので、特にMIS型FETの製造方法に関する。

【背景技術】

【0002】

従来、MIS(Metal-Insulator-Semiconductor)型FET(Field-Effect Transistor)のゲート絶縁膜として、シリコン酸化膜が用いられている。シリコン基板を熱酸化して形成されたシリコン酸化膜は、シリコン基板との界面における欠陥が少なく、偶発的な絶縁破壊が起きる確率も低いため、非常に品質が高い絶縁膜となる。

【0003】

近年、より一層の半導体装置の高集積化の要求に伴い、LSIに用いるMIS型FETは、その寸法を比例関係を保ったまま縮小することでその性能を継続的に向上させてきた。現在、最新のLogic LSI等では、ゲート長40nm以下、ゲート絶縁膜として用いられるシリコン酸化膜の膜厚2nm未満のものが用いられている。本来の比例縮小の原則に従うならば、ゲート絶縁膜は膜厚1nm程度のシリコン酸化膜を用いることが好ましいが、物理膜厚が1nm程度のシリコン酸化膜は、直接トンネリングによるリーク電流が非常に大きく、LSIの消費電力の増大をもたらすこととなる。これを解決するために、high-k膜と呼ばれるシリコン酸化物よりも誘電率の大きい金属酸化物、たとえばHfO2、ZrO2、Al2O3、TiO2などを主成分とした膜がゲート絶縁膜として用いられている。high-k膜を用いることにより、物理膜厚の厚い膜であっても、シリコン酸化物の場合と同等のゲート容量を得ることができるため、トンネル電流の増大を抑制し、消費電力の小さいLSIを製造することができる。

【0004】

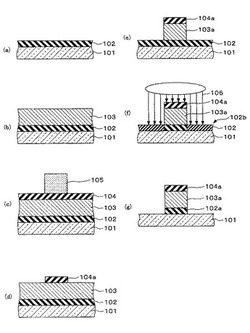

以下、図1に基づき第1の従来技術による半導体装置の製造方法を説明する。

【0005】

最初に、図1(a)に示すようにSi基板等の半導体基板11上にhigh-k膜12をCVD(Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いて形成する。ここで形成されるhigh-k膜12は、としてはHfO2(酸化ハフニウム)などを主体とする膜が代表的である。

【0006】

次に、図1(b)に示すように、high-k膜12上に電極膜13を形成する。電極膜13は単層の多結晶シリコンからなる場合もあるし、下層にTiN等の金属層、上層に多結晶シリコンを積層した構造からなる場合もある。

【0007】

次に、図1(c)に示すように、ハードマスク層14を成膜し、その上にフォトリソグラフィ法等によりレジストパターン15を形成する。その後、レジストパターン15をマスクとしてハードマスク層14の露出している領域をRIE(reactive ion etching)等の異方性エッチングにより除去し、更に、レジストパターン15をアッシング等で除去することにより、図1(d)に示すようにハードマスク14aを形成する。

【0008】

次に、図1(e)に示すように、ハードマスク14aをマスクとして電極膜13の露出している領域をhigh-k膜12に対して選択的にエッチングすることにより、ゲート電極13aを形成する。

【0009】

次に、図1(f)に示すように、ハードマスク14a及びゲート電極13aをマスクとしてRIE等の異方性エッチングを行うことにより、露出しているhigh-k膜12を半導体基板11に対して選択的にエッチングし、半導体基板11を露出させる。これにより、ゲート領域のhigh-k膜12aを形成する。

【0010】

この後、低加速イオン注入と高温短時間アニール等を組み合わせた工程で、浅い不純物拡散層を含むソース・ドレインを形成し、さらに配線を形成してhigh-kゲート絶縁膜を有するMIS型FETを形成することができる。

【0011】

また、異方性エッチングの代わりに、ウェットエッチング等の等方性エッチングを用いて、ゲート電極13aの形成されていない領域のhigh-k膜12を除去しても同等の効果を得ることができる。このような方法により形成されたものの典型的な断面図を図1(g)に示す。

【0012】

一方で、実際のLSIを製造する場合、回路的な要請に応じて同一チップ内で複数の異なる仕様のFETを組み合わせて使用することが通常行われている。この場合、FETのゲート絶縁膜も絶縁膜耐圧やリーク電流などの仕様に合わせて複数の異なる膜厚のものを用いる場合がある。以下図2に基づき第2の従来技術による半導体装置の製造方法を説明する。この方法はhigh-kを用いて多種膜厚のゲート絶縁膜を形成する方法である。

【0013】

最初に、図2(a)に示すように、Si基板等の半導体基板21に素子分離領域22、ウェル23を形成し、さらに半導体基板21の表面を熱酸化することによりSiO2膜24を形成する。

【0014】

次に、図2(b)に示すように、フォトリソグラフィ法等を用いてレジストパターン25を形成する。

【0015】

次に、図2(c)に示すように、レジストパターン25の形成されていない領域のSiO2膜24を希弗酸等を用いて除去する。

【0016】

次に、図2(d)に示すように、レジストパターン25をアッシングやH2SO4とH2O2との混合液等を用いて除去する。このようにして、SiO2膜24が形成されている領域a1とSiO2膜24が形成されていない領域a2とを形成する。

【0017】

次に、図2(e)に示すように、半導体基板21の表面に熱酸化によりSiO2膜を形成する。これにより、SiO2膜24が形成されている領域a1においては、SiO2膜24を含む膜厚の厚いSiO2膜26aが形成され、SiO2膜24が形成されていない領域a2においては、熱酸化により形成された膜厚の薄いSiO2膜26bが形成される。

【0018】

次に、図2(f)に示すように、high-k膜27を形成する。これにより、領域a1においては、厚いSiO2膜26aとhigh-k膜27とが積層された絶縁膜が形成され、領域a2においては、薄いSiO2膜26bとhigh-k膜27とが積層された絶縁膜とが形成される。

【0019】

この後、第1の従来例と同様の方法で、ゲート電極、ソース・ドレイン等を形成することによりMIS型FETが作製される。

【0020】

上記においては、2種類の異なる絶縁膜厚を有するMIS型FETの製造方法について説明したが、同様に追加のフォトリソグラフィとウェットエッチング、酸化を所望の回数行うことで、2種類より多い異なる絶縁膜厚を有するMIS型FETを製造することも可能である。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2004−71973号公報

【特許文献2】特開2002−33477号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

ところで、第1の従来技術による半導体装置の製造方法によれば、図1(f)に示すRIE等のエッチング工程においては、半導体基板との選択性に注意した場合であってもほとんどの場合その選択比は不十分であり、Si基板等の半導体基板11においてオーバーエッチング16aが発生する。また、半導体基板11の基板面に対して垂直な方向への運動エネルギーをもったイオンによりエッチングが行なわれるため、半導体基板11がエッチングされた部分では、ダメージ16bが発生しやすい。これらはいずれも、形成される半導体装置の性能を損なうものである。

【0023】

また、第2の従来技術による半導体装置の製造方法によれば、図2(c)に示すようにSiO2膜24の表面にレジストパターン25を形成しRIE等によりレジストパターン25の形成されていない領域のSiO2膜24を除去するものであるため、レジストパターンやエッチングガスに含まれるC(炭素)等が、半導体基板21またはSiO2膜24の表面に付着し拡散し、半導体基板21とゲート絶縁膜との界面に界面準位が形成される要因や、ゲート絶縁膜の絶縁破壊耐圧の低下の要因となっていた。

【0024】

従って、基板にダメージを与えることなく誘電体膜を完全に除去することによりゲート絶縁膜を形成することができる半導体装置の製造方法、また、シリコン基板等の半導体基板の表面を清浄に保ちつつ基板上に異なる膜厚の誘電体膜を形成することのできる半導体装置の製造方法が望まれている。

【課題を解決するための手段】

【0025】

本発明は、半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする。

【0026】

また、本発明は、前記誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする。

【0027】

また、本発明は、前記電極形成工程は、前記誘電体膜上に電極膜を形成し、前記電極膜上に酸化膜又は窒化膜からなる化合物膜を形成し、前記化合物膜上にレジストパターンを形成し、前記レジストパターンをマスクとして前記レジストパターンの形成されていない領域の化合物膜を除去することにより化合物マスクを形成し、前記化合物マスクの形成されていない領域における前記電極膜を除去するものであることを特徴とする。

【0028】

また、本発明は、前記誘電体膜の膜厚は、2nm以下であることを特徴とする。

【0029】

また、本発明は、半導体基板上に誘電体膜を形成する誘電体膜形成工程と、前記誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、前記レジストパターンの形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、を含むものであって、前記誘電体膜はゲート絶縁膜となるものであり、前記誘電体膜の膜厚が異なる2つの領域を形成することを特徴とする。

【0030】

また、本発明は、半導体基板上に第1の誘電体膜を形成する第1誘電体膜形成工程と、前記第1誘電体膜上に前記第1の誘電体膜を構成する材料の比誘電率よりも高い比誘電率を有する材料により構成される第2の誘電体膜を形成する第2誘電体膜形成工程と、前記第2の誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、前記レジストパターンの形成されていない前記第2の誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記第2の誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、を含むものであって、ゲート絶縁膜は前記第1の誘電体膜と前記第2の誘電体膜とにより形成されるものであり、前記ゲート絶縁膜は、前記イオン化したガスクラスターが照射された領域とされていない領域とにおいて膜厚が異なるものであることを特徴とする。

【0031】

また、本発明は、前記誘電体膜または前記第2の誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする。

【0032】

また、本発明は、前記ウェットエッチングは希フッ酸によるエッチングであることを特徴とする。

【0033】

また、本発明は、前記ガスクラスターを構成する原子の数の平均は、1000以上であることを特徴とする。

【発明の効果】

【0034】

本発明によれば、ゲート絶縁膜等としてHigh-k膜を用いた場合において、基板にダメージを与えることなく完全に除去することのできる半導体装置の製造方法、及び、基板上に異なる膜厚のHigh-k膜を形成する場合に、できるだけコンタミの混入を低減させた半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0035】

【図1】(a)〜(f) 第1の従来技術による半導体装置の製造方法の工程断面図、(g) 第1の従来技術による半導体装置の他の製造方法の説明図

【図2】(a)〜(f) 第2の従来技術による半導体装置の製造方法の工程断面図

【図3】(a)〜(g) 第1の実施の形態における半導体装置の製造方法の工程断面図

【図4】ガスクラスター照射有無によるhigh-k膜の特性図

【図5】ガスクラスター照射装置の構成図

【図6】(a)〜(e) 第2の実施の形態における半導体装置の製造方法の工程断面図

【発明を実施するための形態】

【0036】

本発明を実施するための形態について、以下に説明する。

【0037】

〔第1の実施の形態〕

第1の実施の形態を図3に基づき説明する。本実施の形態はゲート絶縁膜としてhigh-k膜を形成する半導体装置の製造方法である。

【0038】

最初に、図3(a)に示すように、Si基板等の半導体基板101上にhigh-k膜102を成膜する。ここで形成されるhigh-k膜102を構成する材料としてHfO2(酸化ハフニウム)、ZrO2(酸化ジルコニウム)、Al2O3(酸化アルミニウム)、Ta2O5(五酸化タンタル)、TiO2(酸化チタン)、希土類酸化物等及びこれらの混合、及びこれらにSiを添加したもの、さらにそれらを窒化処理したもの等があげられる。high-k膜の形成方法としては、CVDまたはALDが好適であるが、添加する物質の種類によっては、PVDを併用することもできるし、プラズマ窒化等を併用することもできる。high-k膜102の膜厚は、現在最先端のLogic LSIに用いられているもので、典型的には2nmを下回る程度である。high-k膜102を形成した後、望ましくは500℃乃至800℃で数分から数十分、あるいは、900℃乃至1100℃で数秒以内の熱処理を行う。熱処理を行う雰囲気は、Ar、N2などの不活性ガスあるいは、これらに数%以下の微量の酸素を添加した雰囲気が好適である。この熱処理は、high-k膜を緻密化し、誘電率を高くする効果と、後で説明するように、希弗酸によるエッチングレートを遅くする効果がある。

【0039】

次に、図3(b)に示すように、high-k膜102上に電極膜103を形成する。電極膜103としては、多結晶シリコンなどが代表的である。多結晶シリコンには抵抗を低下させ、電極として適切な仕事関数を与えるために、As(ヒ素)、P(リン)等のn型を示す導電性不純物か、あるいはB(ホウ素)等のp型を示す導電性不純物を添加した後に、熱処理を行い電気的に活性化させる。この不純物添加と活性化の処理は、ゲート電極のパターニング前に行ってもよいし、ゲートパターニング後にマスクを除去してから行ってもよい。また、ゲート電極としては、下層に所望の仕事関数を持つ金属を堆積し、その上に適宜多結晶シリコンに導電性不純物を添加した膜やWを含む膜等の電極のシート抵抗を低下させるための膜を積層したものでもよい。ただし、これらの膜は、後にhigh-k膜102の一部を希弗酸で除去する工程の際に、希弗酸におけるエッチングレートが十分に遅いことが必要である。

【0040】

次に、図3(c)に示すように、電極膜103上にハードマスク層104としてSiO2膜を形成し、更に、ハードマスク層104上にレジストパターン105を形成する。ハードマスク層は、SiO2を主成分とするもの等が代表的であるが、電極膜103の材質によってはSiNを主成分とするもの等を適宜選択することができる。また、レジストパターン105は、ハードマスク層104上にフォトレジストを塗布し、プリベーク、露光装置による露光、現像を行うことにより、ハードマスク層104上において、後述するハードマスク104aが形成される領域にレジストパターン105を形成する。

【0041】

次に、図3(d)に示すように、レジストパターン105をマスクとしてハードマスク層104を異方性エッチングし、この後、アッシング等によりレジストパターン105を除去する。これによりハードマスク104aを形成する。

【0042】

次に、図3(e)に示すように、ハードマスク104aをマスクとして、露出している電極膜103を異方性エッチングにより除去することにより、ゲート電極103aを形成する。このとき、電極膜103を形成する材料である多結晶シリコン、金属などはHBr、Cl2、SF6、NF3等を含むガスを用いてRIE等により異方性エッチングすることで、良好にエッチングされることが知られているが、一般にこれらのガス系による基板加熱を併用しないエッチングでは、high-k膜102に対するエッチングレートが非常に遅いことが知られている。そのため、high-k膜102は図に示すように残存する。

【0043】

次に、図3(f)に示すように、イオン化したガスクラスター106を照射することにより、ゲート電極103aの形成されていない領域のhigh-k膜102が変質し、変質膜102bが形成される。この変質膜102bは、後述するように弗酸を含む液に対して高いエッチングレートを持つ。尚、イオン化したガスクラスターの照射装置については後述する。イオン化したガスクラスターに用いられる元素としては、アルゴン、酸素、窒素等が挙げられる。

【0044】

次に、図3(g)に示すように、弗酸を含む液を用いて、変質膜102bを除去する。これにより、ゲート電極103aの形成されている領域にのみゲート領域のhigh-k膜102aを形成することができる。

【0045】

この後、ハードマスク104a及びゲート電極103aをマスクとして半導体基板101にイオン注入を行うことにより、ゲート電極103aに対して自己整合的にソース/ドレイン電極を形成し、周知の方法で層間絶縁膜及び配線を形成する。これにより、high-k膜を有するMOS型FETを形成することができる(図示せず)。

【0046】

本実施の形態における半導体装置の製造方法によれば、半導体基板101にダメージを与えることなく、表面の露出した領域のhigh-k膜102を変質膜102bとし、ウェットエッチングにより完全に除去することができる。これにより、後に形成するソース/ドレインの接合リーク電流の少ない、高品質のMOS型FETを製造することができる。

(high-k膜の特性)

次に、本実施の形態において形成したhigh-k膜のエッチング特性について説明する。ここで用いたhigh-k膜の材料は酸化アルミニウムであり、CVD法を用いて成膜を行った。尚、サンプルAはhigh-k膜を20nm成膜した後に850℃で300秒の熱処理を行った状態のものであり、サンプルBはサンプルAと同様の熱処理を行った後に、さらにクラスターイオンを照射したものである。

【0047】

図4に純水:弗酸=1:100の溶液中でウェットエッチングを行った場合のhigh-k膜厚の時間依存性を示す。サンプルAは、high-k膜が熱処理により結晶化しているため、希弗酸によりほとんどエッチングされない。一方、サンプルBは希弗酸によりhigh-k膜の表面の1〜2nm程度がエッチングされるが、その後はほとんどエッチングされない。

【0048】

このように、イオン化したガスクラスターの照射により、照射された膜の表面の状態は変質するため、本実施の形態を説明する図3(f)に示すように、イオン化したガスクラスターの照射された領域におけるhigh-k膜は、その表面の1〜2nmが変質し、希弗酸によるエッチングがされやすくなったものと推察される。

【0049】

尚、本実施の形態における変質される深さに関しては、イオン化したガスクラスターの条件を調節することにより調整可能である。

【0050】

また、上述したhigh-k膜の特性については、Al2O3について示したが、HfO2、ZrO2、Ta2O5、TiO2についても同様の傾向にある。

【0051】

また、本実施の形態では、イオン化したガスクラスターとして、酸素のイオン化したガスクラスターを用いたが、窒素およびアルゴン等のイオン化したガスクラスターを用いた場合にも同様の効果が得られる。

【0052】

尚、膜中に元素を導入する類似の方法としては、イオン注入法が代表的である。しかし、原子または分子がイオン化されたイオンを膜に注入する方法では、薄いhigh-k膜のみを改質することが非常に困難であり、high-k膜を通り抜け基板にも影響を与えてしまう。

【0053】

また、膜を改質するには、1×1021〜1×1022cm−3程度の密度に原子を注入することが必要であるが、一方で、膜と接するSi基板に注入される原子は1×1018cm−3台を超えるとSi基板自体を酸化するなどの弊害が出てくる。イオン注入では、膜を改質し、Si基板を酸化しないという両方の条件を満たすようなプロファイルを得ることが非常に困難である。また、本発明のように、結晶化した膜を注入の対象にする場合には、結晶の特定の方位に対して、一定数のイオンが散乱を受けずに透過してしまうチャネリングと呼ばれる現象が起こるため、膜の深い位置までイオンが到達する確率が高くなる。

【0054】

一方で、ガスクラスター注入ではイオン注入と不純物導入の原理が異なるためこのような条件を満たすプロファイルを得ることが可能である。数1000個程度の原子数を持つガスクラスターが注入の対象物に衝突すると、瞬間的に衝突が起きた近傍で高温高圧領域が形成される。これで、対象物が瞬間的に溶融し、溶融した部分に注入したい原子が浸透する。不純物深さはこの溶融する深さで決定され、不純物のプロファイルは非常に急峻になる。また、ガスクラスターの衝突過程では、照射される表面近傍で多体衝突が生じるため、上述のチャネリングは発生しない。また、上記の溶融により、対象膜の結晶構造が崩れる効果もあり、チャネリングは発生しない。また、クラスターの平均的な値は、上述のように数1000個以上にすることができ、原子1個当たりのエネルギーは、イオン注入の場合に比べ非常に低くすることができる。これらの効果に関しては、「クラスターイオンビーム基礎と応用」山田公編著、日刊工業新聞社、ISBN4-526-05765-7、p.146-147等に記述されている。

【0055】

(ガスクラスター照射装置)

次に、イオン化したガスクラスターの照射に用いられるガスクラスター照射装置について説明する。

【0056】

図5に、本実施の形態で用いられるクラスターイオン照射装置を示す。このクラスターイオン照射装置は、ガスクラスターを生成するノズル部51、イオン化電極52、加速電極53、クラスター選別部54を有している。

【0057】

ノズル部51では、圧縮されたガスによりガスクラスターが生成される。具体的には、高圧状態でノズル部51に供給されたガスが、ノズル部51より噴出することにより、ガスクラスターが生成される。この際に用いられるガスは、酸素等のガスであり、常温で気体状態を示すものが好ましい。

【0058】

イオン化電極52では、生成されたガスクラスターをイオン化する。これにより、生成されたガスクラスターがイオン化される。

【0059】

次に、加速電極53によりイオン化したガスクラスターが加速される。この際、ガスクラスターは、ガスクラスターを構成する原子の数の平方根、即ち、質量の平方根に反比例する速度で加速される。また、イオン化されている価数の平方根に比例する速度で加速される。

【0060】

次に、クラスター選別部54においてガスクラスターがイオン化されている価数や質量に応じて選別される。具体的には、クラスター選別部54は、電界又は磁界を印加することによりクラスターにはならなかったモノマーイオン等を除去する。

【0061】

この後、ガスクラスター照射装置より供給されるイオン化したガスクラスター55を誘電体膜等に照射する。

【0062】

〔第2の実施の形態〕

次に、図6に基づき第2の実施形態について説明する。本実施の形態は、Si基板等からなる半導体基板上に誘電体膜の膜厚(high-k膜の膜厚)の異なる領域を形成した構造の半導体装置の形成方法に関するものである。

【0063】

最初に、図6(a)に示すように、Si基板からなる半導体基板201に、素子分離202、ウェル203を形成し、半導体基板201の表面に、好ましくは1nm以下のSiO2を主成分とする界面層204を形成する。界面層204の形成方法としては、H2SO4とH2O2との混合液や、H2O2とNH4OHとH2O2の混合液や、O3を溶存させた液などの薬液処理、酸素を含むラジカル等による酸化処理、酸素などの酸化種を含む気体中での熱酸化などがあげられる。さらに、界面層204上にhigh-k膜205を形成する。high-k膜205の材料としては、HfO2、ZrO2、Al2O3、Ta2O5、TiO2や、希土類酸化物、及びこれらの混合、及びこれらにSiを添加したもの、さらにそれらを窒化処理したもの等があげられる。high-k膜205の膜厚は、この後のエッチング工程において除去される分量を勘案して、厚い部分と薄い部分の膜厚要求を満たすように設定される。high-k膜205の成膜方法としては、CVDまたはALDが好適であるが、添加する物質の種類によっては、PVDを併用することもできるし、プラズマ窒化等を併用することもできる。

【0064】

次に、図6(b)に示すように、high-k膜205が厚く残される領域上にレジストパターン206を形成する。

【0065】

次に、図6(c)に示すように、イオン化したガスクラスター207を照射する。このイオン化したガスクラスター207は、第1の実施形態において説明したイオン化したガスクラスターと同様のものであり、イオン化したガスクラスターが照射された領域における表面の状態を変質させる。これにより、レジストパターン206の形成されていない領域の膜厚方向の一部には、変質層205aが形成される。

【0066】

次に、図6(d)に示すように、レジストパターン206をH2SO4とH2O2との混合液により、またはアッシングにより除去する。

【0067】

次に、図6(e)に示すように、希弗酸によりウェットエッチングを行う。イオン化したガスクラスターの照射されていない領域は、図4のサンプルAに対応し、ほとんどエッチングされることはない。これに対し、イオン化したガスクラスターの照射された領域は図4のサンプルBに対応し、表面の1〜2nmがエッチングされるものの、その後はほとんどエッチングされない。このようにして変質層205aは除去される。これにより、エッチング等による除去がされていない膜厚の厚いhigh-k膜205bが形成された領域b1と、変質層205aが除去された膜厚の薄いhigh-k膜205cが形成された領域b2とを形成することができる。

【0068】

本実施形態における製造方法によれば、半導体基板201の表面が露出した状態でレジストがSi基板である半導体基板201の表面に形成されること等がない。即ち、引き続き行われるゲート絶縁膜の形成工程に、レジストパターン206からのC(炭素)等の付着や拡散がない。よって、Si基板である半導体基板201とゲート絶縁膜の界面に界面準位が形成される要因、また、ゲート絶縁膜の絶縁破壊耐圧の低下の要因を排除することができ、品質の高いMOS型FETを製造することができる。

【0069】

また、従来技術による製造方法では、リーク電流を抑制するためにhigh-k膜を使っているが、膜厚差をつけるためにSiO2を用いている。よって、一部では厚いSiO2膜とhigh-k膜とが積層された構造となるため、全部をhigh-kにした場合に比べてリーク電流の低減効果が小さい。しかし、本実施形態による製造方法では、リーク電流を抑制するためにhigh-k膜を使っているので、絶縁膜積層構造におけるhigh-kの膜厚の比率がより大きくなる。このため、リーク電流の低減効果が大きく、リーク電流の少ない高品質のMOS型FETを製造することができる。

【0070】

以上、本発明の実施に係る形態について説明したが、上記内容は、発明の内容を限定するものではない。

【符号の説明】

【0071】

11 半導体基板

12 high-k膜

12a ゲート領域のhigh-k膜

12b 変質膜

13 電極膜

13a ゲート電極

14 ハードマスク層

14a ハードマスク

15 レジストパターン

21 半導体基板

22 素子分離領域

23 ウェル

24 SiO2膜

25 レジストパターン

26 SiO2膜

27 high-k膜

51 ノズル部

52 イオン化電極

53 加速電極

54 クラスター選別部

55 ガスクラスター

101 半導体基板

102 high-k膜

102a ゲート領域のhigh-k膜

102b 変質層

103 電極膜

103a ゲート電極

104 ハードマスク層

104a ハードマスク

105 レジストパターン

201 半導体基板

202 素子分離領域

203 ウェル

204 界面層

205 high-k膜

205a 変質膜

205b 厚いhigh-k膜

205c 薄いhigh-k膜

206 レジストパターン

207 ガスクラスター

b1 厚いhigh-k膜が形成された領域

b2 薄いhigh-k膜が形成された領域

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関するもので、特にMIS型FETの製造方法に関する。

【背景技術】

【0002】

従来、MIS(Metal-Insulator-Semiconductor)型FET(Field-Effect Transistor)のゲート絶縁膜として、シリコン酸化膜が用いられている。シリコン基板を熱酸化して形成されたシリコン酸化膜は、シリコン基板との界面における欠陥が少なく、偶発的な絶縁破壊が起きる確率も低いため、非常に品質が高い絶縁膜となる。

【0003】

近年、より一層の半導体装置の高集積化の要求に伴い、LSIに用いるMIS型FETは、その寸法を比例関係を保ったまま縮小することでその性能を継続的に向上させてきた。現在、最新のLogic LSI等では、ゲート長40nm以下、ゲート絶縁膜として用いられるシリコン酸化膜の膜厚2nm未満のものが用いられている。本来の比例縮小の原則に従うならば、ゲート絶縁膜は膜厚1nm程度のシリコン酸化膜を用いることが好ましいが、物理膜厚が1nm程度のシリコン酸化膜は、直接トンネリングによるリーク電流が非常に大きく、LSIの消費電力の増大をもたらすこととなる。これを解決するために、high-k膜と呼ばれるシリコン酸化物よりも誘電率の大きい金属酸化物、たとえばHfO2、ZrO2、Al2O3、TiO2などを主成分とした膜がゲート絶縁膜として用いられている。high-k膜を用いることにより、物理膜厚の厚い膜であっても、シリコン酸化物の場合と同等のゲート容量を得ることができるため、トンネル電流の増大を抑制し、消費電力の小さいLSIを製造することができる。

【0004】

以下、図1に基づき第1の従来技術による半導体装置の製造方法を説明する。

【0005】

最初に、図1(a)に示すようにSi基板等の半導体基板11上にhigh-k膜12をCVD(Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いて形成する。ここで形成されるhigh-k膜12は、としてはHfO2(酸化ハフニウム)などを主体とする膜が代表的である。

【0006】

次に、図1(b)に示すように、high-k膜12上に電極膜13を形成する。電極膜13は単層の多結晶シリコンからなる場合もあるし、下層にTiN等の金属層、上層に多結晶シリコンを積層した構造からなる場合もある。

【0007】

次に、図1(c)に示すように、ハードマスク層14を成膜し、その上にフォトリソグラフィ法等によりレジストパターン15を形成する。その後、レジストパターン15をマスクとしてハードマスク層14の露出している領域をRIE(reactive ion etching)等の異方性エッチングにより除去し、更に、レジストパターン15をアッシング等で除去することにより、図1(d)に示すようにハードマスク14aを形成する。

【0008】

次に、図1(e)に示すように、ハードマスク14aをマスクとして電極膜13の露出している領域をhigh-k膜12に対して選択的にエッチングすることにより、ゲート電極13aを形成する。

【0009】

次に、図1(f)に示すように、ハードマスク14a及びゲート電極13aをマスクとしてRIE等の異方性エッチングを行うことにより、露出しているhigh-k膜12を半導体基板11に対して選択的にエッチングし、半導体基板11を露出させる。これにより、ゲート領域のhigh-k膜12aを形成する。

【0010】

この後、低加速イオン注入と高温短時間アニール等を組み合わせた工程で、浅い不純物拡散層を含むソース・ドレインを形成し、さらに配線を形成してhigh-kゲート絶縁膜を有するMIS型FETを形成することができる。

【0011】

また、異方性エッチングの代わりに、ウェットエッチング等の等方性エッチングを用いて、ゲート電極13aの形成されていない領域のhigh-k膜12を除去しても同等の効果を得ることができる。このような方法により形成されたものの典型的な断面図を図1(g)に示す。

【0012】

一方で、実際のLSIを製造する場合、回路的な要請に応じて同一チップ内で複数の異なる仕様のFETを組み合わせて使用することが通常行われている。この場合、FETのゲート絶縁膜も絶縁膜耐圧やリーク電流などの仕様に合わせて複数の異なる膜厚のものを用いる場合がある。以下図2に基づき第2の従来技術による半導体装置の製造方法を説明する。この方法はhigh-kを用いて多種膜厚のゲート絶縁膜を形成する方法である。

【0013】

最初に、図2(a)に示すように、Si基板等の半導体基板21に素子分離領域22、ウェル23を形成し、さらに半導体基板21の表面を熱酸化することによりSiO2膜24を形成する。

【0014】

次に、図2(b)に示すように、フォトリソグラフィ法等を用いてレジストパターン25を形成する。

【0015】

次に、図2(c)に示すように、レジストパターン25の形成されていない領域のSiO2膜24を希弗酸等を用いて除去する。

【0016】

次に、図2(d)に示すように、レジストパターン25をアッシングやH2SO4とH2O2との混合液等を用いて除去する。このようにして、SiO2膜24が形成されている領域a1とSiO2膜24が形成されていない領域a2とを形成する。

【0017】

次に、図2(e)に示すように、半導体基板21の表面に熱酸化によりSiO2膜を形成する。これにより、SiO2膜24が形成されている領域a1においては、SiO2膜24を含む膜厚の厚いSiO2膜26aが形成され、SiO2膜24が形成されていない領域a2においては、熱酸化により形成された膜厚の薄いSiO2膜26bが形成される。

【0018】

次に、図2(f)に示すように、high-k膜27を形成する。これにより、領域a1においては、厚いSiO2膜26aとhigh-k膜27とが積層された絶縁膜が形成され、領域a2においては、薄いSiO2膜26bとhigh-k膜27とが積層された絶縁膜とが形成される。

【0019】

この後、第1の従来例と同様の方法で、ゲート電極、ソース・ドレイン等を形成することによりMIS型FETが作製される。

【0020】

上記においては、2種類の異なる絶縁膜厚を有するMIS型FETの製造方法について説明したが、同様に追加のフォトリソグラフィとウェットエッチング、酸化を所望の回数行うことで、2種類より多い異なる絶縁膜厚を有するMIS型FETを製造することも可能である。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2004−71973号公報

【特許文献2】特開2002−33477号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

ところで、第1の従来技術による半導体装置の製造方法によれば、図1(f)に示すRIE等のエッチング工程においては、半導体基板との選択性に注意した場合であってもほとんどの場合その選択比は不十分であり、Si基板等の半導体基板11においてオーバーエッチング16aが発生する。また、半導体基板11の基板面に対して垂直な方向への運動エネルギーをもったイオンによりエッチングが行なわれるため、半導体基板11がエッチングされた部分では、ダメージ16bが発生しやすい。これらはいずれも、形成される半導体装置の性能を損なうものである。

【0023】

また、第2の従来技術による半導体装置の製造方法によれば、図2(c)に示すようにSiO2膜24の表面にレジストパターン25を形成しRIE等によりレジストパターン25の形成されていない領域のSiO2膜24を除去するものであるため、レジストパターンやエッチングガスに含まれるC(炭素)等が、半導体基板21またはSiO2膜24の表面に付着し拡散し、半導体基板21とゲート絶縁膜との界面に界面準位が形成される要因や、ゲート絶縁膜の絶縁破壊耐圧の低下の要因となっていた。

【0024】

従って、基板にダメージを与えることなく誘電体膜を完全に除去することによりゲート絶縁膜を形成することができる半導体装置の製造方法、また、シリコン基板等の半導体基板の表面を清浄に保ちつつ基板上に異なる膜厚の誘電体膜を形成することのできる半導体装置の製造方法が望まれている。

【課題を解決するための手段】

【0025】

本発明は、半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする。

【0026】

また、本発明は、前記誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする。

【0027】

また、本発明は、前記電極形成工程は、前記誘電体膜上に電極膜を形成し、前記電極膜上に酸化膜又は窒化膜からなる化合物膜を形成し、前記化合物膜上にレジストパターンを形成し、前記レジストパターンをマスクとして前記レジストパターンの形成されていない領域の化合物膜を除去することにより化合物マスクを形成し、前記化合物マスクの形成されていない領域における前記電極膜を除去するものであることを特徴とする。

【0028】

また、本発明は、前記誘電体膜の膜厚は、2nm以下であることを特徴とする。

【0029】

また、本発明は、半導体基板上に誘電体膜を形成する誘電体膜形成工程と、前記誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、前記レジストパターンの形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、を含むものであって、前記誘電体膜はゲート絶縁膜となるものであり、前記誘電体膜の膜厚が異なる2つの領域を形成することを特徴とする。

【0030】

また、本発明は、半導体基板上に第1の誘電体膜を形成する第1誘電体膜形成工程と、前記第1誘電体膜上に前記第1の誘電体膜を構成する材料の比誘電率よりも高い比誘電率を有する材料により構成される第2の誘電体膜を形成する第2誘電体膜形成工程と、前記第2の誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、前記レジストパターンの形成されていない前記第2の誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記第2の誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、を含むものであって、ゲート絶縁膜は前記第1の誘電体膜と前記第2の誘電体膜とにより形成されるものであり、前記ゲート絶縁膜は、前記イオン化したガスクラスターが照射された領域とされていない領域とにおいて膜厚が異なるものであることを特徴とする。

【0031】

また、本発明は、前記誘電体膜または前記第2の誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする。

【0032】

また、本発明は、前記ウェットエッチングは希フッ酸によるエッチングであることを特徴とする。

【0033】

また、本発明は、前記ガスクラスターを構成する原子の数の平均は、1000以上であることを特徴とする。

【発明の効果】

【0034】

本発明によれば、ゲート絶縁膜等としてHigh-k膜を用いた場合において、基板にダメージを与えることなく完全に除去することのできる半導体装置の製造方法、及び、基板上に異なる膜厚のHigh-k膜を形成する場合に、できるだけコンタミの混入を低減させた半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0035】

【図1】(a)〜(f) 第1の従来技術による半導体装置の製造方法の工程断面図、(g) 第1の従来技術による半導体装置の他の製造方法の説明図

【図2】(a)〜(f) 第2の従来技術による半導体装置の製造方法の工程断面図

【図3】(a)〜(g) 第1の実施の形態における半導体装置の製造方法の工程断面図

【図4】ガスクラスター照射有無によるhigh-k膜の特性図

【図5】ガスクラスター照射装置の構成図

【図6】(a)〜(e) 第2の実施の形態における半導体装置の製造方法の工程断面図

【発明を実施するための形態】

【0036】

本発明を実施するための形態について、以下に説明する。

【0037】

〔第1の実施の形態〕

第1の実施の形態を図3に基づき説明する。本実施の形態はゲート絶縁膜としてhigh-k膜を形成する半導体装置の製造方法である。

【0038】

最初に、図3(a)に示すように、Si基板等の半導体基板101上にhigh-k膜102を成膜する。ここで形成されるhigh-k膜102を構成する材料としてHfO2(酸化ハフニウム)、ZrO2(酸化ジルコニウム)、Al2O3(酸化アルミニウム)、Ta2O5(五酸化タンタル)、TiO2(酸化チタン)、希土類酸化物等及びこれらの混合、及びこれらにSiを添加したもの、さらにそれらを窒化処理したもの等があげられる。high-k膜の形成方法としては、CVDまたはALDが好適であるが、添加する物質の種類によっては、PVDを併用することもできるし、プラズマ窒化等を併用することもできる。high-k膜102の膜厚は、現在最先端のLogic LSIに用いられているもので、典型的には2nmを下回る程度である。high-k膜102を形成した後、望ましくは500℃乃至800℃で数分から数十分、あるいは、900℃乃至1100℃で数秒以内の熱処理を行う。熱処理を行う雰囲気は、Ar、N2などの不活性ガスあるいは、これらに数%以下の微量の酸素を添加した雰囲気が好適である。この熱処理は、high-k膜を緻密化し、誘電率を高くする効果と、後で説明するように、希弗酸によるエッチングレートを遅くする効果がある。

【0039】

次に、図3(b)に示すように、high-k膜102上に電極膜103を形成する。電極膜103としては、多結晶シリコンなどが代表的である。多結晶シリコンには抵抗を低下させ、電極として適切な仕事関数を与えるために、As(ヒ素)、P(リン)等のn型を示す導電性不純物か、あるいはB(ホウ素)等のp型を示す導電性不純物を添加した後に、熱処理を行い電気的に活性化させる。この不純物添加と活性化の処理は、ゲート電極のパターニング前に行ってもよいし、ゲートパターニング後にマスクを除去してから行ってもよい。また、ゲート電極としては、下層に所望の仕事関数を持つ金属を堆積し、その上に適宜多結晶シリコンに導電性不純物を添加した膜やWを含む膜等の電極のシート抵抗を低下させるための膜を積層したものでもよい。ただし、これらの膜は、後にhigh-k膜102の一部を希弗酸で除去する工程の際に、希弗酸におけるエッチングレートが十分に遅いことが必要である。

【0040】

次に、図3(c)に示すように、電極膜103上にハードマスク層104としてSiO2膜を形成し、更に、ハードマスク層104上にレジストパターン105を形成する。ハードマスク層は、SiO2を主成分とするもの等が代表的であるが、電極膜103の材質によってはSiNを主成分とするもの等を適宜選択することができる。また、レジストパターン105は、ハードマスク層104上にフォトレジストを塗布し、プリベーク、露光装置による露光、現像を行うことにより、ハードマスク層104上において、後述するハードマスク104aが形成される領域にレジストパターン105を形成する。

【0041】

次に、図3(d)に示すように、レジストパターン105をマスクとしてハードマスク層104を異方性エッチングし、この後、アッシング等によりレジストパターン105を除去する。これによりハードマスク104aを形成する。

【0042】

次に、図3(e)に示すように、ハードマスク104aをマスクとして、露出している電極膜103を異方性エッチングにより除去することにより、ゲート電極103aを形成する。このとき、電極膜103を形成する材料である多結晶シリコン、金属などはHBr、Cl2、SF6、NF3等を含むガスを用いてRIE等により異方性エッチングすることで、良好にエッチングされることが知られているが、一般にこれらのガス系による基板加熱を併用しないエッチングでは、high-k膜102に対するエッチングレートが非常に遅いことが知られている。そのため、high-k膜102は図に示すように残存する。

【0043】

次に、図3(f)に示すように、イオン化したガスクラスター106を照射することにより、ゲート電極103aの形成されていない領域のhigh-k膜102が変質し、変質膜102bが形成される。この変質膜102bは、後述するように弗酸を含む液に対して高いエッチングレートを持つ。尚、イオン化したガスクラスターの照射装置については後述する。イオン化したガスクラスターに用いられる元素としては、アルゴン、酸素、窒素等が挙げられる。

【0044】

次に、図3(g)に示すように、弗酸を含む液を用いて、変質膜102bを除去する。これにより、ゲート電極103aの形成されている領域にのみゲート領域のhigh-k膜102aを形成することができる。

【0045】

この後、ハードマスク104a及びゲート電極103aをマスクとして半導体基板101にイオン注入を行うことにより、ゲート電極103aに対して自己整合的にソース/ドレイン電極を形成し、周知の方法で層間絶縁膜及び配線を形成する。これにより、high-k膜を有するMOS型FETを形成することができる(図示せず)。

【0046】

本実施の形態における半導体装置の製造方法によれば、半導体基板101にダメージを与えることなく、表面の露出した領域のhigh-k膜102を変質膜102bとし、ウェットエッチングにより完全に除去することができる。これにより、後に形成するソース/ドレインの接合リーク電流の少ない、高品質のMOS型FETを製造することができる。

(high-k膜の特性)

次に、本実施の形態において形成したhigh-k膜のエッチング特性について説明する。ここで用いたhigh-k膜の材料は酸化アルミニウムであり、CVD法を用いて成膜を行った。尚、サンプルAはhigh-k膜を20nm成膜した後に850℃で300秒の熱処理を行った状態のものであり、サンプルBはサンプルAと同様の熱処理を行った後に、さらにクラスターイオンを照射したものである。

【0047】

図4に純水:弗酸=1:100の溶液中でウェットエッチングを行った場合のhigh-k膜厚の時間依存性を示す。サンプルAは、high-k膜が熱処理により結晶化しているため、希弗酸によりほとんどエッチングされない。一方、サンプルBは希弗酸によりhigh-k膜の表面の1〜2nm程度がエッチングされるが、その後はほとんどエッチングされない。

【0048】

このように、イオン化したガスクラスターの照射により、照射された膜の表面の状態は変質するため、本実施の形態を説明する図3(f)に示すように、イオン化したガスクラスターの照射された領域におけるhigh-k膜は、その表面の1〜2nmが変質し、希弗酸によるエッチングがされやすくなったものと推察される。

【0049】

尚、本実施の形態における変質される深さに関しては、イオン化したガスクラスターの条件を調節することにより調整可能である。

【0050】

また、上述したhigh-k膜の特性については、Al2O3について示したが、HfO2、ZrO2、Ta2O5、TiO2についても同様の傾向にある。

【0051】

また、本実施の形態では、イオン化したガスクラスターとして、酸素のイオン化したガスクラスターを用いたが、窒素およびアルゴン等のイオン化したガスクラスターを用いた場合にも同様の効果が得られる。

【0052】

尚、膜中に元素を導入する類似の方法としては、イオン注入法が代表的である。しかし、原子または分子がイオン化されたイオンを膜に注入する方法では、薄いhigh-k膜のみを改質することが非常に困難であり、high-k膜を通り抜け基板にも影響を与えてしまう。

【0053】

また、膜を改質するには、1×1021〜1×1022cm−3程度の密度に原子を注入することが必要であるが、一方で、膜と接するSi基板に注入される原子は1×1018cm−3台を超えるとSi基板自体を酸化するなどの弊害が出てくる。イオン注入では、膜を改質し、Si基板を酸化しないという両方の条件を満たすようなプロファイルを得ることが非常に困難である。また、本発明のように、結晶化した膜を注入の対象にする場合には、結晶の特定の方位に対して、一定数のイオンが散乱を受けずに透過してしまうチャネリングと呼ばれる現象が起こるため、膜の深い位置までイオンが到達する確率が高くなる。

【0054】

一方で、ガスクラスター注入ではイオン注入と不純物導入の原理が異なるためこのような条件を満たすプロファイルを得ることが可能である。数1000個程度の原子数を持つガスクラスターが注入の対象物に衝突すると、瞬間的に衝突が起きた近傍で高温高圧領域が形成される。これで、対象物が瞬間的に溶融し、溶融した部分に注入したい原子が浸透する。不純物深さはこの溶融する深さで決定され、不純物のプロファイルは非常に急峻になる。また、ガスクラスターの衝突過程では、照射される表面近傍で多体衝突が生じるため、上述のチャネリングは発生しない。また、上記の溶融により、対象膜の結晶構造が崩れる効果もあり、チャネリングは発生しない。また、クラスターの平均的な値は、上述のように数1000個以上にすることができ、原子1個当たりのエネルギーは、イオン注入の場合に比べ非常に低くすることができる。これらの効果に関しては、「クラスターイオンビーム基礎と応用」山田公編著、日刊工業新聞社、ISBN4-526-05765-7、p.146-147等に記述されている。

【0055】

(ガスクラスター照射装置)

次に、イオン化したガスクラスターの照射に用いられるガスクラスター照射装置について説明する。

【0056】

図5に、本実施の形態で用いられるクラスターイオン照射装置を示す。このクラスターイオン照射装置は、ガスクラスターを生成するノズル部51、イオン化電極52、加速電極53、クラスター選別部54を有している。

【0057】

ノズル部51では、圧縮されたガスによりガスクラスターが生成される。具体的には、高圧状態でノズル部51に供給されたガスが、ノズル部51より噴出することにより、ガスクラスターが生成される。この際に用いられるガスは、酸素等のガスであり、常温で気体状態を示すものが好ましい。

【0058】

イオン化電極52では、生成されたガスクラスターをイオン化する。これにより、生成されたガスクラスターがイオン化される。

【0059】

次に、加速電極53によりイオン化したガスクラスターが加速される。この際、ガスクラスターは、ガスクラスターを構成する原子の数の平方根、即ち、質量の平方根に反比例する速度で加速される。また、イオン化されている価数の平方根に比例する速度で加速される。

【0060】

次に、クラスター選別部54においてガスクラスターがイオン化されている価数や質量に応じて選別される。具体的には、クラスター選別部54は、電界又は磁界を印加することによりクラスターにはならなかったモノマーイオン等を除去する。

【0061】

この後、ガスクラスター照射装置より供給されるイオン化したガスクラスター55を誘電体膜等に照射する。

【0062】

〔第2の実施の形態〕

次に、図6に基づき第2の実施形態について説明する。本実施の形態は、Si基板等からなる半導体基板上に誘電体膜の膜厚(high-k膜の膜厚)の異なる領域を形成した構造の半導体装置の形成方法に関するものである。

【0063】

最初に、図6(a)に示すように、Si基板からなる半導体基板201に、素子分離202、ウェル203を形成し、半導体基板201の表面に、好ましくは1nm以下のSiO2を主成分とする界面層204を形成する。界面層204の形成方法としては、H2SO4とH2O2との混合液や、H2O2とNH4OHとH2O2の混合液や、O3を溶存させた液などの薬液処理、酸素を含むラジカル等による酸化処理、酸素などの酸化種を含む気体中での熱酸化などがあげられる。さらに、界面層204上にhigh-k膜205を形成する。high-k膜205の材料としては、HfO2、ZrO2、Al2O3、Ta2O5、TiO2や、希土類酸化物、及びこれらの混合、及びこれらにSiを添加したもの、さらにそれらを窒化処理したもの等があげられる。high-k膜205の膜厚は、この後のエッチング工程において除去される分量を勘案して、厚い部分と薄い部分の膜厚要求を満たすように設定される。high-k膜205の成膜方法としては、CVDまたはALDが好適であるが、添加する物質の種類によっては、PVDを併用することもできるし、プラズマ窒化等を併用することもできる。

【0064】

次に、図6(b)に示すように、high-k膜205が厚く残される領域上にレジストパターン206を形成する。

【0065】

次に、図6(c)に示すように、イオン化したガスクラスター207を照射する。このイオン化したガスクラスター207は、第1の実施形態において説明したイオン化したガスクラスターと同様のものであり、イオン化したガスクラスターが照射された領域における表面の状態を変質させる。これにより、レジストパターン206の形成されていない領域の膜厚方向の一部には、変質層205aが形成される。

【0066】

次に、図6(d)に示すように、レジストパターン206をH2SO4とH2O2との混合液により、またはアッシングにより除去する。

【0067】

次に、図6(e)に示すように、希弗酸によりウェットエッチングを行う。イオン化したガスクラスターの照射されていない領域は、図4のサンプルAに対応し、ほとんどエッチングされることはない。これに対し、イオン化したガスクラスターの照射された領域は図4のサンプルBに対応し、表面の1〜2nmがエッチングされるものの、その後はほとんどエッチングされない。このようにして変質層205aは除去される。これにより、エッチング等による除去がされていない膜厚の厚いhigh-k膜205bが形成された領域b1と、変質層205aが除去された膜厚の薄いhigh-k膜205cが形成された領域b2とを形成することができる。

【0068】

本実施形態における製造方法によれば、半導体基板201の表面が露出した状態でレジストがSi基板である半導体基板201の表面に形成されること等がない。即ち、引き続き行われるゲート絶縁膜の形成工程に、レジストパターン206からのC(炭素)等の付着や拡散がない。よって、Si基板である半導体基板201とゲート絶縁膜の界面に界面準位が形成される要因、また、ゲート絶縁膜の絶縁破壊耐圧の低下の要因を排除することができ、品質の高いMOS型FETを製造することができる。

【0069】

また、従来技術による製造方法では、リーク電流を抑制するためにhigh-k膜を使っているが、膜厚差をつけるためにSiO2を用いている。よって、一部では厚いSiO2膜とhigh-k膜とが積層された構造となるため、全部をhigh-kにした場合に比べてリーク電流の低減効果が小さい。しかし、本実施形態による製造方法では、リーク電流を抑制するためにhigh-k膜を使っているので、絶縁膜積層構造におけるhigh-kの膜厚の比率がより大きくなる。このため、リーク電流の低減効果が大きく、リーク電流の少ない高品質のMOS型FETを製造することができる。

【0070】

以上、本発明の実施に係る形態について説明したが、上記内容は、発明の内容を限定するものではない。

【符号の説明】

【0071】

11 半導体基板

12 high-k膜

12a ゲート領域のhigh-k膜

12b 変質膜

13 電極膜

13a ゲート電極

14 ハードマスク層

14a ハードマスク

15 レジストパターン

21 半導体基板

22 素子分離領域

23 ウェル

24 SiO2膜

25 レジストパターン

26 SiO2膜

27 high-k膜

51 ノズル部

52 イオン化電極

53 加速電極

54 クラスター選別部

55 ガスクラスター

101 半導体基板

102 high-k膜

102a ゲート領域のhigh-k膜

102b 変質層

103 電極膜

103a ゲート電極

104 ハードマスク層

104a ハードマスク

105 レジストパターン

201 半導体基板

202 素子分離領域

203 ウェル

204 界面層

205 high-k膜

205a 変質膜

205b 厚いhigh-k膜

205c 薄いhigh-k膜

206 レジストパターン

207 ガスクラスター

b1 厚いhigh-k膜が形成された領域

b2 薄いhigh-k膜が形成された領域

【特許請求の範囲】

【請求項1】

半導体基板上に誘電体膜を形成する成膜工程と、

前記誘電体膜を熱処理する熱処理工程と、

前記誘電体膜上の一部に電極を形成する電極形成工程と、

前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記電極形成工程は、

前記誘電体膜上に電極膜を形成し、

前記電極膜上に酸化膜又は窒化膜からなる化合物膜を形成し、

前記化合物膜上にレジストパターンを形成し、

前記レジストパターンをマスクとして前記レジストパターンの形成されていない領域の化合物膜を除去することにより化合物マスクを形成し、

前記化合物マスクの形成されていない領域における前記電極膜を除去するものであることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記誘電体膜の膜厚は、2nm以下であることを特徴とする請求項1から3のいずれかに記載の半導体装置の製造方法。

【請求項5】

半導体基板上に誘電体膜を形成する誘電体膜形成工程と、

前記誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、

前記レジストパターンの形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、

を含むものであって、

前記誘電体膜はゲート絶縁膜となるものであり、前記誘電体膜の膜厚が異なる2つの領域を形成することを特徴とする半導体装置の形成方法。

【請求項6】

半導体基板上に第1の誘電体膜を形成する第1誘電体膜形成工程と、

前記第1誘電体膜上に前記第1の誘電体膜を構成する材料の比誘電率よりも高い比誘電率を有する材料により構成される第2の誘電体膜を形成する第2誘電体膜形成工程と、

前記第2の誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、

前記レジストパターンの形成されていない前記第2の誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記第2の誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、

を含むものであって、

ゲート絶縁膜は前記第1の誘電体膜と前記第2の誘電体膜とにより形成されるものであり、前記ゲート絶縁膜は、前記イオン化したガスクラスターが照射された領域とされていない領域とにおいて膜厚が異なるものであることを特徴とする半導体装置の形成方法。

【請求項7】

前記誘電体膜または前記第2の誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記ウェットエッチングは希フッ酸によるエッチングであることを特徴とする請求項1から7のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記ガスクラスターを構成する原子の数の平均は、1000以上であることを特徴とする請求項1から8のいずれかに記載の半導体装置の製造方法。

【請求項1】

半導体基板上に誘電体膜を形成する成膜工程と、

前記誘電体膜を熱処理する熱処理工程と、

前記誘電体膜上の一部に電極を形成する電極形成工程と、

前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記電極形成工程は、

前記誘電体膜上に電極膜を形成し、

前記電極膜上に酸化膜又は窒化膜からなる化合物膜を形成し、

前記化合物膜上にレジストパターンを形成し、

前記レジストパターンをマスクとして前記レジストパターンの形成されていない領域の化合物膜を除去することにより化合物マスクを形成し、

前記化合物マスクの形成されていない領域における前記電極膜を除去するものであることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記誘電体膜の膜厚は、2nm以下であることを特徴とする請求項1から3のいずれかに記載の半導体装置の製造方法。

【請求項5】

半導体基板上に誘電体膜を形成する誘電体膜形成工程と、

前記誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、

前記レジストパターンの形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、

を含むものであって、

前記誘電体膜はゲート絶縁膜となるものであり、前記誘電体膜の膜厚が異なる2つの領域を形成することを特徴とする半導体装置の形成方法。

【請求項6】

半導体基板上に第1の誘電体膜を形成する第1誘電体膜形成工程と、

前記第1誘電体膜上に前記第1の誘電体膜を構成する材料の比誘電率よりも高い比誘電率を有する材料により構成される第2の誘電体膜を形成する第2誘電体膜形成工程と、

前記第2の誘電体膜上にレジストパターンを形成するレジストパターン形成工程と、

前記レジストパターンの形成されていない前記第2の誘電体膜にイオン化したガスクラスターを照射する照射工程と、

前記第2の誘電体膜のうち、前記イオン化したガスクラスターが照射された領域の膜厚方向の一部をウェットエッチングにより除去するエッチング工程と、

を含むものであって、

ゲート絶縁膜は前記第1の誘電体膜と前記第2の誘電体膜とにより形成されるものであり、前記ゲート絶縁膜は、前記イオン化したガスクラスターが照射された領域とされていない領域とにおいて膜厚が異なるものであることを特徴とする半導体装置の形成方法。

【請求項7】

前記誘電体膜または前記第2の誘電体膜を構成する材料は、HfO2、ZrO2、Al2O3、Ta2O5、TiO2のいずれかを含む材料であることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記ウェットエッチングは希フッ酸によるエッチングであることを特徴とする請求項1から7のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記ガスクラスターを構成する原子の数の平均は、1000以上であることを特徴とする請求項1から8のいずれかに記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−80834(P2013−80834A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−220257(P2011−220257)

【出願日】平成23年10月4日(2011.10.4)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月4日(2011.10.4)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

[ Back to top ]