半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に高誘電体材料を含むゲート絶縁膜及び金属膜を含むゲート電極を備えた半導体装置の製造方法に関する。

【背景技術】

【0002】

CMOS(Complementary metal-oxide semiconductor)デバイスは、さらなる微細化が要求されている。CMOSデバイスをさらに微細化するためには、ゲート絶縁膜のさらなる薄膜化が必要となる。しかし、従来のシリコン酸化膜からなるゲート絶縁膜をさらに薄くすると、リーク電流の増大を誘発し、LSI(Large scale integration)回路の待機時電流が増大するおそれがある。このため、シリコン酸化膜からなるゲート絶縁膜の薄膜化は、限界を迎えている。そこで、シリコン酸化膜に代えて高誘電体材料からなる絶縁膜をゲート絶縁膜とする、CMIS(Complementary metal-insulator semiconductor)デバイスが注目されている。高誘電体材料からなる絶縁膜は、物理的な膜厚を厚くしても電気的な膜厚を薄くすることが可能であるため、ゲート絶縁膜の薄膜化をさらに進めることができると期待されている。現在、ゲート絶縁膜用の高誘電体材料として最も有望視されているのは、窒化ハフニウムシリケート(HfSiON)である。また、ゲート電極についても、従来のポリシリコンからなる電極ではその空乏化が無視できなくなってきており、空乏化が生じないメタルゲート電極の開発が盛んに行われている。

【0003】

一方、CMISデバイスを形成する場合には、n型のN−MISFET(N−metal-insulator semiconductor field effect transistor)とp型のP−MISFET(P−metal-insulator semiconductor field effect transistor)とが必要である。しかし、N−MISFETとP−MISFETとでは、ゲート絶縁膜及びゲート電極に求められる特性が互いに異なっている。具体的には、N−MISFETでは実効仕事関数を低くすることが好ましく、P−MISFETでは実効仕事関数を高くすることが好ましい。このため、実効仕事関数が低いN−MISFET用のゲート絶縁膜及びゲート電極と、実効仕事関数が高いP−MISFET用のゲート絶縁膜及びゲート電極とを作り別けるプロセスが提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−267342号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、前記従来のN−MISFETとP−MISFETとを作り別ける方法は、以下のような問題を有している。N−MISFETとP−MISFETとを作り別けるためには、N−MISFETを形成する領域又はP−MISFETを形成する領域の一方だけにキャップ膜を選択的に形成する必要がある。キャップ膜を選択的に形成する方法として、レジスト膜をマスクとして一方の領域に選択的にキャップ膜を形成する方法が知られている。

【0006】

しかし、レジスト膜をマスクとしてキャップ膜を選択的に形成する場合には、キャップ膜を成膜する際にレジスト膜が飛散して、パーティクルが発生したり、異常成長を引き起こしたりする原因となる。また、レジスト膜の上に形成されたキャップ膜がレジスト膜を除去する際に飛散し、レジスト膜の下側の層にキャップ膜が再付着するおそれがある。このため、半導体装置の特性が安定しないという問題がある。

【0007】

キャップ膜を形成した後、一方の領域を覆うレジスト膜を形成し、レジスト膜をマスクとしてドライエッチングを行うことにより、不要なキャップ膜を除去する方法も知られている。しかし、ドライエッチングによりキャップ膜の不要な部分を除去する方法の場合には、キャップ膜の下側の層もエッチングされてしまうおそれがある。また、ドライエッチング後の、残渣洗浄工程において、必要とするキャップ膜が薄くなるおそれがある。

【0008】

このように、従来のN−MISFETとP−MISFETとを作り別ける方法には種々の問題があり、半導体装置の特性を安定させることができず、信頼性が高い半導体装置を実現することが困難であるということを本願発明者らは見出した。

【0009】

本発明は、前記の問題を解決し、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するため、本発明は半導体装置の製造方法を、犠牲導電膜をハードマスクとして、キャップ膜を選択的に形成する構成とする。

【0011】

具体的に、本発明に係る半導体装置の製造方法は、半導体基板に、第1の素子形成領域及び第2の素子形成領域を形成する工程(a)と、半導体基板上の全面に高誘電体膜と、第1の金属元素を含む第1の膜と、犠牲導電膜と、第2の金属元素を含む第2の膜とを順次形成する工程(b)と、第2の膜における第1の素子形成領域の上に形成された部分を第1の薬液を用いて選択的に除去する工程(c)と、工程(c)よりも後で、第2の金属元素を犠牲導電膜における第2の素子形成領域の上に形成された部分に拡散させる工程(d)と、工程(d)よりも後で、犠牲導電膜及び第1の膜における第1の素子形成領域の上に形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去し、第1の素子形成領域において高誘電体膜を露出させる工程(e)と、工程(e)よりも後で、半導体基板上の全面に第3の金属元素を有する第3の膜を形成する工程(f)と、工程(f)よりも後で、第3の金属元素を高誘電体膜中に拡散させる工程(g)と、第3の膜及び犠牲導電膜の残存部分をそれぞれ第4の薬液及び第5の薬液を用いて除去する工程(h)と、(h)よりも後で、半導体基板上の全面に電極膜を形成する工程(i)と、電極膜及び高誘電体膜を選択的に除去することにより、第1の素子形成領域に、第3の金属元素を含む第1のゲート絶縁膜と、電極膜からなる第1のゲート電極とを形成し、第2の素子形成領域に、第1の金属元素を含む第2のゲート絶縁膜と、電極膜からなる第2のゲート電極とを形成する工程(j)とを備えている。

【0012】

本発明の半導体装置の製造方法は、犠牲導電膜からなるハードマスクを用いて、N−MISFET用のキャップ膜である第3の膜を選択的に形成する。このため、第3の膜を成膜する際にレジスト膜が飛散してパーティクルとなったり、異常成長の原因となったりすることがない。また、P−MISFET用のキャップ膜である第1の膜を、ウェットエッチングにより除去している。このため、N−MISFET領域において第1の膜を除去する際に、高誘電体膜はほとんどエッチングされない。従って、信頼性が高い半導体装置を容易に製造することが可能となる。

【0013】

本発明の半導体装置の製造方法において、犠牲導電膜は、窒化チタン、タングステン又は窒化タングステンとし、第2の膜は、酸化ランタンとすればよい。

【0014】

本発明の半導体装置の製造方法において、工程(e)では、第2の薬液としてpHを6以上且つ8以下に調整した、酸化剤を含む中性溶液を用いればよい。

【0015】

本発明の半導体装置の製造方において、酸化剤を含む中性溶液は、5質量%以上且つ30質量%以下の濃度の過酸化水素水とすればよい。

【0016】

本発明の半導体装置の製造方法において、工程(e)では、第3の薬液としてpHを1以下に調整した、酸化剤を含まない酸性溶液を用いればよい。

【0017】

本発明の半導体装置の製造方法において、工程(h)では、第4の薬液としてpHを2以上且つ4以下に調整した、酸化剤を含まない酸性溶液を用い、第5の薬液としてpHを2以上且つ4以下に調整した酸化剤を含む酸性溶液を用いればよい。

【0018】

本発明の半導体装置の製造方法は、工程(d)よりも後で且つ工程(e)よりも前に、第2の膜の犠牲導電膜の上に残存した部分を、pHを1以下に調整した、酸化剤を含まない酸性溶液を用いて除去する工程(k)をさらに備えていてもよい。

【0019】

本発明の半導体装置の製造方法において、工程(c)では、第1の薬液としてpHを4.0以上且つ4.9以下に調整した酸化剤を含まない酸性溶液を用いればよい。

【0020】

本発明の半導体装置の製造方法において、高誘電体膜は、比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物とすればよい。

【0021】

本発明の半導体装置の製造方法において、第2の金属元素は、アルミニウム又はタンタルとすればよい。

【0022】

本発明の半導体装置の製造方法において、第3の金属元素は、ランタン若しくはランタン以外のランタノイド、スカンジウム、ストロンチウム又はマグネシウムとすればよい。

【0023】

本発明の半導体装置の製造方法において、電極膜は、窒化チタン膜とシリコン膜との積層膜とすればよい。

【発明の効果】

【0024】

本発明に係る半導体装置の製造方法によれば、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できる。

【図面の簡単な説明】

【0025】

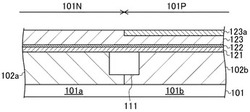

【図1】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図2】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図3】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図4】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図5】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図6】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図7】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図8】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図9】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図10】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図11】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【発明を実施するための形態】

【0026】

図1〜図11は、一実施形態に係る半導体装置の製造方法を工程順に示している。まず、図1に示すように、p型のシリコン基板である半導体基板101に、N−MISFET形成領域101N及びP−MISFET形成領域101Pを形成する。具体的には、まず、素子分離領域111により互いに分離された第1の活性領域101a及び第2の活性領域101bを半導体基板101に形成する。続いて、第1の活性領域101aにp型ウェル102aを形成し、第2の活性領域101bにn型ウェル102bを形成する。素子分離領域111は、半導体基板101に形成されたトレンチに絶縁膜を埋め込む、STI(Shallow Trench Isolation)法により形成すればよい。

【0027】

次に、図2に示すように、下地膜(図示せず)、高誘電体膜121、第1の膜122、犠牲導電膜123及び第2の膜124を半導体基板101上の全面に順次形成する。下地膜は、膜厚が1.1nm程度のシリコン酸化膜(SiO2)膜とすればよい。高誘電体膜121は、膜厚が1.7nm程度の窒素含有ハフニウムシリケート(HfSiON)膜とすればよい。高誘電体膜121は、原子層堆積(Atomic Layer Deposition:ALD)法により形成すればよい。高誘電体膜121は、HfSiON膜に代えて酸化ハフニウム(HfO2)膜又はハフニウムシリケート(HfSiOx)膜等としてもよい。また、この他にも比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物等の高誘電体材料により形成すればよい。第1の膜122は、膜厚が0.5nm程度の酸化アルミニウム(Al2O3)膜とすればよい。第1の膜122は、Al2O2膜に限らず、高誘電体膜121へ拡散させた場合にトランジスタの実効仕事関数を高くする第1の金属を含む材料により形成すればよい。犠牲導電膜123は、膜厚が10nm程度の窒化チタン(TiN)膜とすればよい。犠牲導電膜123は、ALD法により形成すればよい。犠牲導電膜123は、TiN膜に限らず、タングステン(W)膜又は窒化タングステン(WN)膜等であってもよい。第2の膜124は、例えば膜厚が5nmの酸化ランタン(La2O3)膜とすればよい。第2の膜124は、物理気相成長(PVD)法により形成すればよい。第2の膜124は、犠牲導電膜123へ拡散させた場合に、犠牲導電膜123のエッチング特性を変化させることができる第2の金属を含む材料により形成すればよい。

【0028】

次に、図3に示すように、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を選択的に除去する。具体的には、まず犠牲導電膜123の上に、N−MISFET形成領域101Nを露出し、P−MISFET形成領域101Pを覆うレジストパターン151をフォトリソグラフィ法により形成する。続いて、レジストパターン151をマスクとして、第1の薬液を用いたウェットエッチングにより、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を除去する。第1の薬液はpHをpH4.0〜4.9程度に調整した酸化剤を含まない弱酸性薬液とすればよい。例えば、36質量%の塩酸と水とを1対500000の体積比率で混合した塩酸水溶液を用いればよい。この場合pHは4.6程度となる。

【0029】

次に、図4に示すように、シンナー及び水酸化テトラメチルアンモニウム(TMAH)からなる現像液を用いてレジストパターン151を除去した後、第2の膜124に含まれるLaを犠牲導電膜123の上部に拡散させる。これにより、犠牲導電膜123におけるP−MISFET形成領域101Pに形成された部分の上部にLaを含む犠牲導電膜123aが形成される。その後、未拡散の第2の膜124を除去する。Laの拡散は熱処理により行えばよく、熱処理温度は600℃程度とし、処理時間は10分程度とすればよい。なお、熱処理温度は、500℃〜700℃程度であればよく、処理時間は5分〜10分程度であればよい。なお、熱処理の条件によっては第1の膜122に含まれるAlが高誘電体膜121の上部に拡散するが問題ない。未拡散の第2の膜124の除去は、ウェットエッチングにより行えばよい。エッチング溶液は、pHを1以下に調整した酸化剤を含まない強酸性薬液とすればよい。例えば、36質量%の塩酸と水とを1対50の体積比で混合した塩酸水溶液とすればよい。第2の膜124の膜厚及び熱処理条件等によっては、第2の膜124が全て拡散し、残存しない場合もある。この場合には未拡散の第2の膜124の除去を行わなくてもよい。

【0030】

次に、図5に示すように、犠牲導電膜123及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分をそれぞれ第2の薬液及び第3の薬液を用いたウェットエッチングにより除去する。第2の薬液は、pHを6〜8程度に調整した酸化剤を含む中性溶液とすればよい。例えば、5質量%〜30質量%の濃度の過酸化水素水を用いればよい。Laを含む犠牲導電膜123aは、pHを6〜8に調整した酸化剤を含む中性溶液に耐性を有する。このため、Laを含む犠牲導電膜123aがハードマスクとなり、犠牲導電膜123におけるN−MISFET形成領域101Nに形成された部分を選択的に除去することができる。第3の薬液は、pHを1以下に調整した酸化剤を含まない強酸性溶液とすればよい。例えば、36質量%の塩酸と水とを1対50の体積比で混合した塩酸水溶液を用いればよい。pHを1以下に調整した酸化剤を含まない強酸性溶液を用いたウェットエッチングの場合、HfSiONのエッチングレートに対するAl2O3のエッチングレートの比は10000以上となる。このため、高誘電体膜121をエッチングすることなく、第1の膜122を選択的に除去することが容易にできる。なお、高誘電体膜121の上部にAlが拡散している場合には、拡散したAlも問題にならない程度まで除去される。

【0031】

次に、図6に示すように、半導体基板101上の全面に第3の膜125を形成する。第3の膜125は、膜厚が2nm程度のLa2O3膜とすればよい。第3の膜125は、La2O3に限らず、高誘電体膜121へ拡散させた場合に、トランジスタの実効関数を低くする金属を含む材料により形成すればよい。第3の膜は、PVD法により形成すればよい。

【0032】

次に、図7に示すように、半導体基板101に対して例えば650℃で10分間の熱処理を行う。これにより、N−MISFET形成領域101Nにおいては第3の膜に含まれるLaが高誘電体膜へ拡散し、Laを含む高誘電体膜121aが形成される。一方、P−MISFET形成領域101Pにおいては、第1の膜に含まれるAlが高誘電体膜へ拡散し、Alを含む高誘電体膜121bが形成される。図7においては、第1の膜122が完全に拡散して消滅した状態を示しているが、熱処理条件によっては未反応の第1の膜122が残存することもある。また、第3の膜に含まれるLaが犠牲導電膜123へ拡散し、Laを含む犠牲導電膜123aのLa濃度が上昇する。なお、熱処理は600℃〜700℃の温度で5分〜10分程度行えばよい。

【0033】

次に、図8に示すように、未拡散の第3の膜と、Laが拡散した犠牲導電膜123a及び犠牲導電膜123とをそれぞれ第4の薬液及び第5の薬液を用いたウェットエッチングにより除去する。第4の薬液は、pHを2〜4程度に調整した酸化剤を含まない酸性溶液とすればよい。例えば、36質量%の塩酸と水とを1対2000の体積比率で混合した塩酸水溶液とすればよい。第5の薬液は、pHを2〜4程度に調整した酸化剤を含む酸性溶液とすればよい。例えば、36質量%の塩酸と31質量%の過酸化水素水とを1対2000の堆積比率で混合した溶液を用いればよい。酸化剤である過酸化水素の濃度は、1質量%以上であることが好ましい。

【0034】

次に、図9に示すように、半導体基板101上の全面に、膜厚が15nmのTiN膜128と膜厚が90nmのシリコン膜129とをALD法等により形成する。シリコン膜129は、ポリシリコン膜であってもアモルファスシリコン膜であってもよい。

【0035】

次に、レジストパターンを用いたドライエッチングにより、シリコン膜129、TiN膜128、Laを含む高誘電体膜121a、Alを含む高誘電体膜121b及び下地膜(図示せず)をパターニングする。これにより、図10に示すように、N−MISFET形成領域101Nに、TiN膜128及びシリコン膜129が積層された第1のゲート電極130aと、Laを含む高誘電体膜121aと下地膜(図示せず)とを有する第1のゲート絶縁膜が形成される。P−MISFET形成領域101Pに、TiN膜128及びシリコン膜129が積層された第2のゲート電極130bと、Alを含む高誘電体膜121bと下地膜(図示せず)とを有する第2のゲート絶縁膜が形成される。

【0036】

次に、第1のゲート電極130aの側面に上第1のオフセットスペーサ131aを形成し、第2のゲート電極130bの側面上に第2のオフセットスペーサ131bを形成する。第1のゲート電極130a及び第1のオフセットスペーサ131aをマスクとして第1の活性領域101aに不純物を注入しn型エクステンション領域141aを形成する。また、第2のゲート電極130b及び第2のオフセットスペーサ131bをマスクとして第2の活性領域101bに不純物を注入しp型エクステンション領域141bを形成する。その後、第1のオフセットスペーサ131aの側面上及び第2のオフセットスペーサ131bの側面上に、それぞれ第1のサイドウォール133a及び第2のサイドウォール133bを形成する。第1のサイドウォール133aはL字状の第1の内側サイドウォール134a及び第1の外側サイドウォール135aを有し、第2のサイドウォール133bはL字状の第2の内側サイドウォール134b及び第2の外側サイドウォール135bを有する。続いて、第1のゲート電極130a、第1のオフセットスペーサ131a及び第1のサイドウォール133aをマスクとして第1の活性領域101aに不純物を注入し、n型ソースドレイン領域142aを形成する。また、第2のゲート電極130b、第2のオフセットスペーサ131b及び第2のサイドウォール133bをマスクとして第2の活性領域101bに不純物を注入し、p型ソースドレイン領域142bを形成する。続いて、第1のゲート電極130a、第2のゲート電極130b、n型ソースドレイン領域142a及びp型ソースドレイン領域142bの上部に、それぞれニッケルシリサイド等からなるシリサイド層138を形成する。これにより、図11に示すように、N−MISFETとP−MISFETとを有する半導体装置が得られる。

【0037】

本実施形態に係る半導体装置の製造方法は、PMISFET形成領域を覆うマスクとして犠牲導電膜123を用いている。このため、第3の膜を形成する際にレジスト膜が存在せず、レジスト膜によるパーティクルの発生及び異常成長は生じない。また、PMISFET形成領域において犠牲導電膜123の上部にLaが拡散した犠牲導電膜123aを形成しており、N−MISFET形成領域において非常に選択性良く犠牲導電膜123を除去することができる。このため、N−MISFET形成領域において高誘電体膜がエッチングされるおそれがほとんどない。従って、N−MISFET形成領域及びPMISFET形成領域のそれぞれに、最適な特性を有するゲート絶縁膜を再現性良く形成することが可能となる。

【0038】

図7において、高誘電体膜121中にLaが均一に拡散してLaを含む高誘電体膜121aが形成される例を示した。しかし、熱処理条件によっては、高誘電体膜121a中においてLa濃度が均一とならず、上部において下部よりもLa濃度が高い状態が生じたり、下部において上部よりもLa濃度が高い状態が生じたりする。また、La濃度が異なる複数の層が形成される場合もある。また、図7では、熱処理後に第3の膜125が残存している例を示したが、第3の膜125の膜厚及び熱処理条件等によっては、熱処理後に第3の膜125が消失する場合も生じる。

【0039】

同様に、Alを含む高誘電体膜121b中においてAl濃度が均一とならず、上部において下部よりもAl濃度が高い状態が生じたり、下部において上部よりもAl濃度が高い状態が生じたり、Al濃度が異なる複数の層が形成されたりする。また、図7では、熱処理後に第1の膜122が消失する例を示したが、第1の膜122の膜厚及び熱処理条件等によっては、高誘電体膜121bと犠牲導電膜123との間に第1の膜122が残存する場合も生じる。第1の膜122が残存する場合には、犠牲導電膜123を除去する際に第1の膜122の残存する部分も除去すればよい。また、第1の膜122の残存する部分を除去しなくてもよい。この場合、エクステンション領域、ソースドレイン領域及びシリサイド層の形成工程等において行う熱処理によって、第1の膜122の残存する部分は高誘電体膜121中に拡散する。さらに、N−MISFET形成領域101Nにおいて未拡散の第3の膜125は、完全に除去できなくてもよい。この場合にも、後の熱処理工程により第3の膜125の残存する部分は高誘電体膜121中に拡散する。但し、高誘電体膜121中へLaの拡散を正確に制御するという観点からは、第3の膜125の除去を十分に行うことが好ましい。

【0040】

本実施形態は、高誘電体膜121と半導体基板101との間に下地膜(図示せず)を形成する例を示したが、下地膜は形成しなくてもよい。また、第1のゲート絶縁膜121a及び第2のゲート絶縁膜121bの少なくとも一方と半導体基板101との間に下地膜が存在する構成としてもよい。

【0041】

第3の膜125は、La2O3に代えて、La以外のランタノイド、スカンジウム(Sc)、ストロンチウム(Sr)又はマグネシウム(Mg)等を含む膜としてもよい。第3の膜125は酸化膜に限らず、これらの金属元素を含む膜であればよい。また、化合物となっていない金属膜であってもよい。同様に第1の膜122は、Al2O3に代えて、Ta2O3としてもよい。また、酸化膜に限らずAl又はTaを含む膜であればよく、Al膜又はTa膜であってもよい。第1の膜122及び第3の膜125はそれ自身が絶縁膜である必要はなく、第1の膜122及び第3の膜125に含まれる金属元素が拡散した高誘電体膜が絶縁性を示せばよい。

【0042】

なお、メタルゲートの形成について説明したが、犠牲導電膜と第2の膜とを組み合わせてハードマスクを選択的にウェットエッチングする方法は、低誘電率膜を層間絶縁膜とするCu配線の形成工程、非シリサイド形成工程及び注入レジスト代替マスクの形成工程等に用いることができる。

【産業上の利用可能性】

【0043】

本発明に係る半導体装置の製造方法は、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現でき、特に高誘電体材料を含むゲート絶縁膜及び金属膜を含むゲート電極を備えた半導体装置の製造方法等として有用である。

【符号の説明】

【0044】

101 半導体基板

101N N−MISFET形成領域

101P P−MISFET形成領域

101a 第1の活性領域

101b 第2の活性領域

102a p型ウェル

102b n型ウェル

111 素子分離領域

121 高誘電体膜

121a 第1のゲート絶縁膜

121b 第2のゲート絶縁膜

122 第1の膜

123 犠牲導電膜

123a 犠牲導電膜

124 第2の膜

125 第3の膜

128 TiN膜

129 シリコン膜

130a 第1のゲート電極

130b 第2のゲート電極

131a 上第1のオフセットスペーサ

131a 第1のオフセットスペーサ

131b 第2のオフセットスペーサ

133a 第1のサイドウォール

133b 第2のサイドウォール

134a 第1の内側サイドウォール

134b 第2の内側サイドウォール

135a 第1の外側サイドウォール

135b 第2の外側サイドウォール

138 シリサイド層

141a n型エクステンション領域

141b p型エクステンション領域

142a n型ソースドレイン領域

142b p型ソースドレイン領域

151 レジストパターン

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に高誘電体材料を含むゲート絶縁膜及び金属膜を含むゲート電極を備えた半導体装置の製造方法に関する。

【背景技術】

【0002】

CMOS(Complementary metal-oxide semiconductor)デバイスは、さらなる微細化が要求されている。CMOSデバイスをさらに微細化するためには、ゲート絶縁膜のさらなる薄膜化が必要となる。しかし、従来のシリコン酸化膜からなるゲート絶縁膜をさらに薄くすると、リーク電流の増大を誘発し、LSI(Large scale integration)回路の待機時電流が増大するおそれがある。このため、シリコン酸化膜からなるゲート絶縁膜の薄膜化は、限界を迎えている。そこで、シリコン酸化膜に代えて高誘電体材料からなる絶縁膜をゲート絶縁膜とする、CMIS(Complementary metal-insulator semiconductor)デバイスが注目されている。高誘電体材料からなる絶縁膜は、物理的な膜厚を厚くしても電気的な膜厚を薄くすることが可能であるため、ゲート絶縁膜の薄膜化をさらに進めることができると期待されている。現在、ゲート絶縁膜用の高誘電体材料として最も有望視されているのは、窒化ハフニウムシリケート(HfSiON)である。また、ゲート電極についても、従来のポリシリコンからなる電極ではその空乏化が無視できなくなってきており、空乏化が生じないメタルゲート電極の開発が盛んに行われている。

【0003】

一方、CMISデバイスを形成する場合には、n型のN−MISFET(N−metal-insulator semiconductor field effect transistor)とp型のP−MISFET(P−metal-insulator semiconductor field effect transistor)とが必要である。しかし、N−MISFETとP−MISFETとでは、ゲート絶縁膜及びゲート電極に求められる特性が互いに異なっている。具体的には、N−MISFETでは実効仕事関数を低くすることが好ましく、P−MISFETでは実効仕事関数を高くすることが好ましい。このため、実効仕事関数が低いN−MISFET用のゲート絶縁膜及びゲート電極と、実効仕事関数が高いP−MISFET用のゲート絶縁膜及びゲート電極とを作り別けるプロセスが提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−267342号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、前記従来のN−MISFETとP−MISFETとを作り別ける方法は、以下のような問題を有している。N−MISFETとP−MISFETとを作り別けるためには、N−MISFETを形成する領域又はP−MISFETを形成する領域の一方だけにキャップ膜を選択的に形成する必要がある。キャップ膜を選択的に形成する方法として、レジスト膜をマスクとして一方の領域に選択的にキャップ膜を形成する方法が知られている。

【0006】

しかし、レジスト膜をマスクとしてキャップ膜を選択的に形成する場合には、キャップ膜を成膜する際にレジスト膜が飛散して、パーティクルが発生したり、異常成長を引き起こしたりする原因となる。また、レジスト膜の上に形成されたキャップ膜がレジスト膜を除去する際に飛散し、レジスト膜の下側の層にキャップ膜が再付着するおそれがある。このため、半導体装置の特性が安定しないという問題がある。

【0007】

キャップ膜を形成した後、一方の領域を覆うレジスト膜を形成し、レジスト膜をマスクとしてドライエッチングを行うことにより、不要なキャップ膜を除去する方法も知られている。しかし、ドライエッチングによりキャップ膜の不要な部分を除去する方法の場合には、キャップ膜の下側の層もエッチングされてしまうおそれがある。また、ドライエッチング後の、残渣洗浄工程において、必要とするキャップ膜が薄くなるおそれがある。

【0008】

このように、従来のN−MISFETとP−MISFETとを作り別ける方法には種々の問題があり、半導体装置の特性を安定させることができず、信頼性が高い半導体装置を実現することが困難であるということを本願発明者らは見出した。

【0009】

本発明は、前記の問題を解決し、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するため、本発明は半導体装置の製造方法を、犠牲導電膜をハードマスクとして、キャップ膜を選択的に形成する構成とする。

【0011】

具体的に、本発明に係る半導体装置の製造方法は、半導体基板に、第1の素子形成領域及び第2の素子形成領域を形成する工程(a)と、半導体基板上の全面に高誘電体膜と、第1の金属元素を含む第1の膜と、犠牲導電膜と、第2の金属元素を含む第2の膜とを順次形成する工程(b)と、第2の膜における第1の素子形成領域の上に形成された部分を第1の薬液を用いて選択的に除去する工程(c)と、工程(c)よりも後で、第2の金属元素を犠牲導電膜における第2の素子形成領域の上に形成された部分に拡散させる工程(d)と、工程(d)よりも後で、犠牲導電膜及び第1の膜における第1の素子形成領域の上に形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去し、第1の素子形成領域において高誘電体膜を露出させる工程(e)と、工程(e)よりも後で、半導体基板上の全面に第3の金属元素を有する第3の膜を形成する工程(f)と、工程(f)よりも後で、第3の金属元素を高誘電体膜中に拡散させる工程(g)と、第3の膜及び犠牲導電膜の残存部分をそれぞれ第4の薬液及び第5の薬液を用いて除去する工程(h)と、(h)よりも後で、半導体基板上の全面に電極膜を形成する工程(i)と、電極膜及び高誘電体膜を選択的に除去することにより、第1の素子形成領域に、第3の金属元素を含む第1のゲート絶縁膜と、電極膜からなる第1のゲート電極とを形成し、第2の素子形成領域に、第1の金属元素を含む第2のゲート絶縁膜と、電極膜からなる第2のゲート電極とを形成する工程(j)とを備えている。

【0012】

本発明の半導体装置の製造方法は、犠牲導電膜からなるハードマスクを用いて、N−MISFET用のキャップ膜である第3の膜を選択的に形成する。このため、第3の膜を成膜する際にレジスト膜が飛散してパーティクルとなったり、異常成長の原因となったりすることがない。また、P−MISFET用のキャップ膜である第1の膜を、ウェットエッチングにより除去している。このため、N−MISFET領域において第1の膜を除去する際に、高誘電体膜はほとんどエッチングされない。従って、信頼性が高い半導体装置を容易に製造することが可能となる。

【0013】

本発明の半導体装置の製造方法において、犠牲導電膜は、窒化チタン、タングステン又は窒化タングステンとし、第2の膜は、酸化ランタンとすればよい。

【0014】

本発明の半導体装置の製造方法において、工程(e)では、第2の薬液としてpHを6以上且つ8以下に調整した、酸化剤を含む中性溶液を用いればよい。

【0015】

本発明の半導体装置の製造方において、酸化剤を含む中性溶液は、5質量%以上且つ30質量%以下の濃度の過酸化水素水とすればよい。

【0016】

本発明の半導体装置の製造方法において、工程(e)では、第3の薬液としてpHを1以下に調整した、酸化剤を含まない酸性溶液を用いればよい。

【0017】

本発明の半導体装置の製造方法において、工程(h)では、第4の薬液としてpHを2以上且つ4以下に調整した、酸化剤を含まない酸性溶液を用い、第5の薬液としてpHを2以上且つ4以下に調整した酸化剤を含む酸性溶液を用いればよい。

【0018】

本発明の半導体装置の製造方法は、工程(d)よりも後で且つ工程(e)よりも前に、第2の膜の犠牲導電膜の上に残存した部分を、pHを1以下に調整した、酸化剤を含まない酸性溶液を用いて除去する工程(k)をさらに備えていてもよい。

【0019】

本発明の半導体装置の製造方法において、工程(c)では、第1の薬液としてpHを4.0以上且つ4.9以下に調整した酸化剤を含まない酸性溶液を用いればよい。

【0020】

本発明の半導体装置の製造方法において、高誘電体膜は、比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物とすればよい。

【0021】

本発明の半導体装置の製造方法において、第2の金属元素は、アルミニウム又はタンタルとすればよい。

【0022】

本発明の半導体装置の製造方法において、第3の金属元素は、ランタン若しくはランタン以外のランタノイド、スカンジウム、ストロンチウム又はマグネシウムとすればよい。

【0023】

本発明の半導体装置の製造方法において、電極膜は、窒化チタン膜とシリコン膜との積層膜とすればよい。

【発明の効果】

【0024】

本発明に係る半導体装置の製造方法によれば、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できる。

【図面の簡単な説明】

【0025】

【図1】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図2】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図3】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図4】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図5】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図6】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図7】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図8】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図9】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図10】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【図11】一実施形態に係る半導体装置の製造方法の一工程を示す断面図である。

【発明を実施するための形態】

【0026】

図1〜図11は、一実施形態に係る半導体装置の製造方法を工程順に示している。まず、図1に示すように、p型のシリコン基板である半導体基板101に、N−MISFET形成領域101N及びP−MISFET形成領域101Pを形成する。具体的には、まず、素子分離領域111により互いに分離された第1の活性領域101a及び第2の活性領域101bを半導体基板101に形成する。続いて、第1の活性領域101aにp型ウェル102aを形成し、第2の活性領域101bにn型ウェル102bを形成する。素子分離領域111は、半導体基板101に形成されたトレンチに絶縁膜を埋め込む、STI(Shallow Trench Isolation)法により形成すればよい。

【0027】

次に、図2に示すように、下地膜(図示せず)、高誘電体膜121、第1の膜122、犠牲導電膜123及び第2の膜124を半導体基板101上の全面に順次形成する。下地膜は、膜厚が1.1nm程度のシリコン酸化膜(SiO2)膜とすればよい。高誘電体膜121は、膜厚が1.7nm程度の窒素含有ハフニウムシリケート(HfSiON)膜とすればよい。高誘電体膜121は、原子層堆積(Atomic Layer Deposition:ALD)法により形成すればよい。高誘電体膜121は、HfSiON膜に代えて酸化ハフニウム(HfO2)膜又はハフニウムシリケート(HfSiOx)膜等としてもよい。また、この他にも比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物等の高誘電体材料により形成すればよい。第1の膜122は、膜厚が0.5nm程度の酸化アルミニウム(Al2O3)膜とすればよい。第1の膜122は、Al2O2膜に限らず、高誘電体膜121へ拡散させた場合にトランジスタの実効仕事関数を高くする第1の金属を含む材料により形成すればよい。犠牲導電膜123は、膜厚が10nm程度の窒化チタン(TiN)膜とすればよい。犠牲導電膜123は、ALD法により形成すればよい。犠牲導電膜123は、TiN膜に限らず、タングステン(W)膜又は窒化タングステン(WN)膜等であってもよい。第2の膜124は、例えば膜厚が5nmの酸化ランタン(La2O3)膜とすればよい。第2の膜124は、物理気相成長(PVD)法により形成すればよい。第2の膜124は、犠牲導電膜123へ拡散させた場合に、犠牲導電膜123のエッチング特性を変化させることができる第2の金属を含む材料により形成すればよい。

【0028】

次に、図3に示すように、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を選択的に除去する。具体的には、まず犠牲導電膜123の上に、N−MISFET形成領域101Nを露出し、P−MISFET形成領域101Pを覆うレジストパターン151をフォトリソグラフィ法により形成する。続いて、レジストパターン151をマスクとして、第1の薬液を用いたウェットエッチングにより、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を除去する。第1の薬液はpHをpH4.0〜4.9程度に調整した酸化剤を含まない弱酸性薬液とすればよい。例えば、36質量%の塩酸と水とを1対500000の体積比率で混合した塩酸水溶液を用いればよい。この場合pHは4.6程度となる。

【0029】

次に、図4に示すように、シンナー及び水酸化テトラメチルアンモニウム(TMAH)からなる現像液を用いてレジストパターン151を除去した後、第2の膜124に含まれるLaを犠牲導電膜123の上部に拡散させる。これにより、犠牲導電膜123におけるP−MISFET形成領域101Pに形成された部分の上部にLaを含む犠牲導電膜123aが形成される。その後、未拡散の第2の膜124を除去する。Laの拡散は熱処理により行えばよく、熱処理温度は600℃程度とし、処理時間は10分程度とすればよい。なお、熱処理温度は、500℃〜700℃程度であればよく、処理時間は5分〜10分程度であればよい。なお、熱処理の条件によっては第1の膜122に含まれるAlが高誘電体膜121の上部に拡散するが問題ない。未拡散の第2の膜124の除去は、ウェットエッチングにより行えばよい。エッチング溶液は、pHを1以下に調整した酸化剤を含まない強酸性薬液とすればよい。例えば、36質量%の塩酸と水とを1対50の体積比で混合した塩酸水溶液とすればよい。第2の膜124の膜厚及び熱処理条件等によっては、第2の膜124が全て拡散し、残存しない場合もある。この場合には未拡散の第2の膜124の除去を行わなくてもよい。

【0030】

次に、図5に示すように、犠牲導電膜123及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分をそれぞれ第2の薬液及び第3の薬液を用いたウェットエッチングにより除去する。第2の薬液は、pHを6〜8程度に調整した酸化剤を含む中性溶液とすればよい。例えば、5質量%〜30質量%の濃度の過酸化水素水を用いればよい。Laを含む犠牲導電膜123aは、pHを6〜8に調整した酸化剤を含む中性溶液に耐性を有する。このため、Laを含む犠牲導電膜123aがハードマスクとなり、犠牲導電膜123におけるN−MISFET形成領域101Nに形成された部分を選択的に除去することができる。第3の薬液は、pHを1以下に調整した酸化剤を含まない強酸性溶液とすればよい。例えば、36質量%の塩酸と水とを1対50の体積比で混合した塩酸水溶液を用いればよい。pHを1以下に調整した酸化剤を含まない強酸性溶液を用いたウェットエッチングの場合、HfSiONのエッチングレートに対するAl2O3のエッチングレートの比は10000以上となる。このため、高誘電体膜121をエッチングすることなく、第1の膜122を選択的に除去することが容易にできる。なお、高誘電体膜121の上部にAlが拡散している場合には、拡散したAlも問題にならない程度まで除去される。

【0031】

次に、図6に示すように、半導体基板101上の全面に第3の膜125を形成する。第3の膜125は、膜厚が2nm程度のLa2O3膜とすればよい。第3の膜125は、La2O3に限らず、高誘電体膜121へ拡散させた場合に、トランジスタの実効関数を低くする金属を含む材料により形成すればよい。第3の膜は、PVD法により形成すればよい。

【0032】

次に、図7に示すように、半導体基板101に対して例えば650℃で10分間の熱処理を行う。これにより、N−MISFET形成領域101Nにおいては第3の膜に含まれるLaが高誘電体膜へ拡散し、Laを含む高誘電体膜121aが形成される。一方、P−MISFET形成領域101Pにおいては、第1の膜に含まれるAlが高誘電体膜へ拡散し、Alを含む高誘電体膜121bが形成される。図7においては、第1の膜122が完全に拡散して消滅した状態を示しているが、熱処理条件によっては未反応の第1の膜122が残存することもある。また、第3の膜に含まれるLaが犠牲導電膜123へ拡散し、Laを含む犠牲導電膜123aのLa濃度が上昇する。なお、熱処理は600℃〜700℃の温度で5分〜10分程度行えばよい。

【0033】

次に、図8に示すように、未拡散の第3の膜と、Laが拡散した犠牲導電膜123a及び犠牲導電膜123とをそれぞれ第4の薬液及び第5の薬液を用いたウェットエッチングにより除去する。第4の薬液は、pHを2〜4程度に調整した酸化剤を含まない酸性溶液とすればよい。例えば、36質量%の塩酸と水とを1対2000の体積比率で混合した塩酸水溶液とすればよい。第5の薬液は、pHを2〜4程度に調整した酸化剤を含む酸性溶液とすればよい。例えば、36質量%の塩酸と31質量%の過酸化水素水とを1対2000の堆積比率で混合した溶液を用いればよい。酸化剤である過酸化水素の濃度は、1質量%以上であることが好ましい。

【0034】

次に、図9に示すように、半導体基板101上の全面に、膜厚が15nmのTiN膜128と膜厚が90nmのシリコン膜129とをALD法等により形成する。シリコン膜129は、ポリシリコン膜であってもアモルファスシリコン膜であってもよい。

【0035】

次に、レジストパターンを用いたドライエッチングにより、シリコン膜129、TiN膜128、Laを含む高誘電体膜121a、Alを含む高誘電体膜121b及び下地膜(図示せず)をパターニングする。これにより、図10に示すように、N−MISFET形成領域101Nに、TiN膜128及びシリコン膜129が積層された第1のゲート電極130aと、Laを含む高誘電体膜121aと下地膜(図示せず)とを有する第1のゲート絶縁膜が形成される。P−MISFET形成領域101Pに、TiN膜128及びシリコン膜129が積層された第2のゲート電極130bと、Alを含む高誘電体膜121bと下地膜(図示せず)とを有する第2のゲート絶縁膜が形成される。

【0036】

次に、第1のゲート電極130aの側面に上第1のオフセットスペーサ131aを形成し、第2のゲート電極130bの側面上に第2のオフセットスペーサ131bを形成する。第1のゲート電極130a及び第1のオフセットスペーサ131aをマスクとして第1の活性領域101aに不純物を注入しn型エクステンション領域141aを形成する。また、第2のゲート電極130b及び第2のオフセットスペーサ131bをマスクとして第2の活性領域101bに不純物を注入しp型エクステンション領域141bを形成する。その後、第1のオフセットスペーサ131aの側面上及び第2のオフセットスペーサ131bの側面上に、それぞれ第1のサイドウォール133a及び第2のサイドウォール133bを形成する。第1のサイドウォール133aはL字状の第1の内側サイドウォール134a及び第1の外側サイドウォール135aを有し、第2のサイドウォール133bはL字状の第2の内側サイドウォール134b及び第2の外側サイドウォール135bを有する。続いて、第1のゲート電極130a、第1のオフセットスペーサ131a及び第1のサイドウォール133aをマスクとして第1の活性領域101aに不純物を注入し、n型ソースドレイン領域142aを形成する。また、第2のゲート電極130b、第2のオフセットスペーサ131b及び第2のサイドウォール133bをマスクとして第2の活性領域101bに不純物を注入し、p型ソースドレイン領域142bを形成する。続いて、第1のゲート電極130a、第2のゲート電極130b、n型ソースドレイン領域142a及びp型ソースドレイン領域142bの上部に、それぞれニッケルシリサイド等からなるシリサイド層138を形成する。これにより、図11に示すように、N−MISFETとP−MISFETとを有する半導体装置が得られる。

【0037】

本実施形態に係る半導体装置の製造方法は、PMISFET形成領域を覆うマスクとして犠牲導電膜123を用いている。このため、第3の膜を形成する際にレジスト膜が存在せず、レジスト膜によるパーティクルの発生及び異常成長は生じない。また、PMISFET形成領域において犠牲導電膜123の上部にLaが拡散した犠牲導電膜123aを形成しており、N−MISFET形成領域において非常に選択性良く犠牲導電膜123を除去することができる。このため、N−MISFET形成領域において高誘電体膜がエッチングされるおそれがほとんどない。従って、N−MISFET形成領域及びPMISFET形成領域のそれぞれに、最適な特性を有するゲート絶縁膜を再現性良く形成することが可能となる。

【0038】

図7において、高誘電体膜121中にLaが均一に拡散してLaを含む高誘電体膜121aが形成される例を示した。しかし、熱処理条件によっては、高誘電体膜121a中においてLa濃度が均一とならず、上部において下部よりもLa濃度が高い状態が生じたり、下部において上部よりもLa濃度が高い状態が生じたりする。また、La濃度が異なる複数の層が形成される場合もある。また、図7では、熱処理後に第3の膜125が残存している例を示したが、第3の膜125の膜厚及び熱処理条件等によっては、熱処理後に第3の膜125が消失する場合も生じる。

【0039】

同様に、Alを含む高誘電体膜121b中においてAl濃度が均一とならず、上部において下部よりもAl濃度が高い状態が生じたり、下部において上部よりもAl濃度が高い状態が生じたり、Al濃度が異なる複数の層が形成されたりする。また、図7では、熱処理後に第1の膜122が消失する例を示したが、第1の膜122の膜厚及び熱処理条件等によっては、高誘電体膜121bと犠牲導電膜123との間に第1の膜122が残存する場合も生じる。第1の膜122が残存する場合には、犠牲導電膜123を除去する際に第1の膜122の残存する部分も除去すればよい。また、第1の膜122の残存する部分を除去しなくてもよい。この場合、エクステンション領域、ソースドレイン領域及びシリサイド層の形成工程等において行う熱処理によって、第1の膜122の残存する部分は高誘電体膜121中に拡散する。さらに、N−MISFET形成領域101Nにおいて未拡散の第3の膜125は、完全に除去できなくてもよい。この場合にも、後の熱処理工程により第3の膜125の残存する部分は高誘電体膜121中に拡散する。但し、高誘電体膜121中へLaの拡散を正確に制御するという観点からは、第3の膜125の除去を十分に行うことが好ましい。

【0040】

本実施形態は、高誘電体膜121と半導体基板101との間に下地膜(図示せず)を形成する例を示したが、下地膜は形成しなくてもよい。また、第1のゲート絶縁膜121a及び第2のゲート絶縁膜121bの少なくとも一方と半導体基板101との間に下地膜が存在する構成としてもよい。

【0041】

第3の膜125は、La2O3に代えて、La以外のランタノイド、スカンジウム(Sc)、ストロンチウム(Sr)又はマグネシウム(Mg)等を含む膜としてもよい。第3の膜125は酸化膜に限らず、これらの金属元素を含む膜であればよい。また、化合物となっていない金属膜であってもよい。同様に第1の膜122は、Al2O3に代えて、Ta2O3としてもよい。また、酸化膜に限らずAl又はTaを含む膜であればよく、Al膜又はTa膜であってもよい。第1の膜122及び第3の膜125はそれ自身が絶縁膜である必要はなく、第1の膜122及び第3の膜125に含まれる金属元素が拡散した高誘電体膜が絶縁性を示せばよい。

【0042】

なお、メタルゲートの形成について説明したが、犠牲導電膜と第2の膜とを組み合わせてハードマスクを選択的にウェットエッチングする方法は、低誘電率膜を層間絶縁膜とするCu配線の形成工程、非シリサイド形成工程及び注入レジスト代替マスクの形成工程等に用いることができる。

【産業上の利用可能性】

【0043】

本発明に係る半導体装置の製造方法は、所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現でき、特に高誘電体材料を含むゲート絶縁膜及び金属膜を含むゲート電極を備えた半導体装置の製造方法等として有用である。

【符号の説明】

【0044】

101 半導体基板

101N N−MISFET形成領域

101P P−MISFET形成領域

101a 第1の活性領域

101b 第2の活性領域

102a p型ウェル

102b n型ウェル

111 素子分離領域

121 高誘電体膜

121a 第1のゲート絶縁膜

121b 第2のゲート絶縁膜

122 第1の膜

123 犠牲導電膜

123a 犠牲導電膜

124 第2の膜

125 第3の膜

128 TiN膜

129 シリコン膜

130a 第1のゲート電極

130b 第2のゲート電極

131a 上第1のオフセットスペーサ

131a 第1のオフセットスペーサ

131b 第2のオフセットスペーサ

133a 第1のサイドウォール

133b 第2のサイドウォール

134a 第1の内側サイドウォール

134b 第2の内側サイドウォール

135a 第1の外側サイドウォール

135b 第2の外側サイドウォール

138 シリサイド層

141a n型エクステンション領域

141b p型エクステンション領域

142a n型ソースドレイン領域

142b p型ソースドレイン領域

151 レジストパターン

【特許請求の範囲】

【請求項1】

半導体基板に、第1の素子形成領域及び第2の素子形成領域を形成する工程(a)と、

半導体基板上の全面に高誘電体膜と、第1の金属元素を含む第1の膜と、犠牲導電膜と、第2の金属元素を含む第2の膜とを順次形成する工程(b)と、

前記第2の膜における前記第1の素子形成領域の上に形成された部分を第1の薬液を用いて選択的に除去する工程(c)と、

前記工程(c)よりも後で、前記第2の金属元素を前記犠牲導電膜における前記第2の素子形成領域の上に形成された部分に拡散させる工程(d)と、

前記工程(d)よりも後で、前記犠牲導電膜及び第1の膜における前記第1の素子形成領域の上に形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去し、前記第1の素子形成領域において前記高誘電体膜を露出させる工程(e)と、

前記工程(e)よりも後で、前記半導体基板上の全面に第3の金属元素を有する第3の膜を形成する工程(f)と、

前記工程(f)よりも後で、前記第3の金属元素を前記高誘電体膜中に拡散させる工程(g)と、

前記第3の膜及び前記犠牲導電膜の残存部分をそれぞれ第4の薬液及び第5の薬液を用いて除去する工程(h)と、

前記(h)よりも後で、前記半導体基板上の全面に電極膜を形成する工程(i)と、

前記電極膜及び前記高誘電体膜を選択的に除去することにより、前記第1の素子形成領域に、前記第3の金属元素を含む第1のゲート絶縁膜と、前記電極膜からなる第1のゲート電極とを形成し、前記第2の素子形成領域に、前記第1の金属元素を含む第2のゲート絶縁膜と、前記電極膜からなる第2のゲート電極とを形成する工程(j)とを備えていることを特徴とする半導体装置の製造方法。

【請求項2】

前記犠牲導電膜は、窒化チタン、タングステン又は窒化タングステンからなり、

前記第2の膜は、酸化ランタンからなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記工程(e)では、前記第2の薬液としてpHを6以上且つ8以下に調整した、酸化剤を含む中性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記酸化剤を含む中性溶液は、5質量%以上且つ30質量%以下の濃度の過酸化水素水であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記工程(e)では、前記第3の薬液としてpHを1以下に調整した、酸化剤を含まない酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

前記工程(h)では、

前記第4の薬液としてpHを2以上且つ4以下に調整した、酸化剤を含まない酸性溶液を用い、

前記第5の薬液としてpHを2以上且つ4以下に調整した酸化剤を含む酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項7】

前記工程(d)よりも後で且つ前記工程(e)よりも前に、前記第2の膜における前記犠牲導電膜の上に残存した部分を、pHを1以下に調整した、酸化剤を含まない酸性溶液を用いて除去する工程(k)をさらに備えていることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項8】

前記工程(c)では、前記第1の薬液としてpHを4.0以上且つ4.9以下に調整した酸化剤を含まない酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項9】

前記高誘電体膜は、比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物からなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項10】

前記第2の金属元素は、アルミニウム又はタンタルであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項11】

前記第3の金属元素は、ランタン若しくはランタン以外のランタノイド、スカンジウム、ストロンチウム又はマグネシウムであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項12】

前記電極膜は、窒化チタン膜とシリコン膜との積層膜であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項1】

半導体基板に、第1の素子形成領域及び第2の素子形成領域を形成する工程(a)と、

半導体基板上の全面に高誘電体膜と、第1の金属元素を含む第1の膜と、犠牲導電膜と、第2の金属元素を含む第2の膜とを順次形成する工程(b)と、

前記第2の膜における前記第1の素子形成領域の上に形成された部分を第1の薬液を用いて選択的に除去する工程(c)と、

前記工程(c)よりも後で、前記第2の金属元素を前記犠牲導電膜における前記第2の素子形成領域の上に形成された部分に拡散させる工程(d)と、

前記工程(d)よりも後で、前記犠牲導電膜及び第1の膜における前記第1の素子形成領域の上に形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去し、前記第1の素子形成領域において前記高誘電体膜を露出させる工程(e)と、

前記工程(e)よりも後で、前記半導体基板上の全面に第3の金属元素を有する第3の膜を形成する工程(f)と、

前記工程(f)よりも後で、前記第3の金属元素を前記高誘電体膜中に拡散させる工程(g)と、

前記第3の膜及び前記犠牲導電膜の残存部分をそれぞれ第4の薬液及び第5の薬液を用いて除去する工程(h)と、

前記(h)よりも後で、前記半導体基板上の全面に電極膜を形成する工程(i)と、

前記電極膜及び前記高誘電体膜を選択的に除去することにより、前記第1の素子形成領域に、前記第3の金属元素を含む第1のゲート絶縁膜と、前記電極膜からなる第1のゲート電極とを形成し、前記第2の素子形成領域に、前記第1の金属元素を含む第2のゲート絶縁膜と、前記電極膜からなる第2のゲート電極とを形成する工程(j)とを備えていることを特徴とする半導体装置の製造方法。

【請求項2】

前記犠牲導電膜は、窒化チタン、タングステン又は窒化タングステンからなり、

前記第2の膜は、酸化ランタンからなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記工程(e)では、前記第2の薬液としてpHを6以上且つ8以下に調整した、酸化剤を含む中性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記酸化剤を含む中性溶液は、5質量%以上且つ30質量%以下の濃度の過酸化水素水であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記工程(e)では、前記第3の薬液としてpHを1以下に調整した、酸化剤を含まない酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

前記工程(h)では、

前記第4の薬液としてpHを2以上且つ4以下に調整した、酸化剤を含まない酸性溶液を用い、

前記第5の薬液としてpHを2以上且つ4以下に調整した酸化剤を含む酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項7】

前記工程(d)よりも後で且つ前記工程(e)よりも前に、前記第2の膜における前記犠牲導電膜の上に残存した部分を、pHを1以下に調整した、酸化剤を含まない酸性溶液を用いて除去する工程(k)をさらに備えていることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項8】

前記工程(c)では、前記第1の薬液としてpHを4.0以上且つ4.9以下に調整した酸化剤を含まない酸性溶液を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項9】

前記高誘電体膜は、比誘電率が8以上の金属酸化物、金属酸窒化物、硅化物又は窒素含有硅化物からなることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項10】

前記第2の金属元素は、アルミニウム又はタンタルであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項11】

前記第3の金属元素は、ランタン若しくはランタン以外のランタノイド、スカンジウム、ストロンチウム又はマグネシウムであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項12】

前記電極膜は、窒化チタン膜とシリコン膜との積層膜であることを特徴とする請求項1に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−84637(P2013−84637A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2010−36978(P2010−36978)

【出願日】平成22年2月23日(2010.2.23)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成22年2月23日(2010.2.23)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]