半導体装置の製造方法

【課題】ゲート電極の不純物濃度を好適に制御する半導体装置の製造方法を提供する。

【解決手段】第2トランジスタ170のゲート電極171を半導体基板1に対するマスクとして半導体基板1へイオン注入を行うことにより、第2トランジスタのドレイン175を形成するとともに、第2トランジスタ170のゲート電極171へイオン注入を行う。

【解決手段】第2トランジスタ170のゲート電極171を半導体基板1に対するマスクとして半導体基板1へイオン注入を行うことにより、第2トランジスタのドレイン175を形成するとともに、第2トランジスタ170のゲート電極171へイオン注入を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、互いに異なる特性を有するトランジスタを含む半導体装置の製造方法に関し、特に光電変換部を備えた半導体装置の製造方法に関する。

【背景技術】

【0002】

光電変換装置等の半導体装置において、トランジスタの特性を互いに異ならせる場合がある。特許文献1には、光電変換領域に配された第1トランジスタのドレインの不純物濃度が、周辺回路領域に配された第2トランジスタのドレインの不純物濃度よりも低い光電変換装置が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−41726号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トランジスタの安定な動作のためには、ゲート電極の不純物濃度を制御することが好ましい。しかしながら、特許文献1では、第1トランジスタと第2トランジスタのゲート電極の不純物濃度の制御について十分に検討がなされていない。

【0005】

そこで本発明は、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を好適に制御できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するための本発明は、第1トランジスタと、第2トランジスタと、を備える半導体装置の製造方法であって、半導体基板を覆うポリシリコン膜の上に設けられた絶縁膜をパターニングすることにより、前記ポリシリコン膜の上に前記絶縁膜から第1部材および第2部材を形成する第1工程と、前記第1部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第1トランジスタのゲート電極を形成し、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第2トランジスタのゲート電極を形成する第2工程と、前記第1部材を前記第1トランジスタの前記ゲート電極に対するマスクとし、前記第1トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして、前記半導体基板へイオン注入を行うことにより、前記第1トランジスタのドレインを形成する第3工程と、前記第2部材を薄くする第4工程と、前記第4工程の後に、前記第2トランジスタのゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタのドレインを形成するとともに、前記第2トランジスタの前記ゲート電極の不純物濃度が、前記第1トランジスタの前記ゲート電極の不純物濃度と異なるように、前記第2トランジスタの前記ゲート電極へイオン注入を行う第5工程を有することを特徴とする。

【発明の効果】

【0007】

本発明の製造方法によれば、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を好適に制御できる。

【図面の簡単な説明】

【0008】

【図1】(a)光電変換装置の概要の一例を説明するための平面模式図、(b)光電変換ユニットの等価回路の一例を説明するための模式図。

【図2】光電変換ユニットのレイアウトの一例を説明するための平面模式図。

【図3】(a)光電変換装置の主要部の一例を説明するための断面模式図、(b)光電変換装置の主要部の一例を説明するための断面模式図。

【図4】(a)光電変換装置の第1実施形態を説明するための断面模式図、(b)光電変換装置の第2例を説明するための断面模式図。

【図5】(a)第1実施形態の光電変換装置の製造方法の一例における工程aを説明するための断面模式図、(b)第1実施形態の光電変換装置の製造方法の一例における工程bを説明するための断面模式図、(c)第1実施形態の光電変換装置の製造方法の一例における工程cを説明するための断面模式図。

【図6】(d)第1実施形態の光電変換装置の製造方法の一例における工程dを説明するための断面模式図、(e)第1実施形態の光電変換装置の製造方法の一例における工程eを説明するための断面模式図、(f)第1実施形態の光電変換装置の製造方法の一例における工程fを説明するための断面模式図。

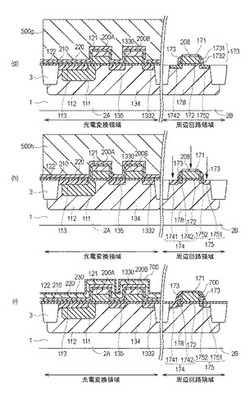

【図7】(g)第1実施形態の光電変換装置の製造方法の一例における工程fを説明するための断面模式図、(h)第1実施形態の光電変換装置の製造方法の一例における工程hを説明するための断面模式図、(i)第1実施形態の光電変換装置の製造方法の一例における工程iを説明するための断面模式図。

【図8】(j)第1実施形態の光電変換装置の製造方法の一例における工程jを説明するための断面模式図、(k)第1実施形態の光電変換装置の製造方法の一例における工程kを説明するための断面模式図、(l)第1実施形態の光電変換装置の製造方法の一例における工程lを説明するための断面模式図。

【図9】(m)第2実施形態の光電変換装置の製造方法の一例における工程mを説明するための断面模式図、(n)第1実施形態の光電変換装置の製造方法の一例における工程nを説明するための断面模式図、(o)第1実施形態の光電変換装置の製造方法の一例における工程oを説明するための断面模式図。

【発明を実施するための形態】

【0009】

まず、図1を用いて、半導体装置である光電変換装置100の一例を説明する。なお、図1以降の図面について、共通の部材には同一の符号をつけて、説明を省略する。光電変換装置100には、図1(a)において一点鎖線で囲まれた光電変換領域101が設けられており、光電変換領域101には、複数の光電変換ユニット102が配列されている。図1(a)では複数の光電変換ユニット102を2次元状に配列したエリアセンサの例を示すが、複数の光電変換ユニット102を1次元状に配列したリニアセンサとしてもよい。

【0010】

図1(b)に示すように、光電変換ユニット102は、光電変換部110と、光電変換部110で生じた信号電荷に基づく電気信号を生成する信号生成部130と、信号電荷を光電変換部110から信号生成部130へ転送する転送ゲート120とを備える。本例の信号生成部130は、キャパシタ131と、キャパシタ131に接続されたゲートを有する増幅トランジスタ132と、キャパシタ131に接続されたソースを有するリセットトランジスタ133とを有している。

【0011】

光電変換部110に光が入射すると、光電変換部110には信号電荷が生じる。転送ゲート120をONにすることにより、光電変換部110で生じた信号電荷を、転送チャネルを介して、信号生成部130のキャパシタ131に転送する。これにより、キャパシタ131に信号電荷が保持される。キャパシタ131に保持された信号電荷の量に応じたゲート電圧が増幅トランジスタ132のゲートに加わる。増幅トランジスタ132は、ソースフォロワ回路を成しており、増幅トランジスタ132のゲート電圧に応じて生成される電気信号が信号出力線340を介して出力される。リセットトランジスタ133をONにすることにより、キャパシタ131に接続された増幅トランジスタ132のゲート電圧が、駆動線350を介して供給される電位に基づく電圧にリセットされる。信号生成部130は、信号出力線340への出力のON/OFFを切り替える選択トランジスタをさらに有することもできる。本例の光電変換ユニット102は、1つの光電変換部110と1つの信号生成部130とが対になっているが、信号生成部130の少なくとも一部(例えば増幅トランジスタ132)を複数の光電変換部110が共有する構造を採用することもできる。その場合、転送ゲート120は複数の光電変換部110の各々ごとに設けることが好ましい。また、転送ゲート120は、グローバルシャッターの実現のために、信号電荷を一時的に保持するための電荷保持構造を有することもできる。光電変換部110と増幅トランジスタ132のゲートと間に転送ゲート120を設けずに、光電変換部110と増幅トランジスタ132を直結することもできる。光電変換部110と増幅トランジスタ132を直結した構造については、例えば特開2000−312024号公報を参照することができる。

【0012】

図2は、光電変換ユニットのレイアウトの一例を説明する平面模式図であり、図3(a)は、図2のX−X’線における断面模式図、図3(b)は図2のY−Y’線における断面模式図である。

【0013】

光電変換部110は単結晶シリコン等の半導体からなる半導体基板1の第1活性部2Aに設けられている。第1活性部2A以外の部分は分離部3であり、第1活性部2Aは分離部3に囲まれている。本例の分離部3はSTI(Shallow Trench IsolaTion)構造を有しているが、LOCOS(Local OxiDaTion Silicon)構造等を有していてもよいし、拡散分離構造を有していてもよい。本例では、光電変換部110と転送ゲート120、第5半導体領域135およびリセットトランジスタ133が同じ活性部2に設けられており、増幅トランジスタ132が別の活性部2に設けられている。しかし、リセットトランジスタ133を光電変換部110とは別の活性部2に設けることもできるし、増幅トランジスタ132とリセットトランジスタ133とを同じ第1活性部2Aに設けることもできる。

【0014】

以下の説明において、第1導電型の半導体領域とは、信号電荷と同極性の電荷を多数キャリアとする不純物領域であり、第1導電型の反対導電型である第2導電型の半導体領域とは、信号電荷と同極性の電荷を少数キャリアとする不純物領域である。例えば、信号電荷が電子である場合には、第1導電型の半導体領域はn型半導体領域であり、第2導電型の半導体領域はp型半導体領域である。信号電荷が正孔である場合には、第1導電型の半導体領域はp型半導体領域であり、第2導電型の半導体領域はn型半導体領域である。

【0015】

各トランジスタはソースとドレインを有し、ソースとドレイン間の導通を間を、ゲートによって制御する、電界効果トランジスタ(FET:Field Effect Transistor)である。ゲートは、ゲート電極と、ゲート絶縁膜と、ゲート絶縁膜の下に位置する半導体領域であるチャネル領域とを有する、いわゆるMIS型(Metal−Insulator−Semiconductor)構造を有する。第1導電型のソース/ドレインを有するトランジスタを第1導電型のトランジスタと定義し、第2導電型のソース/ドレインを有するトランジスタを第2導電型のトランジスタと定義する。例えば、信号電荷が電子である場合には、第1導電型のトランジスタは、n型トランジスタであり、信号電荷が正孔である場合には、第1導電型のトランジスタは、p型トランジスタである。

【0016】

本例の光電変換部110は、第1導電型の第1半導体領域111と第2導電型の第2半導体領域112と、第2導電型の第3半導体領域113とで構成された埋め込み型のフォトダイオードであるが、第3半導体領域113を省略することもできる。また、光電変換部110はフォトゲートであってもよい。

【0017】

光電変換部110を構成する第1半導体領域111および第2半導体領域112は、信号電荷を生じる電荷生成領域として機能する。第1半導体領域111と第2半導体領域112とがpn接合を成しており、第1半導体領域111は信号電荷を蓄積する蓄積領域としても機能する。第3半導体領域113は、半導体基板1の表面と第1半導体領域111との間に位置している。第1半導体領域111と第3半導体領域113とがpn接合を成しており、第3半導体領域113は半導体基板1表面でのノイズの発生を抑制する表面保護領域として機能する。

【0018】

第1導電型の第5半導体領域135は、第2導電型の第4半導体領域134とpn接合を成しており、浮遊拡散領域として機能する。第5半導体領域135はキャパシタ131の一部を成す。そのため、浮遊拡散領域である第5半導体領域135は、信号生成部130の一部を成す。

【0019】

転送ゲート120のゲート電極を転送ゲート電極121と呼ぶ。転送ゲート電極121と半導体基板1の転送チャネル領域との間にはゲート絶縁膜122が設けられている。転送ゲート電極121の材料はポリシコンからなる。典型的なゲート絶縁膜122は、酸化シリコン層からなる単層膜、酸窒化シリコンからなる単層膜、または、酸化シリコン層と酸窒化シリコン層とを有する多層膜である。本例のゲート絶縁膜122は、半導体基板1側から酸化シリコン層と酸窒化シリコン層とがこの順で配された多層膜である。ゲート絶縁膜122の材料に、酸化ハフニウム等のhigh−k材料を用いることもできる。

【0020】

増幅トランジスタ132のゲートは、ポリシリコンからなる増幅ゲート電極1320とゲート絶縁膜122を含む。増幅トランジスタ132は第1導電型のソース1321と第1導電型のドレイン1322を有する第1導電型のトランジスタである。

【0021】

リセットトランジスタ133のゲートは、ポリシリコンからなるリセットゲート電極1330とゲート絶縁膜122を含む。リセットトランジスタ133は第1導電型のソース135と第1導電型のドレイン1332を有する第1導電型のトランジスタである。リセットトランジスタ133の主たる動作であるリセット動作は、第5半導体領域135からの信号電荷の排出を伴う。そのため、便宜的に第5半導体領域135をリセットトランジスタ133のソースと見做している。ただし、光電変換装置100の駆動中、一時的に、リセットトランジスタ133のソースとドレインが逆になる動作があってもよい。

【0022】

光電変換部110および転送ゲート120は、第1中間膜210と、第1中間膜210の上に設けられた第1保護膜220と、第1保護膜220の上に設けられた第2保護膜230で覆われている。第1中間膜210と第1保護膜220と第2保護膜230はそれぞれ、信号生成部130に延在して、増幅トランジスタ132やリセットトランジスタ133を覆っている。第1中間膜210は酸化シリコンからなることが好ましく、第1保護膜220は窒化シリコンからなることが好ましく、第2保護膜230は酸化シリコンからなることが好ましいが、これらに限定されることはない。

【0023】

図3(a)、図3(a)に示す様に、第1中間膜210と転送ゲート電極121の上面との間には第1部材200Aが設けられている。図3(a)に示す様に、第1中間膜210とリセットゲート電極1330の上面との間には第1部材200Bが設けられている。図3(b)に示す様に、第1中間膜210と増幅ゲート電極1320の上面との間には第1部材200Cが設けられている。第1部材200A、200B、200Cは互いに分離した部材である。第1部材200A、200B、200Cのそれぞれは無機絶縁材料からなる。無機絶縁材料としては、窒化シリコン、酸窒化シリコン、酸化シリコン、炭化シリコンなどのシリコン化合物が好適であり、酸化シリコンが特に好適であるが、これらに限定されることはない。光電変換装置100から、第1中間膜210と第1保護膜220と、第2保護膜230と、第1部材200A、第1部材200B、第1部材200Cの少なくともいずれかを削除することもできる。しかし、少なくとも第1部材200Aが酸化シリコンからなる場合、転送ゲート120の近傍の光を制御する上で、当該酸化シリコンからなる第1部材200Aを転送ゲート電極121の上に設けておくことが好ましい。

【0024】

第1部材200Aは転送ゲート電極121の表面のうち上面のみに接している。第1部材200Bはリセットゲート電極1330の表面のうち上面のみに接し、第1部材200Cは増幅ゲート電極1320の表面のうち上面のみに接している。

【0025】

図3(a)、(b)に示す様に、光電変換領域は第1層間絶縁層311で覆われている。第1層間絶縁層311は、酸化シリコン、BPSG,PSG,BSGからなることが好ましい。図2に示す様に、増幅ゲート電極1320は、第5半導体領域135(浮遊拡散領域)に向かって延在している。そして、第5半導体領域135(浮遊拡散領域)と、増幅ゲート電極1320の双方が、シェアードコンタクトプラグ320で接続されている。シェアードコンタクトプラグ320の代わりに、コンタクトプラグと配線層を用いて、第5半導体領域135と増幅トランジスタ132のゲート電極1320とを接続することもできる。転送ゲート電極121には、第1コンタクトプラグ321が接続されている。なお、図3(a)には、参考のため、図2のX−X’線上にはない第1コンタクトプラグ321および第2コンタクトプラグ322を点線にて示している。この第1コンタクトプラグ321をチャネル領域上などの第1活性部2A上に設けることもできる。しかし、図3(a)に示すように、転送ゲート電極121を第1活性部2A上から分離部3上に延在させて、第1コンタクトプラグ321を分離部3上に配置することが好ましい。同様に、リセットトランジスタ133のゲート電極1330には、第2コンタクトプラグ322が接続されている。この第2コンタクトプラグ322も分離部3上に配置することが好ましい。リセットトランジスタ133のドレイン1332には第3コンタクトプラグ323が接続されている。図3(b)に示す様に、増幅トランジスタのドレイン1322には第8コンタクトプラグ328が接続されている。増幅トランジスタのソース1321には不図示のコンタクトプラグが接続されている。転送ゲート電極121、リセットゲート電極1330にそれぞれ接続する第1コンタクトプラグ321、第2コンタクトプラグ322は、第1部材200A、200Bを貫通している。

【0026】

図3(a)に示す様に、第1層間絶縁層311の上には、第1配線3311、第2配線3312、第3配線3313を含む第1配線層331が設けられている。第1配線3311、第2配線3312、第3配線3313は第1コンタクトプラグ321、第2コンタクトプラグ322、第3コンタクトプラグ323にそれぞれ接続されている。図3(b)に示す様に、第1層間絶縁層311の上には、第1配線層331の第7配線3317が設けられている。第7配線3317は、第7コンタクトプラグ327に接続されている。第1配線層331は第2層間絶縁層312で覆われている。本例のコンタクトプラグはタングステンからなり、配線はアルミニウムからなるが、これに限定されることはない。

【0027】

図1(a)に示す様に、光電変換装置100は、信号生成部130で生成された電気信号を処理する信号処理部140を備える。また、光電変換装置100は、信号処理部140に加えて、信号処理部140で処理された信号を外部に出力するための出力部150や、信号生成部130や信号処理部140を制御するための制御部160も備えることができる。本例では、信号処理部140や出力部150、制御部160を、光電変換領域101の周囲に位置する周辺回路領域103に設けているが、信号処理部140の少なくとも一部を光電変換領域101に設けることもできる。図1(a)において、一点鎖線と二点鎖線の間の領域が周辺回路領域103である。本例では、信号処理部140は、複数の列アンプを有する増幅回路141と、複数の列ADコンバータを有する変換回路142と、変換回路142からの出力を選択して出力部150へ出力するための水平走査回路143を有している。出力部150は電極パッドや保護回路を有し、制御部160は、垂直走査回路161やタイミング生成回路162等を有する。周辺回路領域103の構成は適宜設計することができる。

【0028】

信号処理部140は多数のトランジスタで構成される。図2、図3(a)、図3(b)には周辺回路領域103に設けられた信号処理部140のトランジスタの一例を記載している。

【0029】

ここで、信号生成部130の第1導電型のトランジスタである増幅トランジスタ132とリセットトランジスタ133とを総称して第1トランジスタと呼ぶ。上述した選択トランジスタが第1導電型である場合には、当該選択トランジスタも第1トランジスタとなりうる。増幅ゲート電極1320とリセットゲート電極1330とを総称して、第1ゲート電極と呼ぶ。第1ゲート電極は第1トランジスタのゲート電極である。また、転送ゲート120をゲート、光電変換部110の第1半導体領域111をソース、信号生成部130の第5半導体領域135をドレインとするトランジスタも、第1導電型である第1トランジスタを構成している。転送ゲート電極121は、第1トランジスタの第1ゲート電極である。

【0030】

信号処理部140は、図2に示す様に、第1導電型の第2トランジスタ170と、第2導電型の第3トランジスタ180で構成することができる。典型的には、信号処理部140の第2トランジスタ170と、第3トランジスタ180の双方が信号生成部130の第1トランジスタと異なる構造および特性を有する。図3(a)には第1導電型の第2トランジスタ170を示しており、図3(b)には第2導電型の第3トランジスタ180を示している。導電型が反対になる以外は、第1導電型の第2トランジスタ170と第2導電型の第3トランジスタ180は同様の構造を有することができる。

【0031】

第2トランジスタ170のゲート電極である第2ゲート電極171は、第1導電型のポリシリコンからなることが好ましい。第3トランジスタ180のゲート電極である第3ゲート電極181は、第2導電型のポリシリコンからなることが好ましい。

【0032】

第2ゲート電極171の第1導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度よりも高いことが好ましい。第2ゲート電極171の第1導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度の3/2倍以上であることがより好ましい。また、第2ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗よりも低いことが好ましい。第2ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗の2/3倍以下であることがより好ましい。

【0033】

第3ゲート電極191の第2導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度よりも高いことが好ましい。第3ゲート電極191の第2導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度の3/2倍以上であることがより好ましい。また、第3ゲート電極191のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗よりも低いことが好ましい。第3ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗の2/3倍以上であることがより好ましい。なお、典型的に、ポリシリコンのシート抵抗は不純物濃度に反比例する。

【0034】

第2ゲート電極171の第1導電型の不純物濃度と第3ゲート電極181の第2導電型の不純物濃度の少なくとも一方は、1×1021〜1×1022(atoms/cm3)であることが好ましい。転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度は、1×1021〜1×1022(atoms/cm3)であることが好ましい。第2ゲート電極171と第3ゲート電極181の少なくとも一方のシート抵抗は、1000Ω/□以下であることが好ましく、500Ω/□以下であることより好ましい。転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗は、1000Ω/□以下であることが好ましい。なお、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320、第2ゲート電極171および第3ゲート電極181のシート抵抗は、典型的には10Ω以上である。

【0035】

第2ゲート電極171や第3ゲート電極181の不純物濃度を高くし、抵抗を小さくすることにより、第2トランジスタ170や第3トランジスタ180の安定な動作が可能となる。第2トランジスタ170や第3トランジスタ180は、上述した変換回路142に用いると効果的である。変換回路142は、デジタル回路であるから、その第2ゲート電極171や第2ゲート電極181には、リセットトランジスタ133や転送ゲート120に比べて、周波数の高い電圧信号が入力されるためである。また、高速駆動のため、リセットトランジスタ133のゲート電圧よりも振幅の小さい電圧信号が印加される場合にも効果的である。例えば、リセットトランジスタ133や、増幅回路141、水平走査回路143、垂直走査回路161のトランジスタのゲート電圧の波高値を3.3Vとし、変換回路142のトランジスタのゲート電圧の波高値を1.8Vとする。ゲート電圧の振幅が小さいとトランジスタのわずかな特性ばらつきでも、顕著な影響が出るが、不純物濃度を高くすることにより、特性ばらつきを低減することができる。

【0036】

第2トランジスタ170のゲート絶縁膜172の膜厚が転送ゲート120のゲート絶縁膜122の膜厚よりも薄いことが好ましい。第2トランジスタ170のゲート絶縁膜172の膜厚が第1トランジスタのゲート絶縁膜122の膜厚よりも薄いことが好ましい。

【0037】

本例では、第2トランジスタ170のドレイン175の一部はシリサイド層177で覆われている。第2トランジスタ170のシリサイド層177とドレイン175は接している。ソース174に関しても同様である。また、第2ゲート電極171の上面はシリサイド層176で覆われている。ソース174とドレイン175を覆うシリサイド層177と第2ゲート電極171の上面を覆うシリサイド層176の少なくとも一方を省略することもできる。第3トランジスタ180のソース184、ドレイン185、第3ゲート電極181についても同様である。

【0038】

本例では、図2に示す様に、第2ゲート電極171と第3ゲート電極181とが一体化している。一体的に形成された周辺ゲート電極190が、第1導電型の部分(第2ゲート電極171)と第2導電型の部分(第3ゲート電極181)を有することになる。さらには、周辺ゲート電極190において、第1導電型の部分と第2導電型の部分とがpn接合を成す場合もある。

【0039】

本例では、周辺ゲート電極190の第1導電型の部分から第2導電型の部分に渡って、周辺ゲート電極190の上面をシリサイド層176で覆うことにより、第1導電型の部分と第2導電型の部分をシリサイド層176で短絡している。このようにすることにより、周辺ゲート電極190内に形成されるpn接合によって第2トランジスタ170および第3トランジスタ180の動作が不安定になることを抑制することができる。

【0040】

また、第2トランジスタ170は、第2ゲート電極171の側面に接する、サイドウォールスペーサ173を有している。本例では、サイドウォールスペーサ173は第1誘電体層1731と、第1誘電体層1731と第2ゲート電極171および半導体基板1との間に位置する第2誘電体層1732とを有する2層構造を有している。例えば、第1誘電体層1731は窒化シリコンからなり、第2誘電体層1732は酸化シリコンからなる。第2誘電体層1732の誘電率が第1誘電体層1731の誘電率よりも低いことが好ましいが、逆でもよい。なお、本例では、ゲート絶縁膜172が半導体基板1と第2ゲート電極171との間から、半導体基板1とサイドウォールスペーサ173との間に延在している。しかし、ゲート絶縁膜172を半導体基板1と第2ゲート電極171との間のみに設けて、サイドウォールスペーサ173が半導体基板1と接する形態を採用することもできる。

【0041】

サイドウォールスペーサ173の下には、ドレイン175の低濃度部1752が位置している。低濃度部1752は、ドレイン175の他の部分(高濃度部1751)に比べて第1導電型の不純物濃度が低くなっており、いわゆるLDD(Lightly Doped Drain)構造を有している。サイドウォールスペーサ173およびドレイン175の低濃度部1752を省略することもできる。ソース174に関しても同様に低濃度部と高濃度部を有することができる。第3トランジスタ180に関しても同様に、ドレイン185は、高濃度部1851と低濃度部1852を有することができる。

【0042】

第2トランジスタ170および第3トランジスタ180は、第1中間膜210とは別の第2中間膜240で覆われている。詳細には、第2中間膜240は、第2トランジスタ170のソース174とドレイン175を覆うとともに、サイドウォールスペーサ173に沿って、第2ゲート電極171の上面を覆っている。本例では、第2中間膜240とドレイン175の間には、シリサイド層177が、第2中間膜240と第2ゲート電極171の上面との間にはシリサイド層176が位置している。また、本例では、第2中間膜240と第2ゲート電極171の側面との間にはサイドウォールスペーサ173が位置している。第2中間膜240は、酸化シリコンからなることが好ましい。第2導電型の第3トランジスタ180についても同様である。

【0043】

第2トランジスタ170および第3トランジスタ180は、第3保護膜250で覆われている。詳細には、第3保護膜250は、第2トランジスタ170のソース174とドレイン175を覆うとともに、サイドウォールスペーサ173に沿って、第2ゲート電極171の上面を覆っている。本例では、第3保護膜250とドレイン175との間にはシリサイド層177が、第3保護膜250と第2ゲート電極171の上面との間にはシリサイド層176が位置している。また、本例では、第3保護膜250と第2ゲート電極171の側面との間にはサイドウォールスペーサ173が位置している。第3保護膜250は、窒化シリコンからなることが好ましい。上述したように、第3保護膜250と半導体基板1および第2ゲート電極171との間には、第2中間膜240が設けられている。第3保護膜250は第2中間膜240よりも厚いことが好ましい。

【0044】

絶縁膜310の第1層間絶縁層311および第2層間絶縁層312は、光電変換領域101から周辺回路領域103に延在して半導体基板1を覆っている。本例では、周辺回路領域103の絶縁膜310と半導体基板1および第2ゲート電極171との間に第2中間膜240および第3保護膜250が位置している例を示しているが、第2中間膜240および第3保護膜250の少なくとも一方を省略することもできる。

【0045】

図2、図3(a)に示す様に、第2トランジスタ170のソース174とドレイン175には、第4コンタクトプラグ324と第6コンタクトプラグ326がそれぞれ、シリサイド層177を介して接続されている。同様に、第2ゲート電極171には、第5コンタクトプラグ325がシリサイド層176を介して接続されている。第4コンタクトプラグ324、第5コンタクトプラグ325、第6コンタクトプラグ326はそれぞれ、第3保護膜250および第2中間膜240に接するとともに、これら第3保護膜250および第2中間膜240を貫通している。図2、図3(b)に示す様に、第3トランジスタ180のソース184とドレイン185には、第8コンタクトプラグ328と第9コンタクトプラグ329がそれぞれ、シリサイド層177を介して接続されている。同様に、第3ゲート電極181には、第5コンタクトプラグ325がシリサイド層176を介して接続されている。第8コンタクトプラグ328、第9コンタクトプラグ329はそれぞれ、第3保護膜250および第2中間膜240に接するとともに、これら第3保護膜250および第2中間膜240を貫通している。

【0046】

シリサイド層176を設けることにより、第2ゲート電極171と第5コンタクトプラグ325との接続抵抗を小さくして、第2トランジスタ170の高速駆動が可能となる。シリサイド層177を設けることにより、ドレイン175と第6コンタクトプラグ326との接続抵抗を小さくして、第2トランジスタ170の高速駆動が可能となる。ソース174と第4コンタクトプラグ324についても同様であり、第3トランジスタ180についても同様である。一方、光電変換領域101では、少なくとも転送ゲート電極121の上にはシリサイド層を設けないことが、金属汚染によるノイズを抑制する上で好ましい。

【0047】

図3(a)に示す様に、第1層間絶縁層311の上には、第1配線層331の第4配線3314、第5配線3315、第6配線3316が設けられている。第4〜第6配線はそれぞれ、第4〜第6コンタクトプラグに接続されている。図3(b)に示す様に、第1層間絶縁層311の上には、第1配線層331の第8配線3318、第9配線3319が設けられている。第8配線3318、第9配線は、それぞれ第8コンタクトプラグ328、第9コンタクトプラグ329に接続されている。本例のコンタクトプラグはタングステンからなり、配線はアルミニウムからなるが、これに限定されることはない。

【0048】

図4(a)は、光電変換装置100の第1実施形態の一例を説明する断面模式図である。なお、図4(a)では、簡略化のために、絶縁膜310と半導体基板1との間の保護膜や中間膜、制御膜の構成の記載を省略している。

【0049】

絶縁膜310と複数の配線層(第1配線層331、第2配線層332、第3配線層333、第4配線層334の4層)とで配線構造体300が構成されている。本例では、絶縁膜310は、第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313、第4層間絶縁層314で構成されている。

【0050】

配線構造体300の上にはパッシベーション膜440が設けられている。典型的なパッシベーション膜440は窒化シリコン層を含む。パッシベーション膜の窒化シリコン層の上下には、窒化シリコン層よりも薄い酸窒化シリコン層を設けることが好ましい。

【0051】

パッシベーション膜440の上には樹脂からなる第1平坦化膜460が設けられており、第1平坦化膜460の上面は平坦になっている。第1平坦化膜460の上には、カラーフィルタ470が設けられている。ここでは1つのカラーフィルタを示しているが、光電変換領域101には、原色系あるいは補色系の複数種類の色のカラーフィルタを光電変換部110の配置に応じて規則的に配列してなるカラーフィルタアレイが構成されている。カラーフィルタ470の上には樹脂からなる第2平坦化膜480が設けられており、第2平坦化膜480の上面は平坦になっている。第2平坦化膜480の上には、マイクロレンズ490が設けられている。マイクロレンズ490は反射防止コーティングを含むことができる。ここでは1つのマイクロレンズを示しているが、光電変換領域101には、複数のマイクロレンズが光電変換部110の配置に応じて規則的に配列してなるマイクロレンズアレイ構成されている。

【0052】

図4(b)は、光電変換装置100の第2実施形態の一例を説明する断面模式図である。なお、図4(b)では、簡略化のために、絶縁膜310と半導体基板1との間の保護膜や中間膜の構成の記載を省略している。絶縁膜310と複数の配線層(第1配線層331、第2配線層332の2層)とで配線構造体300が構成されている。本例では、絶縁膜310は、第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313、第4層間絶縁層314、第5層間絶縁層315を含む。また絶縁膜310は第1層間分離層316、第2層間分離層317、第3層間分離層318、第4層間分離層319を含む。各層間絶縁層は酸化シリコンからなることが好ましい。各層間分離層は窒化シリコンからなることが好ましい。層間分離層は配線層の金属材料の拡散を抑制したり、配線層の形成時のエッチングストッパとして機能したりする。層間分離層は層間絶縁層よりも薄いことが好ましい。絶縁膜310に囲まれた導光部材420が設けられている。導光部材420は絶縁膜310の層間絶縁層311〜315の高い屈折率を有しており、層間絶縁層311〜315をクラッド、導光部材420をコアとした光導波路構造をなしている。導光部材420は絶縁膜310の上面に延在しているが、延在しなくてもよい。導光部材420は窒化シリコンからなることが好ましい。

【0053】

導光部材420の上には集光膜430が設けられている。集光膜430の上には層内レンズ450が設けられている。層内レンズ450は反射防止コーティングを有することができる。光電変換領域101には、複数の層内レンズが光電変換部110の配置に応じて規則的に配列されてなる層内レンズアレイが構成されている。層内レンズ450は窒化シリコンからなることが好ましい

集光膜430は、層内レンズ450の屈折率よりも低い屈折率を有する。これにより、層内レンズ450から集光膜430に斜めに入射した光を集光膜430内での屈折により、導光部材420に向けて集光することができる。典型的な集光膜430は酸化シリコン層を含む。集光膜は、酸化シリコン層と導光部材420の間に、酸化シリコン層と導光部材420との間の屈折率を有する中間屈折率層を有することが好ましい。集光膜430は、酸化シリコン層と層内レンズとの間に、酸化シリコン層と層内レンズ450の間の屈折率を有する中間屈折率層を有することが好ましい。これら集光膜430の中間屈折率層は、酸化シリコン層と導光部材420あるいは酸化シリコン層と層内レンズ450との間の反射を抑制することができる。導光部材420や層内レンズ450が窒化シリコンからなる場合、中間屈折率層は酸窒化シリコンからなることが好ましい。中間屈折率層は酸化シリコン層よりも薄いことが好ましい。

【0054】

層内レンズ450の上には、樹脂からなる第1平坦化膜460が設けられており、第1平坦化膜460の上面は平坦になっている。カラーフィルタ470と第2平坦化膜480とマイクロレンズ490の構成は、図4(a)で説明した第1実施形態と同様であるため、説明を省略する。

【0055】

また、カラーフィルタアレイやレンズアレイを、半導体基板1に対して、絶縁膜310とは反対側に配置した、いわゆる裏面照射型の光電変換装置100とすることもできる。

【0056】

以上説明した光電変換装置100を用いて、撮像システムを構築することができる。撮像システムは、例えばスチルカメラやビデオカメラなどのカメラを挙げることができる。また、カメラ機能を有する情報端末も挙げることができる。撮像システムは、信号生成部130で生成された電気信号に基づく画像を処理する画像処理エンジン等の画像処理部および画像を表示する液晶ディスプレイ等の画像表示部の少なくとも一方を備えることができる。

【0057】

以下、本発明の半導体装置の製造方法を説明する。本発明の第1の観点は、信号生成部130が含む第1トランジスタと、信号処理部140が含む第2トランジスタ170に関する。第1の観点に係る製造方法では、第1トランジスタの第1ゲート電極は、第1部材200B,200Cをマスクとして用いて形成され、第2トランジスタ170の第2ゲート電極は第2部材207をマスクとして用いて形成される。さらに、第1部材200B、200Cをマスクとして第1トランジスタのドレインを形成する。この時、第1部材200B、200Cにより、第1ゲート電極への不純物の導入が抑制される。第2部材207を薄くした後に、第2トランジスタ170のドレイン175を形成する。これと同時に、第2トランジスタ170の第2ゲート電極171へイオン注入が行われる。これにより、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を制御することができる。

【0058】

本発明の第2の観点は、転送ゲート120を含む第1トランジスタと、信号処理部140が含む第2トランジスタ170に関する。第2の観点に係る製造方法では、転送ゲート電極121は、第1部材200Aをマスクとして用いて形成され、第2トランジスタ170の第2ゲート電極は第2部材200Dを用いて形成される。そして、第1部材200Aをマスクとして第5半導体領域135を形成する。この時、第1部材200Aにより、転送ゲート電極121への不純物の導入が抑制される。第2部材200Dを薄くした後に、第2トランジスタのドレイン185を形成する。これと同時に、第2トランジスタ170の第2ゲート電極171へイオン注入が行われる。これにより、転送ゲート120と第2トランジスタのそれぞれのゲート電極の不純物濃度を制御することができる。

【0059】

以下、光電変換装置100の製造方法について、図4(a)で示した、第1実施形態の光電変換装置100を例に挙げて詳細に説明する。上述した第1の観点に関して、以下の説明では、上記した第1トランジスタとして主にリセットトランジスタ133を例にしているが、第1トランジスタを増幅トランジスタ132としても同様の製造方法を採用することができる。また、第1トランジスタを、転送ゲート120をゲート、光電変換部110をソース、第5半導体領域135をドレインとみなしても、同様の製造方法を採用することができる。増幅トランジスタ132の特性ばらつきは、固定パターンノイズなどの原因になりうるため、増幅ゲート電極1320上の第1部材200Cは効果的である。また、転送ゲート電極121やリセットゲート電極の不純物濃度が高いと、ポリシリコンの空乏化の影響によるリーク電流が生じやすい。そのため、信号電荷を扱う転送ゲート電極121上の第1部材200Aやリセットゲート電極1330上の第2部材200Bも効果的である。

【0060】

(工程a)本工程を図5(a)を用いて説明する。第1導電型の半導体基板1を用意し、光電変換領域に半導体基板1の第1活性部2Aを画定する分離部3を、周辺回路領域に半導体基板1の第2活性部Bを画定する分離部3を、それぞれ形成する。本例では光電変換領域の分離部と周辺回路領域の分離部がともにSTI構造を有しているが、少なくとも一方がLOCOS構造を有していてもよいし、少なくとも一方が拡散分離構造を有していてもよい。

【0061】

次に、第1活性部2Aへ第2導電型の不純物をイオン注入することにより、第1活性部2Aに第2導電型の第2半導体領域112、第4半導体領域134の少なくとも一部を形成する。また、第2活性部2Bへ第2導電型の不純物をイオン注入することにより、第2活性部2Bに第2導電型のウェル領域178の少なくとも一部を形成する。図5(a)の例では、第2半導体領域112、第4半導体領域134の全部、および、ウェル領域178の全部を形成している。しかし、本工程において、第2半導体領域112、第4半導体領域134の一部及び/又はウェル領域178の一部を形成することができる。そして、工程e以降に、第2半導体領域112、第4半導体領域134の残りの一部及び/又はウェル領域178の残りの一部を形成することもできる。

【0062】

本例では、この工程で、第1活性部2Aに、光電変換部110の蓄積領域となる第1導電型の第1半導体領域111を形成するが、工程e以降に第1半導体領域111を形成することもできる。

【0063】

(工程b)本工程を図5(b)を用いて説明する。第1段階として、半導体基板1の上にゲート絶縁膜122、172用の絶縁膜22を形成する。絶縁膜22の厚みは1〜15nmが好ましい。本例では、まず、シリコンからなる半導体基板1を熱酸化して酸化シリコン膜を形成する。その後に、酸化シリコン膜の、第2トランジスタ170のゲート絶縁膜172に対応する部分を、リセットトランジスタ133のゲート絶縁膜122に対応する部分よりも薄くする。次いで、酸化シリコン膜の表面を酸窒化することにより、酸化シリコン層と酸窒化シリコン層とを有するゲート絶縁膜122、172の絶縁膜22を形成する。絶縁膜22はこのような構造および形成方法に限定されるものではない。リセットトランジスタ133のゲート絶縁膜122と第2トランジスタ170用のゲート絶縁膜172とが同じ厚みであってもよいし、酸化シリコン膜を酸窒化せずに、絶縁膜22を酸化シリコン層の単層膜としてもよい。また、リセットトランジスタ133のゲート絶縁膜122と第2トランジスタのゲート絶縁膜172とを、厚みが異なるように別々に形成してもよい。また、酸化ハフニウム等のhigh−k材料を半導体基板上に堆積することによりゲート絶縁膜を形成してもよい。

【0064】

次に、第2段階として、絶縁膜22の上にポリシリコン膜21を形成する。ポリシリコン膜21の厚みは50〜500nmが好ましい。本例では、ノンドープポリシリコンを堆積してポリシリコン膜21を形成している。パターニングされた第1フォトレジストをマスクとして用いて、ポリシリコン膜21の転送ゲート電極121、リセットゲート電極1330および第2ゲート電極171に対応する部分に第1導電型の不純物をイオン注入する。第1フォトレジストを除去する。パターニングされた第2フォトレジストをマスクとして用いて、ポリシリコン膜21の第3ゲート電極181に対応する部分に第2導電型の不純物をイオン注入する。本工程での各イオン注入のドーズ量を1×1015〜1×1016(ions/cm2)、より好ましくは、1×1015〜6×1015(ions/cm2)とするとよい。また、各イオン注入による、ポリシリコン膜21の不純物濃度は、1×1021〜1×1022(atoms/cm3)であることが好ましい。

【0065】

なお、ドープトポリシリコンを堆積してポリシリコン膜21を形成することもでき、上記した不純物濃度と同程度となるようにポリシリコン膜21を成膜することができる。しかし、第3ゲート電極181に対応する部分は、第2導電型にすることが好ましいため、ドープトポリシリコンよりもノンドープポリシリコンを堆積することが好ましい。

【0066】

次に、第3段階として、ポリシリコン膜21の上に絶縁膜20を形成する。絶縁膜20の材料に無機絶縁材料を用いて、絶縁膜20を無機絶縁膜とすることが好ましい。その場合、絶縁膜20の材料には酸化シリコン、酸窒化シリコン、窒化シリコン、炭化シリコンなどのシリコン化合物を用いることができる。なお、絶縁膜20の材料に一般的なフォトレジストよりも耐薬品性や耐熱性の高いポリイミドなどの有機絶縁材料を用いて、絶縁膜20を有機絶縁膜とすることもできる。絶縁膜20は多層膜であってもよい。絶縁膜20の厚みは、ポリシリコン膜21の厚みよりも小さいことが好ましく、ポリシリコン膜21の厚みの1/2以下であることがより好ましい。典型的には、絶縁膜20の厚みは10〜100nmである。図2に、転送ゲート電極121の長さLと幅Wを示している。各ゲート電極の長さは、トランジスタのゲート長が定義される方向におけるゲート電極の長さであり、各ゲート電極の幅はトランジスタのゲート幅が定義される方向におけるゲート電極の幅である。第1部材200A,200B、200Cおよび第2部材207の厚みは、ゲート電極の長さ(L)よりも小さいことが好ましい。上記したポリシリコン膜21への不純物の導入は、絶縁膜20の形成前に行うことが好ましいが、絶縁膜20を介したイオン注入によって行うこともできる。この場合のイオン注入は、絶縁膜20をイオンが透過できるだけの十分に高い注入エネルギーが必要となる。

【0067】

次に、第4段階として、絶縁膜20の上にパターニングされた第3フォトレジストを形成する。第3フォトレジストは、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320、第2ゲート電極171、第3ゲート電極181のレイアウトに応じてパターニングされている。図5(b)では、転送ゲート電極121に対応する第3フォトレジスト24A、リセットゲート電極1330に対応する第3フォトレジスト24B、第2ゲート電極171に対応する第3フォトレジスト24Dを示している。増幅ゲート電極1320に対応する第3フォトレジストと、第3ゲート電極181に対応する第3フォトレジストも同時に形成することができる。

【0068】

(工程c)本工程を図5(c)を用いて説明する。パターニングされた第3フォトレジスト24A,24B、24Dをマスクとして、絶縁膜20のエッチングを行うことにより、絶縁膜20をパターニングする。エッチングは、ドライエッチングが好ましい。これにより、絶縁膜20から、転送ゲート電極121のレイアウトに応じて配置された第1部材200Aが得られる。リセットゲート電極1330のレイアウトに応じて配置された第1部材200Bが得られる。第2ゲート電極171のレイアウトに応じて配置された第2部材207が得られる。同時に、増幅ゲート電極1320のレイアウトに応じて配置された第1部材200C(不図示)と、第3ゲート電極181のレイアウトに応じて配置された第2部材(不図示)も得ることができる。図2を用いて説明したように、本例の第2ゲート電極181と第3ゲート電極181は一体化している。そのため、第2ゲート電極171のレイアウトに応じて配置された第2部材207が、第3ゲート電極181のレイアウトに応じて配置された第2部材と一体的に形成される。

【0069】

(工程d)本工程を図6(d)を用いて説明する。ポリシリコン膜21の上に設けられた第1部材200A,200B、200Cをマスクとして、ポリシリコン膜21のエッチングを行うことにより、ポリシリコン膜21をパターニングする。ポリシリコン膜21の上に設けられた第2部材207をマスクとして、ポリシリコン膜21のエッチングを行うことにより、ポリシリコン膜21をパターニングする。これにより、第1部材200A,200Bの形状に応じた平面形状を有する転送ゲート電極121、リセットゲート電極1330をそれぞれ形成する。また、第2部材207の形状に応じた平面形状を有する第2ゲート電極171を形成する。同時に、増幅ゲート電極1320、第3ゲート電極181も形成することができる。なお本例では、図2に示す様に、第2ゲート電極171と第3ゲート電極181が周辺ゲート電極190として、一体的に形成される。工程aで説明したように、周辺ゲート電極190の第2ゲート電極171に対応する部分は第1導電型になっており。第3ゲート電極181に対応する部分は第2導電型になっている。そのため、周辺ゲート電極190が、第1導電型の部分(第2ゲート電極に対応する部分)と第2導電型の部分(第3ゲート電極に対応する部分)を有することになる。さらには、第1導電型の部分と第2導電型の部分とがpn接合を成す場合もある。

【0070】

工程cで用いた第3フォトレジスト24A,24B,24Cは、ポリシリコン膜21のパターニングに先立って除去しておくことが好ましい。しかし、第3フォトレジスト24A,24Bと第1部材200A,200B及び/又はフォトレジスト24Cと第2部材207をマスクとしてポリシリコン膜21のエッチングを行ってもよい。転送ゲート電極121、リセットゲート電極1330の形成と、第2ゲート電極171の形成とを同時に行うことが好ましい。本工程では、少なくとも絶縁膜22の、ゲート電極121と半導体基板1との間の部分からの延在部を露出させる。絶縁膜22の延在部を薄くしてもよく、さらには絶縁膜22の延在部を完全に除去して半導体基板1を露出させてもよい。

【0071】

(工程e)本工程を図6(e)を用いて説明する。第2トランジスタ170以外の部分を第4フォトレジスト(不図示)で覆う。そして、第2部材207および第2ゲート電極171を半導体基板1に対するマスクとして、半導体基板1の第2活性部2Bへ第2導電型の不純物のイオン注入を行うことにより、第2トランジスタ170のドレイン175の低濃度部1752を形成する。低濃度部1752は、いわゆるLDD(Lightly Dopede Draind)として機能する。同時に、第2トランジスタ170のソース174の低濃度部1742も形成することができる。第4フォトレジストを除去する。

【0072】

リセットトランジスタ133以外の部分を第5フォトレジスト(不図示)で覆う。そして、第1部材200Bおよびリセットゲート電極1330を半導体基板1に対するマスクとして、第1活性部2Bへ第1導電型の不純物をイオン注入を行う。これにより、リセットトランジスタ133のドレイン1332を形成する。同時に、リセットトランジスタ133のソースであり、浮遊拡散領域として機能する第5半導体領域135も形成することができる。第5フォトレジストを除去する。

【0073】

光電変換部110以外の部分を第6フォトレジスト(不図示)で覆う。そして、第1活性部2Aへ第2導電型の不純物のイオン注入を行うことにより、光電変換部の表面保護領域となる、第3半導体領域133を形成する。第6フォトレジストを除去する。

【0074】

第3トランジスタ180以外の部分を第7フォトレジスト(不図示)で覆う。そして、第2部材207および第3ゲート電極181を半導体基板1に対するマスクとして、第2活性部2Bへ第2導電型の不純物のイオン注入を行う。これにより、第3トランジスタ180のドレイン185の低濃度部1852(LDD:Lightly Dpoede Draind)を形成する。同時に、第3トランジスタ180のソース184の低濃度部も形成することができる。第7フォトレジストを除去する。

【0075】

典型的には、本工程での各イオン注入のドーズ量を1×1013〜1×1014(ions/cm2)とする。第1部材200A,200B、200C、第2部材207をマスクとして用いることから、各イオン注入の注入エネルギーは、第1部材200A,200B、200C、第2部材207をイオンが実質的に透過しない程度にする必要があることはいうまでもない。半導体基板1の表面の近傍に形成される低濃度部1752、1852や、第5半導体領域135、第3半導体領域133を形成するために必要な注入エネルギーは、各トランジスタの特性に応じて決定される。したがって、マスクとして機能しうる第1部材200A,200B、200C、第2部材207の厚みは、この注入エネルギーによって適宜決定すればよい。なお、ドレイン175の低濃度部1752の形成段階と、ドレイン1332の形成段階と、第3半導体領域113の形成段階と、ドレイン175の低濃度部1852の形成段階とを、この順で有することに限定されるものではない。

【0076】

(工程f)本工程を図6(f)を用いて説明する。光電変換領域および周辺回路領域を覆う酸化シリコン膜1210を形成する。この酸化シリコン膜1210の厚みは第1部材200A,200B、200Cおよび第2部材207の厚みより小さいことが好ましく、典型的には1〜30nmとする。酸化シリコン膜の上に光電変換領域および周辺回路領域を覆う窒化シリコン膜1220を形成する。この窒化シリコン膜1220の厚みは酸化シリコン膜1210の厚みよりも大きいことが好ましく、典型的には10nm〜100nmとする。

【0077】

(工程g)本工程を図7(g)を用いて説明する。本工程において、第2部材207を薄くする。第2部材207は第1部材200A、200B、200Cよりも薄くされることが好ましい。第2部材207を完全に除去してしまってもよい。具体的には、まず、光電変換間領域を第8フォトレジスト500gで覆う。そして、第8フォトレジスト500gをマスクとして、第2部材207上に位置する窒化シリコン膜1220、酸化シリコン膜1210を順次エッチングし、さらに第2部材207をエッチングする。第2部材207のエッチングは、第2部材208が薄く残る時点で終了してもよいし、第2部材207が完全に除去されて第2ゲート電極171が露出するまで行ってもよい。第1部材200A,200B,200Cを薄くしてもよいし、第1部材200A,200B,200Cを完全に除去してリセットゲート電極1330等の上面を露出させてもよいが、薄くしないことが好ましい。

【0078】

本工程において、第2部材207のエッチングと同時に、第2トランジスタ170のサイドウォールスペーサ173を形成することができる。本例のサイドウォールスペーサ173は、窒化シリコン膜1220の一部である第1誘電体層1731と、酸化シリコン膜1210の一部である第2誘電体層1732との2層構造を有している。第2誘電体層1732が第1誘電体層1731と第2ゲート電極171の側面との間に位置する。窒化シリコン膜1220と酸化シリコン膜1210を用いることにより、第2誘電体層1732の誘電率は第1誘電体層1731の誘電率よりも低くなる。なお、工程fにおいて、酸化シリコン膜1210と窒化シリコン膜1220の上下関係を逆にすることもでき、その場合には、第2誘電体層1732の誘電率は第1誘電体層1731の誘電率よりも高くなる。なお、第2トランジスタ170のサイドウォールスペーサ173の形成と同時に、第3トランジスタ180のサイドウォールスペーサ173も形成することができる。なお、ドレインの低濃度部1742やサイドウォールスペーサ135を形成しない場合には、工程eと工程dの間に第2部材207を薄くすることもできる。

【0079】

(工程h)本工程を図7(h)を用いて説明する。光電変換領域および第3トランジスタ180を覆い、第2トランジスタ170を覆わない第9フォトレジスト500hを形成する。第2ゲート電極171をマスクとして、半導体基板1の第2活性部2Bに第1導電型の不純物をイオン注入する。これにより、第2トランジスタ170のドレイン175の高濃度部1751を形成する。これにより、工程eで説明した低濃度部1752と、本工程で形成される高濃度部1751とを有する、第2トランジスタ170のドレイン175が形成される。同時に、第2トランジスタ170のソース174の高濃度部1741も形成でき、第2トランジスタ170のソース174が形成される。上述したように、工程gにて第2部材208が薄くなっているか、第2部材208が存在せずに第2ゲート電極171が露出している。そのため、高濃度部1751の形成(ドレイン175の形成)のためのイオン注入と同時に、第2ゲート電極171へも不純物が導入される。このイオン注入は、第9フォトレジスト500hで覆われた転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の第1導電型の不純物濃度よりも、第2ゲート電極171の不純物濃度が高くなるように行うことが好ましい。典型的には、本工程でのドレイン175の形成のためのイオン注入のドーズ量を1×1015〜1×1016(ions/cm2)とする。より好ましくは、1×1015〜6×1015(ions/cm2)である。典型的には、ドレイン175形成のためのイオン注入のドーズ量は、工程eにおけるイオン注入のドーズ量の10〜1000倍である。このような転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の不純物濃度は、先の工程bで説明した、ポリシリコン膜21の不純物濃度によって実質的に規定される。これは、工程eでは、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の上には、第1部材200A,200B,200Cが設けられているためである。すなわち、第5半導体領域135やドレイン1332、ソース1321、ドレイン1322の形成のためのイオン注入では、第1部材200A,200B,200Cがゲート電極に対するマスクとして機能する。つまり、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320には実質的にイオン注入がされないためである。そのため、本工程でのイオン注入により、第2ゲート電極171の不純物濃度を、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の不純物濃度よりも高くすることができる。当然、イオン注入の注入エネルギーは、ドレイン175の形成に必要なように設定される。また、工程gは第2部材208の厚みは、ドレイン175の形成に必要な注入エネルギーによって、第2ゲート電極171にイオン注入が可能となる程度に設定することができる。

【0080】

また、光電変換領域および第2トランジスタ170を覆い、第3トランジスタ180を覆わない第10フォトレジスト(不図示)を形成する。第2トランジスタ170と同様にして、第3ゲート電極181に第2導電型の不純物をイオン注入する。また、第3トランジスタのドレイン185の高濃度部1851、ソース184の高濃度部1841を形成する。典型的には、本工程でのドレイン185の形成のためのイオン注入のドーズ量を1×1015〜1×1016(ions/cm2)とする。より好ましくは、1×1015〜6×1015(ions/cm2)である。

【0081】

以上の工程により、転送ゲート120及び各トランジスタの動作に影響するイオン注入は完了する。

【0082】

(工程i)本工程を図7(i)を用いて説明する。光電変換領域および周辺回路領域に酸化シリコン膜を形成する。酸化シリコン膜の上に光電変換領域を覆い、周辺回路領域を覆わない第11フォトレジスト(不図示)を形成する。第11フォトレジストをマスクとして酸化シリコン膜をエッチングすることにより、第2トランジスタ170の第2ゲート電極171の上面を露出させる。なお、工程gにおいて、第2部材207が完全に除去されずに第2部材208として第2ゲート電極171上に残る場合には、本工程で、第2部材208をエッチングすることにより第2ゲート電極181の上面を露出させる。第11フォトレジストを除去する。これにより第11フォトレジストで覆われていた光電変換領域に、酸化シリコン膜の一部として第2保護膜230が形成される。そして、コバルトやチタン、ニッケル、タングステン等のシリサイド化し得る金属材料からなる金属膜700を第2トランジスタ170の第2ゲート電極171の上面およびソース174およびドレイン175に接するように形成する。また、金属膜700は第3トランジスタ180の第3ゲート電極181の上面およびソース174、ドレイン175に接するように形成される。なおこの時、金属膜700は光電変換領域にも形成されるが、金属膜700とリセットトランジスタ133の間には、第1保護膜220や第2保護膜230が位置しており、金属膜700とリセットトランジスタ133や転送ゲート電極121は接しない。

【0083】

(工程j)本工程を図8(j)を用いて説明する。半導体基板1を加熱して、金属膜700と第2ゲート電極171とを熱反応させ、第2ゲート電極171の上面をシリサイド化することにより、第2ゲート電極171の上にシリサイド層176を形成する。同時に、金属膜700と第2トランジスタ170のソース174とドレイン175もシリサイド化することができ、ソース174とドレイン175の上にシリサイド層177を形成することができる。第3トランジスタ180も同様に、シリサイド化することができる。その後、光電変換領域に位置する未反応の金属膜700を除去する。その後、シリサイド層177、176をさらに加熱して、シリサイド層177、176を低抵抗化することもできる。

【0084】

(工程k)本工程を図8(k)を用いて説明する。光電変換領域および周辺回路領域を覆い、サイドウォールスペーサ173、及びシリサイド層176、177に接する酸化シリコン膜を形成する。ついで、光電変換領域および周辺回路領域を覆う窒化シリコン膜をこの酸化シリコン膜の上に形成し、当該窒化シリコン膜の光電変換領域に位置する部分を除去することにより、周辺回路領域に第3保護膜250を形成する。さらに酸化シリコン膜の光電変換領域に位置する部分を除去することにより、周辺回路領域に第2中間膜240を形成する。

【0085】

(工程l)本工程を図8(l)を用いて説明する。光電変換領域を覆い、第2保護膜230に接する第3中間膜260を形成する。なお、この第3中間膜260を、工程kで説明した酸化シリコン膜の光電変換領域に位置する部分を除去せずに、光電変換領域に残すことにより、第2中間膜240と同時に形成することもできる。また、第3中間膜260の形成を図3(a)、(b)のように省略してもよい。

【0086】

光電変換領域および周辺回路領域を覆う絶縁膜を形成し、当該絶縁膜を平坦化することにより、第1層間絶縁層311を形成する。平坦化の手法は、リフロー法、エッチバック法、CMP(Chemical Mecanical Polishing)法などを用いることができる。絶縁膜の材料としては、酸化シリコンや、BSG、PSG、BPSGなどの珪酸塩ガラスを用いることができる。

【0087】

次に、コンタクトを形成する。第1段階として、第1層間絶縁層311に、転送ゲート電極121に達する第1コンタクトホールを形成する。そして、第1コンタクトホールにタングステン等の導電材料を埋め込み、CMP法により余分なタングステンを除去して、転送ゲート電極121に接続する第1コンタクトプラグ321を形成する。同時に、第2コンタクトプラグ322、第3コンタクトプラグ323、第7コンタクトプラグ327、およびシェアードコンタクトプラグ320を形成する。シェアードコンタクトプラグ320は、第5半導体領域135と増幅ゲート電極1320の双方に接続するように形成される。第1コンタクトプラグ、第2コンタクトプラグ322および第7コンタクトプラグ327は、それぞれ、第1部材200A,200B,200Cを貫通して設けられる。しかし、工程f〜工程hにおいて、第1部材200A,200B,200Cを除去することもできる。

【0088】

続いて、第2段階として、第1層間絶縁層311に、第1ゲート電極171上のシリサイド層176に達する第5コンタクトホールを形成する。そして、第5コンタクトホールにタングステン等の導電材料を埋め込み、CMP法により余分なタングステンを除去して、シリサイド層176を介して第2ゲート電極171に接続する第5コンタクトプラグ325を形成する。第5コンタクトプラグ325は、シリサイド層177を貫通して第2ゲート電極171に接続してもよいが、シリサイド層177の上面に接することが好ましい。同時に、第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、および第9コンタクトプラグ329を形成する。第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、および第9コンタクトプラグ329は、それぞれシリサイド層177の上面に接して設けられる。なお、第3保護膜250は、第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、第9コンタクトプラグの形成のための各コンタクトホールの形成時のエッチングストッパとして機能する。つまり、第3保護膜250により、いわゆるセルフアラインコンタクトを実現することができる。なお上述した第1段階と第2段階の順序が逆であってもよい。

【0089】

光電変換領域に設けられるコンタクトプラグと、周辺回路領域に設けられるコンタクトプラグとを同時に形成することもできる。しかし、このように、光電変換領域に設けられるコンタクトプラグと、周辺回路領域に設けられるコンタクトプラグとを互いに異なるタイミングで別々に形成することが好ましい。これは、周辺回路領域にコンタクトホールを形成する際に飛散し得る、シリサイド層176、177に含まれる金属成分(コバルト等)が、光電変換領域での金属汚染の原因となる可能性を低減できるためである。

【0090】

コンタクトプラグの形成後、配線層を形成する。本実施形態では、配線層の主たる材料としてアルミニウムを用いている。第1層間絶縁層の上にアルミニウム膜を形成後、アルミニウム膜を適当にパターニングして、第1配線層を形成することができる。

【0091】

工程lの後は、周知の多層配線技術を用いて、各配線層331〜334および各層間絶縁層312〜315を形成して、配線構造体300を形成することができる。そして、配線構造体300の上に、パッシベーション膜440、第1平坦化膜460、カラーフィルタ470、第2平坦化膜480、マイクロレンズ490を形成することで、図4(a)に示した第1実施形態の光電変換装置100を得ることができる。

【0092】

次に、図4(b)で示した、第2実施形態の光電変換装置100の製造方法の一例を説明する。本実施形態は、第1実施形態の光電変換装置100の製造方法における工程kまでは同様に行えるため、説明を省略し、工程kの後に行われる工程m〜oについて説明する。

【0093】

(工程m)本工程を図9(m)を用いて説明する。工程lでは、酸化シリコン膜の光電変換領域に位置する部分を除去したが、本工程では、酸化シリコン膜を光電変換領域に残すことにより、周辺回路領域の第2中間膜240と、光電変換領域の第3中間膜260とを同時に形成する。また、工程lでは、窒化シリコン膜の光電変換領域に位置する部分を全て除去しているのに対して、本工程では、窒化シリコン膜の光電変換部110上に位置する部分を残している。窒化シリコン膜が光電変換部110上に残されて制御膜410となり、周辺回路領域に残されて第3保護膜250となる。

【0094】

(工程n)本工程を図9(n)を用いて説明する。コンタクトプラグの形成は工程lと同様に行うことができる。コンタクトプラグの形成後、第1配線層331を形成する。本実施形態では、第1配線層331の主たる材料として銅を用いている。第1層間絶縁層311の上に窒化シリコンからなる第1層間分離層316を介して第2層間絶縁層312を形成後、ダマシン法により第2層間絶縁層312に銅からなる第1配線層331を埋め込むことができる。同様にして周知の多層配線技術を用いて、第2配線層332及び、各層間絶縁層313〜315、各層間分離層317〜319を形成して、配線構造体300を形成することができる。その後、配線構造体300の絶縁膜310を部分的にエッチングして、制御膜410に達する深さの開口部421を設ける。制御膜410は、開口部421の形成時のエッチングストッパとして用いることができる。

【0095】

(工程o)本工程を図9(o)を用いて説明する。開口部421に、絶縁膜310の屈折率よりも高い屈折率を有する、窒化シリコン等からなる高屈折率膜を埋め込み、導光部材420を形成する。本例では、導光部材420の屈折率が、絶縁膜310の第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313の屈折率よりも高い。導光部材420は開口部421内から絶縁膜310の上面上に延在させることが好ましい。導光部材420の上面をCMP法等に平坦化する。制御膜410は、導光部材420の埋め込み時の、光電変換部110へのダメージを緩和する機能を有し得る。

【0096】

そして、導光部材420の上に、集光膜430、層内レンズ450、第1平坦化膜460、カラーフィルタ470、第2平坦化膜480、マイクロレンズ490を形成することで、図4(b)に示した第2実施形態の光電変換装置100を得ることができる。

【0097】

以上説明したように、本発明に係る半導体装置の製造方法によれば、第1トランジスタのゲート電極の不純物濃度と、第2トランジスタの不純物濃度を好適に制御することが可能となる。なお、半導体装置として、光電変換部を備えた光電変換装置を例に挙げたが、光電変換部を備えない半導体装置の製造方法にも適用が可能である。例えば、アナログ回路とデジタル回路が混在した半導体装置や、高電圧を扱う回路と低電圧を扱う回路とが混在した半導体装置にも適用することができる。

【0098】

本発明は説明に用いた例のみに限定されることはなく、明細書に記載した技術的思想に基づき、構成の変形や変更、置換、削除、追加を適宜行うことができる。

【符号の説明】

【0099】

110 光電変換部

120 転送ゲート

121 転送ゲート電極

130 信号生成部

132 増幅トランジスタ(第1トランジスタ)

1320 増幅ゲート電極

133 リセットトランジスタ(第1トランジスタ)

1330 リセットゲート電極

1332 ドレイン

135 第5半導体領域

140 信号処理部

170 第2トランジスタ

173 サイドウォールスペーサ

180 第3トランジスタ

200A 第1部材

200B 第1部材

200C 第1部材

207 第2部材

1 半導体基板

21 ポリシリコン膜

20 絶縁膜

【技術分野】

【0001】

本発明は、互いに異なる特性を有するトランジスタを含む半導体装置の製造方法に関し、特に光電変換部を備えた半導体装置の製造方法に関する。

【背景技術】

【0002】

光電変換装置等の半導体装置において、トランジスタの特性を互いに異ならせる場合がある。特許文献1には、光電変換領域に配された第1トランジスタのドレインの不純物濃度が、周辺回路領域に配された第2トランジスタのドレインの不純物濃度よりも低い光電変換装置が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−41726号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トランジスタの安定な動作のためには、ゲート電極の不純物濃度を制御することが好ましい。しかしながら、特許文献1では、第1トランジスタと第2トランジスタのゲート電極の不純物濃度の制御について十分に検討がなされていない。

【0005】

そこで本発明は、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を好適に制御できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するための本発明は、第1トランジスタと、第2トランジスタと、を備える半導体装置の製造方法であって、半導体基板を覆うポリシリコン膜の上に設けられた絶縁膜をパターニングすることにより、前記ポリシリコン膜の上に前記絶縁膜から第1部材および第2部材を形成する第1工程と、前記第1部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第1トランジスタのゲート電極を形成し、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第2トランジスタのゲート電極を形成する第2工程と、前記第1部材を前記第1トランジスタの前記ゲート電極に対するマスクとし、前記第1トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして、前記半導体基板へイオン注入を行うことにより、前記第1トランジスタのドレインを形成する第3工程と、前記第2部材を薄くする第4工程と、前記第4工程の後に、前記第2トランジスタのゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタのドレインを形成するとともに、前記第2トランジスタの前記ゲート電極の不純物濃度が、前記第1トランジスタの前記ゲート電極の不純物濃度と異なるように、前記第2トランジスタの前記ゲート電極へイオン注入を行う第5工程を有することを特徴とする。

【発明の効果】

【0007】

本発明の製造方法によれば、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を好適に制御できる。

【図面の簡単な説明】

【0008】

【図1】(a)光電変換装置の概要の一例を説明するための平面模式図、(b)光電変換ユニットの等価回路の一例を説明するための模式図。

【図2】光電変換ユニットのレイアウトの一例を説明するための平面模式図。

【図3】(a)光電変換装置の主要部の一例を説明するための断面模式図、(b)光電変換装置の主要部の一例を説明するための断面模式図。

【図4】(a)光電変換装置の第1実施形態を説明するための断面模式図、(b)光電変換装置の第2例を説明するための断面模式図。

【図5】(a)第1実施形態の光電変換装置の製造方法の一例における工程aを説明するための断面模式図、(b)第1実施形態の光電変換装置の製造方法の一例における工程bを説明するための断面模式図、(c)第1実施形態の光電変換装置の製造方法の一例における工程cを説明するための断面模式図。

【図6】(d)第1実施形態の光電変換装置の製造方法の一例における工程dを説明するための断面模式図、(e)第1実施形態の光電変換装置の製造方法の一例における工程eを説明するための断面模式図、(f)第1実施形態の光電変換装置の製造方法の一例における工程fを説明するための断面模式図。

【図7】(g)第1実施形態の光電変換装置の製造方法の一例における工程fを説明するための断面模式図、(h)第1実施形態の光電変換装置の製造方法の一例における工程hを説明するための断面模式図、(i)第1実施形態の光電変換装置の製造方法の一例における工程iを説明するための断面模式図。

【図8】(j)第1実施形態の光電変換装置の製造方法の一例における工程jを説明するための断面模式図、(k)第1実施形態の光電変換装置の製造方法の一例における工程kを説明するための断面模式図、(l)第1実施形態の光電変換装置の製造方法の一例における工程lを説明するための断面模式図。

【図9】(m)第2実施形態の光電変換装置の製造方法の一例における工程mを説明するための断面模式図、(n)第1実施形態の光電変換装置の製造方法の一例における工程nを説明するための断面模式図、(o)第1実施形態の光電変換装置の製造方法の一例における工程oを説明するための断面模式図。

【発明を実施するための形態】

【0009】

まず、図1を用いて、半導体装置である光電変換装置100の一例を説明する。なお、図1以降の図面について、共通の部材には同一の符号をつけて、説明を省略する。光電変換装置100には、図1(a)において一点鎖線で囲まれた光電変換領域101が設けられており、光電変換領域101には、複数の光電変換ユニット102が配列されている。図1(a)では複数の光電変換ユニット102を2次元状に配列したエリアセンサの例を示すが、複数の光電変換ユニット102を1次元状に配列したリニアセンサとしてもよい。

【0010】

図1(b)に示すように、光電変換ユニット102は、光電変換部110と、光電変換部110で生じた信号電荷に基づく電気信号を生成する信号生成部130と、信号電荷を光電変換部110から信号生成部130へ転送する転送ゲート120とを備える。本例の信号生成部130は、キャパシタ131と、キャパシタ131に接続されたゲートを有する増幅トランジスタ132と、キャパシタ131に接続されたソースを有するリセットトランジスタ133とを有している。

【0011】

光電変換部110に光が入射すると、光電変換部110には信号電荷が生じる。転送ゲート120をONにすることにより、光電変換部110で生じた信号電荷を、転送チャネルを介して、信号生成部130のキャパシタ131に転送する。これにより、キャパシタ131に信号電荷が保持される。キャパシタ131に保持された信号電荷の量に応じたゲート電圧が増幅トランジスタ132のゲートに加わる。増幅トランジスタ132は、ソースフォロワ回路を成しており、増幅トランジスタ132のゲート電圧に応じて生成される電気信号が信号出力線340を介して出力される。リセットトランジスタ133をONにすることにより、キャパシタ131に接続された増幅トランジスタ132のゲート電圧が、駆動線350を介して供給される電位に基づく電圧にリセットされる。信号生成部130は、信号出力線340への出力のON/OFFを切り替える選択トランジスタをさらに有することもできる。本例の光電変換ユニット102は、1つの光電変換部110と1つの信号生成部130とが対になっているが、信号生成部130の少なくとも一部(例えば増幅トランジスタ132)を複数の光電変換部110が共有する構造を採用することもできる。その場合、転送ゲート120は複数の光電変換部110の各々ごとに設けることが好ましい。また、転送ゲート120は、グローバルシャッターの実現のために、信号電荷を一時的に保持するための電荷保持構造を有することもできる。光電変換部110と増幅トランジスタ132のゲートと間に転送ゲート120を設けずに、光電変換部110と増幅トランジスタ132を直結することもできる。光電変換部110と増幅トランジスタ132を直結した構造については、例えば特開2000−312024号公報を参照することができる。

【0012】

図2は、光電変換ユニットのレイアウトの一例を説明する平面模式図であり、図3(a)は、図2のX−X’線における断面模式図、図3(b)は図2のY−Y’線における断面模式図である。

【0013】

光電変換部110は単結晶シリコン等の半導体からなる半導体基板1の第1活性部2Aに設けられている。第1活性部2A以外の部分は分離部3であり、第1活性部2Aは分離部3に囲まれている。本例の分離部3はSTI(Shallow Trench IsolaTion)構造を有しているが、LOCOS(Local OxiDaTion Silicon)構造等を有していてもよいし、拡散分離構造を有していてもよい。本例では、光電変換部110と転送ゲート120、第5半導体領域135およびリセットトランジスタ133が同じ活性部2に設けられており、増幅トランジスタ132が別の活性部2に設けられている。しかし、リセットトランジスタ133を光電変換部110とは別の活性部2に設けることもできるし、増幅トランジスタ132とリセットトランジスタ133とを同じ第1活性部2Aに設けることもできる。

【0014】

以下の説明において、第1導電型の半導体領域とは、信号電荷と同極性の電荷を多数キャリアとする不純物領域であり、第1導電型の反対導電型である第2導電型の半導体領域とは、信号電荷と同極性の電荷を少数キャリアとする不純物領域である。例えば、信号電荷が電子である場合には、第1導電型の半導体領域はn型半導体領域であり、第2導電型の半導体領域はp型半導体領域である。信号電荷が正孔である場合には、第1導電型の半導体領域はp型半導体領域であり、第2導電型の半導体領域はn型半導体領域である。

【0015】

各トランジスタはソースとドレインを有し、ソースとドレイン間の導通を間を、ゲートによって制御する、電界効果トランジスタ(FET:Field Effect Transistor)である。ゲートは、ゲート電極と、ゲート絶縁膜と、ゲート絶縁膜の下に位置する半導体領域であるチャネル領域とを有する、いわゆるMIS型(Metal−Insulator−Semiconductor)構造を有する。第1導電型のソース/ドレインを有するトランジスタを第1導電型のトランジスタと定義し、第2導電型のソース/ドレインを有するトランジスタを第2導電型のトランジスタと定義する。例えば、信号電荷が電子である場合には、第1導電型のトランジスタは、n型トランジスタであり、信号電荷が正孔である場合には、第1導電型のトランジスタは、p型トランジスタである。

【0016】

本例の光電変換部110は、第1導電型の第1半導体領域111と第2導電型の第2半導体領域112と、第2導電型の第3半導体領域113とで構成された埋め込み型のフォトダイオードであるが、第3半導体領域113を省略することもできる。また、光電変換部110はフォトゲートであってもよい。

【0017】

光電変換部110を構成する第1半導体領域111および第2半導体領域112は、信号電荷を生じる電荷生成領域として機能する。第1半導体領域111と第2半導体領域112とがpn接合を成しており、第1半導体領域111は信号電荷を蓄積する蓄積領域としても機能する。第3半導体領域113は、半導体基板1の表面と第1半導体領域111との間に位置している。第1半導体領域111と第3半導体領域113とがpn接合を成しており、第3半導体領域113は半導体基板1表面でのノイズの発生を抑制する表面保護領域として機能する。

【0018】

第1導電型の第5半導体領域135は、第2導電型の第4半導体領域134とpn接合を成しており、浮遊拡散領域として機能する。第5半導体領域135はキャパシタ131の一部を成す。そのため、浮遊拡散領域である第5半導体領域135は、信号生成部130の一部を成す。

【0019】

転送ゲート120のゲート電極を転送ゲート電極121と呼ぶ。転送ゲート電極121と半導体基板1の転送チャネル領域との間にはゲート絶縁膜122が設けられている。転送ゲート電極121の材料はポリシコンからなる。典型的なゲート絶縁膜122は、酸化シリコン層からなる単層膜、酸窒化シリコンからなる単層膜、または、酸化シリコン層と酸窒化シリコン層とを有する多層膜である。本例のゲート絶縁膜122は、半導体基板1側から酸化シリコン層と酸窒化シリコン層とがこの順で配された多層膜である。ゲート絶縁膜122の材料に、酸化ハフニウム等のhigh−k材料を用いることもできる。

【0020】

増幅トランジスタ132のゲートは、ポリシリコンからなる増幅ゲート電極1320とゲート絶縁膜122を含む。増幅トランジスタ132は第1導電型のソース1321と第1導電型のドレイン1322を有する第1導電型のトランジスタである。

【0021】

リセットトランジスタ133のゲートは、ポリシリコンからなるリセットゲート電極1330とゲート絶縁膜122を含む。リセットトランジスタ133は第1導電型のソース135と第1導電型のドレイン1332を有する第1導電型のトランジスタである。リセットトランジスタ133の主たる動作であるリセット動作は、第5半導体領域135からの信号電荷の排出を伴う。そのため、便宜的に第5半導体領域135をリセットトランジスタ133のソースと見做している。ただし、光電変換装置100の駆動中、一時的に、リセットトランジスタ133のソースとドレインが逆になる動作があってもよい。

【0022】

光電変換部110および転送ゲート120は、第1中間膜210と、第1中間膜210の上に設けられた第1保護膜220と、第1保護膜220の上に設けられた第2保護膜230で覆われている。第1中間膜210と第1保護膜220と第2保護膜230はそれぞれ、信号生成部130に延在して、増幅トランジスタ132やリセットトランジスタ133を覆っている。第1中間膜210は酸化シリコンからなることが好ましく、第1保護膜220は窒化シリコンからなることが好ましく、第2保護膜230は酸化シリコンからなることが好ましいが、これらに限定されることはない。

【0023】

図3(a)、図3(a)に示す様に、第1中間膜210と転送ゲート電極121の上面との間には第1部材200Aが設けられている。図3(a)に示す様に、第1中間膜210とリセットゲート電極1330の上面との間には第1部材200Bが設けられている。図3(b)に示す様に、第1中間膜210と増幅ゲート電極1320の上面との間には第1部材200Cが設けられている。第1部材200A、200B、200Cは互いに分離した部材である。第1部材200A、200B、200Cのそれぞれは無機絶縁材料からなる。無機絶縁材料としては、窒化シリコン、酸窒化シリコン、酸化シリコン、炭化シリコンなどのシリコン化合物が好適であり、酸化シリコンが特に好適であるが、これらに限定されることはない。光電変換装置100から、第1中間膜210と第1保護膜220と、第2保護膜230と、第1部材200A、第1部材200B、第1部材200Cの少なくともいずれかを削除することもできる。しかし、少なくとも第1部材200Aが酸化シリコンからなる場合、転送ゲート120の近傍の光を制御する上で、当該酸化シリコンからなる第1部材200Aを転送ゲート電極121の上に設けておくことが好ましい。

【0024】

第1部材200Aは転送ゲート電極121の表面のうち上面のみに接している。第1部材200Bはリセットゲート電極1330の表面のうち上面のみに接し、第1部材200Cは増幅ゲート電極1320の表面のうち上面のみに接している。

【0025】

図3(a)、(b)に示す様に、光電変換領域は第1層間絶縁層311で覆われている。第1層間絶縁層311は、酸化シリコン、BPSG,PSG,BSGからなることが好ましい。図2に示す様に、増幅ゲート電極1320は、第5半導体領域135(浮遊拡散領域)に向かって延在している。そして、第5半導体領域135(浮遊拡散領域)と、増幅ゲート電極1320の双方が、シェアードコンタクトプラグ320で接続されている。シェアードコンタクトプラグ320の代わりに、コンタクトプラグと配線層を用いて、第5半導体領域135と増幅トランジスタ132のゲート電極1320とを接続することもできる。転送ゲート電極121には、第1コンタクトプラグ321が接続されている。なお、図3(a)には、参考のため、図2のX−X’線上にはない第1コンタクトプラグ321および第2コンタクトプラグ322を点線にて示している。この第1コンタクトプラグ321をチャネル領域上などの第1活性部2A上に設けることもできる。しかし、図3(a)に示すように、転送ゲート電極121を第1活性部2A上から分離部3上に延在させて、第1コンタクトプラグ321を分離部3上に配置することが好ましい。同様に、リセットトランジスタ133のゲート電極1330には、第2コンタクトプラグ322が接続されている。この第2コンタクトプラグ322も分離部3上に配置することが好ましい。リセットトランジスタ133のドレイン1332には第3コンタクトプラグ323が接続されている。図3(b)に示す様に、増幅トランジスタのドレイン1322には第8コンタクトプラグ328が接続されている。増幅トランジスタのソース1321には不図示のコンタクトプラグが接続されている。転送ゲート電極121、リセットゲート電極1330にそれぞれ接続する第1コンタクトプラグ321、第2コンタクトプラグ322は、第1部材200A、200Bを貫通している。

【0026】

図3(a)に示す様に、第1層間絶縁層311の上には、第1配線3311、第2配線3312、第3配線3313を含む第1配線層331が設けられている。第1配線3311、第2配線3312、第3配線3313は第1コンタクトプラグ321、第2コンタクトプラグ322、第3コンタクトプラグ323にそれぞれ接続されている。図3(b)に示す様に、第1層間絶縁層311の上には、第1配線層331の第7配線3317が設けられている。第7配線3317は、第7コンタクトプラグ327に接続されている。第1配線層331は第2層間絶縁層312で覆われている。本例のコンタクトプラグはタングステンからなり、配線はアルミニウムからなるが、これに限定されることはない。

【0027】

図1(a)に示す様に、光電変換装置100は、信号生成部130で生成された電気信号を処理する信号処理部140を備える。また、光電変換装置100は、信号処理部140に加えて、信号処理部140で処理された信号を外部に出力するための出力部150や、信号生成部130や信号処理部140を制御するための制御部160も備えることができる。本例では、信号処理部140や出力部150、制御部160を、光電変換領域101の周囲に位置する周辺回路領域103に設けているが、信号処理部140の少なくとも一部を光電変換領域101に設けることもできる。図1(a)において、一点鎖線と二点鎖線の間の領域が周辺回路領域103である。本例では、信号処理部140は、複数の列アンプを有する増幅回路141と、複数の列ADコンバータを有する変換回路142と、変換回路142からの出力を選択して出力部150へ出力するための水平走査回路143を有している。出力部150は電極パッドや保護回路を有し、制御部160は、垂直走査回路161やタイミング生成回路162等を有する。周辺回路領域103の構成は適宜設計することができる。

【0028】

信号処理部140は多数のトランジスタで構成される。図2、図3(a)、図3(b)には周辺回路領域103に設けられた信号処理部140のトランジスタの一例を記載している。

【0029】

ここで、信号生成部130の第1導電型のトランジスタである増幅トランジスタ132とリセットトランジスタ133とを総称して第1トランジスタと呼ぶ。上述した選択トランジスタが第1導電型である場合には、当該選択トランジスタも第1トランジスタとなりうる。増幅ゲート電極1320とリセットゲート電極1330とを総称して、第1ゲート電極と呼ぶ。第1ゲート電極は第1トランジスタのゲート電極である。また、転送ゲート120をゲート、光電変換部110の第1半導体領域111をソース、信号生成部130の第5半導体領域135をドレインとするトランジスタも、第1導電型である第1トランジスタを構成している。転送ゲート電極121は、第1トランジスタの第1ゲート電極である。

【0030】

信号処理部140は、図2に示す様に、第1導電型の第2トランジスタ170と、第2導電型の第3トランジスタ180で構成することができる。典型的には、信号処理部140の第2トランジスタ170と、第3トランジスタ180の双方が信号生成部130の第1トランジスタと異なる構造および特性を有する。図3(a)には第1導電型の第2トランジスタ170を示しており、図3(b)には第2導電型の第3トランジスタ180を示している。導電型が反対になる以外は、第1導電型の第2トランジスタ170と第2導電型の第3トランジスタ180は同様の構造を有することができる。

【0031】

第2トランジスタ170のゲート電極である第2ゲート電極171は、第1導電型のポリシリコンからなることが好ましい。第3トランジスタ180のゲート電極である第3ゲート電極181は、第2導電型のポリシリコンからなることが好ましい。

【0032】

第2ゲート電極171の第1導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度よりも高いことが好ましい。第2ゲート電極171の第1導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度の3/2倍以上であることがより好ましい。また、第2ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗よりも低いことが好ましい。第2ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗の2/3倍以下であることがより好ましい。

【0033】

第3ゲート電極191の第2導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度よりも高いことが好ましい。第3ゲート電極191の第2導電型の不純物濃度が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度の3/2倍以上であることがより好ましい。また、第3ゲート電極191のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗よりも低いことが好ましい。第3ゲート電極171のシート抵抗が、転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗の2/3倍以上であることがより好ましい。なお、典型的に、ポリシリコンのシート抵抗は不純物濃度に反比例する。

【0034】

第2ゲート電極171の第1導電型の不純物濃度と第3ゲート電極181の第2導電型の不純物濃度の少なくとも一方は、1×1021〜1×1022(atoms/cm3)であることが好ましい。転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかの第1導電型の不純物濃度は、1×1021〜1×1022(atoms/cm3)であることが好ましい。第2ゲート電極171と第3ゲート電極181の少なくとも一方のシート抵抗は、1000Ω/□以下であることが好ましく、500Ω/□以下であることより好ましい。転送ゲート電極121、リセットゲート電極1330および増幅ゲート電極1320の少なくともいずれかのシート抵抗は、1000Ω/□以下であることが好ましい。なお、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320、第2ゲート電極171および第3ゲート電極181のシート抵抗は、典型的には10Ω以上である。

【0035】

第2ゲート電極171や第3ゲート電極181の不純物濃度を高くし、抵抗を小さくすることにより、第2トランジスタ170や第3トランジスタ180の安定な動作が可能となる。第2トランジスタ170や第3トランジスタ180は、上述した変換回路142に用いると効果的である。変換回路142は、デジタル回路であるから、その第2ゲート電極171や第2ゲート電極181には、リセットトランジスタ133や転送ゲート120に比べて、周波数の高い電圧信号が入力されるためである。また、高速駆動のため、リセットトランジスタ133のゲート電圧よりも振幅の小さい電圧信号が印加される場合にも効果的である。例えば、リセットトランジスタ133や、増幅回路141、水平走査回路143、垂直走査回路161のトランジスタのゲート電圧の波高値を3.3Vとし、変換回路142のトランジスタのゲート電圧の波高値を1.8Vとする。ゲート電圧の振幅が小さいとトランジスタのわずかな特性ばらつきでも、顕著な影響が出るが、不純物濃度を高くすることにより、特性ばらつきを低減することができる。

【0036】

第2トランジスタ170のゲート絶縁膜172の膜厚が転送ゲート120のゲート絶縁膜122の膜厚よりも薄いことが好ましい。第2トランジスタ170のゲート絶縁膜172の膜厚が第1トランジスタのゲート絶縁膜122の膜厚よりも薄いことが好ましい。

【0037】

本例では、第2トランジスタ170のドレイン175の一部はシリサイド層177で覆われている。第2トランジスタ170のシリサイド層177とドレイン175は接している。ソース174に関しても同様である。また、第2ゲート電極171の上面はシリサイド層176で覆われている。ソース174とドレイン175を覆うシリサイド層177と第2ゲート電極171の上面を覆うシリサイド層176の少なくとも一方を省略することもできる。第3トランジスタ180のソース184、ドレイン185、第3ゲート電極181についても同様である。

【0038】

本例では、図2に示す様に、第2ゲート電極171と第3ゲート電極181とが一体化している。一体的に形成された周辺ゲート電極190が、第1導電型の部分(第2ゲート電極171)と第2導電型の部分(第3ゲート電極181)を有することになる。さらには、周辺ゲート電極190において、第1導電型の部分と第2導電型の部分とがpn接合を成す場合もある。

【0039】

本例では、周辺ゲート電極190の第1導電型の部分から第2導電型の部分に渡って、周辺ゲート電極190の上面をシリサイド層176で覆うことにより、第1導電型の部分と第2導電型の部分をシリサイド層176で短絡している。このようにすることにより、周辺ゲート電極190内に形成されるpn接合によって第2トランジスタ170および第3トランジスタ180の動作が不安定になることを抑制することができる。

【0040】

また、第2トランジスタ170は、第2ゲート電極171の側面に接する、サイドウォールスペーサ173を有している。本例では、サイドウォールスペーサ173は第1誘電体層1731と、第1誘電体層1731と第2ゲート電極171および半導体基板1との間に位置する第2誘電体層1732とを有する2層構造を有している。例えば、第1誘電体層1731は窒化シリコンからなり、第2誘電体層1732は酸化シリコンからなる。第2誘電体層1732の誘電率が第1誘電体層1731の誘電率よりも低いことが好ましいが、逆でもよい。なお、本例では、ゲート絶縁膜172が半導体基板1と第2ゲート電極171との間から、半導体基板1とサイドウォールスペーサ173との間に延在している。しかし、ゲート絶縁膜172を半導体基板1と第2ゲート電極171との間のみに設けて、サイドウォールスペーサ173が半導体基板1と接する形態を採用することもできる。

【0041】

サイドウォールスペーサ173の下には、ドレイン175の低濃度部1752が位置している。低濃度部1752は、ドレイン175の他の部分(高濃度部1751)に比べて第1導電型の不純物濃度が低くなっており、いわゆるLDD(Lightly Doped Drain)構造を有している。サイドウォールスペーサ173およびドレイン175の低濃度部1752を省略することもできる。ソース174に関しても同様に低濃度部と高濃度部を有することができる。第3トランジスタ180に関しても同様に、ドレイン185は、高濃度部1851と低濃度部1852を有することができる。

【0042】

第2トランジスタ170および第3トランジスタ180は、第1中間膜210とは別の第2中間膜240で覆われている。詳細には、第2中間膜240は、第2トランジスタ170のソース174とドレイン175を覆うとともに、サイドウォールスペーサ173に沿って、第2ゲート電極171の上面を覆っている。本例では、第2中間膜240とドレイン175の間には、シリサイド層177が、第2中間膜240と第2ゲート電極171の上面との間にはシリサイド層176が位置している。また、本例では、第2中間膜240と第2ゲート電極171の側面との間にはサイドウォールスペーサ173が位置している。第2中間膜240は、酸化シリコンからなることが好ましい。第2導電型の第3トランジスタ180についても同様である。

【0043】

第2トランジスタ170および第3トランジスタ180は、第3保護膜250で覆われている。詳細には、第3保護膜250は、第2トランジスタ170のソース174とドレイン175を覆うとともに、サイドウォールスペーサ173に沿って、第2ゲート電極171の上面を覆っている。本例では、第3保護膜250とドレイン175との間にはシリサイド層177が、第3保護膜250と第2ゲート電極171の上面との間にはシリサイド層176が位置している。また、本例では、第3保護膜250と第2ゲート電極171の側面との間にはサイドウォールスペーサ173が位置している。第3保護膜250は、窒化シリコンからなることが好ましい。上述したように、第3保護膜250と半導体基板1および第2ゲート電極171との間には、第2中間膜240が設けられている。第3保護膜250は第2中間膜240よりも厚いことが好ましい。

【0044】

絶縁膜310の第1層間絶縁層311および第2層間絶縁層312は、光電変換領域101から周辺回路領域103に延在して半導体基板1を覆っている。本例では、周辺回路領域103の絶縁膜310と半導体基板1および第2ゲート電極171との間に第2中間膜240および第3保護膜250が位置している例を示しているが、第2中間膜240および第3保護膜250の少なくとも一方を省略することもできる。

【0045】

図2、図3(a)に示す様に、第2トランジスタ170のソース174とドレイン175には、第4コンタクトプラグ324と第6コンタクトプラグ326がそれぞれ、シリサイド層177を介して接続されている。同様に、第2ゲート電極171には、第5コンタクトプラグ325がシリサイド層176を介して接続されている。第4コンタクトプラグ324、第5コンタクトプラグ325、第6コンタクトプラグ326はそれぞれ、第3保護膜250および第2中間膜240に接するとともに、これら第3保護膜250および第2中間膜240を貫通している。図2、図3(b)に示す様に、第3トランジスタ180のソース184とドレイン185には、第8コンタクトプラグ328と第9コンタクトプラグ329がそれぞれ、シリサイド層177を介して接続されている。同様に、第3ゲート電極181には、第5コンタクトプラグ325がシリサイド層176を介して接続されている。第8コンタクトプラグ328、第9コンタクトプラグ329はそれぞれ、第3保護膜250および第2中間膜240に接するとともに、これら第3保護膜250および第2中間膜240を貫通している。

【0046】

シリサイド層176を設けることにより、第2ゲート電極171と第5コンタクトプラグ325との接続抵抗を小さくして、第2トランジスタ170の高速駆動が可能となる。シリサイド層177を設けることにより、ドレイン175と第6コンタクトプラグ326との接続抵抗を小さくして、第2トランジスタ170の高速駆動が可能となる。ソース174と第4コンタクトプラグ324についても同様であり、第3トランジスタ180についても同様である。一方、光電変換領域101では、少なくとも転送ゲート電極121の上にはシリサイド層を設けないことが、金属汚染によるノイズを抑制する上で好ましい。

【0047】

図3(a)に示す様に、第1層間絶縁層311の上には、第1配線層331の第4配線3314、第5配線3315、第6配線3316が設けられている。第4〜第6配線はそれぞれ、第4〜第6コンタクトプラグに接続されている。図3(b)に示す様に、第1層間絶縁層311の上には、第1配線層331の第8配線3318、第9配線3319が設けられている。第8配線3318、第9配線は、それぞれ第8コンタクトプラグ328、第9コンタクトプラグ329に接続されている。本例のコンタクトプラグはタングステンからなり、配線はアルミニウムからなるが、これに限定されることはない。

【0048】

図4(a)は、光電変換装置100の第1実施形態の一例を説明する断面模式図である。なお、図4(a)では、簡略化のために、絶縁膜310と半導体基板1との間の保護膜や中間膜、制御膜の構成の記載を省略している。

【0049】

絶縁膜310と複数の配線層(第1配線層331、第2配線層332、第3配線層333、第4配線層334の4層)とで配線構造体300が構成されている。本例では、絶縁膜310は、第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313、第4層間絶縁層314で構成されている。

【0050】

配線構造体300の上にはパッシベーション膜440が設けられている。典型的なパッシベーション膜440は窒化シリコン層を含む。パッシベーション膜の窒化シリコン層の上下には、窒化シリコン層よりも薄い酸窒化シリコン層を設けることが好ましい。

【0051】

パッシベーション膜440の上には樹脂からなる第1平坦化膜460が設けられており、第1平坦化膜460の上面は平坦になっている。第1平坦化膜460の上には、カラーフィルタ470が設けられている。ここでは1つのカラーフィルタを示しているが、光電変換領域101には、原色系あるいは補色系の複数種類の色のカラーフィルタを光電変換部110の配置に応じて規則的に配列してなるカラーフィルタアレイが構成されている。カラーフィルタ470の上には樹脂からなる第2平坦化膜480が設けられており、第2平坦化膜480の上面は平坦になっている。第2平坦化膜480の上には、マイクロレンズ490が設けられている。マイクロレンズ490は反射防止コーティングを含むことができる。ここでは1つのマイクロレンズを示しているが、光電変換領域101には、複数のマイクロレンズが光電変換部110の配置に応じて規則的に配列してなるマイクロレンズアレイ構成されている。

【0052】

図4(b)は、光電変換装置100の第2実施形態の一例を説明する断面模式図である。なお、図4(b)では、簡略化のために、絶縁膜310と半導体基板1との間の保護膜や中間膜の構成の記載を省略している。絶縁膜310と複数の配線層(第1配線層331、第2配線層332の2層)とで配線構造体300が構成されている。本例では、絶縁膜310は、第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313、第4層間絶縁層314、第5層間絶縁層315を含む。また絶縁膜310は第1層間分離層316、第2層間分離層317、第3層間分離層318、第4層間分離層319を含む。各層間絶縁層は酸化シリコンからなることが好ましい。各層間分離層は窒化シリコンからなることが好ましい。層間分離層は配線層の金属材料の拡散を抑制したり、配線層の形成時のエッチングストッパとして機能したりする。層間分離層は層間絶縁層よりも薄いことが好ましい。絶縁膜310に囲まれた導光部材420が設けられている。導光部材420は絶縁膜310の層間絶縁層311〜315の高い屈折率を有しており、層間絶縁層311〜315をクラッド、導光部材420をコアとした光導波路構造をなしている。導光部材420は絶縁膜310の上面に延在しているが、延在しなくてもよい。導光部材420は窒化シリコンからなることが好ましい。

【0053】

導光部材420の上には集光膜430が設けられている。集光膜430の上には層内レンズ450が設けられている。層内レンズ450は反射防止コーティングを有することができる。光電変換領域101には、複数の層内レンズが光電変換部110の配置に応じて規則的に配列されてなる層内レンズアレイが構成されている。層内レンズ450は窒化シリコンからなることが好ましい

集光膜430は、層内レンズ450の屈折率よりも低い屈折率を有する。これにより、層内レンズ450から集光膜430に斜めに入射した光を集光膜430内での屈折により、導光部材420に向けて集光することができる。典型的な集光膜430は酸化シリコン層を含む。集光膜は、酸化シリコン層と導光部材420の間に、酸化シリコン層と導光部材420との間の屈折率を有する中間屈折率層を有することが好ましい。集光膜430は、酸化シリコン層と層内レンズとの間に、酸化シリコン層と層内レンズ450の間の屈折率を有する中間屈折率層を有することが好ましい。これら集光膜430の中間屈折率層は、酸化シリコン層と導光部材420あるいは酸化シリコン層と層内レンズ450との間の反射を抑制することができる。導光部材420や層内レンズ450が窒化シリコンからなる場合、中間屈折率層は酸窒化シリコンからなることが好ましい。中間屈折率層は酸化シリコン層よりも薄いことが好ましい。

【0054】

層内レンズ450の上には、樹脂からなる第1平坦化膜460が設けられており、第1平坦化膜460の上面は平坦になっている。カラーフィルタ470と第2平坦化膜480とマイクロレンズ490の構成は、図4(a)で説明した第1実施形態と同様であるため、説明を省略する。

【0055】

また、カラーフィルタアレイやレンズアレイを、半導体基板1に対して、絶縁膜310とは反対側に配置した、いわゆる裏面照射型の光電変換装置100とすることもできる。

【0056】

以上説明した光電変換装置100を用いて、撮像システムを構築することができる。撮像システムは、例えばスチルカメラやビデオカメラなどのカメラを挙げることができる。また、カメラ機能を有する情報端末も挙げることができる。撮像システムは、信号生成部130で生成された電気信号に基づく画像を処理する画像処理エンジン等の画像処理部および画像を表示する液晶ディスプレイ等の画像表示部の少なくとも一方を備えることができる。

【0057】

以下、本発明の半導体装置の製造方法を説明する。本発明の第1の観点は、信号生成部130が含む第1トランジスタと、信号処理部140が含む第2トランジスタ170に関する。第1の観点に係る製造方法では、第1トランジスタの第1ゲート電極は、第1部材200B,200Cをマスクとして用いて形成され、第2トランジスタ170の第2ゲート電極は第2部材207をマスクとして用いて形成される。さらに、第1部材200B、200Cをマスクとして第1トランジスタのドレインを形成する。この時、第1部材200B、200Cにより、第1ゲート電極への不純物の導入が抑制される。第2部材207を薄くした後に、第2トランジスタ170のドレイン175を形成する。これと同時に、第2トランジスタ170の第2ゲート電極171へイオン注入が行われる。これにより、第1トランジスタと第2トランジスタのそれぞれのゲート電極の不純物濃度を制御することができる。

【0058】

本発明の第2の観点は、転送ゲート120を含む第1トランジスタと、信号処理部140が含む第2トランジスタ170に関する。第2の観点に係る製造方法では、転送ゲート電極121は、第1部材200Aをマスクとして用いて形成され、第2トランジスタ170の第2ゲート電極は第2部材200Dを用いて形成される。そして、第1部材200Aをマスクとして第5半導体領域135を形成する。この時、第1部材200Aにより、転送ゲート電極121への不純物の導入が抑制される。第2部材200Dを薄くした後に、第2トランジスタのドレイン185を形成する。これと同時に、第2トランジスタ170の第2ゲート電極171へイオン注入が行われる。これにより、転送ゲート120と第2トランジスタのそれぞれのゲート電極の不純物濃度を制御することができる。

【0059】

以下、光電変換装置100の製造方法について、図4(a)で示した、第1実施形態の光電変換装置100を例に挙げて詳細に説明する。上述した第1の観点に関して、以下の説明では、上記した第1トランジスタとして主にリセットトランジスタ133を例にしているが、第1トランジスタを増幅トランジスタ132としても同様の製造方法を採用することができる。また、第1トランジスタを、転送ゲート120をゲート、光電変換部110をソース、第5半導体領域135をドレインとみなしても、同様の製造方法を採用することができる。増幅トランジスタ132の特性ばらつきは、固定パターンノイズなどの原因になりうるため、増幅ゲート電極1320上の第1部材200Cは効果的である。また、転送ゲート電極121やリセットゲート電極の不純物濃度が高いと、ポリシリコンの空乏化の影響によるリーク電流が生じやすい。そのため、信号電荷を扱う転送ゲート電極121上の第1部材200Aやリセットゲート電極1330上の第2部材200Bも効果的である。

【0060】

(工程a)本工程を図5(a)を用いて説明する。第1導電型の半導体基板1を用意し、光電変換領域に半導体基板1の第1活性部2Aを画定する分離部3を、周辺回路領域に半導体基板1の第2活性部Bを画定する分離部3を、それぞれ形成する。本例では光電変換領域の分離部と周辺回路領域の分離部がともにSTI構造を有しているが、少なくとも一方がLOCOS構造を有していてもよいし、少なくとも一方が拡散分離構造を有していてもよい。

【0061】

次に、第1活性部2Aへ第2導電型の不純物をイオン注入することにより、第1活性部2Aに第2導電型の第2半導体領域112、第4半導体領域134の少なくとも一部を形成する。また、第2活性部2Bへ第2導電型の不純物をイオン注入することにより、第2活性部2Bに第2導電型のウェル領域178の少なくとも一部を形成する。図5(a)の例では、第2半導体領域112、第4半導体領域134の全部、および、ウェル領域178の全部を形成している。しかし、本工程において、第2半導体領域112、第4半導体領域134の一部及び/又はウェル領域178の一部を形成することができる。そして、工程e以降に、第2半導体領域112、第4半導体領域134の残りの一部及び/又はウェル領域178の残りの一部を形成することもできる。

【0062】

本例では、この工程で、第1活性部2Aに、光電変換部110の蓄積領域となる第1導電型の第1半導体領域111を形成するが、工程e以降に第1半導体領域111を形成することもできる。

【0063】

(工程b)本工程を図5(b)を用いて説明する。第1段階として、半導体基板1の上にゲート絶縁膜122、172用の絶縁膜22を形成する。絶縁膜22の厚みは1〜15nmが好ましい。本例では、まず、シリコンからなる半導体基板1を熱酸化して酸化シリコン膜を形成する。その後に、酸化シリコン膜の、第2トランジスタ170のゲート絶縁膜172に対応する部分を、リセットトランジスタ133のゲート絶縁膜122に対応する部分よりも薄くする。次いで、酸化シリコン膜の表面を酸窒化することにより、酸化シリコン層と酸窒化シリコン層とを有するゲート絶縁膜122、172の絶縁膜22を形成する。絶縁膜22はこのような構造および形成方法に限定されるものではない。リセットトランジスタ133のゲート絶縁膜122と第2トランジスタ170用のゲート絶縁膜172とが同じ厚みであってもよいし、酸化シリコン膜を酸窒化せずに、絶縁膜22を酸化シリコン層の単層膜としてもよい。また、リセットトランジスタ133のゲート絶縁膜122と第2トランジスタのゲート絶縁膜172とを、厚みが異なるように別々に形成してもよい。また、酸化ハフニウム等のhigh−k材料を半導体基板上に堆積することによりゲート絶縁膜を形成してもよい。

【0064】

次に、第2段階として、絶縁膜22の上にポリシリコン膜21を形成する。ポリシリコン膜21の厚みは50〜500nmが好ましい。本例では、ノンドープポリシリコンを堆積してポリシリコン膜21を形成している。パターニングされた第1フォトレジストをマスクとして用いて、ポリシリコン膜21の転送ゲート電極121、リセットゲート電極1330および第2ゲート電極171に対応する部分に第1導電型の不純物をイオン注入する。第1フォトレジストを除去する。パターニングされた第2フォトレジストをマスクとして用いて、ポリシリコン膜21の第3ゲート電極181に対応する部分に第2導電型の不純物をイオン注入する。本工程での各イオン注入のドーズ量を1×1015〜1×1016(ions/cm2)、より好ましくは、1×1015〜6×1015(ions/cm2)とするとよい。また、各イオン注入による、ポリシリコン膜21の不純物濃度は、1×1021〜1×1022(atoms/cm3)であることが好ましい。

【0065】

なお、ドープトポリシリコンを堆積してポリシリコン膜21を形成することもでき、上記した不純物濃度と同程度となるようにポリシリコン膜21を成膜することができる。しかし、第3ゲート電極181に対応する部分は、第2導電型にすることが好ましいため、ドープトポリシリコンよりもノンドープポリシリコンを堆積することが好ましい。

【0066】

次に、第3段階として、ポリシリコン膜21の上に絶縁膜20を形成する。絶縁膜20の材料に無機絶縁材料を用いて、絶縁膜20を無機絶縁膜とすることが好ましい。その場合、絶縁膜20の材料には酸化シリコン、酸窒化シリコン、窒化シリコン、炭化シリコンなどのシリコン化合物を用いることができる。なお、絶縁膜20の材料に一般的なフォトレジストよりも耐薬品性や耐熱性の高いポリイミドなどの有機絶縁材料を用いて、絶縁膜20を有機絶縁膜とすることもできる。絶縁膜20は多層膜であってもよい。絶縁膜20の厚みは、ポリシリコン膜21の厚みよりも小さいことが好ましく、ポリシリコン膜21の厚みの1/2以下であることがより好ましい。典型的には、絶縁膜20の厚みは10〜100nmである。図2に、転送ゲート電極121の長さLと幅Wを示している。各ゲート電極の長さは、トランジスタのゲート長が定義される方向におけるゲート電極の長さであり、各ゲート電極の幅はトランジスタのゲート幅が定義される方向におけるゲート電極の幅である。第1部材200A,200B、200Cおよび第2部材207の厚みは、ゲート電極の長さ(L)よりも小さいことが好ましい。上記したポリシリコン膜21への不純物の導入は、絶縁膜20の形成前に行うことが好ましいが、絶縁膜20を介したイオン注入によって行うこともできる。この場合のイオン注入は、絶縁膜20をイオンが透過できるだけの十分に高い注入エネルギーが必要となる。

【0067】

次に、第4段階として、絶縁膜20の上にパターニングされた第3フォトレジストを形成する。第3フォトレジストは、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320、第2ゲート電極171、第3ゲート電極181のレイアウトに応じてパターニングされている。図5(b)では、転送ゲート電極121に対応する第3フォトレジスト24A、リセットゲート電極1330に対応する第3フォトレジスト24B、第2ゲート電極171に対応する第3フォトレジスト24Dを示している。増幅ゲート電極1320に対応する第3フォトレジストと、第3ゲート電極181に対応する第3フォトレジストも同時に形成することができる。

【0068】

(工程c)本工程を図5(c)を用いて説明する。パターニングされた第3フォトレジスト24A,24B、24Dをマスクとして、絶縁膜20のエッチングを行うことにより、絶縁膜20をパターニングする。エッチングは、ドライエッチングが好ましい。これにより、絶縁膜20から、転送ゲート電極121のレイアウトに応じて配置された第1部材200Aが得られる。リセットゲート電極1330のレイアウトに応じて配置された第1部材200Bが得られる。第2ゲート電極171のレイアウトに応じて配置された第2部材207が得られる。同時に、増幅ゲート電極1320のレイアウトに応じて配置された第1部材200C(不図示)と、第3ゲート電極181のレイアウトに応じて配置された第2部材(不図示)も得ることができる。図2を用いて説明したように、本例の第2ゲート電極181と第3ゲート電極181は一体化している。そのため、第2ゲート電極171のレイアウトに応じて配置された第2部材207が、第3ゲート電極181のレイアウトに応じて配置された第2部材と一体的に形成される。

【0069】

(工程d)本工程を図6(d)を用いて説明する。ポリシリコン膜21の上に設けられた第1部材200A,200B、200Cをマスクとして、ポリシリコン膜21のエッチングを行うことにより、ポリシリコン膜21をパターニングする。ポリシリコン膜21の上に設けられた第2部材207をマスクとして、ポリシリコン膜21のエッチングを行うことにより、ポリシリコン膜21をパターニングする。これにより、第1部材200A,200Bの形状に応じた平面形状を有する転送ゲート電極121、リセットゲート電極1330をそれぞれ形成する。また、第2部材207の形状に応じた平面形状を有する第2ゲート電極171を形成する。同時に、増幅ゲート電極1320、第3ゲート電極181も形成することができる。なお本例では、図2に示す様に、第2ゲート電極171と第3ゲート電極181が周辺ゲート電極190として、一体的に形成される。工程aで説明したように、周辺ゲート電極190の第2ゲート電極171に対応する部分は第1導電型になっており。第3ゲート電極181に対応する部分は第2導電型になっている。そのため、周辺ゲート電極190が、第1導電型の部分(第2ゲート電極に対応する部分)と第2導電型の部分(第3ゲート電極に対応する部分)を有することになる。さらには、第1導電型の部分と第2導電型の部分とがpn接合を成す場合もある。

【0070】

工程cで用いた第3フォトレジスト24A,24B,24Cは、ポリシリコン膜21のパターニングに先立って除去しておくことが好ましい。しかし、第3フォトレジスト24A,24Bと第1部材200A,200B及び/又はフォトレジスト24Cと第2部材207をマスクとしてポリシリコン膜21のエッチングを行ってもよい。転送ゲート電極121、リセットゲート電極1330の形成と、第2ゲート電極171の形成とを同時に行うことが好ましい。本工程では、少なくとも絶縁膜22の、ゲート電極121と半導体基板1との間の部分からの延在部を露出させる。絶縁膜22の延在部を薄くしてもよく、さらには絶縁膜22の延在部を完全に除去して半導体基板1を露出させてもよい。

【0071】

(工程e)本工程を図6(e)を用いて説明する。第2トランジスタ170以外の部分を第4フォトレジスト(不図示)で覆う。そして、第2部材207および第2ゲート電極171を半導体基板1に対するマスクとして、半導体基板1の第2活性部2Bへ第2導電型の不純物のイオン注入を行うことにより、第2トランジスタ170のドレイン175の低濃度部1752を形成する。低濃度部1752は、いわゆるLDD(Lightly Dopede Draind)として機能する。同時に、第2トランジスタ170のソース174の低濃度部1742も形成することができる。第4フォトレジストを除去する。

【0072】

リセットトランジスタ133以外の部分を第5フォトレジスト(不図示)で覆う。そして、第1部材200Bおよびリセットゲート電極1330を半導体基板1に対するマスクとして、第1活性部2Bへ第1導電型の不純物をイオン注入を行う。これにより、リセットトランジスタ133のドレイン1332を形成する。同時に、リセットトランジスタ133のソースであり、浮遊拡散領域として機能する第5半導体領域135も形成することができる。第5フォトレジストを除去する。

【0073】

光電変換部110以外の部分を第6フォトレジスト(不図示)で覆う。そして、第1活性部2Aへ第2導電型の不純物のイオン注入を行うことにより、光電変換部の表面保護領域となる、第3半導体領域133を形成する。第6フォトレジストを除去する。

【0074】

第3トランジスタ180以外の部分を第7フォトレジスト(不図示)で覆う。そして、第2部材207および第3ゲート電極181を半導体基板1に対するマスクとして、第2活性部2Bへ第2導電型の不純物のイオン注入を行う。これにより、第3トランジスタ180のドレイン185の低濃度部1852(LDD:Lightly Dpoede Draind)を形成する。同時に、第3トランジスタ180のソース184の低濃度部も形成することができる。第7フォトレジストを除去する。

【0075】

典型的には、本工程での各イオン注入のドーズ量を1×1013〜1×1014(ions/cm2)とする。第1部材200A,200B、200C、第2部材207をマスクとして用いることから、各イオン注入の注入エネルギーは、第1部材200A,200B、200C、第2部材207をイオンが実質的に透過しない程度にする必要があることはいうまでもない。半導体基板1の表面の近傍に形成される低濃度部1752、1852や、第5半導体領域135、第3半導体領域133を形成するために必要な注入エネルギーは、各トランジスタの特性に応じて決定される。したがって、マスクとして機能しうる第1部材200A,200B、200C、第2部材207の厚みは、この注入エネルギーによって適宜決定すればよい。なお、ドレイン175の低濃度部1752の形成段階と、ドレイン1332の形成段階と、第3半導体領域113の形成段階と、ドレイン175の低濃度部1852の形成段階とを、この順で有することに限定されるものではない。

【0076】

(工程f)本工程を図6(f)を用いて説明する。光電変換領域および周辺回路領域を覆う酸化シリコン膜1210を形成する。この酸化シリコン膜1210の厚みは第1部材200A,200B、200Cおよび第2部材207の厚みより小さいことが好ましく、典型的には1〜30nmとする。酸化シリコン膜の上に光電変換領域および周辺回路領域を覆う窒化シリコン膜1220を形成する。この窒化シリコン膜1220の厚みは酸化シリコン膜1210の厚みよりも大きいことが好ましく、典型的には10nm〜100nmとする。

【0077】

(工程g)本工程を図7(g)を用いて説明する。本工程において、第2部材207を薄くする。第2部材207は第1部材200A、200B、200Cよりも薄くされることが好ましい。第2部材207を完全に除去してしまってもよい。具体的には、まず、光電変換間領域を第8フォトレジスト500gで覆う。そして、第8フォトレジスト500gをマスクとして、第2部材207上に位置する窒化シリコン膜1220、酸化シリコン膜1210を順次エッチングし、さらに第2部材207をエッチングする。第2部材207のエッチングは、第2部材208が薄く残る時点で終了してもよいし、第2部材207が完全に除去されて第2ゲート電極171が露出するまで行ってもよい。第1部材200A,200B,200Cを薄くしてもよいし、第1部材200A,200B,200Cを完全に除去してリセットゲート電極1330等の上面を露出させてもよいが、薄くしないことが好ましい。

【0078】

本工程において、第2部材207のエッチングと同時に、第2トランジスタ170のサイドウォールスペーサ173を形成することができる。本例のサイドウォールスペーサ173は、窒化シリコン膜1220の一部である第1誘電体層1731と、酸化シリコン膜1210の一部である第2誘電体層1732との2層構造を有している。第2誘電体層1732が第1誘電体層1731と第2ゲート電極171の側面との間に位置する。窒化シリコン膜1220と酸化シリコン膜1210を用いることにより、第2誘電体層1732の誘電率は第1誘電体層1731の誘電率よりも低くなる。なお、工程fにおいて、酸化シリコン膜1210と窒化シリコン膜1220の上下関係を逆にすることもでき、その場合には、第2誘電体層1732の誘電率は第1誘電体層1731の誘電率よりも高くなる。なお、第2トランジスタ170のサイドウォールスペーサ173の形成と同時に、第3トランジスタ180のサイドウォールスペーサ173も形成することができる。なお、ドレインの低濃度部1742やサイドウォールスペーサ135を形成しない場合には、工程eと工程dの間に第2部材207を薄くすることもできる。

【0079】

(工程h)本工程を図7(h)を用いて説明する。光電変換領域および第3トランジスタ180を覆い、第2トランジスタ170を覆わない第9フォトレジスト500hを形成する。第2ゲート電極171をマスクとして、半導体基板1の第2活性部2Bに第1導電型の不純物をイオン注入する。これにより、第2トランジスタ170のドレイン175の高濃度部1751を形成する。これにより、工程eで説明した低濃度部1752と、本工程で形成される高濃度部1751とを有する、第2トランジスタ170のドレイン175が形成される。同時に、第2トランジスタ170のソース174の高濃度部1741も形成でき、第2トランジスタ170のソース174が形成される。上述したように、工程gにて第2部材208が薄くなっているか、第2部材208が存在せずに第2ゲート電極171が露出している。そのため、高濃度部1751の形成(ドレイン175の形成)のためのイオン注入と同時に、第2ゲート電極171へも不純物が導入される。このイオン注入は、第9フォトレジスト500hで覆われた転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の第1導電型の不純物濃度よりも、第2ゲート電極171の不純物濃度が高くなるように行うことが好ましい。典型的には、本工程でのドレイン175の形成のためのイオン注入のドーズ量を1×1015〜1×1016(ions/cm2)とする。より好ましくは、1×1015〜6×1015(ions/cm2)である。典型的には、ドレイン175形成のためのイオン注入のドーズ量は、工程eにおけるイオン注入のドーズ量の10〜1000倍である。このような転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の不純物濃度は、先の工程bで説明した、ポリシリコン膜21の不純物濃度によって実質的に規定される。これは、工程eでは、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の上には、第1部材200A,200B,200Cが設けられているためである。すなわち、第5半導体領域135やドレイン1332、ソース1321、ドレイン1322の形成のためのイオン注入では、第1部材200A,200B,200Cがゲート電極に対するマスクとして機能する。つまり、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320には実質的にイオン注入がされないためである。そのため、本工程でのイオン注入により、第2ゲート電極171の不純物濃度を、転送ゲート電極121、リセットゲート電極1330、増幅ゲート電極1320の不純物濃度よりも高くすることができる。当然、イオン注入の注入エネルギーは、ドレイン175の形成に必要なように設定される。また、工程gは第2部材208の厚みは、ドレイン175の形成に必要な注入エネルギーによって、第2ゲート電極171にイオン注入が可能となる程度に設定することができる。

【0080】

また、光電変換領域および第2トランジスタ170を覆い、第3トランジスタ180を覆わない第10フォトレジスト(不図示)を形成する。第2トランジスタ170と同様にして、第3ゲート電極181に第2導電型の不純物をイオン注入する。また、第3トランジスタのドレイン185の高濃度部1851、ソース184の高濃度部1841を形成する。典型的には、本工程でのドレイン185の形成のためのイオン注入のドーズ量を1×1015〜1×1016(ions/cm2)とする。より好ましくは、1×1015〜6×1015(ions/cm2)である。

【0081】

以上の工程により、転送ゲート120及び各トランジスタの動作に影響するイオン注入は完了する。

【0082】

(工程i)本工程を図7(i)を用いて説明する。光電変換領域および周辺回路領域に酸化シリコン膜を形成する。酸化シリコン膜の上に光電変換領域を覆い、周辺回路領域を覆わない第11フォトレジスト(不図示)を形成する。第11フォトレジストをマスクとして酸化シリコン膜をエッチングすることにより、第2トランジスタ170の第2ゲート電極171の上面を露出させる。なお、工程gにおいて、第2部材207が完全に除去されずに第2部材208として第2ゲート電極171上に残る場合には、本工程で、第2部材208をエッチングすることにより第2ゲート電極181の上面を露出させる。第11フォトレジストを除去する。これにより第11フォトレジストで覆われていた光電変換領域に、酸化シリコン膜の一部として第2保護膜230が形成される。そして、コバルトやチタン、ニッケル、タングステン等のシリサイド化し得る金属材料からなる金属膜700を第2トランジスタ170の第2ゲート電極171の上面およびソース174およびドレイン175に接するように形成する。また、金属膜700は第3トランジスタ180の第3ゲート電極181の上面およびソース174、ドレイン175に接するように形成される。なおこの時、金属膜700は光電変換領域にも形成されるが、金属膜700とリセットトランジスタ133の間には、第1保護膜220や第2保護膜230が位置しており、金属膜700とリセットトランジスタ133や転送ゲート電極121は接しない。

【0083】

(工程j)本工程を図8(j)を用いて説明する。半導体基板1を加熱して、金属膜700と第2ゲート電極171とを熱反応させ、第2ゲート電極171の上面をシリサイド化することにより、第2ゲート電極171の上にシリサイド層176を形成する。同時に、金属膜700と第2トランジスタ170のソース174とドレイン175もシリサイド化することができ、ソース174とドレイン175の上にシリサイド層177を形成することができる。第3トランジスタ180も同様に、シリサイド化することができる。その後、光電変換領域に位置する未反応の金属膜700を除去する。その後、シリサイド層177、176をさらに加熱して、シリサイド層177、176を低抵抗化することもできる。

【0084】

(工程k)本工程を図8(k)を用いて説明する。光電変換領域および周辺回路領域を覆い、サイドウォールスペーサ173、及びシリサイド層176、177に接する酸化シリコン膜を形成する。ついで、光電変換領域および周辺回路領域を覆う窒化シリコン膜をこの酸化シリコン膜の上に形成し、当該窒化シリコン膜の光電変換領域に位置する部分を除去することにより、周辺回路領域に第3保護膜250を形成する。さらに酸化シリコン膜の光電変換領域に位置する部分を除去することにより、周辺回路領域に第2中間膜240を形成する。

【0085】

(工程l)本工程を図8(l)を用いて説明する。光電変換領域を覆い、第2保護膜230に接する第3中間膜260を形成する。なお、この第3中間膜260を、工程kで説明した酸化シリコン膜の光電変換領域に位置する部分を除去せずに、光電変換領域に残すことにより、第2中間膜240と同時に形成することもできる。また、第3中間膜260の形成を図3(a)、(b)のように省略してもよい。

【0086】

光電変換領域および周辺回路領域を覆う絶縁膜を形成し、当該絶縁膜を平坦化することにより、第1層間絶縁層311を形成する。平坦化の手法は、リフロー法、エッチバック法、CMP(Chemical Mecanical Polishing)法などを用いることができる。絶縁膜の材料としては、酸化シリコンや、BSG、PSG、BPSGなどの珪酸塩ガラスを用いることができる。

【0087】

次に、コンタクトを形成する。第1段階として、第1層間絶縁層311に、転送ゲート電極121に達する第1コンタクトホールを形成する。そして、第1コンタクトホールにタングステン等の導電材料を埋め込み、CMP法により余分なタングステンを除去して、転送ゲート電極121に接続する第1コンタクトプラグ321を形成する。同時に、第2コンタクトプラグ322、第3コンタクトプラグ323、第7コンタクトプラグ327、およびシェアードコンタクトプラグ320を形成する。シェアードコンタクトプラグ320は、第5半導体領域135と増幅ゲート電極1320の双方に接続するように形成される。第1コンタクトプラグ、第2コンタクトプラグ322および第7コンタクトプラグ327は、それぞれ、第1部材200A,200B,200Cを貫通して設けられる。しかし、工程f〜工程hにおいて、第1部材200A,200B,200Cを除去することもできる。

【0088】

続いて、第2段階として、第1層間絶縁層311に、第1ゲート電極171上のシリサイド層176に達する第5コンタクトホールを形成する。そして、第5コンタクトホールにタングステン等の導電材料を埋め込み、CMP法により余分なタングステンを除去して、シリサイド層176を介して第2ゲート電極171に接続する第5コンタクトプラグ325を形成する。第5コンタクトプラグ325は、シリサイド層177を貫通して第2ゲート電極171に接続してもよいが、シリサイド層177の上面に接することが好ましい。同時に、第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、および第9コンタクトプラグ329を形成する。第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、および第9コンタクトプラグ329は、それぞれシリサイド層177の上面に接して設けられる。なお、第3保護膜250は、第4コンタクトプラグ324、第6コンタクトプラグ326、第8コンタクトプラグ328、第9コンタクトプラグの形成のための各コンタクトホールの形成時のエッチングストッパとして機能する。つまり、第3保護膜250により、いわゆるセルフアラインコンタクトを実現することができる。なお上述した第1段階と第2段階の順序が逆であってもよい。

【0089】

光電変換領域に設けられるコンタクトプラグと、周辺回路領域に設けられるコンタクトプラグとを同時に形成することもできる。しかし、このように、光電変換領域に設けられるコンタクトプラグと、周辺回路領域に設けられるコンタクトプラグとを互いに異なるタイミングで別々に形成することが好ましい。これは、周辺回路領域にコンタクトホールを形成する際に飛散し得る、シリサイド層176、177に含まれる金属成分(コバルト等)が、光電変換領域での金属汚染の原因となる可能性を低減できるためである。

【0090】

コンタクトプラグの形成後、配線層を形成する。本実施形態では、配線層の主たる材料としてアルミニウムを用いている。第1層間絶縁層の上にアルミニウム膜を形成後、アルミニウム膜を適当にパターニングして、第1配線層を形成することができる。

【0091】

工程lの後は、周知の多層配線技術を用いて、各配線層331〜334および各層間絶縁層312〜315を形成して、配線構造体300を形成することができる。そして、配線構造体300の上に、パッシベーション膜440、第1平坦化膜460、カラーフィルタ470、第2平坦化膜480、マイクロレンズ490を形成することで、図4(a)に示した第1実施形態の光電変換装置100を得ることができる。

【0092】

次に、図4(b)で示した、第2実施形態の光電変換装置100の製造方法の一例を説明する。本実施形態は、第1実施形態の光電変換装置100の製造方法における工程kまでは同様に行えるため、説明を省略し、工程kの後に行われる工程m〜oについて説明する。

【0093】

(工程m)本工程を図9(m)を用いて説明する。工程lでは、酸化シリコン膜の光電変換領域に位置する部分を除去したが、本工程では、酸化シリコン膜を光電変換領域に残すことにより、周辺回路領域の第2中間膜240と、光電変換領域の第3中間膜260とを同時に形成する。また、工程lでは、窒化シリコン膜の光電変換領域に位置する部分を全て除去しているのに対して、本工程では、窒化シリコン膜の光電変換部110上に位置する部分を残している。窒化シリコン膜が光電変換部110上に残されて制御膜410となり、周辺回路領域に残されて第3保護膜250となる。

【0094】

(工程n)本工程を図9(n)を用いて説明する。コンタクトプラグの形成は工程lと同様に行うことができる。コンタクトプラグの形成後、第1配線層331を形成する。本実施形態では、第1配線層331の主たる材料として銅を用いている。第1層間絶縁層311の上に窒化シリコンからなる第1層間分離層316を介して第2層間絶縁層312を形成後、ダマシン法により第2層間絶縁層312に銅からなる第1配線層331を埋め込むことができる。同様にして周知の多層配線技術を用いて、第2配線層332及び、各層間絶縁層313〜315、各層間分離層317〜319を形成して、配線構造体300を形成することができる。その後、配線構造体300の絶縁膜310を部分的にエッチングして、制御膜410に達する深さの開口部421を設ける。制御膜410は、開口部421の形成時のエッチングストッパとして用いることができる。

【0095】

(工程o)本工程を図9(o)を用いて説明する。開口部421に、絶縁膜310の屈折率よりも高い屈折率を有する、窒化シリコン等からなる高屈折率膜を埋め込み、導光部材420を形成する。本例では、導光部材420の屈折率が、絶縁膜310の第1層間絶縁層311、第2層間絶縁層312、第3層間絶縁層313の屈折率よりも高い。導光部材420は開口部421内から絶縁膜310の上面上に延在させることが好ましい。導光部材420の上面をCMP法等に平坦化する。制御膜410は、導光部材420の埋め込み時の、光電変換部110へのダメージを緩和する機能を有し得る。

【0096】

そして、導光部材420の上に、集光膜430、層内レンズ450、第1平坦化膜460、カラーフィルタ470、第2平坦化膜480、マイクロレンズ490を形成することで、図4(b)に示した第2実施形態の光電変換装置100を得ることができる。

【0097】

以上説明したように、本発明に係る半導体装置の製造方法によれば、第1トランジスタのゲート電極の不純物濃度と、第2トランジスタの不純物濃度を好適に制御することが可能となる。なお、半導体装置として、光電変換部を備えた光電変換装置を例に挙げたが、光電変換部を備えない半導体装置の製造方法にも適用が可能である。例えば、アナログ回路とデジタル回路が混在した半導体装置や、高電圧を扱う回路と低電圧を扱う回路とが混在した半導体装置にも適用することができる。

【0098】

本発明は説明に用いた例のみに限定されることはなく、明細書に記載した技術的思想に基づき、構成の変形や変更、置換、削除、追加を適宜行うことができる。

【符号の説明】

【0099】

110 光電変換部

120 転送ゲート

121 転送ゲート電極

130 信号生成部

132 増幅トランジスタ(第1トランジスタ)

1320 増幅ゲート電極

133 リセットトランジスタ(第1トランジスタ)

1330 リセットゲート電極

1332 ドレイン

135 第5半導体領域

140 信号処理部

170 第2トランジスタ

173 サイドウォールスペーサ

180 第3トランジスタ

200A 第1部材

200B 第1部材

200C 第1部材

207 第2部材

1 半導体基板

21 ポリシリコン膜

20 絶縁膜

【特許請求の範囲】

【請求項1】

第1トランジスタと、第2トランジスタと、を備える半導体装置の製造方法であって、

半導体基板を覆うポリシリコン膜の上に設けられた絶縁膜をパターニングすることにより、前記ポリシリコン膜の上に前記絶縁膜から第1部材および第2部材を形成する第1工程と、

前記第1部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第1トランジスタのゲート電極を形成し、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第2トランジスタのゲート電極を形成する第2工程と、

前記第1部材を前記第1トランジスタの前記ゲート電極に対するマスクとし、前記第1トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして、前記半導体基板へイオン注入を行うことにより、前記第1トランジスタのドレインを形成する第3工程と、

前記第2部材を薄くする第4工程と、

前記第4工程の後に、前記第2トランジスタのゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタのドレインを形成するとともに、前記第2トランジスタの前記ゲート電極の不純物濃度が、前記第1トランジスタの前記ゲート電極の不純物濃度と異なるように、前記第2トランジスタの前記ゲート電極へイオン注入を行う第5工程を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第5工程における前記イオン注入により、前記第2トランジスタの前記ゲート電極の不純物濃度を前記第1トランジスタの前記ゲート電極の不純物濃度の3/2倍以上にする、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1工程は、前記ポリシリコン膜へ不純物を導入する段階と、前記不純物が導入された前記ポリシリコン膜の上に前記絶縁膜を形成する段階と、を含む、請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第5工程の後に、前記第2トランジスタの前記ゲート電極の上面と前記第2トランジスタのドレインの表面の少なくとも一方をシリサイド化する第6工程を有する、請求項1乃至3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記第4工程の前に、前記第2トランジスタの前記ゲート電極をマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタの前記ドレインの低濃度部を形成し、

前記第4工程において、前記第2部材を薄くすると同時に、前記第2トランジスタのサイドウォールスペーサを形成し、

前記第5工程において、前記サイドウォールスペーサおよび前記第2トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタの前記ドレインの前記低濃度部より高い不純物濃度を有する高濃度部を形成する、請求項1乃至4のいずれか一項に記載の半導体装置の製造方法。

【請求項6】

前記第2トランジスタと反対導電型の第3トランジスタを含む半導体装置の製造方法であって、

前記第2工程において、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記第3トランジスタのゲート電極と前記第2トランジスタの前記ゲート電極とを一体的に形成する、請求項1乃至5のいずれか一項に記載の半導体装置の製造方法。

【請求項7】

前記第1部材に接するとともに前記第1トランジスタの前記ゲート電極に接続するコンタクトプラグを形成する段階と、前記第2トランジスタの前記ゲート電極に接続するコンタクトプラグを形成する段階と、を含む第7工程を有する、請求項1乃至6のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置は、光電変換部と、前記光電変換部で生じた信号電荷に基づく電気信号を生成する信号生成部と、前記電気信号を処理する信号処理部と、を備え、前記信号生成部が前記第1トランジスタを含み、前記信号処理部が前記第2トランジスタを含む、請求項1乃至7のいずれか一項に記載の半導体装置の製造方法。

【請求項9】

下記の要件(a)および(b)の少なくとも一方を満たす、請求項8に記載の半導体装置の製造方法。

(a)前記第1トランジスタは、前記信号電荷の量に応じたゲート電圧が加わる増幅トランジスタである。

(b)前記第1トランジスタは、前記電気信号の量に応じたゲート電圧が加わる増幅トランジスタの前記ゲート電圧をリセットするリセットトランジスタであり、前記第2トランジスタは、前記リセットトランジスタの前記ゲート電圧よりも振幅の小さい電圧信号及び/又は周波数の高い電圧信号が印加されるゲートを有する。

【請求項10】

前記半導体装置は、光電変換部と、前記光電変換部で生じた信号電荷に基づく電気信号を生成する信号生成部と、前記信号電荷を前記光電変換部から前記信号生成部へ転送する転送ゲートと、前記電気信号を処理する信号処理部と、を備え、

前記転送ゲートが前記第1トランジスタのゲートであり、前記光電変換部が前記第1トランジスタのソースであり、前記信号生成部の半導体領域が前記第1トランジスタのドレインであり、前記信号処理部が前記第2トランジスタを含む、請求項1乃至7のいずれか一項に記載の半導体装置の製造方法。

【請求項11】

前記第1工程の前に、前記光電変換部の、前記信号電荷と同極性の電荷を多数キャリアとする半導体領域を形成する工程を有し、前記第4工程を前記第3工程の後に行う、請求項9乃至10のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

第1トランジスタと、第2トランジスタと、を備える半導体装置の製造方法であって、

半導体基板を覆うポリシリコン膜の上に設けられた絶縁膜をパターニングすることにより、前記ポリシリコン膜の上に前記絶縁膜から第1部材および第2部材を形成する第1工程と、

前記第1部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第1トランジスタのゲート電極を形成し、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記ポリシリコン膜から前記第2トランジスタのゲート電極を形成する第2工程と、

前記第1部材を前記第1トランジスタの前記ゲート電極に対するマスクとし、前記第1トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして、前記半導体基板へイオン注入を行うことにより、前記第1トランジスタのドレインを形成する第3工程と、

前記第2部材を薄くする第4工程と、

前記第4工程の後に、前記第2トランジスタのゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタのドレインを形成するとともに、前記第2トランジスタの前記ゲート電極の不純物濃度が、前記第1トランジスタの前記ゲート電極の不純物濃度と異なるように、前記第2トランジスタの前記ゲート電極へイオン注入を行う第5工程を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第5工程における前記イオン注入により、前記第2トランジスタの前記ゲート電極の不純物濃度を前記第1トランジスタの前記ゲート電極の不純物濃度の3/2倍以上にする、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1工程は、前記ポリシリコン膜へ不純物を導入する段階と、前記不純物が導入された前記ポリシリコン膜の上に前記絶縁膜を形成する段階と、を含む、請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第5工程の後に、前記第2トランジスタの前記ゲート電極の上面と前記第2トランジスタのドレインの表面の少なくとも一方をシリサイド化する第6工程を有する、請求項1乃至3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記第4工程の前に、前記第2トランジスタの前記ゲート電極をマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタの前記ドレインの低濃度部を形成し、

前記第4工程において、前記第2部材を薄くすると同時に、前記第2トランジスタのサイドウォールスペーサを形成し、

前記第5工程において、前記サイドウォールスペーサおよび前記第2トランジスタの前記ゲート電極を前記半導体基板に対するマスクとして前記半導体基板へイオン注入を行うことにより、前記第2トランジスタの前記ドレインの前記低濃度部より高い不純物濃度を有する高濃度部を形成する、請求項1乃至4のいずれか一項に記載の半導体装置の製造方法。

【請求項6】

前記第2トランジスタと反対導電型の第3トランジスタを含む半導体装置の製造方法であって、

前記第2工程において、前記第2部材をマスクとして前記ポリシリコン膜をパターニングすることにより、前記第3トランジスタのゲート電極と前記第2トランジスタの前記ゲート電極とを一体的に形成する、請求項1乃至5のいずれか一項に記載の半導体装置の製造方法。

【請求項7】

前記第1部材に接するとともに前記第1トランジスタの前記ゲート電極に接続するコンタクトプラグを形成する段階と、前記第2トランジスタの前記ゲート電極に接続するコンタクトプラグを形成する段階と、を含む第7工程を有する、請求項1乃至6のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置は、光電変換部と、前記光電変換部で生じた信号電荷に基づく電気信号を生成する信号生成部と、前記電気信号を処理する信号処理部と、を備え、前記信号生成部が前記第1トランジスタを含み、前記信号処理部が前記第2トランジスタを含む、請求項1乃至7のいずれか一項に記載の半導体装置の製造方法。

【請求項9】

下記の要件(a)および(b)の少なくとも一方を満たす、請求項8に記載の半導体装置の製造方法。

(a)前記第1トランジスタは、前記信号電荷の量に応じたゲート電圧が加わる増幅トランジスタである。

(b)前記第1トランジスタは、前記電気信号の量に応じたゲート電圧が加わる増幅トランジスタの前記ゲート電圧をリセットするリセットトランジスタであり、前記第2トランジスタは、前記リセットトランジスタの前記ゲート電圧よりも振幅の小さい電圧信号及び/又は周波数の高い電圧信号が印加されるゲートを有する。

【請求項10】

前記半導体装置は、光電変換部と、前記光電変換部で生じた信号電荷に基づく電気信号を生成する信号生成部と、前記信号電荷を前記光電変換部から前記信号生成部へ転送する転送ゲートと、前記電気信号を処理する信号処理部と、を備え、

前記転送ゲートが前記第1トランジスタのゲートであり、前記光電変換部が前記第1トランジスタのソースであり、前記信号生成部の半導体領域が前記第1トランジスタのドレインであり、前記信号処理部が前記第2トランジスタを含む、請求項1乃至7のいずれか一項に記載の半導体装置の製造方法。

【請求項11】

前記第1工程の前に、前記光電変換部の、前記信号電荷と同極性の電荷を多数キャリアとする半導体領域を形成する工程を有し、前記第4工程を前記第3工程の後に行う、請求項9乃至10のいずれか一項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−84740(P2013−84740A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−223290(P2011−223290)

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]