半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

リセス構造のトランジスタ(以後、「RCAT」(Recessed Channel Transistor)ともいう。)は、ゲート電極の一部が、半導体基板に形成された溝の内部に埋め込まれている。RCATにおいては、溝の内面に形成された絶縁膜がゲート絶縁膜となり、半導体基板の溝に沿った領域がチャネルを構成する。ゲート電極の一部が埋め込まれる溝は、半導体基板に反応性イオンエッチング(RIE:reactive ion etching)を施すことによって形成されるが、溝の形状にバラツキが生じると、RCATの電気的特性が低下する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−231945号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、電気的特性が良好な半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

【図面の簡単な説明】

【0006】

【図1】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図2】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図3】(a)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図4】(a)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図5】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、図4(b)に示すA−A’線による断面図であり、(b)は、図4(b)に示すB−B’線による断面図であり、(c)は、図4(b)に示すC−C’線による断面図である。

【図6】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)及び(c)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図であり、(c)は、(a)に示すC−C’線による断面図である。

【図7】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図8】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図9】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図10】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図11】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

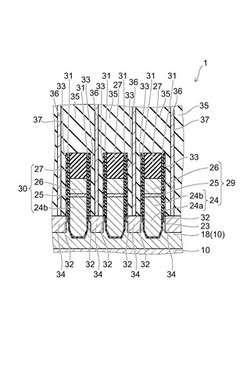

【図14】第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図15】第1の実施形態に係る半導体装置の製造方法において、溝を例示する断面図である。

【図16】第1の実施形態の変形例に係る半導体装置の製造方法において、溝を例示する断面図である。

【図17】(a)及び(b)は、第1の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図18】第1の実施形態の比較例に係る半導体装置の製造方法において、溝を例示する断面図である。

【図19】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図20】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図21】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図22】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図23】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図24】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【発明を実施するための形態】

【0007】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

図1〜図4は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図5(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、図4(b)に示すA−A’線による断面図であり、(b)は、図4(b)に示すB−B’線による断面図であり、(c)は、図4(b)に示すC−C’線による断面図である。

図6(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)及び(c)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図であり、(c)は、(a)に示すC−C’線による断面図である。

図7(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図8(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図9(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図10(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図11(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図12(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図13(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図14は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図15は、第1の実施形態に係る半導体装置の製造方法において、溝を例示する断面図である。

【0008】

先ず、図1(a)に示すように、例えば、単結晶のシリコン(Si)からなるシリコン基板10を用意する。

そして、図1(b)に示すように、シリコン基板10上にハードマスク11となる膜として、例えばシリコン窒化膜(SiN膜)を形成した後、フォトリソグラフィー法でパターニングしてハードマスク11を形成する。ハードマスク11には、シリコン基板10の上面に対して平行な1つの方向に延び、この1つの方向に対して直交する方向に配列された複数本の開口12を形成する。

その後、図1(c)に示すように、ハードマスク11をマスクとしてRIEを行い、シリコン基板10の上層部分に溝13を形成する。

【0009】

次に、図2(a)に示すように、シリコン基板10上にシリコン酸化物を堆積させる。これにより、溝13の内部を埋め込むと共に、ハードマスク11を覆うように、シリコン酸化膜14を形成する。

そして、図2(b)に示すように、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスク11の表面が現れるまでシリコン酸化膜14を研磨する。

次に、図2(c)に示すように、ウェットエッチングを行い、シリコン酸化膜14の上部を除去する。これにより、シリコン酸化膜14の上面を、ハードマスク11の下面、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面と同じ高さまで後退させる。その後、ウェットエッチングを行い、ハードマスク11を除去する。

【0010】

図3(a)及び(b)に示すように、この段階のシリコン基板10において、上方から見てシリコン基板10の上面が現れている領域を「活性領域15」とする。また、上方から見てシリコン酸化膜14の上面が現れている領域を「STI領域16」とする。活性領域15及びSTI領域16は、一方向に沿ってストライプ状に延び、交互に配列されている。

【0011】

次に、図4(a)に示すように、全面にシリコン酸化膜17を形成する。シリコン酸化膜17は、活性領域15におけるシリコン基板10の上面及びSTI領域16におけるシリコン酸化膜14の上面の双方を覆う。その後、シリコン酸化膜17上からイオン注入を行うことにより、シリコン基板10に不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝13の底部より深い位置までの範囲とする。これによって、活性領域15においては、シリコン基板10の上面から、溝13の底部より深い位置に相当する位置までの範囲にボロンが導入される。STI領域16においては、溝13の底面から、溝13の底面より深い位置までの範囲にボロンが導入される。シリコン基板10におけるボロンが導入された部分がp形のウェル18となる。

【0012】

そして、図4(b)及び図5(a)〜(c)に示すように、シリコン酸化膜17上に、ハードマスク19となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク19を形成する。ハードマスク19には、シリコン基板10の面内におけるSTI領域16を形成するために設けられた溝13に対して直交する方向に延び、溝13が延びる方向に沿って配列された複数の開口20を形成する。

【0013】

その後、図6(a)〜(c)に示すように、チャンバー(図示せず)内にシリコン基板10を装着し、ハードマスク19をマスクとしたRIEを行う。これにより、シリコン酸化膜17が選択的に除去される。また、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14が選択的に除去される。このとき、例えば、RIEのエッチングガスとしてCF4ガスを用いれば、シリコンのエッチング速度とシリコン酸化物のエッチング速度との差を小さくすることができる。したがって、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14を同時に加工することができる。これにより、STI領域16が形成されたシリコン基板10に溝21が形成される。

【0014】

図6(a)に示すように、活性領域15におけるシリコン基板10の溝21の底面22aは、シリコン基板10の上面に平行な平面の形状として形成され、STI領域16におけるシリコン酸化膜14の溝21の底面22bも、シリコン基板10の上面に平行な平面の形状として形成される。そして、底面22aと底面22bとは同じ深さで形成される。すなわち、底面22aと底面22bとは段差なく繋がっている。

【0015】

また、図6(b)に示すように、溝21は、シリコン基板10の上面に等間隔で形成される。各溝21は同じ形状で形成される。溝21の上部における側面はシリコン基板10の上面に対して垂直に形成される。また、溝21の下部は、深くなるにつれて細くなるような傾斜面で形成される。そして、溝21の底面22aは、シリコン基板10の上面に平行な平面の形状として形成される。

【0016】

溝21をRIEで形成するときに、エッチングガス中のイオンが溝21の内面に衝突する。その衝突時の衝撃により溝21の内面におけるシリコン結晶に欠陥が導入され、欠陥層が形成される。

また、溝21をRIEで形成するときに、溝21の内面にRIEによる反応生成物の堆積層が形成される。堆積層は、例えば、CF系のエッチングガスを使用した場合には、フルオロカーボン(fluorocarbon)系の堆積物の層又はシリコン酸化物とハロゲン化物の混合物が堆積した層である。

このようなRIEにおいて、溝21の内面に形成される欠陥層及び堆積層を、以後「阻害層」という。

【0017】

溝21を形成するときに、溝21の内面には、阻害層の他に、「荒れ」も発生する。荒れは、例えば、RIEにおけるエッチングガスのイオンにより発生するものである。また、ラジカルによるエッチングによって発生するものもある。さらに、エッチング反応生成物の堆積によって発生するものもある。荒れには、このようなエッチングガスと関係するものの他、ハードマスク19上に形成したレジストの表面の荒れ及びハードマスク19の表面の荒れが溝21の内面に転写されたものも含まれる。

【0018】

図6(c)に示すように、溝21は、シリコン酸化膜14の上面に等間隔で形成される。そして各溝21は、図6(b)に示す溝21と同じ形状で形成される。そこで、以後は図6(a)に示すC−C’線における工程断面図を省く。また、図7〜図10において、(a)は、図4(b)のA−A’線における断面に相当する断面を示し、(b)は、図4(b)のB−B’線における断面に相当する断面を示す。

その後、ハードマスク19を熱燐酸等で除去する。さらに、ハードマスク19の直下に残留したシリコン酸化膜17を希釈弗酸で除去する。

【0019】

次に、図7(a)及び(b)に示すように、溝21が形成されたシリコン基板10を、弗素又は弗化物を含むガス中でプラズマ処理する。これにより、溝21の内面に形成された阻害層を除去する。

【0020】

弗素又は弗化物を含むガスは、例えば、三フッ化窒素ガス(NF3)、弗素ガス(F2)及び六フッ化硫黄(SF6)からなる群より選択された少なくとも1つのガスを含むものである。また、例えば、弗素又は弗化物を含むガスは、三フッ化窒素ガス(NF3)の単一ガス、弗素ガス(F2)の単一ガス及び六フッ化硫黄(SF6)の単一ガスからなる群より選択された1つのガスとすることができる。

プラズマ処理は、上述のRIEを行ったチャンバー内にシリコン基板10を装着したまま、チャンバー内に上述のガスを導入し、このガスに高周波電圧を印加してプラズマ化させることによって行う。このとき、シリコン基板10にはバイアス電圧を印加する。バイアス電圧Vdcは、例えば100V以下とする。

【0021】

プラズマ処理後、シリコン基板10を水素(H2)ガス中において、熱処理する。熱処理温度は、例えば800℃とする。熱処理時間は、例えば数秒間とする。この処理により、溝21の内面におけるシリコン原子を移動させる。シリコン原子の移動により、RIEによる溝21の内面の荒れが、修復される。

【0022】

次に、図8(a)及び(b)に示すように、溝21の内面上及びシリコン基板10の上面上にゲート絶縁膜23、例えば、シリコン酸化膜を形成する。

次に、ゲート絶縁膜23上に導電膜24、例えばポリシリコン膜を形成する。このポリシリコン膜にはリンが不純物として導入されている。導電膜24は、溝21内を埋め込むように形成する。

【0023】

その後、図9(a)及び(b)に示すように、導電膜24上にバリアメタル膜25として、例えば、窒化チタン膜を積層する。そして、その上から低抵抗金属膜26として、例えばタングステン(W)膜を形成する。

次に、図10(a)及び(b)に示すように、低抵抗金属膜26上に、ハードマスク27となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク27を形成する。ハードマスク27には、シリコン基板10の面内における溝21が延びる方向に延び、溝13が延びる方向に配列した複数の開口28を形成する。開口28は、溝21と溝21との間の領域の直上域に形成する。

【0024】

そして、図11(a)に示すように、ハードマスク27をマスクとしてRIEを行い、低抵抗金属膜26、バリアメタル膜25及び導電膜24を選択的に除去する。これにより、ハードマスク27で覆われている部分には、低抵抗金属層26、バリアメタル膜25及び導電膜24からなるゲート電極29が形成される。導電膜24のうち、溝21の内部に埋め込まれた部分を下部導電膜24aといい、下部導電膜24a以外のシリコン基板10の上面上の部分を上部導電膜24bという。

また、上部導電膜24b、バリアメタル膜25、低抵抗金属層26及びハードマスク27からなる積層体を積層体30という。

【0025】

次に、図11(b)に示すように、ハードマスク27をマスクとしてウェットエッチングを行い、ゲート絶縁膜23を選択的に除去する。

その後、図12(a)に示すように、積層体30の側面上にエクステンション側壁31を形成する。エクステンション側壁31は、シリコン基板10上にシリコン窒化膜を形成した後、積層体30の側面上以外の部分を除去して形成する。

そして、図12(b)に示すように、積層体30及びエクステンション側壁31をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体30及びエクステンション側壁31に覆われていない領域にエクステンション領域32を形成する。

【0026】

次に、図13(a)に示すように、積層体30の側面上にソース・ドレイン側壁33を形成する。ソース・ドレイン側壁33は、シリコン基板10上にシリコン窒化膜を形成した後、積層体30の側面上以外の部分を除去して形成する。

そして、図13(b)に示すように、積層体30、エクステンション側壁31及びソース・ドレイン側壁33をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体30、エクステンション側壁31及びソース・ドレイン側壁33に覆われていない領域にソース・ドレイン領域34を形成する。ソース・ドレイン領域34には、エクステンション領域32に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域34には、エクステンション領域31より深くリンを注入する。

【0027】

そして、図14に示すように、シリコン基板10上に層間絶縁膜35を堆積した後、層間絶縁膜35にソース・ドレイン領域34に到達するコンタクトホール36を形成する。コンタクトホール36内に導電部材を埋設してコンタクト37を形成する。

このようにして、半導体装置1が完成する。

【0028】

次に、本実施形態の効果について説明する。

本実施形態によれば、RCATのゲート電極29の一部が埋め込まれる溝21をRIEによって形成した後で、弗素又は弗化物を含むガス中でプラズマ処理することにより、阻害層を除去している。これにより、プラズマ処理後に行う水素熱処理によって、溝21の内面におけるシリコン原子の移動が阻害されない。よって、RIE後の溝21の内面の荒れを修復することができる。

【0029】

また、図15に示すように、例えば、複数のRCATが集まってセル領域51を形成している場合において、セル領域51の中央に溝21aを形成する場合とセル領域51の端に溝21bを形成する場合とでは、イオンの衝撃の強さや生成反応物の付着の仕方が異なる。また、セル領域51に溝21aを形成する場合と、セル領域51から離れて溝21cを形成する場合とでも、イオンの衝撃の強さや生成反応物の付着の仕方が異なる。このように、溝21が形成される位置及び配置密度によって、形成される阻害層が異なることとなる。しかしながら、本実施形態においては、阻害層を除去するため、どの溝21においても、均等にシリコン原子が移動し、溝21の内面の荒れを修復する。よって、溝21の形状を均一化することができる。溝21の形状の均一化によって、RCATの電気的特性にバラツキが生じない。よって、電気的特性が良好なRCATを製造することができる。

【0030】

弗素又は弗化物を含むガスは、プラズマ処理において、反応生成物からなる堆積物を形成しにくい。よって、反応生成物の堆積層を新たに形成することなく、阻害層の除去を行うことができる。

【0031】

プラズマ処理する場合に、シリコン基板10に印加するバイアス電圧Vdcを、100V以下にする。バイアス電圧Vdcを100V以下とすると、シリコン基板10に対するイオンの衝撃を抑えることができる。よって、イオンの衝撃により新たに欠陥層を形成することなく、阻害層の除去を行うことができる。

【0032】

(第1の実施形態の変形例)

次に、第1の実施形態の変形例について説明する。

図16は、第1の実施形態の変形例に係る半導体装置の製造方法において、溝を例示する断面図である。

本変形例においては、溝21の底部を下方に向かって細くなる凸部42が形成された形状としている。そして、溝21a、溝21b及び溝21cの形状を、そのような溝21の形状にそろえている。この場合でも、溝21の形状の均一化によって、電気的特性が良好なRCATを製造することができる。本変形例における上記以外の構成及び効果は、前述の第1の実施形態と同様である。

【0033】

(第1の実施形態の比較例)

次に、第1の実施形態の比較例について説明する。

図17は、第1の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図18は、第1の実施形態の比較例に係る半導体装置の製造方法において、溝を例示する断面図である。

【0034】

先ず、前述の第1の実施形態における図1〜図6に示す工程を実施する。これらの工程については、説明を省略する。

その後、図17(a)及び(b)に示すように、本比較例においては、RIE後に、弗素又は弗化物を含むガスによるプラズマ処理をせずに、シリコン基板10を水素ガス中において熱処理する。

【0035】

本比較例においては、RIEにより溝21を形成後に弗素又は弗化物を含むガスによるプラズマ処理をせずに水素熱処理を行っている。したがって、水素熱処理において、阻害層が溝21の内面におけるシリコンの移動を阻害する。阻害層は、溝21の配置密度及び位置によって、その大きさ、形状及び付着の仕方が異なる。したがって、シリコン原子の移動を阻害する仕方も、形成された溝21の配置密度及び位置によって異なる。その結果、溝21の断面形状が、RIE後は同一の形状であったとしても、水素熱処理後では、形成された溝21の配置密度及び位置によって異なることなる。

例えば、図17(b)に示すように、溝21dにおいては、溝21dの底部に、下方に向かって細くなる凸部42が形成されるのに対して、溝21eにおいては、溝21eの底部に、平面41が形成される。

【0036】

そして、前述の第1の実施形態における図8〜図14に示す工程を実施する。これらの工程については、説明を省略する。

このようにして、本比較例に係る半導体装置が製造される。

【0037】

図18に示すように、溝21の断面形状が、形成された溝21の配置密度や位置によって異なる例としては、次の場合があげられる。すなわち、複数のRCATが集まってセル領域51を形成している場合において、セル領域51の中央に形成された溝21aとセル領域51の端に形成された溝21bとがあげられる。溝21aと溝21bとの間では、イオンの衝撃の強さ並びに生成反応物の付着の程度及び状態が異なる。その結果、阻害層がシリコン原子の移動を阻害する状況も異なる。よって、溝21aの断面形状と溝21bの断面形状とが異なることとなる。例えば、溝21aの底部が平面41となるのに対して、溝21bの底部は下に凸の凸部42となる。

【0038】

また、溝21の断面形状が異なる他の場合として、セル領域51の中央に形成された溝21aとセル領域51から離れて形成された溝21cとがあげられる。溝21aと溝21cとの間でも、イオンの衝撃の強さ並びに生成反応物の付着の程度及び状態が異なり、その結果、阻害層がシリコン原子の移動を阻害する状況も異なる。よって、溝21aの断面形状と溝21cの断面形状も相互に異なり、例えば、溝21aの底部が平面41となるのに対して、溝21cの底部は下に凸の凸部42となる。

このように溝21の形状が異なることによって、RCATの電気的特性にバラツキが生じる。

【0039】

(第2の実施形態)

次に、第2の実施形態について説明する。

図19は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図20は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図21は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

本実施形態は、サドルフィンが形成されたRCATを製造する例である。

【0040】

先ず、前述の第1の実施形態における図1〜図5に示す工程を実施する。これらの工程については、説明を省略する。

次に、図19(a)及び(b)に示すように、ハードマスク19をマスクとしてRIEを行い、シリコン酸化膜17を選択的に除去する。さらに、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14を選択的に除去する。これにより、シリコン基板10に溝21が形成される。本実施形態の半導体装置の製造方法においては、プラズマ処理をする前に、溝21の底面におけるシリコン酸化膜14を除去する。これにより、STI領域16における溝21の底面38は、活性領域15における溝21の底面39より下方に位置するようになる。また、これにより、底面38と底面39との間には段差が形成される。段差には、溝13の側面40が露出する。

その後、ハードマスク19を熱燐酸等で除去する。さらに、ハードマスク19の直下に残留したシリコン酸化膜17を希釈弗酸で除去する。

【0041】

そして、図20(a)及び(b)に示すように、溝21が形成されたシリコン基板10を、弗素又は弗化物を含むガスを用いてプラズマ処理する。その後、水素ガス中において、熱処理を実施する。

【0042】

次に、図21に示すように、溝21の内面上及びシリコン基板10の上面上にゲート絶縁膜23を形成する。ゲート絶縁膜23は、底面38、底面39及び側面40を覆うように形成する。

次に、ゲート絶縁膜23上に導電膜24を形成する。導電膜24は、底面38、底面39及び側面40上に形成されたゲート絶縁膜23を覆い、溝21内を埋め込むように形成する。

【0043】

その後、導電膜24上にバリアメタル膜25を積層する。そして、その上から低抵抗金属膜26を形成する。低抵抗金属膜26上に、ハードマスク27となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク27を形成する。

そして、前述の第1の実施形態における図11〜図14に示す工程を実施する。これらの工程については、説明を省略する。

このようにして、第2の実施形態に係る半導体装置が製造される。

【0044】

次に、本実施形態の効果について説明する。

本実施形態に係る半導体装置の製造方法によれば、溝21の底面には、溝13の側面40が露出している。これにより、活性領域15における溝21の底面には、いわゆるサドルフィンが形成される。また、溝13の側面40にもゲート絶縁膜23を形成している。すなわち、活性領域15においてゲート絶縁膜23で覆われた底面39及び2つの側面40の3面に隣接するシリコン基板10の領域はRCATのチャネルとなる。これにより、チャネル面積を増大させ、チャネルを流れる電流量を増加させることができる。また、チャネルは3面からなる3方向をゲート電極29で囲まれているのでチャネルの電位を精度良くゲート電極29で制御することができる。

【0045】

溝13の側面40を露出させるために、溝21の底面におけるシリコン酸化膜14を除去している。この場合、活性領域15におけるシリコン基板10を除去しないようなエッチング条件としている。そのようなエッチング条件では、イオンのエネルギーを高くする場合があるので、溝21の内面に、多くの阻害層が形成される場合がある。

【0046】

本実施形態によれば、水素熱処理前にプラズマ処理によって阻害層を除去しているので、サドルフィン形成時のエッチングガス中のイオンのエネルギーを高くしても、溝21の形状を均一にすることができる。よって、電気的特性が良好な半導体装置を製造することができる。本実施形態における上記以外の効果は、前述の第1の実施形態と同様である。

【0047】

(第3の実施形態)

次に、第3の実施形態について説明する。

図22は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図23は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図24は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

本実施形態は、フィン型トランジスタを製造する例である。

【0048】

先ず、図22(a)及び(b)に示すように、シリコン基板10を用意する。そして、シリコン基板10上にハードマスク43を形成する。ハードマスク43には、シリコン基板10の面内における1つの方向に延び、1つの方向に直交する方向に配列された複数の開口44を形成する。その後、ハードマスク43をマスクとしてRIEを行い、シリコン基板10の上層部分に柱状体45を形成する。

【0049】

次に、図23(a)及び(b)に示すように、ハードマスク43で覆われた柱状体45を含むシリコン基板10上をシリコン酸化膜46で覆う。そして、CMP法によって、ハードマスク43の表面が現れるまでシリコン酸化膜46を研磨する。

次に、ハードマスク43をマスクとしてシリコン酸化膜46に対してRIEを施し、シリコン酸化膜46の上面を下方に後退させる。柱状体45におけるシリコン酸化膜46の上面から上の部分をフィン47という。シリコン基板10において、上方から見て残留したシリコン酸化膜46がある領域をSTI領域48とする。STI領域48に挟まれたフィン47がある領域を活性領域49とする。その後、ハードマスク43を除去する。

そして、フィン47が形成されたシリコン基板10を、弗素又は弗化物を含むガスを用いてプラズマ処理する。その後、水素ガス中において、熱処理を実施する。

【0050】

次に、図24(a)及び(b)に示すように、フィン47の上面上及び側面上にゲート絶縁膜23として、例えばシリコン酸化膜を形成する。

その後、ゲート絶縁膜23上に、導電膜24を形成する。導電膜24は、フィン47を覆うように、フィン47の高さ以上に形成する。

【0051】

そして、導電膜24上にバリアメタル膜25を形成する。そして、その上から低抵抗金属膜26を形成する。

低抵抗金属膜26上に、ハードマスク27を形成する。ハードマスク27は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク27は、フィン47が延びる方向に対して直交するように形成する。

【0052】

次に、ハードマスク27をマスクとして、RIEを行い、低抵抗金属膜26、バリアメタル膜25、導電膜24及びゲート絶縁膜23を選択的に除去する。これによって、ハードマスク27で覆われている部分には、低抵抗金属膜26、バリアメタル膜25、導電膜24からなるゲート電極29が形成される。ハードマスク27及びゲート電極29からなる積層体を積層体50という。

一方、ハードマスク22で覆われていない部分の表面には、フィン47の上面及び側面が現れている。

【0053】

積層体50の側面上にエクステンション側壁31を形成する。そして、積層体50及びエクステンション側壁31をマスクとして、フィン47にリンをイオン注入する。これにより、フィン47における積層体50及びエクステンション側壁31に覆われていない領域にエクステンション領域32を形成する。

【0054】

さらに、積層体50の側面上にソース・ドレイン側壁33を形成する。そして、積層体50、エクステンション側壁31及びソース・ドレイン側壁33をマスクとして、フィン47にリンをイオン注入する。これにより、フィン47における積層体50、エクステンション側壁31及びソース・ドレイン側壁33に覆われていない領域にソース・ドレイン領域34を形成する。

【0055】

そして、シリコン基板10上に層間絶縁膜35を堆積した後、層間絶縁膜35にソース・ドレイン領域34に到達するコンタクトホール36を形成する。コンタクトホール36内に導電部材を埋設してコンタクト37を形成する。

このようにして、半導体装置3が製造される。

【0056】

次に、本実施形態の効果について説明する。

本実施形態によれば、フィン47をRIEによって形成した後で、弗素又は弗化物を含むガス中でプラズマ処理することにより、阻害層を除去している。これにより、どのフィン47においても、均等にシリコン原子が移動するため、フィン47の形状を均一化することができる。よって、フィン型のトランジスタの電気的特性にバラツキが生じないので、電気的特性が良好なフィン型のトランジスタを製造することができる。

【0057】

また、フィン47を形成するために、STI領域48におけるシリコン酸化膜46を除去している。この場合、フィン47を除去しないようなエッチング条件としている。そのようなエッチング条件では、イオンのエネルギーを高くする場合があるので、フィン47の表面に、多くの阻害層が形成される場合がある。

【0058】

本実施形態によれば、水素熱処理前にプラズマ処理によって阻害層を除去しているので、シリコン酸化膜46を除去するエッチングガス中のイオンのエネルギーを高くしても、フィン47の形状を均一にすることができる。よって、電気的特性が良好な半導体装置を製造することができる。本実施形態における上記以外の効果は、前述の第1の実施形態と同様である。

【0059】

以上説明した実施形態によれば、電気的特性が良好な半導体装置の製造方法を提供することができる。

【0060】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0061】

1:半導体装置、3、半導体装置、10:シリコン基板、11:ハードマスク、12:開口、13:溝、14:シリコン酸化膜、15:活性領域、16:STI領域、17:シリコン酸化膜、18:ウェル、19:ハードマスク、20:開口、21:溝、21a:溝、21b:溝、21c:溝、21d:溝、21e:溝、22a:底面、22b:底面、23:ゲート絶縁膜、24:導電膜、24a:下部導電膜、24b:上部導電膜、25:バリアメタル膜、26:低抵抗金属膜、27:ハードマスク、28:開口、29:ゲート電極、30:積層体、31:エクステンション側壁、32:エクステンション領域、33:ソース・ドレイン側壁、34:ソース・ドレイン領域、35:層間絶縁膜、36:コンタクトホール、37:コンタクト、38:底面、39:底面、40:側面、41:平面、42:凸部、43:ハードマスク、44:開口、45:柱状体、46:シリコン酸化膜、47:フィン、48:STI領域、49:活性領域、50:積層体、51:セル領域

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

リセス構造のトランジスタ(以後、「RCAT」(Recessed Channel Transistor)ともいう。)は、ゲート電極の一部が、半導体基板に形成された溝の内部に埋め込まれている。RCATにおいては、溝の内面に形成された絶縁膜がゲート絶縁膜となり、半導体基板の溝に沿った領域がチャネルを構成する。ゲート電極の一部が埋め込まれる溝は、半導体基板に反応性イオンエッチング(RIE:reactive ion etching)を施すことによって形成されるが、溝の形状にバラツキが生じると、RCATの電気的特性が低下する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−231945号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、電気的特性が良好な半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

【図面の簡単な説明】

【0006】

【図1】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図2】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図3】(a)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図4】(a)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図5】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、図4(b)に示すA−A’線による断面図であり、(b)は、図4(b)に示すB−B’線による断面図であり、(c)は、図4(b)に示すC−C’線による断面図である。

【図6】(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)及び(c)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図であり、(c)は、(a)に示すC−C’線による断面図である。

【図7】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図8】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図9】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図10】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図11】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図14】第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図15】第1の実施形態に係る半導体装置の製造方法において、溝を例示する断面図である。

【図16】第1の実施形態の変形例に係る半導体装置の製造方法において、溝を例示する断面図である。

【図17】(a)及び(b)は、第1の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図18】第1の実施形態の比較例に係る半導体装置の製造方法において、溝を例示する断面図である。

【図19】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図20】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図21】(a)及び(b)は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図22】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図23】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【図24】(a)及び(b)は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

【発明を実施するための形態】

【0007】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

図1〜図4は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図5(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、図4(b)に示すA−A’線による断面図であり、(b)は、図4(b)に示すB−B’線による断面図であり、(c)は、図4(b)に示すC−C’線による断面図である。

図6(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)及び(c)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図であり、(c)は、(a)に示すC−C’線による断面図である。

図7(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図8(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図9(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図10(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図11(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図12(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図13(a)及び(b)は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図14は、第1の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

図15は、第1の実施形態に係る半導体装置の製造方法において、溝を例示する断面図である。

【0008】

先ず、図1(a)に示すように、例えば、単結晶のシリコン(Si)からなるシリコン基板10を用意する。

そして、図1(b)に示すように、シリコン基板10上にハードマスク11となる膜として、例えばシリコン窒化膜(SiN膜)を形成した後、フォトリソグラフィー法でパターニングしてハードマスク11を形成する。ハードマスク11には、シリコン基板10の上面に対して平行な1つの方向に延び、この1つの方向に対して直交する方向に配列された複数本の開口12を形成する。

その後、図1(c)に示すように、ハードマスク11をマスクとしてRIEを行い、シリコン基板10の上層部分に溝13を形成する。

【0009】

次に、図2(a)に示すように、シリコン基板10上にシリコン酸化物を堆積させる。これにより、溝13の内部を埋め込むと共に、ハードマスク11を覆うように、シリコン酸化膜14を形成する。

そして、図2(b)に示すように、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスク11の表面が現れるまでシリコン酸化膜14を研磨する。

次に、図2(c)に示すように、ウェットエッチングを行い、シリコン酸化膜14の上部を除去する。これにより、シリコン酸化膜14の上面を、ハードマスク11の下面、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面と同じ高さまで後退させる。その後、ウェットエッチングを行い、ハードマスク11を除去する。

【0010】

図3(a)及び(b)に示すように、この段階のシリコン基板10において、上方から見てシリコン基板10の上面が現れている領域を「活性領域15」とする。また、上方から見てシリコン酸化膜14の上面が現れている領域を「STI領域16」とする。活性領域15及びSTI領域16は、一方向に沿ってストライプ状に延び、交互に配列されている。

【0011】

次に、図4(a)に示すように、全面にシリコン酸化膜17を形成する。シリコン酸化膜17は、活性領域15におけるシリコン基板10の上面及びSTI領域16におけるシリコン酸化膜14の上面の双方を覆う。その後、シリコン酸化膜17上からイオン注入を行うことにより、シリコン基板10に不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝13の底部より深い位置までの範囲とする。これによって、活性領域15においては、シリコン基板10の上面から、溝13の底部より深い位置に相当する位置までの範囲にボロンが導入される。STI領域16においては、溝13の底面から、溝13の底面より深い位置までの範囲にボロンが導入される。シリコン基板10におけるボロンが導入された部分がp形のウェル18となる。

【0012】

そして、図4(b)及び図5(a)〜(c)に示すように、シリコン酸化膜17上に、ハードマスク19となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク19を形成する。ハードマスク19には、シリコン基板10の面内におけるSTI領域16を形成するために設けられた溝13に対して直交する方向に延び、溝13が延びる方向に沿って配列された複数の開口20を形成する。

【0013】

その後、図6(a)〜(c)に示すように、チャンバー(図示せず)内にシリコン基板10を装着し、ハードマスク19をマスクとしたRIEを行う。これにより、シリコン酸化膜17が選択的に除去される。また、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14が選択的に除去される。このとき、例えば、RIEのエッチングガスとしてCF4ガスを用いれば、シリコンのエッチング速度とシリコン酸化物のエッチング速度との差を小さくすることができる。したがって、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14を同時に加工することができる。これにより、STI領域16が形成されたシリコン基板10に溝21が形成される。

【0014】

図6(a)に示すように、活性領域15におけるシリコン基板10の溝21の底面22aは、シリコン基板10の上面に平行な平面の形状として形成され、STI領域16におけるシリコン酸化膜14の溝21の底面22bも、シリコン基板10の上面に平行な平面の形状として形成される。そして、底面22aと底面22bとは同じ深さで形成される。すなわち、底面22aと底面22bとは段差なく繋がっている。

【0015】

また、図6(b)に示すように、溝21は、シリコン基板10の上面に等間隔で形成される。各溝21は同じ形状で形成される。溝21の上部における側面はシリコン基板10の上面に対して垂直に形成される。また、溝21の下部は、深くなるにつれて細くなるような傾斜面で形成される。そして、溝21の底面22aは、シリコン基板10の上面に平行な平面の形状として形成される。

【0016】

溝21をRIEで形成するときに、エッチングガス中のイオンが溝21の内面に衝突する。その衝突時の衝撃により溝21の内面におけるシリコン結晶に欠陥が導入され、欠陥層が形成される。

また、溝21をRIEで形成するときに、溝21の内面にRIEによる反応生成物の堆積層が形成される。堆積層は、例えば、CF系のエッチングガスを使用した場合には、フルオロカーボン(fluorocarbon)系の堆積物の層又はシリコン酸化物とハロゲン化物の混合物が堆積した層である。

このようなRIEにおいて、溝21の内面に形成される欠陥層及び堆積層を、以後「阻害層」という。

【0017】

溝21を形成するときに、溝21の内面には、阻害層の他に、「荒れ」も発生する。荒れは、例えば、RIEにおけるエッチングガスのイオンにより発生するものである。また、ラジカルによるエッチングによって発生するものもある。さらに、エッチング反応生成物の堆積によって発生するものもある。荒れには、このようなエッチングガスと関係するものの他、ハードマスク19上に形成したレジストの表面の荒れ及びハードマスク19の表面の荒れが溝21の内面に転写されたものも含まれる。

【0018】

図6(c)に示すように、溝21は、シリコン酸化膜14の上面に等間隔で形成される。そして各溝21は、図6(b)に示す溝21と同じ形状で形成される。そこで、以後は図6(a)に示すC−C’線における工程断面図を省く。また、図7〜図10において、(a)は、図4(b)のA−A’線における断面に相当する断面を示し、(b)は、図4(b)のB−B’線における断面に相当する断面を示す。

その後、ハードマスク19を熱燐酸等で除去する。さらに、ハードマスク19の直下に残留したシリコン酸化膜17を希釈弗酸で除去する。

【0019】

次に、図7(a)及び(b)に示すように、溝21が形成されたシリコン基板10を、弗素又は弗化物を含むガス中でプラズマ処理する。これにより、溝21の内面に形成された阻害層を除去する。

【0020】

弗素又は弗化物を含むガスは、例えば、三フッ化窒素ガス(NF3)、弗素ガス(F2)及び六フッ化硫黄(SF6)からなる群より選択された少なくとも1つのガスを含むものである。また、例えば、弗素又は弗化物を含むガスは、三フッ化窒素ガス(NF3)の単一ガス、弗素ガス(F2)の単一ガス及び六フッ化硫黄(SF6)の単一ガスからなる群より選択された1つのガスとすることができる。

プラズマ処理は、上述のRIEを行ったチャンバー内にシリコン基板10を装着したまま、チャンバー内に上述のガスを導入し、このガスに高周波電圧を印加してプラズマ化させることによって行う。このとき、シリコン基板10にはバイアス電圧を印加する。バイアス電圧Vdcは、例えば100V以下とする。

【0021】

プラズマ処理後、シリコン基板10を水素(H2)ガス中において、熱処理する。熱処理温度は、例えば800℃とする。熱処理時間は、例えば数秒間とする。この処理により、溝21の内面におけるシリコン原子を移動させる。シリコン原子の移動により、RIEによる溝21の内面の荒れが、修復される。

【0022】

次に、図8(a)及び(b)に示すように、溝21の内面上及びシリコン基板10の上面上にゲート絶縁膜23、例えば、シリコン酸化膜を形成する。

次に、ゲート絶縁膜23上に導電膜24、例えばポリシリコン膜を形成する。このポリシリコン膜にはリンが不純物として導入されている。導電膜24は、溝21内を埋め込むように形成する。

【0023】

その後、図9(a)及び(b)に示すように、導電膜24上にバリアメタル膜25として、例えば、窒化チタン膜を積層する。そして、その上から低抵抗金属膜26として、例えばタングステン(W)膜を形成する。

次に、図10(a)及び(b)に示すように、低抵抗金属膜26上に、ハードマスク27となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク27を形成する。ハードマスク27には、シリコン基板10の面内における溝21が延びる方向に延び、溝13が延びる方向に配列した複数の開口28を形成する。開口28は、溝21と溝21との間の領域の直上域に形成する。

【0024】

そして、図11(a)に示すように、ハードマスク27をマスクとしてRIEを行い、低抵抗金属膜26、バリアメタル膜25及び導電膜24を選択的に除去する。これにより、ハードマスク27で覆われている部分には、低抵抗金属層26、バリアメタル膜25及び導電膜24からなるゲート電極29が形成される。導電膜24のうち、溝21の内部に埋め込まれた部分を下部導電膜24aといい、下部導電膜24a以外のシリコン基板10の上面上の部分を上部導電膜24bという。

また、上部導電膜24b、バリアメタル膜25、低抵抗金属層26及びハードマスク27からなる積層体を積層体30という。

【0025】

次に、図11(b)に示すように、ハードマスク27をマスクとしてウェットエッチングを行い、ゲート絶縁膜23を選択的に除去する。

その後、図12(a)に示すように、積層体30の側面上にエクステンション側壁31を形成する。エクステンション側壁31は、シリコン基板10上にシリコン窒化膜を形成した後、積層体30の側面上以外の部分を除去して形成する。

そして、図12(b)に示すように、積層体30及びエクステンション側壁31をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体30及びエクステンション側壁31に覆われていない領域にエクステンション領域32を形成する。

【0026】

次に、図13(a)に示すように、積層体30の側面上にソース・ドレイン側壁33を形成する。ソース・ドレイン側壁33は、シリコン基板10上にシリコン窒化膜を形成した後、積層体30の側面上以外の部分を除去して形成する。

そして、図13(b)に示すように、積層体30、エクステンション側壁31及びソース・ドレイン側壁33をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体30、エクステンション側壁31及びソース・ドレイン側壁33に覆われていない領域にソース・ドレイン領域34を形成する。ソース・ドレイン領域34には、エクステンション領域32に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域34には、エクステンション領域31より深くリンを注入する。

【0027】

そして、図14に示すように、シリコン基板10上に層間絶縁膜35を堆積した後、層間絶縁膜35にソース・ドレイン領域34に到達するコンタクトホール36を形成する。コンタクトホール36内に導電部材を埋設してコンタクト37を形成する。

このようにして、半導体装置1が完成する。

【0028】

次に、本実施形態の効果について説明する。

本実施形態によれば、RCATのゲート電極29の一部が埋め込まれる溝21をRIEによって形成した後で、弗素又は弗化物を含むガス中でプラズマ処理することにより、阻害層を除去している。これにより、プラズマ処理後に行う水素熱処理によって、溝21の内面におけるシリコン原子の移動が阻害されない。よって、RIE後の溝21の内面の荒れを修復することができる。

【0029】

また、図15に示すように、例えば、複数のRCATが集まってセル領域51を形成している場合において、セル領域51の中央に溝21aを形成する場合とセル領域51の端に溝21bを形成する場合とでは、イオンの衝撃の強さや生成反応物の付着の仕方が異なる。また、セル領域51に溝21aを形成する場合と、セル領域51から離れて溝21cを形成する場合とでも、イオンの衝撃の強さや生成反応物の付着の仕方が異なる。このように、溝21が形成される位置及び配置密度によって、形成される阻害層が異なることとなる。しかしながら、本実施形態においては、阻害層を除去するため、どの溝21においても、均等にシリコン原子が移動し、溝21の内面の荒れを修復する。よって、溝21の形状を均一化することができる。溝21の形状の均一化によって、RCATの電気的特性にバラツキが生じない。よって、電気的特性が良好なRCATを製造することができる。

【0030】

弗素又は弗化物を含むガスは、プラズマ処理において、反応生成物からなる堆積物を形成しにくい。よって、反応生成物の堆積層を新たに形成することなく、阻害層の除去を行うことができる。

【0031】

プラズマ処理する場合に、シリコン基板10に印加するバイアス電圧Vdcを、100V以下にする。バイアス電圧Vdcを100V以下とすると、シリコン基板10に対するイオンの衝撃を抑えることができる。よって、イオンの衝撃により新たに欠陥層を形成することなく、阻害層の除去を行うことができる。

【0032】

(第1の実施形態の変形例)

次に、第1の実施形態の変形例について説明する。

図16は、第1の実施形態の変形例に係る半導体装置の製造方法において、溝を例示する断面図である。

本変形例においては、溝21の底部を下方に向かって細くなる凸部42が形成された形状としている。そして、溝21a、溝21b及び溝21cの形状を、そのような溝21の形状にそろえている。この場合でも、溝21の形状の均一化によって、電気的特性が良好なRCATを製造することができる。本変形例における上記以外の構成及び効果は、前述の第1の実施形態と同様である。

【0033】

(第1の実施形態の比較例)

次に、第1の実施形態の比較例について説明する。

図17は、第1の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図18は、第1の実施形態の比較例に係る半導体装置の製造方法において、溝を例示する断面図である。

【0034】

先ず、前述の第1の実施形態における図1〜図6に示す工程を実施する。これらの工程については、説明を省略する。

その後、図17(a)及び(b)に示すように、本比較例においては、RIE後に、弗素又は弗化物を含むガスによるプラズマ処理をせずに、シリコン基板10を水素ガス中において熱処理する。

【0035】

本比較例においては、RIEにより溝21を形成後に弗素又は弗化物を含むガスによるプラズマ処理をせずに水素熱処理を行っている。したがって、水素熱処理において、阻害層が溝21の内面におけるシリコンの移動を阻害する。阻害層は、溝21の配置密度及び位置によって、その大きさ、形状及び付着の仕方が異なる。したがって、シリコン原子の移動を阻害する仕方も、形成された溝21の配置密度及び位置によって異なる。その結果、溝21の断面形状が、RIE後は同一の形状であったとしても、水素熱処理後では、形成された溝21の配置密度及び位置によって異なることなる。

例えば、図17(b)に示すように、溝21dにおいては、溝21dの底部に、下方に向かって細くなる凸部42が形成されるのに対して、溝21eにおいては、溝21eの底部に、平面41が形成される。

【0036】

そして、前述の第1の実施形態における図8〜図14に示す工程を実施する。これらの工程については、説明を省略する。

このようにして、本比較例に係る半導体装置が製造される。

【0037】

図18に示すように、溝21の断面形状が、形成された溝21の配置密度や位置によって異なる例としては、次の場合があげられる。すなわち、複数のRCATが集まってセル領域51を形成している場合において、セル領域51の中央に形成された溝21aとセル領域51の端に形成された溝21bとがあげられる。溝21aと溝21bとの間では、イオンの衝撃の強さ並びに生成反応物の付着の程度及び状態が異なる。その結果、阻害層がシリコン原子の移動を阻害する状況も異なる。よって、溝21aの断面形状と溝21bの断面形状とが異なることとなる。例えば、溝21aの底部が平面41となるのに対して、溝21bの底部は下に凸の凸部42となる。

【0038】

また、溝21の断面形状が異なる他の場合として、セル領域51の中央に形成された溝21aとセル領域51から離れて形成された溝21cとがあげられる。溝21aと溝21cとの間でも、イオンの衝撃の強さ並びに生成反応物の付着の程度及び状態が異なり、その結果、阻害層がシリコン原子の移動を阻害する状況も異なる。よって、溝21aの断面形状と溝21cの断面形状も相互に異なり、例えば、溝21aの底部が平面41となるのに対して、溝21cの底部は下に凸の凸部42となる。

このように溝21の形状が異なることによって、RCATの電気的特性にバラツキが生じる。

【0039】

(第2の実施形態)

次に、第2の実施形態について説明する。

図19は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図20は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図21は、第2の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

本実施形態は、サドルフィンが形成されたRCATを製造する例である。

【0040】

先ず、前述の第1の実施形態における図1〜図5に示す工程を実施する。これらの工程については、説明を省略する。

次に、図19(a)及び(b)に示すように、ハードマスク19をマスクとしてRIEを行い、シリコン酸化膜17を選択的に除去する。さらに、活性領域15におけるシリコン基板10及びSTI領域16におけるシリコン酸化膜14を選択的に除去する。これにより、シリコン基板10に溝21が形成される。本実施形態の半導体装置の製造方法においては、プラズマ処理をする前に、溝21の底面におけるシリコン酸化膜14を除去する。これにより、STI領域16における溝21の底面38は、活性領域15における溝21の底面39より下方に位置するようになる。また、これにより、底面38と底面39との間には段差が形成される。段差には、溝13の側面40が露出する。

その後、ハードマスク19を熱燐酸等で除去する。さらに、ハードマスク19の直下に残留したシリコン酸化膜17を希釈弗酸で除去する。

【0041】

そして、図20(a)及び(b)に示すように、溝21が形成されたシリコン基板10を、弗素又は弗化物を含むガスを用いてプラズマ処理する。その後、水素ガス中において、熱処理を実施する。

【0042】

次に、図21に示すように、溝21の内面上及びシリコン基板10の上面上にゲート絶縁膜23を形成する。ゲート絶縁膜23は、底面38、底面39及び側面40を覆うように形成する。

次に、ゲート絶縁膜23上に導電膜24を形成する。導電膜24は、底面38、底面39及び側面40上に形成されたゲート絶縁膜23を覆い、溝21内を埋め込むように形成する。

【0043】

その後、導電膜24上にバリアメタル膜25を積層する。そして、その上から低抵抗金属膜26を形成する。低抵抗金属膜26上に、ハードマスク27となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク27を形成する。

そして、前述の第1の実施形態における図11〜図14に示す工程を実施する。これらの工程については、説明を省略する。

このようにして、第2の実施形態に係る半導体装置が製造される。

【0044】

次に、本実施形態の効果について説明する。

本実施形態に係る半導体装置の製造方法によれば、溝21の底面には、溝13の側面40が露出している。これにより、活性領域15における溝21の底面には、いわゆるサドルフィンが形成される。また、溝13の側面40にもゲート絶縁膜23を形成している。すなわち、活性領域15においてゲート絶縁膜23で覆われた底面39及び2つの側面40の3面に隣接するシリコン基板10の領域はRCATのチャネルとなる。これにより、チャネル面積を増大させ、チャネルを流れる電流量を増加させることができる。また、チャネルは3面からなる3方向をゲート電極29で囲まれているのでチャネルの電位を精度良くゲート電極29で制御することができる。

【0045】

溝13の側面40を露出させるために、溝21の底面におけるシリコン酸化膜14を除去している。この場合、活性領域15におけるシリコン基板10を除去しないようなエッチング条件としている。そのようなエッチング条件では、イオンのエネルギーを高くする場合があるので、溝21の内面に、多くの阻害層が形成される場合がある。

【0046】

本実施形態によれば、水素熱処理前にプラズマ処理によって阻害層を除去しているので、サドルフィン形成時のエッチングガス中のイオンのエネルギーを高くしても、溝21の形状を均一にすることができる。よって、電気的特性が良好な半導体装置を製造することができる。本実施形態における上記以外の効果は、前述の第1の実施形態と同様である。

【0047】

(第3の実施形態)

次に、第3の実施形態について説明する。

図22は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図23は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

図24は、第3の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は、(b)に示すA−A’線による断面図であり、(b)は、(a)に示すB−B’線による断面図である。

本実施形態は、フィン型トランジスタを製造する例である。

【0048】

先ず、図22(a)及び(b)に示すように、シリコン基板10を用意する。そして、シリコン基板10上にハードマスク43を形成する。ハードマスク43には、シリコン基板10の面内における1つの方向に延び、1つの方向に直交する方向に配列された複数の開口44を形成する。その後、ハードマスク43をマスクとしてRIEを行い、シリコン基板10の上層部分に柱状体45を形成する。

【0049】

次に、図23(a)及び(b)に示すように、ハードマスク43で覆われた柱状体45を含むシリコン基板10上をシリコン酸化膜46で覆う。そして、CMP法によって、ハードマスク43の表面が現れるまでシリコン酸化膜46を研磨する。

次に、ハードマスク43をマスクとしてシリコン酸化膜46に対してRIEを施し、シリコン酸化膜46の上面を下方に後退させる。柱状体45におけるシリコン酸化膜46の上面から上の部分をフィン47という。シリコン基板10において、上方から見て残留したシリコン酸化膜46がある領域をSTI領域48とする。STI領域48に挟まれたフィン47がある領域を活性領域49とする。その後、ハードマスク43を除去する。

そして、フィン47が形成されたシリコン基板10を、弗素又は弗化物を含むガスを用いてプラズマ処理する。その後、水素ガス中において、熱処理を実施する。

【0050】

次に、図24(a)及び(b)に示すように、フィン47の上面上及び側面上にゲート絶縁膜23として、例えばシリコン酸化膜を形成する。

その後、ゲート絶縁膜23上に、導電膜24を形成する。導電膜24は、フィン47を覆うように、フィン47の高さ以上に形成する。

【0051】

そして、導電膜24上にバリアメタル膜25を形成する。そして、その上から低抵抗金属膜26を形成する。

低抵抗金属膜26上に、ハードマスク27を形成する。ハードマスク27は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク27は、フィン47が延びる方向に対して直交するように形成する。

【0052】

次に、ハードマスク27をマスクとして、RIEを行い、低抵抗金属膜26、バリアメタル膜25、導電膜24及びゲート絶縁膜23を選択的に除去する。これによって、ハードマスク27で覆われている部分には、低抵抗金属膜26、バリアメタル膜25、導電膜24からなるゲート電極29が形成される。ハードマスク27及びゲート電極29からなる積層体を積層体50という。

一方、ハードマスク22で覆われていない部分の表面には、フィン47の上面及び側面が現れている。

【0053】

積層体50の側面上にエクステンション側壁31を形成する。そして、積層体50及びエクステンション側壁31をマスクとして、フィン47にリンをイオン注入する。これにより、フィン47における積層体50及びエクステンション側壁31に覆われていない領域にエクステンション領域32を形成する。

【0054】

さらに、積層体50の側面上にソース・ドレイン側壁33を形成する。そして、積層体50、エクステンション側壁31及びソース・ドレイン側壁33をマスクとして、フィン47にリンをイオン注入する。これにより、フィン47における積層体50、エクステンション側壁31及びソース・ドレイン側壁33に覆われていない領域にソース・ドレイン領域34を形成する。

【0055】

そして、シリコン基板10上に層間絶縁膜35を堆積した後、層間絶縁膜35にソース・ドレイン領域34に到達するコンタクトホール36を形成する。コンタクトホール36内に導電部材を埋設してコンタクト37を形成する。

このようにして、半導体装置3が製造される。

【0056】

次に、本実施形態の効果について説明する。

本実施形態によれば、フィン47をRIEによって形成した後で、弗素又は弗化物を含むガス中でプラズマ処理することにより、阻害層を除去している。これにより、どのフィン47においても、均等にシリコン原子が移動するため、フィン47の形状を均一化することができる。よって、フィン型のトランジスタの電気的特性にバラツキが生じないので、電気的特性が良好なフィン型のトランジスタを製造することができる。

【0057】

また、フィン47を形成するために、STI領域48におけるシリコン酸化膜46を除去している。この場合、フィン47を除去しないようなエッチング条件としている。そのようなエッチング条件では、イオンのエネルギーを高くする場合があるので、フィン47の表面に、多くの阻害層が形成される場合がある。

【0058】

本実施形態によれば、水素熱処理前にプラズマ処理によって阻害層を除去しているので、シリコン酸化膜46を除去するエッチングガス中のイオンのエネルギーを高くしても、フィン47の形状を均一にすることができる。よって、電気的特性が良好な半導体装置を製造することができる。本実施形態における上記以外の効果は、前述の第1の実施形態と同様である。

【0059】

以上説明した実施形態によれば、電気的特性が良好な半導体装置の製造方法を提供することができる。

【0060】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0061】

1:半導体装置、3、半導体装置、10:シリコン基板、11:ハードマスク、12:開口、13:溝、14:シリコン酸化膜、15:活性領域、16:STI領域、17:シリコン酸化膜、18:ウェル、19:ハードマスク、20:開口、21:溝、21a:溝、21b:溝、21c:溝、21d:溝、21e:溝、22a:底面、22b:底面、23:ゲート絶縁膜、24:導電膜、24a:下部導電膜、24b:上部導電膜、25:バリアメタル膜、26:低抵抗金属膜、27:ハードマスク、28:開口、29:ゲート電極、30:積層体、31:エクステンション側壁、32:エクステンション領域、33:ソース・ドレイン側壁、34:ソース・ドレイン領域、35:層間絶縁膜、36:コンタクトホール、37:コンタクト、38:底面、39:底面、40:側面、41:平面、42:凸部、43:ハードマスク、44:開口、45:柱状体、46:シリコン酸化膜、47:フィン、48:STI領域、49:活性領域、50:積層体、51:セル領域

【特許請求の範囲】

【請求項1】

シリコン基板の上面に、第1方向に延びる複数の溝を形成する工程と、

前記溝の内部に絶縁部材を埋め込んで素子分離領域を形成する工程と、

前記素子分離領域が形成された前記シリコン基板上に、前記第1方向に対して交差した第2方向に延びる複数の開口が形成されたハードマスクを形成する工程と、

前記ハードマスクをマスクとして反応性イオンエッチングにより、前記シリコン基板の上面に、第2方向に延びる複数の凹部を形成する工程と、

前記凹部における絶縁部材を除去して、前記凹部において前記溝の側面を露出させる工程と、

前記凹部を形成する工程と同一容器内において、弗素の単一ガス、三フッ化窒素の単一ガス及び六フッ化硫黄の単一ガスからなる群より選択された1つのガス中で、前記シリコン基板に印加するバイアス電圧を100V以下として、前記溝の側面を露出させた前記凹部が形成された前記シリコン基板をプラズマ処理する工程と、

前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、

前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

を備えた半導体装置の製造方法。

【請求項2】

シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、

前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、

前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、

前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

を備えた半導体装置の製造方法。

【請求項3】

前記凹部を形成する工程の前に、前記シリコン基板の上面に、前記第1方向に対して交差した第2方向に延びる複数の溝を形成する工程と、

前記溝の内部に絶縁部材を埋め込んで素子分離領域を形成する工程と、

前記素子分離領域が形成された前記シリコン基板上に、前記第1方向に延びる複数の開口が形成されたハードマスクを形成する工程と、

をさらに備え、

前記凹部を形成する工程は、前記ハードマスクをマスクとして反応性イオンエッチングにより形成する請求項2記載の半導体装置の製造方法。

【請求項4】

前記プラズマ処理する工程の前に、前記凹部における前記絶縁部材を除去して、前記凹部において前記溝の側面を露出させる工程をさらに備えた請求項3記載の半導体装置の製造方法。

【請求項5】

前記プラズマ処理する工程において、前記弗素又は弗化物を含むガスを、弗素の単一ガス、三フッ化窒素の単一ガス及び六フッ化硫黄の単一ガスからなる群より選択された1つのガスとする請求項2〜4のいずれか1つの半導体装置の製造方法。

【請求項6】

前記プラズマ処理する工程において、前記シリコン基板に印加するバイアス電圧を100V以下とする請求項2〜5のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

前記凹部を形成する工程と、前記プラズマ処理する工程とを、同一のチャンバー内において行う請求項2〜6のいずれか1つに記載の半導体装置の製造方法。

【請求項1】

シリコン基板の上面に、第1方向に延びる複数の溝を形成する工程と、

前記溝の内部に絶縁部材を埋め込んで素子分離領域を形成する工程と、

前記素子分離領域が形成された前記シリコン基板上に、前記第1方向に対して交差した第2方向に延びる複数の開口が形成されたハードマスクを形成する工程と、

前記ハードマスクをマスクとして反応性イオンエッチングにより、前記シリコン基板の上面に、第2方向に延びる複数の凹部を形成する工程と、

前記凹部における絶縁部材を除去して、前記凹部において前記溝の側面を露出させる工程と、

前記凹部を形成する工程と同一容器内において、弗素の単一ガス、三フッ化窒素の単一ガス及び六フッ化硫黄の単一ガスからなる群より選択された1つのガス中で、前記シリコン基板に印加するバイアス電圧を100V以下として、前記溝の側面を露出させた前記凹部が形成された前記シリコン基板をプラズマ処理する工程と、

前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、

前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

を備えた半導体装置の製造方法。

【請求項2】

シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、

前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、

前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、

前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

を備えた半導体装置の製造方法。

【請求項3】

前記凹部を形成する工程の前に、前記シリコン基板の上面に、前記第1方向に対して交差した第2方向に延びる複数の溝を形成する工程と、

前記溝の内部に絶縁部材を埋め込んで素子分離領域を形成する工程と、

前記素子分離領域が形成された前記シリコン基板上に、前記第1方向に延びる複数の開口が形成されたハードマスクを形成する工程と、

をさらに備え、

前記凹部を形成する工程は、前記ハードマスクをマスクとして反応性イオンエッチングにより形成する請求項2記載の半導体装置の製造方法。

【請求項4】

前記プラズマ処理する工程の前に、前記凹部における前記絶縁部材を除去して、前記凹部において前記溝の側面を露出させる工程をさらに備えた請求項3記載の半導体装置の製造方法。

【請求項5】

前記プラズマ処理する工程において、前記弗素又は弗化物を含むガスを、弗素の単一ガス、三フッ化窒素の単一ガス及び六フッ化硫黄の単一ガスからなる群より選択された1つのガスとする請求項2〜4のいずれか1つの半導体装置の製造方法。

【請求項6】

前記プラズマ処理する工程において、前記シリコン基板に印加するバイアス電圧を100V以下とする請求項2〜5のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

前記凹部を形成する工程と、前記プラズマ処理する工程とを、同一のチャンバー内において行う請求項2〜6のいずれか1つに記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2013−89759(P2013−89759A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−228834(P2011−228834)

【出願日】平成23年10月18日(2011.10.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月18日(2011.10.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]