半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置(または半導体集積回路装置)の製造方法における表面保護技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開平5−235006号公報(特許文献1)には、シリコン単結晶ウエハ等の表面に高純度のエピタキシ層を成長させるに際して、ウエハの裏面に高濃度不純物層によるゲッタリング層を設けるとともに、ウエハの裏面を酸化シリコン膜等の外方拡散防止膜で被覆する技術が開示されている。

【0003】

日本特開平4−287328号公報(特許文献2)には、イントリンシックゲッタリング層形成のためのシリコン単結晶ウエハ等の高温アニールに際して、予め、ウエハの全表面を酸化シリコン膜等の保護膜で被覆することにより、窒素雰囲気中での高温アニールの実施を可能とする技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−235006号公報

【特許文献2】特開平4−287328号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、一般に、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、高温熱処理工程の前に、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。

【0006】

しかし、このような対策は、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有ることが、本願発明者等によって明らかにされた。

【0007】

本願発明は、これらの課題を解決するためになされたものである。

【0008】

本発明の目的は、信頼性の高い半導体装置の製造プロセスを提供することにある。

【0009】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0011】

すなわち、本願の一つの発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

【発明の効果】

【0012】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0013】

すなわち、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するので、その後のデバイス主要部の形成に際して、クロスコンタミネーション等を防止することができる。

【図面の簡単な説明】

【0014】

【図1】本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイの構造を説明するためのチップ全体上面図である。

【図2】図1の単位セル領域22の拡大上面図である。

【図3】図2のX−X’断面の模式チップ断面図である。

【図4】本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。

【図5】本願の前記一実施の形態の半導体装置の製造方法における裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。

【図6】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(ウエハ準備工程)の図3に対応するデバイス断面図である。

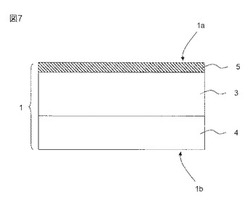

【図7】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。

【図8】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。

【図9】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図10】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面熱酸化膜成膜およびパターニング工程)の図3に対応するデバイス断面図である。

【図11】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(P+型不純物ドープ領域導入工程)の図3に対応するデバイス断面図である。

【図12】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面メタル電極形成工程)の図3に対応するデバイス断面図である。

【図13】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(バックグラインディング工程)の図3に対応するデバイス断面図である。

【図14】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面メタル電極形成工程)の図3に対応するデバイス断面図である。

【図15】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する縦型バッチ式熱CVD装置の模式断面図である。

【図16】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する枚葉式ドライエッチング装置の模式断面図である。

【図17】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用酸化シリコン膜形成工程)の図3に対応するデバイス断面図である。

【図18】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用窒化シリコン膜形成工程)の図3に対応するデバイス断面図である。

【図19】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用窒化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図20】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図21】本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明するための各半導体製造装置群間のプロセスフロー図である。

【発明を実施するための形態】

【0015】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0016】

1.以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面のほぼ全面に、第1の酸化シリコン膜CVDにより、第1の酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、第2の酸化シリコン膜CVDにより、前記第1の酸化シリコン膜よりも厚い第2の酸化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第1の主面および前記第2の主面に対して、同時にウエットエッチングを実行することにより、前記第2の酸化シリコン膜を残した状態で、前記第1の酸化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【0017】

2.前記項1の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【0018】

3.前記項1または2の半導体装置の製造方法において、更に以下の工程を含む:

(f)前記工程(e)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【0019】

4.前記項1から3のいずれか一つの半導体装置の製造方法において、前記第1の酸化シリコン膜CVDおよび前記第2の酸化シリコン膜CVDは、それぞれ枚葉式プラズマCVDである。

【0020】

5.前記項1から4のいずれか一つの半導体装置の製造方法において、前記ウエットエッチングは、浸漬エッチングである。

【0021】

6.前記項3から5のいずれか一つの半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)および(c)は、第2の半導体製造装置群により実行し、前記工程(d)は、前記第2の半導体製造装置群または第3の半導体製造装置群により実行し、前記工程(e)から(g)は、前記第3の半導体製造装置群により実行する。

【0022】

7.以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、酸化シリコン膜CVDにより、酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、窒化シリコン膜CVDにより、窒化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第1のエッチング処理により、前記第1の主面側の前記窒化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第2のエッチング処理により、前記第1の主面側の前記酸化シリコン膜をほぼ全面的に除去する工程;

(f)前記工程(e)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【0023】

8.前記項7の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【0024】

9.前記項7または8の半導体装置の製造方法において、更に以下の工程を含む:

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(h)前記工程(g)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【0025】

10.前記項7から9のいずれか一つの半導体装置の製造方法において、前記酸化シリコン膜CVDおよび前記窒化シリコン膜CVDは、それぞれバッチ式CVDである。

【0026】

11.前記項10の半導体装置の製造方法において、前記バッチ式CVDは、熱CVDである。

【0027】

12.前記項7から11のいずれか一つの半導体装置の製造方法において、前記第1のエッチング処理は、枚葉式ドライエッチングである。

【0028】

13.前記項7から12のいずれか一つの半導体装置の製造方法において、前記第2のエッチング処理は、浸漬ウエットエッチングである。

【0029】

14.前記項9から13のいずれか一つの半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)は、第2の半導体製造装置群により実行し、前記工程(c)から(h)は、第3の半導体製造装置群により実行する。

【0030】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0031】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ、ダイオード(能動素子)等の単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、半導体装置の例としては、たとえばフォトダイオード、フォトダイオードアレイ、光センサ、パワーダイオード、その他のダイオード、パワーMOSFET、IGBT(Insulated Gate Bipolar Transistor)等がある。

【0032】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0033】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0034】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0035】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0036】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0037】

5.「ウエハ」というときは、通常は半導体装置(半導体集積回路装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0038】

6.本願に於いて、「半導体製造装置群」とは、半導体ウエハを処理するための研摩装置、熱処理装置、CVD(Chemical Vapor Deposition)装置、スパッタリング装置、イオン注入装置、塗布装置、露光装置、検査装置、バックグラインディング装置、ダイシング装置等の少なくとも1種類の装置の集合体であり、単一のクリーンルーム内にあるか、異なるクリーンルーム内にあるか、クリーンルーム外にあるかを問わない。しかし、一つの半導体製造装置群に属する半導体製造用装置は、原則として、ここで対象となる他の半導体製造装置群には属していない。

【0039】

また、ウエットエッチングについて「浸漬エッチング」とは、ウエハ等の処理対象物のほぼ全体をエッチング液に浸して処理することを言う。

【0040】

なお、本願に於いて、ウエハの熱処理に関して、「高温」というときは、原則として、摂氏800度以上をいう。

【0041】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0042】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0043】

1.本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイ等の説明(主に図1から図3)

このセクションでは、光デバイスとして、シリコン系半導体基板上に形成されたX線検出用フォトダイオードアレイを例に取り具体的に説明するが、半導体基板としては、シリコンのほか、Ge、SiGe、SiC、AlSb、GaN、GaAs、GaP、GaSb、InAs、InP、InSb、CdS、CdTe、ZnO、ZnS、PbS、PbTe等を例示することができる。

【0044】

図1は本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイの構造を説明するためのチップ全体上面図である。図2は図1の単位セル領域22の拡大上面図である。図3は図2のX−X’断面の模式チップ断面図である。これらに基づいて、本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイ等の構造を説明する。

【0045】

まず、X線検出用フォトダイオードアレイのチップ全体上面図を図1に示す。図1に示すように、半導体チップ2の表面1a(デバイス面または第1の主面)の中央部には、セルマット領域20があり、マトリクス状に(この例では、たとえば、3行12列)単位セル領域22(ピクセルに対応)が敷き詰められている。各単位セル領域22には、表面メタル電極11(例えば、アルミニウム系メタル電極)が設けられており、表面メタル電極11は接続配線23(たとえば、表面メタル電極11と同層のメタル配線)によって半導体チップ2の表面1a周辺部に設けられた外部パッド21(たとえば、表面メタル電極11と同層のメタルパッド)と接続されている。主要な寸法を例示するとすれば、以下のごとくである。すなわち、チップの縦は、10ミリメートル程度、横は、40ミリメートル程度であり、単位セル領域22の縦は、2ミリメートル程度、横は、3ミリメートル程度である。

【0046】

次に、単位セル領域22の拡大上面図を図2に示す。図2に示すように、表面メタル電極11の中央部下方には、P+型不純物ドープ領域10が設けられている。P+型不純物ドープ領域10の不純物濃度としては、たとえば、1020/cm3のオーダ(不純物種は、たとえばボロン)を例示することができる。

【0047】

次に、図2のX−X’断面を図3に示す。図3に示すように、半導体基板領域1s(たとえば、シリコン単結晶基板)の表面1a(デバイス面または第1の主面)側の主要部は、N−型不純物ドープ領域3(第1導電型の第1の不純物ドープ領域)となっており、裏面1b側は、N+型不純物ドープ領域4(第2の不純物ドープ領域)となっている。N−型不純物ドープ領域3(厚さは、たとえば250マイクロメートル程度)の抵抗率は、たとえば、1kΩcm程度(不純物種は、たとえばアンチモン)であり、N+型不純物ドープ領域4(厚さは、たとえば50マイクロメートル程度)の抵抗率は、たとえば、1mΩcm程度(不純物種は、たとえばアンチモン)である。

【0048】

半導体基板領域1sの裏面1b側であって、N+型不純物ドープ領域4の表面のほぼ全体には、裏面メタル電極12(カソード電極)が形成されている。裏面メタル電極12の膜の構成は、N+型不純物ドープ領域4に近い側から、たとえば、チタン膜、ニッケル膜、および金膜(膜厚は、3層で、たとえば300nm程度)である。

【0049】

半導体基板領域1sの表面1a側であって、N−型不純物ドープ領域3の表面領域内には、P+型不純物ドープ領域10が設けられており、これ以外のN−型不純物ドープ領域3の表面は、酸化シリコン膜等のパッシベーション膜7(表面熱酸化膜)で覆われている(例えば、厚さは、1マイクロメートル程度)。更に、P+型不純物ドープ領域10の表面および、その周辺の酸化シリコン膜7の上面は、アルミニウム系メタル膜(例えば、厚さは、1マイクロメートル程度)等の表面メタル電極11(アノード電極)で覆われている。ここで、P+型不純物ドープ領域10、パッシベーション膜7および表面メタル電極11は、このデバイスの主要部15を構成している。

【0050】

このような構造に於いて、X線がN−型不純物ドープ領域3とP+型不純物ドープ領域10の界面のPN接合に入射すると、光起電力効果(Photovoltaic Effect)によって、アノード(P+型不純物ドープ領域10)とカソード(N−型不純物ドープ領域3)間に光起電力が発生する。

【0051】

2.本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜および裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置等の説明(主に図4および5)

ここでは、比較的低温(たとえば、摂氏800度未満)に於いて、ウエハの片面だけに成膜可能な成膜装置として、枚葉式プラズマCVD装置を例に取り具体的に説明するが、比較的定温に於いて、ウエハの片面だけに成膜可能な成膜装置であれば、たとえば、枚葉式熱CVD装置等でもよい。

【0052】

なお、本願に於いては、プラズマCVD装置やドライエッチング装置のプラズマ励起方式として、平行平板方式について具体的に説明するが、これに限らず、ECR(Electron Cyclotron Resonance)方式、ICP(Inductively Coupled Plasma)等でもよいことはいうまでもない。

【0053】

図4は本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。図5は本願の前記一実施の形態の半導体装置の製造方法における裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜および裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置等を説明する。

【0054】

セクション3で説明する第1および第2の酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置51を図4および図5に示す。図4は第1の酸化シリコン膜の成膜の様子を示している。図4に示すように、枚葉式プラズマCVD装置51の主要部は、チャンバ54であり、この内部下方には、下部電極55(ウエハステージ)が設けられており、下部電極55の上には、その表面1aを上に向けて、被処理ウエハ1が置かれている。下部電極55の上方には、上部電極56が設けられており、これらの下部電極55と上部電極56の間に、プラズマ58が生成する。プラズマ58の励起は、高周波電源57によって行われる。処理時には、チャンバ54内は、ガス排出口60を介して真空引きされ、反応ガス等が、ガス導入口59から供給される。

【0055】

次に、図5は第2の酸化シリコン膜の成膜(ウエハ裏面への成膜)の様子を示している(なお、この例では、装置構造は、図4と同じものを使用している)。図5に示すように、ウエハ1の表面1aには、すでに、表面保護用CVD酸化シリコン膜5(第1の酸化シリコン膜)が形成されており、ウエハ1は、その裏面1bを上に向けて、下部電極55の上に置かれている。

【0056】

3.本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)の説明(主に図6から図14)

このセクションでは、セクション1で説明したデバイス構造をセクション2で説明した装置等を用いて形成するプロセスの1例を示す。従って、各種の変形が可能であり、たとえば、酸化シリコン膜等を窒化シリコン膜等に置き換えることも可能である。

【0057】

図6は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(ウエハ準備工程)の図3に対応するデバイス断面図である。図7は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。図8は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。図9は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。図10は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面熱酸化膜成膜およびパターニング工程)の図3に対応するデバイス断面図である。図11は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(P+型不純物ドープ領域導入工程)の図3に対応するデバイス断面図である。図12は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面メタル電極形成工程)の図3に対応するデバイス断面図である。図13は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(バックグラインディング工程)の図3に対応するデバイス断面図である。図14は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面メタル電極形成工程)の図3に対応するデバイス断面図である。これらに基づいて、本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明する。

【0058】

まず、図6に示すように、たとえば、150Φ(直径150ミリメートル程度)のN型シリコン単結晶ウエハ1を準備する。抵抗率は、たとえば、1kΩcm程度を好適なものとして例示することができる。ウエハ1の厚さは、任意であるが、ここでは、たとえば、550マイクロメートル程度とする。なお、ウエハ1の直径は、150Φに限らず、100Φ、200Φ、300Φ、450Φ等であっても良い。

【0059】

次に、たとえば、N型不純物であるアンチモンの固体拡散源膜をウエハ1の裏面1bのほぼ全面に形成した状態で、たとえば、摂氏1000度以上の高温で引き伸ばし拡散を実行することで、N+型不純物ドープ領域4(第2の不純物ドープ領域)をウエハ1の裏面1bのほぼ全面に形成する。N+型不純物ドープ領域4の抵抗率は、たとえば、1mΩcm程度を好適なものとして例示することができる。また、N+型不純物ドープ領域4の厚さは、たとえば、300マイクロメートル程度を好適なものとして例示することができる。従って、ウエハ1の表面1a側の残りの250マイクロメートル程度の部分が、元の濃度で残り、N−型不純物ドープ領域3(第1導電型の第1の不純物ドープ領域)となる。ここで、不要になった固体拡散源膜等の除去、必要であればウエハ1の両面1a、1bの洗浄、補助的な鏡面研摩等を実施した後、次の工程に、ウエハ1を移送する。

【0060】

次に、図7に示すように、ウエハ1の表面1aに、たとえば、TEOS(Tetraethylorthosilicate)を用いたプラズマCVD(Chemical Vapor Deposition)による酸化シリコン系絶縁膜を表面保護用CVD酸化シリコン膜5(第1の酸化シリコン膜)として形成する。表面保護用CVD酸化シリコン膜5の厚さは、たとえば、500nm程度を好適なものとして例示することができる。表面保護用CVD酸化シリコン膜5の成膜条件としては、たとえば、成膜温度:摂氏390度程度、ガス流量:TEOS/O2=1000sccm/400sccm程度を例示することができる。

【0061】

次に、図8に示すように、ウエハ1の裏面1bに、たとえば、TEOSを用いたプラズマCVDによる酸化シリコン系絶縁膜を裏面CVD酸化シリコン膜6(第2の酸化シリコン膜)として形成する。裏面CVD酸化シリコン膜6の厚さは、たとえば、1000nm程度を好適なものとして例示することができる。このように、裏面CVD酸化シリコン膜6の厚さは、表面保護用CVD酸化シリコン膜5の厚さよりも厚くなっている。裏面CVD酸化シリコン膜6の成膜条件としては、たとえば、成膜温度:摂氏390度程度、ガス流量:TEOS/O2=1000sccm/400sccm程度を例示することができる。

【0062】

次に、図9に示すように、たとえば、BHF(Buffered Hydrogen Fluoride)等をエッチング液として、ウエハ1の表面1a側および裏面1b側に対して、浸漬エッチング等のウエットエッチングを施すことにより、ウエハ1の表面1a側および裏面1b側の酸化シリコン系絶縁膜5,6をそれぞれ500nm程度除去する。すなわち、表面保護用CVD酸化シリコン膜5をほぼ全面的に除去する。このとき、裏面CVD酸化シリコン膜6の厚さは、500nm程度となる。

【0063】

次に、図10に示すように、たとえば、摂氏1000度程度のウエット雰囲気で、熱酸化により、ウエハ1の表面1a上のほぼ全面に、表面熱酸化膜7(パッシベーション膜)としての酸化シリコン膜(厚さは、たとえば、1000nm程度)を成膜する。次に、ウエハ1の表面1a上のほぼ全面に、塗布等により、P+型不純物ドープ領域導入用レジスト膜8を形成し、通常のリソグラフィにより、パターニングする。このパターニングされたP+型不純物ドープ領域導入用レジスト膜8を用いて、たとえば、ドライエッチングにより、表面熱酸化膜7にP+型不純物ドープ領域導入用開口9を開口する。

【0064】

次に、図11に示すように、たとえば、イオン注入により、ボロン等を導入することにより、P+型不純物ドープ領域10を形成する。このイオン注入のドーズ量としては、たとえば、1015/cm2程度を例示することができる。その後、不要になったP+型不純物ドープ領域導入用レジスト膜8をアッシング等により除去する。

【0065】

次に、図12に示すように、たとえば、スパッタリング成膜により、ウエハ1の表面1a側のほぼ全面に、アルミニウム系メタル膜を成膜し、通常のリソグラフィにより、パターニングすることにより、表面メタル電極11を形成する。アルミニウム系メタル膜の組成としては、たとえば、1%前後の銅、シリコンを添加したアルミニウムを例示することができる。

【0066】

次に、図13に示すように、ウエハ1の裏面1b側に対して、例えば、バックグラインディング(研削量は、例えば、250マイクロメートル程度)を実行することにより、裏面CVD酸化シリコン膜6の全部とN+型不純物ドープ領域4の一部を除去する。

【0067】

次に、図14に示すように、たとえば、スパッタリング成膜により、ウエハ1の裏面1bのほぼ全面に、裏面メタル電極12を成膜する。

【0068】

その後、必要に応じて、ウエハプローブテスト、ダイシング等を実行して、ウエハ1を個々のチップ2に分割すると、図1から図3に示すようなデバイスとなる。

【0069】

4.本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する装置の説明(主に図15および図16)

このセクションでは、セクション5で説明する不純物外方拡散防止膜形成プロセス(変形例)に使用するCVD装置(図17および図18のプロセスに使用)およびドライエッチング装置(図19のプロセスに使用)を説明する。ここでは、CVD装置として、バッチ式熱CVD装置を例示するが、ウエハの両主面に同時に成膜できるものであれば、他の形式の装置であっても良い(CVD装置に限らない)。また、ドライエッチング装置として、枚葉式ドライエッチング装置を例示するが、ウエハの片面のみをエッチングできるものであれば、バッチ式ドライエッチング装置でも、ウエットエッチング装置でも良い。

【0070】

図15は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する縦型バッチ式熱CVD装置の模式断面図である。図16は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する枚葉式ドライエッチング装置の模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する装置を説明する。

【0071】

バッチ式熱CVD装置52を図15に示す。図15に示すように、バッチ式熱CVD装置52の主要部は、石英反応管61とその周りを取り巻くヒータ62から構成されており、石英反応管61の内部(チャンバ54)には、多数の被処理ウエハ1がセットされたウエハ治具63が置かれている。被処理ウエハ1は、たとえば、その表面1aを上に向けて、ウエハ治具63にセットされている。成膜処理時には、石英反応管61の内部は、減圧され、ガス導入口59から反応ガス等が供給され、ガス排出口60から外部に排出される。

【0072】

次に、枚葉式ドライエッチング装置53を図16に示す。図16に示すように、枚葉式ドライエッチング装置53の主要部は、その壁面が接地されたチャンバ54とその中に置かれた下部電極55(ウエハステージ)から構成されている。下部電極55上には、被処理ウエハ1がその表面1aを上に向けて置かれている。この被処理ウエハ1の表面1aには、セクション5で説明する表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)が形成されており、被処理ウエハ1の裏面1bには、裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)が形成されている。下部電極55には、たとえばバイアスコンデンサ64を介して、高周波電源57が接続されており、プラズマ58を励起する構造となっている。エッチング処理時には、チャンバ54内は、ガス排出口60を介して、真空引きされ、ガス導入口59からエッチングガス等が供給される。

【0073】

5.本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)の説明(主に図17から図20)

このセクションでは、セクション3の不純物外方拡散防止膜形成プロセス(枚葉式CVD方式:図7から図9に対応)に関する変形例(バッチ式CVD方式)を説明するが、酸化シリコン膜および窒化シリコン膜を成膜する順序は、例えば、逆にしても良い。

【0074】

この変形例は、セクション3の図7から図9のプロセスに関する変形例であり、図6および図10から図14の部分は、全く同一であるので、以下では原則として異なる部分のみを説明する。

【0075】

図17は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用酸化シリコン膜形成工程)の図3に対応するデバイス断面図である。図18は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用窒化シリコン膜形成工程)の図3に対応するデバイス断面図である。図19は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用窒化シリコン膜除去工程)の図3に対応するデバイス断面図である。図20は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明する。

【0076】

図6の状態のウエハ1は、セクション3と同様に、次の工程、すなわち、図17で説明する工程に移送される。すなわち、図17に示すように、たとえば、ウエハ1の表面1aおよび裏面1bに、たとえば、TEOSを用いたLP−CVD(Low Pressure−Chemical Vapor Deposition)等のバッチ式熱CVDによる酸化シリコン系絶縁膜を表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)として、それぞれ形成する。表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)の厚さは、たとえば、500nm程度を好適なものとして例示することができる。表面保護用CVD酸化シリコン膜5aおよび裏面保護用CVD酸化シリコン膜5bの成膜条件としては、たとえば、成膜温度:摂氏700度程度、真空度:50パスカル程度、ガス流量:TEOS/O2=100sccm/5sccm程度、チャージ枚数:150枚程度を例示することができる。

【0077】

次に、図18に示すように、たとえば、ウエハ1の表面1a側および裏面1b側に、たとえば、LP−CVD等のバッチ式熱CVDによる窒化シリコン系絶縁膜を表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)として、それぞれ形成する。表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)の厚さは、たとえば、200nm程度を好適なものとして例示することができる。表面保護用CVD窒化シリコン膜14aおよび裏面保護用CVD窒化シリコン膜14bの成膜条件としては、たとえば、成膜温度:摂氏770度程度、真空度:25パスカル程度、ガス流量:SiH2Cl2/NH3=20sccm/200sccm程度、チャージ枚数:150枚程度を例示することができる。

【0078】

次に、図19に示すように、たとえば、枚葉式ドライエッチング(第1のエッチング処理)により、ウエハ1の表面1a側の表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)をほぼ全面的に除去する。このドライエッチング条件としては、たとえば、真空度:3.6キロパスカル程度、ガス流量:Ar/CF4/CHF3=1000sccm/100sccm/30sccm程度を例示することができる。

【0079】

次に、図20に示すように、たとえば、BHF等をエッチング液として、ウエハ1の表面1a側および裏面1b側に対して、浸漬ウエットエッチング等のウエットエッチング(第2のエッチング処理)を施すことにより、ウエハ1の表面1a側の酸化シリコン系絶縁膜5aをほぼ全面的に除去する。

【0080】

その後、図10の工程に移送される。

【0081】

6.本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例の説明(主に図21)

このセクションでは、セクション3およびセクション5における各プロセスを、どの設備を利用して実行するかについての、使い分けの一例を説明する。従って、このような使い分けは、任意であり、他の使用方法を取ることを制限するものではない。

【0082】

図21は本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明するための各半導体製造装置群間のプロセスフロー図である。これに基づいて、本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明する。

【0083】

ここでは、1例として、結晶メーカの設備(第1の半導体製造装置群71)、半導体委託製造組織の設備(第2の半導体製造装置群72)および総合半導体メーカの設備(第3の半導体製造装置群73)の間の設備と工程の振り分けについて説明するが、各群の設備は、同一の組織・メーカに属していても良いし、異なる組織・メーカに属していても良い。

【0084】

(1)枚葉式CVD方式に関する説明(図21および図7から図9)

枚葉式CVD方式については、以下のように運用することが、設備の有効利用およびクロスコンタミネーションの観点から有効である。すなわち、原則として、図6の工程は、第1の半導体製造装置群71に属する装置で処理し、図7から図9の工程は、第2の半導体製造装置群72に属する装置で処理し、図10から図14の工程は、第3の半導体製造装置群73に属する装置で処理する。ただし、図9の工程は、第3の半導体製造装置群73に属する装置で処理してもよい。

【0085】

これは、図6の工程のように、ウエハ1の裏面に不純物外方拡散防止膜がついていない状態で行う高濃度の不純物と摂氏1000度以上の高温を扱う処理と、その他の処理を同一の半導体製造装置群で処理するのは、クロスコンタミネーションの観点から不適当だからである。

【0086】

また、単純な酸化シリコン膜の全面膜付け等からなる工程(図7および図8)と微細加工を伴う複雑なデバイス製造工程(図10から図14)の主要工程とを同一の半導体製造装置群で処理するのは、設備の有効利用の点から効率的ではないからである。ただし、図9の工程は、いずれの工程群に必ず付属するものであり、第1の半導体製造装置群71以外ならいずれで処理してもかまわない。

【0087】

更に、第2の半導体製造装置群72と第3の半導体製造装置群73を分ける利点は、ウエハ1の裏面1bに不純物外方拡散防止膜がついていない状態で行う高温熱処理を行う設備群と、半導体の複雑な主要工程を行う設備群を完全に分離できるところにある。

【0088】

(2)バッチ式CVD方式に関する説明(図21および図17から図20)

バッチ式CVD方式については、以下のように運用することが、設備の有効利用およびクロスコンタミネーションの観点から有効である。すなわち、原則として、図6の工程は、第1の半導体製造装置群71に属する装置で処理し、図17の工程は、第2の半導体製造装置群72に属する装置で処理し、図18から図20および図10から図14の工程は、第3の半導体製造装置群73に属する装置で処理する。

【0089】

図6の工程を第1の半導体製造装置群71に振り分けるのは、サブセクション(1)と同じ理由であるが、図18の比較的単純な窒化シリコン膜の全面膜付けを第2の半導体製造装置群72に振り分けないのは、窒化シリコン膜のバッチ式炉が酸化シリコン膜のバッチ式炉に比べると、数の少ない設備だからである。すなわち、第2の半導体製造装置群72に常備するのは、利用効率上、得策ではないからである。

【0090】

なお、第2の半導体製造装置群72と第3の半導体製造装置群73を分ける理由は、サブセクション(1)と同じ理由である。

【0091】

7.前記各実施の形態(変形例を含む)に関する補助的説明並びに全般的な考察

このセクションでは、本願発明、先の実施の形態、変形例等に関する一般的な考察並びに補足的説明を行う。

【0092】

先にセクション6の述べたクロスコンタミネーションの意義について補足的な説明を行う。半導体ウエハ工程では、多種類の製品が同一のラインを流れるのが普通である。従って、半導体の工程におけるクロスコンタミネーションは、同一工程のあるウエハから他のウエハ(同一製品または他の製品)に汚染が移行する場合と、同一の装置を利用する工程が異なる他のウエハ(同一製品または他の製品)に汚染が移行する場合がある。

【0093】

従って、前記実施の形態(変形例を含む)の効用は、単一の製品の製造方法として有効であるのみならず、多種多様な製品を製造する量産方法としても同様に有効性を有する。

【0094】

以上のように、前記実施の形態(変形例を含む)においては、微細な加工が要求されるデバイス主要部15の形成前に、ウエハ1のデバイス面1aを傷つけることなく、ウエハ1の裏面1bに不純物放出防止膜(不純物外方拡散防止膜)等を形成することで、クロスコンタミネーションを有効に防止することができる。

【0095】

また、デバイス主要部15の形成前に、ウエハ1の裏面1bに不純物放出防止膜(不純物外方拡散防止膜)等を形成するので、デバイス主要部15の形成工程に於いて、高温熱処理を伴う場合に於いても、オートドーピング等を有効に防止することができる。

【0096】

8.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0097】

例えば、前記実施の形態では、対象デバイスとして、主に光デバイス(フォトダイオード)を例に取り具体的に説明したが、本発明はそれに限定されるものではなく、パワー系半導体装置(パワーMOSFET,IGBT,パワーダイオード)、これらのパワー系半導体装置を内蔵する半導体集積回路装置、および、その他の半導体装置、半導体集積回路装置等にも適用できることは言うまでもない。

【0098】

また、前記実施の形態では、裏面に高濃度N型不純物ドープ領域を有するN型ウエハを使用する例を具体的に説明したが、本発明はそれに限定されるものではなく、裏面に高濃度P型不純物ドープ領域を有するN型ウエハを使用する場合にも適用できることは言うまでもない。また、裏面に高濃度P型不純物ドープ領域を有するP型ウエハを使用する場合にも適用できることは言うまでもない。更に、裏面に高濃度N型不純物ドープ領域を有するP型ウエハを使用する場合にも適用できることは言うまでもない。

【符号の説明】

【0099】

1 ウエハ

1a ウエハ又はチップの表面(デバイス面または第1の主面)

1b ウエハ又はチップの裏面(第2の主面)

1s 半導体基板領域

2 半導体チップ(チップ領域)

3 N−型不純物ドープ領域(第1導電型の第1の不純物ドープ領域)

4 N+型不純物ドープ領域(第2の不純物ドープ領域)

5 表面保護用CVD酸化シリコン膜(第1の酸化シリコン膜)

5a 表面保護用CVD酸化シリコン膜(酸化シリコン膜)

5b 裏面保護用CVD酸化シリコン膜(酸化シリコン膜)

6 裏面CVD酸化シリコン膜(第2の酸化シリコン膜)

7 表面熱酸化膜(パッシベーション膜)

8 P+型不純物ドープ領域導入用レジスト膜

9 P+型不純物ドープ領域導入用開口

10 P+型不純物ドープ領域

11 表面メタル電極

12 裏面メタル電極

14a 表面保護用CVD窒化シリコン膜(窒化シリコン膜)

14b 裏面保護用CVD窒化シリコン膜(窒化シリコン膜)

15 デバイスの主要部

20 セルマット領域

21 外部パッド

22 単位セル領域

23 接続配線

51 枚葉式プラズマCVD装置

52 バッチ式低圧CVD装置

53 枚葉式プラズマエッチング装置

54 チャンバ

55 下部電極(ウエハステージ)

56 上部電極

57 高周波電源

58 プラズマ

59 ガス導入口

60 ガス排出口

61 石英反応管

62 ヒータ

63 ウエハ治具

64 バイアスコンデンサ

65 絶縁シール

71 第1の半導体製造装置群

72 第2の半導体製造装置群

73 第3の半導体製造装置群

【技術分野】

【0001】

本発明は、半導体装置(または半導体集積回路装置)の製造方法における表面保護技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開平5−235006号公報(特許文献1)には、シリコン単結晶ウエハ等の表面に高純度のエピタキシ層を成長させるに際して、ウエハの裏面に高濃度不純物層によるゲッタリング層を設けるとともに、ウエハの裏面を酸化シリコン膜等の外方拡散防止膜で被覆する技術が開示されている。

【0003】

日本特開平4−287328号公報(特許文献2)には、イントリンシックゲッタリング層形成のためのシリコン単結晶ウエハ等の高温アニールに際して、予め、ウエハの全表面を酸化シリコン膜等の保護膜で被覆することにより、窒素雰囲気中での高温アニールの実施を可能とする技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−235006号公報

【特許文献2】特開平4−287328号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、一般に、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、高温熱処理工程の前に、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。

【0006】

しかし、このような対策は、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有ることが、本願発明者等によって明らかにされた。

【0007】

本願発明は、これらの課題を解決するためになされたものである。

【0008】

本発明の目的は、信頼性の高い半導体装置の製造プロセスを提供することにある。

【0009】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0011】

すなわち、本願の一つの発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

【発明の効果】

【0012】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0013】

すなわち、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するので、その後のデバイス主要部の形成に際して、クロスコンタミネーション等を防止することができる。

【図面の簡単な説明】

【0014】

【図1】本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイの構造を説明するためのチップ全体上面図である。

【図2】図1の単位セル領域22の拡大上面図である。

【図3】図2のX−X’断面の模式チップ断面図である。

【図4】本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。

【図5】本願の前記一実施の形態の半導体装置の製造方法における裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。

【図6】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(ウエハ準備工程)の図3に対応するデバイス断面図である。

【図7】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。

【図8】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。

【図9】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図10】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面熱酸化膜成膜およびパターニング工程)の図3に対応するデバイス断面図である。

【図11】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(P+型不純物ドープ領域導入工程)の図3に対応するデバイス断面図である。

【図12】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面メタル電極形成工程)の図3に対応するデバイス断面図である。

【図13】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(バックグラインディング工程)の図3に対応するデバイス断面図である。

【図14】本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面メタル電極形成工程)の図3に対応するデバイス断面図である。

【図15】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する縦型バッチ式熱CVD装置の模式断面図である。

【図16】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する枚葉式ドライエッチング装置の模式断面図である。

【図17】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用酸化シリコン膜形成工程)の図3に対応するデバイス断面図である。

【図18】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用窒化シリコン膜形成工程)の図3に対応するデバイス断面図である。

【図19】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用窒化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図20】本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。

【図21】本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明するための各半導体製造装置群間のプロセスフロー図である。

【発明を実施するための形態】

【0015】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0016】

1.以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面のほぼ全面に、第1の酸化シリコン膜CVDにより、第1の酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、第2の酸化シリコン膜CVDにより、前記第1の酸化シリコン膜よりも厚い第2の酸化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第1の主面および前記第2の主面に対して、同時にウエットエッチングを実行することにより、前記第2の酸化シリコン膜を残した状態で、前記第1の酸化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【0017】

2.前記項1の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【0018】

3.前記項1または2の半導体装置の製造方法において、更に以下の工程を含む:

(f)前記工程(e)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【0019】

4.前記項1から3のいずれか一つの半導体装置の製造方法において、前記第1の酸化シリコン膜CVDおよび前記第2の酸化シリコン膜CVDは、それぞれ枚葉式プラズマCVDである。

【0020】

5.前記項1から4のいずれか一つの半導体装置の製造方法において、前記ウエットエッチングは、浸漬エッチングである。

【0021】

6.前記項3から5のいずれか一つの半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)および(c)は、第2の半導体製造装置群により実行し、前記工程(d)は、前記第2の半導体製造装置群または第3の半導体製造装置群により実行し、前記工程(e)から(g)は、前記第3の半導体製造装置群により実行する。

【0022】

7.以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、酸化シリコン膜CVDにより、酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、窒化シリコン膜CVDにより、窒化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第1のエッチング処理により、前記第1の主面側の前記窒化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第2のエッチング処理により、前記第1の主面側の前記酸化シリコン膜をほぼ全面的に除去する工程;

(f)前記工程(e)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【0023】

8.前記項7の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【0024】

9.前記項7または8の半導体装置の製造方法において、更に以下の工程を含む:

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(h)前記工程(g)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【0025】

10.前記項7から9のいずれか一つの半導体装置の製造方法において、前記酸化シリコン膜CVDおよび前記窒化シリコン膜CVDは、それぞれバッチ式CVDである。

【0026】

11.前記項10の半導体装置の製造方法において、前記バッチ式CVDは、熱CVDである。

【0027】

12.前記項7から11のいずれか一つの半導体装置の製造方法において、前記第1のエッチング処理は、枚葉式ドライエッチングである。

【0028】

13.前記項7から12のいずれか一つの半導体装置の製造方法において、前記第2のエッチング処理は、浸漬ウエットエッチングである。

【0029】

14.前記項9から13のいずれか一つの半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)は、第2の半導体製造装置群により実行し、前記工程(c)から(h)は、第3の半導体製造装置群により実行する。

【0030】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0031】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ、ダイオード(能動素子)等の単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、半導体装置の例としては、たとえばフォトダイオード、フォトダイオードアレイ、光センサ、パワーダイオード、その他のダイオード、パワーMOSFET、IGBT(Insulated Gate Bipolar Transistor)等がある。

【0032】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0033】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0034】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0035】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0036】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0037】

5.「ウエハ」というときは、通常は半導体装置(半導体集積回路装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0038】

6.本願に於いて、「半導体製造装置群」とは、半導体ウエハを処理するための研摩装置、熱処理装置、CVD(Chemical Vapor Deposition)装置、スパッタリング装置、イオン注入装置、塗布装置、露光装置、検査装置、バックグラインディング装置、ダイシング装置等の少なくとも1種類の装置の集合体であり、単一のクリーンルーム内にあるか、異なるクリーンルーム内にあるか、クリーンルーム外にあるかを問わない。しかし、一つの半導体製造装置群に属する半導体製造用装置は、原則として、ここで対象となる他の半導体製造装置群には属していない。

【0039】

また、ウエットエッチングについて「浸漬エッチング」とは、ウエハ等の処理対象物のほぼ全体をエッチング液に浸して処理することを言う。

【0040】

なお、本願に於いて、ウエハの熱処理に関して、「高温」というときは、原則として、摂氏800度以上をいう。

【0041】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0042】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0043】

1.本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイ等の説明(主に図1から図3)

このセクションでは、光デバイスとして、シリコン系半導体基板上に形成されたX線検出用フォトダイオードアレイを例に取り具体的に説明するが、半導体基板としては、シリコンのほか、Ge、SiGe、SiC、AlSb、GaN、GaAs、GaP、GaSb、InAs、InP、InSb、CdS、CdTe、ZnO、ZnS、PbS、PbTe等を例示することができる。

【0044】

図1は本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイの構造を説明するためのチップ全体上面図である。図2は図1の単位セル領域22の拡大上面図である。図3は図2のX−X’断面の模式チップ断面図である。これらに基づいて、本願の一実施の形態の半導体装置の製造方法における対象デバイスの一例であるX線検出用フォトダイオードアレイ等の構造を説明する。

【0045】

まず、X線検出用フォトダイオードアレイのチップ全体上面図を図1に示す。図1に示すように、半導体チップ2の表面1a(デバイス面または第1の主面)の中央部には、セルマット領域20があり、マトリクス状に(この例では、たとえば、3行12列)単位セル領域22(ピクセルに対応)が敷き詰められている。各単位セル領域22には、表面メタル電極11(例えば、アルミニウム系メタル電極)が設けられており、表面メタル電極11は接続配線23(たとえば、表面メタル電極11と同層のメタル配線)によって半導体チップ2の表面1a周辺部に設けられた外部パッド21(たとえば、表面メタル電極11と同層のメタルパッド)と接続されている。主要な寸法を例示するとすれば、以下のごとくである。すなわち、チップの縦は、10ミリメートル程度、横は、40ミリメートル程度であり、単位セル領域22の縦は、2ミリメートル程度、横は、3ミリメートル程度である。

【0046】

次に、単位セル領域22の拡大上面図を図2に示す。図2に示すように、表面メタル電極11の中央部下方には、P+型不純物ドープ領域10が設けられている。P+型不純物ドープ領域10の不純物濃度としては、たとえば、1020/cm3のオーダ(不純物種は、たとえばボロン)を例示することができる。

【0047】

次に、図2のX−X’断面を図3に示す。図3に示すように、半導体基板領域1s(たとえば、シリコン単結晶基板)の表面1a(デバイス面または第1の主面)側の主要部は、N−型不純物ドープ領域3(第1導電型の第1の不純物ドープ領域)となっており、裏面1b側は、N+型不純物ドープ領域4(第2の不純物ドープ領域)となっている。N−型不純物ドープ領域3(厚さは、たとえば250マイクロメートル程度)の抵抗率は、たとえば、1kΩcm程度(不純物種は、たとえばアンチモン)であり、N+型不純物ドープ領域4(厚さは、たとえば50マイクロメートル程度)の抵抗率は、たとえば、1mΩcm程度(不純物種は、たとえばアンチモン)である。

【0048】

半導体基板領域1sの裏面1b側であって、N+型不純物ドープ領域4の表面のほぼ全体には、裏面メタル電極12(カソード電極)が形成されている。裏面メタル電極12の膜の構成は、N+型不純物ドープ領域4に近い側から、たとえば、チタン膜、ニッケル膜、および金膜(膜厚は、3層で、たとえば300nm程度)である。

【0049】

半導体基板領域1sの表面1a側であって、N−型不純物ドープ領域3の表面領域内には、P+型不純物ドープ領域10が設けられており、これ以外のN−型不純物ドープ領域3の表面は、酸化シリコン膜等のパッシベーション膜7(表面熱酸化膜)で覆われている(例えば、厚さは、1マイクロメートル程度)。更に、P+型不純物ドープ領域10の表面および、その周辺の酸化シリコン膜7の上面は、アルミニウム系メタル膜(例えば、厚さは、1マイクロメートル程度)等の表面メタル電極11(アノード電極)で覆われている。ここで、P+型不純物ドープ領域10、パッシベーション膜7および表面メタル電極11は、このデバイスの主要部15を構成している。

【0050】

このような構造に於いて、X線がN−型不純物ドープ領域3とP+型不純物ドープ領域10の界面のPN接合に入射すると、光起電力効果(Photovoltaic Effect)によって、アノード(P+型不純物ドープ領域10)とカソード(N−型不純物ドープ領域3)間に光起電力が発生する。

【0051】

2.本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜および裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置等の説明(主に図4および5)

ここでは、比較的低温(たとえば、摂氏800度未満)に於いて、ウエハの片面だけに成膜可能な成膜装置として、枚葉式プラズマCVD装置を例に取り具体的に説明するが、比較的定温に於いて、ウエハの片面だけに成膜可能な成膜装置であれば、たとえば、枚葉式熱CVD装置等でもよい。

【0052】

なお、本願に於いては、プラズマCVD装置やドライエッチング装置のプラズマ励起方式として、平行平板方式について具体的に説明するが、これに限らず、ECR(Electron Cyclotron Resonance)方式、ICP(Inductively Coupled Plasma)等でもよいことはいうまでもない。

【0053】

図4は本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。図5は本願の前記一実施の形態の半導体装置の製造方法における裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置の模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における表面保護用CVD酸化シリコン膜および裏面CVD酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置等を説明する。

【0054】

セクション3で説明する第1および第2の酸化シリコン膜の成膜に使用する枚葉式プラズマCVD装置51を図4および図5に示す。図4は第1の酸化シリコン膜の成膜の様子を示している。図4に示すように、枚葉式プラズマCVD装置51の主要部は、チャンバ54であり、この内部下方には、下部電極55(ウエハステージ)が設けられており、下部電極55の上には、その表面1aを上に向けて、被処理ウエハ1が置かれている。下部電極55の上方には、上部電極56が設けられており、これらの下部電極55と上部電極56の間に、プラズマ58が生成する。プラズマ58の励起は、高周波電源57によって行われる。処理時には、チャンバ54内は、ガス排出口60を介して真空引きされ、反応ガス等が、ガス導入口59から供給される。

【0055】

次に、図5は第2の酸化シリコン膜の成膜(ウエハ裏面への成膜)の様子を示している(なお、この例では、装置構造は、図4と同じものを使用している)。図5に示すように、ウエハ1の表面1aには、すでに、表面保護用CVD酸化シリコン膜5(第1の酸化シリコン膜)が形成されており、ウエハ1は、その裏面1bを上に向けて、下部電極55の上に置かれている。

【0056】

3.本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)の説明(主に図6から図14)

このセクションでは、セクション1で説明したデバイス構造をセクション2で説明した装置等を用いて形成するプロセスの1例を示す。従って、各種の変形が可能であり、たとえば、酸化シリコン膜等を窒化シリコン膜等に置き換えることも可能である。

【0057】

図6は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(ウエハ準備工程)の図3に対応するデバイス断面図である。図7は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。図8は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面CVD酸化シリコン膜成膜工程)の図3に対応するデバイス断面図である。図9は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面保護用CVD酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。図10は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面熱酸化膜成膜およびパターニング工程)の図3に対応するデバイス断面図である。図11は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(P+型不純物ドープ領域導入工程)の図3に対応するデバイス断面図である。図12は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(表面メタル電極形成工程)の図3に対応するデバイス断面図である。図13は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(バックグラインディング工程)の図3に対応するデバイス断面図である。図14は本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明するための製造工程途上(裏面メタル電極形成工程)の図3に対応するデバイス断面図である。これらに基づいて、本願の前記一実施の形態(枚葉式CVD方式)の半導体装置の製造方法における全体プロセス(不純物外方拡散防止膜形成プロセスを含む)を説明する。

【0058】

まず、図6に示すように、たとえば、150Φ(直径150ミリメートル程度)のN型シリコン単結晶ウエハ1を準備する。抵抗率は、たとえば、1kΩcm程度を好適なものとして例示することができる。ウエハ1の厚さは、任意であるが、ここでは、たとえば、550マイクロメートル程度とする。なお、ウエハ1の直径は、150Φに限らず、100Φ、200Φ、300Φ、450Φ等であっても良い。

【0059】

次に、たとえば、N型不純物であるアンチモンの固体拡散源膜をウエハ1の裏面1bのほぼ全面に形成した状態で、たとえば、摂氏1000度以上の高温で引き伸ばし拡散を実行することで、N+型不純物ドープ領域4(第2の不純物ドープ領域)をウエハ1の裏面1bのほぼ全面に形成する。N+型不純物ドープ領域4の抵抗率は、たとえば、1mΩcm程度を好適なものとして例示することができる。また、N+型不純物ドープ領域4の厚さは、たとえば、300マイクロメートル程度を好適なものとして例示することができる。従って、ウエハ1の表面1a側の残りの250マイクロメートル程度の部分が、元の濃度で残り、N−型不純物ドープ領域3(第1導電型の第1の不純物ドープ領域)となる。ここで、不要になった固体拡散源膜等の除去、必要であればウエハ1の両面1a、1bの洗浄、補助的な鏡面研摩等を実施した後、次の工程に、ウエハ1を移送する。

【0060】

次に、図7に示すように、ウエハ1の表面1aに、たとえば、TEOS(Tetraethylorthosilicate)を用いたプラズマCVD(Chemical Vapor Deposition)による酸化シリコン系絶縁膜を表面保護用CVD酸化シリコン膜5(第1の酸化シリコン膜)として形成する。表面保護用CVD酸化シリコン膜5の厚さは、たとえば、500nm程度を好適なものとして例示することができる。表面保護用CVD酸化シリコン膜5の成膜条件としては、たとえば、成膜温度:摂氏390度程度、ガス流量:TEOS/O2=1000sccm/400sccm程度を例示することができる。

【0061】

次に、図8に示すように、ウエハ1の裏面1bに、たとえば、TEOSを用いたプラズマCVDによる酸化シリコン系絶縁膜を裏面CVD酸化シリコン膜6(第2の酸化シリコン膜)として形成する。裏面CVD酸化シリコン膜6の厚さは、たとえば、1000nm程度を好適なものとして例示することができる。このように、裏面CVD酸化シリコン膜6の厚さは、表面保護用CVD酸化シリコン膜5の厚さよりも厚くなっている。裏面CVD酸化シリコン膜6の成膜条件としては、たとえば、成膜温度:摂氏390度程度、ガス流量:TEOS/O2=1000sccm/400sccm程度を例示することができる。

【0062】

次に、図9に示すように、たとえば、BHF(Buffered Hydrogen Fluoride)等をエッチング液として、ウエハ1の表面1a側および裏面1b側に対して、浸漬エッチング等のウエットエッチングを施すことにより、ウエハ1の表面1a側および裏面1b側の酸化シリコン系絶縁膜5,6をそれぞれ500nm程度除去する。すなわち、表面保護用CVD酸化シリコン膜5をほぼ全面的に除去する。このとき、裏面CVD酸化シリコン膜6の厚さは、500nm程度となる。

【0063】

次に、図10に示すように、たとえば、摂氏1000度程度のウエット雰囲気で、熱酸化により、ウエハ1の表面1a上のほぼ全面に、表面熱酸化膜7(パッシベーション膜)としての酸化シリコン膜(厚さは、たとえば、1000nm程度)を成膜する。次に、ウエハ1の表面1a上のほぼ全面に、塗布等により、P+型不純物ドープ領域導入用レジスト膜8を形成し、通常のリソグラフィにより、パターニングする。このパターニングされたP+型不純物ドープ領域導入用レジスト膜8を用いて、たとえば、ドライエッチングにより、表面熱酸化膜7にP+型不純物ドープ領域導入用開口9を開口する。

【0064】

次に、図11に示すように、たとえば、イオン注入により、ボロン等を導入することにより、P+型不純物ドープ領域10を形成する。このイオン注入のドーズ量としては、たとえば、1015/cm2程度を例示することができる。その後、不要になったP+型不純物ドープ領域導入用レジスト膜8をアッシング等により除去する。

【0065】

次に、図12に示すように、たとえば、スパッタリング成膜により、ウエハ1の表面1a側のほぼ全面に、アルミニウム系メタル膜を成膜し、通常のリソグラフィにより、パターニングすることにより、表面メタル電極11を形成する。アルミニウム系メタル膜の組成としては、たとえば、1%前後の銅、シリコンを添加したアルミニウムを例示することができる。

【0066】

次に、図13に示すように、ウエハ1の裏面1b側に対して、例えば、バックグラインディング(研削量は、例えば、250マイクロメートル程度)を実行することにより、裏面CVD酸化シリコン膜6の全部とN+型不純物ドープ領域4の一部を除去する。

【0067】

次に、図14に示すように、たとえば、スパッタリング成膜により、ウエハ1の裏面1bのほぼ全面に、裏面メタル電極12を成膜する。

【0068】

その後、必要に応じて、ウエハプローブテスト、ダイシング等を実行して、ウエハ1を個々のチップ2に分割すると、図1から図3に示すようなデバイスとなる。

【0069】

4.本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する装置の説明(主に図15および図16)

このセクションでは、セクション5で説明する不純物外方拡散防止膜形成プロセス(変形例)に使用するCVD装置(図17および図18のプロセスに使用)およびドライエッチング装置(図19のプロセスに使用)を説明する。ここでは、CVD装置として、バッチ式熱CVD装置を例示するが、ウエハの両主面に同時に成膜できるものであれば、他の形式の装置であっても良い(CVD装置に限らない)。また、ドライエッチング装置として、枚葉式ドライエッチング装置を例示するが、ウエハの片面のみをエッチングできるものであれば、バッチ式ドライエッチング装置でも、ウエットエッチング装置でも良い。

【0070】

図15は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する縦型バッチ式熱CVD装置の模式断面図である。図16は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する枚葉式ドライエッチング装置の模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例に使用する装置を説明する。

【0071】

バッチ式熱CVD装置52を図15に示す。図15に示すように、バッチ式熱CVD装置52の主要部は、石英反応管61とその周りを取り巻くヒータ62から構成されており、石英反応管61の内部(チャンバ54)には、多数の被処理ウエハ1がセットされたウエハ治具63が置かれている。被処理ウエハ1は、たとえば、その表面1aを上に向けて、ウエハ治具63にセットされている。成膜処理時には、石英反応管61の内部は、減圧され、ガス導入口59から反応ガス等が供給され、ガス排出口60から外部に排出される。

【0072】

次に、枚葉式ドライエッチング装置53を図16に示す。図16に示すように、枚葉式ドライエッチング装置53の主要部は、その壁面が接地されたチャンバ54とその中に置かれた下部電極55(ウエハステージ)から構成されている。下部電極55上には、被処理ウエハ1がその表面1aを上に向けて置かれている。この被処理ウエハ1の表面1aには、セクション5で説明する表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)が形成されており、被処理ウエハ1の裏面1bには、裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)が形成されている。下部電極55には、たとえばバイアスコンデンサ64を介して、高周波電源57が接続されており、プラズマ58を励起する構造となっている。エッチング処理時には、チャンバ54内は、ガス排出口60を介して、真空引きされ、ガス導入口59からエッチングガス等が供給される。

【0073】

5.本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)の説明(主に図17から図20)

このセクションでは、セクション3の不純物外方拡散防止膜形成プロセス(枚葉式CVD方式:図7から図9に対応)に関する変形例(バッチ式CVD方式)を説明するが、酸化シリコン膜および窒化シリコン膜を成膜する順序は、例えば、逆にしても良い。

【0074】

この変形例は、セクション3の図7から図9のプロセスに関する変形例であり、図6および図10から図14の部分は、全く同一であるので、以下では原則として異なる部分のみを説明する。

【0075】

図17は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用酸化シリコン膜形成工程)の図3に対応するデバイス断面図である。図18は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(保護用窒化シリコン膜形成工程)の図3に対応するデバイス断面図である。図19は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用窒化シリコン膜除去工程)の図3に対応するデバイス断面図である。図20は本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明するための製造工程途上(表面保護用酸化シリコン膜除去工程)の図3に対応するデバイス断面図である。これらに基づいて、本願の前記一実施の形態の半導体装置の製造方法における前記不純物外方拡散防止膜形成プロセスに関する変形例(バッチ式CVD方式)を説明する。

【0076】

図6の状態のウエハ1は、セクション3と同様に、次の工程、すなわち、図17で説明する工程に移送される。すなわち、図17に示すように、たとえば、ウエハ1の表面1aおよび裏面1bに、たとえば、TEOSを用いたLP−CVD(Low Pressure−Chemical Vapor Deposition)等のバッチ式熱CVDによる酸化シリコン系絶縁膜を表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)として、それぞれ形成する。表面保護用CVD酸化シリコン膜5a(酸化シリコン膜)および裏面保護用CVD酸化シリコン膜5b(酸化シリコン膜)の厚さは、たとえば、500nm程度を好適なものとして例示することができる。表面保護用CVD酸化シリコン膜5aおよび裏面保護用CVD酸化シリコン膜5bの成膜条件としては、たとえば、成膜温度:摂氏700度程度、真空度:50パスカル程度、ガス流量:TEOS/O2=100sccm/5sccm程度、チャージ枚数:150枚程度を例示することができる。

【0077】

次に、図18に示すように、たとえば、ウエハ1の表面1a側および裏面1b側に、たとえば、LP−CVD等のバッチ式熱CVDによる窒化シリコン系絶縁膜を表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)として、それぞれ形成する。表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)および裏面保護用CVD窒化シリコン膜14b(窒化シリコン膜)の厚さは、たとえば、200nm程度を好適なものとして例示することができる。表面保護用CVD窒化シリコン膜14aおよび裏面保護用CVD窒化シリコン膜14bの成膜条件としては、たとえば、成膜温度:摂氏770度程度、真空度:25パスカル程度、ガス流量:SiH2Cl2/NH3=20sccm/200sccm程度、チャージ枚数:150枚程度を例示することができる。

【0078】

次に、図19に示すように、たとえば、枚葉式ドライエッチング(第1のエッチング処理)により、ウエハ1の表面1a側の表面保護用CVD窒化シリコン膜14a(窒化シリコン膜)をほぼ全面的に除去する。このドライエッチング条件としては、たとえば、真空度:3.6キロパスカル程度、ガス流量:Ar/CF4/CHF3=1000sccm/100sccm/30sccm程度を例示することができる。

【0079】

次に、図20に示すように、たとえば、BHF等をエッチング液として、ウエハ1の表面1a側および裏面1b側に対して、浸漬ウエットエッチング等のウエットエッチング(第2のエッチング処理)を施すことにより、ウエハ1の表面1a側の酸化シリコン系絶縁膜5aをほぼ全面的に除去する。

【0080】

その後、図10の工程に移送される。

【0081】

6.本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例の説明(主に図21)

このセクションでは、セクション3およびセクション5における各プロセスを、どの設備を利用して実行するかについての、使い分けの一例を説明する。従って、このような使い分けは、任意であり、他の使用方法を取ることを制限するものではない。

【0082】

図21は本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明するための各半導体製造装置群間のプロセスフロー図である。これに基づいて、本願の前記各実施形態における半導体製造装置群(製造に使用する検査装置を含む)の使用形態の一例を説明する。

【0083】

ここでは、1例として、結晶メーカの設備(第1の半導体製造装置群71)、半導体委託製造組織の設備(第2の半導体製造装置群72)および総合半導体メーカの設備(第3の半導体製造装置群73)の間の設備と工程の振り分けについて説明するが、各群の設備は、同一の組織・メーカに属していても良いし、異なる組織・メーカに属していても良い。

【0084】

(1)枚葉式CVD方式に関する説明(図21および図7から図9)

枚葉式CVD方式については、以下のように運用することが、設備の有効利用およびクロスコンタミネーションの観点から有効である。すなわち、原則として、図6の工程は、第1の半導体製造装置群71に属する装置で処理し、図7から図9の工程は、第2の半導体製造装置群72に属する装置で処理し、図10から図14の工程は、第3の半導体製造装置群73に属する装置で処理する。ただし、図9の工程は、第3の半導体製造装置群73に属する装置で処理してもよい。

【0085】

これは、図6の工程のように、ウエハ1の裏面に不純物外方拡散防止膜がついていない状態で行う高濃度の不純物と摂氏1000度以上の高温を扱う処理と、その他の処理を同一の半導体製造装置群で処理するのは、クロスコンタミネーションの観点から不適当だからである。

【0086】

また、単純な酸化シリコン膜の全面膜付け等からなる工程(図7および図8)と微細加工を伴う複雑なデバイス製造工程(図10から図14)の主要工程とを同一の半導体製造装置群で処理するのは、設備の有効利用の点から効率的ではないからである。ただし、図9の工程は、いずれの工程群に必ず付属するものであり、第1の半導体製造装置群71以外ならいずれで処理してもかまわない。

【0087】

更に、第2の半導体製造装置群72と第3の半導体製造装置群73を分ける利点は、ウエハ1の裏面1bに不純物外方拡散防止膜がついていない状態で行う高温熱処理を行う設備群と、半導体の複雑な主要工程を行う設備群を完全に分離できるところにある。

【0088】

(2)バッチ式CVD方式に関する説明(図21および図17から図20)

バッチ式CVD方式については、以下のように運用することが、設備の有効利用およびクロスコンタミネーションの観点から有効である。すなわち、原則として、図6の工程は、第1の半導体製造装置群71に属する装置で処理し、図17の工程は、第2の半導体製造装置群72に属する装置で処理し、図18から図20および図10から図14の工程は、第3の半導体製造装置群73に属する装置で処理する。

【0089】

図6の工程を第1の半導体製造装置群71に振り分けるのは、サブセクション(1)と同じ理由であるが、図18の比較的単純な窒化シリコン膜の全面膜付けを第2の半導体製造装置群72に振り分けないのは、窒化シリコン膜のバッチ式炉が酸化シリコン膜のバッチ式炉に比べると、数の少ない設備だからである。すなわち、第2の半導体製造装置群72に常備するのは、利用効率上、得策ではないからである。

【0090】

なお、第2の半導体製造装置群72と第3の半導体製造装置群73を分ける理由は、サブセクション(1)と同じ理由である。

【0091】

7.前記各実施の形態(変形例を含む)に関する補助的説明並びに全般的な考察

このセクションでは、本願発明、先の実施の形態、変形例等に関する一般的な考察並びに補足的説明を行う。

【0092】

先にセクション6の述べたクロスコンタミネーションの意義について補足的な説明を行う。半導体ウエハ工程では、多種類の製品が同一のラインを流れるのが普通である。従って、半導体の工程におけるクロスコンタミネーションは、同一工程のあるウエハから他のウエハ(同一製品または他の製品)に汚染が移行する場合と、同一の装置を利用する工程が異なる他のウエハ(同一製品または他の製品)に汚染が移行する場合がある。

【0093】

従って、前記実施の形態(変形例を含む)の効用は、単一の製品の製造方法として有効であるのみならず、多種多様な製品を製造する量産方法としても同様に有効性を有する。

【0094】

以上のように、前記実施の形態(変形例を含む)においては、微細な加工が要求されるデバイス主要部15の形成前に、ウエハ1のデバイス面1aを傷つけることなく、ウエハ1の裏面1bに不純物放出防止膜(不純物外方拡散防止膜)等を形成することで、クロスコンタミネーションを有効に防止することができる。

【0095】

また、デバイス主要部15の形成前に、ウエハ1の裏面1bに不純物放出防止膜(不純物外方拡散防止膜)等を形成するので、デバイス主要部15の形成工程に於いて、高温熱処理を伴う場合に於いても、オートドーピング等を有効に防止することができる。

【0096】

8.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0097】

例えば、前記実施の形態では、対象デバイスとして、主に光デバイス(フォトダイオード)を例に取り具体的に説明したが、本発明はそれに限定されるものではなく、パワー系半導体装置(パワーMOSFET,IGBT,パワーダイオード)、これらのパワー系半導体装置を内蔵する半導体集積回路装置、および、その他の半導体装置、半導体集積回路装置等にも適用できることは言うまでもない。

【0098】

また、前記実施の形態では、裏面に高濃度N型不純物ドープ領域を有するN型ウエハを使用する例を具体的に説明したが、本発明はそれに限定されるものではなく、裏面に高濃度P型不純物ドープ領域を有するN型ウエハを使用する場合にも適用できることは言うまでもない。また、裏面に高濃度P型不純物ドープ領域を有するP型ウエハを使用する場合にも適用できることは言うまでもない。更に、裏面に高濃度N型不純物ドープ領域を有するP型ウエハを使用する場合にも適用できることは言うまでもない。

【符号の説明】

【0099】

1 ウエハ

1a ウエハ又はチップの表面(デバイス面または第1の主面)

1b ウエハ又はチップの裏面(第2の主面)

1s 半導体基板領域

2 半導体チップ(チップ領域)

3 N−型不純物ドープ領域(第1導電型の第1の不純物ドープ領域)

4 N+型不純物ドープ領域(第2の不純物ドープ領域)

5 表面保護用CVD酸化シリコン膜(第1の酸化シリコン膜)

5a 表面保護用CVD酸化シリコン膜(酸化シリコン膜)

5b 裏面保護用CVD酸化シリコン膜(酸化シリコン膜)

6 裏面CVD酸化シリコン膜(第2の酸化シリコン膜)

7 表面熱酸化膜(パッシベーション膜)

8 P+型不純物ドープ領域導入用レジスト膜

9 P+型不純物ドープ領域導入用開口

10 P+型不純物ドープ領域

11 表面メタル電極

12 裏面メタル電極

14a 表面保護用CVD窒化シリコン膜(窒化シリコン膜)

14b 裏面保護用CVD窒化シリコン膜(窒化シリコン膜)

15 デバイスの主要部

20 セルマット領域

21 外部パッド

22 単位セル領域

23 接続配線

51 枚葉式プラズマCVD装置

52 バッチ式低圧CVD装置

53 枚葉式プラズマエッチング装置

54 チャンバ

55 下部電極(ウエハステージ)

56 上部電極

57 高周波電源

58 プラズマ

59 ガス導入口

60 ガス排出口

61 石英反応管

62 ヒータ

63 ウエハ治具

64 バイアスコンデンサ

65 絶縁シール

71 第1の半導体製造装置群

72 第2の半導体製造装置群

73 第3の半導体製造装置群

【特許請求の範囲】

【請求項1】

以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面のほぼ全面に、第1の酸化シリコン膜CVDにより、第1の酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、第2の酸化シリコン膜CVDにより、前記第1の酸化シリコン膜よりも厚い第2の酸化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第1の主面および前記第2の主面に対して、同時にウエットエッチングを実行することにより、前記第2の酸化シリコン膜を残した状態で、前記第1の酸化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【請求項2】

請求項1の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【請求項3】

請求項2の半導体装置の製造方法において、更に以下の工程を含む:

(f)前記工程(e)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【請求項4】

請求項3の半導体装置の製造方法において、前記第1の酸化シリコン膜CVDおよび前記第2の酸化シリコン膜CVDは、それぞれ枚葉式プラズマCVDである。

【請求項5】

請求項4の半導体装置の製造方法において、前記ウエットエッチングは、浸漬エッチングである。

【請求項6】

請求項5の半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)および(c)は、第2の半導体製造装置群により実行し、前記工程(d)は、前記第2の半導体製造装置群または第3の半導体製造装置群により実行し、前記工程(e)から(g)は、前記第3の半導体製造装置群により実行する。

【請求項7】

以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、酸化シリコン膜CVDにより、酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、窒化シリコン膜CVDにより、窒化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第1のエッチング処理により、前記第1の主面側の前記窒化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第2のエッチング処理により、前記第1の主面側の前記酸化シリコン膜をほぼ全面的に除去する工程;

(f)前記工程(e)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【請求項8】

請求項7の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【請求項9】

請求項8の半導体装置の製造方法において、更に以下の工程を含む:

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(h)前記工程(g)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【請求項10】

請求項9の半導体装置の製造方法において、前記酸化シリコン膜CVDおよび前記窒化シリコン膜CVDは、それぞれバッチ式CVDである。

【請求項11】

請求項10の半導体装置の製造方法において、前記バッチ式CVDは、熱CVDである。

【請求項12】

請求項11の半導体装置の製造方法において、前記第1のエッチング処理は、枚葉式ドライエッチングである。

【請求項13】

請求項12の半導体装置の製造方法において、前記第2のエッチング処理は、浸漬ウエットエッチングである。

【請求項14】

請求項13の半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)は、第2の半導体製造装置群により実行し、前記工程(c)から(h)は、第3の半導体製造装置群により実行する。

【請求項1】

以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面のほぼ全面に、第1の酸化シリコン膜CVDにより、第1の酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、第2の酸化シリコン膜CVDにより、前記第1の酸化シリコン膜よりも厚い第2の酸化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第1の主面および前記第2の主面に対して、同時にウエットエッチングを実行することにより、前記第2の酸化シリコン膜を残した状態で、前記第1の酸化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【請求項2】

請求項1の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【請求項3】

請求項2の半導体装置の製造方法において、更に以下の工程を含む:

(f)前記工程(e)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【請求項4】

請求項3の半導体装置の製造方法において、前記第1の酸化シリコン膜CVDおよび前記第2の酸化シリコン膜CVDは、それぞれ枚葉式プラズマCVDである。

【請求項5】

請求項4の半導体装置の製造方法において、前記ウエットエッチングは、浸漬エッチングである。

【請求項6】

請求項5の半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)および(c)は、第2の半導体製造装置群により実行し、前記工程(d)は、前記第2の半導体製造装置群または第3の半導体製造装置群により実行し、前記工程(e)から(g)は、前記第3の半導体製造装置群により実行する。

【請求項7】

以下の工程を含む半導体装置の製造方法:

(a)第1の主面および第2の主面を有する半導体ウエハであって、前記第1の主面のほぼ全面に、第1導電型を有する第1の不純物ドープ領域を有するとともに、前記第2の主面のほぼ全面に前記第1の不純物ドープ領域よりも高濃度の第2の不純物ドープ領域を有する前記半導体ウエハを準備する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、酸化シリコン膜CVDにより、酸化シリコン膜を成膜する工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第1の主面および前記第2の主面のほぼ全面に、窒化シリコン膜CVDにより、窒化シリコン膜を成膜する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第1のエッチング処理により、前記第1の主面側の前記窒化シリコン膜をほぼ全面的に除去する工程;

(e)前記工程(d)の後、前記半導体ウエハの前記第2の主面側の前記窒化シリコン膜を残した状態で、第2のエッチング処理により、前記第1の主面側の前記酸化シリコン膜をほぼ全面的に除去する工程;

(f)前記工程(e)の後、前記半導体ウエハの前記第1の主面側に、デバイスの主要部を形成する工程。

【請求項8】

請求項7の半導体装置の製造方法において、前記第2の不純物ドープ領域の導電型は、前記第1導電型である。

【請求項9】

請求項8の半導体装置の製造方法において、更に以下の工程を含む:

(g)前記工程(f)の後、前記半導体ウエハの前記第2の主面側に対して、バックグラインディングを実行する工程;

(h)前記工程(g)の後、前記半導体ウエハの前記第2の主面のほぼ全面に、裏面メタル電極を形成する工程。

【請求項10】

請求項9の半導体装置の製造方法において、前記酸化シリコン膜CVDおよび前記窒化シリコン膜CVDは、それぞれバッチ式CVDである。

【請求項11】

請求項10の半導体装置の製造方法において、前記バッチ式CVDは、熱CVDである。

【請求項12】

請求項11の半導体装置の製造方法において、前記第1のエッチング処理は、枚葉式ドライエッチングである。

【請求項13】

請求項12の半導体装置の製造方法において、前記第2のエッチング処理は、浸漬ウエットエッチングである。

【請求項14】

請求項13の半導体装置の製造方法において、前記工程(a)は、第1の半導体製造装置群により実行し、前記工程(b)は、第2の半導体製造装置群により実行し、前記工程(c)から(h)は、第3の半導体製造装置群により実行する。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−93442(P2013−93442A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−234730(P2011−234730)

【出願日】平成23年10月26日(2011.10.26)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月26日(2011.10.26)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]