半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば、III−V族化合物半導体を用いた電界効果トランジスタ(FET)や高電子移動度トランジスタ(HEMT)などの半導体装置の製造方法に関する。

【背景技術】

【0002】

特許文献1には、多層構造の上にダミー層を形成する技術が開示されている。ダミー層は成長炉内に残留した不要な元素を取り込むために形成される。不要な元素を取り込んだダミー層は、エッチングにより除去される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−243308号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

引用文献1に開示の半導体装置の製造方法では、基板上に多層構造を形成した後に多層構造の上にダミー層を形成するので、結晶成長前に基板に元々付着していた不純物は除去できない。

【0005】

本発明は、上述のような課題を解決するためになされたもので、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本願の発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

【発明の効果】

【0007】

本発明によれば、基板の上に不純物吸収層を形成して基板に付着している不純物及び成長炉内の不純物を吸収するので、不純物の影響を排除して所望の性能を有する半導体装置を製造できる。

【図面の簡単な説明】

【0008】

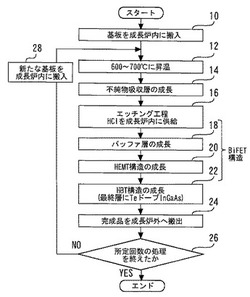

【図1】本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。

【図2】成長炉、及び成長炉に搬入された基板を示す図である。

【図3】不純物吸収層を形成したことを示す図である。

【図4】エッチング工程で成長炉内にHClガスを供給することを示す図である。

【図5】エッチング工程終了後の成長炉内を示す図である。

【図6】バッファ層を形成したことを示す図である。

【図7】バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。

【図8】本発明の実施の形態2において基板の周辺に配置するゲッター材を示す図である。

【図9】成長炉、成長炉に搬入された基板、及びゲッター材を示す図である。

【図10】本発明の実施の形態2に係る吸収層形成工程を示す図である。

【図11】成長炉内にHClガスを供給することを示す図である。

【図12】エッチング工程後の成長炉内を示す図である。

【図13】バッファ層を形成したことを示す図である。

【図14】バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。

【発明を実施するための形態】

【0009】

実施の形態1.

図1は、本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。本発明の実施の形態1に係る半導体装置の製造方法は、このフローチャートに沿って、適宜他の図を参照して説明する。まず、基板を成長炉内に搬入する(ステップ10)。この工程を搬入工程と称する。図2は、成長炉、及び成長炉に搬入された基板を示す図である。成長炉30はMOCVD装置で形成されている。成長炉30には、成長炉内32の排気を行うための接続管34が接続されている。基板36はGaAsで形成され、半絶縁性となっている。

【0010】

基板36を成長炉30に搬入する前に成長炉内32で行われた処理に起因して、成長炉30にはTeが付着している。また、基板36の表面にはSiが付着している。Teなどの不要物とSiなどの不要物をまとめて「不純物」という。

【0011】

次いで、成長炉内32の温度を600℃〜700℃まで昇温する(ステップ12)。次いで、成長炉内32を高温(600℃〜700℃)に維持しつつ、基板36の上と成長炉30の内壁に不純物吸収層を形成する(ステップ14)。この工程を吸収層形成工程と称する。図3は、不純物吸収層を形成したことを示す図である。不純物吸収層40、42は成長炉内32及び基板36表面の不純物を吸収するものである。図3に示すように、基板36の上には不純物吸収層40を形成し、成長炉30の内壁には不純物吸収層42を形成する。不純物吸収層40、42は、成長炉内32にTMGa、TMAl、及びAsH3を供給して成長したアンドープAl0.50Ga0.50As層で形成する。成長温度は600℃〜700℃程度である。成長圧力は60mbarである。キャリアガスには水素を用いることができる。不純物吸収層40、42は500nm程度の膜厚とする。

【0012】

不純物吸収層40、42の成長中に、成長炉内32のTeや基板36表面のSiなどの不純物が不純物吸収層40、42内に取り込まれる。吸収層形成工程を終えると、成長炉内32へのTMGa、TMAl、及びAsH3の供給を停止する。

【0013】

次いで、不純物吸収層40、42と、基板36の一部とをエッチングする(ステップ16)。この工程をエッチング工程と称する。エッチング工程では、成長炉内32にHClガスを供給する。図4は、エッチング工程で成長炉内にHClガスを供給することを示す図である。成長炉内32に供給されたHClガス50により不純物吸収層40、42と、基板36の一部をエッチングする。基板36は1〜2μm程度エッチングする。図5は、エッチング工程終了後の成長炉内を示す図である。エッチング工程前の基板36の厚さはaで表されるが(図4参照)、エッチング工程後はこれがb(<a)となる。エッチング工程により基板36は薄化基板60となる。なおエッチング工程終了まで成長炉内32は高温(600℃〜700℃まで)に維持する。

【0014】

次いで、エッチング工程の後速やかに、薄化基板60の上にバッファ層を形成する(ステップ18)。この工程をバッファ層形成工程と称する。図6は、バッファ層を形成したことを示す図である。バッファ層62は、100nm程度の層厚のアンドープGaAs層で形成する。

【0015】

次いで、バッファ層62の上にHEMT構造を形成する(ステップ20)。HEMT構造はソースドレイン間の電流が流れるチャネル層、及びチャネル層に電子を供給する電子供給層をバッファ層62の上に備える。次いで、HEMT構造の上にHBT構造を形成する(ステップ22)。ステップ20とステップ22ではエピタキシャル半導体層を形成する。図7は、バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。このように、バッファ層62の上にはHEMTとHBT64を形成する。バッファ層、HEMT構造、及びHBT構造は、BiFET(Bipolar Field Effect Transistor)構造と呼ばれる。

【0016】

ところで、ステップ22で形成するHBT構造の最終層はコンタクト層として用いられるTeドープIn0.50Ga0.50As層である。この最終層の形成により成長炉30には不純物であるTeやTeドープIn0.50Ga0.50Asが残留する。

【0017】

次いで、上述の処理が終了して完成品となった半導体装置を、成長炉30の外へ搬出する(ステップ24)。次いで、上述の処理が所定回数実施されたか否かをチェックする(ステップ26)。上述の処理が所定回数実施された場合は、処理を終了する。上述の処理が所定回数実施されていない場合は、新たな基板を成長炉内32に搬入する(ステップ28)。そして、当該新たな基板について、ステップ12以降の工程を実施する。

【0018】

ところで、HEMT構造のリーク電流を抑制し、かつHEMT構造の電気特性を保つためには、バッファ層を高抵抗化してHEMT構造のチャネル層の電流が外に漏れずチャネル層だけに流れるようにする必要がある。しかし、不純物がバッファ層に混入するとバッファ層を高抵抗化できないことがある。ところが、本発明の実施の形態1に係る半導体装置の製造方法では、不純物吸収層40、42により成長炉内32の不純物を吸収することができる。また、不純物吸収層40を基板36の上に形成するので、基板36の不純物を吸収することができる。よって、成長炉内32の不純物、及び基板36に元々付着していた不純物がバッファ層62に混入することを防止できる。また、エッチング工程後速やかにバッファ層62を形成することで、バッファ層62と薄化基板60の界面近傍への不純物混入が抑制された高抵抗なバッファ層62を得ることができる。

【0019】

エッチング工程で基板36をエッチングすることで、表面が清浄な薄化基板60を形成することができる。よって、薄化基板60の上に形成するバッファ層62に不純物が混入することを防止できる。ここで、エッチング工程を実施すると、薄化基板60の表面平坦性を低下させてしまう。しかしながら、薄化基板60の上にバッファ層62を形成したことでエッチングにより悪化した表面平坦性を回復させることができる。

【0020】

本発明の実施の形態1に係る半導体装置の製造方法では、不純物の少ない状態でバッファ層を形成できるので、基板の前処理や、不純物低減のためのダミー成長が必要なくなる。よって半導体装置の生産性向上、及びコスト削減ができる。

【0021】

不純物吸収層40、42はAlを含んでいるため、効果的に不純物を取り込むことが可能となっている。しかしながら、不純物吸収層40、42の組成はアンドープAl0.50Ga0.50As層に限定されない。不純物吸収層は、III族元素であるAl、Ga、Inのうち少なくとも1種とV族元素であるN、P、Asのうち少なくとも一種からなるIII−V族化合物半導体で形成されればよい。III族原料としてトリメチルガリウム(TMGa)、トリメチルアルミニウム(TMAl)、及びトリメチルインジウム(TMIn)、V族原料としてアルシン(AsH3)、及びホスフィン(PH3)、ドーパントとしてシラン(SiH4)、及びジイソプロピルテルル(DIPTe)を用いることができる。なお、不純物吸収層は必ずしも基板と格子整合させる必要はない。

【0022】

また、エッチング工程で用いたHClガスを、他のハロゲン化合物ガスで代用してもよい。さらに、バッファ層の上には、HEMT構造とHBT構造を形成したが、半導体層を形成する半導体層形成工程でバッファ層の上に素子を形成する限りにおいて特に限定されない。不純物としては、TeとSiだけでなく、例えばSeなどがある。エッチング工程における基板36のエッチング量は不純物量を考慮して適宜定めることができる。

【0023】

実施の形態2.

本発明の実施の形態2に係る半導体装置の製造方法は、前述の実施の形態1に係る半導体装置の製造方法と基本的な処理は共通するが、実施の形態1の場合よりも更に成長炉内の不純物を低減できるものである。以後、本発明の実施の形態2に係る半導体装置の製造方法を、実施の形態1と同じ部分は省略しつつ説明する。

【0024】

図8は、本発明の実施の形態2において基板の周辺に配置するゲッター材を示す図である。基板36の周辺にはゲッター材70を配置する。ゲッター材70とは、不純物を吸収するために基板の周辺に配置するものである。図9は、成長炉、成長炉に搬入された基板、及びゲッター材を示す図である。ゲッター材70は、ダミー基板70aを備えている。ダミー基板70aはGaAsで形成されている。ダミー基板70aの上にはゲッター層70bが形成されている。ゲッター層70bは、吸収層形成工程で形成される不純物吸収層と同じ材料、すなわちアンドープAl0.50Ga0.50As層で形成されている。ゲッター層70bの上にはコーティング膜70cが形成されている。コーティング膜70cは、不純物を吸収しない膜であるアンドープGaAs膜で形成されている。

【0025】

次いで、成長炉内32の温度を600℃〜700℃まで昇温し、不純物吸収層を形成する。図10は、本発明の実施の形態2に係る吸収層形成工程を示す図である。吸収層形成工程では、ゲッター材70の上に不純物吸収層と同じ材料の追加不純物吸収層72を形成する。追加不純物吸収層72は不純物吸収層40と同時に形成する。

【0026】

次いでエッチング工程に処理を進める。エッチング工程では、成長炉内32にHClガスを供給する。図11は、成長炉内にHClガスを供給することを示す図である。エッチング工程では、追加不純物吸収層72、コーティング膜70c、及びゲッター層70bの一部をエッチングする。このエッチングは、不純物吸収層40と、基板36の一部とのエッチングと同時に行う。図12は、エッチング工程後の成長炉内を示す図である。ゲッター材70の表面には、ゲッター層がエッチングされた薄化ゲッター層70b´が露出している。エッチング終了直後の成長炉内32は600℃〜700℃の高温となっており、少量の不純物が残存している。この少量の不純物は薄化ゲッター層70b´に吸収される。

【0027】

次いで、薄化基板60の上にバッファ層を形成する。図13は、バッファ層を形成したことを示す図である。次いで、HEMT構造、及びHBT構造をこの順に形成する。図14は、バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。次いで、完成品を成長炉外に搬出し、必要に応じて新たな基板を成長炉内32へ搬入する。

【0028】

本発明の実施の形態2に係る半導体装置の製造方法によれば、不純物吸収層40,42に加えて、追加不純物吸収層72を形成するので吸収層成長工程において効率的に不純物を除去できる。エッチング工程後は炉内が高温を維持しているので、エッチング工程終了後からバッファ層成長前に薄化基板60に不純物が付着するおそれがある。しかしながら、本発明の実施の形態2に係る半導体装置の製造方法によれば、エッチング工程終了後に炉内に残る少量の不純物を薄化ゲッター層70b´により吸収できるので、薄化基板60を清浄に保つことができる。

【0029】

ところで、不純物を吸収しない膜であるコーティング膜70cは以下のような意義を有する。ゲッター層70bは、エッチング工程終了までコーティング膜70cに覆われているため、エッチング工程終了までは不純物を吸収しない。そして、エッチング工程によりエッチングされた薄化ゲッター層70b´は、エッチング工程終了後にはじめて外部に露出する。従って、薄化ゲッター層70b´は、エッチング工程終了後からバッファ層62の形成前に不純物を吸収する能力が高い。そのため、薄化ゲッター層70b´により図12で説明した少量の不純物を十分に吸収し、薄化基板60に不純物が付着することを防止できる。このようにコーティング膜70cはゲッター層70bの機能をエッチング終了時まで温存しておくために形成するものである。

【0030】

コーティング膜70cの材料は、不純物を吸収しない材料であれば特に限定されない。また、コーティング膜70cを省略したゲッター材を用いても良い。ゲッター材70は、ダミー基板上に成長炉内の不純物を吸収するゲッター層が形成されれば特に限定されない。なお、本発明の実施の形態2に係る半導体装置の製造方法は、少なくとも実施の形態1に係る発明と同程度の変形が可能である。

【符号の説明】

【0031】

30 成長炉、 32 成長炉内、 34 接続管、 36 基板、 40,42 不純物吸収層、 50 HClガス、 60 薄化基板、 62 バッファ層、 64 HEMTとHBT、 70 ゲッター材、 70a ダミー基板、 70b ゲッター層、 70b´ 薄化ゲッター層、 70c コーティング膜、 72 追加不純物吸収層

【技術分野】

【0001】

本発明は、例えば、III−V族化合物半導体を用いた電界効果トランジスタ(FET)や高電子移動度トランジスタ(HEMT)などの半導体装置の製造方法に関する。

【背景技術】

【0002】

特許文献1には、多層構造の上にダミー層を形成する技術が開示されている。ダミー層は成長炉内に残留した不要な元素を取り込むために形成される。不要な元素を取り込んだダミー層は、エッチングにより除去される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−243308号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

引用文献1に開示の半導体装置の製造方法では、基板上に多層構造を形成した後に多層構造の上にダミー層を形成するので、結晶成長前に基板に元々付着していた不純物は除去できない。

【0005】

本発明は、上述のような課題を解決するためになされたもので、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本願の発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

【発明の効果】

【0007】

本発明によれば、基板の上に不純物吸収層を形成して基板に付着している不純物及び成長炉内の不純物を吸収するので、不純物の影響を排除して所望の性能を有する半導体装置を製造できる。

【図面の簡単な説明】

【0008】

【図1】本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。

【図2】成長炉、及び成長炉に搬入された基板を示す図である。

【図3】不純物吸収層を形成したことを示す図である。

【図4】エッチング工程で成長炉内にHClガスを供給することを示す図である。

【図5】エッチング工程終了後の成長炉内を示す図である。

【図6】バッファ層を形成したことを示す図である。

【図7】バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。

【図8】本発明の実施の形態2において基板の周辺に配置するゲッター材を示す図である。

【図9】成長炉、成長炉に搬入された基板、及びゲッター材を示す図である。

【図10】本発明の実施の形態2に係る吸収層形成工程を示す図である。

【図11】成長炉内にHClガスを供給することを示す図である。

【図12】エッチング工程後の成長炉内を示す図である。

【図13】バッファ層を形成したことを示す図である。

【図14】バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。

【発明を実施するための形態】

【0009】

実施の形態1.

図1は、本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。本発明の実施の形態1に係る半導体装置の製造方法は、このフローチャートに沿って、適宜他の図を参照して説明する。まず、基板を成長炉内に搬入する(ステップ10)。この工程を搬入工程と称する。図2は、成長炉、及び成長炉に搬入された基板を示す図である。成長炉30はMOCVD装置で形成されている。成長炉30には、成長炉内32の排気を行うための接続管34が接続されている。基板36はGaAsで形成され、半絶縁性となっている。

【0010】

基板36を成長炉30に搬入する前に成長炉内32で行われた処理に起因して、成長炉30にはTeが付着している。また、基板36の表面にはSiが付着している。Teなどの不要物とSiなどの不要物をまとめて「不純物」という。

【0011】

次いで、成長炉内32の温度を600℃〜700℃まで昇温する(ステップ12)。次いで、成長炉内32を高温(600℃〜700℃)に維持しつつ、基板36の上と成長炉30の内壁に不純物吸収層を形成する(ステップ14)。この工程を吸収層形成工程と称する。図3は、不純物吸収層を形成したことを示す図である。不純物吸収層40、42は成長炉内32及び基板36表面の不純物を吸収するものである。図3に示すように、基板36の上には不純物吸収層40を形成し、成長炉30の内壁には不純物吸収層42を形成する。不純物吸収層40、42は、成長炉内32にTMGa、TMAl、及びAsH3を供給して成長したアンドープAl0.50Ga0.50As層で形成する。成長温度は600℃〜700℃程度である。成長圧力は60mbarである。キャリアガスには水素を用いることができる。不純物吸収層40、42は500nm程度の膜厚とする。

【0012】

不純物吸収層40、42の成長中に、成長炉内32のTeや基板36表面のSiなどの不純物が不純物吸収層40、42内に取り込まれる。吸収層形成工程を終えると、成長炉内32へのTMGa、TMAl、及びAsH3の供給を停止する。

【0013】

次いで、不純物吸収層40、42と、基板36の一部とをエッチングする(ステップ16)。この工程をエッチング工程と称する。エッチング工程では、成長炉内32にHClガスを供給する。図4は、エッチング工程で成長炉内にHClガスを供給することを示す図である。成長炉内32に供給されたHClガス50により不純物吸収層40、42と、基板36の一部をエッチングする。基板36は1〜2μm程度エッチングする。図5は、エッチング工程終了後の成長炉内を示す図である。エッチング工程前の基板36の厚さはaで表されるが(図4参照)、エッチング工程後はこれがb(<a)となる。エッチング工程により基板36は薄化基板60となる。なおエッチング工程終了まで成長炉内32は高温(600℃〜700℃まで)に維持する。

【0014】

次いで、エッチング工程の後速やかに、薄化基板60の上にバッファ層を形成する(ステップ18)。この工程をバッファ層形成工程と称する。図6は、バッファ層を形成したことを示す図である。バッファ層62は、100nm程度の層厚のアンドープGaAs層で形成する。

【0015】

次いで、バッファ層62の上にHEMT構造を形成する(ステップ20)。HEMT構造はソースドレイン間の電流が流れるチャネル層、及びチャネル層に電子を供給する電子供給層をバッファ層62の上に備える。次いで、HEMT構造の上にHBT構造を形成する(ステップ22)。ステップ20とステップ22ではエピタキシャル半導体層を形成する。図7は、バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。このように、バッファ層62の上にはHEMTとHBT64を形成する。バッファ層、HEMT構造、及びHBT構造は、BiFET(Bipolar Field Effect Transistor)構造と呼ばれる。

【0016】

ところで、ステップ22で形成するHBT構造の最終層はコンタクト層として用いられるTeドープIn0.50Ga0.50As層である。この最終層の形成により成長炉30には不純物であるTeやTeドープIn0.50Ga0.50Asが残留する。

【0017】

次いで、上述の処理が終了して完成品となった半導体装置を、成長炉30の外へ搬出する(ステップ24)。次いで、上述の処理が所定回数実施されたか否かをチェックする(ステップ26)。上述の処理が所定回数実施された場合は、処理を終了する。上述の処理が所定回数実施されていない場合は、新たな基板を成長炉内32に搬入する(ステップ28)。そして、当該新たな基板について、ステップ12以降の工程を実施する。

【0018】

ところで、HEMT構造のリーク電流を抑制し、かつHEMT構造の電気特性を保つためには、バッファ層を高抵抗化してHEMT構造のチャネル層の電流が外に漏れずチャネル層だけに流れるようにする必要がある。しかし、不純物がバッファ層に混入するとバッファ層を高抵抗化できないことがある。ところが、本発明の実施の形態1に係る半導体装置の製造方法では、不純物吸収層40、42により成長炉内32の不純物を吸収することができる。また、不純物吸収層40を基板36の上に形成するので、基板36の不純物を吸収することができる。よって、成長炉内32の不純物、及び基板36に元々付着していた不純物がバッファ層62に混入することを防止できる。また、エッチング工程後速やかにバッファ層62を形成することで、バッファ層62と薄化基板60の界面近傍への不純物混入が抑制された高抵抗なバッファ層62を得ることができる。

【0019】

エッチング工程で基板36をエッチングすることで、表面が清浄な薄化基板60を形成することができる。よって、薄化基板60の上に形成するバッファ層62に不純物が混入することを防止できる。ここで、エッチング工程を実施すると、薄化基板60の表面平坦性を低下させてしまう。しかしながら、薄化基板60の上にバッファ層62を形成したことでエッチングにより悪化した表面平坦性を回復させることができる。

【0020】

本発明の実施の形態1に係る半導体装置の製造方法では、不純物の少ない状態でバッファ層を形成できるので、基板の前処理や、不純物低減のためのダミー成長が必要なくなる。よって半導体装置の生産性向上、及びコスト削減ができる。

【0021】

不純物吸収層40、42はAlを含んでいるため、効果的に不純物を取り込むことが可能となっている。しかしながら、不純物吸収層40、42の組成はアンドープAl0.50Ga0.50As層に限定されない。不純物吸収層は、III族元素であるAl、Ga、Inのうち少なくとも1種とV族元素であるN、P、Asのうち少なくとも一種からなるIII−V族化合物半導体で形成されればよい。III族原料としてトリメチルガリウム(TMGa)、トリメチルアルミニウム(TMAl)、及びトリメチルインジウム(TMIn)、V族原料としてアルシン(AsH3)、及びホスフィン(PH3)、ドーパントとしてシラン(SiH4)、及びジイソプロピルテルル(DIPTe)を用いることができる。なお、不純物吸収層は必ずしも基板と格子整合させる必要はない。

【0022】

また、エッチング工程で用いたHClガスを、他のハロゲン化合物ガスで代用してもよい。さらに、バッファ層の上には、HEMT構造とHBT構造を形成したが、半導体層を形成する半導体層形成工程でバッファ層の上に素子を形成する限りにおいて特に限定されない。不純物としては、TeとSiだけでなく、例えばSeなどがある。エッチング工程における基板36のエッチング量は不純物量を考慮して適宜定めることができる。

【0023】

実施の形態2.

本発明の実施の形態2に係る半導体装置の製造方法は、前述の実施の形態1に係る半導体装置の製造方法と基本的な処理は共通するが、実施の形態1の場合よりも更に成長炉内の不純物を低減できるものである。以後、本発明の実施の形態2に係る半導体装置の製造方法を、実施の形態1と同じ部分は省略しつつ説明する。

【0024】

図8は、本発明の実施の形態2において基板の周辺に配置するゲッター材を示す図である。基板36の周辺にはゲッター材70を配置する。ゲッター材70とは、不純物を吸収するために基板の周辺に配置するものである。図9は、成長炉、成長炉に搬入された基板、及びゲッター材を示す図である。ゲッター材70は、ダミー基板70aを備えている。ダミー基板70aはGaAsで形成されている。ダミー基板70aの上にはゲッター層70bが形成されている。ゲッター層70bは、吸収層形成工程で形成される不純物吸収層と同じ材料、すなわちアンドープAl0.50Ga0.50As層で形成されている。ゲッター層70bの上にはコーティング膜70cが形成されている。コーティング膜70cは、不純物を吸収しない膜であるアンドープGaAs膜で形成されている。

【0025】

次いで、成長炉内32の温度を600℃〜700℃まで昇温し、不純物吸収層を形成する。図10は、本発明の実施の形態2に係る吸収層形成工程を示す図である。吸収層形成工程では、ゲッター材70の上に不純物吸収層と同じ材料の追加不純物吸収層72を形成する。追加不純物吸収層72は不純物吸収層40と同時に形成する。

【0026】

次いでエッチング工程に処理を進める。エッチング工程では、成長炉内32にHClガスを供給する。図11は、成長炉内にHClガスを供給することを示す図である。エッチング工程では、追加不純物吸収層72、コーティング膜70c、及びゲッター層70bの一部をエッチングする。このエッチングは、不純物吸収層40と、基板36の一部とのエッチングと同時に行う。図12は、エッチング工程後の成長炉内を示す図である。ゲッター材70の表面には、ゲッター層がエッチングされた薄化ゲッター層70b´が露出している。エッチング終了直後の成長炉内32は600℃〜700℃の高温となっており、少量の不純物が残存している。この少量の不純物は薄化ゲッター層70b´に吸収される。

【0027】

次いで、薄化基板60の上にバッファ層を形成する。図13は、バッファ層を形成したことを示す図である。次いで、HEMT構造、及びHBT構造をこの順に形成する。図14は、バッファ層の上にHEMT構造とHBT構造を形成したことを示す図である。次いで、完成品を成長炉外に搬出し、必要に応じて新たな基板を成長炉内32へ搬入する。

【0028】

本発明の実施の形態2に係る半導体装置の製造方法によれば、不純物吸収層40,42に加えて、追加不純物吸収層72を形成するので吸収層成長工程において効率的に不純物を除去できる。エッチング工程後は炉内が高温を維持しているので、エッチング工程終了後からバッファ層成長前に薄化基板60に不純物が付着するおそれがある。しかしながら、本発明の実施の形態2に係る半導体装置の製造方法によれば、エッチング工程終了後に炉内に残る少量の不純物を薄化ゲッター層70b´により吸収できるので、薄化基板60を清浄に保つことができる。

【0029】

ところで、不純物を吸収しない膜であるコーティング膜70cは以下のような意義を有する。ゲッター層70bは、エッチング工程終了までコーティング膜70cに覆われているため、エッチング工程終了までは不純物を吸収しない。そして、エッチング工程によりエッチングされた薄化ゲッター層70b´は、エッチング工程終了後にはじめて外部に露出する。従って、薄化ゲッター層70b´は、エッチング工程終了後からバッファ層62の形成前に不純物を吸収する能力が高い。そのため、薄化ゲッター層70b´により図12で説明した少量の不純物を十分に吸収し、薄化基板60に不純物が付着することを防止できる。このようにコーティング膜70cはゲッター層70bの機能をエッチング終了時まで温存しておくために形成するものである。

【0030】

コーティング膜70cの材料は、不純物を吸収しない材料であれば特に限定されない。また、コーティング膜70cを省略したゲッター材を用いても良い。ゲッター材70は、ダミー基板上に成長炉内の不純物を吸収するゲッター層が形成されれば特に限定されない。なお、本発明の実施の形態2に係る半導体装置の製造方法は、少なくとも実施の形態1に係る発明と同程度の変形が可能である。

【符号の説明】

【0031】

30 成長炉、 32 成長炉内、 34 接続管、 36 基板、 40,42 不純物吸収層、 50 HClガス、 60 薄化基板、 62 バッファ層、 64 HEMTとHBT、 70 ゲッター材、 70a ダミー基板、 70b ゲッター層、 70b´ 薄化ゲッター層、 70c コーティング膜、 72 追加不純物吸収層

【特許請求の範囲】

【請求項1】

基板を成長炉内に搬入する搬入工程と、

前記基板の上と前記成長炉の内壁に、前記基板表面と前記成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、

前記不純物吸収層と、前記基板の一部とをエッチングすることで前記基板を薄化基板にするエッチング工程と、

前記薄化基板の上にバッファ層を形成するバッファ層形成工程と、

前記バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

前記不純物吸収層は、III族元素であるAl、Ga、Inのうち少なくとも1種とV族元素であるN、P、Asのうち少なくとも1種からなるIII−V族化合物半導体で形成されることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記エッチングにはハロゲン化合物ガスを用いることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記吸収層形成工程では、ダミー基板上に前記成長炉内の不純物を吸収するゲッター層が形成されたゲッター材の上に、前記不純物吸収層と同じ材料の追加不純物吸収層を形成し、

前記エッチング工程では、前記追加不純物吸収層と、前記ゲッター層の一部とをエッチングすることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記ゲッター層は前記不純物吸収層と同じ材料で形成されたことを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項6】

前記ゲッター材の表面には、前記不純物を吸収しないコーティング膜が形成され、

前記コーティング膜は前記エッチング工程で除去されることを特徴とする請求項4又は5に記載の半導体装置の製造方法。

【請求項7】

前記半導体層形成工程で最後に形成される層はTeを含む層であることを特徴とする請求項1乃至6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

前記半導体層形成工程ではHEMTとHBTを形成することを特徴とする請求項1乃至7のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

基板を成長炉内に搬入する搬入工程と、

前記基板の上と前記成長炉の内壁に、前記基板表面と前記成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、

前記不純物吸収層と、前記基板の一部とをエッチングすることで前記基板を薄化基板にするエッチング工程と、

前記薄化基板の上にバッファ層を形成するバッファ層形成工程と、

前記バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

前記不純物吸収層は、III族元素であるAl、Ga、Inのうち少なくとも1種とV族元素であるN、P、Asのうち少なくとも1種からなるIII−V族化合物半導体で形成されることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記エッチングにはハロゲン化合物ガスを用いることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記吸収層形成工程では、ダミー基板上に前記成長炉内の不純物を吸収するゲッター層が形成されたゲッター材の上に、前記不純物吸収層と同じ材料の追加不純物吸収層を形成し、

前記エッチング工程では、前記追加不純物吸収層と、前記ゲッター層の一部とをエッチングすることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記ゲッター層は前記不純物吸収層と同じ材料で形成されたことを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項6】

前記ゲッター材の表面には、前記不純物を吸収しないコーティング膜が形成され、

前記コーティング膜は前記エッチング工程で除去されることを特徴とする請求項4又は5に記載の半導体装置の製造方法。

【請求項7】

前記半導体層形成工程で最後に形成される層はTeを含む層であることを特徴とする請求項1乃至6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

前記半導体層形成工程ではHEMTとHBTを形成することを特徴とする請求項1乃至7のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−93489(P2013−93489A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−235691(P2011−235691)

【出願日】平成23年10月27日(2011.10.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]