半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、MISFETを有する半導体装置の製造に適用して有効な技術に関する。

【背景技術】

【0002】

MISFETなどの半導体素子を半導体基板に形成し、更に半導体基板上の配線とコンタクトプラグなどを介して半導体素子との間を結線することで、半導体装置が製造される。

【0003】

素子の微細化に伴い、MISFETとコンタクトプラグとの間の距離も小さくなり、MISFETを構成するゲート電極とコンタクトプラグとの間の短絡を回避する技術が重要となる。

【0004】

例えば、特開2002−319592号公報(特許文献1)には、ゲート電極とコンタクト部材との短絡のない、かつ、微細化にも対応しうる半導体装置の製造方法が開示されている。例えば、Si基板(1)上に、ゲート絶縁膜(2)、ゲート電極(3a)、ゲート上保護層(4a)を形成した後、低濃度ソース・ドレイン領域(6)を形成する。ゲート電極(3a)の側面上に第1サイドウォール(15a)と、第2サイドウォールとを形成した後、これをマスクとして用いるイオン注入により、高濃度ソース・ドレイン領域(9)を形成する。第2サイドウォール(16a)を選択的に除去した後、ポケット注入領域(Rpo)を形成し、全面保護膜(12)を堆積する。その後、層間絶縁膜(10)の堆積と、高濃度ソース・ドレイン領域(9)に到達するコンタクトホール(Hct)の形成と、プラグ電極(11)の形成とを行うという工程が開示されている。

【0005】

また、特開2000−306860号公報(特許文献2)には、コンタクトホールでの素子コンタクト面の洗浄を行った場合でも、コンタクトホール内におけるゲート電極やソース・ドレイン領域等の短絡を確実に防止して、素子不良が発生することがない半導体装置の製造方法が開示されている。例えば、シリコン基板(101)上に素子を形成し、前記素子を覆う層間絶縁膜(111)を形成し、さらに前記層間絶縁膜(111)に前記素子を露呈するコンタクトホール(113)を開口する。次いで、コンタクトホール(113)の内底面に露呈される素子のコンタクト面を洗浄し、しかる上で前記コンタクトホール(113)内に導電材を埋め込んでコンタクトプラグ(115)を形成する。このような工程を含む半導体装置の製造方法において、前記コンタクトホール(113)を開口した後、前記素子のコンタクト面を洗浄する工程の間に、前記洗浄剤に対して耐性のあるストッパ膜(114)を前記コンタクトホール(113)の内側面に形成する工程が開示されている。なお、(かっこ)内は当該文献に記載の符号である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−319592号公報

【特許文献2】特開2000−306860号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者は、MISFETを有する半導体装置の研究開発に従事し、当該半導体装置の特性向上について検討している。

【0008】

前述したように、素子の微細化に伴い、MISFETを構成するゲート電極とコンタクトプラグとの距離が小さくなり、これらの短絡を回避する技術が望まれる。追って詳細に説明するように、本発明者の検討によれば、上記短絡の一要因として、ゲート電極の上部に形成されるシリサイド膜の横方向(ゲート長方向)への張り出しが挙げられることが判明した。

【0009】

そこで、本発明の目的は、特性の良好な半導体装置を製造するための半導体装置の製造方法を提供することにある。特に、ゲート電極とコンタクトプラグとの短絡を低減できる半導体装置の製造方法を提供することにある。

【0010】

本発明の上記目的およびその他の目的と新規な特徴は、本願明細書の記載および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0012】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、半導体膜と上記半導体膜上の絶縁膜との積層膜を形成する工程と、(b)上記積層膜をパターニングすることによりゲート電極と上記ゲート電極の上部に配置され上記絶縁膜よりなる上部絶縁膜との積層体を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記積層体の側壁に側壁膜を形成する工程と、(d)上記(c)工程の後、上記上部絶縁膜を除去する工程と、(e)上記(d)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中にヒ素(As)を注入する工程と、を有する。

【0013】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方にゲート電極を形成する工程と、(b)上記(a)工程の後、上記ゲート電極の側壁に側壁膜を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記ゲート電極および上記側壁膜上に絶縁膜を形成する工程と、(d)上記(c)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中に、上記絶縁膜を介して、ヒ素(As)を注入する工程と、を有する。

【0014】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方にゲート電極を形成する工程と、(b)上記(a)工程の後、上記ゲート電極の側壁に側壁膜を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中に、上記絶縁膜を介して、ヒ素(As)を注入する工程と、(d)上記(c)工程の後、上記ゲート電極の上部をエッチングする工程と、を有する。

【発明の効果】

【0015】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。特に、ゲート電極とコンタクトプラグとの短絡を低減し、半導体装置の性能を向上することができる。

【図面の簡単な説明】

【0016】

【図1】実施の形態1の半導体装置の製造工程を示す要部断面図である。

【図2】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図1に続く半導体装置の製造工程を示す要部断面図である。

【図3】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図2に続く半導体装置の製造工程を示す要部断面図である。

【図4】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図3に続く半導体装置の製造工程を示す要部断面図である。

【図5】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図4に続く半導体装置の製造工程を示す要部断面図である。

【図6】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図5に続く半導体装置の製造工程を示す要部断面図である。

【図7】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図6に続く半導体装置の製造工程を示す要部断面図である。

【図8】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図7に続く半導体装置の製造工程を示す要部断面図である。

【図9】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図8に続く半導体装置の製造工程を示す要部断面図である。

【図10】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図9に続く半導体装置の製造工程を示す要部断面図である。

【図11】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図10に続く半導体装置の製造工程を示す要部断面図である。

【図12】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図11に続く半導体装置の製造工程を示す要部断面図である。

【図13】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図12に続く半導体装置の製造工程を示す要部断面図である。

【図14】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図13に続く半導体装置の製造工程を示す要部断面図である。

【図15】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図14に続く半導体装置の製造工程を示す要部断面図である。

【図16】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図15に続く半導体装置の製造工程を示す要部断面図である。

【図17】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図16に続く半導体装置の製造工程を示す要部断面図である。

【図18】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図17に続く半導体装置の製造工程を示す要部断面図である。

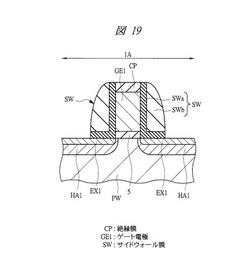

【図19】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図20】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図21】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図22】実施の形態1の比較例の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図23】実施の形態1の比較例の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図24】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図25】nチャネル型MISFETの断面写真である。

【図26】pチャネル型MISFETの断面写真である。

【図27】nチャネル型MISFETのゲート電極にリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。

【図28】nチャネル型MISFETのゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。

【図29】実施の形態1の半導体装置のnチャネル型MISFETの断面図である。

【図30】実施の形態1の半導体装置のnチャネル型MISFETの断面図である。

【図31】実施の形態1の半導体装置のpチャネル型MISFETの断面図である。

【図32】実施の形態1の半導体装置のpチャネル型MISFETの断面図である。

【図33】実施の形態2の半導体装置の製造工程を示す要部断面図である。

【図34】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図33に続く半導体装置の製造工程を示す要部断面図である。

【図35】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図34に続く半導体装置の製造工程を示す要部断面図である。

【図36】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図35に続く半導体装置の製造工程を示す要部断面図である。

【図37】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図36に続く半導体装置の製造工程を示す要部断面図である。

【図38】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図39】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図40】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図41】実施の形態3の半導体装置の製造工程を示す要部断面図である。

【図42】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図41に続く半導体装置の製造工程を示す要部断面図である。

【図43】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図42に続く半導体装置の製造工程を示す要部断面図である。

【図44】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図43に続く半導体装置の製造工程を示す要部断面図である。

【図45】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図44に続く半導体装置の製造工程を示す要部断面図である。

【図46】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図45に続く半導体装置の製造工程を示す要部断面図である。

【図47】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図48】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図49】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【発明を実施するための形態】

【0017】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0018】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等(個数、数値、量、範囲等を含む)についても同様である。

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0020】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0021】

(実施の形態1)

図面を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成を明確にする。図1〜図21は、本実施の形態の半導体装置の製造工程を示す要部断面図である。本実施の形態の半導体装置は、MISFET(Metal Insulator Semiconductor Field Effect Transistor)を有し、ここでは、CMIS(ComplementaryMIS)構成の2つのトランジスタ(Qn、Qp)を有する(図18等参照)。

【0022】

まず、図1に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次いで、半導体基板1の主面に素子分離領域2を形成する。素子分離領域2は酸化シリコン膜などの絶縁体からなり、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon)法などにより形成される。例えば、半導体基板1に溝(素子分離溝)を形成し、この溝の内部に絶縁膜を埋め込むことにより、素子分離領域2を形成することができる。素子分離領域2によって、nチャネル型MISFET(MIS型電界効果トランジスタ)Qnが形成される領域(活性領域)であるnMIS形成領域1Aと、pチャネル型MISFETQpが形成される領域(活性領域)であるpMIS形成領域1Bとが規定される。

【0023】

次いで、半導体基板1の表面の汚染防止のための薄い絶縁膜(スルー膜)3を半導体基板1の表面(主面)に形成した後、図2に示すように、pMIS形成領域1B上に、フォトレジスト膜(フォトレジストパターン)PR1aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜PR1aでは覆われずに露出している。以後、このようなフォトレジスト膜を、nMIS形成領域1Aを開口したフォトレジスト膜ということがある。このフォトレジスト膜PR1aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能する。

【0024】

次いで、nMIS形成領域1Aにおいて、半導体基板1の上層部分に、nチャネル型MISFETQnのしきい値調整用のイオン注入(インプラ)を行なう。MIFETのしきい値調整用のイオン注入は、チャネルドープイオン注入と呼ばれることもあり、このイオン注入(しきい値調整用のイオン注入)によって、MISFETのチャネル領域に不純物が導入(ドープ)され、半導体基板1の表面にチャネルドープ層(図示せず)が形成される。導入される不純物は、例えばホウ素(B)などのp型の不純物を用いることができる。

【0025】

次いで、nMIS形成領域1Aの半導体基板1中にp型ウエル(p型半導体領域)PWを形成する。p型ウエルPWは、例えば、pMIS形成領域1Bを覆う上記フォトレジスト膜PR1aをイオン注入阻止マスクとして、nMIS形成領域1Aの半導体基板1にホウ素(B)などのp型の不純物をイオン注入IM1aすることによって形成する。なお、このp型ウエルPWは、半導体基板1の深くまで延在し、例えば、素子分離領域2の底部より深い位置まで延在している。また、他の形態として、先にp型ウエルPWをイオン注入で形成した後、チャネルドープイオン注入によってチャネルドープ層を形成してもよい。

【0026】

次いで、図3に示すように、アッシングなどによりフォトレジスト膜PR1aを除去した後、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)PR1bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜PR1bでは覆われずに露出している。以後、このようなフォトレジスト膜を、pMIS形成領域1Bを開口したフォトレジスト膜ということがある。このフォトレジスト膜PR1bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能する。

【0027】

次いで、pMIS形成領域1Bにおいて、半導体基板1の上層部分に、pチャネル型MISFETQpのしきい値調整用のイオン注入を行なう。このイオン注入(しきい値調整用のイオン注入)によって、MISFETのチャネル領域に不純物が導入(ドープ)され、半導体基板1の表面にチャネルドープ層(図示せず)が形成される。導入される不純物としては、例えばリン(P)などのn型の不純物を用いることができる。

【0028】

次いで、pMIS形成領域1Bの半導体基板1中にn型ウエル(n型半導体領域)NWを形成する。n型ウエルNWは、nMIS形成領域1Aを覆うフォトレジスト膜PR1bをイオン注入阻止マスクとして、pMIS形成領域1Bの半導体基板1にリン(P)などのn型の不純物をイオン注入IM1bすることによって形成する。なお、このn型ウエルNWは、半導体基板1の深くまで延在し、例えば、素子分離領域2の底部より深い位置まで延在している。また、他の形態として、先にn型ウエルNWをイオン注入で形成した後、チャネルドープイオン注入によってチャネルドープ層を形成してもよい。更に他の形態として、先にpMIS形成領域1Bにチャネルドープ層およびn型ウエルNWを形成した後で、nMIS形成領域1Aにチャネルドープ層およびp型ウエルPWを形成してもよい。

【0029】

次いで、図4に示すように、アッシングなどによりフォトレジスト膜PR1bを除去した後、例えばフッ酸(HF)水溶液を用いたウエットエッチングなどにより上記絶縁膜3を除去する。次いで、半導体基板1の表面を清浄化(洗浄)した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体基板1の表面(主面、ここではp型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜5を形成する。この絶縁膜5は、nチャネル型MISFETQnおよびpチャネル型MISFETQpのゲート絶縁膜となる。絶縁膜5は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成する。

【0030】

次いで、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。例えば、CVD(Chemical Vapor Deposition:化学的気相成長)法などを用い多結晶シリコン膜を堆積し、シリコン膜6とする。例えば、アモルファスシリコン膜を堆積し、その後の熱処理により多結晶化してもよい。

【0031】

次いで、nMIS形成領域1Aを開口したフォトレジスト膜(図示せず)をマスクとして用いて、シリコン膜6(後述するゲート電極GE1となる領域)中に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入する。これにより、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とする。

【0032】

次いで、上記フォトレジスト膜を除去した後、pMIS形成領域1Bを開口したフォトレジスト膜(図示せず)を用いて、シリコン膜6(後述するゲート電極GE2となる領域)中に、ホウ素(B)などのp型の不純物をイオン注入する。これにより、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする。次いで、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、ハードマスク)CPとして例えば窒化シリコン膜をCVD法などを用いて堆積する。これにより、シリコン膜(導電性膜)6と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層膜が半導体基板1の上方に配置される(図4)。

【0033】

次いで、図5に示すように、シリコン膜6およびその上部の絶縁膜CPをフォトリソグラフィ法およびドライエッチング法を用いてパターニングする。これにより、ゲート電極GE1、GE2が形成される。このゲート電極GE1、GE2の上部には、絶縁膜(キャップ絶縁膜、上部絶縁膜)CPが配置される。言い換えれば、ゲート電極GE1、GE2その上部に配置された絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体が形成される。

【0034】

nチャネル型MISFETQnのゲート電極となるゲート電極GE1は、n型の不純物を導入した多結晶シリコン(n型半導体膜、ドープトポリシリコン膜)からなり、nMIS形成領域1Aのp型ウエルPW上に絶縁膜5を介して形成される。ゲート電極GE1の下に残存する絶縁膜5が、nチャネル型MISFETQnのゲート絶縁膜5となる。また、pチャネル型MISFETQpのゲート電極となるゲート電極GE2は、p型の不純物を導入した多結晶シリコン(p型半導体膜、ドープトポリシリコン膜)からなり、pMIS形成領域1Bのn型ウエルNW上に絶縁膜5を介して形成される。ゲート電極GE2の下に残存する絶縁膜5が、pチャネル型MISFETQpのゲート絶縁膜5となる。このように、pチャネル型MISFETQpにおいては、p型の不純物注入したp型ゲートを、nチャネル型MISFETQnにおいては、n型の不純物領域を注入したn型ゲートを採用した構成を、デュアルゲート構造と呼ぶことがある。このデュアルゲート構造によれば、各ゲート電極(GE1、GE2)を低抵抗化できる。また、短チャネル効果を抑制でき、漏れ電流を低減するなど、トランジスタ特性を向上させることができる。

【0035】

次いで、ゲート電極GE1、GE2と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、例えば、半導体基板1(の主面全面)上に酸化シリコン膜7をCVD法などを用いて堆積し、この酸化シリコン膜をRIE(Reactive Ion Etching:反応性イオンエッチング)法などにより異方性エッチングすることによって形成する(図6)。

【0036】

次いで、図6に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR2aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入IM2aすることにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0037】

エクステンション領域EX1はn型の半導体領域であり、後で形成するn+型半導体領域SD1よりも不純物濃度が低い。エクステンション領域EX1の深さ(接合深さ)は、後で形成されるn+型半導体領域SD1の深さ(接合深さ)よりも浅い。

【0038】

次いで、図7に示すように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物のイオン注入(ハローイオン注入)IM3aを行ってハロー領域(p型半導体領域)HA1を形成する。

【0039】

ハロー領域HA1は、エクステンション領域EX1とは逆の導電型で、かつp型ウエルPWとは同じ導電型であり、ここではp型(p型の半導体領域)である。ハロー領域HA1は、短チャネル特性(パンチスルー)抑制のために形成される。ハロー領域HA1は、エクステンション領域EX1を包み込む(覆う)ように形成され、p型ウエルPWよりも不純物濃度(p型不純物濃度)が高い。ハロー領域HA1を形成するためのイオン注入IM3aは、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域EX1を包み込む(覆う)ようにハロー領域HA1を的確に形成することができる。斜めイオン注入では、半導体基板1の主面に対して垂直な方向から所定の角度(傾斜角)傾斜した方向に不純物イオンを加速して打ち込む。

【0040】

次いで、図8に示すように、アッシングなどによりフォトレジスト膜PR2aを除去してから、pMIS形成領域1Bを開口したフォトレジスト膜PR2bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入IM2bすることにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0041】

エクステンション領域EX2はp型の半導体領域であり、後で形成するp+型半導体領域SD2よりも不純物濃度が低い。エクステンション領域EX2の深さ(接合深さ)は、後で形成されるp+型半導体領域SD2の深さ(接合深さ)よりも浅い。

【0042】

次いで、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物のイオン注入(ハローイオン注入:IM3b)を行ってハロー領域(n型半導体領域)HA2を形成する。ハロー領域HA2は、エクステンション領域EX2とは逆の導電型で、かつn型ウエルNWとは同じ導電型であり、ここではn型(n型の半導体領域)である。ハロー領域HA2は、短チャネル特性(パンチスルー)抑制のために形成される。ハロー領域HA2は、エクステンション領域EX2を包み込む(覆う)ように形成され、n型ウエルNWよりも不純物濃度(n型不純物濃度)が高い。ハロー領域HA2を形成するためのイオン注入は、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域EX2を包み込む(覆う)ようにハロー領域HA2を的確に形成することができる。

【0043】

また、他の形態として、先にpMIS形成領域1Bにエクステンション領域EX2およびハロー領域HA2を形成してから、nMIS形成領域1Aにエクステンション領域EX1およびハロー領域HA1を形成してもよい。

【0044】

また、ハロー領域HA1,HA2は、短チャネル特性抑制のために形成することが好ましいが、不要であればその形成を省略することもできる。

【0045】

次いで、図9に示すように、アッシングなどによりフォトレジスト膜PR2bを除去した後、ゲート電極GE1、GE2と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体上を含む半導体基板1上に、絶縁膜S(側壁絶縁膜)として、例えば酸化シリコン膜(O)とその上部の窒化シリコン膜(N)との積層膜をCVD法などにより形成する。次いで、図10に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、その上部の窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、サイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、このサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。このように、酸化膜と窒化膜の積層膜をサイドウォール膜SWとして用いることで、酸化シリコン膜(O)の下層にある窒化シリコン膜(N)を酸化シリコン膜のエッチングストッパとして用いることができ、基板へのダメージを最小限にして、サイドウォール膜SWを加工することができる。

【0046】

次いで、図11に示すように、ゲート電極GE1、GE2上の絶縁膜(窒化シリコン膜)CPをエッチングにより除去する。これにより、ゲート電極(シリコン膜6)GE1、GE2の表面が露出する。また、ゲート電極(シリコン膜6)GE1、GE2の表面の両側にはサイドウォール膜SWの壁が延在する。別の言い方をすれば、ゲート電極(シリコン膜6)GE1、GE2上には凹部が形成され、凹部の側壁は、サイドウォール膜SWで構成されている。

【0047】

次いで、図12に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを、フォトリソグラフィ技術を用いて形成する。次いで、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0048】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、10keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、10keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。このイオン注入IM4aの際、ゲート電極GE1およびその側壁上のサイドウォール膜SWもマスク(イオン注入阻止マスク)として機能するので、n+型半導体領域SD1は、ゲート電極GE1の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。n+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0049】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0050】

次いで、図13に示すように、アッシングなどによりフォトレジスト膜PR3aを除去した後、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを、フォトリソグラフィ技術を用いて形成する。次いで、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、10keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。Geは、半導体基板1の表面をアモルファス状に変質させ、Bを注入する際のチャネリングを抑制し、浅い接合を形成するためにイオン注入する。このp+型半導体領域SD2は、ゲート電極GE2の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。p+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0051】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0052】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0053】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0054】

次いで、図14に示すように、アッシングなどによりフォトレジスト膜PR3bを除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0055】

次いで、いわゆる歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させる。nチャネル型MISFETQnの上部に、例えば、窒化膜を堆積し、熱処理を施した後、この窒化膜を除去する。この際、ゲート電極からチャネル領域に応力(引っ張り応力)が加わり、チャネル領域の結晶を歪ませる。この結果、チャネル領域中のキャリア移動度が増加し、オン電流が増加し、また、動作速度を向上させることができる。

【0056】

例えば、図15に示すように、ゲート電極GE1、GE2およびサイドウォール膜SW上を含む半導体基板1上に、下地絶縁膜9として、例えば薄い酸化シリコン膜(例えば、5nm程度)をCVD法などで堆積した後、その上部に、応力印加膜10として、窒化シリコン膜をCVD法などで例えば20nm程度堆積する。次いで、熱処理として、例えば、1000℃のスパイクアニールの後、1230℃のレーザーアニールを施す。次いで、例えば、熱燐酸などを用いたウエットエッチングにより、応力印加膜(窒化シリコン膜)10を除去する。次いで、残存する下地絶縁膜(酸化シリコン膜)9をドライエッチングまたはウエットエッチングで除去する。これにより、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の表面が露出する。この後、これらの表面に、シリサイド層(金属シリサイド層、シリサイド膜)11を形成するのであるが、このシリサイド層11を形成する必要がない箇所(例えば、高抵抗素子など)には、上記下地絶縁膜9をマスク(シリサイド化阻止マスク)として残存させてもよい。

【0057】

次いで、図16に示すように、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面を必要に応じて洗浄した後、これらの上部に、例えばニッケル(Ni)のような金属膜11aを例えば25nm程度堆積して熱処理(第1アニール)を施す。これにより、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の表面(シリコン表面)と金属膜11aとの界面においてシリサイド化反応が生じ、シリサイド層(金属シリサイド層、シリコンと金属膜との反応層)11が形成される(図17)。このシリサイド層11により、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の拡散抵抗やコンタクト抵抗などを低抵抗化することができる。その後、未反応の金属膜11aを除去し、さらに、熱処理(第2アニール)を施す。なお、このシリサイド層11の形成を省略することもできる。

【0058】

次いで、半導体基板1の主面上に絶縁膜(層間絶縁膜)12を形成する。例えば、ゲート電極GE1、GE2およびサイドウォール膜SW上に、窒化シリコン膜12aを形成し、さらにその上部に、より膜厚の大きい酸化シリコン膜12bを形成し、これらの膜の積層膜よりなる絶縁膜12を形成する。この窒化シリコン膜12aおよび酸化シリコン膜12bは、CVD法などで形成することができる。なお、絶縁膜12として、例えば、酸化シリコン膜の単体膜を用いてもよい。

【0059】

その後、絶縁膜12の表面(上面)をCMP(CMP:Chemical Mechanical Polishing、化学機械研磨)法により研磨するなどして、絶縁膜12の上面を平坦化する。下地段差に起因して絶縁膜12の表面に凹凸形状が形成されていても、絶縁膜12の表面をCMP法により研磨することにより、その表面が平坦化された絶縁膜12を得ることができる。

【0060】

次いで、絶縁膜12をパターニングすることにより、絶縁膜12中にコンタクトホール(接続孔、貫通孔、孔)13を形成する。コンタクトホール13の底部においては、半導体基板1の主面の一部、例えばn+型半導体領域SD1およびp+型半導体領域SD2の表面上のシリサイド層11の一部が露出している。

【0061】

次いで、コンタクトホール13内に、タングステン(W)などからなる導電性のプラグ(コンタクトプラグ、接続用導体部)14を形成する。例えば、コンタクトホール13の内部(底部および側壁上)を含む絶縁膜12上に、プラズマCVD法によりバリア膜(図示せず)として、例えば、チタン膜、窒化チタン膜、あるいはそれらの積層膜を形成した後、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール13を埋めるように形成する。次いで、絶縁膜12上の不要な主導体膜およびバリア膜をCMP法またはエッチバック法などによって除去することにより、プラグ(コンタクトプラグ、接続部)14を形成する。プラグ14は、その底部で、n+型半導体領域SD1またはp+型半導体領域SD2の表面上のシリサイド層11と接して、電気的に接続される。なお、図17においては、n+型半導体領域SD1またはp+型半導体領域SD2上のプラグ14しか表示していないが、ゲート電極GE1、GE2上にもプラグ14が形成される。

【0062】

次いで、図18に示すように、プラグ14が埋め込まれた絶縁膜12上に、配線溝用の絶縁膜15を形成する。絶縁膜15は、例えば、窒化シリコン膜とその上部の酸化シリコン膜との積層膜で構成する。なお、絶縁膜15を単層膜で構成してもよい。

【0063】

次に、シングルダマシン法により第1層目の配線である配線M1を形成する。具体的には、絶縁膜15をパターニングすることにより、所定の領域に配線溝を形成した後、配線溝の底部および側壁上を含む絶縁膜15上にバリア膜(例えば窒化チタン膜、タンタル膜または窒化タンタル膜など)を形成する。続いて、CVD法またはスパッタリング法などによりバリア膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成して、銅めっき膜により配線溝の内部を埋め込む。次いで、配線溝以外の領域の主導体膜(銅めっき膜およびシード層)とバリアメタル膜をCMP法により除去して、配線溝に埋め込まれ銅を主導電材料とする第1層目の配線M1を形成する。なお、図18においては、図面の簡略化のために、配線M1は、バリア導体膜、シード層および銅めっき膜を一体化して示してある。

【0064】

配線M1は、プラグ14を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのソースまたはドレイン用のn+型半導体領域SD1およびp+型半導体領域SD2と電気的に接続されている。また、配線M1は、プラグ14を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのゲート電極GE1、GE2と電気的に接続されている。

【0065】

その後、デュアルダマシン法などにより2層目の配線を形成するが、ここでは、2層目以降の配線およびその形成工程の説明は省略する。

【0066】

以上のようにして、本実施の形態の半導体装置が製造される。

【0067】

ここで、本実施の形態においては、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、この絶縁膜CPを除去した後、ヒ素(As)をイオン注入したので、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができる。

【0068】

図19〜図21に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。また、図22〜図24には、比較例の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0069】

図19〜図21に示すように、本実施の形態においては、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、サイドウォール膜SWを形成した後(図19)、絶縁膜CPをエッチバック(エッチング)により除去し(図20)、ヒ素(As)をイオン注入している(図21)。

【0070】

一方、絶縁膜CPの形成およびエッチバックを行わない比較例においては、図22に示すように、ゲート電極GEの高さとサイドウォール膜SWの高さとがほぼ同じであるため、図23に示すように、ゲート電極GEの上部がヒ素(As)のイオン注入により横方向に膨張する。その結果、図24に示すように、シリサイド層11またはゲート電極GEとプラグ14との距離(白抜き矢印部参照)が小さくなり、ゲート電極GEとプラグ14間での短絡(ショート)の要因となる。なお、前述の図17等においては、図面を見やすくするためゲート電極GEとプラグ14との間を大きく表示してあるが、素子の微細化に伴い、ゲート電極GEとプラグ14が小さくなる傾向にあり、実際には、図24に示すように、サイドウォール膜SWとプラグ14とが近接し、また、平面パターンが重なるような配置となることが多い。

【0071】

本発明者の検討によれば、かかる課題(ゲート電極とプラグ間のショートマージンの低下)は、nチャネル型MISFETで顕著に確認された。

【0072】

図25は、nチャネル型MISFETの断面写真である。図26は、pチャネル型MISFETの断面写真である。図25のnチャネル型MISFETにおいては、ゲート電極上のシリサイド層が横方向に張り出している。これに対し、図26のpチャネル型MISFETにおいては、シリサイド層の横方向の張り出し(突き出し)は少ない。

【0073】

上記現象について、発明者がさらに検討したところ、nチャネル型MISFETのゲート電極(ソース、ドレイン領域)に打ち込まれるイオン種が要因ではないかとの結論に到った。

【0074】

図27は、nチャネル型MISFETのゲート電極にリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。図28は、nチャネル型MISFETのゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。イオン注入条件としては、図27は、リン(P)を8keVのエネルギー、4.0×1015/cm2の条件でイオン注入した場合を示し、また、図28は、ヒ素(As)を10keVのエネルギー、8.0×1015/cm2の条件で、リン(P)を10keVのエネルギー、5.0×1013/cm2の条件でイオン注入した場合を示す。

【0075】

図27に示すように、ゲート電極にリン(P)のみを打ち込んだ場合は、シリサイド層の横方向の張り出しは少ない。図28に示すように、ゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合は、シリサイド層の横方向の張り出しが大きいことが分かった(矢印部参照)。これは、比較的原子量が大きいヒ素(As)の注入ダメージによるものではないかと考察される。

【0076】

これにより、ヒ素(As)のイオン注入により、ゲート電極の上部が、横方向に張り出すようにゲート電極形状が変形し、さらに、この後のシリサイド化反応に伴う堆積膨張により、ゲート電極の上部のシリサイド層がさらに横方向に張り出すことが分かった。

【0077】

このように、ゲート電極の上部およびシリサイド層の横方向の張り出しが大きくなると、ゲート電極(シリサイド層含む)とプラグとの距離が小さくなり、耐圧の劣化や短絡が生じ不良の要因となる(図24参照)。さらに、素子の微細化に伴い、ゲート電極(シリサイド層含む)とプラグとの距離は縮小傾向にあり、素子の微細化が進むほど、上記横方向の張り出しの問題解決が重要となる。

【0078】

これに対し、本実施の形態においては、前述したように、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、この絶縁膜CPを除去することにより、ゲート電極GE1上に、凹部を形成し、この凹部の側壁にサイドウォール膜SWを配置したので、ヒ素(As)のイオン注入により、ゲート電極GE1の上部が張り出す領域をこの凹部内に確保し、さらに、サイドウォール膜SWよりなる凹部の側壁で、ゲート電極GE1の上部の横方向への張り出しを抑制することができる。よって、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0079】

なお、本実施の形態においては、pMIS形成領域1Bのゲート電極GE2上にも絶縁膜CPを形成し、この絶縁膜CPを除去することにより、ゲート電極GE2上にも凹部を形成した。しかしながら、前述したとおり、ゲート電極とプラグ間のショートマージンの低下は、nチャネル型MISFETで顕著であるため、pMIS形成領域1Bの絶縁膜CPをあらかじめ除去しておいてもよい。但し、この除去工程を省くことで、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0080】

次いで、本実施の形態の半導体装置の構造的特徴の一例について説明する。

【0081】

図29および図30は、本実施の形態のnチャネル型MISFETQnの断面図である。図31および図32は、pチャネル型MISFETQpの断面図である。図29および図31は、それぞれ、シリサイド層11の形成後の断面図であり、図30および図32は、それぞれ、窒化シリコン膜12a形成後の断面図である。

【0082】

前述したように、ゲート電極GE1、GE2上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、絶縁膜CPを除去する際、サイドウォール膜SW中の絶縁膜CPと同じ膜種(この場合、窒化シリコン膜)よりなる第2側壁膜SWbもエッチングされる(図29、図30参照)。よって、第2側壁膜(窒化シリコン膜)SWbの高さ(HSWb)は、第1側壁膜(酸化シリコン膜)SWaの高さ(HSWa)よりも低くなる(HSWb<HSWa)。

【0083】

また、nチャネル型MISFETQn(図29)において、絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを除去した際のゲート電極GE1上の凹部内においては、ゲート電極(シリコン膜)GE1が膨張して充填され、さらに、その後のシリサイド化によりシリサイド層11が充填される。一方、pチャネル型MISFETQp(図31)においては、横方向の張り出しが少ない分だけ、ゲート電極(シリコン膜)GE2の膨張量が少なく、その後、シリサイド化しても、nチャネル型MISFETQnのゲート電極(シリサイド層11含む)GE1の高さHQnよりも、pチャネル型MISFETQpのゲート電極(シリサイド層11含む)GE2の高さHQpが小さくなることが考え得る(HQn>HQp、図29、図30参照)。

【0084】

但し、上記高さの関係はあくまで一例にすぎない。即ち、絶縁膜CP除去後にも、種々の洗浄やエッチングの処理があり、これらの処理により第1側壁膜SWa、第2側壁膜SWbがそれぞれ個別にエッチングされ得る。よって、その後の工程によっては、第1側壁膜SWaと第2側壁膜SWbとの高さの関係が逆になるということも考えられる。また、シリサイド化の条件などにより、ゲート電極(シリサイド層11含む)GE1、GE2の高さも変わり得るので、上記高さの関係が、最終的なMISFET(Qn、Qp)の断面形状として必ず表れるわけではない。

【0085】

(実施の形態2)

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図33〜図40は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0086】

まず、上記実施の形態1と同様に、nMIS形成領域1Aの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、p型ウエル(p型半導体領域)PWを形成する。また、pMIS形成領域1Bの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、n型ウエル(n型半導体領域)NWを形成する。これまでの工程については、実施の形態の図1〜図3が参照される。

【0087】

次いで、半導体基板1の表面を清浄化(洗浄)した後、実施の形態1と同様に、ゲート絶縁膜用の絶縁膜5を形成し、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。次いで、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とし、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする(図4参照)。但し、本実施の形態においては、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、窒化シリコン膜)CPを形成せず、図33に示すように、シリコン膜6のパターニングにより、ゲート電極GE1、GE2を形成する。

【0088】

次いで、ゲート電極GE1、GE2の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、実施の形態1と同様に形成することができる。

【0089】

次いで、実施の形態1と同様に、nMIS形成領域1Aを開口したフォトレジスト膜をマスクにゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0090】

また、実施の形態1と同様に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物を傾斜イオン注入することにより、ハロー領域(p型半導体領域)HA1を形成する。

【0091】

次いで、実施の形態1と同様に、pMIS形成領域1Bを開口したフォトレジスト膜をマスクにゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0092】

また、実施の形態1と同様に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物を傾斜イオン注入することにより、ハロー領域(n型半導体領域)HA2を形成する。

【0093】

次いで、アッシングなどにより上記フォトレジスト膜を除去した後、ゲート電極GE1、GE2上を含む半導体基板1上に、絶縁膜(側壁絶縁膜)として、例えば酸化シリコン膜とその上部の窒化シリコン膜との積層膜をCVD法などにより形成する。次いで、図34に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜とその上層の窒化シリコン膜との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。

【0094】

次いで、図35に示すように、ゲート電極GE1、GE2およびサイドウォール膜SW上を含む半導体基板1上に、スルー絶縁膜F5として、例えば、酸化シリコン膜をCVD法などで堆積する。なお、酸化シリコン膜に代えて窒化シリコン膜を用いてもよい。また、これらの絶縁膜の積層膜をスルー絶縁膜F5として用いてもよい。

【0095】

次いで、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを形成し、これをマスクに、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、スルー絶縁膜F5を介して、リン(P)またはヒ素(As)などのn型の不純物をイオン注入(IM4a)することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0096】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、20keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、20keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。なお、本実施の形態においては、スルー絶縁膜F5を介して、イオン注入を行っているため、注入エネルギーを実施の形態1の場合(10keV)より大きく(例えば、20keVと)してある。

【0097】

このn+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0098】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0099】

次いで、アッシングなどにより上記フォトレジスト膜PR3aを除去した後、図36に示すように、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを形成し、これをマスクに、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、スルー絶縁膜F5を介して、ホウ素(B)などのp型の不純物をイオン注入(IM4b)することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、20keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。

【0100】

このp+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0101】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0102】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0103】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0104】

次いで、アッシングなどにより上記フォトレジスト膜PR3bを除去し、例えば、熱燐酸などを用いたウエットエッチングによりスルー絶縁膜F5も除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0105】

次いで、実施の形態1と同様に、歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させた後(図15参照)、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面上に、シリサイド層11を形成する(図16、図17参照)。さらに、この後、実施の形態1と同様に、絶縁膜(層間絶縁膜)12を形成し、その内部のコンタクトホール13内にプラグ14を形成した後、その上部の配線溝用の絶縁膜15中に配線M1を形成する(図37)。その後、デュアルダマシン法などにより2層目の配線を形成するが、ここでは、2層目以降の配線およびその形成工程の説明は省略する。

【0106】

また、他の形態として、このスルー絶縁膜F5を残存させ、歪み印加技術用の絶縁膜(窒化シリコン膜)として用いてもよい。即ち、スルー絶縁膜F5を残存させた状態で、応力印加膜として利用し、実施の形態1で説明したように、熱処理を施す。例えば、1000℃のスパイクアニールの後、1230℃のレーザーアニールを施す。次いで、例えば、熱燐酸などを用いたウエットエッチングにより、スルー絶縁膜F5を除去するが、この際、その後のシリサイド化工程において、このシリサイド層11を形成する必要がない箇所(例えば、高抵抗素子など)には、上記スルー絶縁膜F5をマスク(シリサイド化阻止マスク)として残存させてもよい。

【0107】

以上のようにして、本実施の形態の半導体装置が製造される。

【0108】

ここで、本実施の形態においては、ゲート電極GE1上にスルー絶縁膜F5を形成し、このスルー絶縁膜F5を介して、ヒ素(As)をイオン注入したので、実施の形態1において詳細に説明したヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができる。その結果、ヒ素(As)のイオン注入によるゲート電極GE1の上部の横方向への膨らみを低減でき、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離を確保することができる。

【0109】

図38〜図40に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0110】

図38〜図40に示すように、本実施の形態においては、本実施の形態においては、ゲート電極GE1の側壁にSWを形成した後(図38)、図39に示すように、ゲート電極のGE1上部にスルー絶縁膜F5を形成し、このスルー絶縁膜F5を介してヒ素(As)をイオン注入している(図40)。よって、打ち込まれるイオン、特に、ヒ素(As)のイオン注入により、ゲート電極GE1の上部が横方向に張り出すことを、このスルー絶縁膜F5の応力により抑制することができる。よって、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0111】

なお、本実施の形態においては、スルー絶縁膜F5をpMIS形成領域1Bにも形成し、スルー絶縁膜F5を介して、p型の不純物をイオン注入(IM4b)したが、前述したとおり、ゲート電極とプラグ間のショートマージンの低下は、nチャネル型MISFETで顕著であるため、pMIS形成領域1Bのスルー絶縁膜F5を除去してもよい。但し、この除去工程を省くことで、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0112】

(実施の形態3)

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図41〜図49は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0113】

まず、上記実施の形態1と同様に、nMIS形成領域1Aの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、p型ウエル(p型半導体領域)PWを形成する。また、pMIS形成領域1Bの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、n型ウエル(n型半導体領域)NWを形成する。これまでの工程については、実施の形態の図1〜図3が参照される。

【0114】

次いで、半導体基板1の表面を清浄化(洗浄)した後、実施の形態1と同様に、ゲート絶縁膜用の絶縁膜5を形成し、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。次いで、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とし、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする(図4参照)。但し、本実施の形態においては、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、窒化シリコン膜)CPを形成せず、図41に示すように、シリコン膜6のパターニングにより、ゲート電極GE1、GE2を形成する。

【0115】

次いで、ゲート電極GE1、GE2の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、実施の形態1と同様に形成することができる。

【0116】

次いで、実施の形態1と同様に、nMIS形成領域1Aを開口したフォトレジスト膜をマスクにゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0117】

また、実施の形態1と同様に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物を傾斜イオン注入することにより、ハロー領域(p型半導体領域)HA1を形成する。

【0118】

次いで、実施の形態1と同様に、pMIS形成領域1Bを開口したフォトレジスト膜をマスクにゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0119】

また、実施の形態1と同様に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物を傾斜イオン注入することにより、ハロー領域(n型半導体領域)HA2を形成する。

【0120】

次いで、アッシングなどにより上記フォトレジスト膜を除去した後、ゲート電極GE1、GE2上を含む半導体基板1上に、絶縁膜(側壁絶縁膜)として、例えば酸化シリコン膜とその上部の窒化シリコン膜との積層膜をCVD法などにより形成する。次いで、図42に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜とその上層の窒化シリコン膜との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。

【0121】

次いで、図43に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを形成し、これをマスクに、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入(IM4a)することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0122】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、10keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、10keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。このイオン注入IM4aの際、ゲート電極GE1およびその側壁上のサイドウォール膜SWもマスク(イオン注入阻止マスク)として機能するので、n+型半導体領域SD1は、ゲート電極GE1の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。n+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0123】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0124】

ここで、実施の形態1で詳細に説明したように、ゲート電極にヒ素(As)を打ち込んだ場合は、ゲート電極の上部が、縦方向および横方向に張り出す(図27等参照)。

【0125】

そこで、本実施の形態においては、図44に示すように、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部をエッチバックすることにより、縦方向および横方向の張り出したゲート電極(シリコン膜6)の部分を除去する。具体的には、nMIS形成領域1Aを開口したフォトレジスト膜PR3aをマスクに、ゲート電極(シリコン膜6)GE1の上部を、ドライエッチング(スライトエッチング)する。これにより、ゲート電極の上部の、縦方向および横方向の張り出しがエッチングにより除去される(図45)。エッチバック量は、例えば、5〜15nm程度である。また、不純物が注入されたシリコン膜は、半導体基板に対してエッチングレートが大きいため、半導体基板に対するダメージが少なく、ゲート電極の上部の張り出し領域をドライエッチングすることができる。

【0126】

次いで、アッシングなどにより上記フォトレジスト膜PR3aを除去した後、図45に示すように、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを形成し、これをマスクに、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入(IM4b)することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、10keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。このp+型半導体領域SD2は、ゲート電極GE2の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。p+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0127】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0128】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0129】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0130】

次いで、アッシングなどにより上記フォトレジスト膜PR3bを除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0131】

次いで、実施の形態1と同様に、歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させた後(図15参照)、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面上に、シリサイド層11を形成する(図16、図17参照)。さらに、この後、実施の形態1と同様に、絶縁膜(層間絶縁膜)12を形成し、その内部のコンタクトホール13内にプラグ14を形成した後、その上部の配線溝用の絶縁膜15中に配線M1を形成する(図46)。その後、デュアルダマシン法により2層目の配線を形成するが、ここでは図示およびその説明は省略する。

【0132】

以上のようにして、本実施の形態の半導体装置が製造される。

【0133】

図47〜図49に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0134】

図47〜図49に示すように、本実施の形態においては、ゲート電極GE1の側壁にSWを形成した後(図47)、図48に示すように、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)等をイオン注入し、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部をエッチバックする(図49)。これにより、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0135】

なお、本実施の形態においては、nMIS形成領域1Aにおいて、ヒ素(As)をイオン注入した直後に、ゲート電極(シリコン膜6)GE1の上部のエッチバックを行ったが、エッチバック工程は、このタイミングに限られるものではない。例えば、pMIS形成領域1Bに、p+型半導体領域SD2(ソース、ドレイン)を形成した後、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部のみのエッチバックを行ってもよい。但し、この場合、エッチバック用のフォトレジスト膜を再度形成する必要がある。即ち、本実施の形態においては、n+型半導体領域SD1(ソース、ドレイン)の形成用のフォトレジスト膜PR3aを利用してエッチバックを行うことができ(図43、図44参照)、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0136】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0137】

本発明は、半導体装置の製造方法に関し、特に、MISFETを有する半導体装置の製造に適用することができる。

【符号の説明】

【0138】

1 半導体基板

1A nMIS形成領域

1B pMIS形成領域

2 素子分離領域

3 絶縁膜

5 ゲート絶縁膜(絶縁膜)

6 シリコン膜

7 酸化シリコン膜

9 下地絶縁膜

10 応力印加膜

11 シリサイド層

11a 金属膜

12 絶縁膜

12a 窒化シリコン膜

12b 酸化シリコン膜

13 コンタクトホール

14 プラグ

15 絶縁膜

CP 絶縁膜

EX1 エクステンション領域

EX2 エクステンション領域

F5 スルー絶縁膜

GE ゲート電極

GE1 ゲート電極

GE2 ゲート電極

HA1 ハロー領域

HA2 ハロー領域

IM1a イオン注入

IM1b イオン注入

IM2a イオン注入

IM2b イオン注入

IM3a イオン注入

IM3b イオン注入

IM4a イオン注入

IM4b イオン注入

M1 配線

NW n型ウエル

OFS オフセットスペーサ

PR1a フォトレジスト膜

PR1b フォトレジスト膜

PR2a フォトレジスト膜

PR2b フォトレジスト膜

PR3a フォトレジスト膜

PR3b フォトレジスト膜

PW p型ウエル

Qn nチャネル型MISFET

Qp pチャネル型MISFET

SD1 n+型半導体領域

SD2 p+型半導体領域

SW サイドウォール膜

SWa 第1側壁膜

SWb 第2側壁膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、MISFETを有する半導体装置の製造に適用して有効な技術に関する。

【背景技術】

【0002】

MISFETなどの半導体素子を半導体基板に形成し、更に半導体基板上の配線とコンタクトプラグなどを介して半導体素子との間を結線することで、半導体装置が製造される。

【0003】

素子の微細化に伴い、MISFETとコンタクトプラグとの間の距離も小さくなり、MISFETを構成するゲート電極とコンタクトプラグとの間の短絡を回避する技術が重要となる。

【0004】

例えば、特開2002−319592号公報(特許文献1)には、ゲート電極とコンタクト部材との短絡のない、かつ、微細化にも対応しうる半導体装置の製造方法が開示されている。例えば、Si基板(1)上に、ゲート絶縁膜(2)、ゲート電極(3a)、ゲート上保護層(4a)を形成した後、低濃度ソース・ドレイン領域(6)を形成する。ゲート電極(3a)の側面上に第1サイドウォール(15a)と、第2サイドウォールとを形成した後、これをマスクとして用いるイオン注入により、高濃度ソース・ドレイン領域(9)を形成する。第2サイドウォール(16a)を選択的に除去した後、ポケット注入領域(Rpo)を形成し、全面保護膜(12)を堆積する。その後、層間絶縁膜(10)の堆積と、高濃度ソース・ドレイン領域(9)に到達するコンタクトホール(Hct)の形成と、プラグ電極(11)の形成とを行うという工程が開示されている。

【0005】

また、特開2000−306860号公報(特許文献2)には、コンタクトホールでの素子コンタクト面の洗浄を行った場合でも、コンタクトホール内におけるゲート電極やソース・ドレイン領域等の短絡を確実に防止して、素子不良が発生することがない半導体装置の製造方法が開示されている。例えば、シリコン基板(101)上に素子を形成し、前記素子を覆う層間絶縁膜(111)を形成し、さらに前記層間絶縁膜(111)に前記素子を露呈するコンタクトホール(113)を開口する。次いで、コンタクトホール(113)の内底面に露呈される素子のコンタクト面を洗浄し、しかる上で前記コンタクトホール(113)内に導電材を埋め込んでコンタクトプラグ(115)を形成する。このような工程を含む半導体装置の製造方法において、前記コンタクトホール(113)を開口した後、前記素子のコンタクト面を洗浄する工程の間に、前記洗浄剤に対して耐性のあるストッパ膜(114)を前記コンタクトホール(113)の内側面に形成する工程が開示されている。なお、(かっこ)内は当該文献に記載の符号である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−319592号公報

【特許文献2】特開2000−306860号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者は、MISFETを有する半導体装置の研究開発に従事し、当該半導体装置の特性向上について検討している。

【0008】

前述したように、素子の微細化に伴い、MISFETを構成するゲート電極とコンタクトプラグとの距離が小さくなり、これらの短絡を回避する技術が望まれる。追って詳細に説明するように、本発明者の検討によれば、上記短絡の一要因として、ゲート電極の上部に形成されるシリサイド膜の横方向(ゲート長方向)への張り出しが挙げられることが判明した。

【0009】

そこで、本発明の目的は、特性の良好な半導体装置を製造するための半導体装置の製造方法を提供することにある。特に、ゲート電極とコンタクトプラグとの短絡を低減できる半導体装置の製造方法を提供することにある。

【0010】

本発明の上記目的およびその他の目的と新規な特徴は、本願明細書の記載および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0012】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、半導体膜と上記半導体膜上の絶縁膜との積層膜を形成する工程と、(b)上記積層膜をパターニングすることによりゲート電極と上記ゲート電極の上部に配置され上記絶縁膜よりなる上部絶縁膜との積層体を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記積層体の側壁に側壁膜を形成する工程と、(d)上記(c)工程の後、上記上部絶縁膜を除去する工程と、(e)上記(d)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中にヒ素(As)を注入する工程と、を有する。

【0013】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方にゲート電極を形成する工程と、(b)上記(a)工程の後、上記ゲート電極の側壁に側壁膜を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記ゲート電極および上記側壁膜上に絶縁膜を形成する工程と、(d)上記(c)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中に、上記絶縁膜を介して、ヒ素(As)を注入する工程と、を有する。

【0014】

代表的な実施の形態による半導体装置の製造方法は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方にゲート電極を形成する工程と、(b)上記(a)工程の後、上記ゲート電極の側壁に側壁膜を形成する工程と、を有する。そして、さらに、(c)上記(b)工程の後、上記側壁膜および上記ゲート電極の合成体の両側の半導体基板中および上記ゲート電極中に、上記絶縁膜を介して、ヒ素(As)を注入する工程と、(d)上記(c)工程の後、上記ゲート電極の上部をエッチングする工程と、を有する。

【発明の効果】

【0015】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。特に、ゲート電極とコンタクトプラグとの短絡を低減し、半導体装置の性能を向上することができる。

【図面の簡単な説明】

【0016】

【図1】実施の形態1の半導体装置の製造工程を示す要部断面図である。

【図2】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図1に続く半導体装置の製造工程を示す要部断面図である。

【図3】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図2に続く半導体装置の製造工程を示す要部断面図である。

【図4】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図3に続く半導体装置の製造工程を示す要部断面図である。

【図5】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図4に続く半導体装置の製造工程を示す要部断面図である。

【図6】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図5に続く半導体装置の製造工程を示す要部断面図である。

【図7】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図6に続く半導体装置の製造工程を示す要部断面図である。

【図8】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図7に続く半導体装置の製造工程を示す要部断面図である。

【図9】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図8に続く半導体装置の製造工程を示す要部断面図である。

【図10】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図9に続く半導体装置の製造工程を示す要部断面図である。

【図11】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図10に続く半導体装置の製造工程を示す要部断面図である。

【図12】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図11に続く半導体装置の製造工程を示す要部断面図である。

【図13】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図12に続く半導体装置の製造工程を示す要部断面図である。

【図14】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図13に続く半導体装置の製造工程を示す要部断面図である。

【図15】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図14に続く半導体装置の製造工程を示す要部断面図である。

【図16】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図15に続く半導体装置の製造工程を示す要部断面図である。

【図17】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図16に続く半導体装置の製造工程を示す要部断面図である。

【図18】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図17に続く半導体装置の製造工程を示す要部断面図である。

【図19】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図20】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図21】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図22】実施の形態1の比較例の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図23】実施の形態1の比較例の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図24】実施の形態1の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図25】nチャネル型MISFETの断面写真である。

【図26】pチャネル型MISFETの断面写真である。

【図27】nチャネル型MISFETのゲート電極にリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。

【図28】nチャネル型MISFETのゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。

【図29】実施の形態1の半導体装置のnチャネル型MISFETの断面図である。

【図30】実施の形態1の半導体装置のnチャネル型MISFETの断面図である。

【図31】実施の形態1の半導体装置のpチャネル型MISFETの断面図である。

【図32】実施の形態1の半導体装置のpチャネル型MISFETの断面図である。

【図33】実施の形態2の半導体装置の製造工程を示す要部断面図である。

【図34】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図33に続く半導体装置の製造工程を示す要部断面図である。

【図35】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図34に続く半導体装置の製造工程を示す要部断面図である。

【図36】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図35に続く半導体装置の製造工程を示す要部断面図である。

【図37】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図36に続く半導体装置の製造工程を示す要部断面図である。

【図38】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図39】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図40】実施の形態2の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図41】実施の形態3の半導体装置の製造工程を示す要部断面図である。

【図42】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図41に続く半導体装置の製造工程を示す要部断面図である。

【図43】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図42に続く半導体装置の製造工程を示す要部断面図である。

【図44】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図43に続く半導体装置の製造工程を示す要部断面図である。

【図45】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図44に続く半導体装置の製造工程を示す要部断面図である。

【図46】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図45に続く半導体装置の製造工程を示す要部断面図である。

【図47】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図48】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【図49】実施の形態3の半導体装置の製造工程を示す要部断面図であって、nMIS形成領域1Aの部分拡大図である。

【発明を実施するための形態】

【0017】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0018】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等(個数、数値、量、範囲等を含む)についても同様である。

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0020】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0021】

(実施の形態1)

図面を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成を明確にする。図1〜図21は、本実施の形態の半導体装置の製造工程を示す要部断面図である。本実施の形態の半導体装置は、MISFET(Metal Insulator Semiconductor Field Effect Transistor)を有し、ここでは、CMIS(ComplementaryMIS)構成の2つのトランジスタ(Qn、Qp)を有する(図18等参照)。

【0022】

まず、図1に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次いで、半導体基板1の主面に素子分離領域2を形成する。素子分離領域2は酸化シリコン膜などの絶縁体からなり、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon)法などにより形成される。例えば、半導体基板1に溝(素子分離溝)を形成し、この溝の内部に絶縁膜を埋め込むことにより、素子分離領域2を形成することができる。素子分離領域2によって、nチャネル型MISFET(MIS型電界効果トランジスタ)Qnが形成される領域(活性領域)であるnMIS形成領域1Aと、pチャネル型MISFETQpが形成される領域(活性領域)であるpMIS形成領域1Bとが規定される。

【0023】

次いで、半導体基板1の表面の汚染防止のための薄い絶縁膜(スルー膜)3を半導体基板1の表面(主面)に形成した後、図2に示すように、pMIS形成領域1B上に、フォトレジスト膜(フォトレジストパターン)PR1aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜PR1aでは覆われずに露出している。以後、このようなフォトレジスト膜を、nMIS形成領域1Aを開口したフォトレジスト膜ということがある。このフォトレジスト膜PR1aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能する。

【0024】

次いで、nMIS形成領域1Aにおいて、半導体基板1の上層部分に、nチャネル型MISFETQnのしきい値調整用のイオン注入(インプラ)を行なう。MIFETのしきい値調整用のイオン注入は、チャネルドープイオン注入と呼ばれることもあり、このイオン注入(しきい値調整用のイオン注入)によって、MISFETのチャネル領域に不純物が導入(ドープ)され、半導体基板1の表面にチャネルドープ層(図示せず)が形成される。導入される不純物は、例えばホウ素(B)などのp型の不純物を用いることができる。

【0025】

次いで、nMIS形成領域1Aの半導体基板1中にp型ウエル(p型半導体領域)PWを形成する。p型ウエルPWは、例えば、pMIS形成領域1Bを覆う上記フォトレジスト膜PR1aをイオン注入阻止マスクとして、nMIS形成領域1Aの半導体基板1にホウ素(B)などのp型の不純物をイオン注入IM1aすることによって形成する。なお、このp型ウエルPWは、半導体基板1の深くまで延在し、例えば、素子分離領域2の底部より深い位置まで延在している。また、他の形態として、先にp型ウエルPWをイオン注入で形成した後、チャネルドープイオン注入によってチャネルドープ層を形成してもよい。

【0026】

次いで、図3に示すように、アッシングなどによりフォトレジスト膜PR1aを除去した後、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)PR1bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜PR1bでは覆われずに露出している。以後、このようなフォトレジスト膜を、pMIS形成領域1Bを開口したフォトレジスト膜ということがある。このフォトレジスト膜PR1bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能する。

【0027】

次いで、pMIS形成領域1Bにおいて、半導体基板1の上層部分に、pチャネル型MISFETQpのしきい値調整用のイオン注入を行なう。このイオン注入(しきい値調整用のイオン注入)によって、MISFETのチャネル領域に不純物が導入(ドープ)され、半導体基板1の表面にチャネルドープ層(図示せず)が形成される。導入される不純物としては、例えばリン(P)などのn型の不純物を用いることができる。

【0028】

次いで、pMIS形成領域1Bの半導体基板1中にn型ウエル(n型半導体領域)NWを形成する。n型ウエルNWは、nMIS形成領域1Aを覆うフォトレジスト膜PR1bをイオン注入阻止マスクとして、pMIS形成領域1Bの半導体基板1にリン(P)などのn型の不純物をイオン注入IM1bすることによって形成する。なお、このn型ウエルNWは、半導体基板1の深くまで延在し、例えば、素子分離領域2の底部より深い位置まで延在している。また、他の形態として、先にn型ウエルNWをイオン注入で形成した後、チャネルドープイオン注入によってチャネルドープ層を形成してもよい。更に他の形態として、先にpMIS形成領域1Bにチャネルドープ層およびn型ウエルNWを形成した後で、nMIS形成領域1Aにチャネルドープ層およびp型ウエルPWを形成してもよい。

【0029】

次いで、図4に示すように、アッシングなどによりフォトレジスト膜PR1bを除去した後、例えばフッ酸(HF)水溶液を用いたウエットエッチングなどにより上記絶縁膜3を除去する。次いで、半導体基板1の表面を清浄化(洗浄)した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体基板1の表面(主面、ここではp型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜5を形成する。この絶縁膜5は、nチャネル型MISFETQnおよびpチャネル型MISFETQpのゲート絶縁膜となる。絶縁膜5は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成する。

【0030】

次いで、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。例えば、CVD(Chemical Vapor Deposition:化学的気相成長)法などを用い多結晶シリコン膜を堆積し、シリコン膜6とする。例えば、アモルファスシリコン膜を堆積し、その後の熱処理により多結晶化してもよい。

【0031】

次いで、nMIS形成領域1Aを開口したフォトレジスト膜(図示せず)をマスクとして用いて、シリコン膜6(後述するゲート電極GE1となる領域)中に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入する。これにより、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とする。

【0032】

次いで、上記フォトレジスト膜を除去した後、pMIS形成領域1Bを開口したフォトレジスト膜(図示せず)を用いて、シリコン膜6(後述するゲート電極GE2となる領域)中に、ホウ素(B)などのp型の不純物をイオン注入する。これにより、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする。次いで、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、ハードマスク)CPとして例えば窒化シリコン膜をCVD法などを用いて堆積する。これにより、シリコン膜(導電性膜)6と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層膜が半導体基板1の上方に配置される(図4)。

【0033】

次いで、図5に示すように、シリコン膜6およびその上部の絶縁膜CPをフォトリソグラフィ法およびドライエッチング法を用いてパターニングする。これにより、ゲート電極GE1、GE2が形成される。このゲート電極GE1、GE2の上部には、絶縁膜(キャップ絶縁膜、上部絶縁膜)CPが配置される。言い換えれば、ゲート電極GE1、GE2その上部に配置された絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体が形成される。

【0034】

nチャネル型MISFETQnのゲート電極となるゲート電極GE1は、n型の不純物を導入した多結晶シリコン(n型半導体膜、ドープトポリシリコン膜)からなり、nMIS形成領域1Aのp型ウエルPW上に絶縁膜5を介して形成される。ゲート電極GE1の下に残存する絶縁膜5が、nチャネル型MISFETQnのゲート絶縁膜5となる。また、pチャネル型MISFETQpのゲート電極となるゲート電極GE2は、p型の不純物を導入した多結晶シリコン(p型半導体膜、ドープトポリシリコン膜)からなり、pMIS形成領域1Bのn型ウエルNW上に絶縁膜5を介して形成される。ゲート電極GE2の下に残存する絶縁膜5が、pチャネル型MISFETQpのゲート絶縁膜5となる。このように、pチャネル型MISFETQpにおいては、p型の不純物注入したp型ゲートを、nチャネル型MISFETQnにおいては、n型の不純物領域を注入したn型ゲートを採用した構成を、デュアルゲート構造と呼ぶことがある。このデュアルゲート構造によれば、各ゲート電極(GE1、GE2)を低抵抗化できる。また、短チャネル効果を抑制でき、漏れ電流を低減するなど、トランジスタ特性を向上させることができる。

【0035】

次いで、ゲート電極GE1、GE2と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、例えば、半導体基板1(の主面全面)上に酸化シリコン膜7をCVD法などを用いて堆積し、この酸化シリコン膜をRIE(Reactive Ion Etching:反応性イオンエッチング)法などにより異方性エッチングすることによって形成する(図6)。

【0036】

次いで、図6に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR2aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入IM2aすることにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0037】

エクステンション領域EX1はn型の半導体領域であり、後で形成するn+型半導体領域SD1よりも不純物濃度が低い。エクステンション領域EX1の深さ(接合深さ)は、後で形成されるn+型半導体領域SD1の深さ(接合深さ)よりも浅い。

【0038】

次いで、図7に示すように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物のイオン注入(ハローイオン注入)IM3aを行ってハロー領域(p型半導体領域)HA1を形成する。

【0039】

ハロー領域HA1は、エクステンション領域EX1とは逆の導電型で、かつp型ウエルPWとは同じ導電型であり、ここではp型(p型の半導体領域)である。ハロー領域HA1は、短チャネル特性(パンチスルー)抑制のために形成される。ハロー領域HA1は、エクステンション領域EX1を包み込む(覆う)ように形成され、p型ウエルPWよりも不純物濃度(p型不純物濃度)が高い。ハロー領域HA1を形成するためのイオン注入IM3aは、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域EX1を包み込む(覆う)ようにハロー領域HA1を的確に形成することができる。斜めイオン注入では、半導体基板1の主面に対して垂直な方向から所定の角度(傾斜角)傾斜した方向に不純物イオンを加速して打ち込む。

【0040】

次いで、図8に示すように、アッシングなどによりフォトレジスト膜PR2aを除去してから、pMIS形成領域1Bを開口したフォトレジスト膜PR2bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入IM2bすることにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0041】

エクステンション領域EX2はp型の半導体領域であり、後で形成するp+型半導体領域SD2よりも不純物濃度が低い。エクステンション領域EX2の深さ(接合深さ)は、後で形成されるp+型半導体領域SD2の深さ(接合深さ)よりも浅い。

【0042】

次いで、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物のイオン注入(ハローイオン注入:IM3b)を行ってハロー領域(n型半導体領域)HA2を形成する。ハロー領域HA2は、エクステンション領域EX2とは逆の導電型で、かつn型ウエルNWとは同じ導電型であり、ここではn型(n型の半導体領域)である。ハロー領域HA2は、短チャネル特性(パンチスルー)抑制のために形成される。ハロー領域HA2は、エクステンション領域EX2を包み込む(覆う)ように形成され、n型ウエルNWよりも不純物濃度(n型不純物濃度)が高い。ハロー領域HA2を形成するためのイオン注入は、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域EX2を包み込む(覆う)ようにハロー領域HA2を的確に形成することができる。

【0043】

また、他の形態として、先にpMIS形成領域1Bにエクステンション領域EX2およびハロー領域HA2を形成してから、nMIS形成領域1Aにエクステンション領域EX1およびハロー領域HA1を形成してもよい。

【0044】

また、ハロー領域HA1,HA2は、短チャネル特性抑制のために形成することが好ましいが、不要であればその形成を省略することもできる。

【0045】

次いで、図9に示すように、アッシングなどによりフォトレジスト膜PR2bを除去した後、ゲート電極GE1、GE2と絶縁膜(キャップ絶縁膜、上部絶縁膜)CPとの積層体上を含む半導体基板1上に、絶縁膜S(側壁絶縁膜)として、例えば酸化シリコン膜(O)とその上部の窒化シリコン膜(N)との積層膜をCVD法などにより形成する。次いで、図10に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、その上部の窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、サイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、このサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。このように、酸化膜と窒化膜の積層膜をサイドウォール膜SWとして用いることで、酸化シリコン膜(O)の下層にある窒化シリコン膜(N)を酸化シリコン膜のエッチングストッパとして用いることができ、基板へのダメージを最小限にして、サイドウォール膜SWを加工することができる。

【0046】

次いで、図11に示すように、ゲート電極GE1、GE2上の絶縁膜(窒化シリコン膜)CPをエッチングにより除去する。これにより、ゲート電極(シリコン膜6)GE1、GE2の表面が露出する。また、ゲート電極(シリコン膜6)GE1、GE2の表面の両側にはサイドウォール膜SWの壁が延在する。別の言い方をすれば、ゲート電極(シリコン膜6)GE1、GE2上には凹部が形成され、凹部の側壁は、サイドウォール膜SWで構成されている。

【0047】

次いで、図12に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを、フォトリソグラフィ技術を用いて形成する。次いで、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0048】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、10keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、10keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。このイオン注入IM4aの際、ゲート電極GE1およびその側壁上のサイドウォール膜SWもマスク(イオン注入阻止マスク)として機能するので、n+型半導体領域SD1は、ゲート電極GE1の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。n+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0049】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0050】

次いで、図13に示すように、アッシングなどによりフォトレジスト膜PR3aを除去した後、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを、フォトリソグラフィ技術を用いて形成する。次いで、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、10keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。Geは、半導体基板1の表面をアモルファス状に変質させ、Bを注入する際のチャネリングを抑制し、浅い接合を形成するためにイオン注入する。このp+型半導体領域SD2は、ゲート電極GE2の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。p+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0051】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0052】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0053】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0054】

次いで、図14に示すように、アッシングなどによりフォトレジスト膜PR3bを除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0055】

次いで、いわゆる歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させる。nチャネル型MISFETQnの上部に、例えば、窒化膜を堆積し、熱処理を施した後、この窒化膜を除去する。この際、ゲート電極からチャネル領域に応力(引っ張り応力)が加わり、チャネル領域の結晶を歪ませる。この結果、チャネル領域中のキャリア移動度が増加し、オン電流が増加し、また、動作速度を向上させることができる。

【0056】

例えば、図15に示すように、ゲート電極GE1、GE2およびサイドウォール膜SW上を含む半導体基板1上に、下地絶縁膜9として、例えば薄い酸化シリコン膜(例えば、5nm程度)をCVD法などで堆積した後、その上部に、応力印加膜10として、窒化シリコン膜をCVD法などで例えば20nm程度堆積する。次いで、熱処理として、例えば、1000℃のスパイクアニールの後、1230℃のレーザーアニールを施す。次いで、例えば、熱燐酸などを用いたウエットエッチングにより、応力印加膜(窒化シリコン膜)10を除去する。次いで、残存する下地絶縁膜(酸化シリコン膜)9をドライエッチングまたはウエットエッチングで除去する。これにより、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の表面が露出する。この後、これらの表面に、シリサイド層(金属シリサイド層、シリサイド膜)11を形成するのであるが、このシリサイド層11を形成する必要がない箇所(例えば、高抵抗素子など)には、上記下地絶縁膜9をマスク(シリサイド化阻止マスク)として残存させてもよい。

【0057】

次いで、図16に示すように、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面を必要に応じて洗浄した後、これらの上部に、例えばニッケル(Ni)のような金属膜11aを例えば25nm程度堆積して熱処理(第1アニール)を施す。これにより、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の表面(シリコン表面)と金属膜11aとの界面においてシリサイド化反応が生じ、シリサイド層(金属シリサイド層、シリコンと金属膜との反応層)11が形成される(図17)。このシリサイド層11により、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の拡散抵抗やコンタクト抵抗などを低抵抗化することができる。その後、未反応の金属膜11aを除去し、さらに、熱処理(第2アニール)を施す。なお、このシリサイド層11の形成を省略することもできる。

【0058】

次いで、半導体基板1の主面上に絶縁膜(層間絶縁膜)12を形成する。例えば、ゲート電極GE1、GE2およびサイドウォール膜SW上に、窒化シリコン膜12aを形成し、さらにその上部に、より膜厚の大きい酸化シリコン膜12bを形成し、これらの膜の積層膜よりなる絶縁膜12を形成する。この窒化シリコン膜12aおよび酸化シリコン膜12bは、CVD法などで形成することができる。なお、絶縁膜12として、例えば、酸化シリコン膜の単体膜を用いてもよい。

【0059】

その後、絶縁膜12の表面(上面)をCMP(CMP:Chemical Mechanical Polishing、化学機械研磨)法により研磨するなどして、絶縁膜12の上面を平坦化する。下地段差に起因して絶縁膜12の表面に凹凸形状が形成されていても、絶縁膜12の表面をCMP法により研磨することにより、その表面が平坦化された絶縁膜12を得ることができる。

【0060】

次いで、絶縁膜12をパターニングすることにより、絶縁膜12中にコンタクトホール(接続孔、貫通孔、孔)13を形成する。コンタクトホール13の底部においては、半導体基板1の主面の一部、例えばn+型半導体領域SD1およびp+型半導体領域SD2の表面上のシリサイド層11の一部が露出している。

【0061】

次いで、コンタクトホール13内に、タングステン(W)などからなる導電性のプラグ(コンタクトプラグ、接続用導体部)14を形成する。例えば、コンタクトホール13の内部(底部および側壁上)を含む絶縁膜12上に、プラズマCVD法によりバリア膜(図示せず)として、例えば、チタン膜、窒化チタン膜、あるいはそれらの積層膜を形成した後、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール13を埋めるように形成する。次いで、絶縁膜12上の不要な主導体膜およびバリア膜をCMP法またはエッチバック法などによって除去することにより、プラグ(コンタクトプラグ、接続部)14を形成する。プラグ14は、その底部で、n+型半導体領域SD1またはp+型半導体領域SD2の表面上のシリサイド層11と接して、電気的に接続される。なお、図17においては、n+型半導体領域SD1またはp+型半導体領域SD2上のプラグ14しか表示していないが、ゲート電極GE1、GE2上にもプラグ14が形成される。

【0062】

次いで、図18に示すように、プラグ14が埋め込まれた絶縁膜12上に、配線溝用の絶縁膜15を形成する。絶縁膜15は、例えば、窒化シリコン膜とその上部の酸化シリコン膜との積層膜で構成する。なお、絶縁膜15を単層膜で構成してもよい。

【0063】

次に、シングルダマシン法により第1層目の配線である配線M1を形成する。具体的には、絶縁膜15をパターニングすることにより、所定の領域に配線溝を形成した後、配線溝の底部および側壁上を含む絶縁膜15上にバリア膜(例えば窒化チタン膜、タンタル膜または窒化タンタル膜など)を形成する。続いて、CVD法またはスパッタリング法などによりバリア膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成して、銅めっき膜により配線溝の内部を埋め込む。次いで、配線溝以外の領域の主導体膜(銅めっき膜およびシード層)とバリアメタル膜をCMP法により除去して、配線溝に埋め込まれ銅を主導電材料とする第1層目の配線M1を形成する。なお、図18においては、図面の簡略化のために、配線M1は、バリア導体膜、シード層および銅めっき膜を一体化して示してある。

【0064】

配線M1は、プラグ14を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのソースまたはドレイン用のn+型半導体領域SD1およびp+型半導体領域SD2と電気的に接続されている。また、配線M1は、プラグ14を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのゲート電極GE1、GE2と電気的に接続されている。

【0065】

その後、デュアルダマシン法などにより2層目の配線を形成するが、ここでは、2層目以降の配線およびその形成工程の説明は省略する。

【0066】

以上のようにして、本実施の形態の半導体装置が製造される。

【0067】

ここで、本実施の形態においては、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、この絶縁膜CPを除去した後、ヒ素(As)をイオン注入したので、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができる。

【0068】

図19〜図21に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。また、図22〜図24には、比較例の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0069】

図19〜図21に示すように、本実施の形態においては、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、サイドウォール膜SWを形成した後(図19)、絶縁膜CPをエッチバック(エッチング)により除去し(図20)、ヒ素(As)をイオン注入している(図21)。

【0070】

一方、絶縁膜CPの形成およびエッチバックを行わない比較例においては、図22に示すように、ゲート電極GEの高さとサイドウォール膜SWの高さとがほぼ同じであるため、図23に示すように、ゲート電極GEの上部がヒ素(As)のイオン注入により横方向に膨張する。その結果、図24に示すように、シリサイド層11またはゲート電極GEとプラグ14との距離(白抜き矢印部参照)が小さくなり、ゲート電極GEとプラグ14間での短絡(ショート)の要因となる。なお、前述の図17等においては、図面を見やすくするためゲート電極GEとプラグ14との間を大きく表示してあるが、素子の微細化に伴い、ゲート電極GEとプラグ14が小さくなる傾向にあり、実際には、図24に示すように、サイドウォール膜SWとプラグ14とが近接し、また、平面パターンが重なるような配置となることが多い。

【0071】

本発明者の検討によれば、かかる課題(ゲート電極とプラグ間のショートマージンの低下)は、nチャネル型MISFETで顕著に確認された。

【0072】

図25は、nチャネル型MISFETの断面写真である。図26は、pチャネル型MISFETの断面写真である。図25のnチャネル型MISFETにおいては、ゲート電極上のシリサイド層が横方向に張り出している。これに対し、図26のpチャネル型MISFETにおいては、シリサイド層の横方向の張り出し(突き出し)は少ない。

【0073】

上記現象について、発明者がさらに検討したところ、nチャネル型MISFETのゲート電極(ソース、ドレイン領域)に打ち込まれるイオン種が要因ではないかとの結論に到った。

【0074】

図27は、nチャネル型MISFETのゲート電極にリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。図28は、nチャネル型MISFETのゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合の断面写真(左)およびその模写図(右)である。イオン注入条件としては、図27は、リン(P)を8keVのエネルギー、4.0×1015/cm2の条件でイオン注入した場合を示し、また、図28は、ヒ素(As)を10keVのエネルギー、8.0×1015/cm2の条件で、リン(P)を10keVのエネルギー、5.0×1013/cm2の条件でイオン注入した場合を示す。

【0075】

図27に示すように、ゲート電極にリン(P)のみを打ち込んだ場合は、シリサイド層の横方向の張り出しは少ない。図28に示すように、ゲート電極にヒ素(As)およびリン(P)を打ち込んだ場合は、シリサイド層の横方向の張り出しが大きいことが分かった(矢印部参照)。これは、比較的原子量が大きいヒ素(As)の注入ダメージによるものではないかと考察される。

【0076】

これにより、ヒ素(As)のイオン注入により、ゲート電極の上部が、横方向に張り出すようにゲート電極形状が変形し、さらに、この後のシリサイド化反応に伴う堆積膨張により、ゲート電極の上部のシリサイド層がさらに横方向に張り出すことが分かった。

【0077】

このように、ゲート電極の上部およびシリサイド層の横方向の張り出しが大きくなると、ゲート電極(シリサイド層含む)とプラグとの距離が小さくなり、耐圧の劣化や短絡が生じ不良の要因となる(図24参照)。さらに、素子の微細化に伴い、ゲート電極(シリサイド層含む)とプラグとの距離は縮小傾向にあり、素子の微細化が進むほど、上記横方向の張り出しの問題解決が重要となる。

【0078】

これに対し、本実施の形態においては、前述したように、ゲート電極GE1上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、この絶縁膜CPを除去することにより、ゲート電極GE1上に、凹部を形成し、この凹部の側壁にサイドウォール膜SWを配置したので、ヒ素(As)のイオン注入により、ゲート電極GE1の上部が張り出す領域をこの凹部内に確保し、さらに、サイドウォール膜SWよりなる凹部の側壁で、ゲート電極GE1の上部の横方向への張り出しを抑制することができる。よって、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0079】

なお、本実施の形態においては、pMIS形成領域1Bのゲート電極GE2上にも絶縁膜CPを形成し、この絶縁膜CPを除去することにより、ゲート電極GE2上にも凹部を形成した。しかしながら、前述したとおり、ゲート電極とプラグ間のショートマージンの低下は、nチャネル型MISFETで顕著であるため、pMIS形成領域1Bの絶縁膜CPをあらかじめ除去しておいてもよい。但し、この除去工程を省くことで、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0080】

次いで、本実施の形態の半導体装置の構造的特徴の一例について説明する。

【0081】

図29および図30は、本実施の形態のnチャネル型MISFETQnの断面図である。図31および図32は、pチャネル型MISFETQpの断面図である。図29および図31は、それぞれ、シリサイド層11の形成後の断面図であり、図30および図32は、それぞれ、窒化シリコン膜12a形成後の断面図である。

【0082】

前述したように、ゲート電極GE1、GE2上にあらかじめ絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを形成し、絶縁膜CPを除去する際、サイドウォール膜SW中の絶縁膜CPと同じ膜種(この場合、窒化シリコン膜)よりなる第2側壁膜SWbもエッチングされる(図29、図30参照)。よって、第2側壁膜(窒化シリコン膜)SWbの高さ(HSWb)は、第1側壁膜(酸化シリコン膜)SWaの高さ(HSWa)よりも低くなる(HSWb<HSWa)。

【0083】

また、nチャネル型MISFETQn(図29)において、絶縁膜(キャップ絶縁膜、上部絶縁膜)CPを除去した際のゲート電極GE1上の凹部内においては、ゲート電極(シリコン膜)GE1が膨張して充填され、さらに、その後のシリサイド化によりシリサイド層11が充填される。一方、pチャネル型MISFETQp(図31)においては、横方向の張り出しが少ない分だけ、ゲート電極(シリコン膜)GE2の膨張量が少なく、その後、シリサイド化しても、nチャネル型MISFETQnのゲート電極(シリサイド層11含む)GE1の高さHQnよりも、pチャネル型MISFETQpのゲート電極(シリサイド層11含む)GE2の高さHQpが小さくなることが考え得る(HQn>HQp、図29、図30参照)。

【0084】

但し、上記高さの関係はあくまで一例にすぎない。即ち、絶縁膜CP除去後にも、種々の洗浄やエッチングの処理があり、これらの処理により第1側壁膜SWa、第2側壁膜SWbがそれぞれ個別にエッチングされ得る。よって、その後の工程によっては、第1側壁膜SWaと第2側壁膜SWbとの高さの関係が逆になるということも考えられる。また、シリサイド化の条件などにより、ゲート電極(シリサイド層11含む)GE1、GE2の高さも変わり得るので、上記高さの関係が、最終的なMISFET(Qn、Qp)の断面形状として必ず表れるわけではない。

【0085】

(実施の形態2)

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図33〜図40は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0086】

まず、上記実施の形態1と同様に、nMIS形成領域1Aの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、p型ウエル(p型半導体領域)PWを形成する。また、pMIS形成領域1Bの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、n型ウエル(n型半導体領域)NWを形成する。これまでの工程については、実施の形態の図1〜図3が参照される。

【0087】

次いで、半導体基板1の表面を清浄化(洗浄)した後、実施の形態1と同様に、ゲート絶縁膜用の絶縁膜5を形成し、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。次いで、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とし、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする(図4参照)。但し、本実施の形態においては、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、窒化シリコン膜)CPを形成せず、図33に示すように、シリコン膜6のパターニングにより、ゲート電極GE1、GE2を形成する。

【0088】

次いで、ゲート電極GE1、GE2の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、実施の形態1と同様に形成することができる。

【0089】

次いで、実施の形態1と同様に、nMIS形成領域1Aを開口したフォトレジスト膜をマスクにゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0090】

また、実施の形態1と同様に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物を傾斜イオン注入することにより、ハロー領域(p型半導体領域)HA1を形成する。

【0091】

次いで、実施の形態1と同様に、pMIS形成領域1Bを開口したフォトレジスト膜をマスクにゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0092】

また、実施の形態1と同様に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物を傾斜イオン注入することにより、ハロー領域(n型半導体領域)HA2を形成する。

【0093】

次いで、アッシングなどにより上記フォトレジスト膜を除去した後、ゲート電極GE1、GE2上を含む半導体基板1上に、絶縁膜(側壁絶縁膜)として、例えば酸化シリコン膜とその上部の窒化シリコン膜との積層膜をCVD法などにより形成する。次いで、図34に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜とその上層の窒化シリコン膜との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。

【0094】

次いで、図35に示すように、ゲート電極GE1、GE2およびサイドウォール膜SW上を含む半導体基板1上に、スルー絶縁膜F5として、例えば、酸化シリコン膜をCVD法などで堆積する。なお、酸化シリコン膜に代えて窒化シリコン膜を用いてもよい。また、これらの絶縁膜の積層膜をスルー絶縁膜F5として用いてもよい。

【0095】

次いで、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを形成し、これをマスクに、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、スルー絶縁膜F5を介して、リン(P)またはヒ素(As)などのn型の不純物をイオン注入(IM4a)することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0096】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、20keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、20keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。なお、本実施の形態においては、スルー絶縁膜F5を介して、イオン注入を行っているため、注入エネルギーを実施の形態1の場合(10keV)より大きく(例えば、20keVと)してある。

【0097】

このn+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0098】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0099】

次いで、アッシングなどにより上記フォトレジスト膜PR3aを除去した後、図36に示すように、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを形成し、これをマスクに、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、スルー絶縁膜F5を介して、ホウ素(B)などのp型の不純物をイオン注入(IM4b)することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、20keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。

【0100】

このp+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0101】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0102】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0103】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0104】

次いで、アッシングなどにより上記フォトレジスト膜PR3bを除去し、例えば、熱燐酸などを用いたウエットエッチングによりスルー絶縁膜F5も除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0105】

次いで、実施の形態1と同様に、歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させた後(図15参照)、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面上に、シリサイド層11を形成する(図16、図17参照)。さらに、この後、実施の形態1と同様に、絶縁膜(層間絶縁膜)12を形成し、その内部のコンタクトホール13内にプラグ14を形成した後、その上部の配線溝用の絶縁膜15中に配線M1を形成する(図37)。その後、デュアルダマシン法などにより2層目の配線を形成するが、ここでは、2層目以降の配線およびその形成工程の説明は省略する。

【0106】

また、他の形態として、このスルー絶縁膜F5を残存させ、歪み印加技術用の絶縁膜(窒化シリコン膜)として用いてもよい。即ち、スルー絶縁膜F5を残存させた状態で、応力印加膜として利用し、実施の形態1で説明したように、熱処理を施す。例えば、1000℃のスパイクアニールの後、1230℃のレーザーアニールを施す。次いで、例えば、熱燐酸などを用いたウエットエッチングにより、スルー絶縁膜F5を除去するが、この際、その後のシリサイド化工程において、このシリサイド層11を形成する必要がない箇所(例えば、高抵抗素子など)には、上記スルー絶縁膜F5をマスク(シリサイド化阻止マスク)として残存させてもよい。

【0107】

以上のようにして、本実施の形態の半導体装置が製造される。

【0108】

ここで、本実施の形態においては、ゲート電極GE1上にスルー絶縁膜F5を形成し、このスルー絶縁膜F5を介して、ヒ素(As)をイオン注入したので、実施の形態1において詳細に説明したヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができる。その結果、ヒ素(As)のイオン注入によるゲート電極GE1の上部の横方向への膨らみを低減でき、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離を確保することができる。

【0109】

図38〜図40に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0110】

図38〜図40に示すように、本実施の形態においては、本実施の形態においては、ゲート電極GE1の側壁にSWを形成した後(図38)、図39に示すように、ゲート電極のGE1上部にスルー絶縁膜F5を形成し、このスルー絶縁膜F5を介してヒ素(As)をイオン注入している(図40)。よって、打ち込まれるイオン、特に、ヒ素(As)のイオン注入により、ゲート電極GE1の上部が横方向に張り出すことを、このスルー絶縁膜F5の応力により抑制することができる。よって、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0111】

なお、本実施の形態においては、スルー絶縁膜F5をpMIS形成領域1Bにも形成し、スルー絶縁膜F5を介して、p型の不純物をイオン注入(IM4b)したが、前述したとおり、ゲート電極とプラグ間のショートマージンの低下は、nチャネル型MISFETで顕著であるため、pMIS形成領域1Bのスルー絶縁膜F5を除去してもよい。但し、この除去工程を省くことで、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0112】

(実施の形態3)

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図41〜図49は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0113】

まず、上記実施の形態1と同様に、nMIS形成領域1Aの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、p型ウエル(p型半導体領域)PWを形成する。また、pMIS形成領域1Bの半導体基板1中にチャネルドープ層(図示せず)を形成し、さらに、n型ウエル(n型半導体領域)NWを形成する。これまでの工程については、実施の形態の図1〜図3が参照される。

【0114】

次いで、半導体基板1の表面を清浄化(洗浄)した後、実施の形態1と同様に、ゲート絶縁膜用の絶縁膜5を形成し、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電性膜として、シリコン膜6を形成する。次いで、nMIS形成領域1Aのシリコン膜6を低抵抗のn型半導体膜(ドープトポリシリコン膜)とし、pMIS形成領域1Bのシリコン膜を低抵抗のp型半導体膜(ドープトポリシリコン膜)とする(図4参照)。但し、本実施の形態においては、シリコン膜6上に、絶縁膜(キャップ絶縁膜、上部絶縁膜、窒化シリコン膜)CPを形成せず、図41に示すように、シリコン膜6のパターニングにより、ゲート電極GE1、GE2を形成する。

【0115】

次いで、ゲート電極GE1、GE2の側壁上に、例えば、酸化シリコン膜などからなるオフセットスペーサ(側壁膜、側壁スペーサ)OFSを形成する。オフセットスペーサOFSは、実施の形態1と同様に形成することができる。

【0116】

次いで、実施の形態1と同様に、nMIS形成領域1Aを開口したフォトレジスト膜をマスクにゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)EX1を形成する。

【0117】

また、実施の形態1と同様に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物を傾斜イオン注入することにより、ハロー領域(p型半導体領域)HA1を形成する。

【0118】

次いで、実施の形態1と同様に、pMIS形成領域1Bを開口したフォトレジスト膜をマスクにゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)EX2を形成する。

【0119】

また、実施の形態1と同様に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物を傾斜イオン注入することにより、ハロー領域(n型半導体領域)HA2を形成する。

【0120】

次いで、アッシングなどにより上記フォトレジスト膜を除去した後、ゲート電極GE1、GE2上を含む半導体基板1上に、絶縁膜(側壁絶縁膜)として、例えば酸化シリコン膜とその上部の窒化シリコン膜との積層膜をCVD法などにより形成する。次いで、図42に示すように、上記積層膜をRIE法などにより異方性エッチングすることによってサイドウォール膜(側壁膜、側壁絶縁膜、サイドウォールスペーサ)SWを形成する。このサイドウォール膜SWは、下層の酸化シリコン膜よりなる第1側壁膜SWaと、窒化シリコン膜よりなる第2側壁膜SWbとを有する。なお、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜とその上層の窒化シリコン膜との積層膜で構成したが、いずれかの絶縁膜よりなる単層膜でサイドウォール膜SWを構成してもよい。また、ここでは、のサイドウォール膜SWを、下層に位置する酸化シリコン膜(O)とその上層の窒化シリコン膜(N)との積層膜、即ち、ON構成としたが、さらに、酸化シリコン膜(O)を積層し、ONO構成としてもよい。この他、ONON構成やONONON構成としてもよい。

【0121】

次いで、図43に示すように、nMIS形成領域1Aを開口したフォトレジスト膜PR3aを形成し、これをマスクに、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォール膜SWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入(IM4a)することにより、(一対の)n+型半導体領域SD1(ソース、ドレイン)を形成する。

【0122】

例えば、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)をイオン注入した後、リン(P)をイオン注入する。ヒ素(As)は、例えば、10keVのエネルギー、4.0×1015/cm2の条件でイオン注入する。また、リン(P)は、例えば、10keVのエネルギー、5.0×1013/cm2の条件でイオン注入する。このイオン注入IM4aの際、ゲート電極GE1およびその側壁上のサイドウォール膜SWもマスク(イオン注入阻止マスク)として機能するので、n+型半導体領域SD1は、ゲート電極GE1の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。n+型半導体領域SD1の深さ(接合深さ)は、エクステンション領域EX1の深さ(接合深さ)よりも深い。また、n+型半導体領域(第2半導体領域)SD1とエクステンション領域(第1半導体領域)EX1とは同じ導電型であるが、n+型半導体領域SD1は、エクステンション領域EX1よりも、不純物濃度(n型不純物濃度)が高い。

【0123】

また、このイオン注入IM4aにより、ゲート電極GE1中にもn型の不純物(リンおよびヒ素)が注入される。前述したように、nMIS形成領域1Aのシリコン膜6には、n型の不純物が注入されているが、その後の処理(特に、熱処理)などにより、不純物の揮発・拡散などによる不純物濃度の低下が生じ得る。そこで、上記イオン注入IM4aにより、再度、ゲート電極GE1中にn型の不純物(リンおよびヒ素)を注入することで、ゲート電極GE1中のn型の不純物を補償することができる。

【0124】

ここで、実施の形態1で詳細に説明したように、ゲート電極にヒ素(As)を打ち込んだ場合は、ゲート電極の上部が、縦方向および横方向に張り出す(図27等参照)。

【0125】

そこで、本実施の形態においては、図44に示すように、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部をエッチバックすることにより、縦方向および横方向の張り出したゲート電極(シリコン膜6)の部分を除去する。具体的には、nMIS形成領域1Aを開口したフォトレジスト膜PR3aをマスクに、ゲート電極(シリコン膜6)GE1の上部を、ドライエッチング(スライトエッチング)する。これにより、ゲート電極の上部の、縦方向および横方向の張り出しがエッチングにより除去される(図45)。エッチバック量は、例えば、5〜15nm程度である。また、不純物が注入されたシリコン膜は、半導体基板に対してエッチングレートが大きいため、半導体基板に対するダメージが少なく、ゲート電極の上部の張り出し領域をドライエッチングすることができる。

【0126】

次いで、アッシングなどにより上記フォトレジスト膜PR3aを除去した後、図45に示すように、pMIS形成領域1Bを開口したフォトレジスト膜PR3bを形成し、これをマスクに、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォール膜SWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入(IM4b)することにより、(一対の)p+型半導体領域SD2(ソース、ドレイン)を形成する。例えば、10keVのエネルギー、1.0×1015/cm2の条件でGeをイオン注入した後、例えば、1.4keVのエネルギー、4.0×1015/cm2の条件でBをイオン注入する。このp+型半導体領域SD2は、ゲート電極GE2の側壁上のサイドウォール膜SW(の側壁)に整合して形成される。p+型半導体領域SD2の深さ(接合深さ)は、エクステンション領域EX2の深さ(接合深さ)よりも深い。また、p+型半導体領域(第2半導体領域)SD2とエクステンション領域(第1半導体領域)EX2とは同じ導電型であるが、p+型半導体領域SD2は、エクステンション領域EX2よりも、不純物濃度(p型不純物濃度)が高い。

【0127】

また、このイオン注入IM4bにより、ゲート電極GE2中にもp型の不純物が注入され、ゲート電極GE2中のp型の不純物を補償することができる。

【0128】

なお、他の形態として、先にpMIS形成領域1Bにp+型半導体領域SD2を形成してから、nMIS形成領域1Aにn+型半導体領域SD1を形成してもよい。

【0129】

以上の工程により、nチャネル型MISFETQnのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、n+型半導体領域(不純物拡散層)SD1およびエクステンション領域(n−型半導体領域)EX1よりなる。また、pチャネル型MISFETQpのLDD構造のソース、ドレイン領域が形成される。このLDD構造のソース、ドレイン領域は、p+型半導体領域(不純物拡散層)SD2およびエクステンション領域(p−型半導体領域)EX2よりなる。

【0130】

次いで、アッシングなどにより上記フォトレジスト膜PR3bを除去する。次いで、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のフラッシュランプアニール処理にて行うことができる。

【0131】

次いで、実施の形態1と同様に、歪み印加技術(ストレスメモライゼーション技術;SMT)を用いてMISFETの特性を向上させた後(図15参照)、ゲート電極GE1、GE2、n+型半導体領域SD1およびp+型半導体領域SD2の露出面上に、シリサイド層11を形成する(図16、図17参照)。さらに、この後、実施の形態1と同様に、絶縁膜(層間絶縁膜)12を形成し、その内部のコンタクトホール13内にプラグ14を形成した後、その上部の配線溝用の絶縁膜15中に配線M1を形成する(図46)。その後、デュアルダマシン法により2層目の配線を形成するが、ここでは図示およびその説明は省略する。

【0132】

以上のようにして、本実施の形態の半導体装置が製造される。

【0133】

図47〜図49に、本実施の形態の半導体装置の製造工程におけるnMIS形成領域1Aの部分拡大図を示す。

【0134】

図47〜図49に示すように、本実施の形態においては、ゲート電極GE1の側壁にSWを形成した後(図47)、図48に示すように、ゲート電極GE1およびサイドウォール膜SWの両側の領域に、ヒ素(As)等をイオン注入し、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部をエッチバックする(図49)。これにより、ゲート電極GE1とプラグ14との距離(ショートマージン)を確保することができ、耐圧の向上や短絡の低減などを図ることができ、装置特性を向上させることができる。さらに、ゲート電極GE1の上部にシリサイド層11を形成した場合においても、このシリサイド層11とプラグ14との距離を確保することができる。また、素子の微細化により、ゲート電極(シリサイド層11含む)GE1とプラグ14との距離が小さくなっても、これらの距離を確保することが容易となる。

【0135】

なお、本実施の形態においては、nMIS形成領域1Aにおいて、ヒ素(As)をイオン注入した直後に、ゲート電極(シリコン膜6)GE1の上部のエッチバックを行ったが、エッチバック工程は、このタイミングに限られるものではない。例えば、pMIS形成領域1Bに、p+型半導体領域SD2(ソース、ドレイン)を形成した後、nMIS形成領域1Aのゲート電極(シリコン膜6)GE1の上部のみのエッチバックを行ってもよい。但し、この場合、エッチバック用のフォトレジスト膜を再度形成する必要がある。即ち、本実施の形態においては、n+型半導体領域SD1(ソース、ドレイン)の形成用のフォトレジスト膜PR3aを利用してエッチバックを行うことができ(図43、図44参照)、工程の短縮化やマスク(露光原版)数の低減を図ることができる。

【0136】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0137】

本発明は、半導体装置の製造方法に関し、特に、MISFETを有する半導体装置の製造に適用することができる。

【符号の説明】

【0138】

1 半導体基板

1A nMIS形成領域

1B pMIS形成領域

2 素子分離領域

3 絶縁膜

5 ゲート絶縁膜(絶縁膜)

6 シリコン膜

7 酸化シリコン膜

9 下地絶縁膜

10 応力印加膜

11 シリサイド層

11a 金属膜

12 絶縁膜

12a 窒化シリコン膜

12b 酸化シリコン膜

13 コンタクトホール

14 プラグ

15 絶縁膜

CP 絶縁膜

EX1 エクステンション領域

EX2 エクステンション領域

F5 スルー絶縁膜

GE ゲート電極

GE1 ゲート電極

GE2 ゲート電極

HA1 ハロー領域

HA2 ハロー領域

IM1a イオン注入

IM1b イオン注入

IM2a イオン注入

IM2b イオン注入

IM3a イオン注入

IM3b イオン注入

IM4a イオン注入

IM4b イオン注入

M1 配線

NW n型ウエル

OFS オフセットスペーサ

PR1a フォトレジスト膜

PR1b フォトレジスト膜

PR2a フォトレジスト膜

PR2b フォトレジスト膜

PR3a フォトレジスト膜

PR3b フォトレジスト膜

PW p型ウエル

Qn nチャネル型MISFET

Qp pチャネル型MISFET

SD1 n+型半導体領域

SD2 p+型半導体領域

SW サイドウォール膜

SWa 第1側壁膜

SWb 第2側壁膜

【特許請求の範囲】

【請求項1】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方に、導電性膜と前記導電性膜上の絶縁膜との積層膜を形成する工程と、

(b)前記積層膜をパターニングすることにより前記導電性膜を有するゲート電極と前記ゲート電極の上部に配置され前記絶縁膜よりなる上部絶縁膜との積層体を形成する工程と、

(c)前記(b)工程の後、前記積層体の側壁に側壁膜を形成する工程と、

(d)前記(c)工程の後、前記上部絶縁膜を除去する工程と、

(e)前記(d)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中にヒ素(As)を注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記(e)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記(c)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項2記載の半導体装置の製造方法。

【請求項5】

前記導電性膜はシリコン膜であり、

(f)前記(e)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項6】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方にゲート電極を形成する工程と、

(b)前記(a)工程の後、前記ゲート電極の側壁に側壁膜を形成する工程と、

(c)前記(b)工程の後、前記ゲート電極および前記側壁膜上に絶縁膜を形成する工程と、

(d)前記(c)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中に、前記絶縁膜を介して、ヒ素(As)を注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記(d)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項7記載の半導体装置の製造方法。

【請求項9】

前記(b)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項7記載の半導体装置の製造方法。

【請求項10】

前記ゲート電極はシリコン膜であり、

(e)前記(d)工程の後、前記絶縁膜を除去する工程と、

(f)前記(e)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項11】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方にゲート電極を形成する工程と、

(b)前記(a)工程の後、前記ゲート電極の側壁に側壁膜を形成する工程と、

(c)前記(b)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中に、絶縁膜を介して、ヒ素(As)を注入する工程と、

(d)前記(c)工程の後、前記ゲート電極の上部をエッチングする工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項12】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記(c)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

前記(b)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項15】

前記ゲート電極はシリコン膜であり、

(e)前記(d)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項1】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方に、導電性膜と前記導電性膜上の絶縁膜との積層膜を形成する工程と、

(b)前記積層膜をパターニングすることにより前記導電性膜を有するゲート電極と前記ゲート電極の上部に配置され前記絶縁膜よりなる上部絶縁膜との積層体を形成する工程と、

(c)前記(b)工程の後、前記積層体の側壁に側壁膜を形成する工程と、

(d)前記(c)工程の後、前記上部絶縁膜を除去する工程と、

(e)前記(d)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中にヒ素(As)を注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記(e)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記(c)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項2記載の半導体装置の製造方法。

【請求項5】

前記導電性膜はシリコン膜であり、

(f)前記(e)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項6】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方にゲート電極を形成する工程と、

(b)前記(a)工程の後、前記ゲート電極の側壁に側壁膜を形成する工程と、

(c)前記(b)工程の後、前記ゲート電極および前記側壁膜上に絶縁膜を形成する工程と、

(d)前記(c)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中に、前記絶縁膜を介して、ヒ素(As)を注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記(d)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項7記載の半導体装置の製造方法。

【請求項9】

前記(b)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項7記載の半導体装置の製造方法。

【請求項10】

前記ゲート電極はシリコン膜であり、

(e)前記(d)工程の後、前記絶縁膜を除去する工程と、

(f)前記(e)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項11】

MISFETを有する半導体装置の製造方法であって、

(a)半導体基板の上方にゲート電極を形成する工程と、

(b)前記(a)工程の後、前記ゲート電極の側壁に側壁膜を形成する工程と、

(c)前記(b)工程の後、前記側壁膜および前記ゲート電極の合成体の両側の前記半導体基板中および前記ゲート電極中に、絶縁膜を介して、ヒ素(As)を注入する工程と、

(d)前記(c)工程の後、前記ゲート電極の上部をエッチングする工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項12】

前記ヒ素は、前記MISFETのn型の第1半導体領域を構成することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記(c)工程において、前記ヒ素以外のn型の不純物を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

前記(b)工程の前に、前記ゲート電極の両側の前記半導体基板中にn型の不純物を注入することにより、前記第1半導体領域よりも浅く形成され、前記第1半導体領域よりも前記n型の不純物の濃度が低い第2半導体領域を形成することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項15】

前記ゲート電極はシリコン膜であり、

(e)前記(d)工程の後、前記ゲート電極上に金属膜を形成し、前記ゲート電極を構成する前記シリコン膜と前記金属膜との反応層であるシリサイド層を形成する工程を有することを特徴とする請求項11記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図25】

【図26】

【図27】

【図28】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図25】

【図26】

【図27】

【図28】

【公開番号】特開2013−93501(P2013−93501A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−235796(P2011−235796)

【出願日】平成23年10月27日(2011.10.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]