半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

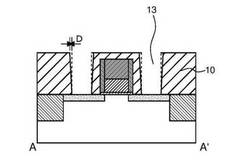

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、詳しくは絶縁膜中に微細なコンタクトホールを形成する方法に関する。

【背景技術】

【0002】

半導体装置において、層間絶縁膜にコンタクトホールを形成して導体(コンタクトプラグ)を埋め込むことで層間絶縁膜の下層の導体と上層の導体とを接続している。

【0003】

通常、このようなコンタクトホールは、フォトリソグラフィー技術とドライエッチング技術により形成される。

【0004】

通常、ドライエッチング法では、マスクパターンに忠実なパターンを被加工物に転写するために異方性ドライエッチングが用いられる。端的にいえば、プラズマ中に発生するエッチングガスイオンの電界加速性を利用した垂直エッチングである。酸化シリコン膜や窒化シリコン膜などのシリコン化合物のエッチングには主にフッ素イオンが用いられ、アルミニウム膜やタングステン膜などの金属のエッチングには主に塩素イオンが用いられている。異方性ドライエッチングでは横方向にマスクパターンからのズレを発生しないので微細パターンを形成することができる。現在では、半導体装置全般の製造に主流技術として用いられている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、より微細化が進んだ世代の半導体装置の製造においては、この垂直エッチングが、逆に悪影響を及ぼす問題が発生してきた。以下、この問題について説明する。

【0006】

図26(a)は、上面の所定領域に拡散層102が形成された半導体基板100上に層間絶縁膜103を形成し、拡散層102の上面を露出させるコンタクトホール104を形成した状態を示している。この後、図26(b)に示すように、全面に導体105を形成し、さらに図26(c)に示すように、ドライエッチング法によりエッチバックし、コンタクトプラグ107を形成し、コンタクトプラグ107の上面に図示しない配線を接続させて、配線と拡散層102を接続する工程が半導体製造においては古くから用いられている。図に記載した拡散層102は一例であって、下層に位置するコンタクトプラグ、下層に位置する配線などの場合もある。

【0007】

図26(a)で、層間絶縁膜103に形成するコンタクトホール104は、半導体装置の微細化に伴い、直径が30nm程度に極めて小さくなってきている。一方、配線108は低抵抗を保持しなければならない必然性から微細化が進んでも薄膜化できない事情がある。したがって、配線108を上層配線と絶縁するための層間絶縁膜103の厚さは、ほとんど薄膜化されず、一定の膜厚が保持される。そのため、コンタクトホール104のアスペクト比(深さ/直径)は半導体装置の微細化世代が進むごとに増加することとなる。アスペクト比が増大すると、図26(b)に示したように、導体105を形成した場合、直径の狭いコンタクトホール内では導体105の埋設が不十分となってボイド106が発生する。次いで、図26(c)に示したように、層間絶縁膜103の上面に形成された導体105を除去してコンタクトプラグ107を形成しても、ボイド106は残存する。この結果、ボイド106が生じている部分のコンタクトプラグ107の平面視における断面積が減少し抵抗が増大する問題がある。抵抗増大は半導体装置の高速動作を阻害する原因となる。また、図26(d)に示したように、層間絶縁膜103の上面に形成された導体105をドライエッチング法によりエッチバックしてコンタクトプラグ107を形成する場合には、オーバーエッチングによりボイド106の上部が露出する結果、拡散層102まで貫通エッチングしてしまい接合不良をもたらす問題も発生する。

【課題を解決するための手段】

【0008】

本発明の半導体装置の製造方法は、上記問題に鑑みて考案されたものであり、絶縁膜にコンタクトホールを形成する工程と、コンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施してコンタクトホールの内壁に傾斜を形成する工程と、コンタクトホール内にコンタクトプラグを形成する工程と、を有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、コンタクトホールの開口径を上部に向かって基板面に均一に拡大することができ、コンタクトホール内に埋め込むコンタクトプラグにボイドが形成されることを防止できる。

【図面の簡単な説明】

【0010】

【図1】ケミカルドライエッチングの温度条件に対するSiN/SiO2選択比を示すグラフである。

【図2】本発明の一実施例に係るMOSトランジスタの平面図である。

【図3】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図4】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図5】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図6】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図7】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図8】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図9】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図10】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図11】本発明の一実施例に係るメモリセルアレイの平面図である。

【図12】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図13】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図14】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図15】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図16】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図17】本発明の別の実施例に係るメモリセルアレイの平面図である。

【図18】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図19】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図20】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図21】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図22】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図23】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図24】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図である。

【図25】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図26】本発明の一つの課題を説明する工程断面図である。

【発明を実施するための形態】

【0011】

本発明に適用するケミカルドライエッチング(CDE)条件の説明

従来のCDEでは酸化シリコン膜の表面を高精度に一定量だけエッチング除去する技術が知られている。本発明者は、窒化シリコン膜に対してCDEを適用する検討を種々行なった結果、エッチング雰囲気の温度を70℃以上に制御することによって、窒化シリコン膜を酸化シリコン膜と同等のエッチング量でエッチングできることを見出した。

【0012】

図1は、CDEの温度条件に対するSiN/SiO2選択比を示すグラフである。同グラフに示すように室温(25℃)から45℃付近まで直線状に選択比が低下し、さらに温度を上げると緩やかに選択比が低下する。そして70℃以上では、ほぼ選択比1となり、窒化シリコン膜を酸化シリコン膜と同等のエッチング量でエッチングできる。酸化シリコン膜単独、或いは窒化シリコン膜単独の場合は選択比を考慮する必要がないため、所望のエッチング速度が得られるように温度を制御すればよい。

【0013】

CDEでは、絶縁膜中の構成原子とエッチングガス中の構成原子との反応物による堆積が起こることがある。酸化シリコンや窒化シリコンなどのシリコンを構成原子として含む絶縁膜に対して、エッチングガスとして、フッ素を含むガス(例えば、HF、NF3など)とアンモニア(NH3)とを用いると、フッ化アンモニウム(NH4F)等がエッチング雰囲気に生成し、一方、フッ素(F)と絶縁膜中のシリコン(Si)とが反応してフッ化ケイ素(SiF4)が生成する。フッ化ケイ素とフッ化アンモニウムが反応してケイフッ化アンモニウム((NH4)2SiF6)が生成する。

例えば、酸化シリコン(SiO2)の場合は、以下の反応が進行する。

SiO2 + 4F → SiF4

SiF4 + 2NH4F → (NH4)2SiF6

【0014】

ケイフッ化アンモニウムは堆積物として絶縁膜に付着し、これによりエッチングが阻害される。条件にも依存するが、10nm程度で反応が飽和して所望のエッチング量を確保することができなくなることがある。ケイフッ化アンモニウムは昇華性があり、昇華により露出した絶縁膜は再度エッチングされる。このように、ケイフッ化アンモニウムの堆積と昇華を繰り返すサイクルエッチングにより徐々にエッチングが進行する。純粋なケイフッ化アンモニウムは160℃を超える温度では分解する。昇華は分解温度よりも低い温度で起こっているが、昇華速度を速めるために好ましくは100℃以上に加熱することが好ましい。したがって、サイクルエッチングは、エッチングガスを供給して、例えば100℃未満でケイフッ化アンモニウムの堆積を行う工程と、エッチングガスの供給を停止し、100℃以上に加熱してケイフッ化アンモニウムを昇華又は分解して除去する工程を繰り返すことで実施することができる。このように、所望のエッチング量を確保することが困難な場合には、サイクルエッチングが適している。

【0015】

さらに、上記条件をコンタクトホールに適用したところ、層間絶縁膜が窒化シリコン膜、酸化シリコン膜のいずれの場合も、コンタクトホールの上方ほどエッチング量が大きくなる現象を知見した。特にケイフッ化アンモニウムの堆積と昇華を繰り返すサイクルエッチングを実施することでコンタクトホールの上部の拡幅を精度良く制御することが可能となる。

【0016】

また、本発明では、コンタクトホールに窒化シリコン膜と酸化シリコン膜とが混在して露出する場合に、いずれの膜に対しても同様のエッチング量とすることで、コンタクトホールの上部の拡幅を図る方法も提供する。

【実施例】

【0017】

以下、実施例を挙げて本発明を具体的に説明するが、本発明はこれらの実施例のみに限定されるものではない。

【0018】

実施例1

図2にMOS型トランジスタのレイアウトの一例の平面図を示す。図3〜図7は図2のA−A’の断面図を示している。

【0019】

(図3)

まず、半導体基板1上に素子分離(STI:Shallow Trench Isolation)領域2で囲まれた活性領域3を形成する。次に、活性領域3を横切り、X方向に延在するゲート電極5を形成する。ここでは、活性領域3の半導体基板1表面に厚さ5nmのゲート絶縁膜4、厚さ50nmのゲート電極5、厚さ50nmの窒化シリコン膜からなるカバー絶縁膜6を積層形成する。次に、リソグラフィとドライエッチング法により順次エッチングした後、側壁に窒化シリコン膜からなるサイドウォール(SW)絶縁膜7を形成する。ゲート電極5は多結晶シリコン上にタングステンなどの金属を積層したポリサイド構造、窒化チタンなどのバリヤ金属上にタングステンなどの低抵抗金属を積層した金属積層膜、ゲート絶縁膜4にハフニウムシリケート膜などの高誘電率膜を用いる場合にはタングステン単層構造などを用いることができる。いずれの場合もゲート電極5の最上面はタングステンなどの金属で構成される。

【0020】

続いて、ゲート電極パターンをマスクとして用い、イオン注入法により半導体基板表面に不純物導入し、ソース拡散層8およびドレイン拡散層9を形成する。

【0021】

最後にゲート電極パターンを覆うように、酸化シリコン膜からなる厚さ140nmの層間絶縁膜10を形成する。層間絶縁膜10はCVD法や回転塗布法により成膜した後、CMP法により表面平坦化することで形成できる。

【0022】

(図4)

次に、リソグラフィにより形成したマスク11を用い、ドライエッチング法によりソース拡散層8およびドレイン拡散層9に接続する直径30nmの拡散層コンタクトホール(第1のコンタクトホール)12を層間絶縁膜10に形成する。拡散層コンタクトホール12は、SW絶縁膜7には接していない。図2では、各々の拡散層上のX方向に3個並列に形成された例を示す。拡散層コンタクトホール12の内壁はこの段階では従来法と同様に垂直に形成されている。

【0023】

(図5)

続いて、マスク11を除去した後、本発明のCDE法により、拡散層コンタクトホールの開口部直径を拡大し、側壁に傾斜を形成する。

【0024】

本実施例のCDE法の条件は以下の通りである。

エッチングガス:NF3(14sccm)、NH3(50sccm)

圧力: 400Pa(3Torr)

温度: 35℃(エッチングガス供給時)/120℃(ケイフッ化アンモニウム昇華時)

RFパワー: 30W

時間: 60秒

【0025】

また、以下の条件でも同様の効果を得られる。

エッチングガス:HF(40sccm)、NH3(50sccm)

圧力: 11Pa(80mTorr)

温度: 35℃(エッチングガス供給時)/120℃(ケイフッ化アンモニウム昇華時)

RFパワー: 0W

時間: 60秒

【0026】

これにより、新たな拡散層コンタクトホール(第2のコンタクトホール)13を形成する。開口部の拡がりDは5nmに制御する。直径は30nmから40nmに拡大する。底面の拡散層はシリコンで構成されているので、CDEでは除去されない。

【0027】

高精度拡幅には、上記のようにケイフッ化アンモニウムの形成と昇華を繰り返すサイクルエッチングが有効である。

【0028】

(図6)

拡散層コンタクトホール13を埋め込むように、CVD法により全面に導体14を形成する。コンタクトホールが垂直側壁から傾斜側壁となっているのでボイドは発生しない。導体14としては、例えば、多結晶シリコン、タングステン等の金属の単層膜あるいは多結晶シリコンとタングステンなどの金属の積層膜などが例示できる。タングステン形成の場合は拡散層表面あるいは先に形成する多結晶シリコン上面に金属シリサイド(例えば、コバルトシリサイド)を形成し、さらに絶縁膜との間に窒化チタン等のバリヤ膜(例えば、Ti/TiNなど)を形成することが好ましい。

【0029】

(図7)

最後に、CMP法もしくはドライエッチング法により層間絶縁膜10上に形成されている導体14を除去し、拡散層コンタクトホール13内に拡散層コンタクトプラグ15を形成する。さらに、拡散層コンタクトプラグ15の上面と接続する配線16を形成する。

【0030】

本実施例によれば、拡散層コンタクトホール12の内壁は、酸化シリコン膜からなる層間絶縁膜10で構成されており、上記のCDE条件を用いることによりホールの上部を拡幅した傾斜を有する拡散層コンタクトホール13に加工することができる。その結果、拡散層コンタクトホール13を埋設する導体14におけるボイドの発生を防止して、抵抗増大や拡散層へのエッチングダメージを回避する拡散層コンタクトプラグ15を形成できる。

【0031】

実施例2

実施例1では、ソース及びドレイン拡散層に接続される拡散層コンタクトホールについて説明したが、図2に示すように、ゲート電極5に接続するゲートコンタクトホールも同様に形成することができる。ゲートコンタクトホールは、酸化シリコン膜からなる層間絶縁膜10と窒化シリコン膜からなるカバー絶縁膜6とを貫通して形成されているが、本発明による方法では、このように異なる絶縁膜が積層されている場合であっても適用できる。

図8〜図10は図2のB−B’の断面図を示している。

【0032】

(図8)

実施例1の図4工程において、拡散層コンタクトホール12の形成と同時又は別個に、ゲートコンタクトホール(第1のコンタクトホール)17を形成する。

【0033】

(図9)

実施例1の図5工程と同様に、本発明のCDE法により、ゲートコンタクトホール17の開口部直径を拡大し、側壁に傾斜を形成する。但し、エッチングガス供給時の雰囲気温度は80℃とした。これにより上部に向かって開口部直径が拡大したゲートコンタクトホール(第2のコンタクトホール)18が形成される。該工程は、実施例1の図5工程と同時に行うことができる。

【0034】

(図10)

その後、実施例1の図6工程、図7工程を経て、ゲートコンタクトプラグ19及び配線16を形成する。

【0035】

本実施例に示すように、コンタクトホールに異種の絶縁膜が露出している場合にも同様に開口部径の拡大を行うことができる。

【0036】

実施例3

図11は、埋込みワード線(WL1〜3)を用いたメモリセルアレイの平面図である。図11において、22はSTI領域、24は活性領域を示し、X’方向(第1の方向)に延在して形成される。活性領域24は、Y方向(第2の方向)にSTI領域23により分断され、それぞれ島状の活性領域24aとなる。各活性領域24aはさらにY方向に延在する2本の埋込ワード線で3つの拡散層に分割される。ビット線に接続される拡散層領域をビット線コンタクト領域25、容量コンタクトプラグ35が接続される拡散層領域を容量コンタクト領域26と呼ぶ。ビット線コンタクト領域25は各活性領域24aの中央部に配置され、X方向(第3の方向)に延在するビット線(BL1〜3)が接続される。容量コンタクト領域26は各活性領域24aの両端に配置され、容量コンタクトプラグ35が接続される。

【0037】

以下、断面図を参照してこのメモリセルアレイの製造方法を説明する。図12〜16は、本実施例に係るメモリセルアレイの製造工程を説明する工程断面図であり、各図(a)は、図11のA−A’線、各図(b)はB−B’線での断面に相当する。

【0038】

(図12)

まず、半導体基板21にSTI領域22,23となる溝を形成し、絶縁膜を埋め込んでSTI領域22,23を形成する。続いて、活性領域24に拡散層用の不純物イオンを注入して拡散層(図示せず)を形成する。次に、ワード線用の溝を図11のY方向に形成し、ワード線導体層を埋込み、さらに窒化シリコン膜からなるキャップ絶縁膜27を形成して表面を平坦化する。なお、ワード線と半導体基板21とは図示しないゲート絶縁膜で分離されている。また、ワード線導体層の表面は活性層の深さよりも深い位置になるように埋め込まれる。なお、STI領域23に代えて、ダミーのワード線を形成して活性領域24を各活性領域24aに分離することもできる。

【0039】

(図13)

次に、酸化シリコン膜からなる第1層間絶縁膜28を形成した後、ビット線コンタクト領域25を露出するビットコンタクトホール(図示せず)を形成し、ビット線となる導体層及び窒化シリコン膜からなるカバー絶縁膜29を成膜し、パターニングしてビット線(BL1〜3)を形成する。さらに、ビット線(BL1〜3)の側壁に窒化シリコン膜からなる第1サイドウォール(SWD1)を形成する。その後、全面に酸化シリコン膜からなる第2層間絶縁膜30を形成し、カバー絶縁膜29及び第1サイドウォール(SWD1)をストッパーとしてCMP等で平坦化する。

【0040】

(図14)

第2層間絶縁膜30上にマスク膜31を形成し、容量コンタクト領域26を露出する容量コンタクトホール(第1のコンタクトホール)32を形成する。

【0041】

(図15)

実施例1の図5工程と同様に、本発明のCDE法により、容量コンタクトホール32の開口部直径を拡大し、側壁に傾斜を形成する。但し、エッチングガス供給時の雰囲気温度は80℃とした。ここでは、酸化シリコン膜からなる第2層間絶縁膜30と窒化シリコン膜からなる第1サイドウォール(SWD1)は同程度にエッチングされ、いずれも上部に向かって直径が拡大した容量コンタクトホール(第2のコンタクトホール)33が形成される。

【0042】

(図16)

その後、容量コンタクトプラグ34を形成し、さらにキャパシタ35を形成する。このように、容量コンタクトプラグ34の上部の径が拡張されていることで、ボイドの発生を抑制すると共に、アレイパターンが微細化されてもキャパシタ35の下部電極とのコンタクト面積を確保することができる。

【0043】

実施例4

実施例3に示したメモリセルアレイにおいて、更に微細化が進むと、容量コンタクト領域に容量コンタクトホールを均一に形成することが困難となり、キャパシタ特性に影響する場合がある。本実施例では、隣接する島状活性領域24aの対向する容量コンタクト領域26を一括して開口し、コンタクトプラグとなる導体を埋め込んだ後、2つのプラグに分割するツインプラグ法により容量コンタクトプラグを形成する方法について説明する。

【0044】

図17は、図11と同様にメモリセルアレイの平面図を示し、Y方向に延在するマスク領域41と開口領域42を示す。開口領域42とビット線(BL1〜3)とで画定される領域を単位開口部44と呼び、この部分にコンタクトプラグとなる導体が埋め込まれる。

【0045】

図18〜図25は、本実施例に係る半導体装置の製造工程を説明する工程断面図であり、各図において、(a)は図17のA−A’線での断面図、(b)は図17のB−B’線での断面図を示す。

【0046】

(図18)

実施例3と同様にビット線の側壁に第1サイドウォールSWD1を形成した後、酸化シリコン膜からなる第2層間絶縁膜30を形成する。実施例3では第1サイドウォールSWD1の上面までとしていたが、本実施例では第2層間絶縁膜30の上面が第1サイドウォールSWD1の上面よりも高い位置となるように形成する。次に、マスク領域41にフォトレジスト等のマスク膜43を形成する。

【0047】

(図19)

マスク膜43をマスクに開口領域42に露出する酸化シリコン膜からなる第1及び第2層間絶縁膜28及び30をエッチングする。これにより単位開口部44が形成される。

【0048】

(図20)

窒化シリコン膜を成膜した後、エッチバックして第2サイドウォールSWD2を単位開口部44に露出する第1及び第2層間絶縁膜28及び30の側壁及び第1サイドウォールSWD1の側壁に形成する。第2サイドウォールSWD2形成後の単位開口部を単位開口部(第1のコンタクトホール)45とする。

【0049】

(図21)

次に、実施例1の図5工程と同様に、本発明のCDE法により、単位開口部45の開口部直径を拡大し、側壁に傾斜を形成する(第2のコンタクトホール)。但し、エッチングガス供給時の雰囲気温度は80℃とした。

【0050】

(図22)

続いて、容量コンタクトプラグとなる導体46を形成する。導体46は、ビット線上のカバー絶縁膜29がちょうど露出するか露出しない程度にエッチバックする。カバー絶縁膜29の表面より低く形成すると、次の工程での第3サイドウォールがビット線側壁の第2サイドウォール側壁にも形成され、その後の導体46の分離が不十分となる場合がある。

【0051】

(図23)

窒化シリコン膜を形成し、エッチバックして第3サイドウォールSWD3を形成する。さらに、第3サイドウォールSWD3をマスクに、導体46をエッチングし、単位開口部45内で2つの容量コンタクトプラグ47に分割する。

【0052】

(図24)

全面に絶縁膜を形成し、CMP等により平坦化する。これにより単位開口部45内の2つの容量コンタクトプラグ47の間に埋込絶縁膜48が埋め込まれる。

【0053】

(図25)

その後、実施例3と同様にキャパシタ35を形成する。

【0054】

本実施例に示すように、単位開口部45側壁がすべて窒化シリコン膜である場合にも同様に開口部径の拡大を行うことができる。また、本発明のCDE法を適用することで開口内側壁の傾斜角を精密に制御できるため、ツインプラグ構造では、一つの単位開口部内で分離して形成された2つのプラグの下部中心点間距離よりも上部中心点間距離が広くなり、キャパシタのレイアウトに制限されることなく、メモリセルレイアウトの自由度が向上する。

【符号の説明】

【0055】

1,21 半導体基板

2,22,23 STI領域

3,24 活性領域

4 ゲート絶縁膜

5 ゲート電極

6 カバー絶縁膜

7 サイドウォール絶縁膜

8 ソース拡散層

9 ドレイン拡散層

10 層間絶縁膜

11 マスク

12,13 拡散層コンタクトホール

14 導体

15 拡散層コンタクトプラグ

16 配線

17,18 ゲートコンタクトホール

19 ゲートコンタクトプラグ

25 ビット線コンタクト領域

26 容量コンタクト領域

27 キャップ絶縁膜

28 第1層間絶縁膜

29 カバー絶縁膜

30 第2層間絶縁膜

31 マスク膜

32,33 容量コンタクトホール

34 容量コンタクトプラグ

35 キャパシタ

41 マスク領域

42 開口領域

43 マスク膜

44,45 単位開口部

46 導体

47 容量コンタクトプラグ

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、詳しくは絶縁膜中に微細なコンタクトホールを形成する方法に関する。

【背景技術】

【0002】

半導体装置において、層間絶縁膜にコンタクトホールを形成して導体(コンタクトプラグ)を埋め込むことで層間絶縁膜の下層の導体と上層の導体とを接続している。

【0003】

通常、このようなコンタクトホールは、フォトリソグラフィー技術とドライエッチング技術により形成される。

【0004】

通常、ドライエッチング法では、マスクパターンに忠実なパターンを被加工物に転写するために異方性ドライエッチングが用いられる。端的にいえば、プラズマ中に発生するエッチングガスイオンの電界加速性を利用した垂直エッチングである。酸化シリコン膜や窒化シリコン膜などのシリコン化合物のエッチングには主にフッ素イオンが用いられ、アルミニウム膜やタングステン膜などの金属のエッチングには主に塩素イオンが用いられている。異方性ドライエッチングでは横方向にマスクパターンからのズレを発生しないので微細パターンを形成することができる。現在では、半導体装置全般の製造に主流技術として用いられている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、より微細化が進んだ世代の半導体装置の製造においては、この垂直エッチングが、逆に悪影響を及ぼす問題が発生してきた。以下、この問題について説明する。

【0006】

図26(a)は、上面の所定領域に拡散層102が形成された半導体基板100上に層間絶縁膜103を形成し、拡散層102の上面を露出させるコンタクトホール104を形成した状態を示している。この後、図26(b)に示すように、全面に導体105を形成し、さらに図26(c)に示すように、ドライエッチング法によりエッチバックし、コンタクトプラグ107を形成し、コンタクトプラグ107の上面に図示しない配線を接続させて、配線と拡散層102を接続する工程が半導体製造においては古くから用いられている。図に記載した拡散層102は一例であって、下層に位置するコンタクトプラグ、下層に位置する配線などの場合もある。

【0007】

図26(a)で、層間絶縁膜103に形成するコンタクトホール104は、半導体装置の微細化に伴い、直径が30nm程度に極めて小さくなってきている。一方、配線108は低抵抗を保持しなければならない必然性から微細化が進んでも薄膜化できない事情がある。したがって、配線108を上層配線と絶縁するための層間絶縁膜103の厚さは、ほとんど薄膜化されず、一定の膜厚が保持される。そのため、コンタクトホール104のアスペクト比(深さ/直径)は半導体装置の微細化世代が進むごとに増加することとなる。アスペクト比が増大すると、図26(b)に示したように、導体105を形成した場合、直径の狭いコンタクトホール内では導体105の埋設が不十分となってボイド106が発生する。次いで、図26(c)に示したように、層間絶縁膜103の上面に形成された導体105を除去してコンタクトプラグ107を形成しても、ボイド106は残存する。この結果、ボイド106が生じている部分のコンタクトプラグ107の平面視における断面積が減少し抵抗が増大する問題がある。抵抗増大は半導体装置の高速動作を阻害する原因となる。また、図26(d)に示したように、層間絶縁膜103の上面に形成された導体105をドライエッチング法によりエッチバックしてコンタクトプラグ107を形成する場合には、オーバーエッチングによりボイド106の上部が露出する結果、拡散層102まで貫通エッチングしてしまい接合不良をもたらす問題も発生する。

【課題を解決するための手段】

【0008】

本発明の半導体装置の製造方法は、上記問題に鑑みて考案されたものであり、絶縁膜にコンタクトホールを形成する工程と、コンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施してコンタクトホールの内壁に傾斜を形成する工程と、コンタクトホール内にコンタクトプラグを形成する工程と、を有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、コンタクトホールの開口径を上部に向かって基板面に均一に拡大することができ、コンタクトホール内に埋め込むコンタクトプラグにボイドが形成されることを防止できる。

【図面の簡単な説明】

【0010】

【図1】ケミカルドライエッチングの温度条件に対するSiN/SiO2選択比を示すグラフである。

【図2】本発明の一実施例に係るMOSトランジスタの平面図である。

【図3】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図4】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図5】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図6】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図7】図2に示すMOSトランジスタの拡散層に接続するコンタクト形成工程を説明する工程断面図である。

【図8】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図9】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図10】図2に示すMOSトランジスタのゲート電極に接続するコンタクト形成工程を説明する工程断面図である。

【図11】本発明の一実施例に係るメモリセルアレイの平面図である。

【図12】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図13】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図14】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図15】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図16】図11のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図11のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図17】本発明の別の実施例に係るメモリセルアレイの平面図である。

【図18】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図19】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図20】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図21】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図22】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図23】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図24】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図である。

【図25】図17のメモリセルアレイにおける容量コンタクトプラグ形成工程を説明する工程断面図であり、(a)は図17のA−A’線での断面図、(b)はB−B’線での断面図を示す。

【図26】本発明の一つの課題を説明する工程断面図である。

【発明を実施するための形態】

【0011】

本発明に適用するケミカルドライエッチング(CDE)条件の説明

従来のCDEでは酸化シリコン膜の表面を高精度に一定量だけエッチング除去する技術が知られている。本発明者は、窒化シリコン膜に対してCDEを適用する検討を種々行なった結果、エッチング雰囲気の温度を70℃以上に制御することによって、窒化シリコン膜を酸化シリコン膜と同等のエッチング量でエッチングできることを見出した。

【0012】

図1は、CDEの温度条件に対するSiN/SiO2選択比を示すグラフである。同グラフに示すように室温(25℃)から45℃付近まで直線状に選択比が低下し、さらに温度を上げると緩やかに選択比が低下する。そして70℃以上では、ほぼ選択比1となり、窒化シリコン膜を酸化シリコン膜と同等のエッチング量でエッチングできる。酸化シリコン膜単独、或いは窒化シリコン膜単独の場合は選択比を考慮する必要がないため、所望のエッチング速度が得られるように温度を制御すればよい。

【0013】

CDEでは、絶縁膜中の構成原子とエッチングガス中の構成原子との反応物による堆積が起こることがある。酸化シリコンや窒化シリコンなどのシリコンを構成原子として含む絶縁膜に対して、エッチングガスとして、フッ素を含むガス(例えば、HF、NF3など)とアンモニア(NH3)とを用いると、フッ化アンモニウム(NH4F)等がエッチング雰囲気に生成し、一方、フッ素(F)と絶縁膜中のシリコン(Si)とが反応してフッ化ケイ素(SiF4)が生成する。フッ化ケイ素とフッ化アンモニウムが反応してケイフッ化アンモニウム((NH4)2SiF6)が生成する。

例えば、酸化シリコン(SiO2)の場合は、以下の反応が進行する。

SiO2 + 4F → SiF4

SiF4 + 2NH4F → (NH4)2SiF6

【0014】

ケイフッ化アンモニウムは堆積物として絶縁膜に付着し、これによりエッチングが阻害される。条件にも依存するが、10nm程度で反応が飽和して所望のエッチング量を確保することができなくなることがある。ケイフッ化アンモニウムは昇華性があり、昇華により露出した絶縁膜は再度エッチングされる。このように、ケイフッ化アンモニウムの堆積と昇華を繰り返すサイクルエッチングにより徐々にエッチングが進行する。純粋なケイフッ化アンモニウムは160℃を超える温度では分解する。昇華は分解温度よりも低い温度で起こっているが、昇華速度を速めるために好ましくは100℃以上に加熱することが好ましい。したがって、サイクルエッチングは、エッチングガスを供給して、例えば100℃未満でケイフッ化アンモニウムの堆積を行う工程と、エッチングガスの供給を停止し、100℃以上に加熱してケイフッ化アンモニウムを昇華又は分解して除去する工程を繰り返すことで実施することができる。このように、所望のエッチング量を確保することが困難な場合には、サイクルエッチングが適している。

【0015】

さらに、上記条件をコンタクトホールに適用したところ、層間絶縁膜が窒化シリコン膜、酸化シリコン膜のいずれの場合も、コンタクトホールの上方ほどエッチング量が大きくなる現象を知見した。特にケイフッ化アンモニウムの堆積と昇華を繰り返すサイクルエッチングを実施することでコンタクトホールの上部の拡幅を精度良く制御することが可能となる。

【0016】

また、本発明では、コンタクトホールに窒化シリコン膜と酸化シリコン膜とが混在して露出する場合に、いずれの膜に対しても同様のエッチング量とすることで、コンタクトホールの上部の拡幅を図る方法も提供する。

【実施例】

【0017】

以下、実施例を挙げて本発明を具体的に説明するが、本発明はこれらの実施例のみに限定されるものではない。

【0018】

実施例1

図2にMOS型トランジスタのレイアウトの一例の平面図を示す。図3〜図7は図2のA−A’の断面図を示している。

【0019】

(図3)

まず、半導体基板1上に素子分離(STI:Shallow Trench Isolation)領域2で囲まれた活性領域3を形成する。次に、活性領域3を横切り、X方向に延在するゲート電極5を形成する。ここでは、活性領域3の半導体基板1表面に厚さ5nmのゲート絶縁膜4、厚さ50nmのゲート電極5、厚さ50nmの窒化シリコン膜からなるカバー絶縁膜6を積層形成する。次に、リソグラフィとドライエッチング法により順次エッチングした後、側壁に窒化シリコン膜からなるサイドウォール(SW)絶縁膜7を形成する。ゲート電極5は多結晶シリコン上にタングステンなどの金属を積層したポリサイド構造、窒化チタンなどのバリヤ金属上にタングステンなどの低抵抗金属を積層した金属積層膜、ゲート絶縁膜4にハフニウムシリケート膜などの高誘電率膜を用いる場合にはタングステン単層構造などを用いることができる。いずれの場合もゲート電極5の最上面はタングステンなどの金属で構成される。

【0020】

続いて、ゲート電極パターンをマスクとして用い、イオン注入法により半導体基板表面に不純物導入し、ソース拡散層8およびドレイン拡散層9を形成する。

【0021】

最後にゲート電極パターンを覆うように、酸化シリコン膜からなる厚さ140nmの層間絶縁膜10を形成する。層間絶縁膜10はCVD法や回転塗布法により成膜した後、CMP法により表面平坦化することで形成できる。

【0022】

(図4)

次に、リソグラフィにより形成したマスク11を用い、ドライエッチング法によりソース拡散層8およびドレイン拡散層9に接続する直径30nmの拡散層コンタクトホール(第1のコンタクトホール)12を層間絶縁膜10に形成する。拡散層コンタクトホール12は、SW絶縁膜7には接していない。図2では、各々の拡散層上のX方向に3個並列に形成された例を示す。拡散層コンタクトホール12の内壁はこの段階では従来法と同様に垂直に形成されている。

【0023】

(図5)

続いて、マスク11を除去した後、本発明のCDE法により、拡散層コンタクトホールの開口部直径を拡大し、側壁に傾斜を形成する。

【0024】

本実施例のCDE法の条件は以下の通りである。

エッチングガス:NF3(14sccm)、NH3(50sccm)

圧力: 400Pa(3Torr)

温度: 35℃(エッチングガス供給時)/120℃(ケイフッ化アンモニウム昇華時)

RFパワー: 30W

時間: 60秒

【0025】

また、以下の条件でも同様の効果を得られる。

エッチングガス:HF(40sccm)、NH3(50sccm)

圧力: 11Pa(80mTorr)

温度: 35℃(エッチングガス供給時)/120℃(ケイフッ化アンモニウム昇華時)

RFパワー: 0W

時間: 60秒

【0026】

これにより、新たな拡散層コンタクトホール(第2のコンタクトホール)13を形成する。開口部の拡がりDは5nmに制御する。直径は30nmから40nmに拡大する。底面の拡散層はシリコンで構成されているので、CDEでは除去されない。

【0027】

高精度拡幅には、上記のようにケイフッ化アンモニウムの形成と昇華を繰り返すサイクルエッチングが有効である。

【0028】

(図6)

拡散層コンタクトホール13を埋め込むように、CVD法により全面に導体14を形成する。コンタクトホールが垂直側壁から傾斜側壁となっているのでボイドは発生しない。導体14としては、例えば、多結晶シリコン、タングステン等の金属の単層膜あるいは多結晶シリコンとタングステンなどの金属の積層膜などが例示できる。タングステン形成の場合は拡散層表面あるいは先に形成する多結晶シリコン上面に金属シリサイド(例えば、コバルトシリサイド)を形成し、さらに絶縁膜との間に窒化チタン等のバリヤ膜(例えば、Ti/TiNなど)を形成することが好ましい。

【0029】

(図7)

最後に、CMP法もしくはドライエッチング法により層間絶縁膜10上に形成されている導体14を除去し、拡散層コンタクトホール13内に拡散層コンタクトプラグ15を形成する。さらに、拡散層コンタクトプラグ15の上面と接続する配線16を形成する。

【0030】

本実施例によれば、拡散層コンタクトホール12の内壁は、酸化シリコン膜からなる層間絶縁膜10で構成されており、上記のCDE条件を用いることによりホールの上部を拡幅した傾斜を有する拡散層コンタクトホール13に加工することができる。その結果、拡散層コンタクトホール13を埋設する導体14におけるボイドの発生を防止して、抵抗増大や拡散層へのエッチングダメージを回避する拡散層コンタクトプラグ15を形成できる。

【0031】

実施例2

実施例1では、ソース及びドレイン拡散層に接続される拡散層コンタクトホールについて説明したが、図2に示すように、ゲート電極5に接続するゲートコンタクトホールも同様に形成することができる。ゲートコンタクトホールは、酸化シリコン膜からなる層間絶縁膜10と窒化シリコン膜からなるカバー絶縁膜6とを貫通して形成されているが、本発明による方法では、このように異なる絶縁膜が積層されている場合であっても適用できる。

図8〜図10は図2のB−B’の断面図を示している。

【0032】

(図8)

実施例1の図4工程において、拡散層コンタクトホール12の形成と同時又は別個に、ゲートコンタクトホール(第1のコンタクトホール)17を形成する。

【0033】

(図9)

実施例1の図5工程と同様に、本発明のCDE法により、ゲートコンタクトホール17の開口部直径を拡大し、側壁に傾斜を形成する。但し、エッチングガス供給時の雰囲気温度は80℃とした。これにより上部に向かって開口部直径が拡大したゲートコンタクトホール(第2のコンタクトホール)18が形成される。該工程は、実施例1の図5工程と同時に行うことができる。

【0034】

(図10)

その後、実施例1の図6工程、図7工程を経て、ゲートコンタクトプラグ19及び配線16を形成する。

【0035】

本実施例に示すように、コンタクトホールに異種の絶縁膜が露出している場合にも同様に開口部径の拡大を行うことができる。

【0036】

実施例3

図11は、埋込みワード線(WL1〜3)を用いたメモリセルアレイの平面図である。図11において、22はSTI領域、24は活性領域を示し、X’方向(第1の方向)に延在して形成される。活性領域24は、Y方向(第2の方向)にSTI領域23により分断され、それぞれ島状の活性領域24aとなる。各活性領域24aはさらにY方向に延在する2本の埋込ワード線で3つの拡散層に分割される。ビット線に接続される拡散層領域をビット線コンタクト領域25、容量コンタクトプラグ35が接続される拡散層領域を容量コンタクト領域26と呼ぶ。ビット線コンタクト領域25は各活性領域24aの中央部に配置され、X方向(第3の方向)に延在するビット線(BL1〜3)が接続される。容量コンタクト領域26は各活性領域24aの両端に配置され、容量コンタクトプラグ35が接続される。

【0037】

以下、断面図を参照してこのメモリセルアレイの製造方法を説明する。図12〜16は、本実施例に係るメモリセルアレイの製造工程を説明する工程断面図であり、各図(a)は、図11のA−A’線、各図(b)はB−B’線での断面に相当する。

【0038】

(図12)

まず、半導体基板21にSTI領域22,23となる溝を形成し、絶縁膜を埋め込んでSTI領域22,23を形成する。続いて、活性領域24に拡散層用の不純物イオンを注入して拡散層(図示せず)を形成する。次に、ワード線用の溝を図11のY方向に形成し、ワード線導体層を埋込み、さらに窒化シリコン膜からなるキャップ絶縁膜27を形成して表面を平坦化する。なお、ワード線と半導体基板21とは図示しないゲート絶縁膜で分離されている。また、ワード線導体層の表面は活性層の深さよりも深い位置になるように埋め込まれる。なお、STI領域23に代えて、ダミーのワード線を形成して活性領域24を各活性領域24aに分離することもできる。

【0039】

(図13)

次に、酸化シリコン膜からなる第1層間絶縁膜28を形成した後、ビット線コンタクト領域25を露出するビットコンタクトホール(図示せず)を形成し、ビット線となる導体層及び窒化シリコン膜からなるカバー絶縁膜29を成膜し、パターニングしてビット線(BL1〜3)を形成する。さらに、ビット線(BL1〜3)の側壁に窒化シリコン膜からなる第1サイドウォール(SWD1)を形成する。その後、全面に酸化シリコン膜からなる第2層間絶縁膜30を形成し、カバー絶縁膜29及び第1サイドウォール(SWD1)をストッパーとしてCMP等で平坦化する。

【0040】

(図14)

第2層間絶縁膜30上にマスク膜31を形成し、容量コンタクト領域26を露出する容量コンタクトホール(第1のコンタクトホール)32を形成する。

【0041】

(図15)

実施例1の図5工程と同様に、本発明のCDE法により、容量コンタクトホール32の開口部直径を拡大し、側壁に傾斜を形成する。但し、エッチングガス供給時の雰囲気温度は80℃とした。ここでは、酸化シリコン膜からなる第2層間絶縁膜30と窒化シリコン膜からなる第1サイドウォール(SWD1)は同程度にエッチングされ、いずれも上部に向かって直径が拡大した容量コンタクトホール(第2のコンタクトホール)33が形成される。

【0042】

(図16)

その後、容量コンタクトプラグ34を形成し、さらにキャパシタ35を形成する。このように、容量コンタクトプラグ34の上部の径が拡張されていることで、ボイドの発生を抑制すると共に、アレイパターンが微細化されてもキャパシタ35の下部電極とのコンタクト面積を確保することができる。

【0043】

実施例4

実施例3に示したメモリセルアレイにおいて、更に微細化が進むと、容量コンタクト領域に容量コンタクトホールを均一に形成することが困難となり、キャパシタ特性に影響する場合がある。本実施例では、隣接する島状活性領域24aの対向する容量コンタクト領域26を一括して開口し、コンタクトプラグとなる導体を埋め込んだ後、2つのプラグに分割するツインプラグ法により容量コンタクトプラグを形成する方法について説明する。

【0044】

図17は、図11と同様にメモリセルアレイの平面図を示し、Y方向に延在するマスク領域41と開口領域42を示す。開口領域42とビット線(BL1〜3)とで画定される領域を単位開口部44と呼び、この部分にコンタクトプラグとなる導体が埋め込まれる。

【0045】

図18〜図25は、本実施例に係る半導体装置の製造工程を説明する工程断面図であり、各図において、(a)は図17のA−A’線での断面図、(b)は図17のB−B’線での断面図を示す。

【0046】

(図18)

実施例3と同様にビット線の側壁に第1サイドウォールSWD1を形成した後、酸化シリコン膜からなる第2層間絶縁膜30を形成する。実施例3では第1サイドウォールSWD1の上面までとしていたが、本実施例では第2層間絶縁膜30の上面が第1サイドウォールSWD1の上面よりも高い位置となるように形成する。次に、マスク領域41にフォトレジスト等のマスク膜43を形成する。

【0047】

(図19)

マスク膜43をマスクに開口領域42に露出する酸化シリコン膜からなる第1及び第2層間絶縁膜28及び30をエッチングする。これにより単位開口部44が形成される。

【0048】

(図20)

窒化シリコン膜を成膜した後、エッチバックして第2サイドウォールSWD2を単位開口部44に露出する第1及び第2層間絶縁膜28及び30の側壁及び第1サイドウォールSWD1の側壁に形成する。第2サイドウォールSWD2形成後の単位開口部を単位開口部(第1のコンタクトホール)45とする。

【0049】

(図21)

次に、実施例1の図5工程と同様に、本発明のCDE法により、単位開口部45の開口部直径を拡大し、側壁に傾斜を形成する(第2のコンタクトホール)。但し、エッチングガス供給時の雰囲気温度は80℃とした。

【0050】

(図22)

続いて、容量コンタクトプラグとなる導体46を形成する。導体46は、ビット線上のカバー絶縁膜29がちょうど露出するか露出しない程度にエッチバックする。カバー絶縁膜29の表面より低く形成すると、次の工程での第3サイドウォールがビット線側壁の第2サイドウォール側壁にも形成され、その後の導体46の分離が不十分となる場合がある。

【0051】

(図23)

窒化シリコン膜を形成し、エッチバックして第3サイドウォールSWD3を形成する。さらに、第3サイドウォールSWD3をマスクに、導体46をエッチングし、単位開口部45内で2つの容量コンタクトプラグ47に分割する。

【0052】

(図24)

全面に絶縁膜を形成し、CMP等により平坦化する。これにより単位開口部45内の2つの容量コンタクトプラグ47の間に埋込絶縁膜48が埋め込まれる。

【0053】

(図25)

その後、実施例3と同様にキャパシタ35を形成する。

【0054】

本実施例に示すように、単位開口部45側壁がすべて窒化シリコン膜である場合にも同様に開口部径の拡大を行うことができる。また、本発明のCDE法を適用することで開口内側壁の傾斜角を精密に制御できるため、ツインプラグ構造では、一つの単位開口部内で分離して形成された2つのプラグの下部中心点間距離よりも上部中心点間距離が広くなり、キャパシタのレイアウトに制限されることなく、メモリセルレイアウトの自由度が向上する。

【符号の説明】

【0055】

1,21 半導体基板

2,22,23 STI領域

3,24 活性領域

4 ゲート絶縁膜

5 ゲート電極

6 カバー絶縁膜

7 サイドウォール絶縁膜

8 ソース拡散層

9 ドレイン拡散層

10 層間絶縁膜

11 マスク

12,13 拡散層コンタクトホール

14 導体

15 拡散層コンタクトプラグ

16 配線

17,18 ゲートコンタクトホール

19 ゲートコンタクトプラグ

25 ビット線コンタクト領域

26 容量コンタクト領域

27 キャップ絶縁膜

28 第1層間絶縁膜

29 カバー絶縁膜

30 第2層間絶縁膜

31 マスク膜

32,33 容量コンタクトホール

34 容量コンタクトプラグ

35 キャパシタ

41 マスク領域

42 開口領域

43 マスク膜

44,45 単位開口部

46 導体

47 容量コンタクトプラグ

【特許請求の範囲】

【請求項1】

絶縁膜に第1のコンタクトホールを形成する工程と、

該第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホールを形成する工程と、

該第2のコンタクトホール内にコンタクトプラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ケミカルドライエッチングは、絶縁膜構成原子とエッチングガス中の構成原子との反応物による堆積と、該反応物の昇華を繰り返すサイクルエッチングを含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁膜は構成原子としてシリコンを含み、前記エッチングガスとしてフッ素を含むガスとアンモニアとを含み、前記反応物としてケイフッ化アンモニウムを生成する請求項2に記載の半導体装置の製造方法。

【請求項4】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜と窒化シリコン膜の少なくとも一方を含む請求項3に記載の半導体装置の製造方法。

【請求項5】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜である請求項4に記載の半導体装置の製造方法。

【請求項6】

前記コンタクトホールの内壁を構成する絶縁膜が、窒化シリコン膜である請求項4に記載の半導体装置の製造方法。

【請求項7】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜と窒化シリコン膜の両方を含む請求項4に記載の半導体装置の製造方法。

【請求項8】

前記ケミカルドライエッチングは、70℃以上の温度で実施される請求項7に記載の半導体装置の製造方法。

【請求項9】

前記ケミカルドライエッチングは、酸化シリコン膜と窒化シリコン膜とのエッチング選択比が1である請求項8に記載の半導体装置の製造方法。

【請求項10】

前記コンタクトホールは、MOSトランジスタのソース及びドレイン拡散層に接続する拡散層コンタクトホールであり、

前記拡散層コンタクトホールが、酸化シリコン膜である層間絶縁膜を貫通して形成される請求項4に記載の半導体装置の製造方法。

【請求項11】

前記コンタクトホールは、MOSトランジスタのゲート電極に接続するゲートコンタクトホールであり、

前記ゲートコンタクトホールが、前記ゲート電極上の窒化シリコン膜であるカバー絶縁膜と該カバー絶縁膜上の酸化シリコン膜である層間絶縁膜を貫通して形成される請求項4に記載の半導体装置の製造方法。

【請求項12】

前記コンタクトホールは、MOSトランジスタのソース及びドレイン拡散層に接続する拡散層コンタクトホールと、MOSトランジスタのゲート電極に接続するゲートコンタクトホールであり、

前記拡散層コンタクトホールの内壁を構成する絶縁膜が酸化シリコン膜であり、

前記ゲートコンタクトホールの内壁を構成する絶縁膜が酸化シリコン膜と窒化シリコン膜であり、

前記ケミカルドライエッチングが前記拡散層コンタクトホールと前記ゲートコンタクトホールの両方に対して同時に実施される請求項4に記載の半導体装置の製造方法。

【請求項13】

前記半導体装置は、半導体基板上に形成された配線と、該配線側壁の窒化シリコン膜からなる第1サイドウォールと、これらを覆う酸化シリコン膜からなる層間絶縁膜を有し、

前記第1のコンタクトホールは、隣接する配線の対向する第1サイドウォールを露出して前記層間絶縁膜に形成され、

前記ケミカルドライエッチングにより前記第1サイドウォールと前記層間絶縁膜の両方に傾斜を有する第2のコンタクトホールが形成される請求項4に記載の半導体装置の製造方法。

【請求項14】

前記半導体装置は、

半導体基板に形成された素子分離領域により画定された第1の方向に延在する活性領域と、

前記第1の方向と交差する第2の方向に延在し、前記半導体基板中に埋め込まれたワード線と、

前記第1及び第2の方向と交差する第3の方向に延在して前記半導体基板上に形成され、前記活性領域の一部に接続されたビット線と、

前記ビット線の接続された活性領域に対して前記ワード線を介して隣接する活性領域に接続された容量コンタクトプラグと、

前記容量コンタクトプラグに接続されたキャパシタと

を有し、

前記半導体基板上に形成された配線が前記ビット線であり、前記第1のコンタクトホールが前記容量コンタクトプラグを接続する活性領域に形成され、前記第2のコンタクトホールに導体を埋め込むことで前記容量コンタクトプラグが形成される請求項13に記載の半導体装置の製造方法。

【請求項15】

前記半導体装置は、半導体基板上に形成された配線と、該配線側壁の窒化シリコン膜からなる第1サイドウォールと、これらを覆う酸化シリコン膜からなる層間絶縁膜を有し、

前記第1のコンタクトホールは、前記層間絶縁膜に前記配線の延在方向と交差する方向に延在する溝を形成し、該溝及び前記溝内に露出する配線の第1サイドウォール表面に窒化シリコン膜からなる第2サイドウォールを形成することで隣接する配線の対向する第2サイドウォールと前記溝の対向する第2サイドウォールにより画定され、

前記ケミカルドライエッチングにより前記第2サイドウォールに傾斜を有する第2のコンタクトホールが形成される請求項4に記載の半導体装置の製造方法。

【請求項16】

前記半導体装置は、

半導体基板に形成された素子分離領域により画定された第1の方向に延在する活性領域と、

前記第1の方向と交差する第2の方向に延在し、前記半導体基板中に埋め込まれたワード線と、

前記第1及び第2の方向と交差する第3の方向に延在して前記半導体基板上に形成され、前記活性領域の一部に接続されたビット線と、

前記ビット線の接続された活性領域に対して前記ワード線を介して隣接する活性領域に接続された容量コンタクトプラグと、

前記容量コンタクトプラグに接続されたキャパシタと

を有し、

前記活性領域は、前記ビット線の接続された活性領域を中央に共有し、隣接する2本のワード線を介して対峙する2つの活性領域を一セル単位として、前記第1の方向に電気的に分離されており、

窒化シリコンからなる第1サイドウォールで保護された前記ビット線を形成した後、酸化シリコンからなる層間絶縁膜を形成する工程と、

前記第1の方向に隣接する2つのセル単位の対向する2つの前記容量コンタクトプラグが接続される活性領域を連続して露出し、前記第2の方向に延在し、略垂直の側壁を有する溝を前記層間絶縁膜に形成する工程と、

前記溝の側壁及び該溝内に露出する前記第1サイドウォールの側壁に窒化シリコンからなる第2サイドウォールを形成する工程と、

前記第2サイドウォールを前記ケミカルドライエッチングによりエッチングして、傾斜を形成する工程と、

前記溝と前記ビット線とで区画される領域に導体膜を埋め込む工程と、

前記導体膜を前記溝内で第2の方向に2分して2つの容量コンタクトプラグを形成する工程と

を有する請求項15に記載の半導体装置の製造方法。

【請求項17】

前記層間絶縁膜はその表面が前記ビット線側壁の第1サイドウォール表面よりも高くなるように形成され、前記導体膜を前記第1サイドウォール表面以上であって、前記層間絶縁膜表面よりも低く埋め込んだ後、該導体膜上に前記溝側壁の第2サイドウォールに対して前記第2の方向に延在する第3サイドウォールを形成し、該第3サイドウォールをマスクに前記導体膜を2分する請求項16に記載の半導体装置の製造方法。

【請求項18】

前記2分された導体膜間に絶縁膜を埋め込み、前記第1サイドウォール表面が露出するまで全面を平坦化することで、前記容量コンタクトプラグを形成する請求項17に記載の半導体装置の製造方法。

【請求項1】

絶縁膜に第1のコンタクトホールを形成する工程と、

該第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホールを形成する工程と、

該第2のコンタクトホール内にコンタクトプラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ケミカルドライエッチングは、絶縁膜構成原子とエッチングガス中の構成原子との反応物による堆積と、該反応物の昇華を繰り返すサイクルエッチングを含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁膜は構成原子としてシリコンを含み、前記エッチングガスとしてフッ素を含むガスとアンモニアとを含み、前記反応物としてケイフッ化アンモニウムを生成する請求項2に記載の半導体装置の製造方法。

【請求項4】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜と窒化シリコン膜の少なくとも一方を含む請求項3に記載の半導体装置の製造方法。

【請求項5】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜である請求項4に記載の半導体装置の製造方法。

【請求項6】

前記コンタクトホールの内壁を構成する絶縁膜が、窒化シリコン膜である請求項4に記載の半導体装置の製造方法。

【請求項7】

前記コンタクトホールの内壁を構成する絶縁膜が、酸化シリコン膜と窒化シリコン膜の両方を含む請求項4に記載の半導体装置の製造方法。

【請求項8】

前記ケミカルドライエッチングは、70℃以上の温度で実施される請求項7に記載の半導体装置の製造方法。

【請求項9】

前記ケミカルドライエッチングは、酸化シリコン膜と窒化シリコン膜とのエッチング選択比が1である請求項8に記載の半導体装置の製造方法。

【請求項10】

前記コンタクトホールは、MOSトランジスタのソース及びドレイン拡散層に接続する拡散層コンタクトホールであり、

前記拡散層コンタクトホールが、酸化シリコン膜である層間絶縁膜を貫通して形成される請求項4に記載の半導体装置の製造方法。

【請求項11】

前記コンタクトホールは、MOSトランジスタのゲート電極に接続するゲートコンタクトホールであり、

前記ゲートコンタクトホールが、前記ゲート電極上の窒化シリコン膜であるカバー絶縁膜と該カバー絶縁膜上の酸化シリコン膜である層間絶縁膜を貫通して形成される請求項4に記載の半導体装置の製造方法。

【請求項12】

前記コンタクトホールは、MOSトランジスタのソース及びドレイン拡散層に接続する拡散層コンタクトホールと、MOSトランジスタのゲート電極に接続するゲートコンタクトホールであり、

前記拡散層コンタクトホールの内壁を構成する絶縁膜が酸化シリコン膜であり、

前記ゲートコンタクトホールの内壁を構成する絶縁膜が酸化シリコン膜と窒化シリコン膜であり、

前記ケミカルドライエッチングが前記拡散層コンタクトホールと前記ゲートコンタクトホールの両方に対して同時に実施される請求項4に記載の半導体装置の製造方法。

【請求項13】

前記半導体装置は、半導体基板上に形成された配線と、該配線側壁の窒化シリコン膜からなる第1サイドウォールと、これらを覆う酸化シリコン膜からなる層間絶縁膜を有し、

前記第1のコンタクトホールは、隣接する配線の対向する第1サイドウォールを露出して前記層間絶縁膜に形成され、

前記ケミカルドライエッチングにより前記第1サイドウォールと前記層間絶縁膜の両方に傾斜を有する第2のコンタクトホールが形成される請求項4に記載の半導体装置の製造方法。

【請求項14】

前記半導体装置は、

半導体基板に形成された素子分離領域により画定された第1の方向に延在する活性領域と、

前記第1の方向と交差する第2の方向に延在し、前記半導体基板中に埋め込まれたワード線と、

前記第1及び第2の方向と交差する第3の方向に延在して前記半導体基板上に形成され、前記活性領域の一部に接続されたビット線と、

前記ビット線の接続された活性領域に対して前記ワード線を介して隣接する活性領域に接続された容量コンタクトプラグと、

前記容量コンタクトプラグに接続されたキャパシタと

を有し、

前記半導体基板上に形成された配線が前記ビット線であり、前記第1のコンタクトホールが前記容量コンタクトプラグを接続する活性領域に形成され、前記第2のコンタクトホールに導体を埋め込むことで前記容量コンタクトプラグが形成される請求項13に記載の半導体装置の製造方法。

【請求項15】

前記半導体装置は、半導体基板上に形成された配線と、該配線側壁の窒化シリコン膜からなる第1サイドウォールと、これらを覆う酸化シリコン膜からなる層間絶縁膜を有し、

前記第1のコンタクトホールは、前記層間絶縁膜に前記配線の延在方向と交差する方向に延在する溝を形成し、該溝及び前記溝内に露出する配線の第1サイドウォール表面に窒化シリコン膜からなる第2サイドウォールを形成することで隣接する配線の対向する第2サイドウォールと前記溝の対向する第2サイドウォールにより画定され、

前記ケミカルドライエッチングにより前記第2サイドウォールに傾斜を有する第2のコンタクトホールが形成される請求項4に記載の半導体装置の製造方法。

【請求項16】

前記半導体装置は、

半導体基板に形成された素子分離領域により画定された第1の方向に延在する活性領域と、

前記第1の方向と交差する第2の方向に延在し、前記半導体基板中に埋め込まれたワード線と、

前記第1及び第2の方向と交差する第3の方向に延在して前記半導体基板上に形成され、前記活性領域の一部に接続されたビット線と、

前記ビット線の接続された活性領域に対して前記ワード線を介して隣接する活性領域に接続された容量コンタクトプラグと、

前記容量コンタクトプラグに接続されたキャパシタと

を有し、

前記活性領域は、前記ビット線の接続された活性領域を中央に共有し、隣接する2本のワード線を介して対峙する2つの活性領域を一セル単位として、前記第1の方向に電気的に分離されており、

窒化シリコンからなる第1サイドウォールで保護された前記ビット線を形成した後、酸化シリコンからなる層間絶縁膜を形成する工程と、

前記第1の方向に隣接する2つのセル単位の対向する2つの前記容量コンタクトプラグが接続される活性領域を連続して露出し、前記第2の方向に延在し、略垂直の側壁を有する溝を前記層間絶縁膜に形成する工程と、

前記溝の側壁及び該溝内に露出する前記第1サイドウォールの側壁に窒化シリコンからなる第2サイドウォールを形成する工程と、

前記第2サイドウォールを前記ケミカルドライエッチングによりエッチングして、傾斜を形成する工程と、

前記溝と前記ビット線とで区画される領域に導体膜を埋め込む工程と、

前記導体膜を前記溝内で第2の方向に2分して2つの容量コンタクトプラグを形成する工程と

を有する請求項15に記載の半導体装置の製造方法。

【請求項17】

前記層間絶縁膜はその表面が前記ビット線側壁の第1サイドウォール表面よりも高くなるように形成され、前記導体膜を前記第1サイドウォール表面以上であって、前記層間絶縁膜表面よりも低く埋め込んだ後、該導体膜上に前記溝側壁の第2サイドウォールに対して前記第2の方向に延在する第3サイドウォールを形成し、該第3サイドウォールをマスクに前記導体膜を2分する請求項16に記載の半導体装置の製造方法。

【請求項18】

前記2分された導体膜間に絶縁膜を埋め込み、前記第1サイドウォール表面が露出するまで全面を平坦化することで、前記容量コンタクトプラグを形成する請求項17に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2013−93512(P2013−93512A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−235966(P2011−235966)

【出願日】平成23年10月27日(2011.10.27)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]