半導体装置の製造方法

【課題】トレンチの深さを安定化する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に前記半導体基板に比べエッチング選択比の高い第一膜を作成する工程と、前記第一膜上に前記第一膜に比べエッチング選択比の高い第二膜を作成する工程と、一部の領域の前記第二膜および第一膜をエッチングし前記領域の半導体基板表面を露出させる工程と、前記露出した半導体基板表面をエッチングしトレンチを作成する工程を有する安定したトレンチ深さを提供する半導体装置の製造方法とした。

【解決手段】半導体基板上に前記半導体基板に比べエッチング選択比の高い第一膜を作成する工程と、前記第一膜上に前記第一膜に比べエッチング選択比の高い第二膜を作成する工程と、一部の領域の前記第二膜および第一膜をエッチングし前記領域の半導体基板表面を露出させる工程と、前記露出した半導体基板表面をエッチングしトレンチを作成する工程を有する安定したトレンチ深さを提供する半導体装置の製造方法とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トレンチを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

時代とともに半導体装置は縮小を続け進化してきた。その縮小の一般的な方法は、微細化技術を駆使した平面上のパターン縮小化であったが、近年その方法に限界が生じ始めており、半導体基板の深さ方向を有効に活用するといった3次元構造により半導体装置を縮小するといった新たな試みがなされるようになってきた。そこで必須となる技術がトレンチエッチングである。しかしながら現在のトレンチエッチング技術におけるトレンチ深さ方向のバラツキは小さいとは言いがたく、深さ方向のサイズ変動によって大きく特性が変化する半導体装置においてこのバラツキは大きな問題となる。このバラツキを改善するために良く用いられる手法がストッパー膜を用いる製造方法である。この発明の概念図を図3に示す。

【0003】

半導体基板上1上にエッチングストッパー膜4、被トレンチエッチング膜5、レジスト6を順に堆積し、レジスト6をパターニングする(図3(a))。ここでエッチングストッパー膜4は被トレンチエッチング膜5に対しエッチングの選択比の大きい物質を用いる。次にレジスト6をマスクとして被トレンチエッチング膜5をエッチングするが、ストッパー膜4でエッチングがストップするので被トレンチエッチング膜5に形成されたトレンチの深さが一定になる。(例えば、特許文献1参照)

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−185532号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来技術の方法では被トレンチエッチング膜5の直下に被トレンチエッチング膜とは別物質のストッパー膜4を作成する必要があり、工程が複雑かつコストが上昇する。また、被トレンチエッチング膜5はストッパー膜4上に堆積させるため、物質的に制限を受けたり、半導体基板1と電気的な導通が取れなかったりと不自由も生じる。特に、シリコン基板上1にそのままトレンチを作成したいときにはこの方法は用いることが出来ない。

【0006】

以上の不具合を鑑み、安定した深さを有するトレンチを作成できる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

(1)半導体基板上に第一膜を作成する工程と、

前記第一膜上に第二膜を作成する工程と、

トレンチを形成する領域を含む前記第二膜の一部の領域をエッチングする第一のエッチング工程と、

前記第一のエッチングにて露出した前記第一膜の一部をエッチングする第二のエッチング工程と、

前記第二膜と露出した前記半導体基板表面を同時にエッチングし、前記第二膜がほとんど全てエッチングされ、モニタしている前記第一膜を構成する元素の検出量が増大するまで前記半導体基板表面にトレンチを作成する第三のエッチング工程と、

を有し、

前記第三のエッチング工程は、前記第一膜に対してはエッチング速度が遅く、前記第二膜および前記半導体基板に対してはエッチング速度が速いというエッチング雰囲気で行われ、前記トレンチのエッチング深さは前記第二膜の膜厚で決定されることを特徴とする半導体装置の製造方法とした。

(2)前記半導体基板をシリコン基板、前記第一膜をシリコン酸化膜、前記第二膜をポリシリコン膜またはシリコン窒化膜とした半導体装置の製造方法とした。

(3)前記半導体基板をシリコン基板、前記第一膜を金属膜、前記第二膜をシリコン酸化堆積膜とした半導体装置の製造方法とした。

(4)前記第三のエッチング工程に続き、前記金属膜を除去した後に、前記シリコン基板をアンモニア過酸化水素水混合液で洗浄することを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0008】

上述の手段を用いることにより、半導体基板にトレンチを作成する際に深さのバラツキを低減させることが出来る。

【図面の簡単な説明】

【0009】

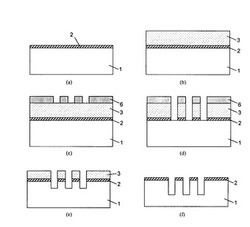

【図1】本発明の第一実施例を示す図。

【図2】本発明の第二実施例を示す図。

【図3】従来技術の実施例を示す図。

【発明を実施するための形態】

【0010】

本発明の代表的な実施例を第一実施例として図1に示す。まず図1(a)に示すように半導体基板1上にトレンチエッチング時にマスクとして用いるための膜として第一膜2を堆積させる。ここで第一膜2は半導体基板1をトレンチエッチングする際にマスクとして活用するためエッチング選択比の高いものを選ぶ。例えば半導体基板1をシリコン基板としたとき、第一膜2はシリコン酸化膜を利用する。

【0011】

次に図1(b)に示すように第一膜2上にトレンチ深さ制御用として第二膜3を堆積させる。ここで第二膜3はトレンチエッチング時に容易に削れるような半導体基板1に対し選択比の低い物質を用いる。例えば、半導体基板1をシリコン基板としたとき、第二膜3はポリシリコンを利用する。トレンチエッチングの際に半導体基板1がエッチングされると同時に第二膜3もエッチングされれば良いのであるから、上述のポリシリコンに限らず、シリコン窒化膜なども利用できる。

【0012】

次に図1(c)に示すように第二膜3上にレジストを塗布しパターニングをし、そのレジストをマスクに第二膜3および第一膜2を図1(d)に示すようにエッチングする。このとき、第一膜2は第二膜3に対しエッチング選択比が高いため第一膜2が露出したところでエッチングされなくなる。エッチング装置により終点検出したならば、その後、第一膜2がエッチングされるようなガスを用いてエッチングを行うが、半導体基板1が第一膜2に対しエッチング選択比が高いため半導体基板1が露出したところでエッチングされなくなる。

【0013】

次いで、レジスト6を除去した後にシリコン基板をエッチングしトレンチ構造を作成する。このトレンチエッチングをする際に図1(e)に示すように半導体基板1だけでなく第二膜3も同時にエッチングされ、最終的に図2(f)に示すように第二膜3が全てエッチングされ、それまで第二膜3に覆われていた第一膜2が表面に露出する。エッチングチャンバ内の特定波長をモニタしておき、第一膜2の元素が検出された時点でエッチングを終了すれば、第二膜3の膜厚に応じたトレンチエッチング深さでエッチングを終了することが可能となり、たとえトレンチエッチングのエッチレートが不安定になったとしても第二膜3の膜厚が常に一定であればトレンチ深さを均一に保つことができる。また、第二膜3の膜厚はトレンチエッチング時の半導体基板1との選択比および狙いのトレンチエッチング深さに応じて任意に決定すればよい。

【0014】

上記に示したように半導体基板1、第一膜2、第二膜3をそれぞれシリコン基板、シリコン酸化膜、ポリシリコンとしたとき、シリコン酸化膜に比べシリコン基板とポリシリコンは大体同じエッチング選択比となるため、作成したいトレンチ深さと同じくらいのポリシリコンが必要となる。そのため、高アスペクト比のトレンチを作成する際にはポリシリコンのトレンチ越しにシリコン基板をエッチングするため、装置の性能を超えてしまい、装置的に作成が困難な場合が生じる。このような場合には次の第二実施例において示される製造方法を用いることで、高アスペクト比のトレンチ作成が容易になる。

【0015】

図2は第二実施例を示す。図2の(a)、(b)は図1の(a)、(b)と全く同じであるが、図2(c)でトレンチを作成する領域の第二膜3をエッチングにより部分的に除去する。その後、図2(d)に示すようにトレンチエッチング用マスクとして第一膜2をエッチングにより任意にパターニングする。最後にパターニングした第一膜2をマスクとしてトレンチエッチングを行うが、このとき図1に示した方法に比べ第二膜の開口部が大きく半導体基板に高アスペクトのトレンチ形状を作成し易い。この方法でもトレンチエッチングをする際に図2(e)に示すように半導体基板1だけでなく第二膜3も同時にエッチングされ、最終的に図2(f)に示すように第二膜3が全てエッチングされ、それまで第二膜3に覆われていた第一膜2が全て表面に露出する。トレンチエッチングの際にエッチングチャンバ内の元素をモニタしておけば、図1(f)の時点で第一膜の元素の検出量が増大するため、その時にエッチングを終了すれば、第二膜の膜厚に応じたトレンチエッチング深さでエッチングを終了することが可能となり、たとえトレンチエッチングのエッチレートが不安定になったとしても第二膜3の膜厚が常に一定であればトレンチ深さを均一に保つことができる。

【0016】

上記実施例においては、トレンチエッチング時の半導体基板のエッチング速度と第二膜のエッチング速度をほぼ同等とする膜構成にて説明したが、次の式1に示される不等式を満たすように設定することで、高アスペクト比のトレンチ構造を作成することも可能となる。

(式1) エッチング速度(半導体基板1)>エッチング速度(第二膜3)>エッチング速度(第一膜2)

たとえば、半導体基板1、第一膜2、第二膜3をそれぞれシリコン基板、金属膜、シリコン酸化堆積膜とした場合などである。こうすることにより、図1(e)の際に第二膜3のシリコン酸化堆積膜が半導体基板1のシリコン基板よりエッチングしづらいため、第二膜3にポリシリコンを利用したときに比べ膜厚を薄くすることができ、半導体基板1上に高アスペクト比のトレンチ構造を作成し易くなる。

【0017】

ただし、第二膜3のシリコン酸化堆積膜をパターニングする際にそれより選択比の高い物質である金属膜を第一膜2に適用しなければならない。そのためトレンチ内の金属汚染が懸念されるが、この汚染は図1(f)後に第一膜2を除去した後に、シリコン表面全体をSC1(アンモニア、過酸化水素水混合液)などで洗浄することで金属汚染部を取り去ることができる。

【0018】

以上、本発明の実施形態を説明したが、本発明は上記の実施形態に限定されるものではなく、本発明はその要旨を逸脱しない範囲で変形して実施できる。

【符号の説明】

【0019】

1 半導体基板

2 第一膜(トレンチエッチングハードマスク用膜)

3 第二膜(トレンチ深さ制御用膜)

4 ストッパー膜

5 被トレンチエッチング膜

6 レジスト

【技術分野】

【0001】

本発明は、トレンチを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

時代とともに半導体装置は縮小を続け進化してきた。その縮小の一般的な方法は、微細化技術を駆使した平面上のパターン縮小化であったが、近年その方法に限界が生じ始めており、半導体基板の深さ方向を有効に活用するといった3次元構造により半導体装置を縮小するといった新たな試みがなされるようになってきた。そこで必須となる技術がトレンチエッチングである。しかしながら現在のトレンチエッチング技術におけるトレンチ深さ方向のバラツキは小さいとは言いがたく、深さ方向のサイズ変動によって大きく特性が変化する半導体装置においてこのバラツキは大きな問題となる。このバラツキを改善するために良く用いられる手法がストッパー膜を用いる製造方法である。この発明の概念図を図3に示す。

【0003】

半導体基板上1上にエッチングストッパー膜4、被トレンチエッチング膜5、レジスト6を順に堆積し、レジスト6をパターニングする(図3(a))。ここでエッチングストッパー膜4は被トレンチエッチング膜5に対しエッチングの選択比の大きい物質を用いる。次にレジスト6をマスクとして被トレンチエッチング膜5をエッチングするが、ストッパー膜4でエッチングがストップするので被トレンチエッチング膜5に形成されたトレンチの深さが一定になる。(例えば、特許文献1参照)

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−185532号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来技術の方法では被トレンチエッチング膜5の直下に被トレンチエッチング膜とは別物質のストッパー膜4を作成する必要があり、工程が複雑かつコストが上昇する。また、被トレンチエッチング膜5はストッパー膜4上に堆積させるため、物質的に制限を受けたり、半導体基板1と電気的な導通が取れなかったりと不自由も生じる。特に、シリコン基板上1にそのままトレンチを作成したいときにはこの方法は用いることが出来ない。

【0006】

以上の不具合を鑑み、安定した深さを有するトレンチを作成できる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

(1)半導体基板上に第一膜を作成する工程と、

前記第一膜上に第二膜を作成する工程と、

トレンチを形成する領域を含む前記第二膜の一部の領域をエッチングする第一のエッチング工程と、

前記第一のエッチングにて露出した前記第一膜の一部をエッチングする第二のエッチング工程と、

前記第二膜と露出した前記半導体基板表面を同時にエッチングし、前記第二膜がほとんど全てエッチングされ、モニタしている前記第一膜を構成する元素の検出量が増大するまで前記半導体基板表面にトレンチを作成する第三のエッチング工程と、

を有し、

前記第三のエッチング工程は、前記第一膜に対してはエッチング速度が遅く、前記第二膜および前記半導体基板に対してはエッチング速度が速いというエッチング雰囲気で行われ、前記トレンチのエッチング深さは前記第二膜の膜厚で決定されることを特徴とする半導体装置の製造方法とした。

(2)前記半導体基板をシリコン基板、前記第一膜をシリコン酸化膜、前記第二膜をポリシリコン膜またはシリコン窒化膜とした半導体装置の製造方法とした。

(3)前記半導体基板をシリコン基板、前記第一膜を金属膜、前記第二膜をシリコン酸化堆積膜とした半導体装置の製造方法とした。

(4)前記第三のエッチング工程に続き、前記金属膜を除去した後に、前記シリコン基板をアンモニア過酸化水素水混合液で洗浄することを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0008】

上述の手段を用いることにより、半導体基板にトレンチを作成する際に深さのバラツキを低減させることが出来る。

【図面の簡単な説明】

【0009】

【図1】本発明の第一実施例を示す図。

【図2】本発明の第二実施例を示す図。

【図3】従来技術の実施例を示す図。

【発明を実施するための形態】

【0010】

本発明の代表的な実施例を第一実施例として図1に示す。まず図1(a)に示すように半導体基板1上にトレンチエッチング時にマスクとして用いるための膜として第一膜2を堆積させる。ここで第一膜2は半導体基板1をトレンチエッチングする際にマスクとして活用するためエッチング選択比の高いものを選ぶ。例えば半導体基板1をシリコン基板としたとき、第一膜2はシリコン酸化膜を利用する。

【0011】

次に図1(b)に示すように第一膜2上にトレンチ深さ制御用として第二膜3を堆積させる。ここで第二膜3はトレンチエッチング時に容易に削れるような半導体基板1に対し選択比の低い物質を用いる。例えば、半導体基板1をシリコン基板としたとき、第二膜3はポリシリコンを利用する。トレンチエッチングの際に半導体基板1がエッチングされると同時に第二膜3もエッチングされれば良いのであるから、上述のポリシリコンに限らず、シリコン窒化膜なども利用できる。

【0012】

次に図1(c)に示すように第二膜3上にレジストを塗布しパターニングをし、そのレジストをマスクに第二膜3および第一膜2を図1(d)に示すようにエッチングする。このとき、第一膜2は第二膜3に対しエッチング選択比が高いため第一膜2が露出したところでエッチングされなくなる。エッチング装置により終点検出したならば、その後、第一膜2がエッチングされるようなガスを用いてエッチングを行うが、半導体基板1が第一膜2に対しエッチング選択比が高いため半導体基板1が露出したところでエッチングされなくなる。

【0013】

次いで、レジスト6を除去した後にシリコン基板をエッチングしトレンチ構造を作成する。このトレンチエッチングをする際に図1(e)に示すように半導体基板1だけでなく第二膜3も同時にエッチングされ、最終的に図2(f)に示すように第二膜3が全てエッチングされ、それまで第二膜3に覆われていた第一膜2が表面に露出する。エッチングチャンバ内の特定波長をモニタしておき、第一膜2の元素が検出された時点でエッチングを終了すれば、第二膜3の膜厚に応じたトレンチエッチング深さでエッチングを終了することが可能となり、たとえトレンチエッチングのエッチレートが不安定になったとしても第二膜3の膜厚が常に一定であればトレンチ深さを均一に保つことができる。また、第二膜3の膜厚はトレンチエッチング時の半導体基板1との選択比および狙いのトレンチエッチング深さに応じて任意に決定すればよい。

【0014】

上記に示したように半導体基板1、第一膜2、第二膜3をそれぞれシリコン基板、シリコン酸化膜、ポリシリコンとしたとき、シリコン酸化膜に比べシリコン基板とポリシリコンは大体同じエッチング選択比となるため、作成したいトレンチ深さと同じくらいのポリシリコンが必要となる。そのため、高アスペクト比のトレンチを作成する際にはポリシリコンのトレンチ越しにシリコン基板をエッチングするため、装置の性能を超えてしまい、装置的に作成が困難な場合が生じる。このような場合には次の第二実施例において示される製造方法を用いることで、高アスペクト比のトレンチ作成が容易になる。

【0015】

図2は第二実施例を示す。図2の(a)、(b)は図1の(a)、(b)と全く同じであるが、図2(c)でトレンチを作成する領域の第二膜3をエッチングにより部分的に除去する。その後、図2(d)に示すようにトレンチエッチング用マスクとして第一膜2をエッチングにより任意にパターニングする。最後にパターニングした第一膜2をマスクとしてトレンチエッチングを行うが、このとき図1に示した方法に比べ第二膜の開口部が大きく半導体基板に高アスペクトのトレンチ形状を作成し易い。この方法でもトレンチエッチングをする際に図2(e)に示すように半導体基板1だけでなく第二膜3も同時にエッチングされ、最終的に図2(f)に示すように第二膜3が全てエッチングされ、それまで第二膜3に覆われていた第一膜2が全て表面に露出する。トレンチエッチングの際にエッチングチャンバ内の元素をモニタしておけば、図1(f)の時点で第一膜の元素の検出量が増大するため、その時にエッチングを終了すれば、第二膜の膜厚に応じたトレンチエッチング深さでエッチングを終了することが可能となり、たとえトレンチエッチングのエッチレートが不安定になったとしても第二膜3の膜厚が常に一定であればトレンチ深さを均一に保つことができる。

【0016】

上記実施例においては、トレンチエッチング時の半導体基板のエッチング速度と第二膜のエッチング速度をほぼ同等とする膜構成にて説明したが、次の式1に示される不等式を満たすように設定することで、高アスペクト比のトレンチ構造を作成することも可能となる。

(式1) エッチング速度(半導体基板1)>エッチング速度(第二膜3)>エッチング速度(第一膜2)

たとえば、半導体基板1、第一膜2、第二膜3をそれぞれシリコン基板、金属膜、シリコン酸化堆積膜とした場合などである。こうすることにより、図1(e)の際に第二膜3のシリコン酸化堆積膜が半導体基板1のシリコン基板よりエッチングしづらいため、第二膜3にポリシリコンを利用したときに比べ膜厚を薄くすることができ、半導体基板1上に高アスペクト比のトレンチ構造を作成し易くなる。

【0017】

ただし、第二膜3のシリコン酸化堆積膜をパターニングする際にそれより選択比の高い物質である金属膜を第一膜2に適用しなければならない。そのためトレンチ内の金属汚染が懸念されるが、この汚染は図1(f)後に第一膜2を除去した後に、シリコン表面全体をSC1(アンモニア、過酸化水素水混合液)などで洗浄することで金属汚染部を取り去ることができる。

【0018】

以上、本発明の実施形態を説明したが、本発明は上記の実施形態に限定されるものではなく、本発明はその要旨を逸脱しない範囲で変形して実施できる。

【符号の説明】

【0019】

1 半導体基板

2 第一膜(トレンチエッチングハードマスク用膜)

3 第二膜(トレンチ深さ制御用膜)

4 ストッパー膜

5 被トレンチエッチング膜

6 レジスト

【特許請求の範囲】

【請求項1】

半導体基板上に第一膜を作成する工程と、

前記第一膜上に第二膜を作成する工程と、

トレンチを形成する領域を含む前記第二膜の一部の領域をエッチングする第一のエッチング工程と、

前記第一のエッチングにて露出した前記第一膜の一部をエッチングする第二のエッチング工程と、

前記第二膜と露出した前記半導体基板表面を同時にエッチングし、前記第二膜がほとんど全てエッチングされ、モニタしている前記第一膜を構成する元素の検出量が増大するまで前記半導体基板表面にトレンチを作成する第三のエッチング工程と、

を有し、

前記第三のエッチング工程は、前記第一膜に対してはエッチング速度が遅く、前記第二膜および前記半導体基板に対してはエッチング速度が速いというエッチング雰囲気で行われ、前記トレンチのエッチング深さは前記第二膜の膜厚で決定されることを特徴とする半導体装置の製造方法。

【請求項2】

前記半導体基板をシリコン基板、前記第一膜をシリコン酸化膜、前記第二膜をポリシリコン膜またはシリコン窒化膜とした請求項1記載の半導体装置の製造方法。

【請求項3】

前記半導体基板をシリコン基板、前記第一膜を金属膜、前記第二膜をシリコン酸化堆積膜とした請求項1記載の半導体装置の製造方法。

【請求項4】

前記第三のエッチング工程に続き、前記金属膜を除去した後に、前記シリコン基板をアンモニア過酸化水素水混合液で洗浄することを特徴とする請求項3記載の半導体装置の製造方法。

【請求項1】

半導体基板上に第一膜を作成する工程と、

前記第一膜上に第二膜を作成する工程と、

トレンチを形成する領域を含む前記第二膜の一部の領域をエッチングする第一のエッチング工程と、

前記第一のエッチングにて露出した前記第一膜の一部をエッチングする第二のエッチング工程と、

前記第二膜と露出した前記半導体基板表面を同時にエッチングし、前記第二膜がほとんど全てエッチングされ、モニタしている前記第一膜を構成する元素の検出量が増大するまで前記半導体基板表面にトレンチを作成する第三のエッチング工程と、

を有し、

前記第三のエッチング工程は、前記第一膜に対してはエッチング速度が遅く、前記第二膜および前記半導体基板に対してはエッチング速度が速いというエッチング雰囲気で行われ、前記トレンチのエッチング深さは前記第二膜の膜厚で決定されることを特徴とする半導体装置の製造方法。

【請求項2】

前記半導体基板をシリコン基板、前記第一膜をシリコン酸化膜、前記第二膜をポリシリコン膜またはシリコン窒化膜とした請求項1記載の半導体装置の製造方法。

【請求項3】

前記半導体基板をシリコン基板、前記第一膜を金属膜、前記第二膜をシリコン酸化堆積膜とした請求項1記載の半導体装置の製造方法。

【請求項4】

前記第三のエッチング工程に続き、前記金属膜を除去した後に、前記シリコン基板をアンモニア過酸化水素水混合液で洗浄することを特徴とする請求項3記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−93633(P2013−93633A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2013−31904(P2013−31904)

【出願日】平成25年2月21日(2013.2.21)

【分割の表示】特願2007−320972(P2007−320972)の分割

【原出願日】平成19年12月12日(2007.12.12)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成25年2月21日(2013.2.21)

【分割の表示】特願2007−320972(P2007−320972)の分割

【原出願日】平成19年12月12日(2007.12.12)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]