半導体装置の製造方法

【課題】GaN系半導体を用い耐圧の異なるトランジスタを作り分ける。

【解決手段】基板1上方に第1、第2GaN系半導体層3,4、電極層5、第1絶縁膜6を積層し、電極層5及び第1絶縁膜6をパターニングして、第1ゲート電極5と第1絶縁膜6が積層された第1構造と、第2ゲート電極5と第1絶縁膜6が積層された第2構造を形成し、第1、第2構造を覆って第2絶縁膜7を形成し、第1ゲート電極5とその両側領域を露出する第1開口8SD、第2ゲート電極5を挟んでそれぞれ一方側、他方側に配置された第2、第3開口8S,8Dを有する第1マスクを用いて、第2絶縁膜7を異方性エッチングし、第1開口内8SDにおいて、第1構造の側面上にサイドウォール絶縁膜7SWを残しつつ、第1ゲート電極を挟んでコンタクトホール9S,9Dを形成し、第2、第3開口内に、それぞれコンタクトホール9S,9Dを形成し、各コンタクトホールに電極を形成する。

【解決手段】基板1上方に第1、第2GaN系半導体層3,4、電極層5、第1絶縁膜6を積層し、電極層5及び第1絶縁膜6をパターニングして、第1ゲート電極5と第1絶縁膜6が積層された第1構造と、第2ゲート電極5と第1絶縁膜6が積層された第2構造を形成し、第1、第2構造を覆って第2絶縁膜7を形成し、第1ゲート電極5とその両側領域を露出する第1開口8SD、第2ゲート電極5を挟んでそれぞれ一方側、他方側に配置された第2、第3開口8S,8Dを有する第1マスクを用いて、第2絶縁膜7を異方性エッチングし、第1開口内8SDにおいて、第1構造の側面上にサイドウォール絶縁膜7SWを残しつつ、第1ゲート電極を挟んでコンタクトホール9S,9Dを形成し、第2、第3開口内に、それぞれコンタクトホール9S,9Dを形成し、各コンタクトホールに電極を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

高電子移動度トランジスタ(HEMT)等、2次元電子ガス層をチャネルとするトランジスタが開発されている(例えば、特許文献1、2参照)。例えばGaN系半導体を用いて、HEMTを形成することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−10663号公報

【特許文献2】特開2010−109322号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、GaN系半導体を用い耐圧の異なるトランジスタを、同一基板上に作り分けることができる、半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、基板上方に、第1GaN系半導体層を形成する工程と、前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、前記ゲート電極層上に、第1絶縁膜を形成する工程と、前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程とを有し、前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法が提供される。

【発明の効果】

【0006】

GaN系半導体を用い耐圧の異なるトランジスタを、同一基板上に作り分けることができる。

【図面の簡単な説明】

【0007】

【図1−1】図1A〜図1Cは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

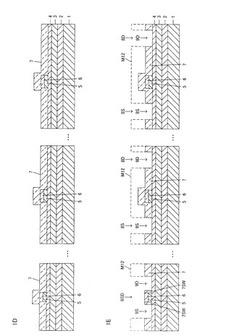

【図1−2】図1D及び図1Eは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−3】図1F及び図1Gは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−4】図1H及び図1Iは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−5】図1J及び図1Kは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図2−1】図2A及び図2Bは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図2−2】図2C及び図2Dは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−1】図3A及び図3Bは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−2】図3C及び図3Dは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−3】図3E及び図3Fは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−1】図4A及び図4Bは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−2】図4C及び図4Dは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−3】図4E及び図4Fは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−4】図4G及び図4Hは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図5−1】図5A及び図5Bは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図5−2】図5C及び図5Dは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−1】図6A及び図6Bは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−2】図6C及び図6Dは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−3】図6E及び図6Fは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−1】図7A及び図7Bは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−2】図7C及び図7Dは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−3】図7E及び図7Fは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図8】図8は、第8実施例による半導体装置の概略断面図である。

【図9】図9は、第1応用例による絶縁型DCDCコンバータの概略的な回路図である。

【図10】図10は、第2応用例、第3応用例による絶縁型DCDCコンバータの概略的な回路図である。

【図11】図11は、第2応用例による電圧測定回路の主要部分を概略的に示す回路図である。

【図12】図12は、第3応用例による電圧測定回路の主要部分を概略的に示す回路図である。

【発明を実施するための形態】

【0008】

本発明の実施例による半導体装置の製造方法について説明する。実施例では、GaN系半導体を用いた高電子移動度トランジスタ(HEMT)を形成し、相対的に低耐圧、中耐圧、及び高耐圧のトランジスタを同時形成する。なお、GaN系半導体は、少なくともGaとNとを含む。

【0009】

まず、第1実施例による半導体装置の製造方法について説明する。図1A〜図1Kは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。各図の左側部分、中央部分、及び右側部分は、それぞれ、低耐圧トランジスタ、中耐圧トランジスタ、及び高耐圧トランジスタの部分を示す。

【0010】

図1Aを参照する。基板(例えばSi基板)1上に、下方から順に、GaNバッファ層2、チャネル層となるGaN層3、及び、電子供給層となるAlGaN層4を、例えば有機金属化学気相堆積(MOCVD)で形成する。GaNバッファ層2、GaN層3、及びAlGaN層4の積層厚さは、例えば3μm〜5μmである。

【0011】

GaN層3と、GaN層3よりもバンドギャップの広いAlGaN層4との界面に、2次元電子ガス層が形成される。なお、2次元電子ガス層を形成させるための、GaN系半導体層の積層構造は、この例に限定されない。少なくとも、相互にバンドギャップの異なる第1GaN系半導体層と第2GaN系半導体層とを積層することにより、2次元電子ガス層を形成することができる。

【0012】

図1Bを参照する。AlGaN層4上に、ゲート電極層5を形成する。ゲート電極層5は、例えば、AlやTaN等の金属層であり、スパッタリング(蒸着)により厚さ300nm程度形成される。なお、ゲート電極層5は、金属膜と絶縁膜、ポリシリコン膜と絶縁膜、及び左記の三層とGaN層との積層構造等とすることもできる。絶縁膜は、例えばSiO膜やSiN膜である。

【0013】

ゲート電極層5上に、絶縁膜6を形成する。絶縁膜6は、例えば窒化シリコン(SiN)膜や酸化シリコン(SiO)膜であり、例えば、化学気相堆積(CVD)で厚さ200nm程度形成される。

【0014】

図1Cを参照する。絶縁膜6上に、ゲート電極形状のレジストパターンM11を形成する。レジストパターンM11をマスクとし、絶縁膜6及びゲート電極層5をパターニングして、低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれのゲート電極5を形成する。低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれについて、ゲート電極5上に絶縁膜6が積層された構造が形成される。その後、レジストパターンM11を除去する。

【0015】

図1Dを参照する。ゲート電極5上に絶縁膜6が積層された構造を覆って、AlGaN層4上に、絶縁膜7を形成する。絶縁膜7は、例えばSiN膜やSiO膜であり、例えば、CVDで厚さ200nm〜500nm程度形成される。なお、SiO膜材料として、テトラエトキシシラン(TEOS)を用いることもできる。

【0016】

図1Eを参照する。絶縁膜7上に、レジストパターンM12を形成する。レジストパターンM12は、中耐圧トランジスタ部分及び高耐圧トランジスタ部分のそれぞれで、ソース電極形成用のコンタクトホール形状の開口8Sと、ドレイン電極形成用のコンタクトホール形状の開口8Dとを有する。中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、ゲート電極5の近傍はレジストパターンM12に覆われている。

【0017】

レジストパターンM12の、低耐圧トランジスタ部分の開口8SDは、ゲート電極5の一方側に配置されるソース電極用のコンタクトホール形成領域から、ゲート電極5の他方側に配置されるドレイン電極用のコンタクトホール形成領域までを露出する。つまり、低耐圧トランジスタ部分では、レジストパターンM12の開口8SD内に、ゲート電極5の形成領域も露出する。

【0018】

レジストパターンM12をマスクとして、異方性ドライエッチングにより絶縁膜7をエッチングする。中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、それぞれ、開口8S内にソース電極形成用のコンタクトホール9Sが形成され、開口8D内にドレイン電極形成用のコンタクトホール9Dが形成される。

【0019】

低耐圧トランジスタ部分では、絶縁膜6の上面上に形成された絶縁膜7が除去され、エッチングの異方性により、ゲート電極5と絶縁膜6との積層構造側面上に絶縁膜7が残って、サイドウォール絶縁膜7SWが形成される。サイドウォール絶縁膜7SWの厚さは、例えば200nm程度である。

【0020】

開口8SD内で、サイドウォール絶縁膜7SWの外側部分の絶縁膜7が除去されて、ゲート電極5を挟んで一方側にソース電極形成用のコンタクトホール9Sが形成され、ゲート電極5を挟んで他方側にドレイン電極形成用のコンタクトホール9Dが形成される。その後、レジストパターンM12を除去する。

【0021】

なお、コンタクトホール9S及びコンタクトホール9Dの形成された絶縁膜7をマスクとして、さらに、AlGaN層4を除去することもできる。

【0022】

このように、低耐圧トランジスタにおいては、コンタクトホール9Sのゲート電極側端部の位置、及び、コンタクトホール9Dのゲート電極側端部の位置が、サイドウォール絶縁膜7SWにより決定される。つまり、低耐圧トランジスタは、ソース電極及びドレイン電極のゲート電極側端部(ゲート端)の位置が、セルフアラインで決定される。一方、中耐圧トランジスタ及び高耐圧トランジスタにおいては、ソース電極及びドレイン電極のゲート端の位置が、マスクM12により決定される。

【0023】

各電極に印加される電圧の例は、例えば以下のようなものである。低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタのいずれも、ソース電極には例えば0Vが印加され、ゲート電極には例えばオフ時に0V、オン時に1V〜10Vが印加される。ドレイン電極には、例えば、低耐圧トランジスタで1V〜10V、中耐圧トランジスタで10V〜100V、高耐圧トランジスタで100V〜1000Vが印加される。

【0024】

低耐圧トランジスタは、ゲート・ソース間、及び、ゲート・ドレイン間の電圧差が最大でも例えば10V程度である。このため、ゲート電極からソース電極までの距離、及び、ゲート電極からドレイン電極までの距離を、比較的短くすることができ、ソース電極及びドレイン電極のゲート端の位置を、セルフアラインで決定することができる。

【0025】

耐圧を向上させるため、ゲート電極からドレイン電極のゲート端までの距離は、低耐圧トランジスタよりも中耐圧トランジスタが長く、中耐圧トランジスタよりも高耐圧トランジスタが長い。ゲート電極からドレイン電極のゲート端までの距離は、例えば、低耐圧トランジスタで200nm程度、中耐圧トランジスタで2μm程度、高耐圧トランジスタで20μm程度である。

【0026】

図1Fを参照する。コンタクトホール9Sの内面及びコンタクトホール9Dの内面を覆って、全面上に、導電膜10を形成する。導電膜10は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。導電膜10の厚さは、例えば300nm程度である。

【0027】

図1Gを参照する。導電膜10上に、レジストパターンM13を形成する。レジストパターンM13は、低耐圧トランジスタ部分、中耐圧トランジスタ部分それぞれについて、ソース電極形状及びドレイン電極形状で形成されており、また、高耐圧トランジスタ部分では、ソース電極形状、ドレイン電極形状、及びフィールドプレート形状で形成されている。

【0028】

レジストパターンM13をマスクとし、導電膜10をパターニングして、低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれのソース電極10S及びドレイン電極10Dと、高耐圧トランジスタのフィールドプレート10FPを形成する。その後、レジストパターンM13を除去する。ゲート電極5とソース電極10Sとの間、及び、ゲート電極5とドレイン電極10Dとの間に、2次元電子ガス層2DEGを示す。

【0029】

なお、低耐圧トランジスタのソース電極10Sあるいはドレイン電極10Dが、ゲート電極5の端部上に重なってパターニングされたとしても、ゲート電極5上に残された絶縁膜6により、ソース電極10Sあるいはドレイン電極10Dとゲート電極5との短絡は抑制される。

【0030】

高耐圧トランジスタのフィールドプレート10FPは、ゲート電極5とドレイン電極10Dとの間で、絶縁膜7上に配置される。フィールドプレート10FPへの印加電圧は、例えば0Vである。フィールドプレート10FPにより、ゲート電極5からドレイン電極10Dのゲート端までの間における電界集中を緩和して、耐圧を高めることができる。

【0031】

図1Hを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜11を形成する。層間絶縁膜11の上面を、化学機械研磨(CMP)で平坦化する。

【0032】

図1Iを参照する。層間絶縁膜11上に、レジストパターンM14を形成する。レジストパターンM14は、各ソース電極10Sを露出するコンタクトホール形状の開口、及び、各ドレイン電極10Dを露出するコンタクトホール形状の開口を有する。

【0033】

レジストパターンM14をマスクとし、層間絶縁膜11をエッチングして、ソース電極10Sを露出するコンタクトホール12S、及び、ドレイン電極10Dを露出するコンタクトホール12Dを形成する。その後、レジストパターンM14を除去する。

【0034】

図1Jを参照する。コンタクトホール12S及びコンタクトホール12Dを埋め込んで、全面上に、導電膜13を形成する。導電膜13は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0035】

図1Kを参照する。導電膜13上に、各ソース電極10Sに接続する配線形状、及び、各ドレイン電極10Dに接続する配線形状のレジストパターンM15を形成する。レジストパターンM15をマスクとし、導電膜13をパターニングして、配線層13S及び配線層13Dを形成する。その後、レジストパターンM15を除去する。

【0036】

第1実施例の配線層13S及び配線層13Dは、層間絶縁膜11に埋め込まれた導電プラグ部分と、層間絶縁膜11上に配置された配線部分とが、一体的に形成される。

【0037】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第1実施例による半導体装置が形成される。

【0038】

次に、第2実施例による半導体装置の製造方法について説明する。図2A〜図2Dは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0039】

まず、第1実施例で図1Iを参照して説明した工程までと同様にして、層間絶縁膜11にコンタクトホール12S及びコンタクトホール12Dを形成する。

【0040】

図2Aを参照する。コンタクトホール12S及びコンタクトホール12Dを埋め込んで、全面上に、導電膜21を形成する。導電膜21は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0041】

図2Bを参照する。導電膜21の上部をCMPで除去して、層間絶縁膜11を露出させる。これにより、コンタクトホール12S及びコンタクトホール12Dに、それぞれ導電プラグ21S及び導電プラグ21Dが形成される。

【0042】

図2Cを参照する。導電プラグ21S及び導電プラグ21Dを覆って、全面上に、導電膜22を形成する。導電膜22は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0043】

図2Dを参照する。導電膜22上に、各導電プラグ21Sに接続する配線形状、及び、各導電プラグ21Dに接続する配線形状のレジストパターンM21を形成する。レジストパターンM21をマスクとし、導電膜22をパターニングして、配線22S及び配線22Dを形成する。その後、レジストパターンM21を除去する。

【0044】

第2実施例のように、ソース電極10Sに接続する配線層や、ドレイン電極10Dに接続する配線層について、層間絶縁膜11に埋め込まれた導電プラグ部分と、層間絶縁膜11上に配置された配線部分とを、別々の工程で形成することもできる。

【0045】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第2実施例による半導体装置が形成される。

【0046】

次に、第3実施例による半導体装置の製造方法について説明する。図3A〜図3Fは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0047】

まず、第1実施例で図1Eを参照して説明した工程までと同様にして、絶縁膜7にコンタクトホール9S及びコンタクトホール9Dを形成する。

【0048】

図3Aを参照する。コンタクトホール9S及びコンタクトホール9Dを埋め込んで、全面上に、導電膜31を形成する。導電膜31は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0049】

図3Bを参照する。導電膜31の上部をCMPで除去する。低耐圧トランジスタでは、ゲート電極5上方で絶縁膜6が露出し、コンタクトホール9S及びコンタクトホール9Dの外側で絶縁膜7が露出し、コンタクトホール9S内にソース電極31Sが形成され、コンタクトホール9D内にドレイン電極31Dが形成される。

【0050】

中耐圧トランジスタ及び高耐圧トランジスタでは、ゲート電極5の上方で導電膜31とともに絶縁膜7が除去されて絶縁膜6が露出し、コンタクトホール9S及びコンタクトホール9Dの外側で絶縁膜7が露出し、コンタクトホール9S内にソース電極31Sが形成され、コンタクトホール9D内にドレイン電極31Dが形成される。

【0051】

第1実施例のような導電膜のパターニングでソース電極及びドレイン電極を形成する方法に限らず、第3実施例のように、導電膜の不要部を研磨除去してソース電極及びドレイン電極を形成することもできる。

【0052】

図3Cを参照する。全面上に、導電膜32を形成する。導電膜32は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0053】

図3Dを参照する。導電膜32上に、レジストパターンM31を形成する。レジストパターンM31は、低耐圧トランジスタ部分、中耐圧トランジスタ部分、高耐圧トランジスタ部分それぞれについて、ソース電極31Sに接続する配線形状、及び、ドレイン電極31Dに接続する配線形状を有するとともに、高耐圧トランジスタ部分では、フィールドプレート形状を有する。

【0054】

レジストパターンM31をマスクとし、導電膜32をパターニングして、配線32S、配線32D、及びフィールドプレート32FPを形成する。その後、レジストパターンM31を除去する。

【0055】

図3Eを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜33を形成する。層間絶縁膜33の上面を、CMPで平坦化する。

【0056】

図3Fを参照する。層間絶縁膜33上に、レジストパターンM32を形成する。レジストパターンM32は、配線32Sを露出するコンタクトホール形状の開口、及び、配線32Dを露出するコンタクトホール形状の開口を有する。

【0057】

レジストパターンM32をマスクとし、層間絶縁膜33をエッチングして、配線32Sを露出するコンタクトホール34S、及び、配線32Dを露出するコンタクトホール34Dを形成する。その後、レジストパターンM32を除去する。

【0058】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第3実施例による半導体装置が形成される。

【0059】

次に、第4実施例による半導体装置の製造方法について説明する。図4A〜図4Hは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0060】

まず、第1実施例で図1Cを参照して説明した工程までと同様にして、ゲート電極5上に絶縁膜6が残った構造を形成する。

【0061】

図4Aを参照する。第1実施例で図1Dを参照して説明した絶縁膜7の形成工程と同様に、ゲート電極5上に絶縁膜6が積層された構造を覆って、AlGaN層4上に、絶縁膜41を形成する。

【0062】

第1実施例(〜第3実施例)では、低耐圧トランジスタのソース電極及びドレイン電極のゲート端の位置を、セルフアラインで決定した。中耐圧トランジスタ及び高耐圧トランジスタにおいても、ゲート・ソース間の電位差は、最大で例えば10V程度に留まる。そこで、第4実施例では、以下に説明するように、中耐圧トランジスタ及び高耐圧トランジスタのソース電極のゲート端の位置も、セルフアラインで決定する。

【0063】

図4Bを参照する。絶縁膜41上にレジストパターンM41を形成する。レジストパターンM41をマスクとし、絶縁膜41を異方性ドライエッチングして、ソース電極形成用のコンタクトホール42Sと、ドレイン電極形成用のコンタクトホール42Dとを形成する。

【0064】

第4実施例によるレジストパターンM41の開口形状は、以下のようなものである。低耐圧トランジスタ部分の開口43SDは、第1実施例によるレジストパターンM12の開口8SDと同様である。低耐圧トランジスタ部分について、第1実施例と同様に、ゲート電極5のソース電極側及びドレイン電極側の側面にサイドウォール絶縁膜41SWが形成されるとともに、コンタクトホール42S及びコンタクトホール42Dが形成される。

【0065】

中耐圧トランジスタ部分及び高耐圧トランジスタ部分において、ソース電極形成用の開口43Sは、ゲート電極5のソース電極側端部上まで重なり、ゲート電極形成領域を露出する。ドレイン電極形成用の開口43Dは、第1実施例によるレジストパターンM12の開口8Dと同様である。ゲート電極5のドレイン電極側端部は、レジストパターンM41に覆われている。

【0066】

従って、第4実施例では、中耐圧トランジスタ部分及び高耐圧トランジスタ部分においても、ゲート電極5のソース電極側側面にはサイドウォール絶縁膜41SWが形成されて、コンタクトホール42Sが形成される。つまり、中耐圧トランジスタ及び高耐圧トランジスタにおいても、ソース電極のゲート端の位置がセルフアラインで決定される。

【0067】

なお、コンタクトホール42S及びコンタクトホール42Dが形成された絶縁膜41をマスクとして、さらに、AlGaN層4を除去することもできる。

【0068】

図4Cを参照する。第1実施例で図1Fを参照して説明した導電膜10の形成工程と同様にして、コンタクトホール42S及びコンタクトホール42Dを覆って、全面上に導電膜44を形成する。

【0069】

図4Dを参照する。第1実施例で図1Gを参照して説明した工程と同様にして、ソース電極形状、ドレイン電極形状、及びフィールドプレート形状で形成されたレジストパターンM42を形成する。レジストパターンM42をマスクとし、導電膜44をパターニングして、ソース電極44S、ドレイン電極44D、及びフィールドプレート44FPを形成する。その後、レジストパターンM42を除去する。

【0070】

図4Eを参照する。第1実施例で図1Hを参照して説明した層間絶縁膜11の形成工程と同様にして、全面上に層間絶縁膜45を形成する。

【0071】

図4Fを参照する。第1実施例で図1Iを参照して説明した工程と同様にして、層間絶縁膜45上に、ソース電極44Sを露出するコンタクトホール形状の開口、及び、ドレイン電極44Dを露出するコンタクトホール形状の開口を有するレジストパターンM43を形成する。

【0072】

レジストパターンM43をマスクとし、層間絶縁膜45をエッチングして、ソース電極44Sを露出するコンタクトホール46S、及び、ドレイン電極44Dを露出するコンタクトホール46Dを形成する。その後、レジストパターンM43を除去する。

【0073】

図4Gを参照する。第1実施例で図1Jを参照して説明した導電膜13の形成工程と同様にして、コンタクトホール46S及びコンタクトホール46Dを埋め込んで、全面上に導電膜47を形成する。

【0074】

図4Hを参照する。第1実施例で図1Kを参照して説明した工程と同様にして、導電膜47上に、ソース電極44Sに接続する配線形状、及び、ドレイン電極44Dに接続する配線形状レジストパターンM44を形成する。

【0075】

レジストパターンM44をマスクとし、導電膜47をパターニングして、配線層47S及び配線層47Dを形成する。その後、レジストパターンM44を除去する。

【0076】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第4実施例による半導体装置が形成される。

【0077】

次に、第5実施例による半導体装置の製造方法について説明する。第5実施例は、中耐圧トランジスタ及び高耐圧トランジスタにおいてもソース電極ゲート端位置をセルフアラインで決定するようにした第4実施例に、第2実施例の配線形成方法を適用した例である。図5A〜図5Dは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

まず、第4実施例で図4Fを参照して説明した工程までと同様にして、層間絶縁膜45にコンタクトホール46S及びコンタクトホール46Dを形成する。

【0078】

図5Aを参照する。第2実施例で図2Aを参照して説明した導電膜21の形成工程と同様にして、コンタクトホール46S及びコンタクトホール46Dを埋め込んで、全面上に導電膜51を形成する。

【0079】

図5Bを参照する。第2実施例で図2Bを参照して説明した工程と同様にして、導電膜51の上部をCMPで除去し、コンタクトホール46S及びコンタクトホール46Dに、それぞれ導電プラグ51S及び導電プラグ51Dを形成する。

【0080】

図5Cを参照する。第2実施例で図2Cを参照して説明した導電膜22の形成工程と同様にして、全面上に導電膜52を形成する。

【0081】

図5Dを参照する。第2実施例で図2Dを参照して説明した工程と同様にして、導電膜52上に、導電プラグ51Sに接続する配線形状、及び、導電プラグ51Dに接続する配線形状のレジストパターンM51を形成する。レジストパターンM51をマスクとし、導電膜52をパターニングして、配線52S及び配線52Dを形成する。その後、レジストパターンM51を除去する。さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第5実施例による半導体装置が形成される。

【0082】

次に、第6実施例による半導体装置の製造方法について説明する。第6実施例は、中耐圧トランジスタ及び高耐圧トランジスタにおいてもソース電極ゲート端位置をセルフアラインで決定するようにした第4実施例に、第3実施例のソース電極・ドレイン電極形成方法を適用した例である。図6A〜図6Fは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0083】

まず、第4実施例で図4Bを参照して説明した工程までと同様にして、絶縁膜41にコンタクトホール42S及びコンタクトホール42Dを形成する。

【0084】

図6Aを参照する。第3実施例で図3Aを参照して説明した導電膜31の形成工程と同様にして、コンタクトホール42S及びコンタクトホール42Dを埋め込んで、全面上に導電膜61を形成する。

【0085】

図6Bを参照する。第3実施例で図3Bを参照して説明した工程と同様にして、導電膜61の上部をCMPで除去し、コンタクトホール42S及びコンタクトホール42Dに、それぞれソース電極61S及びソース電極61Dを形成する。

【0086】

図6Cを参照する。第3実施例で図3Cを参照して説明した導電膜32の形成工程と同様にして、全面上に導電膜62を形成する。

【0087】

図6Dを参照する。第3実施例で図3Dを参照して説明した工程と同様にして、導電膜62上に、ソース電極61Sに接続する配線形状、ドレイン電極61Dに接続する配線形状、及び、フィールドプレート形状のレジストパターンM61を形成する。レジストパターンM61をマスクとし、導電膜62をパターニングして、配線62S、配線62D、及びフィールドプレート62FPを形成する。その後、レジストパターンM61を除去する。

【0088】

図6Eを参照する。第3実施例で図3Eを参照して説明した層間絶縁膜33の形成工程と同様にして、全面上に層間絶縁膜63を形成する。

【0089】

図6Fを参照する。第3実施例で図3Fを参照して説明した工程と同様にして、層間絶縁膜63上に、配線62Sを露出するコンタクトホール形状の開口、及び、配線62Dを露出するコンタクトホール形状の開口を有するレジストパターンM62を形成する。

【0090】

レジストパターンM62をマスクとし、層間絶縁膜63をエッチングして、配線62Sを露出するコンタクトホール64S、及び、配線62Dを露出するコンタクトホール64Dを形成する。その後、レジストパターンM62を除去する。

【0091】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第6実施例による半導体装置が形成される。

【0092】

次に、第7実施例による半導体装置の製造方法について説明する。図7A〜図7Fは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0093】

まず、第1実施例で図1Dを参照して説明した工程までと同様にして、ゲート電極5上に絶縁膜6が積層された構造を覆って全面上に絶縁膜7を形成する。

【0094】

図7Aを参照する。全面の絶縁膜7を、異方性ドライエッチングする。低耐圧トランジスタ部分、中耐圧トランジスタ部分、及び高耐圧トランジスタ部分において、ゲート電極5と絶縁膜6の積層構造の側面に、サイドウォール絶縁膜7SWが形成される。

【0095】

図7Bを参照する。全面上に、例えば、SiOをCVDで堆積して、絶縁膜71を形成する。絶縁膜71は、絶縁膜6(例えばSiN膜)やサイドウォール絶縁膜7(例えばSiN膜)に対して選択的エッチングできる材料とすることが好ましい。そして、絶縁膜71の上面を、CMPで平坦化する。

【0096】

図7Cを参照する。絶縁膜71上に、レジストパターンM71を形成する。レジストパターンM71をマスクとし、絶縁膜71を異方性ドライエッチングして、ソース電極形成用のコンタクトホール72Sと、ドレイン電極形成用のコンタクトホール72Dとを形成する。例えばSiOによる絶縁膜71が、例えばSiNによる絶縁膜6及びサイドウォール絶縁膜7SWに対して選択的にエッチングされるようなエッチング条件とすることが好ましい。

【0097】

レジストパターンM71の開口パターンは、第1実施例で図1Eを参照して説明した工程で用いたレジストパターンM12と同様である。つまり、低耐圧トランジスタ部分では、ゲート電極配置領域とその両側領域を露出する開口パターンでエッチングが行われる。サイドウォール絶縁膜7SWの外側で絶縁膜71がエッチングされ、ゲート電極5及びサイドウォール絶縁膜7SWを挟んで一方側と他方側に、それぞれコンタクトホール72Sとコンタクトホール72Dとが形成される。

【0098】

また、中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、ソース電極形成領域及びドレイン電極形成領域に配置された開口パターンでエッチングが行われ、コンタクトホール72Sとコンタクトホール72Dとが形成される。

【0099】

さらに、レジストパターンM71及び絶縁膜71をマスクとして、コンタクトホール72Sとコンタクトホール72Dの底に露出したAlGaN層4をエッチングする。その後、レジストパターンM71を除去する。このように、第7実施例では、AlGaN層4までを除去し、底にGaN層3が露出したコンタクトホール72S及びコンタクトホール72Dを形成する。

【0100】

図7Dを参照する。コンタクトホール72S及びコンタクトホール72Dを埋め込んで、全面上に、導電膜73を形成する。導電膜73は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0101】

導電膜73の上部をCMPで除去して、絶縁膜71及び絶縁膜6を露出させる。これにより、コンタクトホール72S及びコンタクトホール72Dに、それぞれソース電極73S及びソース電極73Dが形成される。

【0102】

図7Eを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜74を形成する。

【0103】

層間絶縁膜74上に、レジストパターンM72を形成する。レジストパターンM72は、ソース電極73Sを露出するコンタクトホール形状の開口、ソース電極73Dを露出するコンタクトホール形状の開口、及び、高耐圧トランジスタのフィールドプレート形状の開口を有する。

【0104】

レジストパターンM72をマスクとし、層間絶縁膜74をエッチングして、ソース電極73Sを露出するコンタクトホール75S、ドレイン電極73Dを露出するコンタクトホール75D、及び、底に絶縁膜71が露出し、フィールドプレートが埋め込まれる凹部75FPを形成する。その後、レジストパターンM72を除去する。

【0105】

図7Fを参照する。コンタクトホール75S、コンタクトホール75D、及び凹部75FPを埋め込んで、全面上に、導電膜76を形成する。導電膜76は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0106】

導電膜76上に、ソース電極73Sに接続する配線形状、ドレイン電極73Dに接続する配線形状、及び、フィールドプレート形状のレジストパターンM73を形成する。レジストパターンM73をマスクとし、導電膜76をパターニングして、配線層76S、配線層76D、及びフィールドプレート76FPを形成する。その後、レジストパターンM73を除去する。

【0107】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第7実施例による半導体装置が形成される。

なお、第7実施例の変形例として、第4実施例等と同様に、中耐圧トランジスタ及び高耐圧トランジスタのソース電極のゲート端の位置を、セルフアラインで決定させるようにすることもできる。

【0108】

次に、図8を参照して、第8実施例による半導体装置について説明する。図8は、第8実施例によるトランジスタの概略断面図である。第8実施例のトランジスタは、ゲート電極5とドレイン電極10Dとの間のフィールドプレート10FPに加え、ゲート電極5とソース電極10Sとの間にもフィールドプレート10FPSを形成した構造である。第8実施例のトランジスタは、第1実施例の高耐圧トランジスタの製造工程を適宜変更して形成することができる。なお、ドレイン電極側フィールドプレート10FPとソース電極側フィールドプレート10FPSとを電気的に接続することもできる。

【0109】

以上、第1実施例〜第8実施例に沿って説明したように、GaN系半導体を用いたHEMTについて、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板上に同時形成することができる。

【0110】

次に、応用例による絶縁型直流-直流(DCDC)コンバータについて説明する。絶縁型DCDCコンバータは、電源装置の一部であり、力率改善回路で生成された例えば380Vの電源電圧を、例えば48V程度に降圧する回路である。

【0111】

図9は、第1応用例による絶縁型DCDCコンバータの概略的な回路図である。絶縁型DCDCコンバータは、入力電圧(例えば380V)が入力される入力回路101Aと、出力電圧(例えば48V)が出力される出力回路101Bとが、電気的に相互に絶縁されており、入力回路101Aの接地基準電圧VSS1と、出力回路101Bの接地基準電圧VSS2とが独立している。

【0112】

入力回路101Aは、駆動回路102と、ゲートドライバー103と、制御回路104とを含んで形成される。駆動回路102、ゲートドライバー103、及び制御回路104は、同一の半導体チップ105上に形成されている。

【0113】

駆動回路102に、入力電圧VINが入力される。駆動回路102は、トランジスタQH1〜QH4を含んで形成される。トランジスタQH1とトランジスタQH2の直列接続と、トランジスタQH3とトランジスタQH4の直列接続とが、入力電圧VINと接地基準電圧VSS1との間に並列に接続されている。トランジスタQH1とトランジスタQH3が入力電圧VIN側に配置され、トランジスタQH2とトランジスタQH4が接地基準電圧VSS1側に配置されている。

【0114】

ゲートドライバー103から供給される制御信号G1〜G4が、それぞれ、トランジスタQH1〜QH4のゲート電極に入力され、各トランジスタQH1〜QH4のオンオフを制御する。

【0115】

トランジスタQH2のドレイン電極とトランジスタQH1のソース電極との接続点であるノードN1と、トランジスタQH4のドレイン電極とトランジスタQH3のソース電極との接続点であるノードN2との間に、コイルL1が接続されている。

【0116】

制御信号G1〜G4は、トランジスタQH1とトランジスタQH4とがオンとなり、トランジスタQH2とトランジスタQH3とがオフとなる第1の期間と、トランジスタQH1とトランジスタQH4とがオフとなり、トランジスタQH2とトランジスタQH3とがオンとなる第2の期間とを、周期的に切り替える。切り替えの周波数は、例えば100kHz程度である。

【0117】

第1の期間では、電流が、トランジスタQH1、ノードN1、コイルL1、ノードN2、及びトランジスタQH4を経由する向きで流れる。一方、第2の期間では、電流が、トランジスタQH3、ノードN2、コイルL1、ノードN1、及びトランジスタQH2を経由する向きで流れる。つまり、第1の期間では、ノードN1からノードN2へ流れる電流方向となり、第2の期間では、反転して、ノードN2からノードN1へ流れる電流方向となる。従って、第1の期間と第2の期間とを周期的に切り替えることにより、コイルL1に交流電流が流れる。

【0118】

出力回路101Bは、直列接続されたコイルL2及びL3を有する。コイルL2及びL3が、入力回路101AのコイルL1と結合する。コイルL2とコイルL3との接続点であるノードN4に、接地基準電圧VSS2が接続されている。ノードN4と反対側のコイルL2の端部N3と、ノードN4と反対側のコイルL3の端部N5とが、それぞれ、整流用のダイオードD1、D2を介して、出力点Voutに接続されている。出力点Voutと接地基準電圧VSS2との間に、キャパシタC3が接続され、その先の負荷RLに電力が供給される。

【0119】

出力点Voutから出力されている電圧値のデータが、フォトカプラーPCを介して、制御回路104の入力端子VSENSEに入力される。駆動回路102に流れる入力電流が、カレントコイルCCにより測定され、入力電流値が、制御回路104の入力端子CSENSEに入力される。

【0120】

制御回路104は、入力電流値と出力電圧値とに基づき、所望の出力電圧が得られるように、制御信号PWMを生成する。制御回路104から供給された制御信号PWMに基づき、ゲートドライバー103が、駆動回路102の有する各トランジスタQH1〜QH4の制御信号G1〜G4を生成する。

【0121】

駆動回路102に使用されるトランジスタQH1等は、高耐圧であることが望ましい。一方、制御回路104や、ゲートドライバー103に使用されるトランジスタは、駆動回路102に比べて低耐圧でよい。

【0122】

上記実施例で説明した方法を用いれば、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板に形成することができ、低耐圧、中耐圧、及び高耐圧のトランジスタを適宜用いて、同一の半導体チップ上に、駆動回路102と、ゲートドライバー103と、制御回路104とを形成することができる。

【0123】

駆動回路102と、ゲートドライバー103と、制御回路104とを別々の半導体チップ上に形成した絶縁型DCDCコンバータを、比較例とする。応用例の絶縁型DCDCコンバータは、駆動回路102、ゲートドライバー103、及び制御回路104が同一半導体チップ上に形成されていることにより、比較例に比べて、例えば高速動作させることができる。

【0124】

図10は、第2応用例による絶縁型DCDCコンバータの概略的な回路図である。第1応用例との違いは、駆動回路102への入力電流の測定にカレントコイルCCを用いていないことである。

【0125】

第2応用例では、駆動回路102のノードN1及びノードN2での電圧を測定することにより、駆動回路102に流れる電流を測定する。各トランジスタの抵抗は予め測定しておくことができるので、電圧測定により電流値を得ることができる。ノードN1の電圧が、制御回路104の入力端子CSENSE1に入力され、ノードN2の電圧が、制御回路104の入力端子CSENSE2に入力される。

【0126】

図11は、第2応用例による電圧測定回路104Cの主要部分を概略的に示す回路図である。電圧測定回路104Cは、制御回路104に含まれる。代表として、ノードN1に接続された入力端子CSENSE1側部分を示すが、ノードN2に接続された入力端子CSENSE2側部分も同様な構造である。

【0127】

一対のセンストランジスタQL11及びQL12を含む差動アンプが形成されている。センストランジスタQL12のゲート電極に接地基準電圧VSS1が入力され、センストランジスタQL11のゲート電極に、トランジスタQH11を介しノードN1の電圧が入力されて、ノードN1の電圧が測定される。

【0128】

センストランジスタQL11及びQL12は、低耐圧トランジスタで形成されている。トランジスタQH11は、高耐圧トランジスタで形成されている。駆動回路102のトランジスタQH1がオンでトランジスタQH2がオフのとき、ノードN1の電圧は、例えば380V近くまで高くなる。このような高い電圧がセンストランジスタQL11のゲート電極に印加されれば、トランジスタQL11は破壊されてしまう。そこで、第2応用例の電圧測定回路104Cでは、トランジスタQL11とノードN1との間に、高耐圧のトランジスタQH11を挿入している。

【0129】

トランジスタQH11のゲート(ノードN12)の電圧VN12は、トランジスタQH11の閾値Vth+数ボルトとする。例えば、トランジスタQH11の閾値を1Vとして、トランジスタQH11のゲート電圧VN12を3Vとすると、トランジスタQH11のソース(ノードN11)の電圧、つまり、センストランジスタQL11のゲートに印加される電圧VN11は、2Vとなる。ゲート電圧VN11が数ボルトに抑えられることにより、トランジスタQL11の破壊が抑制される。

【0130】

なお、駆動回路102のトランジスタQH2がオンでトランジスタQH1がオフのときは、ノードN1の電圧が、例えば1V程度まで低くなる。トランジスタQH2がオンでトランジスタQH1がオフのときにも、トランジスタQH11がオンとなって電圧測定回路104Cが機能するように、トランジスタQH11のゲート電圧VN12が定められる。

【0131】

次に、図10を再度参照して、第3応用例による絶縁型DCDCコンバータについて説明する。第3応用例では、第2応用例と同様に、カレントコイルCCを用いずに、駆動回路102への入力電流を測定するが、測定回路部分の構造が異なる。また、第3応用例では、図10に破線で示すように、制御回路104に入力電圧VINが供給される。

【0132】

図12は、第3応用例による電圧測定回路104Cの主要部分を概略的に示す回路図である。電圧測定回路104Cは、制御回路104に含まれる。代表として、ノードN1に接続された入力端子CSENSE1側部分を示すが、ノードN2に接続された入力端子CSENSE2側部分も同様な構造である。

【0133】

一対のセンストランジスタQM11及びQM12を含む差動アンプが形成されている。電源電圧として、センストランジスタQM11及びQM12のドレイン側に入力電圧VINが印加されている。センストランジスタQM12のゲート電極に入力電圧VINが入力され、センストランジスタQM11のゲート電極にノードN1の電圧が入力されて、ノードN1の電圧が測定される。

【0134】

駆動回路102のトランジスタQH1がオフでトランジスタQH2がオンのとき、ノードN1の電圧は、例えば0V近くまで低くなり、センストランジスタQM11のゲート・ドレイン間及びゲート・ソース間の電圧差が、例えば380V近くに高くなってしまう。トランジスタQH1がオフ、トランジスタQH2がオンで、ノードN1が低い電位(例えば0V)まで下がった時、トランジスタQM12に(QFP13、QM12、QFP14の経路で)電流が流れ、ノードN12が高い電位となる。

【0135】

第3応用例の電圧測定回路104Cでは、センストランジスタQM11のドレイン側にフィールドプレートを形成するとともに、ソース側にもフィールドプレートを形成して、ゲート・ドレイン間及びゲート・ソース間の耐圧を向上させている(第8実施例参照)。図12では、フィールドプレート形成部をトランジスタとして示し、ドレイン側フィールドプレート形成部をQFP11、ソース側フィールドプレート形成部をQFP12と示している。

【0136】

センストランジスタQM12についても、センストランジスタQM11側と対称となるように、ドレイン側フィールドプレートQFP13及びソース側フィールドプレートQFP14を形成している。

【0137】

以上説明したように、GaN系半導体を用いたHEMTについて、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板上に同時形成することができる。これにより、例えば、絶縁型DCDCコンバータの入力回路における駆動回路、ゲートドライバー、及び制御回路を同一の半導体チップ上に形成することができ、例えば動作の高速化を図ることができる。

【0138】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0139】

以上説明した第1実施例〜第8実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

(付記2)

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記第1マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第2絶縁膜の異方性エッチングは、前記第2構造の前記第2ソース電極側側面上にサイドウォール絶縁膜を残しつつ、前記第2ソース電極形成用コンタクトホールを形成する付記1に記載の半導体装置の製造方法。

(付記3)

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程は、

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び、前記第2ドレイン電極形成用コンタクトホールの上方に第1導電膜を形成する工程と、

前記第1ソース電極の形成領域、前記第1ドレイン電極の形成領域、前記第2ソース電極の形成領域、及び、前記第2ドレイン電極の形成領域を覆う第2マスクを用い、前記第1導電膜をパターニングして、前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程と

を含む付記1または2に記載の半導体装置の製造方法。

(付記4)

前記第1導電膜をパターニングする工程において、前記第2マスクは、前記第2ゲート電極と前記第2ドレイン電極との間に配置されるフィールドプレートの形成領域を覆い、前記第1導電膜のパターニングにより、フィールドプレートが形成される付記3に記載の半導体装置の製造方法。

(付記5)

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程は、

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び、前記第2ドレイン電極形成用コンタクトホールの上方に第2導電膜を形成する工程と、

研磨により、前記第2導電膜の一部と、前記第2構造上方に残った前記第2絶縁膜とを除去して、前記第1ソース電極形成用コンタクトホール内、前記第1ドレイン電極形成用コンタクトホール内、前記第2ソース電極形成用コンタクトホール内、及び、前記第2ドレイン電極形成用コンタクトホール内に、それぞれ、前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程と

を含む付記1または2に記載の半導体装置の製造方法。

(付記6)

さらに、

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を覆って、前記第2絶縁膜上方に、第3導電膜を形成する工程と、

前記第1ソース電極に接続する配線の形成領域、前記第1ドレイン電極に接続する配線の形成領域、前記第2ソース電極に接続する配線の形成領域、及び前記第2ドレイン電極に接続する配線の形成領域を覆うとともに、前記第2ゲート電極と前記第2ドレイン電極との間に配置されるフィールドプレートの形成領域を覆う第3マスクを用い、前記第3導電膜をパターニングして、前記第1ソース電極に接続する配線、前記第1ドレイン電極に接続する配線、前記第2ソース電極に接続する配線、前記第2ドレイン電極に接続する配線、及びフィールドプレートを形成する工程と

を有する付記5に記載の半導体装置の製造方法。

(付記7)

さらに、前記第2絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する付記1または2に記載の半導体装置の製造方法。

(付記8)

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第2絶縁膜を異方性エッチングして、前記第1構造の側面上及び前記第2構造の側面上にサイドウォール絶縁膜を形成する工程と、

前記第1構造、前記第1構造の側面上の前記サイドウォール絶縁膜、前記第2構造、及び、前記第2構造の側面上の前記サイドウォール絶縁膜を覆って、前記第2GaN系半導体層上方に、第3絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有するマスクを用いて、前記第3絶縁膜をエッチングすることにより、前記第1開口内において、前記第1ゲート電極及び前記サイドウォール絶縁膜を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

(付記9)

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第3絶縁膜のエッチングにより、前記第2開口内において、前記第2構造側面上の前記サイドウォール絶縁膜が露出して、第2ソース電極形成用コンタクトホールが形成される付記8に記載の半導体装置の製造方法。

(付記10)

さらに、前記第3絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する付記8または9に記載の半導体装置の製造方法。

【符号の説明】

【0140】

1 Si基板

2 GaNバッファ層

3 GaN層

4 AlGaN層

5 ゲート電極層、ゲート電極

6、7 絶縁膜

7SW サイドウォール絶縁膜

8SD、8S、8D マスクの開口

9S、9D コンタクトホール

10 導電膜

10S ソース電極

10D ドレイン電極

10FP フィールドプレート

11 層間絶縁膜

12S、12D コンタクトホール

13 導電膜

13S、13D 配線層

21、22 導電膜

21S、21D 導電プラグ

22S、22D 配線

31 導電膜

31S ソース電極

31D ドレイン電極

32S、32D 配線

32FP フィールドプレート

33 層間絶縁膜

34S、34D コンタクトホール

41 絶縁膜

42S、42D コンタクトホール

43SD、43S、43D マスクの開口

44 導電膜

44S ソース電極

44D ドレイン電極

44FP フィールドプレート

45 層間絶縁膜

46S、46D コンタクトホール

47 導電膜

47S、47D 配線層

51、52 導電膜

51S、51D 導電プラグ

52S、52D 配線

61 導電膜

61S ソース電極

61D ドレイン電極

62S、62D 配線

62FP フィールドプレート

63 層間絶縁膜

64S、64D コンタクトホール

71 絶縁膜

72S、72D コンタクトホール

73 導電膜

73S ソース電極

73D ドレイン電極

74 層間絶縁膜

75S、75D コンタクトホール

75FP 凹部

76S、76D 配線層

76FP フィールドプレート

10FPS フィールドプレート

M11〜M15、M21、M31、M32、M41〜M44、M51、M61、M62、M71〜M73 レジストパターン

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

高電子移動度トランジスタ(HEMT)等、2次元電子ガス層をチャネルとするトランジスタが開発されている(例えば、特許文献1、2参照)。例えばGaN系半導体を用いて、HEMTを形成することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−10663号公報

【特許文献2】特開2010−109322号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、GaN系半導体を用い耐圧の異なるトランジスタを、同一基板上に作り分けることができる、半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、基板上方に、第1GaN系半導体層を形成する工程と、前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、前記ゲート電極層上に、第1絶縁膜を形成する工程と、前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程とを有し、前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法が提供される。

【発明の効果】

【0006】

GaN系半導体を用い耐圧の異なるトランジスタを、同一基板上に作り分けることができる。

【図面の簡単な説明】

【0007】

【図1−1】図1A〜図1Cは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−2】図1D及び図1Eは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−3】図1F及び図1Gは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−4】図1H及び図1Iは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図1−5】図1J及び図1Kは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図2−1】図2A及び図2Bは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図2−2】図2C及び図2Dは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−1】図3A及び図3Bは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−2】図3C及び図3Dは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図3−3】図3E及び図3Fは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−1】図4A及び図4Bは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−2】図4C及び図4Dは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−3】図4E及び図4Fは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図4−4】図4G及び図4Hは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図5−1】図5A及び図5Bは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図5−2】図5C及び図5Dは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−1】図6A及び図6Bは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−2】図6C及び図6Dは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図6−3】図6E及び図6Fは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−1】図7A及び図7Bは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−2】図7C及び図7Dは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図7−3】図7E及び図7Fは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【図8】図8は、第8実施例による半導体装置の概略断面図である。

【図9】図9は、第1応用例による絶縁型DCDCコンバータの概略的な回路図である。

【図10】図10は、第2応用例、第3応用例による絶縁型DCDCコンバータの概略的な回路図である。

【図11】図11は、第2応用例による電圧測定回路の主要部分を概略的に示す回路図である。

【図12】図12は、第3応用例による電圧測定回路の主要部分を概略的に示す回路図である。

【発明を実施するための形態】

【0008】

本発明の実施例による半導体装置の製造方法について説明する。実施例では、GaN系半導体を用いた高電子移動度トランジスタ(HEMT)を形成し、相対的に低耐圧、中耐圧、及び高耐圧のトランジスタを同時形成する。なお、GaN系半導体は、少なくともGaとNとを含む。

【0009】

まず、第1実施例による半導体装置の製造方法について説明する。図1A〜図1Kは、第1実施例による半導体装置の製造方法の主要工程を示す概略断面図である。各図の左側部分、中央部分、及び右側部分は、それぞれ、低耐圧トランジスタ、中耐圧トランジスタ、及び高耐圧トランジスタの部分を示す。

【0010】

図1Aを参照する。基板(例えばSi基板)1上に、下方から順に、GaNバッファ層2、チャネル層となるGaN層3、及び、電子供給層となるAlGaN層4を、例えば有機金属化学気相堆積(MOCVD)で形成する。GaNバッファ層2、GaN層3、及びAlGaN層4の積層厚さは、例えば3μm〜5μmである。

【0011】

GaN層3と、GaN層3よりもバンドギャップの広いAlGaN層4との界面に、2次元電子ガス層が形成される。なお、2次元電子ガス層を形成させるための、GaN系半導体層の積層構造は、この例に限定されない。少なくとも、相互にバンドギャップの異なる第1GaN系半導体層と第2GaN系半導体層とを積層することにより、2次元電子ガス層を形成することができる。

【0012】

図1Bを参照する。AlGaN層4上に、ゲート電極層5を形成する。ゲート電極層5は、例えば、AlやTaN等の金属層であり、スパッタリング(蒸着)により厚さ300nm程度形成される。なお、ゲート電極層5は、金属膜と絶縁膜、ポリシリコン膜と絶縁膜、及び左記の三層とGaN層との積層構造等とすることもできる。絶縁膜は、例えばSiO膜やSiN膜である。

【0013】

ゲート電極層5上に、絶縁膜6を形成する。絶縁膜6は、例えば窒化シリコン(SiN)膜や酸化シリコン(SiO)膜であり、例えば、化学気相堆積(CVD)で厚さ200nm程度形成される。

【0014】

図1Cを参照する。絶縁膜6上に、ゲート電極形状のレジストパターンM11を形成する。レジストパターンM11をマスクとし、絶縁膜6及びゲート電極層5をパターニングして、低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれのゲート電極5を形成する。低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれについて、ゲート電極5上に絶縁膜6が積層された構造が形成される。その後、レジストパターンM11を除去する。

【0015】

図1Dを参照する。ゲート電極5上に絶縁膜6が積層された構造を覆って、AlGaN層4上に、絶縁膜7を形成する。絶縁膜7は、例えばSiN膜やSiO膜であり、例えば、CVDで厚さ200nm〜500nm程度形成される。なお、SiO膜材料として、テトラエトキシシラン(TEOS)を用いることもできる。

【0016】

図1Eを参照する。絶縁膜7上に、レジストパターンM12を形成する。レジストパターンM12は、中耐圧トランジスタ部分及び高耐圧トランジスタ部分のそれぞれで、ソース電極形成用のコンタクトホール形状の開口8Sと、ドレイン電極形成用のコンタクトホール形状の開口8Dとを有する。中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、ゲート電極5の近傍はレジストパターンM12に覆われている。

【0017】

レジストパターンM12の、低耐圧トランジスタ部分の開口8SDは、ゲート電極5の一方側に配置されるソース電極用のコンタクトホール形成領域から、ゲート電極5の他方側に配置されるドレイン電極用のコンタクトホール形成領域までを露出する。つまり、低耐圧トランジスタ部分では、レジストパターンM12の開口8SD内に、ゲート電極5の形成領域も露出する。

【0018】

レジストパターンM12をマスクとして、異方性ドライエッチングにより絶縁膜7をエッチングする。中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、それぞれ、開口8S内にソース電極形成用のコンタクトホール9Sが形成され、開口8D内にドレイン電極形成用のコンタクトホール9Dが形成される。

【0019】

低耐圧トランジスタ部分では、絶縁膜6の上面上に形成された絶縁膜7が除去され、エッチングの異方性により、ゲート電極5と絶縁膜6との積層構造側面上に絶縁膜7が残って、サイドウォール絶縁膜7SWが形成される。サイドウォール絶縁膜7SWの厚さは、例えば200nm程度である。

【0020】

開口8SD内で、サイドウォール絶縁膜7SWの外側部分の絶縁膜7が除去されて、ゲート電極5を挟んで一方側にソース電極形成用のコンタクトホール9Sが形成され、ゲート電極5を挟んで他方側にドレイン電極形成用のコンタクトホール9Dが形成される。その後、レジストパターンM12を除去する。

【0021】

なお、コンタクトホール9S及びコンタクトホール9Dの形成された絶縁膜7をマスクとして、さらに、AlGaN層4を除去することもできる。

【0022】

このように、低耐圧トランジスタにおいては、コンタクトホール9Sのゲート電極側端部の位置、及び、コンタクトホール9Dのゲート電極側端部の位置が、サイドウォール絶縁膜7SWにより決定される。つまり、低耐圧トランジスタは、ソース電極及びドレイン電極のゲート電極側端部(ゲート端)の位置が、セルフアラインで決定される。一方、中耐圧トランジスタ及び高耐圧トランジスタにおいては、ソース電極及びドレイン電極のゲート端の位置が、マスクM12により決定される。

【0023】

各電極に印加される電圧の例は、例えば以下のようなものである。低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタのいずれも、ソース電極には例えば0Vが印加され、ゲート電極には例えばオフ時に0V、オン時に1V〜10Vが印加される。ドレイン電極には、例えば、低耐圧トランジスタで1V〜10V、中耐圧トランジスタで10V〜100V、高耐圧トランジスタで100V〜1000Vが印加される。

【0024】

低耐圧トランジスタは、ゲート・ソース間、及び、ゲート・ドレイン間の電圧差が最大でも例えば10V程度である。このため、ゲート電極からソース電極までの距離、及び、ゲート電極からドレイン電極までの距離を、比較的短くすることができ、ソース電極及びドレイン電極のゲート端の位置を、セルフアラインで決定することができる。

【0025】

耐圧を向上させるため、ゲート電極からドレイン電極のゲート端までの距離は、低耐圧トランジスタよりも中耐圧トランジスタが長く、中耐圧トランジスタよりも高耐圧トランジスタが長い。ゲート電極からドレイン電極のゲート端までの距離は、例えば、低耐圧トランジスタで200nm程度、中耐圧トランジスタで2μm程度、高耐圧トランジスタで20μm程度である。

【0026】

図1Fを参照する。コンタクトホール9Sの内面及びコンタクトホール9Dの内面を覆って、全面上に、導電膜10を形成する。導電膜10は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。導電膜10の厚さは、例えば300nm程度である。

【0027】

図1Gを参照する。導電膜10上に、レジストパターンM13を形成する。レジストパターンM13は、低耐圧トランジスタ部分、中耐圧トランジスタ部分それぞれについて、ソース電極形状及びドレイン電極形状で形成されており、また、高耐圧トランジスタ部分では、ソース電極形状、ドレイン電極形状、及びフィールドプレート形状で形成されている。

【0028】

レジストパターンM13をマスクとし、導電膜10をパターニングして、低耐圧トランジスタ、中耐圧トランジスタ、高耐圧トランジスタそれぞれのソース電極10S及びドレイン電極10Dと、高耐圧トランジスタのフィールドプレート10FPを形成する。その後、レジストパターンM13を除去する。ゲート電極5とソース電極10Sとの間、及び、ゲート電極5とドレイン電極10Dとの間に、2次元電子ガス層2DEGを示す。

【0029】

なお、低耐圧トランジスタのソース電極10Sあるいはドレイン電極10Dが、ゲート電極5の端部上に重なってパターニングされたとしても、ゲート電極5上に残された絶縁膜6により、ソース電極10Sあるいはドレイン電極10Dとゲート電極5との短絡は抑制される。

【0030】

高耐圧トランジスタのフィールドプレート10FPは、ゲート電極5とドレイン電極10Dとの間で、絶縁膜7上に配置される。フィールドプレート10FPへの印加電圧は、例えば0Vである。フィールドプレート10FPにより、ゲート電極5からドレイン電極10Dのゲート端までの間における電界集中を緩和して、耐圧を高めることができる。

【0031】

図1Hを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜11を形成する。層間絶縁膜11の上面を、化学機械研磨(CMP)で平坦化する。

【0032】

図1Iを参照する。層間絶縁膜11上に、レジストパターンM14を形成する。レジストパターンM14は、各ソース電極10Sを露出するコンタクトホール形状の開口、及び、各ドレイン電極10Dを露出するコンタクトホール形状の開口を有する。

【0033】

レジストパターンM14をマスクとし、層間絶縁膜11をエッチングして、ソース電極10Sを露出するコンタクトホール12S、及び、ドレイン電極10Dを露出するコンタクトホール12Dを形成する。その後、レジストパターンM14を除去する。

【0034】

図1Jを参照する。コンタクトホール12S及びコンタクトホール12Dを埋め込んで、全面上に、導電膜13を形成する。導電膜13は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0035】

図1Kを参照する。導電膜13上に、各ソース電極10Sに接続する配線形状、及び、各ドレイン電極10Dに接続する配線形状のレジストパターンM15を形成する。レジストパターンM15をマスクとし、導電膜13をパターニングして、配線層13S及び配線層13Dを形成する。その後、レジストパターンM15を除去する。

【0036】

第1実施例の配線層13S及び配線層13Dは、層間絶縁膜11に埋め込まれた導電プラグ部分と、層間絶縁膜11上に配置された配線部分とが、一体的に形成される。

【0037】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第1実施例による半導体装置が形成される。

【0038】

次に、第2実施例による半導体装置の製造方法について説明する。図2A〜図2Dは、第2実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0039】

まず、第1実施例で図1Iを参照して説明した工程までと同様にして、層間絶縁膜11にコンタクトホール12S及びコンタクトホール12Dを形成する。

【0040】

図2Aを参照する。コンタクトホール12S及びコンタクトホール12Dを埋め込んで、全面上に、導電膜21を形成する。導電膜21は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0041】

図2Bを参照する。導電膜21の上部をCMPで除去して、層間絶縁膜11を露出させる。これにより、コンタクトホール12S及びコンタクトホール12Dに、それぞれ導電プラグ21S及び導電プラグ21Dが形成される。

【0042】

図2Cを参照する。導電プラグ21S及び導電プラグ21Dを覆って、全面上に、導電膜22を形成する。導電膜22は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0043】

図2Dを参照する。導電膜22上に、各導電プラグ21Sに接続する配線形状、及び、各導電プラグ21Dに接続する配線形状のレジストパターンM21を形成する。レジストパターンM21をマスクとし、導電膜22をパターニングして、配線22S及び配線22Dを形成する。その後、レジストパターンM21を除去する。

【0044】

第2実施例のように、ソース電極10Sに接続する配線層や、ドレイン電極10Dに接続する配線層について、層間絶縁膜11に埋め込まれた導電プラグ部分と、層間絶縁膜11上に配置された配線部分とを、別々の工程で形成することもできる。

【0045】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第2実施例による半導体装置が形成される。

【0046】

次に、第3実施例による半導体装置の製造方法について説明する。図3A〜図3Fは、第3実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0047】

まず、第1実施例で図1Eを参照して説明した工程までと同様にして、絶縁膜7にコンタクトホール9S及びコンタクトホール9Dを形成する。

【0048】

図3Aを参照する。コンタクトホール9S及びコンタクトホール9Dを埋め込んで、全面上に、導電膜31を形成する。導電膜31は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0049】

図3Bを参照する。導電膜31の上部をCMPで除去する。低耐圧トランジスタでは、ゲート電極5上方で絶縁膜6が露出し、コンタクトホール9S及びコンタクトホール9Dの外側で絶縁膜7が露出し、コンタクトホール9S内にソース電極31Sが形成され、コンタクトホール9D内にドレイン電極31Dが形成される。

【0050】

中耐圧トランジスタ及び高耐圧トランジスタでは、ゲート電極5の上方で導電膜31とともに絶縁膜7が除去されて絶縁膜6が露出し、コンタクトホール9S及びコンタクトホール9Dの外側で絶縁膜7が露出し、コンタクトホール9S内にソース電極31Sが形成され、コンタクトホール9D内にドレイン電極31Dが形成される。

【0051】

第1実施例のような導電膜のパターニングでソース電極及びドレイン電極を形成する方法に限らず、第3実施例のように、導電膜の不要部を研磨除去してソース電極及びドレイン電極を形成することもできる。

【0052】

図3Cを参照する。全面上に、導電膜32を形成する。導電膜32は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0053】

図3Dを参照する。導電膜32上に、レジストパターンM31を形成する。レジストパターンM31は、低耐圧トランジスタ部分、中耐圧トランジスタ部分、高耐圧トランジスタ部分それぞれについて、ソース電極31Sに接続する配線形状、及び、ドレイン電極31Dに接続する配線形状を有するとともに、高耐圧トランジスタ部分では、フィールドプレート形状を有する。

【0054】

レジストパターンM31をマスクとし、導電膜32をパターニングして、配線32S、配線32D、及びフィールドプレート32FPを形成する。その後、レジストパターンM31を除去する。

【0055】

図3Eを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜33を形成する。層間絶縁膜33の上面を、CMPで平坦化する。

【0056】

図3Fを参照する。層間絶縁膜33上に、レジストパターンM32を形成する。レジストパターンM32は、配線32Sを露出するコンタクトホール形状の開口、及び、配線32Dを露出するコンタクトホール形状の開口を有する。

【0057】

レジストパターンM32をマスクとし、層間絶縁膜33をエッチングして、配線32Sを露出するコンタクトホール34S、及び、配線32Dを露出するコンタクトホール34Dを形成する。その後、レジストパターンM32を除去する。

【0058】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第3実施例による半導体装置が形成される。

【0059】

次に、第4実施例による半導体装置の製造方法について説明する。図4A〜図4Hは、第4実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0060】

まず、第1実施例で図1Cを参照して説明した工程までと同様にして、ゲート電極5上に絶縁膜6が残った構造を形成する。

【0061】

図4Aを参照する。第1実施例で図1Dを参照して説明した絶縁膜7の形成工程と同様に、ゲート電極5上に絶縁膜6が積層された構造を覆って、AlGaN層4上に、絶縁膜41を形成する。

【0062】

第1実施例(〜第3実施例)では、低耐圧トランジスタのソース電極及びドレイン電極のゲート端の位置を、セルフアラインで決定した。中耐圧トランジスタ及び高耐圧トランジスタにおいても、ゲート・ソース間の電位差は、最大で例えば10V程度に留まる。そこで、第4実施例では、以下に説明するように、中耐圧トランジスタ及び高耐圧トランジスタのソース電極のゲート端の位置も、セルフアラインで決定する。

【0063】

図4Bを参照する。絶縁膜41上にレジストパターンM41を形成する。レジストパターンM41をマスクとし、絶縁膜41を異方性ドライエッチングして、ソース電極形成用のコンタクトホール42Sと、ドレイン電極形成用のコンタクトホール42Dとを形成する。

【0064】

第4実施例によるレジストパターンM41の開口形状は、以下のようなものである。低耐圧トランジスタ部分の開口43SDは、第1実施例によるレジストパターンM12の開口8SDと同様である。低耐圧トランジスタ部分について、第1実施例と同様に、ゲート電極5のソース電極側及びドレイン電極側の側面にサイドウォール絶縁膜41SWが形成されるとともに、コンタクトホール42S及びコンタクトホール42Dが形成される。

【0065】

中耐圧トランジスタ部分及び高耐圧トランジスタ部分において、ソース電極形成用の開口43Sは、ゲート電極5のソース電極側端部上まで重なり、ゲート電極形成領域を露出する。ドレイン電極形成用の開口43Dは、第1実施例によるレジストパターンM12の開口8Dと同様である。ゲート電極5のドレイン電極側端部は、レジストパターンM41に覆われている。

【0066】

従って、第4実施例では、中耐圧トランジスタ部分及び高耐圧トランジスタ部分においても、ゲート電極5のソース電極側側面にはサイドウォール絶縁膜41SWが形成されて、コンタクトホール42Sが形成される。つまり、中耐圧トランジスタ及び高耐圧トランジスタにおいても、ソース電極のゲート端の位置がセルフアラインで決定される。

【0067】

なお、コンタクトホール42S及びコンタクトホール42Dが形成された絶縁膜41をマスクとして、さらに、AlGaN層4を除去することもできる。

【0068】

図4Cを参照する。第1実施例で図1Fを参照して説明した導電膜10の形成工程と同様にして、コンタクトホール42S及びコンタクトホール42Dを覆って、全面上に導電膜44を形成する。

【0069】

図4Dを参照する。第1実施例で図1Gを参照して説明した工程と同様にして、ソース電極形状、ドレイン電極形状、及びフィールドプレート形状で形成されたレジストパターンM42を形成する。レジストパターンM42をマスクとし、導電膜44をパターニングして、ソース電極44S、ドレイン電極44D、及びフィールドプレート44FPを形成する。その後、レジストパターンM42を除去する。

【0070】

図4Eを参照する。第1実施例で図1Hを参照して説明した層間絶縁膜11の形成工程と同様にして、全面上に層間絶縁膜45を形成する。

【0071】

図4Fを参照する。第1実施例で図1Iを参照して説明した工程と同様にして、層間絶縁膜45上に、ソース電極44Sを露出するコンタクトホール形状の開口、及び、ドレイン電極44Dを露出するコンタクトホール形状の開口を有するレジストパターンM43を形成する。

【0072】

レジストパターンM43をマスクとし、層間絶縁膜45をエッチングして、ソース電極44Sを露出するコンタクトホール46S、及び、ドレイン電極44Dを露出するコンタクトホール46Dを形成する。その後、レジストパターンM43を除去する。

【0073】

図4Gを参照する。第1実施例で図1Jを参照して説明した導電膜13の形成工程と同様にして、コンタクトホール46S及びコンタクトホール46Dを埋め込んで、全面上に導電膜47を形成する。

【0074】

図4Hを参照する。第1実施例で図1Kを参照して説明した工程と同様にして、導電膜47上に、ソース電極44Sに接続する配線形状、及び、ドレイン電極44Dに接続する配線形状レジストパターンM44を形成する。

【0075】

レジストパターンM44をマスクとし、導電膜47をパターニングして、配線層47S及び配線層47Dを形成する。その後、レジストパターンM44を除去する。

【0076】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第4実施例による半導体装置が形成される。

【0077】

次に、第5実施例による半導体装置の製造方法について説明する。第5実施例は、中耐圧トランジスタ及び高耐圧トランジスタにおいてもソース電極ゲート端位置をセルフアラインで決定するようにした第4実施例に、第2実施例の配線形成方法を適用した例である。図5A〜図5Dは、第5実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

まず、第4実施例で図4Fを参照して説明した工程までと同様にして、層間絶縁膜45にコンタクトホール46S及びコンタクトホール46Dを形成する。

【0078】

図5Aを参照する。第2実施例で図2Aを参照して説明した導電膜21の形成工程と同様にして、コンタクトホール46S及びコンタクトホール46Dを埋め込んで、全面上に導電膜51を形成する。

【0079】

図5Bを参照する。第2実施例で図2Bを参照して説明した工程と同様にして、導電膜51の上部をCMPで除去し、コンタクトホール46S及びコンタクトホール46Dに、それぞれ導電プラグ51S及び導電プラグ51Dを形成する。

【0080】

図5Cを参照する。第2実施例で図2Cを参照して説明した導電膜22の形成工程と同様にして、全面上に導電膜52を形成する。

【0081】

図5Dを参照する。第2実施例で図2Dを参照して説明した工程と同様にして、導電膜52上に、導電プラグ51Sに接続する配線形状、及び、導電プラグ51Dに接続する配線形状のレジストパターンM51を形成する。レジストパターンM51をマスクとし、導電膜52をパターニングして、配線52S及び配線52Dを形成する。その後、レジストパターンM51を除去する。さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第5実施例による半導体装置が形成される。

【0082】

次に、第6実施例による半導体装置の製造方法について説明する。第6実施例は、中耐圧トランジスタ及び高耐圧トランジスタにおいてもソース電極ゲート端位置をセルフアラインで決定するようにした第4実施例に、第3実施例のソース電極・ドレイン電極形成方法を適用した例である。図6A〜図6Fは、第6実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0083】

まず、第4実施例で図4Bを参照して説明した工程までと同様にして、絶縁膜41にコンタクトホール42S及びコンタクトホール42Dを形成する。

【0084】

図6Aを参照する。第3実施例で図3Aを参照して説明した導電膜31の形成工程と同様にして、コンタクトホール42S及びコンタクトホール42Dを埋め込んで、全面上に導電膜61を形成する。

【0085】

図6Bを参照する。第3実施例で図3Bを参照して説明した工程と同様にして、導電膜61の上部をCMPで除去し、コンタクトホール42S及びコンタクトホール42Dに、それぞれソース電極61S及びソース電極61Dを形成する。

【0086】

図6Cを参照する。第3実施例で図3Cを参照して説明した導電膜32の形成工程と同様にして、全面上に導電膜62を形成する。

【0087】

図6Dを参照する。第3実施例で図3Dを参照して説明した工程と同様にして、導電膜62上に、ソース電極61Sに接続する配線形状、ドレイン電極61Dに接続する配線形状、及び、フィールドプレート形状のレジストパターンM61を形成する。レジストパターンM61をマスクとし、導電膜62をパターニングして、配線62S、配線62D、及びフィールドプレート62FPを形成する。その後、レジストパターンM61を除去する。

【0088】

図6Eを参照する。第3実施例で図3Eを参照して説明した層間絶縁膜33の形成工程と同様にして、全面上に層間絶縁膜63を形成する。

【0089】

図6Fを参照する。第3実施例で図3Fを参照して説明した工程と同様にして、層間絶縁膜63上に、配線62Sを露出するコンタクトホール形状の開口、及び、配線62Dを露出するコンタクトホール形状の開口を有するレジストパターンM62を形成する。

【0090】

レジストパターンM62をマスクとし、層間絶縁膜63をエッチングして、配線62Sを露出するコンタクトホール64S、及び、配線62Dを露出するコンタクトホール64Dを形成する。その後、レジストパターンM62を除去する。

【0091】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第6実施例による半導体装置が形成される。

【0092】

次に、第7実施例による半導体装置の製造方法について説明する。図7A〜図7Fは、第7実施例による半導体装置の製造方法の主要工程を示す概略断面図である。

【0093】

まず、第1実施例で図1Dを参照して説明した工程までと同様にして、ゲート電極5上に絶縁膜6が積層された構造を覆って全面上に絶縁膜7を形成する。

【0094】

図7Aを参照する。全面の絶縁膜7を、異方性ドライエッチングする。低耐圧トランジスタ部分、中耐圧トランジスタ部分、及び高耐圧トランジスタ部分において、ゲート電極5と絶縁膜6の積層構造の側面に、サイドウォール絶縁膜7SWが形成される。

【0095】

図7Bを参照する。全面上に、例えば、SiOをCVDで堆積して、絶縁膜71を形成する。絶縁膜71は、絶縁膜6(例えばSiN膜)やサイドウォール絶縁膜7(例えばSiN膜)に対して選択的エッチングできる材料とすることが好ましい。そして、絶縁膜71の上面を、CMPで平坦化する。

【0096】

図7Cを参照する。絶縁膜71上に、レジストパターンM71を形成する。レジストパターンM71をマスクとし、絶縁膜71を異方性ドライエッチングして、ソース電極形成用のコンタクトホール72Sと、ドレイン電極形成用のコンタクトホール72Dとを形成する。例えばSiOによる絶縁膜71が、例えばSiNによる絶縁膜6及びサイドウォール絶縁膜7SWに対して選択的にエッチングされるようなエッチング条件とすることが好ましい。

【0097】

レジストパターンM71の開口パターンは、第1実施例で図1Eを参照して説明した工程で用いたレジストパターンM12と同様である。つまり、低耐圧トランジスタ部分では、ゲート電極配置領域とその両側領域を露出する開口パターンでエッチングが行われる。サイドウォール絶縁膜7SWの外側で絶縁膜71がエッチングされ、ゲート電極5及びサイドウォール絶縁膜7SWを挟んで一方側と他方側に、それぞれコンタクトホール72Sとコンタクトホール72Dとが形成される。

【0098】

また、中耐圧トランジスタ部分及び高耐圧トランジスタ部分では、ソース電極形成領域及びドレイン電極形成領域に配置された開口パターンでエッチングが行われ、コンタクトホール72Sとコンタクトホール72Dとが形成される。

【0099】

さらに、レジストパターンM71及び絶縁膜71をマスクとして、コンタクトホール72Sとコンタクトホール72Dの底に露出したAlGaN層4をエッチングする。その後、レジストパターンM71を除去する。このように、第7実施例では、AlGaN層4までを除去し、底にGaN層3が露出したコンタクトホール72S及びコンタクトホール72Dを形成する。

【0100】

図7Dを参照する。コンタクトホール72S及びコンタクトホール72Dを埋め込んで、全面上に、導電膜73を形成する。導電膜73は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、W層をCVDで形成する。

【0101】

導電膜73の上部をCMPで除去して、絶縁膜71及び絶縁膜6を露出させる。これにより、コンタクトホール72S及びコンタクトホール72Dに、それぞれソース電極73S及びソース電極73Dが形成される。

【0102】

図7Eを参照する。全面上に、例えば、SiOをCVDで堆積して、層間絶縁膜74を形成する。

【0103】

層間絶縁膜74上に、レジストパターンM72を形成する。レジストパターンM72は、ソース電極73Sを露出するコンタクトホール形状の開口、ソース電極73Dを露出するコンタクトホール形状の開口、及び、高耐圧トランジスタのフィールドプレート形状の開口を有する。

【0104】

レジストパターンM72をマスクとし、層間絶縁膜74をエッチングして、ソース電極73Sを露出するコンタクトホール75S、ドレイン電極73Dを露出するコンタクトホール75D、及び、底に絶縁膜71が露出し、フィールドプレートが埋め込まれる凹部75FPを形成する。その後、レジストパターンM72を除去する。

【0105】

図7Fを参照する。コンタクトホール75S、コンタクトホール75D、及び凹部75FPを埋め込んで、全面上に、導電膜76を形成する。導電膜76は、例えば以下のように形成される。まず、バリアメタル層として、Ti膜とTiN膜の積層を、スパッタリングで形成する。バリアメタル層上に、Al層あるいはAlCu層あるいはTiN層あるいはW層を、スパッタリングあるいはCVDで形成する。

【0106】

導電膜76上に、ソース電極73Sに接続する配線形状、ドレイン電極73Dに接続する配線形状、及び、フィールドプレート形状のレジストパターンM73を形成する。レジストパターンM73をマスクとし、導電膜76をパターニングして、配線層76S、配線層76D、及びフィールドプレート76FPを形成する。その後、レジストパターンM73を除去する。

【0107】

さらに、必要に応じて上方に多層配線構造を形成することができる。このようにして、第7実施例による半導体装置が形成される。

なお、第7実施例の変形例として、第4実施例等と同様に、中耐圧トランジスタ及び高耐圧トランジスタのソース電極のゲート端の位置を、セルフアラインで決定させるようにすることもできる。

【0108】

次に、図8を参照して、第8実施例による半導体装置について説明する。図8は、第8実施例によるトランジスタの概略断面図である。第8実施例のトランジスタは、ゲート電極5とドレイン電極10Dとの間のフィールドプレート10FPに加え、ゲート電極5とソース電極10Sとの間にもフィールドプレート10FPSを形成した構造である。第8実施例のトランジスタは、第1実施例の高耐圧トランジスタの製造工程を適宜変更して形成することができる。なお、ドレイン電極側フィールドプレート10FPとソース電極側フィールドプレート10FPSとを電気的に接続することもできる。

【0109】

以上、第1実施例〜第8実施例に沿って説明したように、GaN系半導体を用いたHEMTについて、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板上に同時形成することができる。

【0110】

次に、応用例による絶縁型直流-直流(DCDC)コンバータについて説明する。絶縁型DCDCコンバータは、電源装置の一部であり、力率改善回路で生成された例えば380Vの電源電圧を、例えば48V程度に降圧する回路である。

【0111】

図9は、第1応用例による絶縁型DCDCコンバータの概略的な回路図である。絶縁型DCDCコンバータは、入力電圧(例えば380V)が入力される入力回路101Aと、出力電圧(例えば48V)が出力される出力回路101Bとが、電気的に相互に絶縁されており、入力回路101Aの接地基準電圧VSS1と、出力回路101Bの接地基準電圧VSS2とが独立している。

【0112】

入力回路101Aは、駆動回路102と、ゲートドライバー103と、制御回路104とを含んで形成される。駆動回路102、ゲートドライバー103、及び制御回路104は、同一の半導体チップ105上に形成されている。

【0113】

駆動回路102に、入力電圧VINが入力される。駆動回路102は、トランジスタQH1〜QH4を含んで形成される。トランジスタQH1とトランジスタQH2の直列接続と、トランジスタQH3とトランジスタQH4の直列接続とが、入力電圧VINと接地基準電圧VSS1との間に並列に接続されている。トランジスタQH1とトランジスタQH3が入力電圧VIN側に配置され、トランジスタQH2とトランジスタQH4が接地基準電圧VSS1側に配置されている。

【0114】

ゲートドライバー103から供給される制御信号G1〜G4が、それぞれ、トランジスタQH1〜QH4のゲート電極に入力され、各トランジスタQH1〜QH4のオンオフを制御する。

【0115】

トランジスタQH2のドレイン電極とトランジスタQH1のソース電極との接続点であるノードN1と、トランジスタQH4のドレイン電極とトランジスタQH3のソース電極との接続点であるノードN2との間に、コイルL1が接続されている。

【0116】

制御信号G1〜G4は、トランジスタQH1とトランジスタQH4とがオンとなり、トランジスタQH2とトランジスタQH3とがオフとなる第1の期間と、トランジスタQH1とトランジスタQH4とがオフとなり、トランジスタQH2とトランジスタQH3とがオンとなる第2の期間とを、周期的に切り替える。切り替えの周波数は、例えば100kHz程度である。

【0117】

第1の期間では、電流が、トランジスタQH1、ノードN1、コイルL1、ノードN2、及びトランジスタQH4を経由する向きで流れる。一方、第2の期間では、電流が、トランジスタQH3、ノードN2、コイルL1、ノードN1、及びトランジスタQH2を経由する向きで流れる。つまり、第1の期間では、ノードN1からノードN2へ流れる電流方向となり、第2の期間では、反転して、ノードN2からノードN1へ流れる電流方向となる。従って、第1の期間と第2の期間とを周期的に切り替えることにより、コイルL1に交流電流が流れる。

【0118】

出力回路101Bは、直列接続されたコイルL2及びL3を有する。コイルL2及びL3が、入力回路101AのコイルL1と結合する。コイルL2とコイルL3との接続点であるノードN4に、接地基準電圧VSS2が接続されている。ノードN4と反対側のコイルL2の端部N3と、ノードN4と反対側のコイルL3の端部N5とが、それぞれ、整流用のダイオードD1、D2を介して、出力点Voutに接続されている。出力点Voutと接地基準電圧VSS2との間に、キャパシタC3が接続され、その先の負荷RLに電力が供給される。

【0119】

出力点Voutから出力されている電圧値のデータが、フォトカプラーPCを介して、制御回路104の入力端子VSENSEに入力される。駆動回路102に流れる入力電流が、カレントコイルCCにより測定され、入力電流値が、制御回路104の入力端子CSENSEに入力される。

【0120】

制御回路104は、入力電流値と出力電圧値とに基づき、所望の出力電圧が得られるように、制御信号PWMを生成する。制御回路104から供給された制御信号PWMに基づき、ゲートドライバー103が、駆動回路102の有する各トランジスタQH1〜QH4の制御信号G1〜G4を生成する。

【0121】

駆動回路102に使用されるトランジスタQH1等は、高耐圧であることが望ましい。一方、制御回路104や、ゲートドライバー103に使用されるトランジスタは、駆動回路102に比べて低耐圧でよい。

【0122】

上記実施例で説明した方法を用いれば、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板に形成することができ、低耐圧、中耐圧、及び高耐圧のトランジスタを適宜用いて、同一の半導体チップ上に、駆動回路102と、ゲートドライバー103と、制御回路104とを形成することができる。

【0123】

駆動回路102と、ゲートドライバー103と、制御回路104とを別々の半導体チップ上に形成した絶縁型DCDCコンバータを、比較例とする。応用例の絶縁型DCDCコンバータは、駆動回路102、ゲートドライバー103、及び制御回路104が同一半導体チップ上に形成されていることにより、比較例に比べて、例えば高速動作させることができる。

【0124】

図10は、第2応用例による絶縁型DCDCコンバータの概略的な回路図である。第1応用例との違いは、駆動回路102への入力電流の測定にカレントコイルCCを用いていないことである。

【0125】

第2応用例では、駆動回路102のノードN1及びノードN2での電圧を測定することにより、駆動回路102に流れる電流を測定する。各トランジスタの抵抗は予め測定しておくことができるので、電圧測定により電流値を得ることができる。ノードN1の電圧が、制御回路104の入力端子CSENSE1に入力され、ノードN2の電圧が、制御回路104の入力端子CSENSE2に入力される。

【0126】

図11は、第2応用例による電圧測定回路104Cの主要部分を概略的に示す回路図である。電圧測定回路104Cは、制御回路104に含まれる。代表として、ノードN1に接続された入力端子CSENSE1側部分を示すが、ノードN2に接続された入力端子CSENSE2側部分も同様な構造である。

【0127】

一対のセンストランジスタQL11及びQL12を含む差動アンプが形成されている。センストランジスタQL12のゲート電極に接地基準電圧VSS1が入力され、センストランジスタQL11のゲート電極に、トランジスタQH11を介しノードN1の電圧が入力されて、ノードN1の電圧が測定される。

【0128】

センストランジスタQL11及びQL12は、低耐圧トランジスタで形成されている。トランジスタQH11は、高耐圧トランジスタで形成されている。駆動回路102のトランジスタQH1がオンでトランジスタQH2がオフのとき、ノードN1の電圧は、例えば380V近くまで高くなる。このような高い電圧がセンストランジスタQL11のゲート電極に印加されれば、トランジスタQL11は破壊されてしまう。そこで、第2応用例の電圧測定回路104Cでは、トランジスタQL11とノードN1との間に、高耐圧のトランジスタQH11を挿入している。

【0129】

トランジスタQH11のゲート(ノードN12)の電圧VN12は、トランジスタQH11の閾値Vth+数ボルトとする。例えば、トランジスタQH11の閾値を1Vとして、トランジスタQH11のゲート電圧VN12を3Vとすると、トランジスタQH11のソース(ノードN11)の電圧、つまり、センストランジスタQL11のゲートに印加される電圧VN11は、2Vとなる。ゲート電圧VN11が数ボルトに抑えられることにより、トランジスタQL11の破壊が抑制される。

【0130】

なお、駆動回路102のトランジスタQH2がオンでトランジスタQH1がオフのときは、ノードN1の電圧が、例えば1V程度まで低くなる。トランジスタQH2がオンでトランジスタQH1がオフのときにも、トランジスタQH11がオンとなって電圧測定回路104Cが機能するように、トランジスタQH11のゲート電圧VN12が定められる。

【0131】

次に、図10を再度参照して、第3応用例による絶縁型DCDCコンバータについて説明する。第3応用例では、第2応用例と同様に、カレントコイルCCを用いずに、駆動回路102への入力電流を測定するが、測定回路部分の構造が異なる。また、第3応用例では、図10に破線で示すように、制御回路104に入力電圧VINが供給される。

【0132】

図12は、第3応用例による電圧測定回路104Cの主要部分を概略的に示す回路図である。電圧測定回路104Cは、制御回路104に含まれる。代表として、ノードN1に接続された入力端子CSENSE1側部分を示すが、ノードN2に接続された入力端子CSENSE2側部分も同様な構造である。

【0133】

一対のセンストランジスタQM11及びQM12を含む差動アンプが形成されている。電源電圧として、センストランジスタQM11及びQM12のドレイン側に入力電圧VINが印加されている。センストランジスタQM12のゲート電極に入力電圧VINが入力され、センストランジスタQM11のゲート電極にノードN1の電圧が入力されて、ノードN1の電圧が測定される。

【0134】

駆動回路102のトランジスタQH1がオフでトランジスタQH2がオンのとき、ノードN1の電圧は、例えば0V近くまで低くなり、センストランジスタQM11のゲート・ドレイン間及びゲート・ソース間の電圧差が、例えば380V近くに高くなってしまう。トランジスタQH1がオフ、トランジスタQH2がオンで、ノードN1が低い電位(例えば0V)まで下がった時、トランジスタQM12に(QFP13、QM12、QFP14の経路で)電流が流れ、ノードN12が高い電位となる。

【0135】

第3応用例の電圧測定回路104Cでは、センストランジスタQM11のドレイン側にフィールドプレートを形成するとともに、ソース側にもフィールドプレートを形成して、ゲート・ドレイン間及びゲート・ソース間の耐圧を向上させている(第8実施例参照)。図12では、フィールドプレート形成部をトランジスタとして示し、ドレイン側フィールドプレート形成部をQFP11、ソース側フィールドプレート形成部をQFP12と示している。

【0136】

センストランジスタQM12についても、センストランジスタQM11側と対称となるように、ドレイン側フィールドプレートQFP13及びソース側フィールドプレートQFP14を形成している。

【0137】

以上説明したように、GaN系半導体を用いたHEMTについて、低耐圧、中耐圧、及び高耐圧のトランジスタを、同一基板上に同時形成することができる。これにより、例えば、絶縁型DCDCコンバータの入力回路における駆動回路、ゲートドライバー、及び制御回路を同一の半導体チップ上に形成することができ、例えば動作の高速化を図ることができる。

【0138】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0139】

以上説明した第1実施例〜第8実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

(付記2)

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記第1マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第2絶縁膜の異方性エッチングは、前記第2構造の前記第2ソース電極側側面上にサイドウォール絶縁膜を残しつつ、前記第2ソース電極形成用コンタクトホールを形成する付記1に記載の半導体装置の製造方法。

(付記3)

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程は、

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び、前記第2ドレイン電極形成用コンタクトホールの上方に第1導電膜を形成する工程と、

前記第1ソース電極の形成領域、前記第1ドレイン電極の形成領域、前記第2ソース電極の形成領域、及び、前記第2ドレイン電極の形成領域を覆う第2マスクを用い、前記第1導電膜をパターニングして、前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程と

を含む付記1または2に記載の半導体装置の製造方法。

(付記4)

前記第1導電膜をパターニングする工程において、前記第2マスクは、前記第2ゲート電極と前記第2ドレイン電極との間に配置されるフィールドプレートの形成領域を覆い、前記第1導電膜のパターニングにより、フィールドプレートが形成される付記3に記載の半導体装置の製造方法。

(付記5)

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程は、

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び、前記第2ドレイン電極形成用コンタクトホールの上方に第2導電膜を形成する工程と、

研磨により、前記第2導電膜の一部と、前記第2構造上方に残った前記第2絶縁膜とを除去して、前記第1ソース電極形成用コンタクトホール内、前記第1ドレイン電極形成用コンタクトホール内、前記第2ソース電極形成用コンタクトホール内、及び、前記第2ドレイン電極形成用コンタクトホール内に、それぞれ、前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を形成する工程と

を含む付記1または2に記載の半導体装置の製造方法。

(付記6)

さらに、

前記第1ソース電極、前記第1ドレイン電極、前記第2ソース電極、及び前記第2ドレイン電極を覆って、前記第2絶縁膜上方に、第3導電膜を形成する工程と、

前記第1ソース電極に接続する配線の形成領域、前記第1ドレイン電極に接続する配線の形成領域、前記第2ソース電極に接続する配線の形成領域、及び前記第2ドレイン電極に接続する配線の形成領域を覆うとともに、前記第2ゲート電極と前記第2ドレイン電極との間に配置されるフィールドプレートの形成領域を覆う第3マスクを用い、前記第3導電膜をパターニングして、前記第1ソース電極に接続する配線、前記第1ドレイン電極に接続する配線、前記第2ソース電極に接続する配線、前記第2ドレイン電極に接続する配線、及びフィールドプレートを形成する工程と

を有する付記5に記載の半導体装置の製造方法。

(付記7)

さらに、前記第2絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する付記1または2に記載の半導体装置の製造方法。

(付記8)

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第2絶縁膜を異方性エッチングして、前記第1構造の側面上及び前記第2構造の側面上にサイドウォール絶縁膜を形成する工程と、

前記第1構造、前記第1構造の側面上の前記サイドウォール絶縁膜、前記第2構造、及び、前記第2構造の側面上の前記サイドウォール絶縁膜を覆って、前記第2GaN系半導体層上方に、第3絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有するマスクを用いて、前記第3絶縁膜をエッチングすることにより、前記第1開口内において、前記第1ゲート電極及び前記サイドウォール絶縁膜を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

(付記9)

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第3絶縁膜のエッチングにより、前記第2開口内において、前記第2構造側面上の前記サイドウォール絶縁膜が露出して、第2ソース電極形成用コンタクトホールが形成される付記8に記載の半導体装置の製造方法。

(付記10)

さらに、前記第3絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する付記8または9に記載の半導体装置の製造方法。

【符号の説明】

【0140】

1 Si基板

2 GaNバッファ層

3 GaN層

4 AlGaN層

5 ゲート電極層、ゲート電極

6、7 絶縁膜

7SW サイドウォール絶縁膜

8SD、8S、8D マスクの開口

9S、9D コンタクトホール

10 導電膜

10S ソース電極

10D ドレイン電極

10FP フィールドプレート

11 層間絶縁膜

12S、12D コンタクトホール

13 導電膜

13S、13D 配線層

21、22 導電膜

21S、21D 導電プラグ

22S、22D 配線

31 導電膜

31S ソース電極

31D ドレイン電極

32S、32D 配線

32FP フィールドプレート

33 層間絶縁膜

34S、34D コンタクトホール

41 絶縁膜

42S、42D コンタクトホール

43SD、43S、43D マスクの開口

44 導電膜

44S ソース電極

44D ドレイン電極

44FP フィールドプレート

45 層間絶縁膜

46S、46D コンタクトホール

47 導電膜

47S、47D 配線層

51、52 導電膜

51S、51D 導電プラグ

52S、52D 配線

61 導電膜

61S ソース電極

61D ドレイン電極

62S、62D 配線

62FP フィールドプレート

63 層間絶縁膜

64S、64D コンタクトホール

71 絶縁膜

72S、72D コンタクトホール

73 導電膜

73S ソース電極

73D ドレイン電極

74 層間絶縁膜

75S、75D コンタクトホール

75FP 凹部

76S、76D 配線層

76FP フィールドプレート

10FPS フィールドプレート

M11〜M15、M21、M31、M32、M41〜M44、M51、M61、M62、M71〜M73 レジストパターン

【特許請求の範囲】

【請求項1】

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

【請求項2】

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記第1マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第2絶縁膜の異方性エッチングは、前記第2構造の前記第2ソース電極側側面上にサイドウォール絶縁膜を残しつつ、前記第2ソース電極形成用コンタクトホールを形成する請求項1に記載の半導体装置の製造方法。

【請求項3】

さらに、前記第2絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する請求項1または2に記載の半導体装置の製造方法。

【請求項4】

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第2絶縁膜を異方性エッチングして、前記第1構造の側面上及び前記第2構造の側面上にサイドウォール絶縁膜を形成する工程と、

前記第1構造、前記第1構造の側面上の前記サイドウォール絶縁膜、前記第2構造、及び、前記第2構造の側面上の前記サイドウォール絶縁膜を覆って、前記第2GaN系半導体層上方に、第3絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有するマスクを用いて、前記第3絶縁膜をエッチングすることにより、前記第1開口内において、前記第1ゲート電極及び前記サイドウォール絶縁膜を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

【請求項5】

さらに、前記第3絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する請求項4に記載の半導体装置の製造方法。

【請求項1】

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有する第1マスクを用いて、前記第2絶縁膜を異方性エッチングすることにより、前記第1開口内において、前記第1構造の側面上にサイドウォール絶縁膜を残しつつ、前記第1ゲート電極を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

【請求項2】

前記第1ソース電極形成用コンタクトホール、前記第1ドレイン電極形成用コンタクトホール、前記第2ソース電極形成用コンタクトホール、及び前記第2ドレイン電極形成用コンタクトホールを形成する工程において、

前記第1マスクは、前記第2開口が前記第2ゲート電極の形成領域上を一部露出し、

前記第2絶縁膜の異方性エッチングは、前記第2構造の前記第2ソース電極側側面上にサイドウォール絶縁膜を残しつつ、前記第2ソース電極形成用コンタクトホールを形成する請求項1に記載の半導体装置の製造方法。

【請求項3】

さらに、前記第2絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する請求項1または2に記載の半導体装置の製造方法。

【請求項4】

基板上方に、第1GaN系半導体層を形成する工程と、

前記第1GaN系半導体層上に、前記第1GaN系半導体層とバンドギャップの異なる第2GaN系半導体層を形成する工程と、

前記第2GaN系半導体層上方に、ゲート電極層を形成する工程と、

前記ゲート電極層上に、第1絶縁膜を形成する工程と、

前記ゲート電極層及び前記第1絶縁膜をパターニングして、前記第2GaN系半導体層上方の第1領域に、第1ゲート電極と前記第1絶縁膜の第1部分とが積層された第1構造を形成し、前記第2GaN系半導体層上方の第2領域に、第2ゲート電極と前記第1絶縁膜の第2部分とが積層された第2構造を形成する工程と、

前記第1構造及び前記第2構造を覆って、前記第2GaN系半導体層上方に、第2絶縁膜を形成する工程と、

前記第2絶縁膜を異方性エッチングして、前記第1構造の側面上及び前記第2構造の側面上にサイドウォール絶縁膜を形成する工程と、

前記第1構造、前記第1構造の側面上の前記サイドウォール絶縁膜、前記第2構造、及び、前記第2構造の側面上の前記サイドウォール絶縁膜を覆って、前記第2GaN系半導体層上方に、第3絶縁膜を形成する工程と、

前記第1ゲート電極とその両側の領域を露出する第1開口、前記第2ゲート電極を挟んで一方側と他方側にそれぞれ配置された第2開口及び第3開口を有するマスクを用いて、前記第3絶縁膜をエッチングすることにより、前記第1開口内において、前記第1ゲート電極及び前記サイドウォール絶縁膜を挟んで一方側に第1ソース電極形成用コンタクトホールを形成し、他方側に第1ドレイン電極形成用コンタクトホールを形成し、前記第2開口内に、第2ソース電極形成用コンタクトホールを形成し、前記第3開口内に、第2ドレイン電極形成用コンタクトホールを形成する工程と、

前記第1ソース電極形成用コンタクトホール内に第1ソース電極を形成し、前記第1ドレイン電極形成用コンタクトホール内に第1ドレイン電極を形成し、前記第2ソース電極形成用コンタクトホール内に第2ソース電極を形成し、前記第2ドレイン電極形成用コンタクトホール内に第2ドレイン電極を形成する工程と

を有し、

前記第1ゲート電極から前記第1ドレイン電極までの距離に比べて、前記第2ゲート電極から前記第2ドレイン電極までの距離が長い半導体装置の製造方法。

【請求項5】

さらに、前記第3絶縁膜上方の、前記第2ゲート電極と前記第2ドレイン電極との間に、フィールドプレートを形成する工程を有する請求項4に記載の半導体装置の製造方法。

【図1−1】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2−1】

【図2−2】

【図3−1】

【図3−2】

【図3−3】

【図4−1】

【図4−2】

【図4−3】

【図4−4】

【図5−1】

【図5−2】

【図6−1】

【図6−2】

【図6−3】

【図7−1】

【図7−2】

【図7−3】

【図8】

【図9】

【図10】

【図11】

【図12】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2−1】

【図2−2】

【図3−1】

【図3−2】

【図3−3】

【図4−1】

【図4−2】

【図4−3】

【図4−4】

【図5−1】

【図5−2】

【図6−1】

【図6−2】

【図6−3】

【図7−1】

【図7−2】

【図7−3】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−98374(P2013−98374A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240126(P2011−240126)

【出願日】平成23年11月1日(2011.11.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月1日(2011.11.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]