半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

NAND型フラッシュメモリでは、STI(Shallow Trench Isolation)構造の素子分離方式が用いられている。このSTI構造として、シリコン酸化膜が用いられている。しかし、素子パターンの微細化に伴い、STIのシリコン酸化膜を介して隣接する浮遊ゲート間で電流が漏れてしまうYupin/Enda効果が大きくなる。この漏れ電流により、メモリの読み出しおよび書き込みにおいて誤動作が生じ、特に素子サイズが30nm世代以降において顕著になる。このようなYupin/Enda効果を低減するために、STIとして種々の材料を選択したり、構造を提案したりすることで、STI中の漏れ電流を低減している。

【0003】

例えば、上記問題を解決する方法として、STIに中空構造(エアギャップ)を用いる方法が挙げられる。エアギャップは、その内部が空気であるため、絶縁性に優れている。また、誘電率が1であるため、漏れ電流を極限まで低減することができる。

【0004】

しかし、エアギャップの形成において、様々な問題が生じる。例えば、CVD(Chemical Vapor Deposition)法を用いて埋め込み特性の悪い膜を溝に堆積させることで、溝を埋め込まないようにエアギャップを形成する方法がある。しかし、この方法では、溝の側壁に膜が付着することで、メモリの電荷保持特性に悪影響を与える。また、エアギャップの形成が不十分となり、十分な絶縁性が得られない。

【0005】

これに対し、一旦溝を犠牲膜で完全に埋め込み、電極間絶縁膜等を形成した後、一部を開口してエッチングにより埋め込まれた犠牲膜を除去する方法などが提案されている。この犠牲膜として、PSZ(ポリシラザン)膜が用いられる。しかし、PSZ膜は、比較的エッチング耐性が高いため、エアギャップとなる大きな空洞を形成しにくいという問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−250656号公報

【特許文献2】特開2010−27922号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

デバイス特性の向上を図る半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0008】

本実施形態によれば、半導体装置の製造方法が提供される。前記半導体装置の製造方法においては、半導体層上に、トンネル絶縁膜を形成する。前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する。前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する。前記溝内の下部側に、第1犠牲膜を埋め込む。前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりも高密度な第2犠牲膜を形成する。前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する。前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する。前記第2導電膜を加工することにより、前記第2犠牲膜を露出する。前記第1犠牲膜および前記第2犠牲膜を除去する。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る半導体装置の構造を示す平面図。

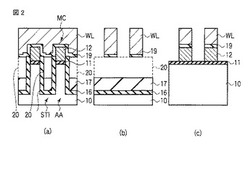

【図2】第1の実施形態に係る半導体装置の構造を示す断面図

【図3】第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図4】図3に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図5】図4に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図6】図5に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図7】図6に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図8】図7に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図9】図8に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図10】図9に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図11】図10に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図12】図11に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図13】図12に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図14】図13に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図15】図14に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図16】第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図17】図16に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図18】図17に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図19】図18に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図20】第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図21】図20に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図22】図21に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図23】図22に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図24】図23に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図25】図24に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図26】図25に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図27】図26に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【発明を実施するための形態】

【0010】

本実施形態を以下に図面を参照して説明する。図面において、同一部分には同一の参照符号を付す。また、重複する説明は、必要に応じて行う。

【0011】

<第1の実施形態>

図1乃至図15を用いて、第1の実施形態に係る半導体装置について説明する。第1の実施形態は、STIとして設けられた溝15内に、HSQ(ハイドロジェンシルセスキオキサン)膜17と、その上部に位置し、HSQ膜17よりもエッチング耐性の強い酸化膜18とを形成した後、これらを除去することでエアギャップ20を形成する例である。

【0012】

[第1の実施形態の構造]

以下に、図1および図2を用いて、第1の実施形態に係る半導体装置の構造について説明する。

【0013】

図1は、第1の実施形態に係る半導体装置の構造を示す平面図である。

【0014】

図1に示すように、半導体装置は、複数のビット線BLおよびこれらに直交する複数のワード線WLを備える。

【0015】

複数のビット線BLと複数のワード線WLとの各交差位置には、メモリセルMCが形成される。メモリセルMCは、ビット線方向およびこれに直交するワード線方向に、所定間隔を有して配置される。すなわち、メモリセルMCは、ビット線方向およびワード線方向にマトリクス状に配置される。

【0016】

メモリセルMCは、ビット線方向に沿った素子領域(AA:Active Area)に形成される。また、ワード線方向に沿って隣接するメモリセルMCは、ビット線方向に沿って形成される素子分離領域(STI)によって区画される。

【0017】

図2は、第1の実施形態に係る半導体装置の構造を示す断面図である。より具体的には、図2(a)は図1のA−A線に沿った断面図であり、図2(b)は図1のB−B線に沿った断面図であり、図2(c)は図1のC−C線に沿った断面図である。すなわち、図2(a)はワード線方向に沿ったメモリセルMCの断面図であり、図2(b)はビット線方向に沿った素子分離領域の断面図であり、図2(c)はワード線方向に沿った素子領域の断面図である。ここで、図2において、ビット線BLは省略している。

【0018】

図2(a)乃至(c)に示すように、第1の実施形態に係る半導体装置は、半導体層10上において、メモリセルMCが形成された素子領域(AA)と、素子領域を区画するSTI構造からなる素子分離領域とで構成される。

【0019】

半導体層10は、例えばシリコン基板であるが、これに限らず、SOI(Silicon On Insulating)基板でもよい。半導体層10は、素子領域と素子分離領域とで段差を有する。より具体的には、半導体層10は、素子領域において上段面を有し、素子分離領域において下段面を有する。すなわち、半導体層10は、素子分離領域において溝15を有する。この溝15は、ワード線方向における幅が例えば30nm以下であり、積層方向における深さが例えば200nm以上500nm以下であるが、これに限らず、デバイス構造やその世代によって適宜異なる。

【0020】

素子領域におけるメモリセルMCは、半導体層10上に形成されたトンネル絶縁膜11、浮遊ゲート電極12、電極間絶縁膜19、およびワード線WL(制御ゲート電極)で構成される。

【0021】

素子領域において、トンネル絶縁膜11は、半導体層10上に形成される。トンネル絶縁膜11は、例えばシリコン酸化膜またはシリコン窒化膜、もしくはこれらの積層膜で構成される。トンネル絶縁膜11の膜厚は、例えば8nm以下である。

【0022】

浮遊ゲート電極12は、トンネル絶縁膜11上に形成される。浮遊ゲート電極12は、例えばポリシリコン膜で構成されるが、これに限らず、Wシリサイド膜またはCoシリサイド膜で構成されてもよい。浮遊ゲート電極12がポリシリコン膜である場合、その膜厚は例えば100nmである。一方、浮遊ゲート電極12がWシリサイド膜またはCoシリサイド膜である場合、その膜厚は例えば100nm以上200nm以下である。この浮遊ゲート電極12は、電荷蓄積膜として機能する。

【0023】

電極間絶縁膜19は、浮遊ゲート電極12上に形成される。すなわち、電極間絶縁膜19は、浮遊ゲート電極12の上面および上側面を覆うように形成される。電極間絶縁膜19は、例えばシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜が順に形成された積層膜で構成されるが、これに限らない。シリコン酸化膜またはシリコン窒化膜の単層膜で構成されてもよく、もしくはこれらが交互に4層以上形成された積層膜で構成されてもよい。電極間絶縁膜19の膜厚は、例えば20nm程度である。

【0024】

ワード線WLとなる制御ゲート電極は、電極間絶縁膜19上に形成される。制御ゲート電極は、例えば、ポリシリコン膜およびW膜が順に形成された積層膜で構成されるが、これに限らない。ポリシリコン膜またはW膜の単層膜で構成されてもよく、もしくはWシリサイド膜またはCoシリサイド膜で構成されてもよい。制御ゲート電極の膜厚は、例えば50nm程度である。

【0025】

一方、素子分離領域において、半導体層10に形成された溝15内にSTI構造が形成される。図1(a)に示すように、STI構造は、ワード線方向に隣接するメモリセルMC間(浮遊ゲート電極12間)に形成され、ビット線方向に延在する。このSTI構造は、ライナー膜16およびエアギャップ20で構成される。

【0026】

ライナー膜16は、溝15の内面上に形成される。すなわち、ライナー膜16は、溝15内における半導体層10の側面上および底面上、トンネル絶縁膜11の側面上、および浮遊ゲート電極12の下側面上に形成される。浮遊ゲート電極12の下側面上に形成されたライナー膜16は、浮遊ゲート電極12の上側面上に形成された電極間絶縁膜19と接する。ライナー膜16は、例えばTEOS膜またはHTO膜で構成される。ライナー膜16の膜厚は、例えば1nm以上20nm以下である。このライナー膜16は、STI構造の側壁を保護する保護膜として機能する。

【0027】

エアギャップ20は、溝15内のライナー膜16上に形成される。すなわち、エアギャップ20は、溝15内におけるライナー膜16の底面上および側面上に形成される。図2(a)および(b)に示すように、エアギャップ20の上面上には、電極間絶縁膜19および図示せぬ層間絶縁膜が形成される。すなわち、エアギャップ20は、ワード線方向における側面がライナー膜19に覆われ、上面が電極間絶縁膜19および層間絶縁膜に覆われる。また、エアギャップ20の上面は、トンネル絶縁膜11の上面よりも高く浮遊ゲート電極12の上面よりも低い。すなわち、隣接する浮遊ゲート電極12間の少なくとも一部に、エアギャップ20が形成される。なお、隣接する浮遊ゲート電極12間の領域のうち、エアギャップ20が形成される領域をできる限り大きくすることが望ましい。

【0028】

このエアギャップ20は、中空構造であり、例えば空気で満たされる。エアギャップ20がワード線方向に隣接するメモリセルMC間(浮遊ゲート電極12間)に形成されることで、浮遊ゲート電極12間の絶縁性を向上させ、漏れ電流を抑制することができる。

【0029】

なお、本実施形態において、エアギャップ20の下部に、HSQ酸化膜17が形成されてもよい。すなわち、溝15内におけるライナー膜16の底面上および下側側面上にHSQ酸化膜17が形成され、ライナー膜16の上側側面上にエアギャップ20が形成される。このHSQ酸化膜17は、後述する製造工程において、犠牲膜として溝15内に形成され、除去する際に残存したものである。

【0030】

このHSQ酸化膜17は、多くのボイドを含む。このため、HSQ酸化膜17は、後述するPHPS(ペルヒドロポリシラザン)酸化膜やCVD法またはALD(Atomic Layer Deposition)法により形成されるシリコン酸化膜よりも低密度の膜である。

【0031】

[第1の実施形態の製造方法]

以下に、図3乃至図15を用いて、第1の実施形態に係る半導体装置の製造方法について説明する。

【0032】

図3乃至図15は、第1の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図3(a)乃至図15(a)は図1のA−A線に沿った断面図であり、図3(b)乃至図15(b)は図1のB−B線に沿った断面図であり、図3(c)乃至図15(c)は図1のC−C線に沿った断面図である。

【0033】

まず、図3(a)乃至(c)に示すように、半導体層10上に、例えば熱酸化法により、シリコン酸化膜で構成されるトンネル絶縁膜11が形成される。なお、トンネル絶縁膜11は、例えばCVD法またはALD法で形成されるシリコン酸化膜またはシリコン窒化膜、もしくはこれらの積層膜で構成されてもよい。トンネル絶縁膜11の膜厚は、例えば8nm以下である。

【0034】

次に、トンネル絶縁膜11上に、例えばCVD法またはALD法により、浮遊ゲート電極12が形成される。浮遊ゲート電極12は、例えば、膜厚が100nmのポリシリコン膜、または膜厚が100nm以上200nm以下のWシリサイド膜もしくはCoシリサイド膜で構成される。

【0035】

次に、浮遊ゲート電極12上に、例えばLP(Low Pressure)CVD法により、ストッパー膜13が形成される。ストッパー膜13は、例えば、膜厚が200nmのシリコン窒化膜、または膜厚が100nm以上200nm以下のポリシリコン膜で構成される。

【0036】

次に、ストッパー膜13上に、例えばLPCVD法により、ハードマスク14が形成される。ハードマスク14は、例えば膜厚が300nmのTEOS膜で構成される。

【0037】

次に、図4(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ハードマスク14をマスクとして、ストッパー膜13、浮遊ゲート電極膜12、トンネル絶縁膜11、および半導体層10が加工される。これにより、ストッパー膜13、浮遊ゲート電極膜12、およびトンネル絶縁膜11を貫通し、半導体層10に達する溝15が形成される。溝15は、幅が例えば30nm以下であり、半導体層10内における深さが例えば200nm以上500nm以下であるが、これに限らず、デバイス構造やその世代によって適宜異なる。

【0038】

なお、このとき、ハードマスク14も一部エッチングされるが、ストッパー膜13上に残存する。

【0039】

次に、図5(a)乃至(c)に示すように、例えばCVD法により、溝15の内面上に、ライナー膜16が形成される。すなわち、ライナー膜16は、溝15内における半導体層10の側面上および底面上、トンネル絶縁膜11の側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、ハードマスク14の側面上、溝15外におけるハードマスク14の上面上に形成される。ライナー膜16は、例えばTEOS膜またはHTO膜で構成される。ライナー膜16の膜厚は、例えば1nm以上20nm以下である。

【0040】

ここまでの工程は、上記方法に限らず、公知の種々の方法を用いて行うことができる。

【0041】

次に、STI構造としてエアギャップ20の形成工程が行われる。以下に、本実施形態に係るエアギャップ20の形成工程について詳説する。

【0042】

まず、図6(a)乃至(c)に示すように、塗布法により、全面が覆われるようにライナー膜16上に、犠牲膜となるHSQ膜17が形成される。すなわち、HSQ膜17は、溝15内におけるライナー膜16の底面上および側面上、溝15外におけるライナー膜16の上面上に形成される。これにより、溝15内に、HSQ膜17が埋め込まれる。HSQ膜17は、塗布法により薄膜形成が可能であり、埋め込み特性に優れている。このため、溝15の幅が微細化されたとしてもその内部をHSQ膜17により埋め込むことができる。

【0043】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、HSQ膜17が酸化され、HSQ酸化膜17に転換される。このとき、熱処理は、例えば230℃以上900℃以下で行われる。さらに、窒素雰囲気中で熱処理することにより、HSQ酸化膜17を硬化させてもよい。

【0044】

なお、本明細書において、HSQ酸化膜17は、HSQ膜17から誘導された酸化膜を示す。また、以下において、HSQ酸化膜17を単にHSQ膜17と称する。

【0045】

このように形成されたHSQ膜17は、多くのボイドを含む。このため、HSQ膜17は、後述するPHPS膜やCVD法またはALD法により形成される酸化膜よりも低密度である(膜密度が低い)。また、HSQ膜17は、PHPS膜やCVD法またはALD法により形成される酸化膜よりもエッチング耐性が弱い(エッチングレートが高い)。

【0046】

次に、図7(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMP(Chemical Mechanical Polishing)が行われる。これにより、上部のHSQ膜17、上部のライナー膜16、およびハードマスク14が除去され、HSQ膜17、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0047】

次に、図8(a)乃至(c)に示すように、HSQ膜17がエッチングされる。このとき、HSQ膜17の上面がトンネル絶縁膜11の上面から下面の高さ付近になるように、HSQ膜17が加工されるが、これに限らない。後述するHSQ膜17の除去工程を考慮すると、HSQ膜17の上面がトンネル絶縁膜11の上面よりも高くなるように加工されることが望ましい。すなわち、溝15内の下部側がHSQ膜17によって埋め込まれる。

【0048】

このとき、ライナー膜16も同時にエッチングされてもよい。すなわち、ストッパー膜13および浮遊ゲート電極12の側面が露出してもよい。また、ライナー膜16のエッチング耐性は、HSQ膜17のエッチング耐性よりも強い。このため、ライナー膜16の上面がHSQ膜17の上面よりも高くなるように加工される。

【0049】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。ウェットエッチングの場合、エッチング液として例えばDHF(dilute hydrofluoric acid)が用いられる。

【0050】

次に、図9(a)乃至(c)に示すように、全面が覆われるように、犠牲膜となる酸化膜18が形成される。すなわち、酸化膜18は、溝15内におけるHSQ膜17の上面上、ライナー膜16の上面上および側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、溝15外におけるストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、酸化膜18が埋め込まれる。

【0051】

酸化膜18は、例えばCVD法またはALD法によって形成されるシリコン酸化膜で構成されてもよいが、埋め込み特性の観点から、塗布法により形成されるPHPS膜で構成されることが望ましい。酸化膜18としてPHPS膜が形成される場合、以下のように形成される。

【0052】

まず、塗布法により、PHPS膜が溝15内に埋め込まれる。PHPS膜は、塗布法により薄膜形成が可能であり、埋め込み特性に優れている。このため、溝15の幅が微細化されたとしてもその内部をPHPS膜により埋め込むことができる。その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜が酸化され、PHPS酸化膜に転換される。この熱処理は、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10がライナー膜16に覆われていない場合、これらが酸化してしまうことを防ぐために比較的低温、例えば230℃以上500℃以下で行われる。さらに、窒素雰囲気中で熱処理することにより、PHPS酸化膜を硬化させてもよい。このように、埋め込み特性に優れたPHPS酸化膜が形成される。

【0053】

このように形成された酸化膜18(シリコン酸化膜またはPHPS酸化膜)は、その下部に位置するHSQ膜17よりも高密度な膜である(膜密度が高い)。また、酸化膜18は、HSQ膜17よりもエッチング耐性が強い(エッチングレートが低い)。

【0054】

次に、図10(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部の酸化膜18が除去され、酸化膜18およびストッパー膜13の上面が平坦化される。

【0055】

次に、図11(a)乃至(c)に示すように、酸化膜18がエッチングされる。このとき、酸化膜18の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、酸化膜18が浮遊ゲート電極12側部に位置するように加工されることが望ましい。また、酸化膜18の上面がライナー膜16の上面よりも高くなってもよい。すなわち、ライナー膜16は、酸化膜18に覆われてもよい。また、溝15内に形成される酸化膜18は、その表面形状や高さの均一性が得られる程度で、できる限り少ないほうが望ましい。

【0056】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。ウェットエッチングの場合、エッチング液として例えばDHFが用いられる。

【0057】

次に、図12(a)乃至(c)に示すように、例えばリン酸水溶液を用いたウェットエッチングにより、ストッパー膜13が除去される。これにより、浮遊ゲート電極12の上面が露出する。

【0058】

次に、図13(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、電極間絶縁膜19が形成される。電極間絶縁膜19は、例えばシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜が順に形成された積層膜で構成されるが、これに限らない。シリコン酸化膜またはシリコン窒化膜の単層膜で構成されてもよく、もしくはこれらが交互に4層以上形成された積層膜で構成されてもよい。電極間絶縁膜19の膜厚は、例えば20nm程度である。

【0059】

このとき、電極間絶縁膜19は、酸化膜18上にも形成される。言い換えると、酸化膜18は、電極間絶縁膜19に覆われる。ここで、酸化膜18は、HSQ膜17よりも高密度に形成される膜である。このため、複数の溝15において、酸化膜18の表面形状や高さを均一にさせることができる。これにより、電極間絶縁膜19の膜厚や構造を均一に形成することができる。

【0060】

次に、図14(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、ワード線WLとなる制御ゲート電極が形成される。制御ゲート電極は、例えば、ポリシリコン膜およびW膜が順に形成された積層膜で構成されるが、これに限らない。ポリシリコン膜またはW膜の単層膜で構成されてもよく、もしくはWシリサイド膜またはCoシリサイド膜で構成されてもよい。制御ゲート電極の膜厚は、例えば50nm程度である。

【0061】

次に、図15(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ビット線方向に沿ってワード線WLが加工される。このとき、エッチングは、トンネル絶縁膜11に達するまで行われる。すなわち、トンネル絶縁膜11よりも上方に位置する各層が加工される。より具体的には、ワード線WL、電極間絶縁膜19、および浮遊ゲート電極12が加工される。

【0062】

このとき、前工程において、少なくとも酸化膜18の一部がトンネル絶縁膜11よりも上方に位置している。このため、酸化膜18の一部も同時に加工され、少なくとも酸化膜18の一部が露出する。なお、図15において、HSQ膜17の一部もトンネル絶縁膜11より上方に位置する。このため、酸化膜18を貫通し、HSQ膜17の一部に達するように加工される。これにより、酸化膜18およびHSQ膜17は、その一部が露出する。

【0063】

次に、図2(a)乃至(c)に示すように、例えば等方的なウェットエッチングにより、HSQ膜17および酸化膜18が除去される。エッチング液として、例えばDHFが用いられる。これにより、溝15内のライナー膜16上に、エアギャップ20が形成される。

【0064】

このとき、酸化膜18およびHSQ膜17の露出した表面から除去されていく。このため、HSQ膜17が露出していない場合、エッチング耐性の強い酸化膜18を除去した後でなければHSQ膜17を除去できず、HSQ膜17の除去が比較的困難になる。このため、前工程において酸化膜18だけでなく、HSQ膜17の表面も露出していることが望ましい。

【0065】

なお、HSQ膜17は、上部側から除去されていくが、下部側まで全て除去しなくてもよい。隣接する浮遊ゲート電極12間でYupin/Enda効果を抑制できる程度まで除去すればよい。また、このとき、ライナー膜16も除去され得るが、残存してもよい。

【0066】

その後、例えばCVD法により、全面に、例えばTEOSで構成される図示せぬ層間絶縁膜が形成される。この層間絶縁膜は、CVD法等の埋め込み特性の低い方法により形成されるため、エアギャップ20内には形成されない。

【0067】

このようにして、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0068】

[第1の実施形態の効果]

上記第1の実施形態によれば、STIとして設けられた溝15内に、犠牲膜として、膜密度が小さくかつエッチング耐性の弱いHSQ膜17を形成した後、その上部にHSQ膜17よりも膜密度が大きくかつエッチング耐性の強い酸化膜18を形成する。その後、これらを電極間絶縁膜19およびワード線WLで覆った後、一部を露出して除去することで、STI構造としてエアギャップ20を形成する。

【0069】

このように、犠牲膜として膜密度が小さくかつエッチング耐性の弱いHSQ膜17を用いることで、犠牲膜の除去を容易に行うことができる。すなわち、犠牲膜のエッチング液による溶解性を向上させることができ、エアギャップ20となるより大きな空洞を形成することができる。したがって、隣接する浮遊ゲート電極12間のYupin/Enda効果を低減し、デバイス特性の向上を図ることができる。

【0070】

また、第1の実施形態によれば、犠牲膜として、HSQ膜17だけでなく、HSQ膜17上に酸化膜18が形成される。酸化膜18は、HSQ膜17よりもエッチング耐性が強く、膜密度が大きい膜である。このため、複数の溝15において、酸化膜18の表面形状や高さの均一性を図ることができる。すなわち、その上部に形成される電極間絶縁膜19の膜厚や構造を均一に形成することができ、デバイスの信頼性を向上させることできる。

【0071】

<第2の実施形態>

図16乃至図19を用いて、第2の実施形態に係る半導体装置について説明する。第2の実施形態は、第1の実施形態における酸化膜18としてPHPS膜21が形成される場合であり、PHPS膜21の形成工程において、浮遊ゲート電極12の表面がライナー膜16で覆われる例である。なお、第2の実施形態において、上記第1の実施形態と同様の点については説明を省略し、主に異なる点について説明する。

【0072】

[第2の実施形態の製造方法]

以下に、図16乃至図19を用いて、第2の実施形態に係る半導体装置の製造方法について説明する。

【0073】

図16乃至図19は、第2の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図16(a)乃至図19(a)は図1のA−A線に沿った断面図であり、図16(b)乃至図19(b)は図1のB−B線に沿った断面図であり、図16(c)乃至図19(c)は図1のC−C線に沿った断面図である。

【0074】

まず、第1の実施形態と同様に、図3乃至図7の工程が行われる。すなわち、溝15を埋め込むようにHSQ膜17が形成された後、HSQ膜17、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0075】

次に、図16(a)乃至(c)に示すように、HSQ膜17がエッチングされる。このとき、HSQ膜17の上面がトンネル絶縁膜11の上面から下面の高さ付近になるように、HSQ膜17が加工されるが、これに限らない。後述するHSQ膜17の除去工程を考慮すると、HSQ膜17の上面がトンネル絶縁膜11の上面よりも高くなるように加工されることが望ましい。

【0076】

このとき、第2の実施形態において、ライナー膜16は、エッチングされない。すなわち、ストッパー膜13および浮遊ゲート電極12の側面がライナー膜16に覆われたまま露出しないように、エッチング条件が調整される。

【0077】

このエッチング条件として、エッチング液に例えばアルカリ溶液を用いたウェットエッチングが挙げられる。HSQ膜17は、ライナー膜16よりもアルカリ溶液に対するエッチング耐性が弱い。このため、アルカリ溶液によるウェットエッチングを行うことで、HSQ膜17のみをエッチングすることができる。

【0078】

次に、図17(a)乃至(c)に示すように、塗布法により、全面が覆われるように、犠牲膜となるPHPS膜21が形成される。すなわち、PHPS膜21は、溝15内におけるHSQ膜17の上面上、ライナー膜16の側面上、溝15外におけるライナー膜16の上面上、ストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、PHPS膜21が埋め込まれる。

【0079】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜21が酸化され、PHPS酸化膜21に転換される。

【0080】

なお、本明細書において、PHPS酸化膜21は、PHPS膜21から誘導された酸化膜を示す。また、以下において、PHPS酸化膜21を単にPHPS膜21と称する。

【0081】

このとき、熱処理は、例えば230℃以上900℃以下で行われる。ここで、第2の実施形態において、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10は、ライナー膜16で覆われている。このため、PHPS膜21の酸化工程(熱処理)を比較的高温で行っても、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10が酸化されることはない。

【0082】

次に、図18(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部のPHPS膜21が除去され、PHPS膜21、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0083】

次に、図19(a)乃至(c)に示すように、PHPS膜21がエッチングされる。このとき、PHPS膜21の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、PHPS膜21が浮遊ゲート電極12側部に位置するように加工されることが望ましい。

【0084】

このとき、ライナー膜16も同時に形成される。すなわち、ストッパー膜13および浮遊ゲート電極12の側面が露出する。

【0085】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。

【0086】

その後、第1の実施形態と同様に、図12乃至図15、および図2の工程が行われ、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0087】

[第2の実施形態の効果]

上記第2の実施形態によれば、第1の実施形態と同様の効果を得ることができる。

【0088】

さらに、第2の実施形態では、溝15にHSQ膜17を埋め込んだ後にエッチングする際、エッチング条件を調整することにより、ライナー膜16を除去しない。これにより、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10の側面をライナー膜16で覆ったまま、PHPS膜21の塗布および酸化工程を行うことができる。すなわち、PHPS膜21の酸化工程における熱処理によって、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10が酸化されることを抑制することができる。

【0089】

<第3の実施形態>

図20乃至図27を用いて、第3の実施形態に係る半導体装置について説明する。第3の実施形態は、第1の実施形態における酸化膜18としてPHPS膜21が形成される場合であり、HSQ膜17とPHPS膜21との間に高密度のシリコン酸化膜22を形成する例である。なお、第3の実施形態において、上記各実施形態と同様の点については説明を省略し、主に異なる点について説明する。

【0090】

[第3の実施形態の製造方法]

以下に、図20乃至図27を用いて、第3の実施形態に係る半導体装置の製造方法について説明する。

【0091】

図20乃至図27は、第3の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図20(a)乃至図27(a)は図1のA−A線に沿った断面図であり、図20(b)乃至図27(b)は図1のB−B線に沿った断面図であり、図20(c)乃至図27(c)は図1のC−C線に沿った断面図である。

【0092】

まず、第1の実施形態と同様に、図3乃至図8の工程が行われる。すなわち、溝15を埋め込むようにHSQ膜17が形成された後、エッチングされることで、溝15の下部側にHSQ膜17が埋め込まれる。

【0093】

次に、図20(a)乃至(c)に示すように、例えばALD法またはCVD法により、HSQ膜17上に、シリコン酸化膜22が形成される。すなわち、シリコン酸化膜22は、溝15内におけるHSQ膜17の上面上に形成される。これにより、HSQ膜17の上面は、シリコン酸化膜22に覆われる。

【0094】

このとき、シリコン酸化膜22は、HSQ膜17以外の膜の全面にも形成される。すなわち、シリコン酸化膜22は、溝15内におけるライナー膜16の上面上および側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、溝15外におけるストッパー膜13の上面上にも形成される。

【0095】

なお、本明細書において、犠牲膜としてのシリコン酸化膜22は、塗布法ではなく、例えばCVD法またはALD法等の堆積法によって形成される酸化膜を示す。

【0096】

シリコン酸化膜22の膜厚は、例えば3nm以下である。しかし、これに限らず、シリコン酸化膜22の膜厚は、後工程においてPHPS膜21がHSQ膜のボイドに侵入しない程度に大きく、犠牲膜としてエッチングしやすい程度に小さければよい。

【0097】

このように形成されたシリコン酸化膜22は、その下部に位置するHSQ膜17および後にその上部に形成されるPHPS膜21よりも高密度な膜である。また、シリコン酸化膜22は、HSQ膜17およびPHPS膜21よりもエッチング耐性が強い。

【0098】

なお、シリコン酸化膜22は、ライナー膜16と同様の効果を有する。すなわち、後述するPHPS膜21の酸化工程において、浮遊ゲート電極12等がシリコン酸化膜22で覆われることにより浮遊ゲート電極12等の酸化を抑制することができる。また、上記観点から、シリコン酸化膜22は浮遊ゲート電極12等の表面に残すことが望ましいが、除去してもよい。

【0099】

次に、図21(a)乃至(c)に示すように、塗布法により、全面が覆われるように、犠牲膜となるPHPS膜21が形成される。すなわち、PHPS膜21は、溝15内におけるシリコン酸化膜22の上面上、ライナー膜16の側面上、溝15外におけるライナー膜16の上面上、ストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、PHPS膜21が埋め込まれる。

【0100】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜21が酸化される。この熱処理は、浮遊ゲート電極12およびトンネル絶縁膜11がライナー膜16(および/またはシリコン酸化膜22)に覆われていない場合、例えば230℃以上500℃以下で行われ、覆われている場合、例えば230℃以上900℃以下で行われる。

【0101】

このように形成されたPHPS膜21は、その下部に位置するシリコン酸化膜22よりも低密度な膜であり、さらに下部に位置するHSQ膜よりも高密度な膜である。また、酸化膜18は、シリコン酸化膜22よりもエッチング耐性が弱く、HSQ膜17よりもエッチング耐性が強い。

【0102】

次に、図22(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部のPHPS膜21が除去され、PHPS膜21、シリコン酸化膜22およびストッパー膜13の上面が平坦化される。

【0103】

次に、図23(a)乃至(c)に示すように、PHPS膜21がエッチングされる。このとき、PHPS膜21の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、PHPS膜21が浮遊ゲート電極12側部に位置するように加工されることが望ましい。

【0104】

このとき、シリコン酸化膜22もエッチングされる。これにより、シリコン酸化膜22が浮遊ゲート電極12の側面上から除去されることが望ましいが、一部残存してもよい。

【0105】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。

【0106】

次に、図24(a)乃至(c)に示すように、例えばリン酸水溶液を用いたウェットエッチングにより、ストッパー膜13が除去される。これにより、浮遊ゲート電極12の上面が露出する。

【0107】

次に、図25(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、電極間絶縁膜19が形成される。このとき、電極間絶縁膜19は、PHPS膜21上にも形成される。

【0108】

次に、図26(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、ワード線WLとなる制御ゲート電極が形成される。

【0109】

次に、図27(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ビット線方向に沿ってワード線WLが加工される。このとき、エッチングは、トンネル絶縁膜11に達するまで行われる。

【0110】

このとき、前工程において、少なくともPHPS膜21の一部がトンネル絶縁膜11よりも上方に位置している。このため、PHPS膜21の一部も同時に加工され、少なくともPHPS膜21の一部が露出する。なお、図15において、シリコン酸化膜22およびHSQ膜17の一部もトンネル絶縁膜11より上方に位置する。このため、PHPS膜21およびシリコン酸化膜22を貫通し、HSQ膜17の一部に達するように加工される。これにより、PHPS膜21、シリコン酸化膜22およびHSQ膜17は、その一部が露出する。

【0111】

次に、図2(a)乃至(c)に示すように、例えば等方的なウェットエッチングにより、HSQ膜17およびPHPS膜21が除去される。エッチング液として、例えばDHFが用いられる。これにより、溝15内のライナー膜16上に、エアギャップ20が形成される。

【0112】

ここで、シリコン酸化膜22は、HSQ膜17およびPHPS膜21よりもエッチング耐性の強い膜である、しかし、シリコン酸化膜22は、薄く(例えば、3nm以下で)形成されているため、犠牲膜として機能し、HSQ膜17およびPHPS膜21と同時にエッチングされて除去される。

【0113】

このようにして、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0114】

[第3の実施形態の効果]

上記第3の実施形態によれば、第1の実施形態と同様の効果を得ることができる。

【0115】

ところで、HSQ膜17は、ボイドを多く含む膜であり、低密度な膜である。このHSQ膜17上に塗布法によりPHPS膜21を形成した場合、埋め込み特性の高いPHPS膜21はHSQ膜17のボイド内に侵入する恐れがある。HSQ膜17にPHPS膜21が侵入した場合、高密度かつエッチング耐性の強い膜になってしまう。その結果、これらの膜は、エアギャップ20の形成のための犠牲膜として除去しにくい膜になってしまう。

【0116】

これに対し、第3の実施形態では、HSQ膜17とPHPS膜21との界面に、薄いシリコン酸化膜22が形成される。このシリコン酸化膜22は、ALD法またはCVD法により形成される埋め込み特性が低く、高密度な膜である。シリコン酸化膜22は、埋め込み特性が低いためにHSQ膜17のボイドに侵入することはなく、高密度な膜であるためにPHPS膜21がHSQ膜17に侵入することを防ぐことができる。

【0117】

その他、本発明は、上記各実施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題が解決でき、発明の効果の欄で述べられている効果が得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

【符号の説明】

【0118】

10…半導体層、11…トンネル絶縁膜、12…浮遊ゲート電極、15…溝、16…ライナー膜、17…HSQ膜、18…酸化膜、19…電極間絶縁膜、21…PHPS膜、22…シリコン酸化膜。

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

NAND型フラッシュメモリでは、STI(Shallow Trench Isolation)構造の素子分離方式が用いられている。このSTI構造として、シリコン酸化膜が用いられている。しかし、素子パターンの微細化に伴い、STIのシリコン酸化膜を介して隣接する浮遊ゲート間で電流が漏れてしまうYupin/Enda効果が大きくなる。この漏れ電流により、メモリの読み出しおよび書き込みにおいて誤動作が生じ、特に素子サイズが30nm世代以降において顕著になる。このようなYupin/Enda効果を低減するために、STIとして種々の材料を選択したり、構造を提案したりすることで、STI中の漏れ電流を低減している。

【0003】

例えば、上記問題を解決する方法として、STIに中空構造(エアギャップ)を用いる方法が挙げられる。エアギャップは、その内部が空気であるため、絶縁性に優れている。また、誘電率が1であるため、漏れ電流を極限まで低減することができる。

【0004】

しかし、エアギャップの形成において、様々な問題が生じる。例えば、CVD(Chemical Vapor Deposition)法を用いて埋め込み特性の悪い膜を溝に堆積させることで、溝を埋め込まないようにエアギャップを形成する方法がある。しかし、この方法では、溝の側壁に膜が付着することで、メモリの電荷保持特性に悪影響を与える。また、エアギャップの形成が不十分となり、十分な絶縁性が得られない。

【0005】

これに対し、一旦溝を犠牲膜で完全に埋め込み、電極間絶縁膜等を形成した後、一部を開口してエッチングにより埋め込まれた犠牲膜を除去する方法などが提案されている。この犠牲膜として、PSZ(ポリシラザン)膜が用いられる。しかし、PSZ膜は、比較的エッチング耐性が高いため、エアギャップとなる大きな空洞を形成しにくいという問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−250656号公報

【特許文献2】特開2010−27922号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

デバイス特性の向上を図る半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0008】

本実施形態によれば、半導体装置の製造方法が提供される。前記半導体装置の製造方法においては、半導体層上に、トンネル絶縁膜を形成する。前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する。前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する。前記溝内の下部側に、第1犠牲膜を埋め込む。前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりも高密度な第2犠牲膜を形成する。前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する。前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する。前記第2導電膜を加工することにより、前記第2犠牲膜を露出する。前記第1犠牲膜および前記第2犠牲膜を除去する。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る半導体装置の構造を示す平面図。

【図2】第1の実施形態に係る半導体装置の構造を示す断面図

【図3】第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図4】図3に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図5】図4に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図6】図5に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図7】図6に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図8】図7に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図9】図8に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図10】図9に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図11】図10に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図12】図11に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図13】図12に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図14】図13に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図15】図14に続く、第1の実施形態に係る半導体装置の製造工程を示す断面図。

【図16】第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図17】図16に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図18】図17に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図19】図18に続く、第2の実施形態に係る半導体装置の製造工程を示す断面図。

【図20】第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図21】図20に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図22】図21に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図23】図22に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図24】図23に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図25】図24に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図26】図25に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【図27】図26に続く、第3の実施形態に係る半導体装置の製造工程を示す断面図。

【発明を実施するための形態】

【0010】

本実施形態を以下に図面を参照して説明する。図面において、同一部分には同一の参照符号を付す。また、重複する説明は、必要に応じて行う。

【0011】

<第1の実施形態>

図1乃至図15を用いて、第1の実施形態に係る半導体装置について説明する。第1の実施形態は、STIとして設けられた溝15内に、HSQ(ハイドロジェンシルセスキオキサン)膜17と、その上部に位置し、HSQ膜17よりもエッチング耐性の強い酸化膜18とを形成した後、これらを除去することでエアギャップ20を形成する例である。

【0012】

[第1の実施形態の構造]

以下に、図1および図2を用いて、第1の実施形態に係る半導体装置の構造について説明する。

【0013】

図1は、第1の実施形態に係る半導体装置の構造を示す平面図である。

【0014】

図1に示すように、半導体装置は、複数のビット線BLおよびこれらに直交する複数のワード線WLを備える。

【0015】

複数のビット線BLと複数のワード線WLとの各交差位置には、メモリセルMCが形成される。メモリセルMCは、ビット線方向およびこれに直交するワード線方向に、所定間隔を有して配置される。すなわち、メモリセルMCは、ビット線方向およびワード線方向にマトリクス状に配置される。

【0016】

メモリセルMCは、ビット線方向に沿った素子領域(AA:Active Area)に形成される。また、ワード線方向に沿って隣接するメモリセルMCは、ビット線方向に沿って形成される素子分離領域(STI)によって区画される。

【0017】

図2は、第1の実施形態に係る半導体装置の構造を示す断面図である。より具体的には、図2(a)は図1のA−A線に沿った断面図であり、図2(b)は図1のB−B線に沿った断面図であり、図2(c)は図1のC−C線に沿った断面図である。すなわち、図2(a)はワード線方向に沿ったメモリセルMCの断面図であり、図2(b)はビット線方向に沿った素子分離領域の断面図であり、図2(c)はワード線方向に沿った素子領域の断面図である。ここで、図2において、ビット線BLは省略している。

【0018】

図2(a)乃至(c)に示すように、第1の実施形態に係る半導体装置は、半導体層10上において、メモリセルMCが形成された素子領域(AA)と、素子領域を区画するSTI構造からなる素子分離領域とで構成される。

【0019】

半導体層10は、例えばシリコン基板であるが、これに限らず、SOI(Silicon On Insulating)基板でもよい。半導体層10は、素子領域と素子分離領域とで段差を有する。より具体的には、半導体層10は、素子領域において上段面を有し、素子分離領域において下段面を有する。すなわち、半導体層10は、素子分離領域において溝15を有する。この溝15は、ワード線方向における幅が例えば30nm以下であり、積層方向における深さが例えば200nm以上500nm以下であるが、これに限らず、デバイス構造やその世代によって適宜異なる。

【0020】

素子領域におけるメモリセルMCは、半導体層10上に形成されたトンネル絶縁膜11、浮遊ゲート電極12、電極間絶縁膜19、およびワード線WL(制御ゲート電極)で構成される。

【0021】

素子領域において、トンネル絶縁膜11は、半導体層10上に形成される。トンネル絶縁膜11は、例えばシリコン酸化膜またはシリコン窒化膜、もしくはこれらの積層膜で構成される。トンネル絶縁膜11の膜厚は、例えば8nm以下である。

【0022】

浮遊ゲート電極12は、トンネル絶縁膜11上に形成される。浮遊ゲート電極12は、例えばポリシリコン膜で構成されるが、これに限らず、Wシリサイド膜またはCoシリサイド膜で構成されてもよい。浮遊ゲート電極12がポリシリコン膜である場合、その膜厚は例えば100nmである。一方、浮遊ゲート電極12がWシリサイド膜またはCoシリサイド膜である場合、その膜厚は例えば100nm以上200nm以下である。この浮遊ゲート電極12は、電荷蓄積膜として機能する。

【0023】

電極間絶縁膜19は、浮遊ゲート電極12上に形成される。すなわち、電極間絶縁膜19は、浮遊ゲート電極12の上面および上側面を覆うように形成される。電極間絶縁膜19は、例えばシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜が順に形成された積層膜で構成されるが、これに限らない。シリコン酸化膜またはシリコン窒化膜の単層膜で構成されてもよく、もしくはこれらが交互に4層以上形成された積層膜で構成されてもよい。電極間絶縁膜19の膜厚は、例えば20nm程度である。

【0024】

ワード線WLとなる制御ゲート電極は、電極間絶縁膜19上に形成される。制御ゲート電極は、例えば、ポリシリコン膜およびW膜が順に形成された積層膜で構成されるが、これに限らない。ポリシリコン膜またはW膜の単層膜で構成されてもよく、もしくはWシリサイド膜またはCoシリサイド膜で構成されてもよい。制御ゲート電極の膜厚は、例えば50nm程度である。

【0025】

一方、素子分離領域において、半導体層10に形成された溝15内にSTI構造が形成される。図1(a)に示すように、STI構造は、ワード線方向に隣接するメモリセルMC間(浮遊ゲート電極12間)に形成され、ビット線方向に延在する。このSTI構造は、ライナー膜16およびエアギャップ20で構成される。

【0026】

ライナー膜16は、溝15の内面上に形成される。すなわち、ライナー膜16は、溝15内における半導体層10の側面上および底面上、トンネル絶縁膜11の側面上、および浮遊ゲート電極12の下側面上に形成される。浮遊ゲート電極12の下側面上に形成されたライナー膜16は、浮遊ゲート電極12の上側面上に形成された電極間絶縁膜19と接する。ライナー膜16は、例えばTEOS膜またはHTO膜で構成される。ライナー膜16の膜厚は、例えば1nm以上20nm以下である。このライナー膜16は、STI構造の側壁を保護する保護膜として機能する。

【0027】

エアギャップ20は、溝15内のライナー膜16上に形成される。すなわち、エアギャップ20は、溝15内におけるライナー膜16の底面上および側面上に形成される。図2(a)および(b)に示すように、エアギャップ20の上面上には、電極間絶縁膜19および図示せぬ層間絶縁膜が形成される。すなわち、エアギャップ20は、ワード線方向における側面がライナー膜19に覆われ、上面が電極間絶縁膜19および層間絶縁膜に覆われる。また、エアギャップ20の上面は、トンネル絶縁膜11の上面よりも高く浮遊ゲート電極12の上面よりも低い。すなわち、隣接する浮遊ゲート電極12間の少なくとも一部に、エアギャップ20が形成される。なお、隣接する浮遊ゲート電極12間の領域のうち、エアギャップ20が形成される領域をできる限り大きくすることが望ましい。

【0028】

このエアギャップ20は、中空構造であり、例えば空気で満たされる。エアギャップ20がワード線方向に隣接するメモリセルMC間(浮遊ゲート電極12間)に形成されることで、浮遊ゲート電極12間の絶縁性を向上させ、漏れ電流を抑制することができる。

【0029】

なお、本実施形態において、エアギャップ20の下部に、HSQ酸化膜17が形成されてもよい。すなわち、溝15内におけるライナー膜16の底面上および下側側面上にHSQ酸化膜17が形成され、ライナー膜16の上側側面上にエアギャップ20が形成される。このHSQ酸化膜17は、後述する製造工程において、犠牲膜として溝15内に形成され、除去する際に残存したものである。

【0030】

このHSQ酸化膜17は、多くのボイドを含む。このため、HSQ酸化膜17は、後述するPHPS(ペルヒドロポリシラザン)酸化膜やCVD法またはALD(Atomic Layer Deposition)法により形成されるシリコン酸化膜よりも低密度の膜である。

【0031】

[第1の実施形態の製造方法]

以下に、図3乃至図15を用いて、第1の実施形態に係る半導体装置の製造方法について説明する。

【0032】

図3乃至図15は、第1の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図3(a)乃至図15(a)は図1のA−A線に沿った断面図であり、図3(b)乃至図15(b)は図1のB−B線に沿った断面図であり、図3(c)乃至図15(c)は図1のC−C線に沿った断面図である。

【0033】

まず、図3(a)乃至(c)に示すように、半導体層10上に、例えば熱酸化法により、シリコン酸化膜で構成されるトンネル絶縁膜11が形成される。なお、トンネル絶縁膜11は、例えばCVD法またはALD法で形成されるシリコン酸化膜またはシリコン窒化膜、もしくはこれらの積層膜で構成されてもよい。トンネル絶縁膜11の膜厚は、例えば8nm以下である。

【0034】

次に、トンネル絶縁膜11上に、例えばCVD法またはALD法により、浮遊ゲート電極12が形成される。浮遊ゲート電極12は、例えば、膜厚が100nmのポリシリコン膜、または膜厚が100nm以上200nm以下のWシリサイド膜もしくはCoシリサイド膜で構成される。

【0035】

次に、浮遊ゲート電極12上に、例えばLP(Low Pressure)CVD法により、ストッパー膜13が形成される。ストッパー膜13は、例えば、膜厚が200nmのシリコン窒化膜、または膜厚が100nm以上200nm以下のポリシリコン膜で構成される。

【0036】

次に、ストッパー膜13上に、例えばLPCVD法により、ハードマスク14が形成される。ハードマスク14は、例えば膜厚が300nmのTEOS膜で構成される。

【0037】

次に、図4(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ハードマスク14をマスクとして、ストッパー膜13、浮遊ゲート電極膜12、トンネル絶縁膜11、および半導体層10が加工される。これにより、ストッパー膜13、浮遊ゲート電極膜12、およびトンネル絶縁膜11を貫通し、半導体層10に達する溝15が形成される。溝15は、幅が例えば30nm以下であり、半導体層10内における深さが例えば200nm以上500nm以下であるが、これに限らず、デバイス構造やその世代によって適宜異なる。

【0038】

なお、このとき、ハードマスク14も一部エッチングされるが、ストッパー膜13上に残存する。

【0039】

次に、図5(a)乃至(c)に示すように、例えばCVD法により、溝15の内面上に、ライナー膜16が形成される。すなわち、ライナー膜16は、溝15内における半導体層10の側面上および底面上、トンネル絶縁膜11の側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、ハードマスク14の側面上、溝15外におけるハードマスク14の上面上に形成される。ライナー膜16は、例えばTEOS膜またはHTO膜で構成される。ライナー膜16の膜厚は、例えば1nm以上20nm以下である。

【0040】

ここまでの工程は、上記方法に限らず、公知の種々の方法を用いて行うことができる。

【0041】

次に、STI構造としてエアギャップ20の形成工程が行われる。以下に、本実施形態に係るエアギャップ20の形成工程について詳説する。

【0042】

まず、図6(a)乃至(c)に示すように、塗布法により、全面が覆われるようにライナー膜16上に、犠牲膜となるHSQ膜17が形成される。すなわち、HSQ膜17は、溝15内におけるライナー膜16の底面上および側面上、溝15外におけるライナー膜16の上面上に形成される。これにより、溝15内に、HSQ膜17が埋め込まれる。HSQ膜17は、塗布法により薄膜形成が可能であり、埋め込み特性に優れている。このため、溝15の幅が微細化されたとしてもその内部をHSQ膜17により埋め込むことができる。

【0043】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、HSQ膜17が酸化され、HSQ酸化膜17に転換される。このとき、熱処理は、例えば230℃以上900℃以下で行われる。さらに、窒素雰囲気中で熱処理することにより、HSQ酸化膜17を硬化させてもよい。

【0044】

なお、本明細書において、HSQ酸化膜17は、HSQ膜17から誘導された酸化膜を示す。また、以下において、HSQ酸化膜17を単にHSQ膜17と称する。

【0045】

このように形成されたHSQ膜17は、多くのボイドを含む。このため、HSQ膜17は、後述するPHPS膜やCVD法またはALD法により形成される酸化膜よりも低密度である(膜密度が低い)。また、HSQ膜17は、PHPS膜やCVD法またはALD法により形成される酸化膜よりもエッチング耐性が弱い(エッチングレートが高い)。

【0046】

次に、図7(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMP(Chemical Mechanical Polishing)が行われる。これにより、上部のHSQ膜17、上部のライナー膜16、およびハードマスク14が除去され、HSQ膜17、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0047】

次に、図8(a)乃至(c)に示すように、HSQ膜17がエッチングされる。このとき、HSQ膜17の上面がトンネル絶縁膜11の上面から下面の高さ付近になるように、HSQ膜17が加工されるが、これに限らない。後述するHSQ膜17の除去工程を考慮すると、HSQ膜17の上面がトンネル絶縁膜11の上面よりも高くなるように加工されることが望ましい。すなわち、溝15内の下部側がHSQ膜17によって埋め込まれる。

【0048】

このとき、ライナー膜16も同時にエッチングされてもよい。すなわち、ストッパー膜13および浮遊ゲート電極12の側面が露出してもよい。また、ライナー膜16のエッチング耐性は、HSQ膜17のエッチング耐性よりも強い。このため、ライナー膜16の上面がHSQ膜17の上面よりも高くなるように加工される。

【0049】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。ウェットエッチングの場合、エッチング液として例えばDHF(dilute hydrofluoric acid)が用いられる。

【0050】

次に、図9(a)乃至(c)に示すように、全面が覆われるように、犠牲膜となる酸化膜18が形成される。すなわち、酸化膜18は、溝15内におけるHSQ膜17の上面上、ライナー膜16の上面上および側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、溝15外におけるストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、酸化膜18が埋め込まれる。

【0051】

酸化膜18は、例えばCVD法またはALD法によって形成されるシリコン酸化膜で構成されてもよいが、埋め込み特性の観点から、塗布法により形成されるPHPS膜で構成されることが望ましい。酸化膜18としてPHPS膜が形成される場合、以下のように形成される。

【0052】

まず、塗布法により、PHPS膜が溝15内に埋め込まれる。PHPS膜は、塗布法により薄膜形成が可能であり、埋め込み特性に優れている。このため、溝15の幅が微細化されたとしてもその内部をPHPS膜により埋め込むことができる。その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜が酸化され、PHPS酸化膜に転換される。この熱処理は、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10がライナー膜16に覆われていない場合、これらが酸化してしまうことを防ぐために比較的低温、例えば230℃以上500℃以下で行われる。さらに、窒素雰囲気中で熱処理することにより、PHPS酸化膜を硬化させてもよい。このように、埋め込み特性に優れたPHPS酸化膜が形成される。

【0053】

このように形成された酸化膜18(シリコン酸化膜またはPHPS酸化膜)は、その下部に位置するHSQ膜17よりも高密度な膜である(膜密度が高い)。また、酸化膜18は、HSQ膜17よりもエッチング耐性が強い(エッチングレートが低い)。

【0054】

次に、図10(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部の酸化膜18が除去され、酸化膜18およびストッパー膜13の上面が平坦化される。

【0055】

次に、図11(a)乃至(c)に示すように、酸化膜18がエッチングされる。このとき、酸化膜18の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、酸化膜18が浮遊ゲート電極12側部に位置するように加工されることが望ましい。また、酸化膜18の上面がライナー膜16の上面よりも高くなってもよい。すなわち、ライナー膜16は、酸化膜18に覆われてもよい。また、溝15内に形成される酸化膜18は、その表面形状や高さの均一性が得られる程度で、できる限り少ないほうが望ましい。

【0056】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。ウェットエッチングの場合、エッチング液として例えばDHFが用いられる。

【0057】

次に、図12(a)乃至(c)に示すように、例えばリン酸水溶液を用いたウェットエッチングにより、ストッパー膜13が除去される。これにより、浮遊ゲート電極12の上面が露出する。

【0058】

次に、図13(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、電極間絶縁膜19が形成される。電極間絶縁膜19は、例えばシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜が順に形成された積層膜で構成されるが、これに限らない。シリコン酸化膜またはシリコン窒化膜の単層膜で構成されてもよく、もしくはこれらが交互に4層以上形成された積層膜で構成されてもよい。電極間絶縁膜19の膜厚は、例えば20nm程度である。

【0059】

このとき、電極間絶縁膜19は、酸化膜18上にも形成される。言い換えると、酸化膜18は、電極間絶縁膜19に覆われる。ここで、酸化膜18は、HSQ膜17よりも高密度に形成される膜である。このため、複数の溝15において、酸化膜18の表面形状や高さを均一にさせることができる。これにより、電極間絶縁膜19の膜厚や構造を均一に形成することができる。

【0060】

次に、図14(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、ワード線WLとなる制御ゲート電極が形成される。制御ゲート電極は、例えば、ポリシリコン膜およびW膜が順に形成された積層膜で構成されるが、これに限らない。ポリシリコン膜またはW膜の単層膜で構成されてもよく、もしくはWシリサイド膜またはCoシリサイド膜で構成されてもよい。制御ゲート電極の膜厚は、例えば50nm程度である。

【0061】

次に、図15(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ビット線方向に沿ってワード線WLが加工される。このとき、エッチングは、トンネル絶縁膜11に達するまで行われる。すなわち、トンネル絶縁膜11よりも上方に位置する各層が加工される。より具体的には、ワード線WL、電極間絶縁膜19、および浮遊ゲート電極12が加工される。

【0062】

このとき、前工程において、少なくとも酸化膜18の一部がトンネル絶縁膜11よりも上方に位置している。このため、酸化膜18の一部も同時に加工され、少なくとも酸化膜18の一部が露出する。なお、図15において、HSQ膜17の一部もトンネル絶縁膜11より上方に位置する。このため、酸化膜18を貫通し、HSQ膜17の一部に達するように加工される。これにより、酸化膜18およびHSQ膜17は、その一部が露出する。

【0063】

次に、図2(a)乃至(c)に示すように、例えば等方的なウェットエッチングにより、HSQ膜17および酸化膜18が除去される。エッチング液として、例えばDHFが用いられる。これにより、溝15内のライナー膜16上に、エアギャップ20が形成される。

【0064】

このとき、酸化膜18およびHSQ膜17の露出した表面から除去されていく。このため、HSQ膜17が露出していない場合、エッチング耐性の強い酸化膜18を除去した後でなければHSQ膜17を除去できず、HSQ膜17の除去が比較的困難になる。このため、前工程において酸化膜18だけでなく、HSQ膜17の表面も露出していることが望ましい。

【0065】

なお、HSQ膜17は、上部側から除去されていくが、下部側まで全て除去しなくてもよい。隣接する浮遊ゲート電極12間でYupin/Enda効果を抑制できる程度まで除去すればよい。また、このとき、ライナー膜16も除去され得るが、残存してもよい。

【0066】

その後、例えばCVD法により、全面に、例えばTEOSで構成される図示せぬ層間絶縁膜が形成される。この層間絶縁膜は、CVD法等の埋め込み特性の低い方法により形成されるため、エアギャップ20内には形成されない。

【0067】

このようにして、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0068】

[第1の実施形態の効果]

上記第1の実施形態によれば、STIとして設けられた溝15内に、犠牲膜として、膜密度が小さくかつエッチング耐性の弱いHSQ膜17を形成した後、その上部にHSQ膜17よりも膜密度が大きくかつエッチング耐性の強い酸化膜18を形成する。その後、これらを電極間絶縁膜19およびワード線WLで覆った後、一部を露出して除去することで、STI構造としてエアギャップ20を形成する。

【0069】

このように、犠牲膜として膜密度が小さくかつエッチング耐性の弱いHSQ膜17を用いることで、犠牲膜の除去を容易に行うことができる。すなわち、犠牲膜のエッチング液による溶解性を向上させることができ、エアギャップ20となるより大きな空洞を形成することができる。したがって、隣接する浮遊ゲート電極12間のYupin/Enda効果を低減し、デバイス特性の向上を図ることができる。

【0070】

また、第1の実施形態によれば、犠牲膜として、HSQ膜17だけでなく、HSQ膜17上に酸化膜18が形成される。酸化膜18は、HSQ膜17よりもエッチング耐性が強く、膜密度が大きい膜である。このため、複数の溝15において、酸化膜18の表面形状や高さの均一性を図ることができる。すなわち、その上部に形成される電極間絶縁膜19の膜厚や構造を均一に形成することができ、デバイスの信頼性を向上させることできる。

【0071】

<第2の実施形態>

図16乃至図19を用いて、第2の実施形態に係る半導体装置について説明する。第2の実施形態は、第1の実施形態における酸化膜18としてPHPS膜21が形成される場合であり、PHPS膜21の形成工程において、浮遊ゲート電極12の表面がライナー膜16で覆われる例である。なお、第2の実施形態において、上記第1の実施形態と同様の点については説明を省略し、主に異なる点について説明する。

【0072】

[第2の実施形態の製造方法]

以下に、図16乃至図19を用いて、第2の実施形態に係る半導体装置の製造方法について説明する。

【0073】

図16乃至図19は、第2の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図16(a)乃至図19(a)は図1のA−A線に沿った断面図であり、図16(b)乃至図19(b)は図1のB−B線に沿った断面図であり、図16(c)乃至図19(c)は図1のC−C線に沿った断面図である。

【0074】

まず、第1の実施形態と同様に、図3乃至図7の工程が行われる。すなわち、溝15を埋め込むようにHSQ膜17が形成された後、HSQ膜17、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0075】

次に、図16(a)乃至(c)に示すように、HSQ膜17がエッチングされる。このとき、HSQ膜17の上面がトンネル絶縁膜11の上面から下面の高さ付近になるように、HSQ膜17が加工されるが、これに限らない。後述するHSQ膜17の除去工程を考慮すると、HSQ膜17の上面がトンネル絶縁膜11の上面よりも高くなるように加工されることが望ましい。

【0076】

このとき、第2の実施形態において、ライナー膜16は、エッチングされない。すなわち、ストッパー膜13および浮遊ゲート電極12の側面がライナー膜16に覆われたまま露出しないように、エッチング条件が調整される。

【0077】

このエッチング条件として、エッチング液に例えばアルカリ溶液を用いたウェットエッチングが挙げられる。HSQ膜17は、ライナー膜16よりもアルカリ溶液に対するエッチング耐性が弱い。このため、アルカリ溶液によるウェットエッチングを行うことで、HSQ膜17のみをエッチングすることができる。

【0078】

次に、図17(a)乃至(c)に示すように、塗布法により、全面が覆われるように、犠牲膜となるPHPS膜21が形成される。すなわち、PHPS膜21は、溝15内におけるHSQ膜17の上面上、ライナー膜16の側面上、溝15外におけるライナー膜16の上面上、ストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、PHPS膜21が埋め込まれる。

【0079】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜21が酸化され、PHPS酸化膜21に転換される。

【0080】

なお、本明細書において、PHPS酸化膜21は、PHPS膜21から誘導された酸化膜を示す。また、以下において、PHPS酸化膜21を単にPHPS膜21と称する。

【0081】

このとき、熱処理は、例えば230℃以上900℃以下で行われる。ここで、第2の実施形態において、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10は、ライナー膜16で覆われている。このため、PHPS膜21の酸化工程(熱処理)を比較的高温で行っても、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10が酸化されることはない。

【0082】

次に、図18(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部のPHPS膜21が除去され、PHPS膜21、ライナー膜16、およびストッパー膜13の上面が平坦化される。

【0083】

次に、図19(a)乃至(c)に示すように、PHPS膜21がエッチングされる。このとき、PHPS膜21の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、PHPS膜21が浮遊ゲート電極12側部に位置するように加工されることが望ましい。

【0084】

このとき、ライナー膜16も同時に形成される。すなわち、ストッパー膜13および浮遊ゲート電極12の側面が露出する。

【0085】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。

【0086】

その後、第1の実施形態と同様に、図12乃至図15、および図2の工程が行われ、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0087】

[第2の実施形態の効果]

上記第2の実施形態によれば、第1の実施形態と同様の効果を得ることができる。

【0088】

さらに、第2の実施形態では、溝15にHSQ膜17を埋め込んだ後にエッチングする際、エッチング条件を調整することにより、ライナー膜16を除去しない。これにより、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10の側面をライナー膜16で覆ったまま、PHPS膜21の塗布および酸化工程を行うことができる。すなわち、PHPS膜21の酸化工程における熱処理によって、浮遊ゲート電極12、トンネル絶縁膜11、および半導体層10が酸化されることを抑制することができる。

【0089】

<第3の実施形態>

図20乃至図27を用いて、第3の実施形態に係る半導体装置について説明する。第3の実施形態は、第1の実施形態における酸化膜18としてPHPS膜21が形成される場合であり、HSQ膜17とPHPS膜21との間に高密度のシリコン酸化膜22を形成する例である。なお、第3の実施形態において、上記各実施形態と同様の点については説明を省略し、主に異なる点について説明する。

【0090】

[第3の実施形態の製造方法]

以下に、図20乃至図27を用いて、第3の実施形態に係る半導体装置の製造方法について説明する。

【0091】

図20乃至図27は、第3の実施形態に係る半導体装置の製造工程を示す断面図である。より具体的には、図20(a)乃至図27(a)は図1のA−A線に沿った断面図であり、図20(b)乃至図27(b)は図1のB−B線に沿った断面図であり、図20(c)乃至図27(c)は図1のC−C線に沿った断面図である。

【0092】

まず、第1の実施形態と同様に、図3乃至図8の工程が行われる。すなわち、溝15を埋め込むようにHSQ膜17が形成された後、エッチングされることで、溝15の下部側にHSQ膜17が埋め込まれる。

【0093】

次に、図20(a)乃至(c)に示すように、例えばALD法またはCVD法により、HSQ膜17上に、シリコン酸化膜22が形成される。すなわち、シリコン酸化膜22は、溝15内におけるHSQ膜17の上面上に形成される。これにより、HSQ膜17の上面は、シリコン酸化膜22に覆われる。

【0094】

このとき、シリコン酸化膜22は、HSQ膜17以外の膜の全面にも形成される。すなわち、シリコン酸化膜22は、溝15内におけるライナー膜16の上面上および側面上、浮遊ゲート電極12の側面上、ストッパー膜13の側面上、溝15外におけるストッパー膜13の上面上にも形成される。

【0095】

なお、本明細書において、犠牲膜としてのシリコン酸化膜22は、塗布法ではなく、例えばCVD法またはALD法等の堆積法によって形成される酸化膜を示す。

【0096】

シリコン酸化膜22の膜厚は、例えば3nm以下である。しかし、これに限らず、シリコン酸化膜22の膜厚は、後工程においてPHPS膜21がHSQ膜のボイドに侵入しない程度に大きく、犠牲膜としてエッチングしやすい程度に小さければよい。

【0097】

このように形成されたシリコン酸化膜22は、その下部に位置するHSQ膜17および後にその上部に形成されるPHPS膜21よりも高密度な膜である。また、シリコン酸化膜22は、HSQ膜17およびPHPS膜21よりもエッチング耐性が強い。

【0098】

なお、シリコン酸化膜22は、ライナー膜16と同様の効果を有する。すなわち、後述するPHPS膜21の酸化工程において、浮遊ゲート電極12等がシリコン酸化膜22で覆われることにより浮遊ゲート電極12等の酸化を抑制することができる。また、上記観点から、シリコン酸化膜22は浮遊ゲート電極12等の表面に残すことが望ましいが、除去してもよい。

【0099】

次に、図21(a)乃至(c)に示すように、塗布法により、全面が覆われるように、犠牲膜となるPHPS膜21が形成される。すなわち、PHPS膜21は、溝15内におけるシリコン酸化膜22の上面上、ライナー膜16の側面上、溝15外におけるライナー膜16の上面上、ストッパー膜13の上面上に形成される。これにより、溝15内の上部側に、PHPS膜21が埋め込まれる。

【0100】

その後、酸素雰囲気中または水蒸気中で熱処理することにより、PHPS膜21が酸化される。この熱処理は、浮遊ゲート電極12およびトンネル絶縁膜11がライナー膜16(および/またはシリコン酸化膜22)に覆われていない場合、例えば230℃以上500℃以下で行われ、覆われている場合、例えば230℃以上900℃以下で行われる。

【0101】

このように形成されたPHPS膜21は、その下部に位置するシリコン酸化膜22よりも低密度な膜であり、さらに下部に位置するHSQ膜よりも高密度な膜である。また、酸化膜18は、シリコン酸化膜22よりもエッチング耐性が弱く、HSQ膜17よりもエッチング耐性が強い。

【0102】

次に、図22(a)乃至(c)に示すように、ストッパー膜13をストッパーとしてCMPが行われる。これにより、上部のPHPS膜21が除去され、PHPS膜21、シリコン酸化膜22およびストッパー膜13の上面が平坦化される。

【0103】

次に、図23(a)乃至(c)に示すように、PHPS膜21がエッチングされる。このとき、PHPS膜21の上面がトンネル絶縁膜11の上面よりも高く、浮遊ゲート電極12の上面よりも低くなるように加工される。すなわち、PHPS膜21が浮遊ゲート電極12側部に位置するように加工されることが望ましい。

【0104】

このとき、シリコン酸化膜22もエッチングされる。これにより、シリコン酸化膜22が浮遊ゲート電極12の側面上から除去されることが望ましいが、一部残存してもよい。

【0105】

なお、エッチングは、ウェットエッチングでもドライエッチングでもよく、また等方的でも異方的でもよい。

【0106】

次に、図24(a)乃至(c)に示すように、例えばリン酸水溶液を用いたウェットエッチングにより、ストッパー膜13が除去される。これにより、浮遊ゲート電極12の上面が露出する。

【0107】

次に、図25(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、電極間絶縁膜19が形成される。このとき、電極間絶縁膜19は、PHPS膜21上にも形成される。

【0108】

次に、図26(a)乃至(c)に示すように、例えばCVD法により、浮遊ゲート電極12上に、ワード線WLとなる制御ゲート電極が形成される。

【0109】

次に、図27(a)乃至(c)に示すように、フォトリソグラフィおよびドライエッチング法により、ビット線方向に沿ってワード線WLが加工される。このとき、エッチングは、トンネル絶縁膜11に達するまで行われる。

【0110】

このとき、前工程において、少なくともPHPS膜21の一部がトンネル絶縁膜11よりも上方に位置している。このため、PHPS膜21の一部も同時に加工され、少なくともPHPS膜21の一部が露出する。なお、図15において、シリコン酸化膜22およびHSQ膜17の一部もトンネル絶縁膜11より上方に位置する。このため、PHPS膜21およびシリコン酸化膜22を貫通し、HSQ膜17の一部に達するように加工される。これにより、PHPS膜21、シリコン酸化膜22およびHSQ膜17は、その一部が露出する。

【0111】

次に、図2(a)乃至(c)に示すように、例えば等方的なウェットエッチングにより、HSQ膜17およびPHPS膜21が除去される。エッチング液として、例えばDHFが用いられる。これにより、溝15内のライナー膜16上に、エアギャップ20が形成される。

【0112】

ここで、シリコン酸化膜22は、HSQ膜17およびPHPS膜21よりもエッチング耐性の強い膜である、しかし、シリコン酸化膜22は、薄く(例えば、3nm以下で)形成されているため、犠牲膜として機能し、HSQ膜17およびPHPS膜21と同時にエッチングされて除去される。

【0113】

このようにして、本実施形態に係る半導体装置におけるエアギャップ20が形成される。

【0114】

[第3の実施形態の効果]

上記第3の実施形態によれば、第1の実施形態と同様の効果を得ることができる。

【0115】

ところで、HSQ膜17は、ボイドを多く含む膜であり、低密度な膜である。このHSQ膜17上に塗布法によりPHPS膜21を形成した場合、埋め込み特性の高いPHPS膜21はHSQ膜17のボイド内に侵入する恐れがある。HSQ膜17にPHPS膜21が侵入した場合、高密度かつエッチング耐性の強い膜になってしまう。その結果、これらの膜は、エアギャップ20の形成のための犠牲膜として除去しにくい膜になってしまう。

【0116】

これに対し、第3の実施形態では、HSQ膜17とPHPS膜21との界面に、薄いシリコン酸化膜22が形成される。このシリコン酸化膜22は、ALD法またはCVD法により形成される埋め込み特性が低く、高密度な膜である。シリコン酸化膜22は、埋め込み特性が低いためにHSQ膜17のボイドに侵入することはなく、高密度な膜であるためにPHPS膜21がHSQ膜17に侵入することを防ぐことができる。

【0117】

その他、本発明は、上記各実施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題が解決でき、発明の効果の欄で述べられている効果が得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

【符号の説明】

【0118】

10…半導体層、11…トンネル絶縁膜、12…浮遊ゲート電極、15…溝、16…ライナー膜、17…HSQ膜、18…酸化膜、19…電極間絶縁膜、21…PHPS膜、22…シリコン酸化膜。

【特許請求の範囲】

【請求項1】

半導体層上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する工程と、

前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する工程と、

前記溝内の下部側に、第1犠牲膜を埋め込む工程と、

前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりも高密度な第2犠牲膜を形成する工程と、

前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する工程と、

前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する工程と、

前記第2導電膜を加工することにより、前記第2犠牲膜を露出する工程と、

前記第1犠牲膜および前記第2犠牲膜を除去する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

半導体層上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する工程と、

前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する工程と、

前記溝内の下部側に、第1犠牲膜を埋め込む工程と、

前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりもエッチング耐性の強い第2犠牲膜を形成する工程と、

前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する工程と、

前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する工程と、

前記第2導電膜を加工することにより、前記第2犠牲膜を露出する工程と、

前記第1犠牲膜および前記第2犠牲膜を除去する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

前記第1犠牲膜は、塗布法により形成されるHSQ膜で構成されることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第2犠牲膜は、塗布法により形成されるPHPS膜で構成されることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記第2犠牲膜は、CVD法またはALD法により形成されるシリコン酸化膜で構成されることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項6】

前記第1犠牲膜を埋め込む工程の後、前記第1犠牲膜上に、CVD法またはALD法によりシリコン酸化膜で構成される第3犠牲膜を形成する工程をさらに具備し、

前記第1犠牲膜は塗布法により形成されるHSQ膜で構成され、前記第2犠牲膜は塗布法により形成されるPHPS膜で構成される

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項7】

前記第1犠牲膜を埋め込む工程において、前記第1犠牲膜は、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、形成され、

前記第2犠牲膜を露出する工程において、前記第1犠牲膜も露出する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項8】

前記溝を形成する工程の後、前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を覆うように、ライナー膜を形成する工程をさらに具備することを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項1】

半導体層上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する工程と、

前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する工程と、

前記溝内の下部側に、第1犠牲膜を埋め込む工程と、

前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりも高密度な第2犠牲膜を形成する工程と、

前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する工程と、

前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する工程と、

前記第2導電膜を加工することにより、前記第2犠牲膜を露出する工程と、

前記第1犠牲膜および前記第2犠牲膜を除去する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

半導体層上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜を形成する工程と、

前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を加工することにより、溝を形成する工程と、

前記溝内の下部側に、第1犠牲膜を埋め込む工程と、

前記溝内の前記第1犠牲膜上に、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、前記第1犠牲膜よりもエッチング耐性の強い第2犠牲膜を形成する工程と、

前記第1導電膜上および前記第2犠牲膜上に、絶縁膜を形成する工程と、

前記絶縁膜上に制御ゲート電極となる第2導電膜を形成する工程と、

前記第2導電膜を加工することにより、前記第2犠牲膜を露出する工程と、

前記第1犠牲膜および前記第2犠牲膜を除去する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

前記第1犠牲膜は、塗布法により形成されるHSQ膜で構成されることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第2犠牲膜は、塗布法により形成されるPHPS膜で構成されることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記第2犠牲膜は、CVD法またはALD法により形成されるシリコン酸化膜で構成されることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項6】

前記第1犠牲膜を埋め込む工程の後、前記第1犠牲膜上に、CVD法またはALD法によりシリコン酸化膜で構成される第3犠牲膜を形成する工程をさらに具備し、

前記第1犠牲膜は塗布法により形成されるHSQ膜で構成され、前記第2犠牲膜は塗布法により形成されるPHPS膜で構成される

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項7】

前記第1犠牲膜を埋め込む工程において、前記第1犠牲膜は、その上面が前記トンネル絶縁膜の上面よりも高く、前記第1導電膜の上面よりも低くなるように、形成され、

前記第2犠牲膜を露出する工程において、前記第1犠牲膜も露出する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項8】

前記溝を形成する工程の後、前記第1導電膜、前記トンネル絶縁膜、および前記半導体層を覆うように、ライナー膜を形成する工程をさらに具備することを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【公開番号】特開2013−98490(P2013−98490A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−242590(P2011−242590)

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]