半導体装置の製造方法

【目的】 ガラス板等に貼りつけられたGaAs基板の裏面に、あらかじめ格子状の溝を形成しその溝を厚膜で埋め込むことにより、クラックの広がり、基板のそりによる浮きを低減する。

【構成】 表面工程加工済みの半導体基板1とガラス板2を、表面がガラス板に密着するように貼りつけ、その半導体基板1の裏面にPRで格子状のパターニングを施し、それを目印に基板1を削り格子状の溝1aを形成する。続いてポリイミド3を厚く塗布し溝1aを埋め、基板の研磨、エッチングを行う。続いてバイアホール形成、メタライズ等を行い、その後にポリイミド3を除去し、エッチカット、ガラス板からの分離を行い、チップに分割する。

【構成】 表面工程加工済みの半導体基板1とガラス板2を、表面がガラス板に密着するように貼りつけ、その半導体基板1の裏面にPRで格子状のパターニングを施し、それを目印に基板1を削り格子状の溝1aを形成する。続いてポリイミド3を厚く塗布し溝1aを埋め、基板の研磨、エッチングを行う。続いてバイアホール形成、メタライズ等を行い、その後にポリイミド3を除去し、エッチカット、ガラス板からの分離を行い、チップに分割する。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、半導体装置の製造方法に関し、特に、PHS(Plated Heat Sink)構造を有する超高周波用半導体に関する。

【0002】

【従来の技術】従来のPHS(Plated Heat Sink)構造を有する超高周波用半導体で、例えばGaAs MESFETの場合、表面に半導体装置が形成されたGaAs基板と、例えば補強板として用いられるガラス板を、GaAs基板の表面とガラス板が密着するように貼り付け、そのGaAs基板の裏面を100μmの厚さになるまで研磨、エッチングを行う。続いて裏面からソース電極をとるためのバイアホール形成、メタライズ等の裏面の加工を行う。次に複数の半導体装置が形成された基板を個々のチップに分割するときにチップに対応する裏面をレジスト等で覆い、ドライエッチング、あるいはウェットエッチングによりレジストで覆っていない領域のGaAs基板を除去した後に、ガラス板とGaAs基板を分離してチップに分割する。

【0003】

【発明が解決しようとする課題】しかしながら、従来の方法では、ガラス板に貼り付けられたGaAs基板を加工する際に研磨エッチング、その他この後の工程で基板にクラップが入り、このクラックが半導体装置が形成されたチップ上に伸びることにより著しく歩留りを落とすことがある。

【0004】また、このクラック部分から基板がそりガラス板から浮いたり、部分的に欠落し、以降の工程で所望の加工が困難になるという課題があった。

【0005】本発明は従来の上記実情に鑑みてなされたものであり、従って本発明の目的は、従来の技術に内在する上記課題を解決することを可能とした半導体装置の新規な製造方法を提供することにある。

【0006】

【課題を解決するための手段】上記目的を達成するために、本発明に係る半導体装置の製造方法は、ガラス板に貼り付けられた半導体基板を研磨して薄くする前に、裏面にあらかじめ、例えば格子状の溝を形成しておき、この溝の部分に半導体基板を構成する物質と異なる物質を埋め込むことで構成され、これにより応力によるクラックを格子状の溝で発生させ、またチップ上でクラックが発生しても格子単位で食い止めクラックの広がりを防止させるとともに、溝の部分で応力を分散することにより基板のそりを低減する。

【0007】また溝に埋め込んだ物質により溝にクラックが入っても、半導体基板とガラス板を貼り付けている貼り付け剤を裏面加工工程での薬品等の腐食から防ぐことができると同時に研磨中での研磨クズを格子状の溝に入り込まぬようにすることができる。

【0008】

【実施例】次に本発明をその好ましい一実施例について図面を参照しながら具体的に説明する。

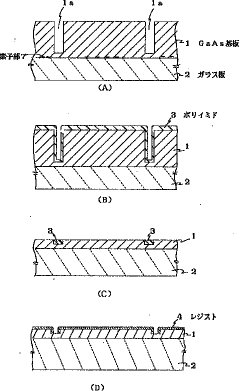

【0009】図1(A)〜(D)は本発明による第1の実施例を示す工程図である。

【0010】図1(A)〜(D)を参照するに、まず表面にFETまたは電気回路等が形成されたGaAs基板1を素子部7がガラス板2と密着するようにガラス板2に貼り付ける。次に両面目合わせを行い、GaAs基板1の裏面にチップに分割する際に溝を格子状にフォトレジストをチップの裏面に残し、他の分割領域のレジストを除去し、分割するためのGaAs基板1を露出させ目安のパターンを形成する。

【0011】次に図1(A)のようにGaAs基板1の裏面のレジストを除去してパターニングされた部分をダイサで50μmの厚さが残るように削り格子状の溝1aを作る。溝1aは結晶軸の方向になるようにあらかじめ表面の素子を配置しておく。

【0012】続いて、図1(B)のようにポリイミド3を1000rpmで2度の重ね塗りで塗布し溝1aの部分に少なくとも50μmの厚さにポリイミドが堆積するようにする。

【0013】次にGaAs基板1の裏面全体を研磨、エッチングし、図1(C)のように100μm厚の平坦に形状にする。次いでソース電極をとるためのバイアホール形成、Auめっき等の裏面加工工程を行った後に、ポリイミドをO2 プラズマで除去する。

【0014】次に図1(D)の溝の部分を除くチップ領域をレジストで覆ってGaAsを全てエッチング除去する。続いて、GaAs基板1とガラス板2を分離しチップに分割する。

【0015】図2は本発明による第2の実施例を示す断面図である。

【0016】図2に示された第2の実施例は、第1の実施例で示した分割線を複数個のチップが入るように形成することを特徴とする。ここでは第1の実施例と同様に、裏面を加工した後にチップを分割する直前に図2に示すように、複数個のチップをあらかじめ分割する形状に更に裏面からエッチングして分割するための溝を形成してから、ガラス板2からチップをはがす。これはステップ露光方式(ステッパ)による表面側素子の形成を行って、裏面加工する場合に重要であり、ステッパの1ショット内に複数個の素子をチップ形状を任意にとる場合に重要であり、クラック防止用の溝は1ショット毎のパターンにとる。

【0017】

【発明の効果】以上説明したように、本発明によれば、ガラス板に貼りつけられた半導体基板の裏面に格子状の溝を形成しその溝を厚膜で埋め込むことにより、クラックの広がりの防止、応力によるそりの低減、またそりやクラックによる基板の部分的な欠落を防ぐ効果が得られる。

【0018】本発明によればまた、チップ上にクラックの入った場合に裏面加工工程でのフォトレジストを使った加工時のレジスト厚みの不均一性によるクラック以外でのパターニング不良も防ぐことができ、裏面加工工程での歩留りの向上もできる。

【図面の簡単な説明】

【図1】本発明による第1の実施例の工程フロー図である。

【図2】本発明による第2の実施例の工程フロー図である。

【符号の説明】

1…半導体基板

1a…溝

2…ガラス板

3…ポリイミド

4…レジスト

5…ステッパ1ショット領域

7…素子部

【0001】

【産業上の利用分野】本発明は、半導体装置の製造方法に関し、特に、PHS(Plated Heat Sink)構造を有する超高周波用半導体に関する。

【0002】

【従来の技術】従来のPHS(Plated Heat Sink)構造を有する超高周波用半導体で、例えばGaAs MESFETの場合、表面に半導体装置が形成されたGaAs基板と、例えば補強板として用いられるガラス板を、GaAs基板の表面とガラス板が密着するように貼り付け、そのGaAs基板の裏面を100μmの厚さになるまで研磨、エッチングを行う。続いて裏面からソース電極をとるためのバイアホール形成、メタライズ等の裏面の加工を行う。次に複数の半導体装置が形成された基板を個々のチップに分割するときにチップに対応する裏面をレジスト等で覆い、ドライエッチング、あるいはウェットエッチングによりレジストで覆っていない領域のGaAs基板を除去した後に、ガラス板とGaAs基板を分離してチップに分割する。

【0003】

【発明が解決しようとする課題】しかしながら、従来の方法では、ガラス板に貼り付けられたGaAs基板を加工する際に研磨エッチング、その他この後の工程で基板にクラップが入り、このクラックが半導体装置が形成されたチップ上に伸びることにより著しく歩留りを落とすことがある。

【0004】また、このクラック部分から基板がそりガラス板から浮いたり、部分的に欠落し、以降の工程で所望の加工が困難になるという課題があった。

【0005】本発明は従来の上記実情に鑑みてなされたものであり、従って本発明の目的は、従来の技術に内在する上記課題を解決することを可能とした半導体装置の新規な製造方法を提供することにある。

【0006】

【課題を解決するための手段】上記目的を達成するために、本発明に係る半導体装置の製造方法は、ガラス板に貼り付けられた半導体基板を研磨して薄くする前に、裏面にあらかじめ、例えば格子状の溝を形成しておき、この溝の部分に半導体基板を構成する物質と異なる物質を埋め込むことで構成され、これにより応力によるクラックを格子状の溝で発生させ、またチップ上でクラックが発生しても格子単位で食い止めクラックの広がりを防止させるとともに、溝の部分で応力を分散することにより基板のそりを低減する。

【0007】また溝に埋め込んだ物質により溝にクラックが入っても、半導体基板とガラス板を貼り付けている貼り付け剤を裏面加工工程での薬品等の腐食から防ぐことができると同時に研磨中での研磨クズを格子状の溝に入り込まぬようにすることができる。

【0008】

【実施例】次に本発明をその好ましい一実施例について図面を参照しながら具体的に説明する。

【0009】図1(A)〜(D)は本発明による第1の実施例を示す工程図である。

【0010】図1(A)〜(D)を参照するに、まず表面にFETまたは電気回路等が形成されたGaAs基板1を素子部7がガラス板2と密着するようにガラス板2に貼り付ける。次に両面目合わせを行い、GaAs基板1の裏面にチップに分割する際に溝を格子状にフォトレジストをチップの裏面に残し、他の分割領域のレジストを除去し、分割するためのGaAs基板1を露出させ目安のパターンを形成する。

【0011】次に図1(A)のようにGaAs基板1の裏面のレジストを除去してパターニングされた部分をダイサで50μmの厚さが残るように削り格子状の溝1aを作る。溝1aは結晶軸の方向になるようにあらかじめ表面の素子を配置しておく。

【0012】続いて、図1(B)のようにポリイミド3を1000rpmで2度の重ね塗りで塗布し溝1aの部分に少なくとも50μmの厚さにポリイミドが堆積するようにする。

【0013】次にGaAs基板1の裏面全体を研磨、エッチングし、図1(C)のように100μm厚の平坦に形状にする。次いでソース電極をとるためのバイアホール形成、Auめっき等の裏面加工工程を行った後に、ポリイミドをO2 プラズマで除去する。

【0014】次に図1(D)の溝の部分を除くチップ領域をレジストで覆ってGaAsを全てエッチング除去する。続いて、GaAs基板1とガラス板2を分離しチップに分割する。

【0015】図2は本発明による第2の実施例を示す断面図である。

【0016】図2に示された第2の実施例は、第1の実施例で示した分割線を複数個のチップが入るように形成することを特徴とする。ここでは第1の実施例と同様に、裏面を加工した後にチップを分割する直前に図2に示すように、複数個のチップをあらかじめ分割する形状に更に裏面からエッチングして分割するための溝を形成してから、ガラス板2からチップをはがす。これはステップ露光方式(ステッパ)による表面側素子の形成を行って、裏面加工する場合に重要であり、ステッパの1ショット内に複数個の素子をチップ形状を任意にとる場合に重要であり、クラック防止用の溝は1ショット毎のパターンにとる。

【0017】

【発明の効果】以上説明したように、本発明によれば、ガラス板に貼りつけられた半導体基板の裏面に格子状の溝を形成しその溝を厚膜で埋め込むことにより、クラックの広がりの防止、応力によるそりの低減、またそりやクラックによる基板の部分的な欠落を防ぐ効果が得られる。

【0018】本発明によればまた、チップ上にクラックの入った場合に裏面加工工程でのフォトレジストを使った加工時のレジスト厚みの不均一性によるクラック以外でのパターニング不良も防ぐことができ、裏面加工工程での歩留りの向上もできる。

【図面の簡単な説明】

【図1】本発明による第1の実施例の工程フロー図である。

【図2】本発明による第2の実施例の工程フロー図である。

【符号の説明】

1…半導体基板

1a…溝

2…ガラス板

3…ポリイミド

4…レジスト

5…ステッパ1ショット領域

7…素子部

【特許請求の範囲】

【請求項1】 一表面に半導体装置が形成された半導体基板を、この半導体基板を貼り合わせて補強するための補強板に、この半導体基板の表面が密着するように貼り合わせて、この半導体基板の裏面を研磨して薄く加工するに際して、あらかじめこの補強板に貼りつけた半導体基板裏面に少なくとも1本以上の溝を形成した後に、この溝をこの半導体基板を構成する物質とは異なる物質で覆った後、この半導体基板の裏面を研磨することを特徴とする半導体装置の製造方法。

【請求項2】 前記半導体基板の裏面に形成された前記溝の深さは、この半導体基板の裏面研磨後にこの溝が残っている程度であることを更に特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】 前記半導体基板の裏面に形成された前記溝に埋め込まれた物質の厚さは、この半導体基板の裏面研磨後に、この溝に残っている程度であることを更に特徴とする請求項1に記載の半導体装置の製造方法。

【請求項1】 一表面に半導体装置が形成された半導体基板を、この半導体基板を貼り合わせて補強するための補強板に、この半導体基板の表面が密着するように貼り合わせて、この半導体基板の裏面を研磨して薄く加工するに際して、あらかじめこの補強板に貼りつけた半導体基板裏面に少なくとも1本以上の溝を形成した後に、この溝をこの半導体基板を構成する物質とは異なる物質で覆った後、この半導体基板の裏面を研磨することを特徴とする半導体装置の製造方法。

【請求項2】 前記半導体基板の裏面に形成された前記溝の深さは、この半導体基板の裏面研磨後にこの溝が残っている程度であることを更に特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】 前記半導体基板の裏面に形成された前記溝に埋め込まれた物質の厚さは、この半導体基板の裏面研磨後に、この溝に残っている程度であることを更に特徴とする請求項1に記載の半導体装置の製造方法。

【図1】

【図2】

【図2】

【公開番号】特開平5−335292

【公開日】平成5年(1993)12月17日

【国際特許分類】

【出願番号】特願平4−136800

【出願日】平成4年(1992)5月28日

【出願人】(000004237)日本電気株式会社 (19,353)

【公開日】平成5年(1993)12月17日

【国際特許分類】

【出願日】平成4年(1992)5月28日

【出願人】(000004237)日本電気株式会社 (19,353)

[ Back to top ]