半導体装置の製造装置及び半導体装置の製造方法

【課題】ステージを小さくして装置を小型化することができる半導体装置の製造方法を得る。

【解決手段】本発明の半導体装置は、ウェハ10を搭載するステージ31と、ステージ31を覆い、開口部53を有するカバー54と、カバー54の開口部53を通してウェハ10上にチップ20をボンディングするボンディングヘッド32とを備える。そして、カバー54はステージ31に対して回転して開口部53をウェハ10の所望の位置に合わせる。

【解決手段】本発明の半導体装置は、ウェハ10を搭載するステージ31と、ステージ31を覆い、開口部53を有するカバー54と、カバー54の開口部53を通してウェハ10上にチップ20をボンディングするボンディングヘッド32とを備える。そして、カバー54はステージ31に対して回転して開口部53をウェハ10の所望の位置に合わせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆い、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする半導体装置の製造装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

近年、マザーチップにドーターチップをフリップチップ接続したCOC(チップ・オン・チップ)構造を有し、更にマザーチップを回路基板にフリップチップ接続した半導体装置が提案されている。このマザーチップとドーターチップのフリップチップ接続において、両者のメタルポストが半田膜を介して熱圧着される。ここで、マザーチップ及びドーターチップの双方のメタルポスト表面に半田膜を形成したもの(例えば、特許文献1,2参照)や、一方のメタルポスト上にAu膜を形成し、他方のメタルポスト上に半田膜を形成したもの(例えば、特許文献3,4参照)が提案されている。

【0003】

また、COC接続においてチップの傾き調整は、従来は手動で行われ、チップを個片基板に搭載する場合は問題がなかった。しかし、ウェハレベルで行うCOC接続は、広いウェハステージ面積上に高い温度で接合が行われるため、ウェハを搭載するステージには反りが発生する。具体的には、直径30cmのアルミ製ステージの場合、18μm程度の反りが発生する。このため、ウェハレベルのCOC接合を行う場合は接合不良が発生する。具体的には、一辺が1cmのチップだとステージの反りによって、端のバンプで1μm以上の段差が発生する場合があり、その他の機械的な誤差が同時に生じることにより、チップ傾きの許容値2μm程度を超えて接合不良が発生する可能性がある。近年、メタルポストのピッチは小さくなっているので、チップ傾きの許容値も小さくなっている。そこで、プリヒートしたステージの傾きを測定し、ボンディングツールのならい機構でならわせた状態でチップをフリップチップ接続する技術が提案されている(例えば、特許文献5参照)。

【0004】

また、フリップチップ接続において、半田バンプが酸化すると、バンプ同士が接合しなくなる。従って、フラックスレスでチップ接続するには、窒素雰囲気中で行う必要がある。そこで、基板を搭載するステージをカバーで囲って窒素雰囲気とし、カバーに設けられたシャッター付きの開口部からボンディングを行う技術が提案されている(例えば、特許文献6参照)。

【0005】

また、マザーチップ及びドーターチップの表面にそれぞれマークを形成し、両チップの接合後に、ドーターチップの裏面側から両マークを赤外線によって撮像することで、両チップの水平方向の接合ずれの有無を検査する技術が提案されている(例えば、特許文献7参照)。

【0006】

【特許文献1】特開2004−79685号公報

【特許文献2】特開2004−146728号公報

【特許文献3】特開2002−164498号公報

【特許文献4】特開2003−133508号公報

【特許文献5】特開平9−219425号公報

【特許文献6】特開2000−68331号公報

【特許文献7】特開2001−110983号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、従来は、基板を搭載したステージをx−y方向に動かして、カバーの開口部をウェハのボンディング位置に合わせていた。このため、ステージの大きさが基板の2倍以上必要であった。特に近年の直径が大きくなったウェハに対して、その2倍以上の大きさを有するステージもしくは、ステージ格納領域を用意しようとすると、装置が大型化し、装置コストの上昇を招くという問題がある。

【0008】

また、鉛フリー半田を用いた接合においては、接合時に半田を確実に溶融するために、非常に高温に加熱する必要がある。更に、COC接合では、X−Y平面のチップ位置合わせ性能の目安として、半田ピッチの1/10程度を要求されており(50μmピッチの場合、位置合わせ精度は±5μm)、高温下で高精度の位置決め機構を実現する必要がある。この高精度の光学系測定(分解能が0.7μm/pixel×認識誤差±0.5pixel=±0.35μmの場合に許容測定誤差が±0.5μm以下)を実現する場合、高温に昇温されたステージ上の測定対象物に対してカメラを例えば20mm程度にまで近づける必要がある。これに対し、特許文献6に記載されているように、窒素雰囲気の加熱ステージを含む領域と、カメラなどその他の機構を含む領域とをカバーで分離することで、カメラは加熱ステージからの輻射熱によって温まり難くなる。特許文献6には、接合に必要な工程温度までの加熱は、基板を搭載するヒートブロックを用いることが開示されている。しかし、COC接合を実現するにあたって、配線基板などに比較して、極端に面積の大きい、例えば直径30センチの半導体ウェハを、接合に必要な温度までステージを用いて昇温しようとすると、装置全体に対する輻射熱の影響が非常に大きくなり、カメラ自体やカメラを保持する治具が動作保証温度範囲(例えば50℃以下)を超えてしまう可能性がある。

【0009】

また、特許文献7記載の技術では、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することはできないという問題があった。

【0010】

本発明は、上述のような課題を解決するためになされたもので、その第1の目的は、ステージを小さくして装置を小型化することができる半導体装置の製造方法を得るものである。

【0011】

本発明の第2の目的は、ウェハの傾きを測定する測定器を熱から保護し、かつ高精度の接合を実現することができる半導体装置の製造方法を得るものである。

【0012】

本発明の第3の目的は、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することができる半導体装置の製造方法を得るものである。

【課題を解決するための手段】

【0013】

本発明の請求項1に係る半導体装置は、ウェハを搭載するステージと、ステージを覆い、開口部を有するカバーと、カバーの開口部を通してウェハ上にチップをボンディングするボンディングヘッドとを備え、カバーはステージに対して回転して開口部をウェハの所望の位置に合わせる。

【0014】

本発明の請求項2に係る半導体装置の製造方法は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆う工程と、カバーの開口部を通してウェハの傾きを測定器で測定する工程と、ボンディングヘッドによりチップを保持し、チップの傾きをウェハの傾きに合わせて調整する工程と、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする工程とを備え、ステージの温度をウェハとチップとの接合温度よりも低くする。

【0015】

本発明の請求項3に係る半導体装置の製造方法は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆う工程と、カバーの開口部を通してウェハの傾きを測定器で測定する工程と、ボンディングヘッドによりチップを保持し、チップの傾きをウェハの傾きに合わせて調整する工程と、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする工程と、ウェハ上にチップをボンディングした後に、チップとウェハにそれぞれ設けられたマークについて、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、チップとウェハの垂直方向のずれを検査する工程とを備え、ボンディングヘッドにより保持されたチップの傾きをウェハの傾きに合わせて調整する際に、赤外線カメラによる検査結果を反映する。本発明のその他の特徴は以下に明らかにする。

【発明の効果】

【0016】

本発明の請求項1に係る半導体装置により、ステージを小さくして装置を小型化することができる。

【0017】

本発明の請求項2に係る半導体装置の製造方法により、ウェハの傾きを測定する測定器を熱から保護することができる。

【0018】

本発明の請求項3に係る半導体装置の製造方法により、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することができる。

【発明を実施するための最良の形態】

【0019】

実施の形態1.

図1のフローチャート及び他の図面を参照しながら、実施の形態1に係る半導体装置の製造方法について説明する。

【0020】

マザーチップ10の形成工程について説明する。まず、図2(a)に示すように、基板11上(回路面)にAl電極12を形成し、それ以外の領域を例えば、窒化シリコン膜と、ポリイミド膜の積層膜からなる表面保護膜13で覆う。そして、このAl電極12にプローブを当てて検査を行う(ステップS1)。この検査はウェハ上に形成された複数のマザーチップ10に対してそれぞれ行い、ウェハ上の各マザーチップ10の合否を示すウェハマップを作成する。

【0021】

次に、図2(b)に示すように、全面にTi,Cu,Ni,Cr,W等の多層膜からなるバリアメタル14をスパッタ技術又はめっき技術等により形成する。そして、図2(c)に示すように、Al電極12の存在する領域に開口を有するレジスト15を形成し、レジスト15の開口に、前記バリアメタル14を給電膜として利用した電解めっき技術により膜厚5〜10μmのNi膜を充填してメタルポスト16を形成する。このメタルポスト16上に、Sn,Ag,Cu等の何れか若しくはこれらを組み合わせた半田膜17を形成する(ステップS2)。半田膜17としては、本実施の形態においては、Snに1.5wt%のAgを添加した物であるが、半田の組成としては、これに限る物ではない。例えば、Sn−Bi系半田膜や、Sn膜、もしくはSn−Pb共晶半田膜を用いることもできる。但し、半田膜17としては、メタルポスト16よりも融点の低い金属であることが好ましい。従って、Snを含む金属膜であることが好ましい。その後、図2(d)に示すように、レジスト15を除去する。そして、メタルポスト16同士のピッチは20〜100μmである。また、半田膜17の厚みは3〜15μm程度である。メタルポスト16が不要な場合は、メタルポスト16を形成せずに、バリアメタル14上に半田膜17を形成しても良い。

【0022】

次に、ウェハ全面にフラックスを塗布して(ステップS3)、図2(e)に示すように、N2リフロー炉又はN2+H2リフロー炉のような表面酸化が抑制される環境下においてリフロー(溶融)させる(ステップS4)。これにより、半田膜17とメタルポスト16との密着性が向上し、半田膜17の強度が向上する。その後、洗浄を行ってフラックスを除去する(ステップS5)。フラックスの洗浄条件としては、特に限定する物ではないが、ロジン系フラックスを使用する場合は、アルコールなど有機溶媒系の洗浄剤を使用し、水溶性フラックスを使用する場合は、純水などを使用するのが好適である。メタルポスト16の材料として、Ni膜を使用することにより、半田膜17を溶融する工程において、メタルポスト16から半田膜17への金属拡散を抑えることができ、半田膜17の組成への悪影響を抑えることができる。

【0023】

次に、図3(a)に示すように、メタルポスト16をマスクとしてバリアメタル14を異方性エッチングする。そして、図3(b)に示すように、ウェハ厚が所定の厚さ、例えば200〜600μmとなるまでウェハ裏面研磨(バックグラインディング)を行う(ステップS6)。ウェハ裏面研磨(バックグラインディング)工程としては、回転する砥石によってウェハ裏面を機械的に研磨する方法や、エッチング液などによって、化学的にウェハ裏面を溶かして薄くする方法、機械的手段と化学的手段を併用して薄くする方法などを適宜使用することができる。また、ウェハ裏面研磨工程において、ウェハ主面を保護するために、フィルム状の樹脂保護膜であるバックグラインドテープをウェハ主面に貼り付けた状態で行うのが好ましい。なお、ハンドリング等に問題が無ければ、バリアメタル形成前等にウェハ裏面研磨を予め実施することもできる。

【0024】

次に、図3(c)に示すように、半田ボール(後述)を形成する領域に開口を有するメタルマスク18aを形成し、メタルマスク18aの開口に半田ペースト19aを充填して、マザーチップ10上に半田ペーストを印刷する(ステップS7)。半田ペーストには、微細な半田粒子がフラックス中に分散して混合されており、後述するリフロー工程において、フラックスの活性成分から遊離する水素イオンの還元作用により、半田粒子の表面酸化膜は効果的に還元される。半田ペーストに含まれる半田粒子の組成は、本実施例においてはSn−1%Ag−0.5%Cuであるが、これに限る物ではない。

【0025】

次に、図3(d)に示すように、メタルマスク18aを取り外し、酸素濃度が500ppm以下の窒素雰囲気中においてマザーチップ10を加熱して半田ペースト19aをリフロー(溶融)させて半田ボール19を形成する(ステップS8)。半田ボール19を形成するための半田ペーストには、還元作用を有するフラックスが含まれる。フラックスの還元作用によって、ペースト中の半田粒子や、下地の半田膜17表面にある金属酸化膜は除去され、半田ボール19と、下地のメタルポスト16との良好な接続が確保される。このように、フラックスを含有する半田ペーストのリフロー工程においては、最もコストの低い大気雰囲気中の熱処理によってリフローを行うことが一般的であった。しかし、本実施の形態においては、半田ボール19をリフローする工程において、半田ボール19を形成しないメタルポスト上に、既に半田膜17が形成されているという事情がある。従って、一般的な大気雰囲気中での熱処理によるリフロー法を使用すると、半田膜17の露出する表面に例えば10nm以上の膜厚を有する厚い酸化膜が形成され、後に行うCOC接続工程時に、半田接合強度の低下を引き起こす可能性がある。このような特別の問題に顧み、本実施の形態においては、半田ボール19のリフロー工程において、半田ボール19を形成しないメタルポスト上に露出する半田膜17表面に厚い酸化膜が形成されないように、酸素濃度が500ppm以下と酸化性が低い雰囲気において、半田ボール19リフローのための熱処理を施すことが好ましい。

【0026】

このように、半田ボール19を形成するためのリフローを窒素雰囲気中で行うことにより、半田膜17の表面酸化膜の膜厚を数nmに抑えることができる。また、半田ボール19を形成しないメタルポスト上に露出する半田膜17表面に、厚い酸化膜が形成されないようにするための対策として、半田ペーストを塗布した後、半田ボール19のリフロー工程前に、露出する半田膜17上に、還元作用を有するフラックスを塗布した状態で熱処理を施すことも可能である。露出する半田膜17上へのフラックスの塗布方法としては、例えば、露出する半田膜17上のみに、部分的にフラックスを塗布する事も可能であるが、露出する半田膜17表面を含むウェハ全面上にスピンコーティングによりフラックスを塗布するのが最も容易である。なお、半田ボール19は、本実施の形態においては、Sn−1%Ag−0.5%CuからなるPbフリー半田を使用するが、これに限る物ではなく、例えばSn,Ag,Cu等を含む鉛フリー半田、又はSn−Pb共晶半田を使用することができる。また、本実施の形態においては、ボール径が120μmΦ、ボール高さが80μmである。

【0027】

その後、洗浄(ステップS9)及び外観検査(ステップS10)を行う。以上の工程により、マザーチップ10が形成される。

【0028】

次に、ドーターチップ20の形成工程について説明する。まず、図4(a)に示すように、基板21上(回路面)にAl電極22を形成し、それ以外の領域を表面保護膜23で覆う。そして、このAl電極22にプローブを当てて検査を行う(ステップS11)。この検査はウェハ上に形成された複数のドーターチップ20に対してそれぞれ行い、ウェハ上の各ドーターチップ20の合否を示すウェハマップを作成する。

【0029】

次に、図4(b)に示すように、全面にTi,Cu,Ni,Cr,W等の多層膜からなるバリアメタル24をスパッタ技術又はめっき技術等により形成する。バリアメタル24の膜厚は、本実施の形態においては総厚で1μm以下である。そして、図4(c)に示すように、Al電極22の存在する領域に開口を有するレジスト25を形成し、レジスト25の開口に、バリアメタル24を給電膜とした電解めっき技術により膜厚5〜10μmのNi膜を充填してメタルポスト26を形成する。なお、メタルポスト26同士のピッチは20〜100μmである。また、Au膜28の厚みは0.1μm程度である。このメタルポスト26の表面に活性化処理を施した後、メタルポスト26上にAu膜28を無電解メッキ等により形成する(ステップS12)。または、バリアメタル24を給電膜とした電解メッキ技術によりAu膜28を形成しても良い。その後、図4(d)に示すように、レジスト25を除去し、洗浄を行う(ステップS13)。

【0030】

次に、図4(e)に示すように、メタルポスト26をマスクとしてバリアメタル24を異方性エッチングする。そして、ウェハ厚が所定の厚さ、例えば30〜50μmとなるまでウェハ裏面研磨を行う(ステップS14)。ウェハ裏面研磨工程においては、図5に示すように、ウェハ主面の保護のために、ウェハ主面に、表面に粘着層41を有するバックグラインドテープ42を貼り付けた状態で、ウェハ裏面を砥石43により研磨する。ウェハ裏面研磨工程としては、砥石43による機械的研磨に限らず、エッチング液による化学的手段などを適宜使用することができる。

【0031】

ウェハ裏面研磨完了後、図6に示すように、次のダイシング工程を行うために、ウェハ裏面にダイシングテープ44を貼り付け、ウェハ主面のバックグラインドテープ42を剥離する。この際、ウェハ主面上に突出するバリアメタル24、メタルポスト26、Au膜28の厚さを合計した、ウェハ主面上の突起電極の高さが高すぎると、バックグラインドテープ42の粘着層に突起電極が食い込んで、バックグラインドテープ42との粘着力が高くなり、バックグラインドテープ42の剥離の際に、ウェハが割れるなどの問題を起こす可能性がある。また、このような問題は、特に、ウェハ裏面研磨によってウェハを非常に薄くし、ウェハ自体の剛性が大きく低下する場合に特に顕著になる。そこで、バックグラインドテープ42をウェハ主面に貼り付けた状態で、ウェハ裏面研磨によって、ウェハの厚さを100μm以下にする場合には、その後のバックグラインドテープ42の剥離工程で、ウェハが損傷するのを防ぐために、ウェハ主面上に突出する電極の高さ、すなわち本実施の形態においては、バリアメタル24、Niメタルポスト26、Au膜28の合計厚さが15μm以下になるようにするのが好ましい。本実施の形態においては、マザーチップ10側は、ウェハ裏面研磨後の厚さが200〜600μmであるため、マザーチップ10ウェハの方が剛性を確保するのが比較的容易である。そこで、マザーチップ10側のバリアメタル14、Niメタルポスト16、半田膜17の厚さを合計した突起電極の高さを、ドーターチップ20側のバリアメタル24、Niメタルポスト26、Au膜28を合計した突起電極の高さよりも高くしておくことで、ドーターチップ20側の突起電極の高さを低くした場合でも、メタルポスト接合後のマザーチップ10−ドーターチップ20主面間の間隔を十分に確保することができる。また、メタルポスト間の接合材となる半田膜を、マザーチップ10側のみに形成したことも、ドーターチップ20側の突起電極の高さを低くする上で有効である。また、マザーチップ10側の突起電極についても、その高さが15μm以下になるように形成することにより、バックグラインドテープ42を使用したウェハ裏面研磨工程後のバックグラインドテープ剥離工程での過剰な応力の印可を避けることができ好ましい。本実施の形態においては、マザーチップ10側のNiメタルポスト16の厚さが5μm、半田膜17の厚さが5μm、ドーターチップ20側のNiメタルポスト27の厚さが1〜5μm、Au膜28の厚さが0.1μm、それぞれのチップのバリアメタルの厚さは1μm以下となっている。

【0032】

次に、図4(f)に示すように、ウェハ上に形成された複数のドーターチップ20をダイシングにより個々に分離する(ステップS15)。その後、外観検査を行う(ステップS16)。以上の工程により、ドーターチップ20が形成される。なお、ドーターチップ20としてメモリ等の能動素子を用いることや、チップコンデンサ等の受動素子を合わせて搭載することができる。本実施の形態においては、マザーチップ10が外部から入力された信号を処理するCPU(Central Processing Unit)を有するロジック回路チップであり、ドーターチップ20が、CPUの動作時に、動作中のプログラムやデータをキャッシュするキャッシュメモリとして働くDRAM(Dynamic Random Access Memory)を搭載したメモリチップである。本発明の適用対象としては、これらのシステム構成に限る物ではないが、特に高速ロジック回路を有するマザーチップ10と、キャッシュメモリである高速RAM回路を有するドーターチップ20との間を、COC接続し、かつ、マザーチップ10と回路基板33との間をフリップチップ接続することにより、高速かつ高信頼なデータ送受信を実現することができる。

【0033】

次に、マザーチップの回路面にドーターチップをフリップチップ接続する工程について説明する。まず、ステップS1のプローブ検査及びステップS6の外観検査で合格したマザーチップ10の回路面に、ステップS11のプローブ検査及びステップS16の外観検査で合格したドーターチップ20をフリップチップ接続する(ステップS17)。

【0034】

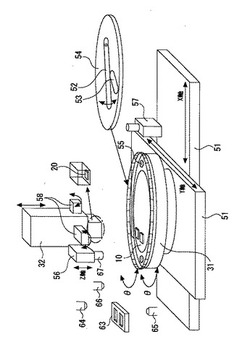

このフリップチップ接続において図7に示す装置を用いる。この装置は、ウェハ状態のマザーチップ10(ウェハ)を搭載するステージ31と、ステージ31を覆い、シャッター52付きの開口部53を有するカバー54と、ステージ31及びカバー54をx軸及びy軸の方向に移動させ、θ方向(ステージ31の中心を軸に水平面内で回転する方向)に回転させるxyθテーブル51と、ウェハの外周からカバー54内に窒素を供給する窒素供給手段55と、カバー54の開口部53を通してマザーチップ10上にドーターチップ20(チップ)をボンディングするボンディングヘッド32と、マザーチップ10を測定する測定器56と、ドーターチップ20を測定する測定器57とを備える。

【0035】

また、ボンディングヘッド32は、保持しているドーターチップ20の傾きを調整するならい角度調整機構58を有する。これに限らず、ステージ31にならい角度調整機構を設けてもよい。これにより、マザーチップ10の傾きに合わせて、ドーターチップ20の傾きを調整することができるため、両者の接合不良を防ぎ、歩留まりを向上させることができる。そして、測定器56,57として、ステージ31の温度や、チップとの非接触を考慮し、レーザー変位計やオートフォーカスのカメラを用いる。

【0036】

図8は、カバーで覆われたステージを示す断面図であり、図9〜11はその上面図である。図9はシャッター52が閉まった状態を示し、図10はシャッター52が開いた状態を示している。そして、図11に示すように、カバー54は、シャッター52の開閉状態に関係なく、ステージ31の回転とは独立してステージ31に対してθ方向に回転して、開口部53をマザーチップ10の所望の位置に合わせることができる。これにより、ステージをx軸及びy軸の方向に動かすことだけでカバー54の開口部53をマザーチップ10の所望の位置に合わせる場合と比較して、ステージ31を小さくすることができる。従って、装置を小型化することができる。また、装置全部ではなくシャッター52内のみを窒素雰囲気にすることで、窒素の使用量を減らすことができる。なお、この装置は直径300mm以下のウェハ全てに対応可能である。

【0037】

実施の形態1に係るフリップチップ接続の方法について、図12に示すフローチャートを参照しながら説明する。まず、ステージ31上にマザーチップ10を搭載し、カバー54でステージ31を覆い、カバー54内に窒素を供給する。そして、ステージ31をプリヒートする。ただし、粘着テープを用いるとステージ31の熱によって変質する場合があるため、粘着フィルムが無い状態で、金属のステージ31上に直接マザーチップ10を吸着させるのが好ましい。

【0038】

次に、カバー54のシャッター52を開いて、測定器56により開口部53を通してマザーチップ10を確認する(ステップS21)。この際、測定器56に搭載した低倍カメラ(2)で測定する。低倍カメラとマザーチップ10の距離は焦点距離が65mm程度を選択し、ステージからの熱影響がないようにする。

【0039】

次に、測定器56によりトレイ63上のドーターチップ20を低倍カメラ64で測定する(ステップS22)。この際、マザーチップと同様に測定器56の焦点距離は、ドーターチップ20との距離が65mm程度を選択する。

【0040】

次に、ドーターチップ20をトレイからピックアップし、ボンディングヘッド32に受け渡す(ステップS23)。そして、測定器56の校正を前記低倍カメラに比較して、倍率の高い高倍カメラ65で行って、測定器56の認識オフセット及びxy座標(データ1)を取得する(ステップS24)。

【0041】

次に、測定器57によりドーターチップ20を高倍カメラ65で認識して、ドーターチップ20のxyθ座標(データ2)を取得する(ステップS25)。そして、低倍カメラ66よりも倍率の高い、測定器56に設置した高倍カメラ67によりマザーチップ10を認識して、マザーチップ10のxyθ座標(データ3)を取得する(ステップS25)。

【0042】

次に、データ1,2,3が設定値内か否かを判定する(ステップS27)。設定値内でない場合は、xyθテーブル51によりステージ31のxyθ方向の補正を行い(ステップS28)、ステップS26に戻る。一方、設定値内である場合は、カバー54のシャッター52を開いて、図13に示すように、ドーターチップ20の回路面をマザーチップ10の回路面と向かい合わせる。そして、ボンディングヘッド32によりカバー54の開口部53を通してマザーチップ10上にドーターチップ20をボンディングする(ステップS29)。その後、次のドーターチップ20について同様の工程を繰り返す(ステップS30)。

【0043】

具体的には、ドーターチップ20をボンディングヘッド32に設けられたヒータにより半田膜17の融点(Sn−Ag系半田の一般的な融点は210〜230℃)よりも高温、例えば300℃に加熱して、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26とを半田膜17を介して熱圧着させる。

【0044】

ここで、半田膜17が薄すぎると、メタルポスト16、26の高さばらつきや、ステージ31とボンディングヘッド32の平行度のばらつきにより、表面酸化膜を破壊するのに十分な応力が発生せず、接合不良が発生する場合がある。そこで、半田膜17の膜厚を5μm以上にすることが望ましい。

【0045】

また、この熱圧着の際に、ステージ31に設けたヒータを調整して、マザーチップ10の温度を半田ボール19の融点よりも低く、例えば100℃〜150℃にして半田ボール19を再溶融させないようにする。これにより、再溶融による半田ボール19の表面の酸化や、半田ボール19同士のリンクを防ぐことができる。なお、ドーターチップ20を半田膜17の融点よりも高温に保ったままフリップチップ接続するが、マザーチップ10が複数形成されたウェハは熱伝導が良く、熱が広がり、マザーチップ10を設置しているステージ31は熱容量が大きいため、温度の上昇を抑制することができる。また、後述するように、半田膜17、および半田ボール19の表面が酸化するのを防止するために、ステージ31付近を窒素環境とする。

【0046】

上記のように、本実施の形態では、ドーターチップ20のメタルポスト26上に、酸化膜がほとんど形成されないAu膜28を形成する。これにより、メタルポスト同士の接合部における酸化膜の総厚を薄くすることができるため、フリップチップ接続の際に確実に酸化膜を破壊することができる。そして、メタルポスト間からの半田膜のはみ出し量を削減することもできる。

【0047】

また、図14に示すように、ドーターチップ20のメタルポスト26上のAu膜28は、高融点の材料であるため、ドーターチップ20が半田膜17の融点以上、例えば300℃に加熱された状態でも、固体の状態を保つ。そして、マザーチップ10は半田ボール19の融点より低い温度、例えば150℃にプリヒートされているため、マザーチップ10のメタルポスト16上の半田膜17も、ドーターチップ20のAu膜28との接触前の状態ではやはり固体の状態を保つ。このような状態で、半田膜17の融点以上に加熱されたAu膜28と、融点以下の温度にプリヒートされた半田膜17を接触させると、半田膜17はAu膜28に接触した部分から部分的に融点以上に加熱され溶融する。そして、メタルポスト16,26間に加重を印可することによって、半田膜17は良好に流動する。特に、Au膜28からの熱伝導によって、半田膜17の溶融が進む間、メタルポスト16,26に荷重を印可し続けることによって、半田膜17表面の酸化膜がより確実に破壊され、半田膜17が溶融した部分から順次流動する。接合工程において印可すべき加重の大きさについて、最低でも、Au膜28−半田膜17界面全体が受ける加重の総和として、ドーターチップ20の重さ以上の加重を、印可しておくことが好ましい。すなわち、半田膜17の融点以上に加熱されたAu膜28と、融点以下の温度にプリヒートされた半田膜17を接触させる工程において、ドーターチップ20裏面に、ボンディングヘッド32から加重を印可しておくことが好ましい。従って、半田膜17表面に厚い酸化膜が形成されていても、COC接続の際に確実に酸化膜を破壊することができる。荷重の大きさとしては、特に限る物ではないが、例えば、少なくとも1電極あたり10mg以上印可しておくことが好ましい。本実施の形態においては、ドーターチップ20とマザーチップ10間を接続する電極の数が10000個である場合に、ドーターチップ20裏面に2kg以上の荷重を印可するものである。本実施の形態のように、電極の接触時に、1電極あたり200mg以上の荷重を印可すると、固体状態の半田膜17表面に形成された酸化膜の破壊を誘発することができ、半田膜17の溶融時の流動性を更に向上することができる。

【0048】

ただし、SnNi合金の成長速度は遅いため、Ni材料からなるメタルポスト16,26間に介在するSn膜の厚さが大きいとメタルポスト16,26間にNi3Sn4合金による架橋が十分に形成されない。従って、Sn層が膜状に残り、このSn層とNi3Sn4合金層の界面に沿って拡散ボイドが膜状に連なって形成され、接合疲労耐性の低下を招くという問題が発生する。そこで、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26の間隔を5μm以下に狭める。これにより、より確実にNi3Sn4合金による架橋を形成することができる。Ni3Sn4合金の架橋が形成されることにより、Sn層は部分的に分断された構成となる。そうすると、Sn層内界面付近に拡散ボイドが発生し、Sn層界面部分の機械的強度が低下した場合でも、ボイドが少なく、比較的機械強度の高いNi3Sn4合金の架橋が形成されることにより、マザーチップ10とドーターチップ20間の接合強度の低下を抑制することができるため、製品の信頼性を向上させることができる。

【0049】

次に、図15に示すように、マザーチップ10主面と、ドーターチップ20主面との間に、ペースト状のアンダーフィル樹脂を注入し、樹脂を硬化させることにより、COC間のアンダーフィル樹脂30を形成する。COC間にアンダーフィル樹脂30を注入するためには、マザーチップ10主面と、ドーターチップ20主面との間隔を10μm以上にすることが好ましい。これは、マザーチップ10主面と、ドーターチップ20主面との間隔が10μm以下になると、アンダーフィル樹脂30の流動抵抗が大きくなり、充填にかかる時間が長くなって、生産性が低下するだけでなく、チップ周辺の流動抵抗が小さい領域を流れるアンダーフィル樹脂と、チップ下の流動抵抗が大きい領域を流れる樹脂との流速の差が大きくなり、チップ間に未充填ボイドが残る可能性も大きくなるからである。

【0050】

次に、図16に示すように、レーザー60を用いたレーザーダイシングにより、ウェハ上に形成された複数のマザーチップ10が形成されたウェハを個々のマザーチップ10に分離する(ステップS18)。ここで、COC接続工程の後は、マザーチップ10の表面は、ドーターチップ20が載り、メタルポスト16,26が形成されて凸凹となっている。従って、ブレードを用いた通常のダイシングを行うと、それにより発生した汚れが洗いきれず、メタルポスト16,26がショートするという問題がある。そこで、汚れが発生しずらいレーザーダイシングを行う。

【0051】

次に、図17に示すように、半田ボール19を用いて回路基板33上にマザーチップ10をフリップチップ接続する(ステップS21)。なお、回路基板33としては、多層有機基板、シリコンインターポーザ、チップ等を用いることができる。その後、マザーチップ10と回路基板33の間に樹脂34を注入してアンダーフィルを行う(ステップS22)。また、外部接続用に回路基板33の下面にアウターボール35を形成する。以上の工程により、マザーチップ10の回路面にドーターチップ20がフリップチップ接続され、このマザーチップ10が回路基板にフリップチップ接続された半導体装置が製造される。

【0052】

なお、この半導体装置において、半田ボール19同士のピッチ(半田ボール19中心同士の距離)が200μm、メタルポスト16(又はメタルポスト26)同士のピッチ(メタルポスト16中心同士の距離)が20〜100μm、ドーターチップ20の厚みが30〜50μm、ドーターチップ20とマザーチップ10の間隔が10〜50μm、半田ボールの直径が120μm、半田ボールの高さが80μm、アウターボール35同士のピッチ(アウターボール35中心同士の距離)が0.6〜1.8mmである。

【0053】

完成した半導体装置は、図18に示すように、半導体装置の外部接続端子であるアウターボール35を介して、例えば、ネットワークサーバーのシステムボードなど、電子装置のマザーボード配線基板45上に接続される。

【0054】

なお、半田膜17表面の酸化膜は薄い方が好ましいので、マザーチップの周辺電極上に半田ボールを接合するリフロー工程で、メタルポスト上の半田表面に厚い酸化膜が形成されないような工程を行うのが好ましい。また、本実施の形態においては、メタルポスト16と、メタルポスト26の直径が同等の場合について記載したが、これに限る物ではない。例えば、メタルポスト16および半田膜17に比較して、メタルポスト26およびAu膜28の平面上の面積が大きな場合には、半田膜17がAu膜28に濡れる面積を大きくすることができ、接合強度を確保する上で有利である。また、加重を印可した状態で熱圧着接合を行う場合は、溶融した半田膜17が流動して、メタルポスト16とAu膜28の間からはみ出す場合があるが、このような場合でも、メタルポスト16の周囲に突出する部分のAu膜28上に、はみ出した半田膜17が濡れ広がるため、隣接する電極同士の半田リークを防ぐことができるため好ましい。

【0055】

また、チップ厚さ100μm以下にウェハ裏面研磨するドーターチップ20については、チップ主面上の突起電極の高さを低くした方が、バックグラインドテープからの剥離時の応力を低減する上で好ましい。これらの事より、本実施の形態においては、マザーチップ10主面上に突出する突起電極の高さを、ドーターチップ20主面上に突出する突起電極より高くしたため、半導体装置の製造工程全体としての生産性をより高めることができる。

【0056】

実施の形態2.

本実施の形態2では、フリップチップ接続の方法が実施の形態1とは異なる。その他の工程は実施の形態1と同様である。実施の形態2に係るフリップチップ接続の方法について、図19に示すフローチャートを参照しながら説明する。

【0057】

まず、実施の形態1と同様にマザーチップ10を確認する(ステップS21)。次に、カバー54のシャッター52を開いて、測定器56により開口部53を通してマザーチップ10を測定して、マザーチップ10の傾き(データ4)を取得する(ステップS31)。この際、図20に示すように、測定器56とマザーチップ10の距離を20.3mmとし、高倍カメラで測定する。ここで、マザーチップ10からカバー54の上面までが18mmであり、マザーチップ10からカバー54の下面までが10mmである。具体的には、マザーチップ10の高さを少なくとも2点測定する。この2点の高さa,bと2点間の水平距離dとから、マザーチップ10の傾きはθ=tan((a−b)/d)であることがわかる。

【0058】

次に、実施の形態1と同様に、トレイ上のドーターチップ20を確認し(ステップS22)、ドーターチップ20をトレイからピックアップし、ボンディングヘッド32に受け渡し(ステップS23)、測定器56の校正を高倍カメラで行って、測定器56の認識オフセット及びxy座標(データ1)を取得する(ステップS24)。

【0059】

次に、測定器57によりドーターチップ20を高倍カメラで認識して、ドーターチップ20のxyθ座標(データ2)と、ドーターチップ20の傾き(データ5)を取得する(ステップS25)。そして、マザーチップ10の傾きとドーターチップ20の傾きの差分が設定値内か否かを判定する(ステップS32)。設定値内でない場合は、ならい角度調整機構58により、ボンディングヘッド32に保持されているドーターチップ20の傾きをマザーチップ10の傾きに合わせて調整し(ステップS33)、ステップS25に戻る。一方、設定値内である場合は、測定器56によりマザーチップ10を高倍カメラで認識して、マザーチップ10のxyθ座標(データ3)を取得する(ステップS25)。

【0060】

次に、データ1,2,3が設定値内か否かを判定する(ステップS27)。設定値内でない場合は、xyθテーブル51によりステージ31のxyθ方向の補正を行い(ステップS28)、ステップS26に戻る。設定値内である場合は、カバー54のシャッター52を開いて、ボンディングヘッド32によりカバー54の開口部53を通してマザーチップ10上にドーターチップ20をボンディングする(ステップS29)。その後、次のドーターチップ20について同様の工程を繰り返す(ステップS30)。

【0061】

上記のように、マザーチップ10の傾きを取得するためには、測定器56とマザーチップ10の距離を20.3mmまで近づける必要がある。そこで、測定器56に対する温度の影響を減少させるために、カバー54によりステージ31からの輻射熱を遮断するだけでなく、ステージ31の温度をなるべく下げてやる。具体的には、ステージ31のプリヒート温度を、マザーチップ10とドーターチップ20との接合温度(〜300℃)や、半田の融点(〜230℃)よりも低い温度(<200℃)、例えば150℃〜200℃にする。これにより、面積の大きなステージ31から測定器56が被る輻射熱を減少させることができる。

【0062】

そして、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26とを半田膜17を介して熱圧着させるために、ドーターチップ20をボンディングヘッド32に設けられたヒータにより例えば300℃に加熱する。ここで、ボンディングヘッド32は、ステージ31よりも測定器56に近い位置に配置されているが、体積が小さいため、ボンディングヘッド32から測定器56が被る熱量は小さい。従って、測定器56の昇温を許容範囲に収めることができる。

【0063】

実施の形態3.

本実施の形態3では、フリップチップ接続の方法が実施の形態1,2とは異なる。その他の工程は実施の形態1,2と同様である。実施の形態3に係るフリップチップ接続の方法について、図21に示すフローチャートを参照しながら説明する。

【0064】

本実施の形態では、図22に示すように、マザーチップ10にマーク61を設け、ドーターチップ20にマーク62を設ける。ここで、図23に示すように、マーク61は例えば丸型とし、マーク62は例えば十字とし、マザーチップ10とドーターチップ20が位置ずれなく接合されている場合に互いに重なるように両マークを配置する。また、両マークを少なくともチップの2コーナー以上に配置し、両マークの周りには他の配線を配置しないようにする。そして、ステップS29においてマザーチップ10上にドーターチップ20をボンディングした後に、マザーチップ10とドーターチップ20にそれぞれ設けられたマーク61,62について赤外線カメラでドーターチップ20の裏面から透過して測定する。ここで、両マークが重ね合わさっているかを調べることで、マザーチップ10とドーターチップ20の水平方向の位置ずれを検査する。そして、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、マザーチップ10とドーターチップ20の垂直方向のずれを検査する(ステップS34)。この垂直方向のずれを2コーナーで測定し、2コーナの水平距離からドーターチップ20の傾き角度を算出することができる。これにより、ドーターチップ20がマザーチップ10に傾いて接続されて接合不良が生じた不良品をスクリーニングすることができる。

【0065】

また、この検査によってドーターチップ20がマザーチップ10に傾いて接続されていることが確認された場合、ステップS32においてボンディングヘッド32により保持されたドーターチップ20の傾きをマザーチップ10の傾きに合わせて調整する際に、赤外線カメラによる測定結果(データ6)を反映して、傾きを補正することができる。これにより測定時間の短縮、歩留向上、自働化を行うことができる。

【0066】

実施の形態4.

図面を参照しながら、本発明の実施の形態4に係る半導体装置の製造方法について説明する。

【0067】

まず、図24(a)に示すように、マザーチップ70として、基板71の表面に、トレンチ電極72と、この電極72に接続するように表面電極73とを形成する。

【0068】

次に、図24(b)に示すように、ウェハ状態のマザーチップ70の表面電極73に、ドーターチップ20のメタルポスト26が接続するように、マザーチップ10の回路面にドーターチップ20をフリップチップ接続する。このフリップチップ接続は、実施の形態1〜3の何れか1つと同様に行う。

【0069】

次に、図24(c)に示すように、ウェハ状態のマザーチップ70の表面及びドーターチップ20をモールド樹脂74で封止する。そして、図24(d)に示すように、マザーチップ70の基板71の裏面を砥石43により研磨して、トレンチ電極72を露出させる。

【0070】

次に、図25(a)に示すように、マザーチップ70の裏面にアウターボール35を形成する。そして、図25(b)に示すように、ブレード75により個々のパッケージをダイシングする。ここで、ドーターチップ20はモールド樹脂74で封止されているため、ダイシングにより発生した汚れがマザーチップ70とドーターチップ20の隙間に入り込むことはない。以上の工程により、図25(c)に示すように、半導体装置が製造される。

【図面の簡単な説明】

【0071】

【図1】本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。

【図2】本発明の実施の形態1に係るマザーチップを形成する工程を示す断面図である。

【図3】本発明の実施の形態1に係るマザーチップを形成する工程を示す断面図である。

【図4】本発明の実施の形態1に係るドーターチップを形成する工程を示す断面図である。

【図5】ウェハ裏面研磨工程を示す断面図である。

【図6】ウェハ裏面にダイシングテープを貼り付け、ウェハ主面のバックグラインドテープを剥離する工程を示す断面図である。

【図7】本発明の実施の形態1に係る半導体装置の製造装置を示す斜視図である。

【図8】カバーで覆われたステージを示す断面図である。

【図9】カバーで覆われたステージを示す上面図である。

【図10】カバーで覆われたステージを示す上面図である。

【図11】カバーで覆われたステージを示す上面図である。

【図12】本発明の実施の形態1に係るフリップチップ接続の方法を示すフローチャートである。

【図13】本発明の実施の形態7に係るマザーチップの回路面にドーターチップをフリップチップ接続する工程を示す断面図である。

【図14】図13のメタルポスト同士の接合部を拡大した断面図である。

【図15】チップ・オン・チップ間のアンダーフィル樹脂を形成する工程を示す断面図である。

【図16】レーザーダイシングを行っている状態を示す断面図である。

【図17】マザーチップを回路基板にフリップチップ接続した状態を示す断面図である。

【図18】完成した半導体装置をアウターボールを介して電子装置のマザーボード配線基板上に接続する工程を示す断面図である。

【図19】本発明の実施の形態2に係るフリップチップ接続の方法を示すフローチャートである。

【図20】測定器により開口部を通してマザーチップを高倍カメラで測定する状態を示す断面図である。

【図21】本発明の実施の形態3に係るフリップチップ接続の方法を示すフローチャートである。

【図22】マークを設けたマザーチップ及びドーターチップを示す断面図である。

【図23】マザーチップのマークとドーターチップのマークの重なり具合を示す上面図である。

【図24】本発明の実施の形態4に係る半導体装置の製造方法を説明するための断面図である。

【図25】本発明の実施の形態4に係る半導体装置の製造方法を説明するための断面図である。

【符号の説明】

【0072】

10 マザーチップ(ウェハ)

20 ドーターチップ(チップ)

31 ステージ

32 ボンディングヘッド

53 開口部

54 カバー

56 測定器

61,62 マーク

【技術分野】

【0001】

本発明は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆い、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする半導体装置の製造装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

近年、マザーチップにドーターチップをフリップチップ接続したCOC(チップ・オン・チップ)構造を有し、更にマザーチップを回路基板にフリップチップ接続した半導体装置が提案されている。このマザーチップとドーターチップのフリップチップ接続において、両者のメタルポストが半田膜を介して熱圧着される。ここで、マザーチップ及びドーターチップの双方のメタルポスト表面に半田膜を形成したもの(例えば、特許文献1,2参照)や、一方のメタルポスト上にAu膜を形成し、他方のメタルポスト上に半田膜を形成したもの(例えば、特許文献3,4参照)が提案されている。

【0003】

また、COC接続においてチップの傾き調整は、従来は手動で行われ、チップを個片基板に搭載する場合は問題がなかった。しかし、ウェハレベルで行うCOC接続は、広いウェハステージ面積上に高い温度で接合が行われるため、ウェハを搭載するステージには反りが発生する。具体的には、直径30cmのアルミ製ステージの場合、18μm程度の反りが発生する。このため、ウェハレベルのCOC接合を行う場合は接合不良が発生する。具体的には、一辺が1cmのチップだとステージの反りによって、端のバンプで1μm以上の段差が発生する場合があり、その他の機械的な誤差が同時に生じることにより、チップ傾きの許容値2μm程度を超えて接合不良が発生する可能性がある。近年、メタルポストのピッチは小さくなっているので、チップ傾きの許容値も小さくなっている。そこで、プリヒートしたステージの傾きを測定し、ボンディングツールのならい機構でならわせた状態でチップをフリップチップ接続する技術が提案されている(例えば、特許文献5参照)。

【0004】

また、フリップチップ接続において、半田バンプが酸化すると、バンプ同士が接合しなくなる。従って、フラックスレスでチップ接続するには、窒素雰囲気中で行う必要がある。そこで、基板を搭載するステージをカバーで囲って窒素雰囲気とし、カバーに設けられたシャッター付きの開口部からボンディングを行う技術が提案されている(例えば、特許文献6参照)。

【0005】

また、マザーチップ及びドーターチップの表面にそれぞれマークを形成し、両チップの接合後に、ドーターチップの裏面側から両マークを赤外線によって撮像することで、両チップの水平方向の接合ずれの有無を検査する技術が提案されている(例えば、特許文献7参照)。

【0006】

【特許文献1】特開2004−79685号公報

【特許文献2】特開2004−146728号公報

【特許文献3】特開2002−164498号公報

【特許文献4】特開2003−133508号公報

【特許文献5】特開平9−219425号公報

【特許文献6】特開2000−68331号公報

【特許文献7】特開2001−110983号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、従来は、基板を搭載したステージをx−y方向に動かして、カバーの開口部をウェハのボンディング位置に合わせていた。このため、ステージの大きさが基板の2倍以上必要であった。特に近年の直径が大きくなったウェハに対して、その2倍以上の大きさを有するステージもしくは、ステージ格納領域を用意しようとすると、装置が大型化し、装置コストの上昇を招くという問題がある。

【0008】

また、鉛フリー半田を用いた接合においては、接合時に半田を確実に溶融するために、非常に高温に加熱する必要がある。更に、COC接合では、X−Y平面のチップ位置合わせ性能の目安として、半田ピッチの1/10程度を要求されており(50μmピッチの場合、位置合わせ精度は±5μm)、高温下で高精度の位置決め機構を実現する必要がある。この高精度の光学系測定(分解能が0.7μm/pixel×認識誤差±0.5pixel=±0.35μmの場合に許容測定誤差が±0.5μm以下)を実現する場合、高温に昇温されたステージ上の測定対象物に対してカメラを例えば20mm程度にまで近づける必要がある。これに対し、特許文献6に記載されているように、窒素雰囲気の加熱ステージを含む領域と、カメラなどその他の機構を含む領域とをカバーで分離することで、カメラは加熱ステージからの輻射熱によって温まり難くなる。特許文献6には、接合に必要な工程温度までの加熱は、基板を搭載するヒートブロックを用いることが開示されている。しかし、COC接合を実現するにあたって、配線基板などに比較して、極端に面積の大きい、例えば直径30センチの半導体ウェハを、接合に必要な温度までステージを用いて昇温しようとすると、装置全体に対する輻射熱の影響が非常に大きくなり、カメラ自体やカメラを保持する治具が動作保証温度範囲(例えば50℃以下)を超えてしまう可能性がある。

【0009】

また、特許文献7記載の技術では、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することはできないという問題があった。

【0010】

本発明は、上述のような課題を解決するためになされたもので、その第1の目的は、ステージを小さくして装置を小型化することができる半導体装置の製造方法を得るものである。

【0011】

本発明の第2の目的は、ウェハの傾きを測定する測定器を熱から保護し、かつ高精度の接合を実現することができる半導体装置の製造方法を得るものである。

【0012】

本発明の第3の目的は、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することができる半導体装置の製造方法を得るものである。

【課題を解決するための手段】

【0013】

本発明の請求項1に係る半導体装置は、ウェハを搭載するステージと、ステージを覆い、開口部を有するカバーと、カバーの開口部を通してウェハ上にチップをボンディングするボンディングヘッドとを備え、カバーはステージに対して回転して開口部をウェハの所望の位置に合わせる。

【0014】

本発明の請求項2に係る半導体装置の製造方法は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆う工程と、カバーの開口部を通してウェハの傾きを測定器で測定する工程と、ボンディングヘッドによりチップを保持し、チップの傾きをウェハの傾きに合わせて調整する工程と、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする工程とを備え、ステージの温度をウェハとチップとの接合温度よりも低くする。

【0015】

本発明の請求項3に係る半導体装置の製造方法は、ステージ上にウェハを搭載し、開口部を有するカバーでステージを覆う工程と、カバーの開口部を通してウェハの傾きを測定器で測定する工程と、ボンディングヘッドによりチップを保持し、チップの傾きをウェハの傾きに合わせて調整する工程と、ボンディングヘッドによりカバーの開口部を通してウェハ上にチップをボンディングする工程と、ウェハ上にチップをボンディングした後に、チップとウェハにそれぞれ設けられたマークについて、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、チップとウェハの垂直方向のずれを検査する工程とを備え、ボンディングヘッドにより保持されたチップの傾きをウェハの傾きに合わせて調整する際に、赤外線カメラによる検査結果を反映する。本発明のその他の特徴は以下に明らかにする。

【発明の効果】

【0016】

本発明の請求項1に係る半導体装置により、ステージを小さくして装置を小型化することができる。

【0017】

本発明の請求項2に係る半導体装置の製造方法により、ウェハの傾きを測定する測定器を熱から保護することができる。

【0018】

本発明の請求項3に係る半導体装置の製造方法により、マザーチップとドーターチップの接合後に、両チップの垂直方向のずれを検査することができる。

【発明を実施するための最良の形態】

【0019】

実施の形態1.

図1のフローチャート及び他の図面を参照しながら、実施の形態1に係る半導体装置の製造方法について説明する。

【0020】

マザーチップ10の形成工程について説明する。まず、図2(a)に示すように、基板11上(回路面)にAl電極12を形成し、それ以外の領域を例えば、窒化シリコン膜と、ポリイミド膜の積層膜からなる表面保護膜13で覆う。そして、このAl電極12にプローブを当てて検査を行う(ステップS1)。この検査はウェハ上に形成された複数のマザーチップ10に対してそれぞれ行い、ウェハ上の各マザーチップ10の合否を示すウェハマップを作成する。

【0021】

次に、図2(b)に示すように、全面にTi,Cu,Ni,Cr,W等の多層膜からなるバリアメタル14をスパッタ技術又はめっき技術等により形成する。そして、図2(c)に示すように、Al電極12の存在する領域に開口を有するレジスト15を形成し、レジスト15の開口に、前記バリアメタル14を給電膜として利用した電解めっき技術により膜厚5〜10μmのNi膜を充填してメタルポスト16を形成する。このメタルポスト16上に、Sn,Ag,Cu等の何れか若しくはこれらを組み合わせた半田膜17を形成する(ステップS2)。半田膜17としては、本実施の形態においては、Snに1.5wt%のAgを添加した物であるが、半田の組成としては、これに限る物ではない。例えば、Sn−Bi系半田膜や、Sn膜、もしくはSn−Pb共晶半田膜を用いることもできる。但し、半田膜17としては、メタルポスト16よりも融点の低い金属であることが好ましい。従って、Snを含む金属膜であることが好ましい。その後、図2(d)に示すように、レジスト15を除去する。そして、メタルポスト16同士のピッチは20〜100μmである。また、半田膜17の厚みは3〜15μm程度である。メタルポスト16が不要な場合は、メタルポスト16を形成せずに、バリアメタル14上に半田膜17を形成しても良い。

【0022】

次に、ウェハ全面にフラックスを塗布して(ステップS3)、図2(e)に示すように、N2リフロー炉又はN2+H2リフロー炉のような表面酸化が抑制される環境下においてリフロー(溶融)させる(ステップS4)。これにより、半田膜17とメタルポスト16との密着性が向上し、半田膜17の強度が向上する。その後、洗浄を行ってフラックスを除去する(ステップS5)。フラックスの洗浄条件としては、特に限定する物ではないが、ロジン系フラックスを使用する場合は、アルコールなど有機溶媒系の洗浄剤を使用し、水溶性フラックスを使用する場合は、純水などを使用するのが好適である。メタルポスト16の材料として、Ni膜を使用することにより、半田膜17を溶融する工程において、メタルポスト16から半田膜17への金属拡散を抑えることができ、半田膜17の組成への悪影響を抑えることができる。

【0023】

次に、図3(a)に示すように、メタルポスト16をマスクとしてバリアメタル14を異方性エッチングする。そして、図3(b)に示すように、ウェハ厚が所定の厚さ、例えば200〜600μmとなるまでウェハ裏面研磨(バックグラインディング)を行う(ステップS6)。ウェハ裏面研磨(バックグラインディング)工程としては、回転する砥石によってウェハ裏面を機械的に研磨する方法や、エッチング液などによって、化学的にウェハ裏面を溶かして薄くする方法、機械的手段と化学的手段を併用して薄くする方法などを適宜使用することができる。また、ウェハ裏面研磨工程において、ウェハ主面を保護するために、フィルム状の樹脂保護膜であるバックグラインドテープをウェハ主面に貼り付けた状態で行うのが好ましい。なお、ハンドリング等に問題が無ければ、バリアメタル形成前等にウェハ裏面研磨を予め実施することもできる。

【0024】

次に、図3(c)に示すように、半田ボール(後述)を形成する領域に開口を有するメタルマスク18aを形成し、メタルマスク18aの開口に半田ペースト19aを充填して、マザーチップ10上に半田ペーストを印刷する(ステップS7)。半田ペーストには、微細な半田粒子がフラックス中に分散して混合されており、後述するリフロー工程において、フラックスの活性成分から遊離する水素イオンの還元作用により、半田粒子の表面酸化膜は効果的に還元される。半田ペーストに含まれる半田粒子の組成は、本実施例においてはSn−1%Ag−0.5%Cuであるが、これに限る物ではない。

【0025】

次に、図3(d)に示すように、メタルマスク18aを取り外し、酸素濃度が500ppm以下の窒素雰囲気中においてマザーチップ10を加熱して半田ペースト19aをリフロー(溶融)させて半田ボール19を形成する(ステップS8)。半田ボール19を形成するための半田ペーストには、還元作用を有するフラックスが含まれる。フラックスの還元作用によって、ペースト中の半田粒子や、下地の半田膜17表面にある金属酸化膜は除去され、半田ボール19と、下地のメタルポスト16との良好な接続が確保される。このように、フラックスを含有する半田ペーストのリフロー工程においては、最もコストの低い大気雰囲気中の熱処理によってリフローを行うことが一般的であった。しかし、本実施の形態においては、半田ボール19をリフローする工程において、半田ボール19を形成しないメタルポスト上に、既に半田膜17が形成されているという事情がある。従って、一般的な大気雰囲気中での熱処理によるリフロー法を使用すると、半田膜17の露出する表面に例えば10nm以上の膜厚を有する厚い酸化膜が形成され、後に行うCOC接続工程時に、半田接合強度の低下を引き起こす可能性がある。このような特別の問題に顧み、本実施の形態においては、半田ボール19のリフロー工程において、半田ボール19を形成しないメタルポスト上に露出する半田膜17表面に厚い酸化膜が形成されないように、酸素濃度が500ppm以下と酸化性が低い雰囲気において、半田ボール19リフローのための熱処理を施すことが好ましい。

【0026】

このように、半田ボール19を形成するためのリフローを窒素雰囲気中で行うことにより、半田膜17の表面酸化膜の膜厚を数nmに抑えることができる。また、半田ボール19を形成しないメタルポスト上に露出する半田膜17表面に、厚い酸化膜が形成されないようにするための対策として、半田ペーストを塗布した後、半田ボール19のリフロー工程前に、露出する半田膜17上に、還元作用を有するフラックスを塗布した状態で熱処理を施すことも可能である。露出する半田膜17上へのフラックスの塗布方法としては、例えば、露出する半田膜17上のみに、部分的にフラックスを塗布する事も可能であるが、露出する半田膜17表面を含むウェハ全面上にスピンコーティングによりフラックスを塗布するのが最も容易である。なお、半田ボール19は、本実施の形態においては、Sn−1%Ag−0.5%CuからなるPbフリー半田を使用するが、これに限る物ではなく、例えばSn,Ag,Cu等を含む鉛フリー半田、又はSn−Pb共晶半田を使用することができる。また、本実施の形態においては、ボール径が120μmΦ、ボール高さが80μmである。

【0027】

その後、洗浄(ステップS9)及び外観検査(ステップS10)を行う。以上の工程により、マザーチップ10が形成される。

【0028】

次に、ドーターチップ20の形成工程について説明する。まず、図4(a)に示すように、基板21上(回路面)にAl電極22を形成し、それ以外の領域を表面保護膜23で覆う。そして、このAl電極22にプローブを当てて検査を行う(ステップS11)。この検査はウェハ上に形成された複数のドーターチップ20に対してそれぞれ行い、ウェハ上の各ドーターチップ20の合否を示すウェハマップを作成する。

【0029】

次に、図4(b)に示すように、全面にTi,Cu,Ni,Cr,W等の多層膜からなるバリアメタル24をスパッタ技術又はめっき技術等により形成する。バリアメタル24の膜厚は、本実施の形態においては総厚で1μm以下である。そして、図4(c)に示すように、Al電極22の存在する領域に開口を有するレジスト25を形成し、レジスト25の開口に、バリアメタル24を給電膜とした電解めっき技術により膜厚5〜10μmのNi膜を充填してメタルポスト26を形成する。なお、メタルポスト26同士のピッチは20〜100μmである。また、Au膜28の厚みは0.1μm程度である。このメタルポスト26の表面に活性化処理を施した後、メタルポスト26上にAu膜28を無電解メッキ等により形成する(ステップS12)。または、バリアメタル24を給電膜とした電解メッキ技術によりAu膜28を形成しても良い。その後、図4(d)に示すように、レジスト25を除去し、洗浄を行う(ステップS13)。

【0030】

次に、図4(e)に示すように、メタルポスト26をマスクとしてバリアメタル24を異方性エッチングする。そして、ウェハ厚が所定の厚さ、例えば30〜50μmとなるまでウェハ裏面研磨を行う(ステップS14)。ウェハ裏面研磨工程においては、図5に示すように、ウェハ主面の保護のために、ウェハ主面に、表面に粘着層41を有するバックグラインドテープ42を貼り付けた状態で、ウェハ裏面を砥石43により研磨する。ウェハ裏面研磨工程としては、砥石43による機械的研磨に限らず、エッチング液による化学的手段などを適宜使用することができる。

【0031】

ウェハ裏面研磨完了後、図6に示すように、次のダイシング工程を行うために、ウェハ裏面にダイシングテープ44を貼り付け、ウェハ主面のバックグラインドテープ42を剥離する。この際、ウェハ主面上に突出するバリアメタル24、メタルポスト26、Au膜28の厚さを合計した、ウェハ主面上の突起電極の高さが高すぎると、バックグラインドテープ42の粘着層に突起電極が食い込んで、バックグラインドテープ42との粘着力が高くなり、バックグラインドテープ42の剥離の際に、ウェハが割れるなどの問題を起こす可能性がある。また、このような問題は、特に、ウェハ裏面研磨によってウェハを非常に薄くし、ウェハ自体の剛性が大きく低下する場合に特に顕著になる。そこで、バックグラインドテープ42をウェハ主面に貼り付けた状態で、ウェハ裏面研磨によって、ウェハの厚さを100μm以下にする場合には、その後のバックグラインドテープ42の剥離工程で、ウェハが損傷するのを防ぐために、ウェハ主面上に突出する電極の高さ、すなわち本実施の形態においては、バリアメタル24、Niメタルポスト26、Au膜28の合計厚さが15μm以下になるようにするのが好ましい。本実施の形態においては、マザーチップ10側は、ウェハ裏面研磨後の厚さが200〜600μmであるため、マザーチップ10ウェハの方が剛性を確保するのが比較的容易である。そこで、マザーチップ10側のバリアメタル14、Niメタルポスト16、半田膜17の厚さを合計した突起電極の高さを、ドーターチップ20側のバリアメタル24、Niメタルポスト26、Au膜28を合計した突起電極の高さよりも高くしておくことで、ドーターチップ20側の突起電極の高さを低くした場合でも、メタルポスト接合後のマザーチップ10−ドーターチップ20主面間の間隔を十分に確保することができる。また、メタルポスト間の接合材となる半田膜を、マザーチップ10側のみに形成したことも、ドーターチップ20側の突起電極の高さを低くする上で有効である。また、マザーチップ10側の突起電極についても、その高さが15μm以下になるように形成することにより、バックグラインドテープ42を使用したウェハ裏面研磨工程後のバックグラインドテープ剥離工程での過剰な応力の印可を避けることができ好ましい。本実施の形態においては、マザーチップ10側のNiメタルポスト16の厚さが5μm、半田膜17の厚さが5μm、ドーターチップ20側のNiメタルポスト27の厚さが1〜5μm、Au膜28の厚さが0.1μm、それぞれのチップのバリアメタルの厚さは1μm以下となっている。

【0032】

次に、図4(f)に示すように、ウェハ上に形成された複数のドーターチップ20をダイシングにより個々に分離する(ステップS15)。その後、外観検査を行う(ステップS16)。以上の工程により、ドーターチップ20が形成される。なお、ドーターチップ20としてメモリ等の能動素子を用いることや、チップコンデンサ等の受動素子を合わせて搭載することができる。本実施の形態においては、マザーチップ10が外部から入力された信号を処理するCPU(Central Processing Unit)を有するロジック回路チップであり、ドーターチップ20が、CPUの動作時に、動作中のプログラムやデータをキャッシュするキャッシュメモリとして働くDRAM(Dynamic Random Access Memory)を搭載したメモリチップである。本発明の適用対象としては、これらのシステム構成に限る物ではないが、特に高速ロジック回路を有するマザーチップ10と、キャッシュメモリである高速RAM回路を有するドーターチップ20との間を、COC接続し、かつ、マザーチップ10と回路基板33との間をフリップチップ接続することにより、高速かつ高信頼なデータ送受信を実現することができる。

【0033】

次に、マザーチップの回路面にドーターチップをフリップチップ接続する工程について説明する。まず、ステップS1のプローブ検査及びステップS6の外観検査で合格したマザーチップ10の回路面に、ステップS11のプローブ検査及びステップS16の外観検査で合格したドーターチップ20をフリップチップ接続する(ステップS17)。

【0034】

このフリップチップ接続において図7に示す装置を用いる。この装置は、ウェハ状態のマザーチップ10(ウェハ)を搭載するステージ31と、ステージ31を覆い、シャッター52付きの開口部53を有するカバー54と、ステージ31及びカバー54をx軸及びy軸の方向に移動させ、θ方向(ステージ31の中心を軸に水平面内で回転する方向)に回転させるxyθテーブル51と、ウェハの外周からカバー54内に窒素を供給する窒素供給手段55と、カバー54の開口部53を通してマザーチップ10上にドーターチップ20(チップ)をボンディングするボンディングヘッド32と、マザーチップ10を測定する測定器56と、ドーターチップ20を測定する測定器57とを備える。

【0035】

また、ボンディングヘッド32は、保持しているドーターチップ20の傾きを調整するならい角度調整機構58を有する。これに限らず、ステージ31にならい角度調整機構を設けてもよい。これにより、マザーチップ10の傾きに合わせて、ドーターチップ20の傾きを調整することができるため、両者の接合不良を防ぎ、歩留まりを向上させることができる。そして、測定器56,57として、ステージ31の温度や、チップとの非接触を考慮し、レーザー変位計やオートフォーカスのカメラを用いる。

【0036】

図8は、カバーで覆われたステージを示す断面図であり、図9〜11はその上面図である。図9はシャッター52が閉まった状態を示し、図10はシャッター52が開いた状態を示している。そして、図11に示すように、カバー54は、シャッター52の開閉状態に関係なく、ステージ31の回転とは独立してステージ31に対してθ方向に回転して、開口部53をマザーチップ10の所望の位置に合わせることができる。これにより、ステージをx軸及びy軸の方向に動かすことだけでカバー54の開口部53をマザーチップ10の所望の位置に合わせる場合と比較して、ステージ31を小さくすることができる。従って、装置を小型化することができる。また、装置全部ではなくシャッター52内のみを窒素雰囲気にすることで、窒素の使用量を減らすことができる。なお、この装置は直径300mm以下のウェハ全てに対応可能である。

【0037】

実施の形態1に係るフリップチップ接続の方法について、図12に示すフローチャートを参照しながら説明する。まず、ステージ31上にマザーチップ10を搭載し、カバー54でステージ31を覆い、カバー54内に窒素を供給する。そして、ステージ31をプリヒートする。ただし、粘着テープを用いるとステージ31の熱によって変質する場合があるため、粘着フィルムが無い状態で、金属のステージ31上に直接マザーチップ10を吸着させるのが好ましい。

【0038】

次に、カバー54のシャッター52を開いて、測定器56により開口部53を通してマザーチップ10を確認する(ステップS21)。この際、測定器56に搭載した低倍カメラ(2)で測定する。低倍カメラとマザーチップ10の距離は焦点距離が65mm程度を選択し、ステージからの熱影響がないようにする。

【0039】

次に、測定器56によりトレイ63上のドーターチップ20を低倍カメラ64で測定する(ステップS22)。この際、マザーチップと同様に測定器56の焦点距離は、ドーターチップ20との距離が65mm程度を選択する。

【0040】

次に、ドーターチップ20をトレイからピックアップし、ボンディングヘッド32に受け渡す(ステップS23)。そして、測定器56の校正を前記低倍カメラに比較して、倍率の高い高倍カメラ65で行って、測定器56の認識オフセット及びxy座標(データ1)を取得する(ステップS24)。

【0041】

次に、測定器57によりドーターチップ20を高倍カメラ65で認識して、ドーターチップ20のxyθ座標(データ2)を取得する(ステップS25)。そして、低倍カメラ66よりも倍率の高い、測定器56に設置した高倍カメラ67によりマザーチップ10を認識して、マザーチップ10のxyθ座標(データ3)を取得する(ステップS25)。

【0042】

次に、データ1,2,3が設定値内か否かを判定する(ステップS27)。設定値内でない場合は、xyθテーブル51によりステージ31のxyθ方向の補正を行い(ステップS28)、ステップS26に戻る。一方、設定値内である場合は、カバー54のシャッター52を開いて、図13に示すように、ドーターチップ20の回路面をマザーチップ10の回路面と向かい合わせる。そして、ボンディングヘッド32によりカバー54の開口部53を通してマザーチップ10上にドーターチップ20をボンディングする(ステップS29)。その後、次のドーターチップ20について同様の工程を繰り返す(ステップS30)。

【0043】

具体的には、ドーターチップ20をボンディングヘッド32に設けられたヒータにより半田膜17の融点(Sn−Ag系半田の一般的な融点は210〜230℃)よりも高温、例えば300℃に加熱して、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26とを半田膜17を介して熱圧着させる。

【0044】

ここで、半田膜17が薄すぎると、メタルポスト16、26の高さばらつきや、ステージ31とボンディングヘッド32の平行度のばらつきにより、表面酸化膜を破壊するのに十分な応力が発生せず、接合不良が発生する場合がある。そこで、半田膜17の膜厚を5μm以上にすることが望ましい。

【0045】

また、この熱圧着の際に、ステージ31に設けたヒータを調整して、マザーチップ10の温度を半田ボール19の融点よりも低く、例えば100℃〜150℃にして半田ボール19を再溶融させないようにする。これにより、再溶融による半田ボール19の表面の酸化や、半田ボール19同士のリンクを防ぐことができる。なお、ドーターチップ20を半田膜17の融点よりも高温に保ったままフリップチップ接続するが、マザーチップ10が複数形成されたウェハは熱伝導が良く、熱が広がり、マザーチップ10を設置しているステージ31は熱容量が大きいため、温度の上昇を抑制することができる。また、後述するように、半田膜17、および半田ボール19の表面が酸化するのを防止するために、ステージ31付近を窒素環境とする。

【0046】

上記のように、本実施の形態では、ドーターチップ20のメタルポスト26上に、酸化膜がほとんど形成されないAu膜28を形成する。これにより、メタルポスト同士の接合部における酸化膜の総厚を薄くすることができるため、フリップチップ接続の際に確実に酸化膜を破壊することができる。そして、メタルポスト間からの半田膜のはみ出し量を削減することもできる。

【0047】

また、図14に示すように、ドーターチップ20のメタルポスト26上のAu膜28は、高融点の材料であるため、ドーターチップ20が半田膜17の融点以上、例えば300℃に加熱された状態でも、固体の状態を保つ。そして、マザーチップ10は半田ボール19の融点より低い温度、例えば150℃にプリヒートされているため、マザーチップ10のメタルポスト16上の半田膜17も、ドーターチップ20のAu膜28との接触前の状態ではやはり固体の状態を保つ。このような状態で、半田膜17の融点以上に加熱されたAu膜28と、融点以下の温度にプリヒートされた半田膜17を接触させると、半田膜17はAu膜28に接触した部分から部分的に融点以上に加熱され溶融する。そして、メタルポスト16,26間に加重を印可することによって、半田膜17は良好に流動する。特に、Au膜28からの熱伝導によって、半田膜17の溶融が進む間、メタルポスト16,26に荷重を印可し続けることによって、半田膜17表面の酸化膜がより確実に破壊され、半田膜17が溶融した部分から順次流動する。接合工程において印可すべき加重の大きさについて、最低でも、Au膜28−半田膜17界面全体が受ける加重の総和として、ドーターチップ20の重さ以上の加重を、印可しておくことが好ましい。すなわち、半田膜17の融点以上に加熱されたAu膜28と、融点以下の温度にプリヒートされた半田膜17を接触させる工程において、ドーターチップ20裏面に、ボンディングヘッド32から加重を印可しておくことが好ましい。従って、半田膜17表面に厚い酸化膜が形成されていても、COC接続の際に確実に酸化膜を破壊することができる。荷重の大きさとしては、特に限る物ではないが、例えば、少なくとも1電極あたり10mg以上印可しておくことが好ましい。本実施の形態においては、ドーターチップ20とマザーチップ10間を接続する電極の数が10000個である場合に、ドーターチップ20裏面に2kg以上の荷重を印可するものである。本実施の形態のように、電極の接触時に、1電極あたり200mg以上の荷重を印可すると、固体状態の半田膜17表面に形成された酸化膜の破壊を誘発することができ、半田膜17の溶融時の流動性を更に向上することができる。

【0048】

ただし、SnNi合金の成長速度は遅いため、Ni材料からなるメタルポスト16,26間に介在するSn膜の厚さが大きいとメタルポスト16,26間にNi3Sn4合金による架橋が十分に形成されない。従って、Sn層が膜状に残り、このSn層とNi3Sn4合金層の界面に沿って拡散ボイドが膜状に連なって形成され、接合疲労耐性の低下を招くという問題が発生する。そこで、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26の間隔を5μm以下に狭める。これにより、より確実にNi3Sn4合金による架橋を形成することができる。Ni3Sn4合金の架橋が形成されることにより、Sn層は部分的に分断された構成となる。そうすると、Sn層内界面付近に拡散ボイドが発生し、Sn層界面部分の機械的強度が低下した場合でも、ボイドが少なく、比較的機械強度の高いNi3Sn4合金の架橋が形成されることにより、マザーチップ10とドーターチップ20間の接合強度の低下を抑制することができるため、製品の信頼性を向上させることができる。

【0049】

次に、図15に示すように、マザーチップ10主面と、ドーターチップ20主面との間に、ペースト状のアンダーフィル樹脂を注入し、樹脂を硬化させることにより、COC間のアンダーフィル樹脂30を形成する。COC間にアンダーフィル樹脂30を注入するためには、マザーチップ10主面と、ドーターチップ20主面との間隔を10μm以上にすることが好ましい。これは、マザーチップ10主面と、ドーターチップ20主面との間隔が10μm以下になると、アンダーフィル樹脂30の流動抵抗が大きくなり、充填にかかる時間が長くなって、生産性が低下するだけでなく、チップ周辺の流動抵抗が小さい領域を流れるアンダーフィル樹脂と、チップ下の流動抵抗が大きい領域を流れる樹脂との流速の差が大きくなり、チップ間に未充填ボイドが残る可能性も大きくなるからである。

【0050】

次に、図16に示すように、レーザー60を用いたレーザーダイシングにより、ウェハ上に形成された複数のマザーチップ10が形成されたウェハを個々のマザーチップ10に分離する(ステップS18)。ここで、COC接続工程の後は、マザーチップ10の表面は、ドーターチップ20が載り、メタルポスト16,26が形成されて凸凹となっている。従って、ブレードを用いた通常のダイシングを行うと、それにより発生した汚れが洗いきれず、メタルポスト16,26がショートするという問題がある。そこで、汚れが発生しずらいレーザーダイシングを行う。

【0051】

次に、図17に示すように、半田ボール19を用いて回路基板33上にマザーチップ10をフリップチップ接続する(ステップS21)。なお、回路基板33としては、多層有機基板、シリコンインターポーザ、チップ等を用いることができる。その後、マザーチップ10と回路基板33の間に樹脂34を注入してアンダーフィルを行う(ステップS22)。また、外部接続用に回路基板33の下面にアウターボール35を形成する。以上の工程により、マザーチップ10の回路面にドーターチップ20がフリップチップ接続され、このマザーチップ10が回路基板にフリップチップ接続された半導体装置が製造される。

【0052】

なお、この半導体装置において、半田ボール19同士のピッチ(半田ボール19中心同士の距離)が200μm、メタルポスト16(又はメタルポスト26)同士のピッチ(メタルポスト16中心同士の距離)が20〜100μm、ドーターチップ20の厚みが30〜50μm、ドーターチップ20とマザーチップ10の間隔が10〜50μm、半田ボールの直径が120μm、半田ボールの高さが80μm、アウターボール35同士のピッチ(アウターボール35中心同士の距離)が0.6〜1.8mmである。

【0053】

完成した半導体装置は、図18に示すように、半導体装置の外部接続端子であるアウターボール35を介して、例えば、ネットワークサーバーのシステムボードなど、電子装置のマザーボード配線基板45上に接続される。

【0054】

なお、半田膜17表面の酸化膜は薄い方が好ましいので、マザーチップの周辺電極上に半田ボールを接合するリフロー工程で、メタルポスト上の半田表面に厚い酸化膜が形成されないような工程を行うのが好ましい。また、本実施の形態においては、メタルポスト16と、メタルポスト26の直径が同等の場合について記載したが、これに限る物ではない。例えば、メタルポスト16および半田膜17に比較して、メタルポスト26およびAu膜28の平面上の面積が大きな場合には、半田膜17がAu膜28に濡れる面積を大きくすることができ、接合強度を確保する上で有利である。また、加重を印可した状態で熱圧着接合を行う場合は、溶融した半田膜17が流動して、メタルポスト16とAu膜28の間からはみ出す場合があるが、このような場合でも、メタルポスト16の周囲に突出する部分のAu膜28上に、はみ出した半田膜17が濡れ広がるため、隣接する電極同士の半田リークを防ぐことができるため好ましい。

【0055】

また、チップ厚さ100μm以下にウェハ裏面研磨するドーターチップ20については、チップ主面上の突起電極の高さを低くした方が、バックグラインドテープからの剥離時の応力を低減する上で好ましい。これらの事より、本実施の形態においては、マザーチップ10主面上に突出する突起電極の高さを、ドーターチップ20主面上に突出する突起電極より高くしたため、半導体装置の製造工程全体としての生産性をより高めることができる。

【0056】

実施の形態2.

本実施の形態2では、フリップチップ接続の方法が実施の形態1とは異なる。その他の工程は実施の形態1と同様である。実施の形態2に係るフリップチップ接続の方法について、図19に示すフローチャートを参照しながら説明する。

【0057】

まず、実施の形態1と同様にマザーチップ10を確認する(ステップS21)。次に、カバー54のシャッター52を開いて、測定器56により開口部53を通してマザーチップ10を測定して、マザーチップ10の傾き(データ4)を取得する(ステップS31)。この際、図20に示すように、測定器56とマザーチップ10の距離を20.3mmとし、高倍カメラで測定する。ここで、マザーチップ10からカバー54の上面までが18mmであり、マザーチップ10からカバー54の下面までが10mmである。具体的には、マザーチップ10の高さを少なくとも2点測定する。この2点の高さa,bと2点間の水平距離dとから、マザーチップ10の傾きはθ=tan((a−b)/d)であることがわかる。

【0058】

次に、実施の形態1と同様に、トレイ上のドーターチップ20を確認し(ステップS22)、ドーターチップ20をトレイからピックアップし、ボンディングヘッド32に受け渡し(ステップS23)、測定器56の校正を高倍カメラで行って、測定器56の認識オフセット及びxy座標(データ1)を取得する(ステップS24)。

【0059】

次に、測定器57によりドーターチップ20を高倍カメラで認識して、ドーターチップ20のxyθ座標(データ2)と、ドーターチップ20の傾き(データ5)を取得する(ステップS25)。そして、マザーチップ10の傾きとドーターチップ20の傾きの差分が設定値内か否かを判定する(ステップS32)。設定値内でない場合は、ならい角度調整機構58により、ボンディングヘッド32に保持されているドーターチップ20の傾きをマザーチップ10の傾きに合わせて調整し(ステップS33)、ステップS25に戻る。一方、設定値内である場合は、測定器56によりマザーチップ10を高倍カメラで認識して、マザーチップ10のxyθ座標(データ3)を取得する(ステップS25)。

【0060】

次に、データ1,2,3が設定値内か否かを判定する(ステップS27)。設定値内でない場合は、xyθテーブル51によりステージ31のxyθ方向の補正を行い(ステップS28)、ステップS26に戻る。設定値内である場合は、カバー54のシャッター52を開いて、ボンディングヘッド32によりカバー54の開口部53を通してマザーチップ10上にドーターチップ20をボンディングする(ステップS29)。その後、次のドーターチップ20について同様の工程を繰り返す(ステップS30)。

【0061】

上記のように、マザーチップ10の傾きを取得するためには、測定器56とマザーチップ10の距離を20.3mmまで近づける必要がある。そこで、測定器56に対する温度の影響を減少させるために、カバー54によりステージ31からの輻射熱を遮断するだけでなく、ステージ31の温度をなるべく下げてやる。具体的には、ステージ31のプリヒート温度を、マザーチップ10とドーターチップ20との接合温度(〜300℃)や、半田の融点(〜230℃)よりも低い温度(<200℃)、例えば150℃〜200℃にする。これにより、面積の大きなステージ31から測定器56が被る輻射熱を減少させることができる。

【0062】

そして、マザーチップ10のメタルポスト16とドーターチップ20のメタルポスト26とを半田膜17を介して熱圧着させるために、ドーターチップ20をボンディングヘッド32に設けられたヒータにより例えば300℃に加熱する。ここで、ボンディングヘッド32は、ステージ31よりも測定器56に近い位置に配置されているが、体積が小さいため、ボンディングヘッド32から測定器56が被る熱量は小さい。従って、測定器56の昇温を許容範囲に収めることができる。

【0063】

実施の形態3.

本実施の形態3では、フリップチップ接続の方法が実施の形態1,2とは異なる。その他の工程は実施の形態1,2と同様である。実施の形態3に係るフリップチップ接続の方法について、図21に示すフローチャートを参照しながら説明する。

【0064】

本実施の形態では、図22に示すように、マザーチップ10にマーク61を設け、ドーターチップ20にマーク62を設ける。ここで、図23に示すように、マーク61は例えば丸型とし、マーク62は例えば十字とし、マザーチップ10とドーターチップ20が位置ずれなく接合されている場合に互いに重なるように両マークを配置する。また、両マークを少なくともチップの2コーナー以上に配置し、両マークの周りには他の配線を配置しないようにする。そして、ステップS29においてマザーチップ10上にドーターチップ20をボンディングした後に、マザーチップ10とドーターチップ20にそれぞれ設けられたマーク61,62について赤外線カメラでドーターチップ20の裏面から透過して測定する。ここで、両マークが重ね合わさっているかを調べることで、マザーチップ10とドーターチップ20の水平方向の位置ずれを検査する。そして、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、マザーチップ10とドーターチップ20の垂直方向のずれを検査する(ステップS34)。この垂直方向のずれを2コーナーで測定し、2コーナの水平距離からドーターチップ20の傾き角度を算出することができる。これにより、ドーターチップ20がマザーチップ10に傾いて接続されて接合不良が生じた不良品をスクリーニングすることができる。

【0065】

また、この検査によってドーターチップ20がマザーチップ10に傾いて接続されていることが確認された場合、ステップS32においてボンディングヘッド32により保持されたドーターチップ20の傾きをマザーチップ10の傾きに合わせて調整する際に、赤外線カメラによる測定結果(データ6)を反映して、傾きを補正することができる。これにより測定時間の短縮、歩留向上、自働化を行うことができる。

【0066】

実施の形態4.

図面を参照しながら、本発明の実施の形態4に係る半導体装置の製造方法について説明する。

【0067】

まず、図24(a)に示すように、マザーチップ70として、基板71の表面に、トレンチ電極72と、この電極72に接続するように表面電極73とを形成する。

【0068】

次に、図24(b)に示すように、ウェハ状態のマザーチップ70の表面電極73に、ドーターチップ20のメタルポスト26が接続するように、マザーチップ10の回路面にドーターチップ20をフリップチップ接続する。このフリップチップ接続は、実施の形態1〜3の何れか1つと同様に行う。

【0069】

次に、図24(c)に示すように、ウェハ状態のマザーチップ70の表面及びドーターチップ20をモールド樹脂74で封止する。そして、図24(d)に示すように、マザーチップ70の基板71の裏面を砥石43により研磨して、トレンチ電極72を露出させる。

【0070】

次に、図25(a)に示すように、マザーチップ70の裏面にアウターボール35を形成する。そして、図25(b)に示すように、ブレード75により個々のパッケージをダイシングする。ここで、ドーターチップ20はモールド樹脂74で封止されているため、ダイシングにより発生した汚れがマザーチップ70とドーターチップ20の隙間に入り込むことはない。以上の工程により、図25(c)に示すように、半導体装置が製造される。

【図面の簡単な説明】

【0071】

【図1】本発明の実施の形態1に係る半導体装置の製造方法を示すフローチャートである。

【図2】本発明の実施の形態1に係るマザーチップを形成する工程を示す断面図である。

【図3】本発明の実施の形態1に係るマザーチップを形成する工程を示す断面図である。

【図4】本発明の実施の形態1に係るドーターチップを形成する工程を示す断面図である。

【図5】ウェハ裏面研磨工程を示す断面図である。

【図6】ウェハ裏面にダイシングテープを貼り付け、ウェハ主面のバックグラインドテープを剥離する工程を示す断面図である。

【図7】本発明の実施の形態1に係る半導体装置の製造装置を示す斜視図である。

【図8】カバーで覆われたステージを示す断面図である。

【図9】カバーで覆われたステージを示す上面図である。

【図10】カバーで覆われたステージを示す上面図である。

【図11】カバーで覆われたステージを示す上面図である。

【図12】本発明の実施の形態1に係るフリップチップ接続の方法を示すフローチャートである。

【図13】本発明の実施の形態7に係るマザーチップの回路面にドーターチップをフリップチップ接続する工程を示す断面図である。

【図14】図13のメタルポスト同士の接合部を拡大した断面図である。

【図15】チップ・オン・チップ間のアンダーフィル樹脂を形成する工程を示す断面図である。

【図16】レーザーダイシングを行っている状態を示す断面図である。

【図17】マザーチップを回路基板にフリップチップ接続した状態を示す断面図である。

【図18】完成した半導体装置をアウターボールを介して電子装置のマザーボード配線基板上に接続する工程を示す断面図である。

【図19】本発明の実施の形態2に係るフリップチップ接続の方法を示すフローチャートである。

【図20】測定器により開口部を通してマザーチップを高倍カメラで測定する状態を示す断面図である。

【図21】本発明の実施の形態3に係るフリップチップ接続の方法を示すフローチャートである。

【図22】マークを設けたマザーチップ及びドーターチップを示す断面図である。

【図23】マザーチップのマークとドーターチップのマークの重なり具合を示す上面図である。

【図24】本発明の実施の形態4に係る半導体装置の製造方法を説明するための断面図である。

【図25】本発明の実施の形態4に係る半導体装置の製造方法を説明するための断面図である。

【符号の説明】

【0072】

10 マザーチップ(ウェハ)

20 ドーターチップ(チップ)

31 ステージ

32 ボンディングヘッド

53 開口部

54 カバー

56 測定器

61,62 マーク

【特許請求の範囲】

【請求項1】

ウェハを搭載するステージと、

前記ステージを覆い、開口部を有するカバーと、

前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングするボンディングヘッドとを備え、

前記カバーは前記ステージに対して回転して前記開口部を前記ウェハの所望の位置に合わせることを特徴とする半導体装置の製造装置。

【請求項2】

ステージ上にウェハを搭載し、開口部を有するカバーで前記ステージを覆う工程と、

前記カバーの前記開口部を通して前記ウェハの傾きを測定器で測定する工程と、

ボンディングヘッドによりチップを保持し、前記チップの傾きを前記ウェハの傾きに合わせて調整する工程と、

前記ボンディングヘッドにより前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングする工程とを備え、

前記ステージの温度を前記ウェハと前記チップとの接合温度よりも低くすることを特徴とする半導体装置の製造方法。

【請求項3】

ステージ上にウェハを搭載し、開口部を有するカバーで前記ステージを覆う工程と、

前記カバーの前記開口部を通して前記ウェハの傾きを測定器で測定する工程と、

ボンディングヘッドによりチップを保持し、前記チップの傾きを前記ウェハの傾きに合わせて調整する工程と、

前記ボンディングヘッドにより前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングする工程と、

前記ウェハ上に前記チップをボンディングした後に、前記チップと前記ウェハにそれぞれ設けられたマークについて、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、前記チップと前記ウェハの垂直方向のずれを検査する工程とを備え、

前記ボンディングヘッドにより保持された前記チップの傾きを前記ウェハの傾きに合わせて調整する際に、前記赤外線カメラによる検査結果を反映することを特徴とする半導体装置の製造方法。

【請求項1】

ウェハを搭載するステージと、

前記ステージを覆い、開口部を有するカバーと、

前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングするボンディングヘッドとを備え、

前記カバーは前記ステージに対して回転して前記開口部を前記ウェハの所望の位置に合わせることを特徴とする半導体装置の製造装置。

【請求項2】

ステージ上にウェハを搭載し、開口部を有するカバーで前記ステージを覆う工程と、

前記カバーの前記開口部を通して前記ウェハの傾きを測定器で測定する工程と、

ボンディングヘッドによりチップを保持し、前記チップの傾きを前記ウェハの傾きに合わせて調整する工程と、

前記ボンディングヘッドにより前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングする工程とを備え、

前記ステージの温度を前記ウェハと前記チップとの接合温度よりも低くすることを特徴とする半導体装置の製造方法。

【請求項3】

ステージ上にウェハを搭載し、開口部を有するカバーで前記ステージを覆う工程と、

前記カバーの前記開口部を通して前記ウェハの傾きを測定器で測定する工程と、

ボンディングヘッドによりチップを保持し、前記チップの傾きを前記ウェハの傾きに合わせて調整する工程と、

前記ボンディングヘッドにより前記カバーの前記開口部を通して前記ウェハ上にチップをボンディングする工程と、

前記ウェハ上に前記チップをボンディングした後に、前記チップと前記ウェハにそれぞれ設けられたマークについて、赤外線カメラのフォーカス機能によって焦点の合う高さを調べることで、前記チップと前記ウェハの垂直方向のずれを検査する工程とを備え、

前記ボンディングヘッドにより保持された前記チップの傾きを前記ウェハの傾きに合わせて調整する際に、前記赤外線カメラによる検査結果を反映することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【公開番号】特開2008−78385(P2008−78385A)

【公開日】平成20年4月3日(2008.4.3)

【国際特許分類】

【出願番号】特願2006−255790(P2006−255790)

【出願日】平成18年9月21日(2006.9.21)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成20年4月3日(2008.4.3)

【国際特許分類】

【出願日】平成18年9月21日(2006.9.21)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]