半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、硼窒化ジルコニウム膜を用いた半導体装置の製造装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置における多層配線技術では、半導体装置の微細化や多層化が進展することに伴い、エレクトロマイクレーションの耐性を確保するための銅配線技術が不可欠となる。この銅配線技術においては、層間絶縁膜にトレンチを形成して当該トレンチ内に配線材料である銅(Cu)を充填する、いわゆるダマシン法が利用される。アルミ配線技術に用いるバリア膜や洗浄技術をこのCuダマシン法へ転用する場合には、配線材料である銅原子が絶縁膜中へ拡散し易いことから配線寿命の短命化を招く虞があり、また上記トレンチのアスペクト比が非常に高くなることから、トレンチ底部を洗浄し難くなり、ひいては銅配線と下地配線との間でコンタクト抵抗の増大を招く虞がある。そこで、上記の銅配線技術では、従来から、こうした問題を解消すべく、銅配線に適した各種のバリア膜とメタルキャップ膜とが提案されている。

【0003】

特許文献1では、上記バリア膜の構成材料として硼化ジルコニウムや硼窒化ジルコニウムを提案し、前駆体であるZr(BH4)4の分解反応をALD(Atomic Layer Deposition )法を利用した表面反応で具現化する。これにより、アスペクト比の高い微細なトレンチに段差被覆性の高い硼化ジルコニウム膜や硼窒化ジルコニウム膜を成膜できることから、銅配線に対するバリア性を十分に確保でき、しかもバリア膜を450℃以下の低温で成膜することで配線構造への熱投入量(サーマルバジェット(Thermal Budget ))を抑え

ることができる。

【0004】

特許文献2では、上記ジルコニウム化合物を下地膜に積層し、ジルコニウム化合物が有する比抵抗値の下地依存性、いわゆる抵抗選択性を利用してメタルキャップ膜を形成する。いわば、ジルコニウム化合物からなる1つのメタルキャップ膜が、銅配線上においては導電性を有したキャップ膜として機能し、層間絶縁膜上においては絶縁性を有したキャップ膜として機能する。これによれば、耐酸化性に優れた導電性のジルコニウム化合物でトレンチ底部が構成されるため、洗浄工程後のトレンチ底部においてメタルキャップ膜の残膜が在る場合であっても、銅配線と下地配線との間のコンタクト抵抗を良好な水準で維持できる。

【特許文献1】特開2006−57162号公報

【特許文献2】特開2003−17496号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、上記バリア膜やメタルキャップ膜の成膜時には、上記層間絶縁膜の他、先行するトレンチ形成で利用したエッチストップ膜やハードマスク等の各種絶縁膜が基板表面に露出している。上記エッチストップ膜やハードマスクには、層間絶縁膜との間のエッチングの選択比を確保するために、一般的にCVD法を利用した炭化シリコン膜が利用される。バリア膜やメタルキャップ膜として上記ZrBN膜を適用する上では、半導体装置の信頼性を確保するために、この炭化シリコン膜とバリア膜との間、また炭化シリコン膜とメタルキャップ膜との間に高い密着性が要求される。

【0006】

一方、上記CVD法における成膜終了時には、炭素や炭化シリコンからなる微粒子や未結合手が炭化シリコン膜の表面に高い頻度で形成されてしまう。こうした微粒子や未結合

手が膜表面に存在すると、上記Zr(BH4)4を用いる表面反応系では、当該微粒子や未結合手を核とした硼窒化ジルコニウムのグレインが成長してしまい、下地膜と硼窒化ジルコニウム膜との間の密着性が大きく損なわれ、さらには硼窒化ジルコニウム膜自身が発現すべきバリア性や抵抗選択性等の膜特性が著しく劣化してしまう。

【0007】

本願発明は、上記問題に鑑みてなされたものであって、多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に記載する半導体装置の製造装置は、炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する真空槽と、励起した水素を前記真空槽へ供給して加熱下の基板表面を表面処理する表面処理部と、Zr(BH4)4と励起した窒素とを前記真空槽へ供給して加熱下の前記基板表面に硼窒化ジルコニウム膜を成膜処理する成膜処理部と、前記表面処理部を駆動して前記表面処理を実行した後に前記成膜処理部を駆動して前記成膜処理を実行する制御部とを備えたことを要旨とする。

【0009】

請求項1に記載する半導体装置の製造装置によれば、先行して駆動する表面処理部が、シリコン系絶縁膜上にある炭素含有の微粒子や未結合手を、励起した水素による還元反応で成膜処理前に取り除くことができる。したがって、シリコン系絶縁膜と硼窒化ジルコニウム膜との間の密着性と、さらには金属膜と硼窒化ジルコニウム膜との間の密着性とを向上させることができる。そして、硼窒化ジルコニウム膜の膜特性の均一化を図ることができ、ひいては半導体装置の信頼性を向上させることができる。

【0010】

請求項2に記載する半導体装置の製造装置は、請求項1に記載する半導体装置の製造装置であって、前記真空槽に連結された1つの管へ水素ガスと窒素ガスとを選択的に供給するガス供給部と、前記管内へマイクロ波を照射するマイクロ波電源とを備え、前記制御部は、前記表面処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記水素ガスにマイクロ波を照射することにより前記水素ガスを前記励起した水素にして前記真空槽へ供給し、前記成膜処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記窒素ガスにマイクロ波を照射することで前記窒素ガスを前記励起した窒素にして前記真空槽へ供給することを要旨とする。

【0011】

請求項2に記載する半導体装置の製造装置によれば、表面処理と成膜処理との異なる処理において、表面処理と成膜処理とで制御部が共通する管、ガス供給部及びマイクロ波電源を利用することから、より簡便な構成の下で双方の処理を実行できる。したがって、より簡便な構成の下で半導体装置の信頼性を向上させることができる。

【0012】

請求項3に記載する半導体装置の製造方法は、炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とを露出する基板を加熱して基板表面に硼窒化ジルコニウム膜を成膜する工程を備えた半導体装置の製造方法であって、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板が搬入された真空槽に励起した水素を供給して加熱下の前記基板表面を前記励起した水素に曝した後、前記真空槽への前記水素の供給を停止してZr(BH4)4と励起した窒素とを前記真空槽に供給することにより加熱下の前記基板表面に前記硼窒化ジルコニウム膜を成膜することを要旨とする。

【0013】

請求項3に記載する半導体装置の製造方法によれば、シリコン系絶縁膜上にある炭素含有の微粒子や未結合手を、励起した水素による還元反応で予め取り除くことができる。したがって、シリコン系絶縁膜と硼窒化ジルコニウム膜との間の密着性、さらには金属膜と

硼窒化ジルコニウム膜との間の密着性を向上させることができる。この結果、シリコン系絶縁膜を被覆する硼窒化ジルコニウム膜に関してその膜特性の均一化を図ることができ、ひいては半導体装置の信頼性を向上させることができる。

【0014】

請求項4に記載する半導体装置の製造方法は、請求項3に記載する半導体装置の製造方法であって、前記基板に形成された下地金属膜に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記下地金属膜までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程と、前記凹部内を埋め込むように前記シリコン系絶縁膜に前記金属膜を積層して当該金属膜を平坦化することにより前記凹部に埋め込まれた配線を形成し、前記金属膜である前記配線と前記配線を囲う前記シリコン系絶縁膜とを前記基板表面に露出させる工程とを備え、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板表面に前記硼窒化ジルコニウム膜を成膜することで前記シリコン系絶縁膜と前記配線とを覆うメタルキャップ膜を形成することを要旨とする。

【0015】

請求項4に記載する半導体装置の製造方法によれば、シリコン系絶縁膜と配線とを覆うメタルキャップ膜に関してその膜特性の均一化を図ることができる。したがって、シリコン系絶縁膜とメタルキャップ膜との間の密着性と、銅配線とメタルキャップ膜との間の密着性とを向上させることができ、ひいては半導体装置の信頼性を向上させることができる。

【0016】

請求項5に記載する半導体装置の製造方法は、請求項3に記載する半導体装置の製造方法であって、前記基板に形成された前記金属膜である配線に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記配線までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程を備え、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板表面に前記硼窒化ジルコニウム膜を成膜することで、前記シリコン系絶縁膜と、前記凹部の底部である前記配線とを覆うバリア膜を形成することを要旨とする。

【0017】

請求項5に記載する半導体装置の製造方法によれば、シリコン系絶縁膜と配線とを覆うバリア膜に関してその膜特性の均一化を図ることができる。したがって、シリコン系絶縁膜とバリア膜との間の密着性、銅配線とバリア膜との間の密着性を向上させることができ、ひいては半導体装置の信頼性を向上させることができる。

【発明の効果】

【0018】

上記したように、本発明によれば、多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

【0019】

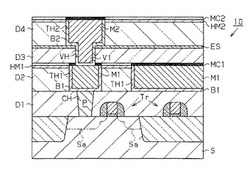

以下、本発明を具体化した一実施形態について図1〜図7を参照して説明する。まず、本発明を利用して製造した半導体装置10について説明する。図1は、半導体装置10を示す部分断面図であり、半導体装置10は、例えば各種RAMや各種ROMを含むメモリ、あるいはMPUや汎用ロジックを含むロジック等である。

【0020】

[半導体装置10]

図1において、半導体装置10が有する基板Sの表面(図1の上面)には、拡散領域Sa上のMOSトランジスタTrを覆うように第1層間絶縁膜D1が積層されている。第1層間絶縁膜D1には、拡散領域Saまで貫通するコンタクトホールCHが形成されて、コンタクトホールCHの内側には、コンタクトプラグPが充填されている。

【0021】

第1層間絶縁膜D1の表面には、第2層間絶縁膜D2と、当該第2層間絶縁膜D2を覆

う第1ハードマスクHM1とが順に積層されている。第2層間絶縁膜D2としては、シリコン酸化膜等からなる多孔性の低誘電率膜を用いることができ、第1ハードマスクHM1としては炭化シリコンや炭化水素シリコン等、炭素含有のシリコン系絶縁膜を用いることができる。これら第2層間絶縁膜D2と第1ハードマスクHM1とには、コンタクトホールCHから上方へ拡開する凹部(第1トレンチTH1)が貫通形成されている。この第1トレンチTH1の内面全体には、硼窒化ジルコニウムからなる第1バリア膜B1が被覆されて、その第1バリア膜B1で被覆された第1トレンチTH1の内部には、配線材料である銅からなる第1配線M1が充填されている。第1配線M1の上面には、第1ハードマスクHM1の上面全体に広がり硼窒化ジルコニウムからなる第1メタルキャップ膜MC1が被覆されている。

【0022】

第1バリア膜B1は、水分に対する高いバリア性を有し、第1メタルキャップ膜MC1と協働して第1配線M1の全体を囲うことにより、第1配線M1の酸化を阻止する。また、第1バリア膜B1は、第1トレンチTH1の内面及び第1配線M1に対して高い密着性を有し、第1配線M1とコンタクトプラグPとの間で十分に低いコンタクト抵抗を実現する。さらに、第1バリア膜B1は、銅原子に対する高いバリア性を有し、第1配線M1からの銅原子の拡散や第1配線M1のマイグレーションを防止する。

【0023】

第1メタルキャップ膜MC1は、下地の比抵抗値に応じた比抵抗値を有する膜であり、いわば抵抗選択性を有する。例えば、第1メタルキャップ膜MC1は、導電体である第1配線M1の表面上の領域(図1において濃いドットで示す領域)で5〜8[μΩ・cm]の低い比抵抗値を有し、絶縁体である第1ハードマスクHM1の表面上の領域(図1において薄いドットで示す領域)で102[Ω・cm]以上の高い比抵抗値を有する。

【0024】

第1メタルキャップ膜MC1の表面には、第3層間絶縁膜D3、エッチストップ膜ES、第4層間絶縁膜D4及び第2ハードマスクHM2が順に積層されている。第3層間絶縁膜D3及び第4層間絶縁膜D4としては、シリコン酸化膜等からなる多孔性の低誘電率膜を用いることができ、エッチストップ膜ES及び第2ハードマスクHM2としては炭化シリコンや炭化水素シリコン等、炭素含有のシリコン系絶縁膜を用いることができる。第1メタルキャップ膜MC1、第3層間絶縁膜D3及びエッチストップ膜ESには、第1配線M1から上方へ延びる共通の凹部(ビアホールVH)が貫通形成されて、第4層間絶縁膜D4と第2ハードマスクHM2とには、そのビアホールVHから上方へ拡開する共通の凹部(第2トレンチTH2)が貫通形成されている。

【0025】

上記ビアホールVH及び上記第2トレンチTH2の内面全体には、硼窒化ジルコニウムからなる第2バリア膜B2が被覆されている。その第2バリア膜B2で被覆されたビアホールVHの内部には、配線材料である銅からなるビア配線V1が充填され、また第2バリア膜B2で被覆された第2トレンチTH2の内部には、配線材料である銅からなる第2配線M2が充填されている。第2配線M2の上面には、第2ハードマスクHM2の上面全体にわたり、硼窒化ジルコニウムからなる共通の第2メタルキャップ膜MC2が被覆されている。

【0026】

第2バリア膜B2は、第1バリア膜B1と同じく、水分に対する高いバリア性を有し、第2メタルキャップ膜MC2と協働してビア配線V1及び第2配線M2の全体を囲うことにより、ビア配線V1及び第2配線M2の酸化を阻止する。また、第2バリア膜B2は、ビアホールVH及び第2トレンチTH2の内面、さらには第1メタルキャップ膜MC1に対して高い密着性を有し、ビア配線V1と第1配線M1との間で十分に低いコンタクト抵抗を実現する。また、第2バリア膜B2は、銅原子に対する高いバリア性を有し、ビア配線V1及び第2配線M2からの銅原子の拡散やマイグレーションを防止する。

【0027】

第2メタルキャップ膜MC2は、第1メタルキャップ膜MC1と同じく、下地の導電性に応じた導電性を有する膜であり、例えば第2配線M2の表面上の領域(図1において濃いドットで示す領域)で5〜8[μΩ・cm]の比抵抗値を有し、第2ハードマスクHM2の表面上の領域(図1において薄いドットで示す領域)で102[Ω・cm]以上の比抵抗値を有する。

【0028】

[成膜装置20]

次に、上記半導体装置10の製造装置としての成膜装置20について図2〜図6を参照して説明する。図2は成膜装置20の全体を示す断面図であり、図3は成膜チャンバ23の構成を示す断面図である。また、図4は成膜チャンバ23の電気的構成を示すブロック図である。

【0029】

図2において、成膜装置20は、ロードロックチャンバ21と、ロードロックチャンバ21に連結されたコアチャンバ22と、コアチャンバ22に連結された4つの成膜チャンバ23とを搭載し、前記ロードロックチャンバ21と各成膜チャンバ23とは、コアチャンバ22を介して互いに解除可能に連通し、共通の真空系を形成可能にする。

【0030】

ロードロックチャンバ21は、複数の基板Sを収容する真空槽であり、基板Sに関する表面処理と成膜処理とを開始するとき、各基板Sを成膜装置20の内部へ搬入する。また、ロードロックチャンバ21は、基板Sの成膜処理を終了するとき、成膜処理後の基板Sを大気に解放し成膜装置20の外部に搬出する。コアチャンバ22は、搬送ロボット22aを搭載する真空槽であり、基板Sの表面処理と成膜処理とを開始するとき、基板Sをロードロックチャンバ21から搬入して成膜チャンバ23へ搬出する。コアチャンバ22は、基板Sの成膜処理を終了するとき、成膜チャンバ23にある基板Sを搬入してロードロックチャンバ21へ搬出する。

【0031】

成膜チャンバ23は、CVD法を用いて上記硼窒化ジルコニウム膜を成膜するチャンバであり、成膜処理を実行するときには、まず基板Sをコアチャンバ22から搬入して基板Sへ表面処理を施した後、上記硼窒化ジルコニウム膜、すなわち上記第1バリア膜B1、第2バリア膜B2、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2を成膜する。

【0032】

図3において、成膜チャンバ23は、その上部を開口したチャンバ本体31と、チャンバ本体31の上部に配設されてチャンバ本体31の上部開口を開閉可能にするチャンバリッド32とを有する。成膜チャンバ23は、これらチャンバ本体31とチャンバリッド32とに囲まれた内部空間(以下単に、処理室31Sという。)を有する。チャンバ本体31には、基板Sを載置する基板ステージ33が配設されている。基板ステージ33は、抵抗加熱ヒータ33Hを内蔵したステージであり、基板Sを載置するときには、基板Sを所定の温度(200℃〜240℃)に昇温させる。基板ステージ33の下側には、基板ステージ33を上下方向に昇降して基板Sの搬入や搬出を可能にする昇降機構34が連結されている。チャンバ本体31の一側には、排気ポートP1を介して排気ポンプ35が接続されている。排気ポンプ35は、ターボ分子ポンプやドライポンプ等の各種のポンプにより構成され、前記表面処理及び成膜処理を実行するときには、処理室31Sの圧力を所定の圧力(1Pa〜1000Pa)の範囲に減圧する。

【0033】

チャンバリッド32の下側には、複数の第1供給孔H1と、各第1供給孔H1から独立する複数の第2供給孔H2とを有したシャワーヘッド36が取付けられている。各第1供給孔H1は、硼窒化ジルコニウム膜の原料であるZr(BH4)4を処理室31Sに供給するものであり、各第2供給孔H2は、励起した窒素あるいは励起した水素を処理室31Sに供給するものである。詳述すると、各第1供給孔H1には、チャンバリッド32の内

部と原料ガスポートP2とを介して原料タンクTKが連結され、原料タンクTKには、キャリアガスであるアルゴンを供給するための流量コントローラMFC1が連結されている。流量コントローラMFC1からのキャリアガスが原料タンクTKに供給されるとき、原料タンクTKは、収容するZr(BH4)4をバブリングさせて、Zr(BH4)4をキャリアガスと共に原料ガスポートP2へ導出し、当該Zr(BH4)4とキャリアガスとを、各第1供給孔H1から処理室31Sに供給する。

【0034】

各第2供給孔H2には、チャンバリッド32の内部と励起ガスポートP3とを介して3つの流量コントローラMFC2、MFC3、MFC4が連結されている。各流量コントローラMFC2、MFC3、MFC4は、それぞれ窒素ガス、アルゴンガス、水素ガスを所定の流量に調整して励起ガスポートP3へ導出する。チャンバリッド32の内部であって、励起ガスポートP3と各第2供給孔H2との間には、石英管あるいはアルミナ管からなる耐熱性を有した照射管37が内設されている。この照射管37の径方向外側には、マイクロ波電源FGによって駆動されるマイクロ波源38と、マイクロ波源38に連結されて照射管37へ延びる導波管39とが配設されている。マイクロ波源38は、例えば2.45GHzのマイクロ波を発生するマイクロ波発振器、すなわちマグネトロンであって、マイクロ波電源FGの駆動電力を受けて所定の出力範囲、例えば0.01kW〜3.0kWの範囲でマイクロ波を出力する。導波管39は、マイクロ波源38が発振するマイクロ波を導波管39の内部に伝播させて照射管37の内部へ照射する。マイクロ波源38がマイクロ波を発振するとき、導波管39は、照射管37を通過するガスにマイクロ波を照射して、当該ガスを励起させる。

【0035】

各第2供給孔H2と照射管37との間には、チャンバリッド32を介して接地されたメッシュ32aが配設されている。マイクロ波源38が照射管37でガスを励起するとき、すなわちマイクロ波源38が照射管37内にプラズマを生成するとき、メッシュ32aは、照射管37から各第2供給孔H2へ流れるプラズマ中のイオン成分を中性化し、当該プラズマ中のラジカル成分と中性化したガス成分とを、各第2供給孔H2から処理室31Sに供給する。これにより、原料ガスポートP2から照射管37へ導入される水素ガス、アルゴンガス及び窒素ガスは、照射管37でプラズマ化された後に、メッシュ32aによってそのイオン成分が中性化され、前記プラズマ中のラジカル成分のみが処理室31Sに供給される。

【0036】

次に、上記成膜装置20の電気的構成について説明する。図4において、制御部41は、成膜装置20に各種の処理動作、例えば基板Sの搬送や前記表面処理、さらには成膜処理等を実行させるものである。制御部41は、各種の演算処理を実行するCPU、各種データや各種プログラムを格納する記憶部41A、各種処理工程の経過時間を計時するタイマ41B等を有する。制御部41は、例えば記憶部41Aが格納する表面処理プログラムを読み出し、タイマ41Bが計時する処理時間と前記表面処理プログラムとに基づいて前記表面処理を実行する。また、制御部41は、記憶部41Aが格納する成膜処理プログラムを読み出し、タイマ41Bが計時する処理時間と成膜処理プログラムとに基づいて前記成膜処理を実行する。

【0037】

制御部41には、起動スイッチや停止スイッチ等の各種操作スイッチや液晶ディスプレイ等の各種表示装置等からなる入出力部42が接続されている。入出力部42は、各処理動作に利用する各種のデータを制御部41に入力し、成膜装置20における前記表面処理の状況や前記成膜処理の状況に関するデータを出力する。例えば、入出力部42は、前記表面処理や前記成膜処理に必要となる各種の条件データId(処理時間、ガス流量、処理圧力、処理温度、マイクロ波電源FGの出力等)を制御部41に入力する。制御部41は、入出力部42から入力される上記各種の条件データIdを受信し、当該条件データIdに応じた各種の制御信号を生成して、その条件データIdに相当する処理条件の下で前記

表面処理や前記成膜処理を実行する。

【0038】

制御部41は、排気系を駆動するための排気系駆動回路43に接続されて、排気系駆動回路43に対応する駆動信号を排気系駆動回路43へ出力する。排気系駆動回路43は、制御部41からの駆動信号に応答して前記排気ポンプ35等の排気系を駆動し、これにより前記処理室31S等の各チャンバ内部を所定の処理圧力に調整する。

【0039】

制御部41は、搬送系を駆動するための搬送系駆動回路44に接続されて、搬送系駆動回路44に対応する駆動信号を搬送系駆動回路44へ出力する。搬送系駆動回路44は、制御部41からの駆動制御信号に応答して搬送ロボット22aや昇降機構34、さらには基板ステージ33に搭載される抵抗加熱ヒータ33H等の搬送系を駆動し、これにより基板Sを所定の搬送経路に沿って搬送して所定の処理温度に温調する。

【0040】

制御部41は、各流量コントローラMFC1〜MFC4を駆動するための流量コントローラ駆動回路45に接続されて、流量コントローラ駆動回路45に対応する駆動信号を流量コントローラ駆動回路45へ出力する。流量コントローラ駆動回路45は、制御部41からの駆動信号に応答して各流量コントローラMFC1〜MFC4をそれぞれ駆動し、これにより所定流量のガスを選択的に処理室31Sへ供給する。

【0041】

制御部41は、マイクロ波電源FGを駆動するためのマイクロ波電源駆動回路46に接続されて、マイクロ波電源駆動回路46に対応する駆動信号をマイクロ波電源駆動回路46へ出力する。マイクロ波電源駆動回路46は、制御部41からの駆動信号に応答してマイクロ波電源FGを駆動し、これにより所定の出力値でマイクロ波を出力する。

【0042】

[半導体装置10の製造方法]

次に、上記成膜装置20を用いた半導体装置10の製造方法について説明する。図5及び図6は半導体装置10の製造工程を示す工程図であり、図7は成膜装置20における各部の動作を示すタイミングチャートである。

【0043】

まず、公知の半導体装置製造技術を用いて、上記MOSトランジスタTr、第1層間絶縁膜D1及びコンタクトプラグPが基板Sに形成され、次いで、公知のダマシン法を用いて、第2層間絶縁膜D2、第1ハードマスクHM1、第1バリア膜B1及び金属膜からなる第1配線M1が形成される。この際、図5に示すように、第1ハードマスクHM1の成膜処理によって、第1ハードマスクHM1の表面には、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手等が残存する。また、第1配線M1(金属膜)へのCMP処理や第1配線M1と大気との接触等によって、第1配線M1の表面には、酸化層MOが形成される。第1配線M1が形成されると、第1配線M1を有する基板Sが成膜装置20へ搬入されて、基板Sの表面である第1ハードマスクHM1と第1配線M1とに表面処理と成膜処理とが施される。

【0044】

表面処理と成膜処理とを開始するにあたり、成膜装置20の制御部41は、まず上記表面処理プログラムと上記成膜処理プログラムとを記憶部41Aから読み出し、入出力部42からの各種の条件データIdに基づいて排気ポンプ35を駆動し、処理室31Sの圧力を条件データIdに基づく処理圧力に調整し続ける。処理室31Sの圧力を前記処理圧力に調整すると、制御部41は、図7に示すように、抵抗加熱ヒータ33Hを駆動して基板ステージ33の温度を条件データIdに基づく処理温度、例えば220℃に温調する。そして、制御部41は、搬送ロボット22aを駆動して基板ステージ33に基板Sを載置し、基板Sを前記処理温度に加熱する。

【0045】

次いで、制御部41は、タイマ41Bを用いた処理時間の計時動作を開始し、流量コン

トローラMFC3、MFC4を駆動して処理条件に基づく流量のアルゴンガス及び水素ガスを照射管37へ導入する。続いて、制御部41は、マイクロ波電源FGを駆動して照射管37の内部にアルゴンと水素とを用いたプラズマを生成し、メッシュ32aによって抽出される水素ラジカルを基板Sの表面に供給する。

【0046】

この際、加熱された基板Sの表面へ励起状態の水素が供給されることから、前記微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理、いわば基板Sの表面処理が実行される。制御部41は、上記の計時結果に基づいてマイクロ波の照射時間が所定の時間だけ経過すると、マイクロ波電源FGの出力を停止させることにより水素ラジカルの供給を停止させる。そして、制御部41は、上記表面処理の処理時間が条件データIdに基づく処理時間になると、流量コントローラMFC3、MFC4のガス供給を停止させて上記の表面処理を完了する。なお、上記の処理時間は、各種試験等に基づいて決定される時間であり、例えば前記のエッチング処理により微粒子DOが消失する時間と、前記末端処理により未結合手が消失する時間と、前記還元処理により酸化層MOが消失する時間との中で最も長い時間に設定される。

【0047】

制御部41は、上記表面処理を完了すると、引き続き基板Sを処理温度に加熱し、流量コントローラMFC2を駆動して処理条件に基づく流量の窒素ガスを照射管37へ導入し、マイクロ波電源FGを駆動して照射管37の内部に窒素プラズマを生成し、メッシュ32aによって抽出される窒素ラジカルを基板Sの表面に供給する。また、制御部41は、マイクロ波電源FGを駆動するタイミングで流量コントローラMFC1を駆動し、処理条件に基づく流量のキャリアガスを原料タンクTKに導入し、キャリアガスとZr(BH4)4とを基板Sの表面に供給する。

【0048】

この際、加熱された基板Sの表面へ励起状態の窒素が供給され、その後にZr(BH4)4が供給されることから、基板Sの表面では吸着したZr(BH4)4の窒化反応や熱分解反応等が表面反応として進行し、基板Sの表面全体に硼窒化ジルコニウム膜が成膜される。この硼窒化ジルコニウム膜は、先行する表面処理によって基板表面が清浄化されているため、表面反応により成長する一方で、前記微粒子DOや未結合手を核としたグレインの成長を回避でき、下地膜である第1ハードマスクHM1や第1配線M1との間で高い密着性を発現することができる。また、この硼窒化ジルコニウム膜は、上記の表面処理によって酸化層MOが除去されているため、下地膜である第1ハードマスクHM1と第1配線M1との上で高い抵抗選択性を発現することができる。それゆえに、この硼窒化ジルコニウム膜は、上記第1メタルキャップ膜MC1としての抵抗選択性、バリア性及び耐酸化性を十分に発現することができる。

【0049】

上記第1メタルキャップ膜MC1の成膜処理を完了すると、上記成膜装置20から基板Sが搬出されて、上記第1メタルキャップ膜MC1に第3層間絶縁膜D3、エッチストップ膜ES、第4層間絶縁膜D4及び第2ハードマスクHM2が順に積層される。続いて、公知のデュアルダマシン法を用いて、第2ハードマスクHM2、第4層間絶縁膜D4、及びエッチストップ膜ESに第2トレンチTH2が形成されて、第3層間絶縁膜D3及び第1メタルキャップ膜MC1にビアホールVHが形成される。

【0050】

この際、図6に示すように、第2ハードマスクHM2の表面には、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手が残存する。また、第2トレンチTH2から露出するエッチストップ膜ESの表面には、同じく、エッチストップ膜ESの成膜処理によって、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手が残存する。また、ビアホールVHから露出する第1配線M1の表面には、酸化層MOが形成される。

【0051】

ビアホールVHと第2トレンチTH2とが形成されると、これらを有する基板Sが再び成膜装置20へ搬入され、基板Sの表面に表面処理と成膜処理とが施される。詳述すると、成膜装置20の制御部41は、上記第1メタルキャップ膜MC1の成膜時と同じく、図7に示すように、まず抵抗加熱ヒータ33Hを駆動して条件データIdに基づく処理温度に基板Sを加熱する。次いで、制御部41は、タイマ41Bを用いた処理時間の計時動作を開始し、流量コントローラMFC3、MFC4とマイクロ波電源FGとを駆動して、基板Sの表面に所定の処理時間だけ水素ラジカルを供給する。そして、加熱された基板Sの表面へ励起状態の水素が供給されることから、前記微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理、いわば基板Sの表面処理が実行される。制御部41は、条件データIdに基づく処理時間だけ水素ラジカルを供給すると、マイクロ波電源FGと流量コントローラMFC3、MFC4とを停止させて、第2ハードマスクHM2、エッチストップ膜ES及び第1配線M1への表面処理を完了する。

【0052】

制御部41は、上記表面処理を完了すると、上記第1メタルキャップ膜MC1の成膜時と同じく、引き続き基板Sを処理温度に加熱し、流量コントローラMFC1、流量コントローラMFC2、及びマイクロ波電源FGを駆動して、加熱された基板Sの表面へ、Zr(BH4)4と励起状態の窒素とを供給する。これにより、第2ハードマスクHM2の表面と、第2トレンチTH2及びビアホールVHの内面とには、吸着したZr(BH4)4の熱分解反応やその窒化反応等が表面反応として進行し、基板Sの表面全体に硼窒化ジルコニウム膜が成膜される。

【0053】

この硼窒化ジルコニウム膜は、上記第1メタルキャップ膜MC1と同じく、先行する表面処理によって基板表面が清浄化されているため、前記微粒子DOや未結合手を核としたグレインの成長を来たすことがなく、下地膜である第2ハードマスクHM2、エッチストップ膜ES及び第1配線M1との間で高い密着性を発現することができる。また、この硼窒化ジルコニウム膜は、上記の表面処理によって酸化層MOが除去されるため、第1配線M1との間で低い接触抵抗を実現することができる。さらに、この硼窒化ジルコニウム膜は、導電性の第1メタルキャップ膜MC1で第1配線M1が覆われていたことから、第1メタルキャップ膜MC1のエッチング残渣が第1配線M1の表面に残存する場合であっても、第1配線M1との間で低い接触抵抗を実現することができる。それゆえに、この硼窒化ジルコニウム膜は、上記第1バリア膜B1としてのバリア性及び導電性を十分に発現することができる。

【0054】

上記第1バリア膜B1の成膜処理を完了すると、上記成膜装置20から基板Sが搬出されて、ビアホールVH内と第2トレンチTH2内とを埋め込むように、上記第1バリア膜B1の全体に金属膜が成膜される。次いで、上記第2ハードマスクHM2をCMPストッパとするCMP処理等によって前記金属膜が平坦化されて、ビアホールVH内と第2トレンチTH2内とを充填する第2配線M2が形成される。そして、第2配線M2が形成されると、第2配線M2を有する基板Sが成膜装置20へ搬入されて、第1メタルキャップ膜MC1と同じく、基板Sの表面である第2ハードマスクHM2と第2配線M2とに表面処理と成膜処理とが順に施されて、硼窒化ジルコニウム膜からなる第2メタルキャップ膜MC2が形成される。

【0055】

[実施例]

上記の基板Sとしてシリコン基板を用い、当該シリコン基板上にCVD法を利用して膜厚が50nmの炭化シリコン膜を成膜した。次いで、当該炭化シリコン膜を有するシリコン基板を上記成膜装置20へ搬入し、炭化シリコン膜の表面に対して以下に示す表面処理と成膜処理とを順に施して膜厚が3nmの硼窒化ジルコニウム膜を成膜した。続いて、当該硼窒化ジルコニウム膜上にPVD法を利用して膜厚が200nmの金属膜を成膜し、実施例の積層膜を得た。そして、カーターナイフを用いて前記積層膜に3mm間隔の格子状

のスクラッチを形成し、このスクラッチ上に粘着テープを一旦貼着して剥がし、硼窒化ジルコニウム膜が炭化シリコン膜から剥がれるか否かを検出した。

【0056】

(表面処理条件)

・基板温度:220℃

・水素ガスの流量(MFC4):100sccm

・アルゴンガスの流量(MFC3):30sccm

・マイクロ波出力:100W

・処理圧力:50Pa

・処理時間:120sec

(成膜処理条件)

・基板温度:220℃

・Zr(BH4)4:55sccm

・キャリアガスの流量(MFC1):100sccm

・窒素ガスの流量(MFC2):50sccm

・マイクロ波出力:100W

・処理圧力:400Pa

また、上記実施例の表面処理を省略し、その他の条件を同じくして得た比較例1を用い、実施例と同じく、密着性テストを実施した。また、上記実施例及び比較例1における炭化シリコン膜を酸化シリコン膜に変更し、その他の条件を同じくして得た比較例2及び比較例3を用い、実施例と同じく、密着性テストを実施した。

【0057】

実施例の密着性テストにおいては、炭化シリコン膜−硼窒化ジルコニウム膜−金属膜の膜間に剥がれが認められず、積層構造にて十分な密着性を発現していることが分った。また、比較例2及び比較例3においても、実施例と同じく、膜間に剥がれが認められず、積層構造にて十分な密着性を発現していることが分った。一方、比較例1の密着性テストにおいては、炭化シリコン膜−硼窒化ジルコニウム膜の膜間で剥がれが認められ、これにより上記表面処理による密着性の向上が認められた。なお、こうした密着性の向上は、上記表面処理が成膜処理の前に施される上において認められ、上記の処理条件に限らず、例えば基板温度が200℃〜240℃の範囲においても認められ、また上記第1トレンチTH1や第2トレンチTH2に適用する場合においても認められた。

【0058】

上記実施形態によれば、以下の効果を奏する。

(1)上記実施形態によれば、第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず表面処理部を構成する流量コントローラMFC3、MFC4及びマイクロ波電源FGが駆動されて、基板Sの表面に水素ラジカルが供給される。そして、表面処理である微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理が実行される。次いで、この表面処理が基板Sに施された後、成膜処理部を構成する流量コントローラMFC3、MFC4及びマイクロ波電源FGが駆動されて、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給される。そして、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

【0059】

したがって、先行する表面処理によって、炭素含有の微粒子DOやシリコンの未結合手、さらには酸化層MOを取り除くことができため、第1配線M1と第1メタルキャップ膜MC1との間の密着性と、第1ハードマスクHM1と第1メタルキャップ膜MC1との間の密着性とを向上させることができる。また、第2配線M2と第2メタルキャップ膜MC2との間の密着性と、第2ハードマスクHM2と第2メタルキャップ膜MC2との間の密着性とを向上させることができる。この結果、第1メタルキャップ膜MC1と第2メタルキャップ膜MC2との膜特性の均一化を図ることができ、ひいては半導体装置10の信頼

性を向上させることができる。

【0060】

(2)上記実施形態によれば、第2バリア膜B2が成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第2バリア膜B2である硼窒化ジルコニウム膜が成膜される。

【0061】

したがって、先行する表面処理によって、炭素含有の微粒子DOやシリコンの未結合手、さらには酸化層MOを取り除くことができため、第2配線M2と第2バリア膜B2との間、エッチストップ膜ESと第2バリア膜B2との間、さらには第2ハードマスクHM2と第2バリア膜B2との間において、密着性を向上させることができる。また、第2配線M2と第2メタルキャップ膜MC2との間の密着性と、第2ハードマスクHM2と第2メタルキャップ膜MC2との間の密着性とを向上させることができる。この結果、第2バリア膜B2の膜特性の均一化を図ることができ、ひいては半導体装置10の信頼性を向上させることができる。

【0062】

(3)上記実施形態によれば、制御部41は、表面処理を実行するときに、ガス供給部を構成する流量コントローラMFC3、MFC4と、マイクロ波電源FGとを駆動し、真空槽である処理室31Sに水素ラジカルを供給する。また、制御部41は、成膜処理を実行するときに、ガス供給部を構成する流量コントローラMFC1、MFC2と、前記マイクロ波電源FGとを駆動し、真空槽である処理室31Sに窒素ラジカルとZr(BH4)4とを供給する。

【0063】

したがって、表面処理と成膜処理との異なる処理において、制御部41が共通するガス供給部と共通するマイクロ波電源FGとを利用することから、より簡便な構成の下で双方の処理を実行できる。したがって、より簡便な構成の下で半導体装置10の信頼性を向上させることができる。

【0064】

尚、上記実施形態は、以下の態様で実施してもよい。

・上記実施形態では、成膜チャンバ23が1つのマイクロ波源38を搭載する例について説明したが、これに限らず、上記表面処理と成膜処理とを順に実施する上では、成膜チャンバ23が、水素ラジカルを生成するマイクロ波源と、窒素ラジカルを生成するマイクロ波源とをそれぞれ搭載する構成であってもよい。これによれば、2種類のラジカルを2つのマイクロ波源で生成できることから、水素ラジカルを生成するタイミングと、窒素ラジカルを生成するタイミングとに自由度を得ることができ、それゆえ、表面処理に関わる処理条件の範囲と成膜処理に関わる処理条件の範囲とを拡張することができる。

【0065】

・上記実施形態では、水素ガスにマイクロ波を照射することで励起した水素である水素ラジカルを生成する構成にしたが、これに限らず、水素ガスに電磁波を供給することで励起した水素である水素ラジカルや水素イオンを生成する構成にしてもよい。

【0066】

・上記実施形態では、窒素ガスにマイクロ波を照射することで励起した窒素である窒素ラジカルを生成する構成にしたが、これに限らず、窒素ガスに電磁波を供給することで励起した窒素である窒素ラジカルや窒素イオンを生成する構成にしてもよい。

【0067】

・上記実施形態では、表面処理において水素ガスとアルゴンガスとを用いる例について説明したが、これに限らず、基板Sの表面に水素ラジカルを照射する上では、アルゴンガスを用いない構成であってもよい。また、硼窒化ジルコニウム膜と下地膜との密着性を向上させる上では、水素ラジカルに加えて、さらに窒素ラジカルを添加する構成であっても

よい。

【0068】

・上記実施形態では、成膜処理において窒素ガスをプラズマ化する例について説明したが、これに限らず、窒素のプラズマ状態を安定させる上では、窒素ガスとアルゴンガスとの混合ガスをプラズマ化する構成であってもよい。

【0069】

・上記実施形態では、第1メタルキャップ膜MC1を貫通するビアホールVHを形成したが、これに限らず、第1メタルキャップ膜MC1の表面がビアホールVHの底面をなす構成であってもよい。

【0070】

・上記実施形態では、硼窒化ジルコニウム膜を、第1メタルキャップ膜MC1、第2メタルキャップ膜MC2及び第2バリア膜B2に具体化したが、これに限らず、上記表面処理と成膜処理とを順に実施する上では、硼窒化ジルコニウム膜を、メタルキャップ膜だけに具体化してもよく、あるいはバリア膜だけに具体化してもよい。

【0071】

・上記実施形態では、半導体装置10が2層の銅配線を有する例について説明したが、これに限らず、上記の硼窒化ジルコニウム膜をメタルキャップ膜又はバリア膜として利用する構成であれば、半導体装置10は、その銅配線の層数に限定されるものではない。

【図面の簡単な説明】

【0072】

【図1】半導体装置を示す部分断面図。

【図2】成膜装置の全体を示す図。

【図3】成膜チャンバを示す部分断面図。

【図4】成膜装置の電気的構成を示すブロック図。

【図5】半導体装置の製造方法を示す工程図。

【図6】半導体装置の製造方法を示す工程図。

【図7】半導体装置の製造方法を示すタイムチャート。

【符号の説明】

【0073】

MC1…硼窒化ジルコニウム膜を構成する第1メタルキャップ膜、MC2…硼窒化ジルコニウム膜を構成する第2メタルキャップ膜、B2…硼窒化ジルコニウム膜を構成する第2バリア膜、ES…シリコン系絶縁膜を構成するエッチストップ膜、M1…下地金属膜としての金属膜である第1配線、M2…金属膜である第2配線、MFC1,MFC2,MFC3,MFC4…成膜処理部及びガス供給部を構成する流量コントローラ、FG…マイクロ波電源、10…半導体装置、31S…真空槽を構成する処理室、37…照射管、38…マイクロ波源。

【技術分野】

【0001】

本発明は、硼窒化ジルコニウム膜を用いた半導体装置の製造装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置における多層配線技術では、半導体装置の微細化や多層化が進展することに伴い、エレクトロマイクレーションの耐性を確保するための銅配線技術が不可欠となる。この銅配線技術においては、層間絶縁膜にトレンチを形成して当該トレンチ内に配線材料である銅(Cu)を充填する、いわゆるダマシン法が利用される。アルミ配線技術に用いるバリア膜や洗浄技術をこのCuダマシン法へ転用する場合には、配線材料である銅原子が絶縁膜中へ拡散し易いことから配線寿命の短命化を招く虞があり、また上記トレンチのアスペクト比が非常に高くなることから、トレンチ底部を洗浄し難くなり、ひいては銅配線と下地配線との間でコンタクト抵抗の増大を招く虞がある。そこで、上記の銅配線技術では、従来から、こうした問題を解消すべく、銅配線に適した各種のバリア膜とメタルキャップ膜とが提案されている。

【0003】

特許文献1では、上記バリア膜の構成材料として硼化ジルコニウムや硼窒化ジルコニウムを提案し、前駆体であるZr(BH4)4の分解反応をALD(Atomic Layer Deposition )法を利用した表面反応で具現化する。これにより、アスペクト比の高い微細なトレンチに段差被覆性の高い硼化ジルコニウム膜や硼窒化ジルコニウム膜を成膜できることから、銅配線に対するバリア性を十分に確保でき、しかもバリア膜を450℃以下の低温で成膜することで配線構造への熱投入量(サーマルバジェット(Thermal Budget ))を抑え

ることができる。

【0004】

特許文献2では、上記ジルコニウム化合物を下地膜に積層し、ジルコニウム化合物が有する比抵抗値の下地依存性、いわゆる抵抗選択性を利用してメタルキャップ膜を形成する。いわば、ジルコニウム化合物からなる1つのメタルキャップ膜が、銅配線上においては導電性を有したキャップ膜として機能し、層間絶縁膜上においては絶縁性を有したキャップ膜として機能する。これによれば、耐酸化性に優れた導電性のジルコニウム化合物でトレンチ底部が構成されるため、洗浄工程後のトレンチ底部においてメタルキャップ膜の残膜が在る場合であっても、銅配線と下地配線との間のコンタクト抵抗を良好な水準で維持できる。

【特許文献1】特開2006−57162号公報

【特許文献2】特開2003−17496号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、上記バリア膜やメタルキャップ膜の成膜時には、上記層間絶縁膜の他、先行するトレンチ形成で利用したエッチストップ膜やハードマスク等の各種絶縁膜が基板表面に露出している。上記エッチストップ膜やハードマスクには、層間絶縁膜との間のエッチングの選択比を確保するために、一般的にCVD法を利用した炭化シリコン膜が利用される。バリア膜やメタルキャップ膜として上記ZrBN膜を適用する上では、半導体装置の信頼性を確保するために、この炭化シリコン膜とバリア膜との間、また炭化シリコン膜とメタルキャップ膜との間に高い密着性が要求される。

【0006】

一方、上記CVD法における成膜終了時には、炭素や炭化シリコンからなる微粒子や未結合手が炭化シリコン膜の表面に高い頻度で形成されてしまう。こうした微粒子や未結合

手が膜表面に存在すると、上記Zr(BH4)4を用いる表面反応系では、当該微粒子や未結合手を核とした硼窒化ジルコニウムのグレインが成長してしまい、下地膜と硼窒化ジルコニウム膜との間の密着性が大きく損なわれ、さらには硼窒化ジルコニウム膜自身が発現すべきバリア性や抵抗選択性等の膜特性が著しく劣化してしまう。

【0007】

本願発明は、上記問題に鑑みてなされたものであって、多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に記載する半導体装置の製造装置は、炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する真空槽と、励起した水素を前記真空槽へ供給して加熱下の基板表面を表面処理する表面処理部と、Zr(BH4)4と励起した窒素とを前記真空槽へ供給して加熱下の前記基板表面に硼窒化ジルコニウム膜を成膜処理する成膜処理部と、前記表面処理部を駆動して前記表面処理を実行した後に前記成膜処理部を駆動して前記成膜処理を実行する制御部とを備えたことを要旨とする。

【0009】

請求項1に記載する半導体装置の製造装置によれば、先行して駆動する表面処理部が、シリコン系絶縁膜上にある炭素含有の微粒子や未結合手を、励起した水素による還元反応で成膜処理前に取り除くことができる。したがって、シリコン系絶縁膜と硼窒化ジルコニウム膜との間の密着性と、さらには金属膜と硼窒化ジルコニウム膜との間の密着性とを向上させることができる。そして、硼窒化ジルコニウム膜の膜特性の均一化を図ることができ、ひいては半導体装置の信頼性を向上させることができる。

【0010】

請求項2に記載する半導体装置の製造装置は、請求項1に記載する半導体装置の製造装置であって、前記真空槽に連結された1つの管へ水素ガスと窒素ガスとを選択的に供給するガス供給部と、前記管内へマイクロ波を照射するマイクロ波電源とを備え、前記制御部は、前記表面処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記水素ガスにマイクロ波を照射することにより前記水素ガスを前記励起した水素にして前記真空槽へ供給し、前記成膜処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記窒素ガスにマイクロ波を照射することで前記窒素ガスを前記励起した窒素にして前記真空槽へ供給することを要旨とする。

【0011】

請求項2に記載する半導体装置の製造装置によれば、表面処理と成膜処理との異なる処理において、表面処理と成膜処理とで制御部が共通する管、ガス供給部及びマイクロ波電源を利用することから、より簡便な構成の下で双方の処理を実行できる。したがって、より簡便な構成の下で半導体装置の信頼性を向上させることができる。

【0012】

請求項3に記載する半導体装置の製造方法は、炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とを露出する基板を加熱して基板表面に硼窒化ジルコニウム膜を成膜する工程を備えた半導体装置の製造方法であって、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板が搬入された真空槽に励起した水素を供給して加熱下の前記基板表面を前記励起した水素に曝した後、前記真空槽への前記水素の供給を停止してZr(BH4)4と励起した窒素とを前記真空槽に供給することにより加熱下の前記基板表面に前記硼窒化ジルコニウム膜を成膜することを要旨とする。

【0013】

請求項3に記載する半導体装置の製造方法によれば、シリコン系絶縁膜上にある炭素含有の微粒子や未結合手を、励起した水素による還元反応で予め取り除くことができる。したがって、シリコン系絶縁膜と硼窒化ジルコニウム膜との間の密着性、さらには金属膜と

硼窒化ジルコニウム膜との間の密着性を向上させることができる。この結果、シリコン系絶縁膜を被覆する硼窒化ジルコニウム膜に関してその膜特性の均一化を図ることができ、ひいては半導体装置の信頼性を向上させることができる。

【0014】

請求項4に記載する半導体装置の製造方法は、請求項3に記載する半導体装置の製造方法であって、前記基板に形成された下地金属膜に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記下地金属膜までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程と、前記凹部内を埋め込むように前記シリコン系絶縁膜に前記金属膜を積層して当該金属膜を平坦化することにより前記凹部に埋め込まれた配線を形成し、前記金属膜である前記配線と前記配線を囲う前記シリコン系絶縁膜とを前記基板表面に露出させる工程とを備え、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板表面に前記硼窒化ジルコニウム膜を成膜することで前記シリコン系絶縁膜と前記配線とを覆うメタルキャップ膜を形成することを要旨とする。

【0015】

請求項4に記載する半導体装置の製造方法によれば、シリコン系絶縁膜と配線とを覆うメタルキャップ膜に関してその膜特性の均一化を図ることができる。したがって、シリコン系絶縁膜とメタルキャップ膜との間の密着性と、銅配線とメタルキャップ膜との間の密着性とを向上させることができ、ひいては半導体装置の信頼性を向上させることができる。

【0016】

請求項5に記載する半導体装置の製造方法は、請求項3に記載する半導体装置の製造方法であって、前記基板に形成された前記金属膜である配線に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記配線までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程を備え、前記硼窒化ジルコニウム膜を成膜する工程は、前記基板表面に前記硼窒化ジルコニウム膜を成膜することで、前記シリコン系絶縁膜と、前記凹部の底部である前記配線とを覆うバリア膜を形成することを要旨とする。

【0017】

請求項5に記載する半導体装置の製造方法によれば、シリコン系絶縁膜と配線とを覆うバリア膜に関してその膜特性の均一化を図ることができる。したがって、シリコン系絶縁膜とバリア膜との間の密着性、銅配線とバリア膜との間の密着性を向上させることができ、ひいては半導体装置の信頼性を向上させることができる。

【発明の効果】

【0018】

上記したように、本発明によれば、多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

【0019】

以下、本発明を具体化した一実施形態について図1〜図7を参照して説明する。まず、本発明を利用して製造した半導体装置10について説明する。図1は、半導体装置10を示す部分断面図であり、半導体装置10は、例えば各種RAMや各種ROMを含むメモリ、あるいはMPUや汎用ロジックを含むロジック等である。

【0020】

[半導体装置10]

図1において、半導体装置10が有する基板Sの表面(図1の上面)には、拡散領域Sa上のMOSトランジスタTrを覆うように第1層間絶縁膜D1が積層されている。第1層間絶縁膜D1には、拡散領域Saまで貫通するコンタクトホールCHが形成されて、コンタクトホールCHの内側には、コンタクトプラグPが充填されている。

【0021】

第1層間絶縁膜D1の表面には、第2層間絶縁膜D2と、当該第2層間絶縁膜D2を覆

う第1ハードマスクHM1とが順に積層されている。第2層間絶縁膜D2としては、シリコン酸化膜等からなる多孔性の低誘電率膜を用いることができ、第1ハードマスクHM1としては炭化シリコンや炭化水素シリコン等、炭素含有のシリコン系絶縁膜を用いることができる。これら第2層間絶縁膜D2と第1ハードマスクHM1とには、コンタクトホールCHから上方へ拡開する凹部(第1トレンチTH1)が貫通形成されている。この第1トレンチTH1の内面全体には、硼窒化ジルコニウムからなる第1バリア膜B1が被覆されて、その第1バリア膜B1で被覆された第1トレンチTH1の内部には、配線材料である銅からなる第1配線M1が充填されている。第1配線M1の上面には、第1ハードマスクHM1の上面全体に広がり硼窒化ジルコニウムからなる第1メタルキャップ膜MC1が被覆されている。

【0022】

第1バリア膜B1は、水分に対する高いバリア性を有し、第1メタルキャップ膜MC1と協働して第1配線M1の全体を囲うことにより、第1配線M1の酸化を阻止する。また、第1バリア膜B1は、第1トレンチTH1の内面及び第1配線M1に対して高い密着性を有し、第1配線M1とコンタクトプラグPとの間で十分に低いコンタクト抵抗を実現する。さらに、第1バリア膜B1は、銅原子に対する高いバリア性を有し、第1配線M1からの銅原子の拡散や第1配線M1のマイグレーションを防止する。

【0023】

第1メタルキャップ膜MC1は、下地の比抵抗値に応じた比抵抗値を有する膜であり、いわば抵抗選択性を有する。例えば、第1メタルキャップ膜MC1は、導電体である第1配線M1の表面上の領域(図1において濃いドットで示す領域)で5〜8[μΩ・cm]の低い比抵抗値を有し、絶縁体である第1ハードマスクHM1の表面上の領域(図1において薄いドットで示す領域)で102[Ω・cm]以上の高い比抵抗値を有する。

【0024】

第1メタルキャップ膜MC1の表面には、第3層間絶縁膜D3、エッチストップ膜ES、第4層間絶縁膜D4及び第2ハードマスクHM2が順に積層されている。第3層間絶縁膜D3及び第4層間絶縁膜D4としては、シリコン酸化膜等からなる多孔性の低誘電率膜を用いることができ、エッチストップ膜ES及び第2ハードマスクHM2としては炭化シリコンや炭化水素シリコン等、炭素含有のシリコン系絶縁膜を用いることができる。第1メタルキャップ膜MC1、第3層間絶縁膜D3及びエッチストップ膜ESには、第1配線M1から上方へ延びる共通の凹部(ビアホールVH)が貫通形成されて、第4層間絶縁膜D4と第2ハードマスクHM2とには、そのビアホールVHから上方へ拡開する共通の凹部(第2トレンチTH2)が貫通形成されている。

【0025】

上記ビアホールVH及び上記第2トレンチTH2の内面全体には、硼窒化ジルコニウムからなる第2バリア膜B2が被覆されている。その第2バリア膜B2で被覆されたビアホールVHの内部には、配線材料である銅からなるビア配線V1が充填され、また第2バリア膜B2で被覆された第2トレンチTH2の内部には、配線材料である銅からなる第2配線M2が充填されている。第2配線M2の上面には、第2ハードマスクHM2の上面全体にわたり、硼窒化ジルコニウムからなる共通の第2メタルキャップ膜MC2が被覆されている。

【0026】

第2バリア膜B2は、第1バリア膜B1と同じく、水分に対する高いバリア性を有し、第2メタルキャップ膜MC2と協働してビア配線V1及び第2配線M2の全体を囲うことにより、ビア配線V1及び第2配線M2の酸化を阻止する。また、第2バリア膜B2は、ビアホールVH及び第2トレンチTH2の内面、さらには第1メタルキャップ膜MC1に対して高い密着性を有し、ビア配線V1と第1配線M1との間で十分に低いコンタクト抵抗を実現する。また、第2バリア膜B2は、銅原子に対する高いバリア性を有し、ビア配線V1及び第2配線M2からの銅原子の拡散やマイグレーションを防止する。

【0027】

第2メタルキャップ膜MC2は、第1メタルキャップ膜MC1と同じく、下地の導電性に応じた導電性を有する膜であり、例えば第2配線M2の表面上の領域(図1において濃いドットで示す領域)で5〜8[μΩ・cm]の比抵抗値を有し、第2ハードマスクHM2の表面上の領域(図1において薄いドットで示す領域)で102[Ω・cm]以上の比抵抗値を有する。

【0028】

[成膜装置20]

次に、上記半導体装置10の製造装置としての成膜装置20について図2〜図6を参照して説明する。図2は成膜装置20の全体を示す断面図であり、図3は成膜チャンバ23の構成を示す断面図である。また、図4は成膜チャンバ23の電気的構成を示すブロック図である。

【0029】

図2において、成膜装置20は、ロードロックチャンバ21と、ロードロックチャンバ21に連結されたコアチャンバ22と、コアチャンバ22に連結された4つの成膜チャンバ23とを搭載し、前記ロードロックチャンバ21と各成膜チャンバ23とは、コアチャンバ22を介して互いに解除可能に連通し、共通の真空系を形成可能にする。

【0030】

ロードロックチャンバ21は、複数の基板Sを収容する真空槽であり、基板Sに関する表面処理と成膜処理とを開始するとき、各基板Sを成膜装置20の内部へ搬入する。また、ロードロックチャンバ21は、基板Sの成膜処理を終了するとき、成膜処理後の基板Sを大気に解放し成膜装置20の外部に搬出する。コアチャンバ22は、搬送ロボット22aを搭載する真空槽であり、基板Sの表面処理と成膜処理とを開始するとき、基板Sをロードロックチャンバ21から搬入して成膜チャンバ23へ搬出する。コアチャンバ22は、基板Sの成膜処理を終了するとき、成膜チャンバ23にある基板Sを搬入してロードロックチャンバ21へ搬出する。

【0031】

成膜チャンバ23は、CVD法を用いて上記硼窒化ジルコニウム膜を成膜するチャンバであり、成膜処理を実行するときには、まず基板Sをコアチャンバ22から搬入して基板Sへ表面処理を施した後、上記硼窒化ジルコニウム膜、すなわち上記第1バリア膜B1、第2バリア膜B2、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2を成膜する。

【0032】

図3において、成膜チャンバ23は、その上部を開口したチャンバ本体31と、チャンバ本体31の上部に配設されてチャンバ本体31の上部開口を開閉可能にするチャンバリッド32とを有する。成膜チャンバ23は、これらチャンバ本体31とチャンバリッド32とに囲まれた内部空間(以下単に、処理室31Sという。)を有する。チャンバ本体31には、基板Sを載置する基板ステージ33が配設されている。基板ステージ33は、抵抗加熱ヒータ33Hを内蔵したステージであり、基板Sを載置するときには、基板Sを所定の温度(200℃〜240℃)に昇温させる。基板ステージ33の下側には、基板ステージ33を上下方向に昇降して基板Sの搬入や搬出を可能にする昇降機構34が連結されている。チャンバ本体31の一側には、排気ポートP1を介して排気ポンプ35が接続されている。排気ポンプ35は、ターボ分子ポンプやドライポンプ等の各種のポンプにより構成され、前記表面処理及び成膜処理を実行するときには、処理室31Sの圧力を所定の圧力(1Pa〜1000Pa)の範囲に減圧する。

【0033】

チャンバリッド32の下側には、複数の第1供給孔H1と、各第1供給孔H1から独立する複数の第2供給孔H2とを有したシャワーヘッド36が取付けられている。各第1供給孔H1は、硼窒化ジルコニウム膜の原料であるZr(BH4)4を処理室31Sに供給するものであり、各第2供給孔H2は、励起した窒素あるいは励起した水素を処理室31Sに供給するものである。詳述すると、各第1供給孔H1には、チャンバリッド32の内

部と原料ガスポートP2とを介して原料タンクTKが連結され、原料タンクTKには、キャリアガスであるアルゴンを供給するための流量コントローラMFC1が連結されている。流量コントローラMFC1からのキャリアガスが原料タンクTKに供給されるとき、原料タンクTKは、収容するZr(BH4)4をバブリングさせて、Zr(BH4)4をキャリアガスと共に原料ガスポートP2へ導出し、当該Zr(BH4)4とキャリアガスとを、各第1供給孔H1から処理室31Sに供給する。

【0034】

各第2供給孔H2には、チャンバリッド32の内部と励起ガスポートP3とを介して3つの流量コントローラMFC2、MFC3、MFC4が連結されている。各流量コントローラMFC2、MFC3、MFC4は、それぞれ窒素ガス、アルゴンガス、水素ガスを所定の流量に調整して励起ガスポートP3へ導出する。チャンバリッド32の内部であって、励起ガスポートP3と各第2供給孔H2との間には、石英管あるいはアルミナ管からなる耐熱性を有した照射管37が内設されている。この照射管37の径方向外側には、マイクロ波電源FGによって駆動されるマイクロ波源38と、マイクロ波源38に連結されて照射管37へ延びる導波管39とが配設されている。マイクロ波源38は、例えば2.45GHzのマイクロ波を発生するマイクロ波発振器、すなわちマグネトロンであって、マイクロ波電源FGの駆動電力を受けて所定の出力範囲、例えば0.01kW〜3.0kWの範囲でマイクロ波を出力する。導波管39は、マイクロ波源38が発振するマイクロ波を導波管39の内部に伝播させて照射管37の内部へ照射する。マイクロ波源38がマイクロ波を発振するとき、導波管39は、照射管37を通過するガスにマイクロ波を照射して、当該ガスを励起させる。

【0035】

各第2供給孔H2と照射管37との間には、チャンバリッド32を介して接地されたメッシュ32aが配設されている。マイクロ波源38が照射管37でガスを励起するとき、すなわちマイクロ波源38が照射管37内にプラズマを生成するとき、メッシュ32aは、照射管37から各第2供給孔H2へ流れるプラズマ中のイオン成分を中性化し、当該プラズマ中のラジカル成分と中性化したガス成分とを、各第2供給孔H2から処理室31Sに供給する。これにより、原料ガスポートP2から照射管37へ導入される水素ガス、アルゴンガス及び窒素ガスは、照射管37でプラズマ化された後に、メッシュ32aによってそのイオン成分が中性化され、前記プラズマ中のラジカル成分のみが処理室31Sに供給される。

【0036】

次に、上記成膜装置20の電気的構成について説明する。図4において、制御部41は、成膜装置20に各種の処理動作、例えば基板Sの搬送や前記表面処理、さらには成膜処理等を実行させるものである。制御部41は、各種の演算処理を実行するCPU、各種データや各種プログラムを格納する記憶部41A、各種処理工程の経過時間を計時するタイマ41B等を有する。制御部41は、例えば記憶部41Aが格納する表面処理プログラムを読み出し、タイマ41Bが計時する処理時間と前記表面処理プログラムとに基づいて前記表面処理を実行する。また、制御部41は、記憶部41Aが格納する成膜処理プログラムを読み出し、タイマ41Bが計時する処理時間と成膜処理プログラムとに基づいて前記成膜処理を実行する。

【0037】

制御部41には、起動スイッチや停止スイッチ等の各種操作スイッチや液晶ディスプレイ等の各種表示装置等からなる入出力部42が接続されている。入出力部42は、各処理動作に利用する各種のデータを制御部41に入力し、成膜装置20における前記表面処理の状況や前記成膜処理の状況に関するデータを出力する。例えば、入出力部42は、前記表面処理や前記成膜処理に必要となる各種の条件データId(処理時間、ガス流量、処理圧力、処理温度、マイクロ波電源FGの出力等)を制御部41に入力する。制御部41は、入出力部42から入力される上記各種の条件データIdを受信し、当該条件データIdに応じた各種の制御信号を生成して、その条件データIdに相当する処理条件の下で前記

表面処理や前記成膜処理を実行する。

【0038】

制御部41は、排気系を駆動するための排気系駆動回路43に接続されて、排気系駆動回路43に対応する駆動信号を排気系駆動回路43へ出力する。排気系駆動回路43は、制御部41からの駆動信号に応答して前記排気ポンプ35等の排気系を駆動し、これにより前記処理室31S等の各チャンバ内部を所定の処理圧力に調整する。

【0039】

制御部41は、搬送系を駆動するための搬送系駆動回路44に接続されて、搬送系駆動回路44に対応する駆動信号を搬送系駆動回路44へ出力する。搬送系駆動回路44は、制御部41からの駆動制御信号に応答して搬送ロボット22aや昇降機構34、さらには基板ステージ33に搭載される抵抗加熱ヒータ33H等の搬送系を駆動し、これにより基板Sを所定の搬送経路に沿って搬送して所定の処理温度に温調する。

【0040】

制御部41は、各流量コントローラMFC1〜MFC4を駆動するための流量コントローラ駆動回路45に接続されて、流量コントローラ駆動回路45に対応する駆動信号を流量コントローラ駆動回路45へ出力する。流量コントローラ駆動回路45は、制御部41からの駆動信号に応答して各流量コントローラMFC1〜MFC4をそれぞれ駆動し、これにより所定流量のガスを選択的に処理室31Sへ供給する。

【0041】

制御部41は、マイクロ波電源FGを駆動するためのマイクロ波電源駆動回路46に接続されて、マイクロ波電源駆動回路46に対応する駆動信号をマイクロ波電源駆動回路46へ出力する。マイクロ波電源駆動回路46は、制御部41からの駆動信号に応答してマイクロ波電源FGを駆動し、これにより所定の出力値でマイクロ波を出力する。

【0042】

[半導体装置10の製造方法]

次に、上記成膜装置20を用いた半導体装置10の製造方法について説明する。図5及び図6は半導体装置10の製造工程を示す工程図であり、図7は成膜装置20における各部の動作を示すタイミングチャートである。

【0043】

まず、公知の半導体装置製造技術を用いて、上記MOSトランジスタTr、第1層間絶縁膜D1及びコンタクトプラグPが基板Sに形成され、次いで、公知のダマシン法を用いて、第2層間絶縁膜D2、第1ハードマスクHM1、第1バリア膜B1及び金属膜からなる第1配線M1が形成される。この際、図5に示すように、第1ハードマスクHM1の成膜処理によって、第1ハードマスクHM1の表面には、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手等が残存する。また、第1配線M1(金属膜)へのCMP処理や第1配線M1と大気との接触等によって、第1配線M1の表面には、酸化層MOが形成される。第1配線M1が形成されると、第1配線M1を有する基板Sが成膜装置20へ搬入されて、基板Sの表面である第1ハードマスクHM1と第1配線M1とに表面処理と成膜処理とが施される。

【0044】

表面処理と成膜処理とを開始するにあたり、成膜装置20の制御部41は、まず上記表面処理プログラムと上記成膜処理プログラムとを記憶部41Aから読み出し、入出力部42からの各種の条件データIdに基づいて排気ポンプ35を駆動し、処理室31Sの圧力を条件データIdに基づく処理圧力に調整し続ける。処理室31Sの圧力を前記処理圧力に調整すると、制御部41は、図7に示すように、抵抗加熱ヒータ33Hを駆動して基板ステージ33の温度を条件データIdに基づく処理温度、例えば220℃に温調する。そして、制御部41は、搬送ロボット22aを駆動して基板ステージ33に基板Sを載置し、基板Sを前記処理温度に加熱する。

【0045】

次いで、制御部41は、タイマ41Bを用いた処理時間の計時動作を開始し、流量コン

トローラMFC3、MFC4を駆動して処理条件に基づく流量のアルゴンガス及び水素ガスを照射管37へ導入する。続いて、制御部41は、マイクロ波電源FGを駆動して照射管37の内部にアルゴンと水素とを用いたプラズマを生成し、メッシュ32aによって抽出される水素ラジカルを基板Sの表面に供給する。

【0046】

この際、加熱された基板Sの表面へ励起状態の水素が供給されることから、前記微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理、いわば基板Sの表面処理が実行される。制御部41は、上記の計時結果に基づいてマイクロ波の照射時間が所定の時間だけ経過すると、マイクロ波電源FGの出力を停止させることにより水素ラジカルの供給を停止させる。そして、制御部41は、上記表面処理の処理時間が条件データIdに基づく処理時間になると、流量コントローラMFC3、MFC4のガス供給を停止させて上記の表面処理を完了する。なお、上記の処理時間は、各種試験等に基づいて決定される時間であり、例えば前記のエッチング処理により微粒子DOが消失する時間と、前記末端処理により未結合手が消失する時間と、前記還元処理により酸化層MOが消失する時間との中で最も長い時間に設定される。

【0047】

制御部41は、上記表面処理を完了すると、引き続き基板Sを処理温度に加熱し、流量コントローラMFC2を駆動して処理条件に基づく流量の窒素ガスを照射管37へ導入し、マイクロ波電源FGを駆動して照射管37の内部に窒素プラズマを生成し、メッシュ32aによって抽出される窒素ラジカルを基板Sの表面に供給する。また、制御部41は、マイクロ波電源FGを駆動するタイミングで流量コントローラMFC1を駆動し、処理条件に基づく流量のキャリアガスを原料タンクTKに導入し、キャリアガスとZr(BH4)4とを基板Sの表面に供給する。

【0048】

この際、加熱された基板Sの表面へ励起状態の窒素が供給され、その後にZr(BH4)4が供給されることから、基板Sの表面では吸着したZr(BH4)4の窒化反応や熱分解反応等が表面反応として進行し、基板Sの表面全体に硼窒化ジルコニウム膜が成膜される。この硼窒化ジルコニウム膜は、先行する表面処理によって基板表面が清浄化されているため、表面反応により成長する一方で、前記微粒子DOや未結合手を核としたグレインの成長を回避でき、下地膜である第1ハードマスクHM1や第1配線M1との間で高い密着性を発現することができる。また、この硼窒化ジルコニウム膜は、上記の表面処理によって酸化層MOが除去されているため、下地膜である第1ハードマスクHM1と第1配線M1との上で高い抵抗選択性を発現することができる。それゆえに、この硼窒化ジルコニウム膜は、上記第1メタルキャップ膜MC1としての抵抗選択性、バリア性及び耐酸化性を十分に発現することができる。

【0049】

上記第1メタルキャップ膜MC1の成膜処理を完了すると、上記成膜装置20から基板Sが搬出されて、上記第1メタルキャップ膜MC1に第3層間絶縁膜D3、エッチストップ膜ES、第4層間絶縁膜D4及び第2ハードマスクHM2が順に積層される。続いて、公知のデュアルダマシン法を用いて、第2ハードマスクHM2、第4層間絶縁膜D4、及びエッチストップ膜ESに第2トレンチTH2が形成されて、第3層間絶縁膜D3及び第1メタルキャップ膜MC1にビアホールVHが形成される。

【0050】

この際、図6に示すように、第2ハードマスクHM2の表面には、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手が残存する。また、第2トレンチTH2から露出するエッチストップ膜ESの表面には、同じく、エッチストップ膜ESの成膜処理によって、炭素や炭化シリコンからなる微粒子DO、さらにはシリコンの未結合手が残存する。また、ビアホールVHから露出する第1配線M1の表面には、酸化層MOが形成される。

【0051】

ビアホールVHと第2トレンチTH2とが形成されると、これらを有する基板Sが再び成膜装置20へ搬入され、基板Sの表面に表面処理と成膜処理とが施される。詳述すると、成膜装置20の制御部41は、上記第1メタルキャップ膜MC1の成膜時と同じく、図7に示すように、まず抵抗加熱ヒータ33Hを駆動して条件データIdに基づく処理温度に基板Sを加熱する。次いで、制御部41は、タイマ41Bを用いた処理時間の計時動作を開始し、流量コントローラMFC3、MFC4とマイクロ波電源FGとを駆動して、基板Sの表面に所定の処理時間だけ水素ラジカルを供給する。そして、加熱された基板Sの表面へ励起状態の水素が供給されることから、前記微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理、いわば基板Sの表面処理が実行される。制御部41は、条件データIdに基づく処理時間だけ水素ラジカルを供給すると、マイクロ波電源FGと流量コントローラMFC3、MFC4とを停止させて、第2ハードマスクHM2、エッチストップ膜ES及び第1配線M1への表面処理を完了する。

【0052】

制御部41は、上記表面処理を完了すると、上記第1メタルキャップ膜MC1の成膜時と同じく、引き続き基板Sを処理温度に加熱し、流量コントローラMFC1、流量コントローラMFC2、及びマイクロ波電源FGを駆動して、加熱された基板Sの表面へ、Zr(BH4)4と励起状態の窒素とを供給する。これにより、第2ハードマスクHM2の表面と、第2トレンチTH2及びビアホールVHの内面とには、吸着したZr(BH4)4の熱分解反応やその窒化反応等が表面反応として進行し、基板Sの表面全体に硼窒化ジルコニウム膜が成膜される。

【0053】

この硼窒化ジルコニウム膜は、上記第1メタルキャップ膜MC1と同じく、先行する表面処理によって基板表面が清浄化されているため、前記微粒子DOや未結合手を核としたグレインの成長を来たすことがなく、下地膜である第2ハードマスクHM2、エッチストップ膜ES及び第1配線M1との間で高い密着性を発現することができる。また、この硼窒化ジルコニウム膜は、上記の表面処理によって酸化層MOが除去されるため、第1配線M1との間で低い接触抵抗を実現することができる。さらに、この硼窒化ジルコニウム膜は、導電性の第1メタルキャップ膜MC1で第1配線M1が覆われていたことから、第1メタルキャップ膜MC1のエッチング残渣が第1配線M1の表面に残存する場合であっても、第1配線M1との間で低い接触抵抗を実現することができる。それゆえに、この硼窒化ジルコニウム膜は、上記第1バリア膜B1としてのバリア性及び導電性を十分に発現することができる。

【0054】

上記第1バリア膜B1の成膜処理を完了すると、上記成膜装置20から基板Sが搬出されて、ビアホールVH内と第2トレンチTH2内とを埋め込むように、上記第1バリア膜B1の全体に金属膜が成膜される。次いで、上記第2ハードマスクHM2をCMPストッパとするCMP処理等によって前記金属膜が平坦化されて、ビアホールVH内と第2トレンチTH2内とを充填する第2配線M2が形成される。そして、第2配線M2が形成されると、第2配線M2を有する基板Sが成膜装置20へ搬入されて、第1メタルキャップ膜MC1と同じく、基板Sの表面である第2ハードマスクHM2と第2配線M2とに表面処理と成膜処理とが順に施されて、硼窒化ジルコニウム膜からなる第2メタルキャップ膜MC2が形成される。

【0055】

[実施例]

上記の基板Sとしてシリコン基板を用い、当該シリコン基板上にCVD法を利用して膜厚が50nmの炭化シリコン膜を成膜した。次いで、当該炭化シリコン膜を有するシリコン基板を上記成膜装置20へ搬入し、炭化シリコン膜の表面に対して以下に示す表面処理と成膜処理とを順に施して膜厚が3nmの硼窒化ジルコニウム膜を成膜した。続いて、当該硼窒化ジルコニウム膜上にPVD法を利用して膜厚が200nmの金属膜を成膜し、実施例の積層膜を得た。そして、カーターナイフを用いて前記積層膜に3mm間隔の格子状

のスクラッチを形成し、このスクラッチ上に粘着テープを一旦貼着して剥がし、硼窒化ジルコニウム膜が炭化シリコン膜から剥がれるか否かを検出した。

【0056】

(表面処理条件)

・基板温度:220℃

・水素ガスの流量(MFC4):100sccm

・アルゴンガスの流量(MFC3):30sccm

・マイクロ波出力:100W

・処理圧力:50Pa

・処理時間:120sec

(成膜処理条件)

・基板温度:220℃

・Zr(BH4)4:55sccm

・キャリアガスの流量(MFC1):100sccm

・窒素ガスの流量(MFC2):50sccm

・マイクロ波出力:100W

・処理圧力:400Pa

また、上記実施例の表面処理を省略し、その他の条件を同じくして得た比較例1を用い、実施例と同じく、密着性テストを実施した。また、上記実施例及び比較例1における炭化シリコン膜を酸化シリコン膜に変更し、その他の条件を同じくして得た比較例2及び比較例3を用い、実施例と同じく、密着性テストを実施した。

【0057】

実施例の密着性テストにおいては、炭化シリコン膜−硼窒化ジルコニウム膜−金属膜の膜間に剥がれが認められず、積層構造にて十分な密着性を発現していることが分った。また、比較例2及び比較例3においても、実施例と同じく、膜間に剥がれが認められず、積層構造にて十分な密着性を発現していることが分った。一方、比較例1の密着性テストにおいては、炭化シリコン膜−硼窒化ジルコニウム膜の膜間で剥がれが認められ、これにより上記表面処理による密着性の向上が認められた。なお、こうした密着性の向上は、上記表面処理が成膜処理の前に施される上において認められ、上記の処理条件に限らず、例えば基板温度が200℃〜240℃の範囲においても認められ、また上記第1トレンチTH1や第2トレンチTH2に適用する場合においても認められた。

【0058】

上記実施形態によれば、以下の効果を奏する。

(1)上記実施形態によれば、第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず表面処理部を構成する流量コントローラMFC3、MFC4及びマイクロ波電源FGが駆動されて、基板Sの表面に水素ラジカルが供給される。そして、表面処理である微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理が実行される。次いで、この表面処理が基板Sに施された後、成膜処理部を構成する流量コントローラMFC3、MFC4及びマイクロ波電源FGが駆動されて、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給される。そして、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

【0059】

したがって、先行する表面処理によって、炭素含有の微粒子DOやシリコンの未結合手、さらには酸化層MOを取り除くことができため、第1配線M1と第1メタルキャップ膜MC1との間の密着性と、第1ハードマスクHM1と第1メタルキャップ膜MC1との間の密着性とを向上させることができる。また、第2配線M2と第2メタルキャップ膜MC2との間の密着性と、第2ハードマスクHM2と第2メタルキャップ膜MC2との間の密着性とを向上させることができる。この結果、第1メタルキャップ膜MC1と第2メタルキャップ膜MC2との膜特性の均一化を図ることができ、ひいては半導体装置10の信頼

性を向上させることができる。

【0060】

(2)上記実施形態によれば、第2バリア膜B2が成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子DOのエッチング処理や未結合手への末端処理、さらには酸化層MOの還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第2バリア膜B2である硼窒化ジルコニウム膜が成膜される。

【0061】

したがって、先行する表面処理によって、炭素含有の微粒子DOやシリコンの未結合手、さらには酸化層MOを取り除くことができため、第2配線M2と第2バリア膜B2との間、エッチストップ膜ESと第2バリア膜B2との間、さらには第2ハードマスクHM2と第2バリア膜B2との間において、密着性を向上させることができる。また、第2配線M2と第2メタルキャップ膜MC2との間の密着性と、第2ハードマスクHM2と第2メタルキャップ膜MC2との間の密着性とを向上させることができる。この結果、第2バリア膜B2の膜特性の均一化を図ることができ、ひいては半導体装置10の信頼性を向上させることができる。

【0062】

(3)上記実施形態によれば、制御部41は、表面処理を実行するときに、ガス供給部を構成する流量コントローラMFC3、MFC4と、マイクロ波電源FGとを駆動し、真空槽である処理室31Sに水素ラジカルを供給する。また、制御部41は、成膜処理を実行するときに、ガス供給部を構成する流量コントローラMFC1、MFC2と、前記マイクロ波電源FGとを駆動し、真空槽である処理室31Sに窒素ラジカルとZr(BH4)4とを供給する。

【0063】

したがって、表面処理と成膜処理との異なる処理において、制御部41が共通するガス供給部と共通するマイクロ波電源FGとを利用することから、より簡便な構成の下で双方の処理を実行できる。したがって、より簡便な構成の下で半導体装置10の信頼性を向上させることができる。

【0064】

尚、上記実施形態は、以下の態様で実施してもよい。

・上記実施形態では、成膜チャンバ23が1つのマイクロ波源38を搭載する例について説明したが、これに限らず、上記表面処理と成膜処理とを順に実施する上では、成膜チャンバ23が、水素ラジカルを生成するマイクロ波源と、窒素ラジカルを生成するマイクロ波源とをそれぞれ搭載する構成であってもよい。これによれば、2種類のラジカルを2つのマイクロ波源で生成できることから、水素ラジカルを生成するタイミングと、窒素ラジカルを生成するタイミングとに自由度を得ることができ、それゆえ、表面処理に関わる処理条件の範囲と成膜処理に関わる処理条件の範囲とを拡張することができる。

【0065】

・上記実施形態では、水素ガスにマイクロ波を照射することで励起した水素である水素ラジカルを生成する構成にしたが、これに限らず、水素ガスに電磁波を供給することで励起した水素である水素ラジカルや水素イオンを生成する構成にしてもよい。

【0066】

・上記実施形態では、窒素ガスにマイクロ波を照射することで励起した窒素である窒素ラジカルを生成する構成にしたが、これに限らず、窒素ガスに電磁波を供給することで励起した窒素である窒素ラジカルや窒素イオンを生成する構成にしてもよい。

【0067】

・上記実施形態では、表面処理において水素ガスとアルゴンガスとを用いる例について説明したが、これに限らず、基板Sの表面に水素ラジカルを照射する上では、アルゴンガスを用いない構成であってもよい。また、硼窒化ジルコニウム膜と下地膜との密着性を向上させる上では、水素ラジカルに加えて、さらに窒素ラジカルを添加する構成であっても

よい。

【0068】

・上記実施形態では、成膜処理において窒素ガスをプラズマ化する例について説明したが、これに限らず、窒素のプラズマ状態を安定させる上では、窒素ガスとアルゴンガスとの混合ガスをプラズマ化する構成であってもよい。

【0069】

・上記実施形態では、第1メタルキャップ膜MC1を貫通するビアホールVHを形成したが、これに限らず、第1メタルキャップ膜MC1の表面がビアホールVHの底面をなす構成であってもよい。

【0070】

・上記実施形態では、硼窒化ジルコニウム膜を、第1メタルキャップ膜MC1、第2メタルキャップ膜MC2及び第2バリア膜B2に具体化したが、これに限らず、上記表面処理と成膜処理とを順に実施する上では、硼窒化ジルコニウム膜を、メタルキャップ膜だけに具体化してもよく、あるいはバリア膜だけに具体化してもよい。

【0071】

・上記実施形態では、半導体装置10が2層の銅配線を有する例について説明したが、これに限らず、上記の硼窒化ジルコニウム膜をメタルキャップ膜又はバリア膜として利用する構成であれば、半導体装置10は、その銅配線の層数に限定されるものではない。

【図面の簡単な説明】

【0072】

【図1】半導体装置を示す部分断面図。

【図2】成膜装置の全体を示す図。

【図3】成膜チャンバを示す部分断面図。

【図4】成膜装置の電気的構成を示すブロック図。

【図5】半導体装置の製造方法を示す工程図。

【図6】半導体装置の製造方法を示す工程図。

【図7】半導体装置の製造方法を示すタイムチャート。

【符号の説明】

【0073】

MC1…硼窒化ジルコニウム膜を構成する第1メタルキャップ膜、MC2…硼窒化ジルコニウム膜を構成する第2メタルキャップ膜、B2…硼窒化ジルコニウム膜を構成する第2バリア膜、ES…シリコン系絶縁膜を構成するエッチストップ膜、M1…下地金属膜としての金属膜である第1配線、M2…金属膜である第2配線、MFC1,MFC2,MFC3,MFC4…成膜処理部及びガス供給部を構成する流量コントローラ、FG…マイクロ波電源、10…半導体装置、31S…真空槽を構成する処理室、37…照射管、38…マイクロ波源。

【特許請求の範囲】

【請求項1】

炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する真空槽と、

励起した水素を前記真空槽へ供給して加熱下の基板表面を表面処理する表面処理部と、

Zr(BH4)4と励起した窒素とを前記真空槽へ供給して加熱下の前記基板表面に硼窒化ジルコニウム膜を成膜処理する成膜処理部と、

前記表面処理部を駆動して前記表面処理を実行した後に前記成膜処理部を駆動して前記成膜処理を実行する制御部と

を備えた半導体装置の製造装置。

【請求項2】

請求項1に記載する半導体装置の製造装置であって、

前記真空槽に連結された1つの管へ水素ガスと窒素ガスとを選択的に供給するガス供給部と、

前記管内へマイクロ波を照射するマイクロ波電源とを備え、

前記制御部は、

前記表面処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記水素ガスにマイクロ波を照射することにより前記水素ガスを前記励起した水素にして前記真空槽へ供給し、前記成膜処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記窒素ガスにマイクロ波を照射することで前記窒素ガスを前記励起した窒素にして前記真空槽へ供給することを特徴とする半導体装置の製造装置。

【請求項3】

炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱して基板表面に硼窒化ジルコニウム膜を成膜する工程を備えた半導体装置の製造方法であって、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板が搬入された真空槽に励起した水素を供給して加熱下の前記基板表面を前記励起した水素に曝した後、前記真空槽への前記水素の供給を停止してZr(BH4)4と励起した窒素とを前記真空槽に供給することにより加熱下の前記基板表面に前記硼窒化ジルコニウム膜を成膜することを特徴とする半導体装置の製造方法。

【請求項4】

請求項3に記載する半導体装置の製造方法であって、

前記基板に形成された下地金属膜に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記下地金属膜までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程と、

前記凹部内を埋め込むように前記シリコン系絶縁膜に前記金属膜を積層して当該金属膜を平坦化することにより前記凹部に埋め込まれた配線を形成し、前記金属膜である前記配線と前記配線を囲う前記シリコン系絶縁膜とを前記基板表面に露出させる工程とを備え、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板表面に前記硼窒化ジルコニウム膜を成膜することで前記シリコン系絶縁膜と前記配線とを覆うメタルキャップ膜を形成することを特徴とする半導体装置の製造方法。

【請求項5】

請求項3に記載する半導体装置の製造方法であって、

前記基板に形成された前記金属膜である配線に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記配線までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程を備え、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板表面に前記硼窒化ジルコニウム膜を成膜することで、前記シリコン系絶縁膜と、前記凹部の底部である前記配線とを覆うバリア膜を形成することを特徴とする半導体装

置の製造方法。

【請求項1】

炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱した状態で収容する真空槽と、

励起した水素を前記真空槽へ供給して加熱下の基板表面を表面処理する表面処理部と、

Zr(BH4)4と励起した窒素とを前記真空槽へ供給して加熱下の前記基板表面に硼窒化ジルコニウム膜を成膜処理する成膜処理部と、

前記表面処理部を駆動して前記表面処理を実行した後に前記成膜処理部を駆動して前記成膜処理を実行する制御部と

を備えた半導体装置の製造装置。

【請求項2】

請求項1に記載する半導体装置の製造装置であって、

前記真空槽に連結された1つの管へ水素ガスと窒素ガスとを選択的に供給するガス供給部と、

前記管内へマイクロ波を照射するマイクロ波電源とを備え、

前記制御部は、

前記表面処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記水素ガスにマイクロ波を照射することにより前記水素ガスを前記励起した水素にして前記真空槽へ供給し、前記成膜処理を実行するときに、前記ガス供給部と前記マイクロ波電源とを駆動して前記管内の前記窒素ガスにマイクロ波を照射することで前記窒素ガスを前記励起した窒素にして前記真空槽へ供給することを特徴とする半導体装置の製造装置。

【請求項3】

炭素含有のシリコン系絶縁膜と前記シリコン系絶縁膜に囲まれた金属膜とが露出する基板を加熱して基板表面に硼窒化ジルコニウム膜を成膜する工程を備えた半導体装置の製造方法であって、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板が搬入された真空槽に励起した水素を供給して加熱下の前記基板表面を前記励起した水素に曝した後、前記真空槽への前記水素の供給を停止してZr(BH4)4と励起した窒素とを前記真空槽に供給することにより加熱下の前記基板表面に前記硼窒化ジルコニウム膜を成膜することを特徴とする半導体装置の製造方法。

【請求項4】

請求項3に記載する半導体装置の製造方法であって、

前記基板に形成された下地金属膜に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記下地金属膜までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程と、

前記凹部内を埋め込むように前記シリコン系絶縁膜に前記金属膜を積層して当該金属膜を平坦化することにより前記凹部に埋め込まれた配線を形成し、前記金属膜である前記配線と前記配線を囲う前記シリコン系絶縁膜とを前記基板表面に露出させる工程とを備え、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板表面に前記硼窒化ジルコニウム膜を成膜することで前記シリコン系絶縁膜と前記配線とを覆うメタルキャップ膜を形成することを特徴とする半導体装置の製造方法。

【請求項5】

請求項3に記載する半導体装置の製造方法であって、

前記基板に形成された前記金属膜である配線に前記シリコン系絶縁膜を積層して前記シリコン系絶縁膜の表面から前記配線までを貫通する凹部を前記シリコン系絶縁膜に凹設する工程を備え、

前記硼窒化ジルコニウム膜を成膜する工程は、

前記基板表面に前記硼窒化ジルコニウム膜を成膜することで、前記シリコン系絶縁膜と、前記凹部の底部である前記配線とを覆うバリア膜を形成することを特徴とする半導体装

置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−10624(P2010−10624A)

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願番号】特願2008−171470(P2008−171470)

【出願日】平成20年6月30日(2008.6.30)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願日】平成20年6月30日(2008.6.30)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

[ Back to top ]