半導体装置の配線およびその製造方法

【課題】 半導体基板に電気的に接続するアルミニウム系金属からなる配線は、オーバエッチング時にその配線下部にアンダーカットを生じるため、配線の信頼性を大きく低下させていた。

【解決手段】 半導体基板11に電気的に接続されている配線21であって、配線21は、半導体基板11上に形成された絶縁膜12上に設けられ、サイドエッチング防止層22とこのサイドエッチング防止層22上に形成した導電層23とからなるものである。上記サイドエッチング防止層22は絶縁膜12上で少なくとも70nmの厚さを有することが必要である。

【解決手段】 半導体基板11に電気的に接続されている配線21であって、配線21は、半導体基板11上に形成された絶縁膜12上に設けられ、サイドエッチング防止層22とこのサイドエッチング防止層22上に形成した導電層23とからなるものである。上記サイドエッチング防止層22は絶縁膜12上で少なくとも70nmの厚さを有することが必要である。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、半導体装置の配線およびその製造方法に関し、詳しくは半導体基板に電気的に接続する配線およびその製造方法に関する。

【0002】

【従来の技術】従来の半導体装置の配線は、例えば半導体基板上の絶縁膜上に配線が設けられていた。その配線は例えばアルミニウム系金属で形成されており、浅い接合の拡散層にコンタクトを取る場合には、通常、拡散層とのコンタクト部分にアルミニウムの突き抜けを防止するためのバリア層となるバリアメタルが形成されている。

【0003】

【発明が解決しようとする課題】しかしながら、半導体基板に電気的に接続するアルミニウム系金属からなる導電膜をエッチングして形成した配線は、図5に示すように、配線111のアルミニウム系金属部112の下部にいわゆるサイドエッチングが生じてアンダーカット121が形成される。このアンダーカット121は、下地となる絶縁膜上からおよそ50nmの高さまでを中心にして生じている。このアンダーカット部121の発生によって配線111の断面形状が悪化するので、配線111の信頼性は低下していた。さらにサイドエッチングが進行すると配線111は絶縁膜101上から浮いた状態に形成されるため、配線の信頼性は非常に低下した。なお、図5では、配線111の下層にバリアメタル層131が形成され、また配線111上には反射防止膜132、酸化シリコン膜133およびエッチングマスクとして用いたレジストパターン134が形成された状態が示されている。

【0004】次に上記アンダーカット部が配線の下部に発生する原因を説明する。エッチングにより配線の形成を行うと、通常、配線の側壁にはエッチングにともなう反応生成物からなる側壁保護膜が形成される。この側壁保護膜は、配線の側壁上部に厚く形成され、下部に向かうにしたがって薄く形成される。そのため、配線下部の薄く形成されている側壁保護膜が最も弱くなるので、その部分がオーバエッチング時に破れ、そこから配線の中央部方向に向かってサイドエッチングが進行してアンダーカットが形成されることになる。

【0005】

【課題を解決するための手段】本発明は、上記課題を解決するためになされた半導体装置の配線およびその製造方法である。

【0006】すなわち、半導体装置の配線は、半導体基板に電気的に接続されているものであって、半導体基板上に形成された絶縁膜上に設けられたサイドエッチング防止層と、その上に形成した導電層とからなる。

【0007】上記半導体装置の配線では、導電層の下層にサイドエッチング防止層が形成されていることから、オーバエッチングを行っても配線の下部にサイドエッチングによるアンダーカットがほとんど形成されないものとなる。

【0008】配線の製造方法は、半導体基板に電気的に接続する導電層を同半導体基板上の絶縁膜上に形成した後、この導電層をエッチングして半導体基板に電気的に接続する配線を形成する配線の製造方法であって、配線形成時のエッチングの際に生じるサイドエッチングを防ぐ材料からなり導電性を有するサイドエッチング防止層を上記絶縁膜上に形成した後、このサイドエッチング防止層上に上記導電層を形成するという製造方法である。

【0009】上記配線の製造方法では、導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層を形成した後、このサイドエッチング防止層上に導電層を形成することから、上記導電層およびサイドエッチング防止層をエッチングして形成される配線の下部はエッチング防止層となる。そのため、オーバエッチングを行っても、エッチング防止層によってサイドエッチングの発生が抑制されるので、配線にはアンダーカットがほとんど形成されなくなる。

【0010】

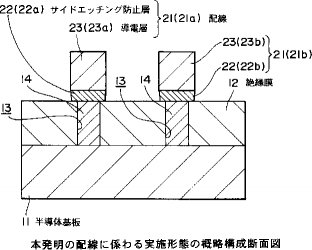

【発明の実施の形態】本発明の半導体装置の配線に係わる実施形態の一例を、図1の概略構成断面図によって説明する。

【0011】図1に示すように、半導体基板11上には絶縁膜12が例えば酸化膜で形成されている。この絶縁膜12には上記半導体基板11に形成された例えば拡散層(図示省略)に達するコンタクトホール13が形成されている。このコンタクトホール13には、上記半導体基板11に電気的に接続するプラグ14が例えばタングステンで形成されている。このプラグ14の下層にはいわゆるバリアメタル(図示省略)が形成されている場合もある。

【0012】上記絶縁膜12上には、上記プラグ14を介して上記半導体基板11に電気的に接続する配線21(21a,21b)が形成されている。上記配線21(21a,21b)は、サイドエッチング防止層22(22a,22b)と、このサイドエッチング防止層22(22a,22b)上に形成した導電層23(23a,23b)とからなる。

【0013】上記サイドエッチング防止層22は、例えば窒化チタン(TiN)、チタン(Ti)、チタンタングステン(TiW)のうちの1種類または複数種類からなる。すなわち、サイドエッチング防止層22は単層または複数層からなる。このサイドエッチング防止層22の厚さは、下地の絶縁膜12上において少なくとも70nmの厚さを有していることが必要であり、90nm〜250nm程度の厚さを有することが好ましい。

【0014】上記導電層23は、例えばアルミニウム金属またはアルミニウム合金層からなる。なお、上記サイドエッチング防止層22とその下地となる絶縁膜12との密着性が不十分の場合には、その間にチタン膜のような下地との密着性に優れている密着層(図示省略)を形成することが好ましい。

【0015】上記半導体装置の配線21では、導電層23の下層にサイドエッチング防止層22が形成されている。しかも、サイドエッチング防止層22は下地の絶縁膜12上で少なくとも70nmの厚さを有する状態に形成されていることから、サイドエッチングを最も生じる配線21の領域はサイドエッチング防止層22で形成されていることになる。したがって、オーバエッチングが行われてもサイドエッチングの発生が防止されるので、信頼性に影響を及ぼすようなアンダーカットは形成されない。

【0016】なお、上記配線21において導電層23上に反射防止膜(図示省略)を形成した構成であっても、反射防止膜に影響されることなく上記同様に、オーバエッチング時のサイドエッチングの発生を防止することができる。また上記配線21ではコンタクトホール13の内部にプラグ14を形成した構成で説明したが、プラグを形成せずにコンタクトホール13の内部に直接サイドエッチング防止層22を形成し、さらに導電層23を形成した構成であってもよい。この構成では、サイドエッチング防止層22にバリアメタルの作用を持たせることも可能である。

【0017】次に本発明の配線の製造方法に係わる実施形態の一例を、図2の製造工程図によって説明する。図2R>2では、プラグを介して半導体基板に電気的に接続される配線の製造方法を示す。また前記図1によって説明した構成部品と同様のものには同一符号を付す。

【0018】図2の(1)に示すように、通常のプロセスによって、半導体基板11上に絶縁膜12を例えば酸化膜で形成する。次いでレジスト塗布およびリソグラフィー技術によって、上記絶縁膜12上にレジストからなるエッチングマスク(図示省略)を形成した後、それをマスクに用いたエッチングによって、上記絶縁膜12に、上記半導体基板11に形成された例えば拡散層(図示省略)に達するコンタクトホール13を形成する。その後上記エッチングマスクを除去する。次に上記コンタクトホール13内に、上記半導体基板11に電気的に接続する導電性のプラグ14を、例えばコンタクトホール13内にタングステン膜を埋め込んだ後にそれをエッチバックする方法(ブランケットタングステンプラグ形成法)によって形成する。なお、上記プラグ14の下層に、いわゆるバリアメタル(図示省略)を形成する場合もある。

【0019】次いで上記絶縁膜12上に、上記プラグ14を介して上記半導体基板11に電気的に接続するサイドエッチング防止層22を、例えばスパッタリングまたはCVD法のような薄膜形成技術によって形成する。このサイドエッチング防止層22は、例えば窒化チタン(TiN)、チタン(Ti)、チタンタングステン(TiW)等のチタン系材料のうちの1種類または複数種類からなる。すなわち、サイドエッチング防止層22は単層に形成してもよく、または複数層に形成してもよい。しかも下地となる絶縁膜12上での厚さが少なくとも70nmを有する状態になるように形成する必要があり、好ましくは90nm〜250nm程度の厚さを有する状態に形成する。なお、上記サイドエッチング防止層22とその下地となる絶縁膜12との密着性が不十分の場合には、その間に例えばチタン膜のような下地との密着性に優れている密着層(図示省略)を形成することが好ましい。

【0020】次いで、上記サイドエッチング防止層22上に導電層となる導電層23を形成する。この導電層23は、例えばアルミニウム金属またはアルミニウム合金層からなる。必要があれば、上記導電層23上に反射防止膜(図示省略)等を形成する。

【0021】その後図2の(2)に示すように、レジスト塗布技術によって上記導電層23上にレジスト膜を形成する。その後、通常のリソグラフィー技術によって上記レジスト膜をパターニングしてエッチングマスクとなるレジストパターン41を形成する。なお、この(2)の図面では、半導体基板11の図示は省略した。

【0022】次いで上記レジストパターン41をエッチングマスクに用いて、上記導電層23およびサイドエッチング防止層22をエッチングする。その結果、図2の(3)に示すように、上記プラグ14(14a)に接続するサイドエッチング防止層22(22a)と導電層23(23a)とからなる配線21(21a)が形成されるとともに、上記プラグ14(14b)に接続するサイドエッチング防止層22(22b)と導電層23(23b)とからなる配線21(21b)が形成される。その後、上記レジストパターン41〔前記図2の(2)参照〕を除去する。

【0023】上記配線の製造方法では、導電層23をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層22を絶縁膜12上に形成した後に、サイドエッチング防止層22上に導電層23を形成することから、オーバエッチングの際にはエッチング防止層22によってサイドエッチングの発生が防止される。そのため、配線21には信頼性の影響を及ぼすようなアンダーカットは形成されない。しかも上記サイドエッチング防止層22は、少なくとも70nm程度の膜厚、好ましくは90nm〜250nm程度の膜厚に形成されていることから、サイドエッチングが最も進行しやすい高さの領域はサイドエッチング防止層22が形成されていることになる。このように、オーバエッチング時にこの配線21の側壁に形成されている側壁保護膜(図示省略)の最も弱い部分にサイドエッチング防止層22が形成されているので、オーバエッチング時のサイドエッチングによるアンダーカットは形成されなくなる。

【0024】一方、サイドエッチング防止層22の厚さが70nmよりも薄く形成された場合には、導電層23のオーバエッチングの際にアンダーカットを発生する可能性が高くなる。またサイドエッチング防止層22の厚さが250nmを越える場合には、配線抵抗が大きくなりすぎるので好ましいとはいえない。したがって、サイドエッチング防止層22の厚さは90nm〜250nmが好ましいといえる。

【0025】上記製造方法において、図3の(1)に示すように、半導体基板11上に絶縁膜12を形成した後にサイドエッチング防止層22を形成する。その後図3の(2)に示すように、上記サイドエッチング防止層22および絶縁膜12にコンタクトホール13を形成し、さらにコンタクトホール13の内部にプラグ14を形成する。そして図3の(3)に示すように、上記サイドエッチング防止膜22上にプラグ14に接続する導電層23を形成してもよい。その後の工程は上記図2の(2),(3)によって説明した工程と同様である。

【0026】上記各製造方法ではコンタクトホール13の内部にプラグ14を形成したが、プラグを形成せずにコンタクトホール13の内部に直接サイドエッチング防止層22を形成し、さらに導電層23を形成してもよい。このような製造方法では、サイドエッチング防止層22にバリアメタルの作用を持たせることも可能である。

【0027】次にサイドエッチング防止膜22の膜厚とサイドエッチング量との関係を調べた。その結果を図4によって説明する。なお、エッチングでは、有磁場型マイクロ波エッチング装置を用い、エッチングガスに三塩化ホウ素(BCl3 )〔流量=80sccm〕と塩素(Cl2 )〔流量=120sccm〕とを用い、エッチング雰囲気の圧力を1.067Pa、マイクロ波パワーを100W、基板バイアス電流を350mA、オーバエッチング時間をジャストエッチング時間に対して50%とした。

【0028】図4の(1)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが20nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが500nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23の下部に大きなアンダーカット51が形成された。これは、上記アンダーカット51を生じた付近の側壁保護膜がオーバエッチング時に最も弱くなっていたためである。なお、このエッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0029】図4の(2)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが100nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが400nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23には、アンダーカットは形成されず、サイドエッチング防止膜22が逆テーパ形状にわずかにエッチングされたに止まった。なお、エッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0030】図4の(3)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが200nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが300nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23には、アンダーカットは形成されず、サイドエッチング防止膜22が逆テーパ形状にわずかにエッチングされたに止まった。なお、エッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0031】上記結果より、サイドエッチング防止膜22を少なくとも70nm程度の厚さに形成しておけば、導電層23のエッチング(特にオーバエッチング時)に、配線21には信頼性に影響を及ぼすようなアンダーカットは形成されないことが確認された。このことは、サイドエッチング防止膜22によって、配線を形成する際に行うオーバエッチング時に発生するサイドエッチングが防止されているためといえる。

【0032】

【発明の効果】以上、説明したように本発明の半導体装置の配線によれば、導電層の下層にサイドエッチング防止層が形成されているので、配線の下部にエッチングによるアンダーカットがほとんど形成されないものとなる。よって、信頼性の高い配線となり、半導体装置の信頼性の向上が図れる。

【0033】本発明のの配線の製造方法によれば、導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層を形成してから、この上に導電層を形成した後、配線を形成するエッチングを行うので、エッチング防止層によりオーバエッチング時のサイドエッチングの発生が防止される。したがって、配線にはアンダーカットがほとんど形成されなくなるので、信頼性の高い配線を形成することが可能になる。

【図面の簡単な説明】

【図1】本発明の配線に係わる実施形態の概略構成断面図である。

【図2】本発明の配線の製造方法に係わる製造工程図である。

【図3】配線の製造方法に係わる別の製造工程図である。

【図4】サイドエッチング防止膜の膜厚によるサイドエッチング状態の説明図である。

【図5】課題の説明図である。

【符号の説明】

11 半導体基板 12 絶縁膜 21 配線

22 サイドエッチング防止層 23 導電層

【0001】

【発明の属する技術分野】本発明は、半導体装置の配線およびその製造方法に関し、詳しくは半導体基板に電気的に接続する配線およびその製造方法に関する。

【0002】

【従来の技術】従来の半導体装置の配線は、例えば半導体基板上の絶縁膜上に配線が設けられていた。その配線は例えばアルミニウム系金属で形成されており、浅い接合の拡散層にコンタクトを取る場合には、通常、拡散層とのコンタクト部分にアルミニウムの突き抜けを防止するためのバリア層となるバリアメタルが形成されている。

【0003】

【発明が解決しようとする課題】しかしながら、半導体基板に電気的に接続するアルミニウム系金属からなる導電膜をエッチングして形成した配線は、図5に示すように、配線111のアルミニウム系金属部112の下部にいわゆるサイドエッチングが生じてアンダーカット121が形成される。このアンダーカット121は、下地となる絶縁膜上からおよそ50nmの高さまでを中心にして生じている。このアンダーカット部121の発生によって配線111の断面形状が悪化するので、配線111の信頼性は低下していた。さらにサイドエッチングが進行すると配線111は絶縁膜101上から浮いた状態に形成されるため、配線の信頼性は非常に低下した。なお、図5では、配線111の下層にバリアメタル層131が形成され、また配線111上には反射防止膜132、酸化シリコン膜133およびエッチングマスクとして用いたレジストパターン134が形成された状態が示されている。

【0004】次に上記アンダーカット部が配線の下部に発生する原因を説明する。エッチングにより配線の形成を行うと、通常、配線の側壁にはエッチングにともなう反応生成物からなる側壁保護膜が形成される。この側壁保護膜は、配線の側壁上部に厚く形成され、下部に向かうにしたがって薄く形成される。そのため、配線下部の薄く形成されている側壁保護膜が最も弱くなるので、その部分がオーバエッチング時に破れ、そこから配線の中央部方向に向かってサイドエッチングが進行してアンダーカットが形成されることになる。

【0005】

【課題を解決するための手段】本発明は、上記課題を解決するためになされた半導体装置の配線およびその製造方法である。

【0006】すなわち、半導体装置の配線は、半導体基板に電気的に接続されているものであって、半導体基板上に形成された絶縁膜上に設けられたサイドエッチング防止層と、その上に形成した導電層とからなる。

【0007】上記半導体装置の配線では、導電層の下層にサイドエッチング防止層が形成されていることから、オーバエッチングを行っても配線の下部にサイドエッチングによるアンダーカットがほとんど形成されないものとなる。

【0008】配線の製造方法は、半導体基板に電気的に接続する導電層を同半導体基板上の絶縁膜上に形成した後、この導電層をエッチングして半導体基板に電気的に接続する配線を形成する配線の製造方法であって、配線形成時のエッチングの際に生じるサイドエッチングを防ぐ材料からなり導電性を有するサイドエッチング防止層を上記絶縁膜上に形成した後、このサイドエッチング防止層上に上記導電層を形成するという製造方法である。

【0009】上記配線の製造方法では、導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層を形成した後、このサイドエッチング防止層上に導電層を形成することから、上記導電層およびサイドエッチング防止層をエッチングして形成される配線の下部はエッチング防止層となる。そのため、オーバエッチングを行っても、エッチング防止層によってサイドエッチングの発生が抑制されるので、配線にはアンダーカットがほとんど形成されなくなる。

【0010】

【発明の実施の形態】本発明の半導体装置の配線に係わる実施形態の一例を、図1の概略構成断面図によって説明する。

【0011】図1に示すように、半導体基板11上には絶縁膜12が例えば酸化膜で形成されている。この絶縁膜12には上記半導体基板11に形成された例えば拡散層(図示省略)に達するコンタクトホール13が形成されている。このコンタクトホール13には、上記半導体基板11に電気的に接続するプラグ14が例えばタングステンで形成されている。このプラグ14の下層にはいわゆるバリアメタル(図示省略)が形成されている場合もある。

【0012】上記絶縁膜12上には、上記プラグ14を介して上記半導体基板11に電気的に接続する配線21(21a,21b)が形成されている。上記配線21(21a,21b)は、サイドエッチング防止層22(22a,22b)と、このサイドエッチング防止層22(22a,22b)上に形成した導電層23(23a,23b)とからなる。

【0013】上記サイドエッチング防止層22は、例えば窒化チタン(TiN)、チタン(Ti)、チタンタングステン(TiW)のうちの1種類または複数種類からなる。すなわち、サイドエッチング防止層22は単層または複数層からなる。このサイドエッチング防止層22の厚さは、下地の絶縁膜12上において少なくとも70nmの厚さを有していることが必要であり、90nm〜250nm程度の厚さを有することが好ましい。

【0014】上記導電層23は、例えばアルミニウム金属またはアルミニウム合金層からなる。なお、上記サイドエッチング防止層22とその下地となる絶縁膜12との密着性が不十分の場合には、その間にチタン膜のような下地との密着性に優れている密着層(図示省略)を形成することが好ましい。

【0015】上記半導体装置の配線21では、導電層23の下層にサイドエッチング防止層22が形成されている。しかも、サイドエッチング防止層22は下地の絶縁膜12上で少なくとも70nmの厚さを有する状態に形成されていることから、サイドエッチングを最も生じる配線21の領域はサイドエッチング防止層22で形成されていることになる。したがって、オーバエッチングが行われてもサイドエッチングの発生が防止されるので、信頼性に影響を及ぼすようなアンダーカットは形成されない。

【0016】なお、上記配線21において導電層23上に反射防止膜(図示省略)を形成した構成であっても、反射防止膜に影響されることなく上記同様に、オーバエッチング時のサイドエッチングの発生を防止することができる。また上記配線21ではコンタクトホール13の内部にプラグ14を形成した構成で説明したが、プラグを形成せずにコンタクトホール13の内部に直接サイドエッチング防止層22を形成し、さらに導電層23を形成した構成であってもよい。この構成では、サイドエッチング防止層22にバリアメタルの作用を持たせることも可能である。

【0017】次に本発明の配線の製造方法に係わる実施形態の一例を、図2の製造工程図によって説明する。図2R>2では、プラグを介して半導体基板に電気的に接続される配線の製造方法を示す。また前記図1によって説明した構成部品と同様のものには同一符号を付す。

【0018】図2の(1)に示すように、通常のプロセスによって、半導体基板11上に絶縁膜12を例えば酸化膜で形成する。次いでレジスト塗布およびリソグラフィー技術によって、上記絶縁膜12上にレジストからなるエッチングマスク(図示省略)を形成した後、それをマスクに用いたエッチングによって、上記絶縁膜12に、上記半導体基板11に形成された例えば拡散層(図示省略)に達するコンタクトホール13を形成する。その後上記エッチングマスクを除去する。次に上記コンタクトホール13内に、上記半導体基板11に電気的に接続する導電性のプラグ14を、例えばコンタクトホール13内にタングステン膜を埋め込んだ後にそれをエッチバックする方法(ブランケットタングステンプラグ形成法)によって形成する。なお、上記プラグ14の下層に、いわゆるバリアメタル(図示省略)を形成する場合もある。

【0019】次いで上記絶縁膜12上に、上記プラグ14を介して上記半導体基板11に電気的に接続するサイドエッチング防止層22を、例えばスパッタリングまたはCVD法のような薄膜形成技術によって形成する。このサイドエッチング防止層22は、例えば窒化チタン(TiN)、チタン(Ti)、チタンタングステン(TiW)等のチタン系材料のうちの1種類または複数種類からなる。すなわち、サイドエッチング防止層22は単層に形成してもよく、または複数層に形成してもよい。しかも下地となる絶縁膜12上での厚さが少なくとも70nmを有する状態になるように形成する必要があり、好ましくは90nm〜250nm程度の厚さを有する状態に形成する。なお、上記サイドエッチング防止層22とその下地となる絶縁膜12との密着性が不十分の場合には、その間に例えばチタン膜のような下地との密着性に優れている密着層(図示省略)を形成することが好ましい。

【0020】次いで、上記サイドエッチング防止層22上に導電層となる導電層23を形成する。この導電層23は、例えばアルミニウム金属またはアルミニウム合金層からなる。必要があれば、上記導電層23上に反射防止膜(図示省略)等を形成する。

【0021】その後図2の(2)に示すように、レジスト塗布技術によって上記導電層23上にレジスト膜を形成する。その後、通常のリソグラフィー技術によって上記レジスト膜をパターニングしてエッチングマスクとなるレジストパターン41を形成する。なお、この(2)の図面では、半導体基板11の図示は省略した。

【0022】次いで上記レジストパターン41をエッチングマスクに用いて、上記導電層23およびサイドエッチング防止層22をエッチングする。その結果、図2の(3)に示すように、上記プラグ14(14a)に接続するサイドエッチング防止層22(22a)と導電層23(23a)とからなる配線21(21a)が形成されるとともに、上記プラグ14(14b)に接続するサイドエッチング防止層22(22b)と導電層23(23b)とからなる配線21(21b)が形成される。その後、上記レジストパターン41〔前記図2の(2)参照〕を除去する。

【0023】上記配線の製造方法では、導電層23をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層22を絶縁膜12上に形成した後に、サイドエッチング防止層22上に導電層23を形成することから、オーバエッチングの際にはエッチング防止層22によってサイドエッチングの発生が防止される。そのため、配線21には信頼性の影響を及ぼすようなアンダーカットは形成されない。しかも上記サイドエッチング防止層22は、少なくとも70nm程度の膜厚、好ましくは90nm〜250nm程度の膜厚に形成されていることから、サイドエッチングが最も進行しやすい高さの領域はサイドエッチング防止層22が形成されていることになる。このように、オーバエッチング時にこの配線21の側壁に形成されている側壁保護膜(図示省略)の最も弱い部分にサイドエッチング防止層22が形成されているので、オーバエッチング時のサイドエッチングによるアンダーカットは形成されなくなる。

【0024】一方、サイドエッチング防止層22の厚さが70nmよりも薄く形成された場合には、導電層23のオーバエッチングの際にアンダーカットを発生する可能性が高くなる。またサイドエッチング防止層22の厚さが250nmを越える場合には、配線抵抗が大きくなりすぎるので好ましいとはいえない。したがって、サイドエッチング防止層22の厚さは90nm〜250nmが好ましいといえる。

【0025】上記製造方法において、図3の(1)に示すように、半導体基板11上に絶縁膜12を形成した後にサイドエッチング防止層22を形成する。その後図3の(2)に示すように、上記サイドエッチング防止層22および絶縁膜12にコンタクトホール13を形成し、さらにコンタクトホール13の内部にプラグ14を形成する。そして図3の(3)に示すように、上記サイドエッチング防止膜22上にプラグ14に接続する導電層23を形成してもよい。その後の工程は上記図2の(2),(3)によって説明した工程と同様である。

【0026】上記各製造方法ではコンタクトホール13の内部にプラグ14を形成したが、プラグを形成せずにコンタクトホール13の内部に直接サイドエッチング防止層22を形成し、さらに導電層23を形成してもよい。このような製造方法では、サイドエッチング防止層22にバリアメタルの作用を持たせることも可能である。

【0027】次にサイドエッチング防止膜22の膜厚とサイドエッチング量との関係を調べた。その結果を図4によって説明する。なお、エッチングでは、有磁場型マイクロ波エッチング装置を用い、エッチングガスに三塩化ホウ素(BCl3 )〔流量=80sccm〕と塩素(Cl2 )〔流量=120sccm〕とを用い、エッチング雰囲気の圧力を1.067Pa、マイクロ波パワーを100W、基板バイアス電流を350mA、オーバエッチング時間をジャストエッチング時間に対して50%とした。

【0028】図4の(1)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが20nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが500nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23の下部に大きなアンダーカット51が形成された。これは、上記アンダーカット51を生じた付近の側壁保護膜がオーバエッチング時に最も弱くなっていたためである。なお、このエッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0029】図4の(2)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが100nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが400nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23には、アンダーカットは形成されず、サイドエッチング防止膜22が逆テーパ形状にわずかにエッチングされたに止まった。なお、エッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0030】図4の(3)には、サイドエッチング防止膜22を下層から、チタン膜(厚さが20nm)、窒化チタン膜(厚さが200nm)、チタン膜(厚さが5nm)で形成し、その上にアルミニウム−銅合金層からなる導電層23(厚さが300nm)、反射防止膜24となるチタン膜(厚さが5nm)、窒化チタン膜(厚さが100nm)およびチタン膜(厚さが5nm)、さらに酸化シリコン膜25を順に形成して、それらをエッチングして配線21を形成した場合を示す。なお、エッチングマスクにはレジストパターン41を用いた。その結果、導電層23には、アンダーカットは形成されず、サイドエッチング防止膜22が逆テーパ形状にわずかにエッチングされたに止まった。なお、エッチングの際には、下地の絶縁膜12の表層もわずかにエッチングされている。

【0031】上記結果より、サイドエッチング防止膜22を少なくとも70nm程度の厚さに形成しておけば、導電層23のエッチング(特にオーバエッチング時)に、配線21には信頼性に影響を及ぼすようなアンダーカットは形成されないことが確認された。このことは、サイドエッチング防止膜22によって、配線を形成する際に行うオーバエッチング時に発生するサイドエッチングが防止されているためといえる。

【0032】

【発明の効果】以上、説明したように本発明の半導体装置の配線によれば、導電層の下層にサイドエッチング防止層が形成されているので、配線の下部にエッチングによるアンダーカットがほとんど形成されないものとなる。よって、信頼性の高い配線となり、半導体装置の信頼性の向上が図れる。

【0033】本発明のの配線の製造方法によれば、導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなるサイドエッチング防止層を形成してから、この上に導電層を形成した後、配線を形成するエッチングを行うので、エッチング防止層によりオーバエッチング時のサイドエッチングの発生が防止される。したがって、配線にはアンダーカットがほとんど形成されなくなるので、信頼性の高い配線を形成することが可能になる。

【図面の簡単な説明】

【図1】本発明の配線に係わる実施形態の概略構成断面図である。

【図2】本発明の配線の製造方法に係わる製造工程図である。

【図3】配線の製造方法に係わる別の製造工程図である。

【図4】サイドエッチング防止膜の膜厚によるサイドエッチング状態の説明図である。

【図5】課題の説明図である。

【符号の説明】

11 半導体基板 12 絶縁膜 21 配線

22 サイドエッチング防止層 23 導電層

【特許請求の範囲】

【請求項1】 半導体基板に電気的に接続されている配線であって、前記配線は、前記半導体基板上に形成された絶縁膜上に設けられ、サイドエッチング防止層と該サイドエッチング防止層上に形成した導電層とからなることを特徴とする半導体装置の配線。

【請求項2】 請求項1記載の半導体装置の配線において、前記サイドエッチング防止層は前記絶縁膜上で少なくとも70nmの厚さを有することを特徴とする半導体装置の配線。

【請求項3】 半導体基板に電気的に接続する導電層を該半導体基板上の絶縁膜上に形成した後、該導電層をエッチングして該半導体基板に電気的に接続する配線を形成する配線の製造方法において、前記絶縁膜上に、前記導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなり導電性を有するサイドエッチング防止層を形成した後、前記サイドエッチング防止層上に前記導電層を形成することを特徴とする配線の製造方法。

【請求項4】 請求項1記載の半導体装置の配線において、前記サイドエッチング防止層は、前記絶縁膜上での厚さが少なくとも70nmを有する状態に形成されることを特徴とする配線の製造方法。

【請求項1】 半導体基板に電気的に接続されている配線であって、前記配線は、前記半導体基板上に形成された絶縁膜上に設けられ、サイドエッチング防止層と該サイドエッチング防止層上に形成した導電層とからなることを特徴とする半導体装置の配線。

【請求項2】 請求項1記載の半導体装置の配線において、前記サイドエッチング防止層は前記絶縁膜上で少なくとも70nmの厚さを有することを特徴とする半導体装置の配線。

【請求項3】 半導体基板に電気的に接続する導電層を該半導体基板上の絶縁膜上に形成した後、該導電層をエッチングして該半導体基板に電気的に接続する配線を形成する配線の製造方法において、前記絶縁膜上に、前記導電層をエッチングする際に生じるサイドエッチングを防ぐ材料からなり導電性を有するサイドエッチング防止層を形成した後、前記サイドエッチング防止層上に前記導電層を形成することを特徴とする配線の製造方法。

【請求項4】 請求項1記載の半導体装置の配線において、前記サイドエッチング防止層は、前記絶縁膜上での厚さが少なくとも70nmを有する状態に形成されることを特徴とする配線の製造方法。

【図1】

【図5】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【公開番号】特開平10−233395

【公開日】平成10年(1998)9月2日

【国際特許分類】

【出願番号】特願平9−34532

【出願日】平成9年(1997)2月19日

【出願人】(000002185)ソニー株式会社 (34,172)

【公開日】平成10年(1998)9月2日

【国際特許分類】

【出願日】平成9年(1997)2月19日

【出願人】(000002185)ソニー株式会社 (34,172)

[ Back to top ]