半導体装置の配線接続孔の形成方法

【課題】 簡略化された工程により、良好な被覆率が得られる半導体装置の配線接続孔の形成方法を目的とする。

【解決手段】 半導体素子1が形成された半導体基板2側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら層間絶縁層8、9、10を積層する工程と、層間絶縁層8、9、10上にフォトレジスト11を塗布しフォトレジストパタ−ン12a、12bを形成後、層間絶縁層8、9、10を前記半導体素子まで異方性エッチングして、配線接続孔13c、13dを形成する工程と、フォトレジスト11を除去後、不純物の濃度が増加すると共に層間絶縁層8、9、10のエッチング量が増加するアンモニア過水により配線接続孔13c、13dをエッチングして、配線接続孔13c、13dの上部が下部よりも広がった形状にする。

【解決手段】 半導体素子1が形成された半導体基板2側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら層間絶縁層8、9、10を積層する工程と、層間絶縁層8、9、10上にフォトレジスト11を塗布しフォトレジストパタ−ン12a、12bを形成後、層間絶縁層8、9、10を前記半導体素子まで異方性エッチングして、配線接続孔13c、13dを形成する工程と、フォトレジスト11を除去後、不純物の濃度が増加すると共に層間絶縁層8、9、10のエッチング量が増加するアンモニア過水により配線接続孔13c、13dをエッチングして、配線接続孔13c、13dの上部が下部よりも広がった形状にする。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、半導体装置の製造方法に係わり、特に、半導体装置の配線接続孔の形成方法に関する。

【0002】

【従来の技術】近年、LSIの微細化と共に、各半導体素子間を接続する配線の寸法幅は0.5μm以下にまで要求されている。各半導体素子間の配線は、半導体素子が形成された半導体基板上に層間絶縁層を形成後、フォトリソグラフィ法により前記層間絶縁層に配線接続孔を形成し、更に前記層間絶縁層及び前記配線接続孔にスパッタ法等により配線用金属材料を形成し、配線パタ−ンを形成して行っていた。配線の寸法幅の微細化に伴い、この配線接続孔の大きさも狭くなってくると、スパッタ法や蒸着法等により形成された配線材料は、この配線接続孔中に侵入しにくくなり、特に、配線接続孔の側壁に配線材料が付着しにくくなるため、半導体素子の接触不良や断線の原因となる可能性があった。LSIの信頼性の向上や安定動作のためには、配線接続孔中に均一に配線材料を充填し、接触不良や断線を生じることなく配線を行うことが必要とされていた。

【0003】従来のMOSFETに配線を施すための配線接続孔の形成方法について以下、図面を参照しながら説明する。図3は従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。Siからなる半導体基板2上にゲ−ト絶縁層6及びポリシリコンを順次形成後、図示しないフォトレジストを塗布し、フォトリソグラフィ法により、フォトレジストパタ−ンを形成して、前記金属膜をエッチング除去し、ゲ−ト電極7を形成する。ゲ−ト電極7下部に相当する部分の半導体基板2はゲ−ト5となる。このためゲ−ト5は半導体基板2の一部となっている。その後、ゲ−ト電極7をマスクとして拡散を行い、ソ−ス3及びドレイン4を形成する。こうして、ソ−ス3、ドレイン4及びゲ−ト5を備えたMOSFET1が得られる。更に、層間絶縁層15を積層後、フォトレジスト11を塗布する(図3R>3(A))。

【0004】フォトリソグラフィ法により、フォトレジスト11のゲ−ト電極7及びソ−ス3上部に相当する部分にフォトレジストパタ−ン16a及び16bを形成する(図3(B))。引き続いて、RIE(リアクティブ・イオン・エッチング)により、ゲ−ト絶縁膜6及び層間絶縁層15の異方性エッチング(エッチング深さ方向のみエッチングが可能なエッチング)を行って配線接続孔17a、17bを形成する。その後、アセトン等の有機溶剤や硫酸等によりフォトレジスト11を除去する(図3(C))。

【0005】この後、層間絶縁層15上及び配線接続孔17a、17bにスパッタ等によりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去してMOSFET1上に配線18を形成する(図4R>4)。この際、LSIの微細化のために、配線幅は0.5μm以下にすることが要求されることから配線接続孔17a、17bの幅は極めて細いため、図4に示すように、配線接続孔17a、17bにはAl等の配線用金属材料が均一に入り込まず、特に配線接続孔17a、17bの側壁で薄くなり、配線材料が配線接続孔を覆う割合を示す被覆率が悪かった。このため、ゲ−ト電極7やソ−ス3との接続が不安定になり、MOSFET1の接触不良を生じたり、断線を生じたりしていた。また、配線材料が配線接続孔17a、17bを覆う被覆率を改良するために、配線接続孔17a、17bの上部を下部より広く開口するようにしたものが提案された。

【0006】図5は他の従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。図3、図4と同一部分には同一符号を用い、その詳細な説明を省略する。半導体基板2上にソ−ス3、ドレイン4及びゲ−ト5を有したMOSFETを形成し、その上部にフォトレジスト11を塗布後、フォトレジスト11のゲ−ト電極7及びソ−ス3上部に相当する部分にフォトレジストパタ−ン16a及び16bを形成する工程までは、図3(A)及び(B)に示す図と同様であるので、詳細な説明は省略する。

【0007】この後、アンモニア過水等のウェットエッチングにより等方性エッチング(エッチング深さ方向と同時にエッチング面と平行な面方向にエッチングが可能なエッチング)を行って、層間絶縁層15を途中までエッチングして、凹部19a、19bを形成する(図5(A))。この際、等方性エッチングによりエッチング深さ方向と同時にエッチング面と平行な面方向にもエッチングするため、フォトレジスト11の下部における層間絶縁膜15がエッチングされ、凹部19a、19bは、フォトレジストパタ−ン16a及び16bの幅よりも広い形状となる。

【0008】引き続いて、RIEにより、ゲ−ト絶縁膜6及び層間絶縁層15の異方性エッチングを行って配線接続孔20a、20bを形成する。更に、アセトン等の有機溶剤や硫酸によりフォトレジスト11を除去する(図5(B))。この結果、配線接続孔20a、20bは、層間絶縁層15表面が開口したロ−ト形状となる。この後、層間絶縁層15上及び配線接続孔20a、20bにスパッタ等によりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去して配線する。

【0009】このようすると、配線接続孔20a、20bは層間絶縁層14表面で広く開口した形状となっているので、配線接続孔20a、20bの内部にAl等の配線金属材料が侵入しやすくなり、均一な配線金属材料を形成することができる。このため、配線接続孔20a、20bの配線金属材料の被覆率が良好となり、MOSFET1に接触不良や断線のない配線を行うことができる。

【0010】

【発明が解決しようとする課題】しかしながら、配線接続孔20a、20bの形成は、アンモニア過水等のエッチングによるウェット工程から、RIEによるドライ工程に続き、再びアセトン等の有機溶剤によるウェット工程が必要となり、ウェット工程からドライ工程、また、ドライ工程からウェット工程へ進む際のドライ工程とウエット工程間で洗浄等の準備工程が必要となるため、工程が増加し、繁雑になり、製造工程歩留りが低下するという原因を生じていた。そこで、本発明は、上記のような問題点を解消するためになされたもので、簡略化された工程により、良好な被覆率が得られる半導体装置の配線接続孔の形成方法を提供することを目的とする。

【0011】

【課題を解決するための手段】本発明の半導体装置の配線接続孔の形成方法による第1の発明は、半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物の濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする。

【0012】第2の発明は、半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を多層に積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記多層に積層された層間絶縁層を異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする。

【0013】第3の発明は、請求項2記載の半導体装置の配線接続孔の形成方法において、前記半導体基板上に多層に積層された前記層間絶縁層のうち、最下層の前記層間絶縁層はノンド−プであることを特徴とする。

【0014】半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら層間絶縁層を多層に積層し、更にフォトレジストパタ−ンを形成後、前記層間絶縁層を異方性エッチングして、配線接続孔を形成し、前記配線接続孔をアンモニア過水でエッチングして、前記配線接続孔の上部が下部よりも広がった形状にしているので、簡略化した工程で前記配線接続孔の下部まで十分、金属配線材料が入りやすくなり、被覆率の良好な配線を行うことができる。また、半導体基板上に多層に積層した前記層間絶縁層のうち、最下層の前記層間絶縁層をノンド−プにすると、その上部にリン、ボロンのうち少なくとも一方を含む不純物がド−プされ、積層された前記層間絶縁層からのボロン及びリンの拡散が抑えられるため半導体基板への拡散を防止することができる。

【0015】

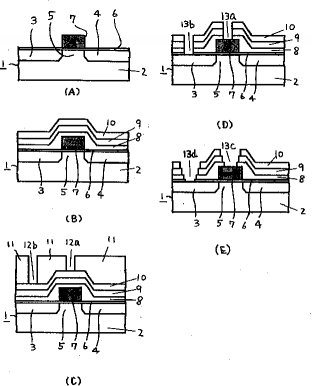

【発明の実施の形態】本発明によるMOSFETに配線を施すための配線接続孔の形成方法の一実施例について図を参照しながら以下に説明する。図1は、本発明のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。図2は、本発明におけるMOSFETに配線を施した断面図である。

【0016】(第1工程)Siからなる基板2上にゲ−ト絶縁層6及びポリシリコンを順次形成後、図示しないフォトレジストを塗布し、フォトリソグラフィ法により、フォトレジストパタ−ンを形成し、前記金属膜をエッチング除去し、ゲ−ト電極7を形成する。ゲ−ト電極7下部に相当する部分の半導体基板2はゲ−ト5となる。このためゲ−ト5は半導体基板2の一部となっている。その後、ゲ−ト電極7をマスクとして拡散を行い、ソ−ス3及びドレイン4を形成する。こうして、ソ−ス3、ドレイン4及びゲ−ト5を備えたMOSFET1が得られる(図1(A))。

【0017】(第2工程)次に、ゲ−ト絶縁層6及びゲ−ト電極7上にボロン及びリン不純物をド−プしながら第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を順次積層する(図1(B))。ここで、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10は、酸化シリコンからなる。この際、ボロン及びリン不純物の濃度は、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10の順に高くなっている。

【0018】(第3工程)この後、フォトレジスト11を塗布後、フォトリソ法により、フォトレジスト11のゲ−ト電極7及びソ−ス3に相当する部分の第3層間絶縁層10上にフォトレジストパタ−ン12a及び12bを形成する(図1(C))。

【0019】引き続いて、RIE(リアクティブ・イオン・エッチング)により、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10及びゲ−ト絶縁層6を異方性エッチングして、孔13a及び13bを形成する。その後、アセトン等の有機溶剤や硫酸によりフォトレジスト11を除去する(図1(D))。

【0020】(第4工程)次に、アンモニア過水(例えば、NH3 :H2 02 :H2 O=4000:50:50)でエッチングを行い、配線絶縁孔13c及び13dを形成する。この場合、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10は、ボロン及びリンの濃度が高い程、エッチング量は大きくなるので、ボロン及びリン濃度が最も低い第1層間絶縁層8ではエッチング量が小さく、濃度が最も高い第3層間絶縁層10ではエッチング量が最も大きくなる。第2層間絶縁層9のエッチング量は、第1層間絶縁層8のエッチング量と第3層間絶縁層10のエッチング量の間になる。このため、配線絶縁孔13c及び13dの幅は、第1層間絶縁層8から第3層間絶縁層10に向かって、広く開口した形状になる(図1(E))。

【0021】この後、層間絶縁層10上及び配線接続孔13c及び13dに図示しないスパッタによりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去して配線14をする(図2)。

【0022】このようにすると、図2に示すように配線接続孔13c、13dの幅は第3層間絶縁層10側が第1層間絶縁層8側よりも広く開口最も広がった形状であるので、配線接続孔13c、13dの内部にAl等の配線金属材料が侵入しやすくなり、配線接続孔13c、13d中での配線の被覆率が良好な配線14を行うことができる。また、RIEによる異方性エッチングを行うドライ工程からアンモニア過水を用いたウェット工程への切り替わりために必要な洗浄等の準備工程回数は1回だけとなり、工程が簡略化される。

【0023】本発明の実施例では、MOSFET1が形成された半導体基板2上に第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を形成する3層の場合について述べたが、第2層間絶縁層9、第3層間絶縁層10の形成を行わずに第1層間絶縁層8だけをけ形成し、第1層間絶縁層8に半導体基板2側から積層方向に向かってボロン及びリンを含む不純物の濃度を連続的に高くしても同様の効果が得られる。なお、2層以上の層間絶縁層についても広く適用されことはいうまでもない。また、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10にボロンとリンを同時にド−プしたが、ボロンとリンのどちらか一方の不純物をド−プするようにしても同様の効果が得られる。更に、半導体基板2上に第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を形成する3層の場合において、第1層間絶縁層8に不純物をド−プせず、ノンド−プにすると、半導体プロセスにおける熱処理工程で第2層間絶縁層9、第3層間絶縁層10にド−プしたボロン及びリンの半導体基板2への拡散が抑えられので、MOSFET1のしきい値電流の上昇やリ−ク電流の発生を防止できる。

【0024】

【発明の効果】本発明の半導体装置の配線接続孔の形成方法によれば、半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層し、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成し、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成後、前記フォトレジストを除去し、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にできるので、簡略化された工程で、かつ前記配線接続孔の下部まで十分、金属配線材料が入りやすくなり、被覆率の良好な配線を行うことができる。また、半導体基板上に多層に積層した前記層間絶縁層のうち、最下層の前記層間絶縁層をノンド−プにすると、その上部にリン、ボロンのうち少なくとも一方を含む不純物がド−プされ、積層された前記層間絶縁層からのボロン及びリンの拡散が抑えられるため半導体基板への拡散を防止することができる。

【図面の簡単な説明】

【図1】本発明におけるMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【図2】本発明におけるMOSFETに配線を施した断面図である。

【図3】従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【図4】従来のMOSFETに配線を施した断面図である。

【図5】従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【符号の説明】

1…MOSFET、2…半導体基板、3…ソ−ス、4…ドレイン、5…ゲ−ト6…ゲ−ト絶縁層、7…ゲ−ト電極、8…第1層間絶縁層、9…第2層間絶縁層、10…第3層間絶縁層、11…フォトレジスト、12a、12b…フォトレジストパタ−ン、13a、13b…孔、13c、13d…配線接続孔、14…配線

【0001】

【発明の属する技術分野】本発明は、半導体装置の製造方法に係わり、特に、半導体装置の配線接続孔の形成方法に関する。

【0002】

【従来の技術】近年、LSIの微細化と共に、各半導体素子間を接続する配線の寸法幅は0.5μm以下にまで要求されている。各半導体素子間の配線は、半導体素子が形成された半導体基板上に層間絶縁層を形成後、フォトリソグラフィ法により前記層間絶縁層に配線接続孔を形成し、更に前記層間絶縁層及び前記配線接続孔にスパッタ法等により配線用金属材料を形成し、配線パタ−ンを形成して行っていた。配線の寸法幅の微細化に伴い、この配線接続孔の大きさも狭くなってくると、スパッタ法や蒸着法等により形成された配線材料は、この配線接続孔中に侵入しにくくなり、特に、配線接続孔の側壁に配線材料が付着しにくくなるため、半導体素子の接触不良や断線の原因となる可能性があった。LSIの信頼性の向上や安定動作のためには、配線接続孔中に均一に配線材料を充填し、接触不良や断線を生じることなく配線を行うことが必要とされていた。

【0003】従来のMOSFETに配線を施すための配線接続孔の形成方法について以下、図面を参照しながら説明する。図3は従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。Siからなる半導体基板2上にゲ−ト絶縁層6及びポリシリコンを順次形成後、図示しないフォトレジストを塗布し、フォトリソグラフィ法により、フォトレジストパタ−ンを形成して、前記金属膜をエッチング除去し、ゲ−ト電極7を形成する。ゲ−ト電極7下部に相当する部分の半導体基板2はゲ−ト5となる。このためゲ−ト5は半導体基板2の一部となっている。その後、ゲ−ト電極7をマスクとして拡散を行い、ソ−ス3及びドレイン4を形成する。こうして、ソ−ス3、ドレイン4及びゲ−ト5を備えたMOSFET1が得られる。更に、層間絶縁層15を積層後、フォトレジスト11を塗布する(図3R>3(A))。

【0004】フォトリソグラフィ法により、フォトレジスト11のゲ−ト電極7及びソ−ス3上部に相当する部分にフォトレジストパタ−ン16a及び16bを形成する(図3(B))。引き続いて、RIE(リアクティブ・イオン・エッチング)により、ゲ−ト絶縁膜6及び層間絶縁層15の異方性エッチング(エッチング深さ方向のみエッチングが可能なエッチング)を行って配線接続孔17a、17bを形成する。その後、アセトン等の有機溶剤や硫酸等によりフォトレジスト11を除去する(図3(C))。

【0005】この後、層間絶縁層15上及び配線接続孔17a、17bにスパッタ等によりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去してMOSFET1上に配線18を形成する(図4R>4)。この際、LSIの微細化のために、配線幅は0.5μm以下にすることが要求されることから配線接続孔17a、17bの幅は極めて細いため、図4に示すように、配線接続孔17a、17bにはAl等の配線用金属材料が均一に入り込まず、特に配線接続孔17a、17bの側壁で薄くなり、配線材料が配線接続孔を覆う割合を示す被覆率が悪かった。このため、ゲ−ト電極7やソ−ス3との接続が不安定になり、MOSFET1の接触不良を生じたり、断線を生じたりしていた。また、配線材料が配線接続孔17a、17bを覆う被覆率を改良するために、配線接続孔17a、17bの上部を下部より広く開口するようにしたものが提案された。

【0006】図5は他の従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。図3、図4と同一部分には同一符号を用い、その詳細な説明を省略する。半導体基板2上にソ−ス3、ドレイン4及びゲ−ト5を有したMOSFETを形成し、その上部にフォトレジスト11を塗布後、フォトレジスト11のゲ−ト電極7及びソ−ス3上部に相当する部分にフォトレジストパタ−ン16a及び16bを形成する工程までは、図3(A)及び(B)に示す図と同様であるので、詳細な説明は省略する。

【0007】この後、アンモニア過水等のウェットエッチングにより等方性エッチング(エッチング深さ方向と同時にエッチング面と平行な面方向にエッチングが可能なエッチング)を行って、層間絶縁層15を途中までエッチングして、凹部19a、19bを形成する(図5(A))。この際、等方性エッチングによりエッチング深さ方向と同時にエッチング面と平行な面方向にもエッチングするため、フォトレジスト11の下部における層間絶縁膜15がエッチングされ、凹部19a、19bは、フォトレジストパタ−ン16a及び16bの幅よりも広い形状となる。

【0008】引き続いて、RIEにより、ゲ−ト絶縁膜6及び層間絶縁層15の異方性エッチングを行って配線接続孔20a、20bを形成する。更に、アセトン等の有機溶剤や硫酸によりフォトレジスト11を除去する(図5(B))。この結果、配線接続孔20a、20bは、層間絶縁層15表面が開口したロ−ト形状となる。この後、層間絶縁層15上及び配線接続孔20a、20bにスパッタ等によりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去して配線する。

【0009】このようすると、配線接続孔20a、20bは層間絶縁層14表面で広く開口した形状となっているので、配線接続孔20a、20bの内部にAl等の配線金属材料が侵入しやすくなり、均一な配線金属材料を形成することができる。このため、配線接続孔20a、20bの配線金属材料の被覆率が良好となり、MOSFET1に接触不良や断線のない配線を行うことができる。

【0010】

【発明が解決しようとする課題】しかしながら、配線接続孔20a、20bの形成は、アンモニア過水等のエッチングによるウェット工程から、RIEによるドライ工程に続き、再びアセトン等の有機溶剤によるウェット工程が必要となり、ウェット工程からドライ工程、また、ドライ工程からウェット工程へ進む際のドライ工程とウエット工程間で洗浄等の準備工程が必要となるため、工程が増加し、繁雑になり、製造工程歩留りが低下するという原因を生じていた。そこで、本発明は、上記のような問題点を解消するためになされたもので、簡略化された工程により、良好な被覆率が得られる半導体装置の配線接続孔の形成方法を提供することを目的とする。

【0011】

【課題を解決するための手段】本発明の半導体装置の配線接続孔の形成方法による第1の発明は、半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物の濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする。

【0012】第2の発明は、半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を多層に積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記多層に積層された層間絶縁層を異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする。

【0013】第3の発明は、請求項2記載の半導体装置の配線接続孔の形成方法において、前記半導体基板上に多層に積層された前記層間絶縁層のうち、最下層の前記層間絶縁層はノンド−プであることを特徴とする。

【0014】半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら層間絶縁層を多層に積層し、更にフォトレジストパタ−ンを形成後、前記層間絶縁層を異方性エッチングして、配線接続孔を形成し、前記配線接続孔をアンモニア過水でエッチングして、前記配線接続孔の上部が下部よりも広がった形状にしているので、簡略化した工程で前記配線接続孔の下部まで十分、金属配線材料が入りやすくなり、被覆率の良好な配線を行うことができる。また、半導体基板上に多層に積層した前記層間絶縁層のうち、最下層の前記層間絶縁層をノンド−プにすると、その上部にリン、ボロンのうち少なくとも一方を含む不純物がド−プされ、積層された前記層間絶縁層からのボロン及びリンの拡散が抑えられるため半導体基板への拡散を防止することができる。

【0015】

【発明の実施の形態】本発明によるMOSFETに配線を施すための配線接続孔の形成方法の一実施例について図を参照しながら以下に説明する。図1は、本発明のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。図2は、本発明におけるMOSFETに配線を施した断面図である。

【0016】(第1工程)Siからなる基板2上にゲ−ト絶縁層6及びポリシリコンを順次形成後、図示しないフォトレジストを塗布し、フォトリソグラフィ法により、フォトレジストパタ−ンを形成し、前記金属膜をエッチング除去し、ゲ−ト電極7を形成する。ゲ−ト電極7下部に相当する部分の半導体基板2はゲ−ト5となる。このためゲ−ト5は半導体基板2の一部となっている。その後、ゲ−ト電極7をマスクとして拡散を行い、ソ−ス3及びドレイン4を形成する。こうして、ソ−ス3、ドレイン4及びゲ−ト5を備えたMOSFET1が得られる(図1(A))。

【0017】(第2工程)次に、ゲ−ト絶縁層6及びゲ−ト電極7上にボロン及びリン不純物をド−プしながら第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を順次積層する(図1(B))。ここで、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10は、酸化シリコンからなる。この際、ボロン及びリン不純物の濃度は、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10の順に高くなっている。

【0018】(第3工程)この後、フォトレジスト11を塗布後、フォトリソ法により、フォトレジスト11のゲ−ト電極7及びソ−ス3に相当する部分の第3層間絶縁層10上にフォトレジストパタ−ン12a及び12bを形成する(図1(C))。

【0019】引き続いて、RIE(リアクティブ・イオン・エッチング)により、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10及びゲ−ト絶縁層6を異方性エッチングして、孔13a及び13bを形成する。その後、アセトン等の有機溶剤や硫酸によりフォトレジスト11を除去する(図1(D))。

【0020】(第4工程)次に、アンモニア過水(例えば、NH3 :H2 02 :H2 O=4000:50:50)でエッチングを行い、配線絶縁孔13c及び13dを形成する。この場合、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10は、ボロン及びリンの濃度が高い程、エッチング量は大きくなるので、ボロン及びリン濃度が最も低い第1層間絶縁層8ではエッチング量が小さく、濃度が最も高い第3層間絶縁層10ではエッチング量が最も大きくなる。第2層間絶縁層9のエッチング量は、第1層間絶縁層8のエッチング量と第3層間絶縁層10のエッチング量の間になる。このため、配線絶縁孔13c及び13dの幅は、第1層間絶縁層8から第3層間絶縁層10に向かって、広く開口した形状になる(図1(E))。

【0021】この後、層間絶縁層10上及び配線接続孔13c及び13dに図示しないスパッタによりAl等からなる金属層を形成した後、フォトリソグラフィ法により、配線用のフォトリソパタ−ンを形成し、前記金属層をエッチング除去して配線14をする(図2)。

【0022】このようにすると、図2に示すように配線接続孔13c、13dの幅は第3層間絶縁層10側が第1層間絶縁層8側よりも広く開口最も広がった形状であるので、配線接続孔13c、13dの内部にAl等の配線金属材料が侵入しやすくなり、配線接続孔13c、13d中での配線の被覆率が良好な配線14を行うことができる。また、RIEによる異方性エッチングを行うドライ工程からアンモニア過水を用いたウェット工程への切り替わりために必要な洗浄等の準備工程回数は1回だけとなり、工程が簡略化される。

【0023】本発明の実施例では、MOSFET1が形成された半導体基板2上に第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を形成する3層の場合について述べたが、第2層間絶縁層9、第3層間絶縁層10の形成を行わずに第1層間絶縁層8だけをけ形成し、第1層間絶縁層8に半導体基板2側から積層方向に向かってボロン及びリンを含む不純物の濃度を連続的に高くしても同様の効果が得られる。なお、2層以上の層間絶縁層についても広く適用されことはいうまでもない。また、第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10にボロンとリンを同時にド−プしたが、ボロンとリンのどちらか一方の不純物をド−プするようにしても同様の効果が得られる。更に、半導体基板2上に第1層間絶縁層8、第2層間絶縁層9、第3層間絶縁層10を形成する3層の場合において、第1層間絶縁層8に不純物をド−プせず、ノンド−プにすると、半導体プロセスにおける熱処理工程で第2層間絶縁層9、第3層間絶縁層10にド−プしたボロン及びリンの半導体基板2への拡散が抑えられので、MOSFET1のしきい値電流の上昇やリ−ク電流の発生を防止できる。

【0024】

【発明の効果】本発明の半導体装置の配線接続孔の形成方法によれば、半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層し、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成し、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成後、前記フォトレジストを除去し、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にできるので、簡略化された工程で、かつ前記配線接続孔の下部まで十分、金属配線材料が入りやすくなり、被覆率の良好な配線を行うことができる。また、半導体基板上に多層に積層した前記層間絶縁層のうち、最下層の前記層間絶縁層をノンド−プにすると、その上部にリン、ボロンのうち少なくとも一方を含む不純物がド−プされ、積層された前記層間絶縁層からのボロン及びリンの拡散が抑えられるため半導体基板への拡散を防止することができる。

【図面の簡単な説明】

【図1】本発明におけるMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【図2】本発明におけるMOSFETに配線を施した断面図である。

【図3】従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【図4】従来のMOSFETに配線を施した断面図である。

【図5】従来のMOSFETに配線を施すための配線接続孔の形成方法の製造工程断面図である。

【符号の説明】

1…MOSFET、2…半導体基板、3…ソ−ス、4…ドレイン、5…ゲ−ト6…ゲ−ト絶縁層、7…ゲ−ト電極、8…第1層間絶縁層、9…第2層間絶縁層、10…第3層間絶縁層、11…フォトレジスト、12a、12b…フォトレジストパタ−ン、13a、13b…孔、13c、13d…配線接続孔、14…配線

【特許請求の範囲】

【請求項1】半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物の濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする半導体装置の配線接続孔の形成方法。

【請求項2】半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を多層に積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記多層に積層された層間絶縁層を異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする半導体装置の配線接続孔の形成方法。

【請求項3】前記半導体基板上に多層に積層された前記層間絶縁層のうち、最下層の前記層間絶縁層はノンド−プであることを特徴とする請求項2記載の半導体装置の配線接続孔の形成方法。

【請求項1】半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記層間絶縁層を前記半導体素子まで異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物の濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする半導体装置の配線接続孔の形成方法。

【請求項2】半導体素子が形成された半導体基板上に積層された層間絶縁層に前記半導体素子の配線接続を行うための半導体装置の配線接続孔の形成方法において、前記半導体基板側から積層方向に向かって高濃度になるようにリン、ボロンのうち少なくとも一方を含む不純物をド−プしながら前記層間絶縁層を多層に積層する工程と、前記層間絶縁層上にフォトレジストを塗布し、フォトレジストパタ−ンを形成する工程と、前記多層に積層された層間絶縁層を異方性エッチングして、配線接続孔を形成する工程と、前記フォトレジストを除去後、前記不純物濃度が増加すると共に前記層間絶縁層のエッチング量が増加するアンモニア過水により前記配線接続孔をエッチングして、前記配線接続孔の上部が下部よりも広がった形状にする工程とからなることを特徴とする半導体装置の配線接続孔の形成方法。

【請求項3】前記半導体基板上に多層に積層された前記層間絶縁層のうち、最下層の前記層間絶縁層はノンド−プであることを特徴とする請求項2記載の半導体装置の配線接続孔の形成方法。

【図1】

【図2】

【図4】

【図3】

【図5】

【図2】

【図4】

【図3】

【図5】

【公開番号】特開平10−284599

【公開日】平成10年(1998)10月23日

【国際特許分類】

【出願番号】特願平9−97987

【出願日】平成9年(1997)3月31日

【出願人】(000004329)日本ビクター株式会社 (3,896)

【公開日】平成10年(1998)10月23日

【国際特許分類】

【出願日】平成9年(1997)3月31日

【出願人】(000004329)日本ビクター株式会社 (3,896)

[ Back to top ]