半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法に関し、特に、半導体基板上に複数の配線層及びビアを積層した半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法に関する。

【背景技術】

【0002】

半導体装置のレイアウト設計では、タイミング制約を満たすようにタイミング調整を図りながらフリップフロップを含む回路の配置配線が行われている。このタイミング制約には、フリップフロップに対し供給されるデータがクロックよりどの程度前に確定すべきかを示すセットアップ制約と、フリップフロップに対し供給されるデータがクロックよりどの程度後まで保持されるべきかを示すホールド制約がある。

【0003】

このセットアップ制約とホールド制約を満たすために、半導体チップ内部全域に分配されているクロックパスと、ある特定で小規模な領域で生成されたデータパスというような回路構成が異なる経路の遅延時間を合わせる必要がある。なお、クロックパスとはフリップフロップにクロックを供給するための経路であり、データパスはフリップフロップにデータを供給するための経路である。

【0004】

一般的に遅延時間の調整は、クロックパスやデータパス上に遅延回路を挿入することで行われている。例えば、遅延回路によりタイミングを調整する従来技術として特許文献1が知られている。

【0005】

図17は、特許文献1に記載された、遅延時間を調整するための従来のバッファ回路ブロックを示している。図に示されるように、従来のバッファ回路ブロック900は、入力部901と遅延調整部902と出力部903とから構成されている。従来のバッファ回路ブロック900は、入力端子905が設けられた入力部901の入力端子容量と出力部903の負荷依存性も含む駆動能力を固定した状態で、遅延調整部902の遅延時間を所定範囲で変化させることができる構成となっている。

【0006】

例えば、入力部901を所定のサイズPMOSとNMOSからなる第1のインバータINV901で構成し、出力部903をそれぞれがk個ずつ並列に接続されてPMOSとNMOSからなる第3のインバータINV903で構成し、遅延調整部902をPMOSとNMOSの組をm組(INV921〜INV92mとする)並べて構成している。

【0007】

従って、従来のバッファ回路ブロック900の外形形状,外形寸法,入力端子905の位置,出力端子907の位置,入力部901と出力部903のレイアウトパターンを固定したままでも、遅延調整部902に並べられたINV921〜INV92mそれぞれのPMOSとNMOSをどのように接続するかにより、入力部901から出力部903までの遅延量を変化させることができると共に、出力信号の論理を入力信号の論理と同じにするか反転させるかも設定できるようになっている。

【0008】

図18は、特許文献1に記載された従来のバッファ回路ブロックを用いたタイミング調整方法を示している。

【0009】

図18に示されるように、従来のタイミング調整方法では、まず、図17で示した、ブロックの外形形状,寸法、入/出力端子の位置、入力端子容量、出力部の負荷依存性も含めた駆動能力等が同じで遅延値のみが異なる複数のバッファ回路ブロックで構成された遅延調整ブロック群を回路ライブラリに登録する(S910)。この回路ライブラリを用いて、クロックネットを構成する各クロック経路の中に所定の信号遅延値を有する第1のバッファ回路を選択して挿入し、LSIの第1の回路接続情報を作成し(S920)、回路ライブラリ及び第1の回路接続情報に基づいて配置配線を行い第1のレイアウト情報を作成する(S930)。

【0010】

次に、第1のレイアウト情報から抽出されたパラメータを含む所定の情報を用いてLSIの実配線遅延シミュレーションを行い(S940)、実配線遅延シミュレーションで得られたシミュレーション結果からクロックネットを含む各経路の信号遅延値情報を抽出する(S950)。そして、抽出された各経路の信号遅延値を所定の規格値と比較すると共にクロックネットのスキューを所定の第1の規格値と比較しタイミングエラーの有無を判定し(S960)、タイミングエラーが検出された場合は、配置配線の変更を施して第2の回路接続情報及び第2のレイアウト情報を作成する(S970)。

【0011】

少なくともクロックネットのスキューが第1の規格値以下になるまで、このS970と,S940と,S950と,S960とを繰り返し、全てのタイミングエラーが解消された時点で、このときの実配線遅延シミュレーションの結果から抽出されたクロックネットを構成する各クロック経路の信号遅延値が、所定の第1のクロック経路の信号遅延値に対して、その差が所定の第2の規格値を超えている第2のクロック経路を全て抽出し(S980)、全ての第2のクロック経路ついて、当該第2のクロック経路の信号遅延値と第1のクロック経路の信号遅延値との差が第2の規格値以下になるような信号遅延値を有する第2のバッファ回路を選択して当該第2のクロック経路中の第1のバッファ回路と置き換えて第3のレイアウト情報を作成し(S990)、最終レイアウト情報を作成する(S999)。これにより、図17のバッファ回路ブロックを用いてタイミング調整を実施しタイミングエラーを収束させることができる。

【0012】

なお、特許文献2には、ホールドエラーに係るデータの伝送経路に、制御信号によって電源供給及び遅延量が制御される可変遅延バッファ回路を挿入し、タイミング検証の結果に基づく要求遅延量及び動作モードに応じて可変遅延バッファ回路に供給する制御信号を決定することでタイミング調整を行うことが記載されている。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2001−332693号公報

【特許文献2】特開2010−152718号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

上記従来技術であるタイミング調整方法では、タイミングエラーやスキューエラーがあった場合に、ブロックの外形形状、寸法、入/出力端子位置、入力端子容量、出力部の負荷依存性も含めた駆動能力等が同じで遅延値のみが異なるバッファを複数準備して、バッファ置き換えを行うことでタイミングを調整している。

【0015】

しかしながら、本願発明者は、遅延回路を挿入してタイミングを調整する従来技術では、半導体装置の動作条件(水準)の違いにより生じる遅延時間のバラツキが考慮されていないことを見出した。

【0016】

したがって、従来技術では、半導体装置の動作条件(水準)の違いにより遅延時間にバラツキが発生した場合など様々な条件において、タイミング制約を満たすように適切に遅延時間を調整することが困難であるという問題があった。

【課題を解決するための手段】

【0017】

本発明に係る半導体装置の配線構造セルは、半導体基板上に複数の配線層及びビアを積層して構成された半導体装置の配線構造セルであって、前記複数の配線層の中間層に、平面形状が第1プロセス基準値を満たす四辺からなる矩形に形成された第1配線と、前記中間層に前記第1配線の四辺から前記第1プロセス基準値を満たすよう離間し、平面形状が口字型に形成された第2配線と、前記第1配線の上に前記第1配線に接して、平面形状が第2プロセス基準値を満たす四辺からなる矩形に形成された第1ビアと、前記中間層の上層に前記第1ビアに接して、平面形状が前記第1プロセス基準値を満たす幅で前記第1配線の中心線に沿って伸長した矩形に形成された第3配線と、前記第1配線の下に前記第1配線に接して、前記第1ビアと同じ平面形状に形成された第2ビアと、前記中間層の下層に前記第2ビアに接して、前記第3配線と同じ平面形状に形成された第4配線と、を有し、前記第2配線の対抗して延在する第1及び第2の配線部の第1及び第2の中心線間を前記配線構造セルのセルピッチとし、前記第3配線及び前記第4配線の伸長方向の両端は、前記第1及び第2の中心線から前記口字型の内側へ前記第1プロセス基準値の半分を満たす第1及び第2の位置に形成されているものである。

【0018】

本発明に係る半導体装置のレイアウト設計タイミング調整方法は、上記の配線構造セルを配置する半導体装置のレイアウト設計タイミング調整方法であって、クロック及びデータを入力する複数のフリップフロップを配置し、前記複数のフリップフロップに到達するクロックの遅延時間を同じにするクロックツリーを構成し、前記クロックツリーの遅延時間に基づき、当該クロックツリーに接続される前記フリップフロップに対するデータパスの遅延時間を算出し、前記算出したデータパスの遅延時間に基づき、前記第2配線をGND電位に接続し、前記第1配線と前記第2配線との間の発生する寄生容量を容量素子とし、前記第1ビア及び第2ビアを抵抗素子とする前記配線構造セルを、当該データパス上に配置し、前記フリップフロップのタイミングを検証するものである。

【0019】

本発明では、上記配線構造セルの寄生容量及び寄生抵抗により遅延時間を複数設定できるため、複数の動作条件においてもタイミング制約を満たすように調整することができる。

【発明の効果】

【0020】

本発明によれば、複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することが可能な半導体装置の配線構造セル及び半導体装置のレイアウト設計タイミング調整方法を提供することができる。

【図面の簡単な説明】

【0021】

【図1A】本発明の実施の形態1に係る配線構造セルの構成を示す平面図である。

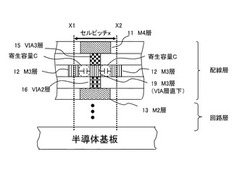

【図1B】本発明の実施の形態1に係る配線構造セルの構成を示す断面図である。

【図1C】本発明の実施の形態1に係る配線構造セルの構成を示す等価回路図である。

【図2A】本発明の実施の形態1に係る配線構造セルの接続構成を示す平面図である。

【図2B】本発明の実施の形態1に係る配線構造セルの接続構成を示す断面図である。

【図2C】本発明の実施の形態1に係る配線構造セルの接続構成を示す等価回路図である。

【図3A】本発明の実施の形態1に係る配線構造セルの接続構成を示す平面図である。

【図3B】本発明の実施の形態1に係る配線構造セルの接続構成を示す断面図である。

【図3C】本発明の実施の形態1に係る配線構造セルの接続構成を示す等価回路図である。

【図4】本発明の実施の形態1に係る自動レイアウトシステムの構成を示す構成図である。

【図5】本発明の実施の形態1に係る自動レイアウトシステムの機能構成を示すブロック図である。

【図6】本発明の実施の形態1に係る自動レイアウトシステムで用いる水準表を示す図である。

【図7】本発明の実施の形態1に係るタイミング調整方法を示すフローチャートである。

【図8】本発明の実施の形態1に係るタイミング調整方法を比較して説明するためのレイアウトイメージ図である。

【図9】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図10】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図11】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図12A】本発明の実施の形態2に係る配線構造セルの構成を示す平面図である。

【図12B】本発明の実施の形態2に係る配線構造セルの構成を示す断面図である。

【図12C】本発明の実施の形態2に係る配線構造セルの構成を示す等価回路図である。

【図13】本発明の実施の形態2に係るタイミング調整方法を示すフローチャートである。

【図14】本発明の実施の形態2に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図15】本発明の実施の形態2に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図16A】本発明の実施の形態3に係る配線構造セルの構成を示す平面図である。

【図16B】本発明の実施の形態3に係る配線構造セルの構成を示す断面図である。

【図16C】本発明の実施の形態3に係る配線構造セルの構成を示す等価回路図である。

【図17】従来のバッファ回路ブロックの構成を示す回路ブロック図である。

【図18】従来のタイミング調整方法を示すフローチャートである。

【発明を実施するための形態】

【0022】

(本発明の実施の形態1)

以下、図面を参照して本発明の実施の形態1について説明する。本実施形態では、抵抗及び容量を調整可能な配線構造セルHSCを用いてレイアウトを行い、タイミングの調整を図る。

【0023】

まず、この配線構造セルHSCについて説明する。図1A〜図1Cは、本発明の実施の形態1に係る配線構造セルHSCの構造を示している。この配線構造セルHSCは、同一面積内で寄生抵抗と寄生容量が調整可能である。

【0024】

図1A〜図1Cにおいて、半導体基板から積層方向に数えた場合のメタル配線層をM1層、M2層、M3層、M4層とした場合の例を示している。M2層〜M4層は、回路が自動配置される回路層よりも上位の配線層に形成されている。

【0025】

図1Aは、配線構造セルHSCのレイアウト平面図、図1Bは、図1Aの点線A−B断面図、図1Cは、配線構造セルHSCの等価回路を示している。さらに、図1A(1)は、全レイアウト層を平面表示し、図1A(2)は、M4層を平面表示し、図1A(3)は、M3層を平面表示し、図1A(4)は、M2層を平面表示している。

【0026】

配線構造セルHSCでは、図1Bに示すように、図1A(4)のM2層13の上にVIA2層16が形成され、その上に図1A(3)のM3層19及びM3層12が形成され、その上に図1A(2)のVIA3層15が形成され、その上に図1A(2)のM4層11が形成されている。M2層13、M3層19、M3層12、M4層11は、メタル配線で形成されている。M3層12とM4層11とはVIA3層15(第1ビア)により接続され、M2層13とM3層12とはVIA2層16(第2ビア)により接続されている。

【0027】

図1Aに示すように、M3層(中間層)には、VIA3層15とVIA2層16との間にM3層19(第1配線)が形成されている。M3層19は、平面形状がプロセス基準を満たすような矩形に形成されている。

【0028】

ここで、プロセス基準(プロセスルール)とは、半導体装置を半導体基板上に積層して形成する際の基本となる値を規定したものであり、メタル配線やVIAを形成可能な最小単位である。ここでは、図1A(2)の基準値c、図1A(3)の基準値a、基準値bがプロセス基準であり、例えば、基準値a、b、cは全て同じ値であるが、半導体プロセスによっては異なる値とすることも可能である。なお、矩形のVIA3層15及びVIA2層16のプロセス基準は、基準値a,b,cよりも小さい。

【0029】

つまり、M3層19の平面形状は、各四辺を基準値bの長さとする矩形である。M3層19が形成される基準値bは、VIA3層15及びVIA2層16の基準値よりも大きい囲みプロセス基準でもある。したがって、M3層19は、図1Aでは、VIA3層15及びVIA2層16と同じ大きさとなっているが、実際には、VIA3層15及びVIA2層16よりも大きく、VIA3層15及びVIA2層16を囲むように形成されている。

【0030】

さらに、M3層には、M3層19から基準値aのプロセス基準分離れた位置に、M3層19の周囲を囲むようにリング状のM3層12(第2配線)が形成されている。M3層12は、M3層19の各辺から基準値a離れて形成され、平面形状が所定幅の4つの直線部を接続した略口字型となっている。例えば、M3層12の直線部の幅は、プロセス基準(基準値a)の幅である。言い換えると、M3層12は、矩形のメタル配線であり、その中央に、M3層19から基準値a離れた大きさの開口部を有しているともいえる。

【0031】

ここでは、M3層12の対抗する2つの直線部の中心線の間が、配線構造セルHSCの大きさであるセルピッチとなる。すなわち、M3層12において、Y方向に延びる2直線部の中心線X1とX2の間が、X方向のピッチであるセルピッチxである。また、M3層12において、X方向に延びる2直線部の中心線Y1とY2の間が、Y方向のピッチであるセルピッチyである。

【0032】

M4層には、平面形状をX方向に所定幅で延びた長方形とするM4層11(第3配線)が形成されている。M4層11は、M3層19のX方向に延びる辺(矩形に対し相対するどちらか一方の辺)に対して平行に、つまり、M3層19の中心線に沿って伸張形成されている。M4層11のY方向の幅が、基準値cのプロセス基準を満たす大きさである。M4層11が形成される基準値cは、VIA3層15及びVIA2層16の基準値よりも大きい囲みプロセス基準でもある。

【0033】

例えば、セルピッチx方向の伸長とした場合、セルピッチxに対しプロセス基準値(例えば基準値b)の半分の距離までM4層11が形成されている。すなわち、M4層11は、M3層12の2直線部の中心線であるX1の近傍からX2の近傍まで延在しており、X1とM4層11のX1側端部との間隔は基準値bの半分の距離であり、X2とM4層11のX2側端部との間隔も基準値bの半分の距離である。

【0034】

後述するように、複数の配線構造セルHSCを隣接配置した場合に、隣接するM4層11間の間隔がプロセス基準(基準値b)となり、必要に応じてM4層11間にプロセス基準のメタル配線が形成されて、M4層11間が接続されることになる。

【0035】

また、M2層には、M4層と同一形状となるM2層13(第4配線)が形成される。すなわち、M2層には、M4層と同様に、平面形状をX方向に所定幅で延びた長方形とするM2層13が形成されている。

【0036】

なお、ここでは、図中M2層、M4層矩形の伸長方向である長辺方向をセルピッチx、短辺方向をセルピッチyとしている。

【0037】

また、リング状のM3層12と中心部のM3層19の間には寄生容量Cが両サイドに形成され、VIA3層15とVIA2層16は抵抗体となる。すなわち、M3層19とM3層12との間には、シリコンや酸化膜などが形成されて寄生容量が生じ、VIA3層15及びVIA2層16は、メタル等で形成されて寄生抵抗が生じている。

【0038】

したがって、配線構造セルHSCの等価回路は、図1Cに示すような寄生容量と寄生抵抗で構成される。M2層13の一端を端子Taとし、上層で重なっているM4層11の逆側の端子を端子Tbとし、M2層13の配線抵抗をM2r、M4層11の配線抵抗をM4r、VIA3層15とVIA2層16の抵抗をVIArとすると、端子Taと端子Tbの間に、M2層寄生抵抗M2r、VIA2層寄生抵抗VIAr、VIA3層寄生抵抗VIAr、M4層寄生抵抗M4rが直列に接続された構成となる。さらに、VIA2層寄生抵抗VIArとVIA3層寄生抵抗VIArとの接続点に2つの寄生容量Cが接続された構成となる。

【0039】

そうすると、リング状のM3層12をGNDに接続した場合、端子Taから端子Tbへの配線に次の式1の抵抗・容量(RC)が付加される。

M2r+2VIAr+M4r+2C (ここでVIAr>>M2r、M4rとなる)・・・(式1)

【0040】

本実施形態では、図1A〜図1Cに示した配線構造セルHSCを基本構造として、M3層12をGND電位に接続し、M2層13とM4層11に信号線を接続し、セルピッチx、yで複数個並べた状態でレイアウト設計しタイミング調整を行う。

【0041】

次に、配線構造セルHSCを複数配置し接続する構成例を説明する。図2A〜図2Cは、配線構造セルHSCをセル配置ピッチ(セルピッチx)に合わせて、配線構造セルHSC1〜5の順に5セルを隣接配置し、さらに、M2層とM4層に配線構造セルHSC間を接続する配線を追加した例である。図2Aはレイアウト平面図、図2Bは図2Aの点線A−B断面図、図2Cは等価回路である。なお、追加配置されるM2層32及びM4層31は、回路が自動配置される回路層よりも上位の上位階層配線である。

【0042】

図2A、図2Bに示すように、M2層32が、配線構造セルHSC1の配線構造セルHSC2側と反対側の端(端子Taとする)、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC4と配線構造セルHSC5の間において、M2層13を接続するように、追加配置されている。なお、M2層32とM3層12との間に寄生容量Cが生じる。

【0043】

また、M4層31が、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC5の配線構造セルHSC4側と反対側の端(端子Tbとする)において、M4層11を接続するように、追加配置されている。なお、M4層31とM3層12との間に寄生容量Cが生じる。

【0044】

そうすると、図2A及び図2Bの等価回路は、図2Cに示すように、配線構造セルHSCの各要素を全て直列接続した構成となり、等価回路の抵抗、容量値は次の式2に示すようになる。なお、各寄生抵抗、寄生容量は図1Cと同様である。

5M2r+10VIAr+5M4r+16C=5(M2r+2VIAr+M4r+2C)+6C ・・・(式2)

このように、図2A〜図2Cの配線構造セルにおける容量・抵抗値は、図1A〜図1Cの基本配線構造セルの(式1)と比較して約5倍となる。

【0045】

図3A〜図3Cは、図2A〜図2Cと同様に配線構造セルHSCを5セル(HSC1〜5)隣接配置し、M2層32、M4層31を全ての配線構造セルHSC間に配置した例である。図3Aはレイアウト平面図、図3Bは、図3Aの点線A−B断面図、図3Cは等価回路である。

【0046】

図3Aに示すように、M2層32が、配線構造セルHSC1の配線構造セルHSC2側と反対側の端(端子Taとする)、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC4と配線構造セルHSC5の間において、M2層13を接続するように、追加配置されている。なお、M2層32とM3層12との間に寄生容量Cが生じる。

【0047】

また、M4層31が、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC4と配線構造セルHSC5の間、配線構造セルHSC5の配線構造セルHSC4側と反対側の端(端子Tbとする)において、M4層11を接続するように追加配置されている。なお、M4層31とM3層12との間に寄生容量Cが生じる。

【0048】

そうすると、図3A及び図3Bの等価回路は、図3Cに示すように、配線構造セルHSCの各要素を直列接続するとともに並列接続した構成となり、抵抗値・容量値は次の式3に示すようになる。なお、各寄生抵抗、寄生容量は図1Cと同様である。

M2r+(2VIAr÷5)+M4r+20C ・・・(式3)

このように、図3A〜図3Cの配線構造セルにおける容量・抵抗値を、図2A〜図2Cの配線構造セルの(式2)と比較すると、抵抗値を削減し、容量値を増加した構成となっている。

【0049】

ここで、上記式2、式3の算出例を説明する。算出に用いた各パラメータの1例は次の通りである。

配線抵抗(M2r,M4r):0.5Ω

VIA抵抗(VIAr):5Ω

寄生容量(C):0.2fF/箇所

配線幅:0.5um、配線長:VIA−VIA間距離:1um

【0050】

図2A〜図2Cの配線構造セルにおける寄生抵抗・容量算出結果は、上記式2より次のようになる。

5M2r+10VIAr+5M4r+16C=5(M2r+2VIAr+M4r+2C)+6C

R1=56(直列抵抗成分10×0.5Ω+10×5Ω)=55Ω

C1=0.2×16=3.2fF=16C

【0051】

また、図3A〜図3Cの配線構造セルにおける寄生抵抗・容量算出結果は、上記式3より次のようになる。

M2r+(2VIAr÷5)+M4r+20C R2=2(直列抵抗成分2×0.5Ω)+2(並列抵抗成分 10Ω/5並列)=3Ω

C1=0.2×20=4.0fF=20C

このように、図2A〜図2C、図3A〜図3Cのように、配線構造セルを複数配列してM2層32、M4層31の配置箇所を変更することで、同一面積内で抵抗値3〜55Ω、容量値3.2〜4.0fFの範囲で可変することが可能である。これにより、抵抗値と容量値の変動範囲内で遅延合わせに必要な時定数(RC)を複数選択することができる。なお、M2層32とM4層31の数を任意に選択することで、さらに複数の時定数を選択することが可能である。例えば、M2層32とM4層31をそれぞれ4個としてもよい。

【0052】

また、図2A〜図2C、図3A〜図3Cにおいて、平面図のM3層12をGND電位で信号配線周囲に配置することで、自動レイアウトツールで引かれる信号配線が近づけないため隣接配線の影響を受けにくく、配線セル同士の寄生容量値を均一にすることができ、複数のデータパスに適用しても同様の遅延調整が容易に実現できる。

【0053】

次に、上記配線構造セルHSCをレイアウトしタイミング調整を行う自動レイアウトシステムについて説明する。図4は、本発明の実施の形態1に係る自動レイアウトシステムの構成図である。図4に示すように、自動レイアウトシステム100は、コンピュータ装置110とサーバ114と記録媒体115とネットワーク116とで構成される。

【0054】

記録媒体115は、実行プログラムの提供に供されるサーバ114に保持されている。サーバ114は、インターネットなどのネットワーク116を介してエンジニアリングワークステーションなどのコンピュータ装置110に接続される。

【0055】

記録媒体115に格納されている実行プログラムは、ネットワーク116を介してコンピュータ装置110にダウンロードされる。ダウンロードされたプログラムは、コンピュータ装置110のローカルなハードディスク或はメモリなどにストアされて実行処理を行う構成になっている。記録媒体115に格納されている実行プログラムは、図7に後述する処理を行うものであり、コンピュータ装置110で、各々シリアルに処理を行う構成になっている。

【0056】

図5は、本発明の実施の形態1に係る自動レイアウトシステムの機能ブロック図である。この自動レイアウトシステム100は、主に図4のコンピュータ装置110においプログラムが実行されることで実現されている。

【0057】

図5に示すように、この自動レイアウトシステム100は、制御部200と記憶部210を備えている。例えば、制御部200は、コンピュータ装置110におけるCPU等の制御装置からなり、記憶部210は、コンピュータ装置110のメモリやハードディスク等の記憶装置からなる。

【0058】

そして、記憶部210に、サーバ114からダウンロードされた実行プログラムが格納されており、制御部200がプログラムを実行することで、各ブロックが実現される。

【0059】

記憶部210には、レイアウトデータ212及びライブラリ213を含む自動レイアウト設計タイミング調整入力情報211が格納されている。なお、記憶部210には、自動レイアウトシステム100、制御部200の処理に必要な各種データが記憶されている。

【0060】

レイアウトデータ212は、半導体装置のレイアウト面における配置配線データであり、配置されるセル・回路の位置、セル・回路間を接続する配線の位置等が含まれている。

【0061】

ライブラリ213は、ゲート遅延情報やセルに関する情報が含まれている。セルに関する情報として、各セルの構造、特性、サイズ、端子位置等が記述されている。ライブラリ212には、特に、本発明の配線構造セルHSCの情報が含まれている。例えば、ライブラリ212は、サーバ114からダウンロードされて格納される。

【0062】

制御部200は、クロックTREE構成部201、データパス時定数算出部202、配線構造セル配置配線部203、タイミング検証部204を備えている。なお、制御部200には、その他、回路を自動配置する自動配置配線部(自動レイアウトツール)など、自動レイアウトに必要な構成が含まれている。

【0063】

クロックTREE構成部201は、クロックの入力から複数のフリップフロップまでの接続経路であるクロックTREEを構成する。データパス時定数算出部202は、データの入力から複数のフリップフロップまでの接続経路であるデータパスについて時定数を算出する。

【0064】

配線構造セル配置配線部203は、データパスの時定数が所定水準を満たすように、データパスに配線構造セルHSCを配置配線する。

【0065】

ここで、水準とは、温度や電源電圧が異なる半導体装置の動作条件であり、高速で動作可能な水準と低速で動作可能な水準が規定される。図6は、本発明で用いる水準の水準表を示している。図6に示すように、この例では、水準1を電圧高(1.1V)、トランジスタの閾値小、温度低(−40度)とし、水準2を電圧中(1.0V)、トランジスタの閾値中、温度中(25度)とし、水準3を電圧低(0.9V)、トランジスタの閾値高、温度高(110度)としている。水準1は、半導体装置が最も高速に動作可能な条件であり、水準3は、半導体装置が最も低速に動作可能な条件である。これらの水準において、必要な時定数を満たすように配線構造セルHSCを配置する。最も動作条件の良い水準1の場合と、最も動作条件の悪い水準3の場合とで、タイミング制約を満たすことができれば、中間の水準である水準2の場合でも、タイミング制約を満たすことになるため、以下では、水準1と水準3を考慮した例について説明するが、水準2やその他の水準を考慮してタイミング調整を行ってもよい。

【0066】

タイミング検証部204は、配線構造セルHSCが配置配線されたレイアウトについて、タイミング制約を満たすかどうかタイミング検証を行う。

【0067】

次に、自動レイアウトシステム100の動作について説明する。まず、図7を用いて、自動レイアウトシステム100により実行される自動レイアウト設計処理(タイミング調整処理)の流れを説明する。

【0068】

図7に示すように、自動レイアウトシステム100において、自動レイアウト設計処理(タイミング調整処理)が開始されると、クロックTREE構成部201は、レイアウトデータ212及びライブラリ213を含む自動レイアウト設計タイミング調整入力情報211を入力情報として、タイミング調整が必要な複数のフリップフロップに到達するまでのクロックパス遅延時間が同じになるようなクロックTREE構造を構成する(ステップS10)。

【0069】

次に、データパス時定数算出部202は、確定させたクロック信号遅延に合わせ込むデータパスの遅延時間を実現する時定数を算出する(ステップS20)。すなわち、クロックTREEとデータパスの遅延時間を合わせるため、構築したクロックTREEの遅延時間に基づいて、異なる水準でもデータパスの遅延時間を満たすために必要となる時定数を算出する。例えば、クロックTREEの配線の時定数とデータパスの配線の時定数を同じにすれば、クロックTREEとデータパスの遅延時間を合わせることができる。また、クロックTREEのインバータとデータパスのインバータの駆動能力を考慮してもよい。一般にデータパスのインバータは駆動能力が低いため、データパスの時定数も同じ比率で低くすることで、さらに遅延時間を合わせることができる。

【0070】

次に、配線構造セル配置配線部203は、必要な時定数を満たすために本発明の配線構造セルHSCをデータパスに必要な個数をアレイ配置し、上位階層で必要な箇所に配線を追加したレイアウトを構成する(ステップS30)。すなわち、図2A〜図2C,図3A〜図3Cで示したように、配線構造セルHSCの配列数、追加配線の配置箇所により、抵抗値及び容量値を調整し、各水準のデータパスに必要となる時定数を実現するように、配線構造セルHSCを配置配線する。

【0071】

次に、一旦各パス遅延時間検証(タイミング検証)を実施し、タイミング的に問題ないかを判定する(ステップS40)。タイミング検証において問題があった場合は、データパス遅延時間を遅らせるか早めるかの判断をタイミング検証結果レポートを元に行い、その遅延時間を実現する時定数を実現する配線セルに変更して再度タイミング検証を実施し、タイミング検証で問題がなくなるまで繰り返して、タイミング調整が完了したレイアウトデータ212とライブラリ213を自動レイアウト設計タイミング調整出力情報211に出力して完了する

【0072】

一般的には1度目のタイミング検証にてデータパスの時定数と遅延時間の関係が把握でき、必要であれば補正係数を考慮することができ、2回目以降は微調整で対応できるためタイミング調整回数は2〜3回程度で収束することが可能である。

【0073】

ここで、本発明の動作を詳細に理解するため、従来技術を用いてクロックパスとデータパスのタイミング調整を行った参考例と、本発明を用いてクロックパスとデータパスのタイミング調整を行った場合の具体例とを説明する。

【0074】

図8は、従来技術を用いてクロックパスとデータパスのタイミングを調整した参考例のレイアウトイメージを示している。

【0075】

図8に示すように、フリップフロップ40のクロックCKに対し、クロックCK1を供給するクロックパス(クロックTREE)53が構築され、フリップフロップ40のデータDに対し、データD1を供給するデータパス63が構築される。クロックパス53では、インバータとして4個のクロックパス用インバータINV51がクロックパス配線52により接続されており、データパス63では、インバータとして4個のデータパス用インバータINV61がデータパス配線62により接続されている。

【0076】

タイミング制約を満たすためクロックパス53とデータパス63の遅延時間を合わせる必要がある。例えば、図6の水準1の条件ではクロックパス遅延時間を300ps、データパス遅延時間を300psに合わせる必要があり、この場合、ゲート段数の合わせこみとデータパス用インバータINV61の駆動能力を調整することで、遅延時間を合わせることができる。

【0077】

しかし、図6の水準3では最も低速な動作条件となり動作時間にばらつきが生じるため、遅延時間が大きくずれる。この例では、クロックパスの遅延時間が450psであり、データパスの遅延時間が350psであるため、データパスの遅延時間を450psに合わせる必要が生じる。この水準ばらつきによる遅延変動は、ゲート遅延変動分と配線部遅延変動の総和で決まるものである。このため、図8の従来技術のようにゲート段数を合わせても配線分遅延変動分を吸収することができない。

【0078】

また、低い周波数帯(10KHz〜100MHz)においては、クロックに対するフリップフロップのセットアップとホールドの推移可能範囲(以降WINDOW幅と記す)はある程度ゲート段数追加や冗長素子追加などで対応できていた。しかし、近年動作周波数は向上してきており、高周波帯(500MHz〜1GHz)においては、従来のようにゲート段数での調整方法では、調整単位が大きくなるため遅延時間の調整が難しくなってきている。

【0079】

そこで、本発明では、上述の配線構造セルHSCを用いることで、近年の高周波製品において、上述したWINDOW幅を満たすようなタイミング調整を可能にする。

【0080】

図9は、図7で説明した本発明の実施の形態1の自動レイアウト設計処理によりクロックパスとデータパスのタイミングを配線構造セルHSCにより調整したレイアウトイメージを示している。

【0081】

図9は、図8と同様、フリップフロップ40のクロックCKとデータDの入力に対し、クロックCK1とデータD1がクロックパス用インバータINV51、データパス用インバータINV61を4個経由して接続された例であり、図7の流れに沿って動作を説明する。

【0082】

ステップS10におけるクロックTREE構造の構成では、具体的に、図9のフリップフロップ40のクロックCKへのクロックパス(クロックTREE)53を構成する。複数のフリップフロップへのクロック信号遅延を合わせる時定数を求め、クロックパス53では、クロックCK1のクロックパス用インバータINV51への最初の入力からフリップフロップ40のクロックCKへ到達するまで、4段のクロックパス用インバータINV51をクロックパス配線52により接続する。

【0083】

次に、ステップS20におけるデータパスの時定数の算出では、具体的に、ステップS10で求めたクロックパス配線52から算出した時定数に基づき、クロックパスとデータパスの遅延時間を合わせるため、データパス配線62に必要な時定数を求める。最も高速な水準1と最も低速な水準3とで、クロックパスとデータパスの遅延時間が合うような時定数を求める。クロックパス53の時定数は、水準1で300ps、水準3で450psの遅延となる時定数であり、データパス63の時定数も、同様に、水準1で300ps、水準3で450psの遅延となる時定数とする。このとき、クロックパス配線の時定数をデータパス配線の時定数とし、さらに、クロックパス用インバータINVとデータパス用インバータINVの駆動能力の比に応じた時定数をデータパス配線の時定数とする。

【0084】

次に、ステップS30における配線構造セルHSCの配置配線では、具体的に、クロックパスで定まる時定数は水準1で300ps、水準3で450psの遅延となる時定数であり、これに合わせて、データパスの時定数が水準1で300ps、水準3で450psの遅延となる時定数になるよう、データパス配線67に配線構造セルHSCの配列数、接続箇所を決定し配置配線する。上記、図2A〜図2C、図3A〜図3Cの算出例で説明したように、配線構造セルHSCの配列数、接続箇所により、抵抗値及び容量値を複数選択できるため、ステップS20で算出した時定数となるように配線構造セルの配置・接続構成を決定する。

【0085】

このようにして、本発明の配線構造セルHSCを配置し水準を考慮してタイミングを調整することができる。

【0086】

さらに、図10及び図11を用いて、本発明の配線構造セルHSCを自動レイアウト素子配置イメージに配置した状態(レイアウト平面)の具体例について説明する。図10及び図11における各符号は、図9に対応している。

【0087】

図10及び図11では、2つのデータパス用インバータINV61の間を、回路層よりも上位の配線層のダミー配線セル66(配線構造セルHSC)により接続する。データパス用インバータINV61の間に複数のダミー配線セル66(配線構造セルHSC)を配置し、ダミー配線セル66間を配線セル間追加配線65(M2層32、M4層31)により接続する。なお、この配線構造セルHSCの配置と接続については、図2A〜図2Cや図3A〜図3Cと同様である。図1A〜図1C、図2A〜図2C、図3A〜図3Cでは、配線構造セルHSCをX方向に配置接続する例を説明したが、M2層、M4層をY方向に配線して図10のようにY方向に配置接続することも可能である。

【0088】

図10では、データパス用インバータINV61aとデータパス用インバータINV61b、データパス用インバータINV61bとデータパス用インバータINV61cの間がY方向に4セルのセルピッチ分離れている。なお、ここでは、自動レイアウトセル配置位置8の幅が、セルピッチとなっている。

【0089】

データパス用インバータINV61aとデータパス用インバータINV61bは、Y方向に並ぶ4つのダミー配線セル66を介して接続され、さらに、データパス用インバータINV61bとデータパス用インバータINV61cも、Y方向に並ぶ4つのダミー配線セル66を介して折り返し接続されている。データパス用インバータINV61aとデータパス用インバータINV61bを接続するダミー配線セル66の層と、データパス用インバータINV61bとデータパス用インバータINV61cを接続するダミー配線セル66の層とは、同じ配線層であり、自動配置セル7の上位層に形成されている。

【0090】

また、図11では、データパス用インバータINV61aとデータパス用インバータINV61b、データパス用インバータINV61bとデータパス用インバータINV61cの間がY方向に2セルのセルピッチ分離れている。

【0091】

データパス用インバータINV61aとデータパス用インバータINV61bは、X方向に並ぶ4つのダミー配線セル66を介して接続され、さらに、データパス用インバータINV61bとデータパス用インバータINV61cも、X方向に並ぶ4つのダミー配線セル66を介して接続されている。この場合も、データパス用インバータINV61aとデータパス用インバータINV61bを接続するダミー配線セル66の層と、データパス用インバータINV61bとデータパス用インバータINV61cを接続するダミー配線セル66の層とは、同じ配線層であり、自動配置セル7の上位層に形成されている。

【0092】

なお、図11では、データパス用インバータINV61aから、X方向に4つのダミー配線セル66を経由し、さらに、Y方向に1つのダミー配線セル66を跨いで、データパス用インバータINV61bに接続される。さらに、データパス用インバータINV61bから、X方向に4つのダミー配線セル66を経由し、さらに、Y方向に1つのダミー配線セル66を跨いで、データパス用インバータINV61cに接続される。Y方向に1つのダミー配線セル66を跨いで接続するため、ダミー配線セル66のさらに上層に配線を形成し、この上層配線により接続する。図11では、4つのダミー配線セル66と4つのダミー配線セル66とを隣接して配置するため、レイアウト面積が小さいが、寄生容量成分が大きくなる可能性がある。例えば、寄生容量の影響を低く抑える必要がある場合、図10のレイアウトを採用し、レイアウト面積を小さくする必要がある場合、図11のレイアウトを採用する。

【0093】

図10及び図11のように、自動レイアウト設計により自動配置セル7に部品セルが配置され、この自動配置セル7よりも上の層に、本発明の配線構造セルHSCを配置する。これにより、配線構造セルの下層の領域に部品セルを配置できる領域として有効利用することができ、面積を増加させることなく、水準ばらつきを考慮したタイミング調整を実現できる。

【0094】

また、同じ遅延調整が必要な箇所に対しては、従来技術ではフラット階層でのレイアウト設計で数十箇所に対して全ての箇所に同じレイアウト修正を行っていたが、図1A〜図1Cに示す配線構造セルHSCをセル化して配置することでセルの差し替えにて一括修正対応可能なため、自動レイアウト設計において大幅な工数削減を実現できる。

【0095】

以上のように本実施形態では、図1A〜図1Cの配線構造セルHSCを用いて、図2A〜図2C、図3A〜図3Cのように配置配線することで、同一面積内で抵抗値、容量値を可変に設定することができる。このため、クロックパスとデータパスの遅延時間を合わせる際に、複数の水準に必要となる時定数を満たすように、配線構造セルHSCを配置配線し、複数の水準でもタイミング制約を満たすようにタイミングを調整することができる。

【0096】

したがって、自動レイアウト設計での水準ばらつき時の遅延調整を冗長素子配置なしで面積最小化かつ短TAT(Turn Around Time)で容易に実現が可能となる。

【0097】

(本発明の実施の形態2)

以下、図面を参照して本発明の実施の形態2について説明する。実施の形態1の配線構造セルは図1A〜図1Cに示す基本の配線構造セルHSCを複数アレイし、接続配線をその後追加した処理であったが、本実施形態では、予め複数の配線構造セルと接続配線を組み合わせた配線構造セル群HSCAを設けておき、レイアウト設計では配線構造セル群を入れ替える処理のみとした点が異なる。

【0098】

図12A〜図12Cは、本発明の実施の形態2に係る配線構造セル群HSCAの構成を示している。この配線構造セル群HSCAは、図2A〜図2Cと同じM2層〜M3層〜M4層の3層構造をセル化した配線構造であり、M4層31(最上位層)とM2層32(最下位層)のパターンを変更することにより、同一面積内で寄生抵抗と寄生容量の調整が実現できる構造である。図12A〜図12Cの配線構造セルの構成は、図2A〜図2Cと同様であり、セル階層が異なるだけあるため、説明を省略する。なお、実施の形態1と同様にM2層32、M4層31の数は任意に可能である。

【0099】

図12A〜図12Cの基本となる配線構造セル群において、M3層12をGND電位に接続し、M2層13とM4層11に信号線を接続した配線セルを本発明の実施の形態に係るレイアウト設計に適用する。

【0100】

図13は、本発明の実施の形態2に係る配線構造セル群を用いてタイミング調整を行うフローチャートである。実施の形態1との違いは、ステップS31において、指定された時定数を実現するダミー配線セル群(配線構造セル群)を配置する。具体的には、図9で示したようなクロックパス配線52から算出した時定数にデータパス配線62で決まる時定数を合わせ込むための配線構造セル群HSCAをデータパス配線62の箇所に配置するレイアウト構成となる。

【0101】

図14及び図15は、図12A〜図12Cの配線構造セル群HSCAを配置した状態を示している。実施の形態1では、図10及び図11のように、複数のダミー配線セル66によりタイミング調整を行った。

【0102】

本実施形態では、図14に示すように、図11でY方向に複数配置されたダミー配線セル66に代えて、縦置きのダミー配線セル群τを配置する。このダミー配線セル群τは、予め4つの配線構造セルをY方向に接続した状態のセルである。時定数の異なるダミー配線セル群τ1、τ2、τ3を用意しておき、ダミー配線セル群τを差し替えることでタイミング調整を行う。

【0103】

また、本実施形態では、図15に示すように、図12でX方向に複数配置されたダミー配線セル66に代えて、横置きのダミー配線セル群τを配置する。このダミー配線セル群τは、予め4つの配線構造セルをX方向に接続した状態のセルである。時定数の異なるダミー配線セル群τ1、τ2、τ3を用意しておき、ダミー配線セル群τを差し替えることでタイミング調整を行う。

【0104】

本実施形態のタイミング調整方法は図13に示すように時定数の変更方法が実施の形態1と異なっているが、タイミング調整回数削減効果、レイアウト設計工数削減効果、面積削減効果は実施の形態1と同様である。

【0105】

本実施形態では、実施の形態1の配線構造セルアレイ配置および上位階層配線によるタイミング調整とは異なり、図12A〜図12Cの配線構造セル群の差し替えでタイミング調整を実現する。これにより、複数の水準に必要となる時定数を満たすように、配線構造セル群HSCAを配置配線することで、複数の水準でもタイミング制約を満たすようにタイミングを調整することができる。複数の配線構造セルを含む配線構造セル群HSCAごとに配置できるため、抵抗・容量を一括で変更でき、設計工数をさらに削減することができる。

【0106】

(本発明の実施の形態3)

以下、図面を参照して本発明の実施の形態3について説明する。実施の形態1、2の配線構造セルは3層構造であったが、本実施の形態では、配線構造セルを4層構造とし、同一面積で更に大きな抵抗値と寄生容量値を調整可能とした点が異なる。

【0107】

図16A〜図16Cは、本発明の実施の形態3に係る配線構造セルHSCの構造を示している。図16A(1)は、全レイアウト層を平面表示し、図16A(2)は、M5層を平面表示し、図16A(3)は、M4層を平面表示し、図16A(4)は、M3層を平面表示し、図16A(5)は、M2層を平面表示している。

【0108】

図16A〜図16Cに示すように、この配線構造セルHSCは、M2層〜M3層〜M4層〜M5層の4層構造である。配線構造セルHSCでは、図16Bに示すように、図16A(5)のM2層13の上にVIA2層16が形成され、その上に図16A(4)のM3層19及びM3層12が形成され、その上に図16A(4)のVIA3層15が形成され、その上に図16A(3)のM4層20及びM4層11が形成され、その上に図16A(2)のVIA4層14が形成され、その上に図16A(2)のM5層18が形成されている。

【0109】

M4層11とM3層12で示す中間層をGND電位にすることで、図16Cの等価回路となり、端子Taから端子Tbへの配線に次の式4の抵抗・容量が付加される。

M2r+3VIAr+M4r+4C (ここでVIAr>>M2r、M4rとなる)・・・(式4)

このように、図16A〜図16Cの4層構造の配線構造セルでは、図1A〜図1Cの3層構造よりも同一面積内でより大きい寄生容量及び寄生抵抗値の制御が実現でき、効果として遅延変動量を増やすことが可能である。なお、その他、タイミング調整方法等については、実施の形態1と同様の動作であるため省略する。

【0110】

実施の形態1では中間層をM3層の1層とし、本実施の形態では中間層をM3層、M4層の2層としたが、中間層をさらに増やすことで、同一面積内での抵抗値・容量値の設定範囲をさらに増加することが出来、より様々な条件における時定数に対応してタイミングを調整することができる。

【0111】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0112】

11 M4層

12 M3層

13 M2層

14 VIA4層

15 VIA3層

16 VIA2層

18 M5層

19 M3層(VIA層直下)

20 M4層(VIA層直下)

31 M4層(上位階層配線)

32 M2層(上位階層配線)

40 フリップフロップ

52 クロックパス配線

53 クロックパス

62 データパス配線

63 データパス

65 配線セル間追加配線

66 ダミー配線セル

67 データパス配線

7 自動配置セル

8 自動レイアウトセル配置位置

100 自動レイアウトシステム

110 コンピュータ装置

114 サーバ

115 記録媒体

116 ネットワーク

200 制御部

201 クロックTREE構成部

202 データパス時定数算出部

203 配線構造セル配置配線部

204 タイミング検証部

210 記憶部

211 自動レイアウト設計タイミング調整入力情報

212 レイアウトデータ

213 ライブラリ

HSC(HSC1〜5) 配線構造セル

HSCA 配線構造セル群

INV51 クロックパス用インバータ

INV61 データパス用インバータ

【技術分野】

【0001】

本発明は、半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法に関し、特に、半導体基板上に複数の配線層及びビアを積層した半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法に関する。

【背景技術】

【0002】

半導体装置のレイアウト設計では、タイミング制約を満たすようにタイミング調整を図りながらフリップフロップを含む回路の配置配線が行われている。このタイミング制約には、フリップフロップに対し供給されるデータがクロックよりどの程度前に確定すべきかを示すセットアップ制約と、フリップフロップに対し供給されるデータがクロックよりどの程度後まで保持されるべきかを示すホールド制約がある。

【0003】

このセットアップ制約とホールド制約を満たすために、半導体チップ内部全域に分配されているクロックパスと、ある特定で小規模な領域で生成されたデータパスというような回路構成が異なる経路の遅延時間を合わせる必要がある。なお、クロックパスとはフリップフロップにクロックを供給するための経路であり、データパスはフリップフロップにデータを供給するための経路である。

【0004】

一般的に遅延時間の調整は、クロックパスやデータパス上に遅延回路を挿入することで行われている。例えば、遅延回路によりタイミングを調整する従来技術として特許文献1が知られている。

【0005】

図17は、特許文献1に記載された、遅延時間を調整するための従来のバッファ回路ブロックを示している。図に示されるように、従来のバッファ回路ブロック900は、入力部901と遅延調整部902と出力部903とから構成されている。従来のバッファ回路ブロック900は、入力端子905が設けられた入力部901の入力端子容量と出力部903の負荷依存性も含む駆動能力を固定した状態で、遅延調整部902の遅延時間を所定範囲で変化させることができる構成となっている。

【0006】

例えば、入力部901を所定のサイズPMOSとNMOSからなる第1のインバータINV901で構成し、出力部903をそれぞれがk個ずつ並列に接続されてPMOSとNMOSからなる第3のインバータINV903で構成し、遅延調整部902をPMOSとNMOSの組をm組(INV921〜INV92mとする)並べて構成している。

【0007】

従って、従来のバッファ回路ブロック900の外形形状,外形寸法,入力端子905の位置,出力端子907の位置,入力部901と出力部903のレイアウトパターンを固定したままでも、遅延調整部902に並べられたINV921〜INV92mそれぞれのPMOSとNMOSをどのように接続するかにより、入力部901から出力部903までの遅延量を変化させることができると共に、出力信号の論理を入力信号の論理と同じにするか反転させるかも設定できるようになっている。

【0008】

図18は、特許文献1に記載された従来のバッファ回路ブロックを用いたタイミング調整方法を示している。

【0009】

図18に示されるように、従来のタイミング調整方法では、まず、図17で示した、ブロックの外形形状,寸法、入/出力端子の位置、入力端子容量、出力部の負荷依存性も含めた駆動能力等が同じで遅延値のみが異なる複数のバッファ回路ブロックで構成された遅延調整ブロック群を回路ライブラリに登録する(S910)。この回路ライブラリを用いて、クロックネットを構成する各クロック経路の中に所定の信号遅延値を有する第1のバッファ回路を選択して挿入し、LSIの第1の回路接続情報を作成し(S920)、回路ライブラリ及び第1の回路接続情報に基づいて配置配線を行い第1のレイアウト情報を作成する(S930)。

【0010】

次に、第1のレイアウト情報から抽出されたパラメータを含む所定の情報を用いてLSIの実配線遅延シミュレーションを行い(S940)、実配線遅延シミュレーションで得られたシミュレーション結果からクロックネットを含む各経路の信号遅延値情報を抽出する(S950)。そして、抽出された各経路の信号遅延値を所定の規格値と比較すると共にクロックネットのスキューを所定の第1の規格値と比較しタイミングエラーの有無を判定し(S960)、タイミングエラーが検出された場合は、配置配線の変更を施して第2の回路接続情報及び第2のレイアウト情報を作成する(S970)。

【0011】

少なくともクロックネットのスキューが第1の規格値以下になるまで、このS970と,S940と,S950と,S960とを繰り返し、全てのタイミングエラーが解消された時点で、このときの実配線遅延シミュレーションの結果から抽出されたクロックネットを構成する各クロック経路の信号遅延値が、所定の第1のクロック経路の信号遅延値に対して、その差が所定の第2の規格値を超えている第2のクロック経路を全て抽出し(S980)、全ての第2のクロック経路ついて、当該第2のクロック経路の信号遅延値と第1のクロック経路の信号遅延値との差が第2の規格値以下になるような信号遅延値を有する第2のバッファ回路を選択して当該第2のクロック経路中の第1のバッファ回路と置き換えて第3のレイアウト情報を作成し(S990)、最終レイアウト情報を作成する(S999)。これにより、図17のバッファ回路ブロックを用いてタイミング調整を実施しタイミングエラーを収束させることができる。

【0012】

なお、特許文献2には、ホールドエラーに係るデータの伝送経路に、制御信号によって電源供給及び遅延量が制御される可変遅延バッファ回路を挿入し、タイミング検証の結果に基づく要求遅延量及び動作モードに応じて可変遅延バッファ回路に供給する制御信号を決定することでタイミング調整を行うことが記載されている。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2001−332693号公報

【特許文献2】特開2010−152718号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

上記従来技術であるタイミング調整方法では、タイミングエラーやスキューエラーがあった場合に、ブロックの外形形状、寸法、入/出力端子位置、入力端子容量、出力部の負荷依存性も含めた駆動能力等が同じで遅延値のみが異なるバッファを複数準備して、バッファ置き換えを行うことでタイミングを調整している。

【0015】

しかしながら、本願発明者は、遅延回路を挿入してタイミングを調整する従来技術では、半導体装置の動作条件(水準)の違いにより生じる遅延時間のバラツキが考慮されていないことを見出した。

【0016】

したがって、従来技術では、半導体装置の動作条件(水準)の違いにより遅延時間にバラツキが発生した場合など様々な条件において、タイミング制約を満たすように適切に遅延時間を調整することが困難であるという問題があった。

【課題を解決するための手段】

【0017】

本発明に係る半導体装置の配線構造セルは、半導体基板上に複数の配線層及びビアを積層して構成された半導体装置の配線構造セルであって、前記複数の配線層の中間層に、平面形状が第1プロセス基準値を満たす四辺からなる矩形に形成された第1配線と、前記中間層に前記第1配線の四辺から前記第1プロセス基準値を満たすよう離間し、平面形状が口字型に形成された第2配線と、前記第1配線の上に前記第1配線に接して、平面形状が第2プロセス基準値を満たす四辺からなる矩形に形成された第1ビアと、前記中間層の上層に前記第1ビアに接して、平面形状が前記第1プロセス基準値を満たす幅で前記第1配線の中心線に沿って伸長した矩形に形成された第3配線と、前記第1配線の下に前記第1配線に接して、前記第1ビアと同じ平面形状に形成された第2ビアと、前記中間層の下層に前記第2ビアに接して、前記第3配線と同じ平面形状に形成された第4配線と、を有し、前記第2配線の対抗して延在する第1及び第2の配線部の第1及び第2の中心線間を前記配線構造セルのセルピッチとし、前記第3配線及び前記第4配線の伸長方向の両端は、前記第1及び第2の中心線から前記口字型の内側へ前記第1プロセス基準値の半分を満たす第1及び第2の位置に形成されているものである。

【0018】

本発明に係る半導体装置のレイアウト設計タイミング調整方法は、上記の配線構造セルを配置する半導体装置のレイアウト設計タイミング調整方法であって、クロック及びデータを入力する複数のフリップフロップを配置し、前記複数のフリップフロップに到達するクロックの遅延時間を同じにするクロックツリーを構成し、前記クロックツリーの遅延時間に基づき、当該クロックツリーに接続される前記フリップフロップに対するデータパスの遅延時間を算出し、前記算出したデータパスの遅延時間に基づき、前記第2配線をGND電位に接続し、前記第1配線と前記第2配線との間の発生する寄生容量を容量素子とし、前記第1ビア及び第2ビアを抵抗素子とする前記配線構造セルを、当該データパス上に配置し、前記フリップフロップのタイミングを検証するものである。

【0019】

本発明では、上記配線構造セルの寄生容量及び寄生抵抗により遅延時間を複数設定できるため、複数の動作条件においてもタイミング制約を満たすように調整することができる。

【発明の効果】

【0020】

本発明によれば、複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することが可能な半導体装置の配線構造セル及び半導体装置のレイアウト設計タイミング調整方法を提供することができる。

【図面の簡単な説明】

【0021】

【図1A】本発明の実施の形態1に係る配線構造セルの構成を示す平面図である。

【図1B】本発明の実施の形態1に係る配線構造セルの構成を示す断面図である。

【図1C】本発明の実施の形態1に係る配線構造セルの構成を示す等価回路図である。

【図2A】本発明の実施の形態1に係る配線構造セルの接続構成を示す平面図である。

【図2B】本発明の実施の形態1に係る配線構造セルの接続構成を示す断面図である。

【図2C】本発明の実施の形態1に係る配線構造セルの接続構成を示す等価回路図である。

【図3A】本発明の実施の形態1に係る配線構造セルの接続構成を示す平面図である。

【図3B】本発明の実施の形態1に係る配線構造セルの接続構成を示す断面図である。

【図3C】本発明の実施の形態1に係る配線構造セルの接続構成を示す等価回路図である。

【図4】本発明の実施の形態1に係る自動レイアウトシステムの構成を示す構成図である。

【図5】本発明の実施の形態1に係る自動レイアウトシステムの機能構成を示すブロック図である。

【図6】本発明の実施の形態1に係る自動レイアウトシステムで用いる水準表を示す図である。

【図7】本発明の実施の形態1に係るタイミング調整方法を示すフローチャートである。

【図8】本発明の実施の形態1に係るタイミング調整方法を比較して説明するためのレイアウトイメージ図である。

【図9】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図10】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図11】本発明の実施の形態1に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図12A】本発明の実施の形態2に係る配線構造セルの構成を示す平面図である。

【図12B】本発明の実施の形態2に係る配線構造セルの構成を示す断面図である。

【図12C】本発明の実施の形態2に係る配線構造セルの構成を示す等価回路図である。

【図13】本発明の実施の形態2に係るタイミング調整方法を示すフローチャートである。

【図14】本発明の実施の形態2に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図15】本発明の実施の形態2に係るタイミング調整方法を説明するためのレイアウトイメージ図である。

【図16A】本発明の実施の形態3に係る配線構造セルの構成を示す平面図である。

【図16B】本発明の実施の形態3に係る配線構造セルの構成を示す断面図である。

【図16C】本発明の実施の形態3に係る配線構造セルの構成を示す等価回路図である。

【図17】従来のバッファ回路ブロックの構成を示す回路ブロック図である。

【図18】従来のタイミング調整方法を示すフローチャートである。

【発明を実施するための形態】

【0022】

(本発明の実施の形態1)

以下、図面を参照して本発明の実施の形態1について説明する。本実施形態では、抵抗及び容量を調整可能な配線構造セルHSCを用いてレイアウトを行い、タイミングの調整を図る。

【0023】

まず、この配線構造セルHSCについて説明する。図1A〜図1Cは、本発明の実施の形態1に係る配線構造セルHSCの構造を示している。この配線構造セルHSCは、同一面積内で寄生抵抗と寄生容量が調整可能である。

【0024】

図1A〜図1Cにおいて、半導体基板から積層方向に数えた場合のメタル配線層をM1層、M2層、M3層、M4層とした場合の例を示している。M2層〜M4層は、回路が自動配置される回路層よりも上位の配線層に形成されている。

【0025】

図1Aは、配線構造セルHSCのレイアウト平面図、図1Bは、図1Aの点線A−B断面図、図1Cは、配線構造セルHSCの等価回路を示している。さらに、図1A(1)は、全レイアウト層を平面表示し、図1A(2)は、M4層を平面表示し、図1A(3)は、M3層を平面表示し、図1A(4)は、M2層を平面表示している。

【0026】

配線構造セルHSCでは、図1Bに示すように、図1A(4)のM2層13の上にVIA2層16が形成され、その上に図1A(3)のM3層19及びM3層12が形成され、その上に図1A(2)のVIA3層15が形成され、その上に図1A(2)のM4層11が形成されている。M2層13、M3層19、M3層12、M4層11は、メタル配線で形成されている。M3層12とM4層11とはVIA3層15(第1ビア)により接続され、M2層13とM3層12とはVIA2層16(第2ビア)により接続されている。

【0027】

図1Aに示すように、M3層(中間層)には、VIA3層15とVIA2層16との間にM3層19(第1配線)が形成されている。M3層19は、平面形状がプロセス基準を満たすような矩形に形成されている。

【0028】

ここで、プロセス基準(プロセスルール)とは、半導体装置を半導体基板上に積層して形成する際の基本となる値を規定したものであり、メタル配線やVIAを形成可能な最小単位である。ここでは、図1A(2)の基準値c、図1A(3)の基準値a、基準値bがプロセス基準であり、例えば、基準値a、b、cは全て同じ値であるが、半導体プロセスによっては異なる値とすることも可能である。なお、矩形のVIA3層15及びVIA2層16のプロセス基準は、基準値a,b,cよりも小さい。

【0029】

つまり、M3層19の平面形状は、各四辺を基準値bの長さとする矩形である。M3層19が形成される基準値bは、VIA3層15及びVIA2層16の基準値よりも大きい囲みプロセス基準でもある。したがって、M3層19は、図1Aでは、VIA3層15及びVIA2層16と同じ大きさとなっているが、実際には、VIA3層15及びVIA2層16よりも大きく、VIA3層15及びVIA2層16を囲むように形成されている。

【0030】

さらに、M3層には、M3層19から基準値aのプロセス基準分離れた位置に、M3層19の周囲を囲むようにリング状のM3層12(第2配線)が形成されている。M3層12は、M3層19の各辺から基準値a離れて形成され、平面形状が所定幅の4つの直線部を接続した略口字型となっている。例えば、M3層12の直線部の幅は、プロセス基準(基準値a)の幅である。言い換えると、M3層12は、矩形のメタル配線であり、その中央に、M3層19から基準値a離れた大きさの開口部を有しているともいえる。

【0031】

ここでは、M3層12の対抗する2つの直線部の中心線の間が、配線構造セルHSCの大きさであるセルピッチとなる。すなわち、M3層12において、Y方向に延びる2直線部の中心線X1とX2の間が、X方向のピッチであるセルピッチxである。また、M3層12において、X方向に延びる2直線部の中心線Y1とY2の間が、Y方向のピッチであるセルピッチyである。

【0032】

M4層には、平面形状をX方向に所定幅で延びた長方形とするM4層11(第3配線)が形成されている。M4層11は、M3層19のX方向に延びる辺(矩形に対し相対するどちらか一方の辺)に対して平行に、つまり、M3層19の中心線に沿って伸張形成されている。M4層11のY方向の幅が、基準値cのプロセス基準を満たす大きさである。M4層11が形成される基準値cは、VIA3層15及びVIA2層16の基準値よりも大きい囲みプロセス基準でもある。

【0033】

例えば、セルピッチx方向の伸長とした場合、セルピッチxに対しプロセス基準値(例えば基準値b)の半分の距離までM4層11が形成されている。すなわち、M4層11は、M3層12の2直線部の中心線であるX1の近傍からX2の近傍まで延在しており、X1とM4層11のX1側端部との間隔は基準値bの半分の距離であり、X2とM4層11のX2側端部との間隔も基準値bの半分の距離である。

【0034】

後述するように、複数の配線構造セルHSCを隣接配置した場合に、隣接するM4層11間の間隔がプロセス基準(基準値b)となり、必要に応じてM4層11間にプロセス基準のメタル配線が形成されて、M4層11間が接続されることになる。

【0035】

また、M2層には、M4層と同一形状となるM2層13(第4配線)が形成される。すなわち、M2層には、M4層と同様に、平面形状をX方向に所定幅で延びた長方形とするM2層13が形成されている。

【0036】

なお、ここでは、図中M2層、M4層矩形の伸長方向である長辺方向をセルピッチx、短辺方向をセルピッチyとしている。

【0037】

また、リング状のM3層12と中心部のM3層19の間には寄生容量Cが両サイドに形成され、VIA3層15とVIA2層16は抵抗体となる。すなわち、M3層19とM3層12との間には、シリコンや酸化膜などが形成されて寄生容量が生じ、VIA3層15及びVIA2層16は、メタル等で形成されて寄生抵抗が生じている。

【0038】

したがって、配線構造セルHSCの等価回路は、図1Cに示すような寄生容量と寄生抵抗で構成される。M2層13の一端を端子Taとし、上層で重なっているM4層11の逆側の端子を端子Tbとし、M2層13の配線抵抗をM2r、M4層11の配線抵抗をM4r、VIA3層15とVIA2層16の抵抗をVIArとすると、端子Taと端子Tbの間に、M2層寄生抵抗M2r、VIA2層寄生抵抗VIAr、VIA3層寄生抵抗VIAr、M4層寄生抵抗M4rが直列に接続された構成となる。さらに、VIA2層寄生抵抗VIArとVIA3層寄生抵抗VIArとの接続点に2つの寄生容量Cが接続された構成となる。

【0039】

そうすると、リング状のM3層12をGNDに接続した場合、端子Taから端子Tbへの配線に次の式1の抵抗・容量(RC)が付加される。

M2r+2VIAr+M4r+2C (ここでVIAr>>M2r、M4rとなる)・・・(式1)

【0040】

本実施形態では、図1A〜図1Cに示した配線構造セルHSCを基本構造として、M3層12をGND電位に接続し、M2層13とM4層11に信号線を接続し、セルピッチx、yで複数個並べた状態でレイアウト設計しタイミング調整を行う。

【0041】

次に、配線構造セルHSCを複数配置し接続する構成例を説明する。図2A〜図2Cは、配線構造セルHSCをセル配置ピッチ(セルピッチx)に合わせて、配線構造セルHSC1〜5の順に5セルを隣接配置し、さらに、M2層とM4層に配線構造セルHSC間を接続する配線を追加した例である。図2Aはレイアウト平面図、図2Bは図2Aの点線A−B断面図、図2Cは等価回路である。なお、追加配置されるM2層32及びM4層31は、回路が自動配置される回路層よりも上位の上位階層配線である。

【0042】

図2A、図2Bに示すように、M2層32が、配線構造セルHSC1の配線構造セルHSC2側と反対側の端(端子Taとする)、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC4と配線構造セルHSC5の間において、M2層13を接続するように、追加配置されている。なお、M2層32とM3層12との間に寄生容量Cが生じる。

【0043】

また、M4層31が、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC5の配線構造セルHSC4側と反対側の端(端子Tbとする)において、M4層11を接続するように、追加配置されている。なお、M4層31とM3層12との間に寄生容量Cが生じる。

【0044】

そうすると、図2A及び図2Bの等価回路は、図2Cに示すように、配線構造セルHSCの各要素を全て直列接続した構成となり、等価回路の抵抗、容量値は次の式2に示すようになる。なお、各寄生抵抗、寄生容量は図1Cと同様である。

5M2r+10VIAr+5M4r+16C=5(M2r+2VIAr+M4r+2C)+6C ・・・(式2)

このように、図2A〜図2Cの配線構造セルにおける容量・抵抗値は、図1A〜図1Cの基本配線構造セルの(式1)と比較して約5倍となる。

【0045】

図3A〜図3Cは、図2A〜図2Cと同様に配線構造セルHSCを5セル(HSC1〜5)隣接配置し、M2層32、M4層31を全ての配線構造セルHSC間に配置した例である。図3Aはレイアウト平面図、図3Bは、図3Aの点線A−B断面図、図3Cは等価回路である。

【0046】

図3Aに示すように、M2層32が、配線構造セルHSC1の配線構造セルHSC2側と反対側の端(端子Taとする)、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC4と配線構造セルHSC5の間において、M2層13を接続するように、追加配置されている。なお、M2層32とM3層12との間に寄生容量Cが生じる。

【0047】

また、M4層31が、配線構造セルHSC1と配線構造セルHSC2の間、配線構造セルHSC2と配線構造セルHSC3の間、配線構造セルHSC3と配線構造セルHSC4の間、配線構造セルHSC4と配線構造セルHSC5の間、配線構造セルHSC5の配線構造セルHSC4側と反対側の端(端子Tbとする)において、M4層11を接続するように追加配置されている。なお、M4層31とM3層12との間に寄生容量Cが生じる。

【0048】

そうすると、図3A及び図3Bの等価回路は、図3Cに示すように、配線構造セルHSCの各要素を直列接続するとともに並列接続した構成となり、抵抗値・容量値は次の式3に示すようになる。なお、各寄生抵抗、寄生容量は図1Cと同様である。

M2r+(2VIAr÷5)+M4r+20C ・・・(式3)

このように、図3A〜図3Cの配線構造セルにおける容量・抵抗値を、図2A〜図2Cの配線構造セルの(式2)と比較すると、抵抗値を削減し、容量値を増加した構成となっている。

【0049】

ここで、上記式2、式3の算出例を説明する。算出に用いた各パラメータの1例は次の通りである。

配線抵抗(M2r,M4r):0.5Ω

VIA抵抗(VIAr):5Ω

寄生容量(C):0.2fF/箇所

配線幅:0.5um、配線長:VIA−VIA間距離:1um

【0050】

図2A〜図2Cの配線構造セルにおける寄生抵抗・容量算出結果は、上記式2より次のようになる。

5M2r+10VIAr+5M4r+16C=5(M2r+2VIAr+M4r+2C)+6C

R1=56(直列抵抗成分10×0.5Ω+10×5Ω)=55Ω

C1=0.2×16=3.2fF=16C

【0051】

また、図3A〜図3Cの配線構造セルにおける寄生抵抗・容量算出結果は、上記式3より次のようになる。

M2r+(2VIAr÷5)+M4r+20C R2=2(直列抵抗成分2×0.5Ω)+2(並列抵抗成分 10Ω/5並列)=3Ω

C1=0.2×20=4.0fF=20C

このように、図2A〜図2C、図3A〜図3Cのように、配線構造セルを複数配列してM2層32、M4層31の配置箇所を変更することで、同一面積内で抵抗値3〜55Ω、容量値3.2〜4.0fFの範囲で可変することが可能である。これにより、抵抗値と容量値の変動範囲内で遅延合わせに必要な時定数(RC)を複数選択することができる。なお、M2層32とM4層31の数を任意に選択することで、さらに複数の時定数を選択することが可能である。例えば、M2層32とM4層31をそれぞれ4個としてもよい。

【0052】

また、図2A〜図2C、図3A〜図3Cにおいて、平面図のM3層12をGND電位で信号配線周囲に配置することで、自動レイアウトツールで引かれる信号配線が近づけないため隣接配線の影響を受けにくく、配線セル同士の寄生容量値を均一にすることができ、複数のデータパスに適用しても同様の遅延調整が容易に実現できる。

【0053】

次に、上記配線構造セルHSCをレイアウトしタイミング調整を行う自動レイアウトシステムについて説明する。図4は、本発明の実施の形態1に係る自動レイアウトシステムの構成図である。図4に示すように、自動レイアウトシステム100は、コンピュータ装置110とサーバ114と記録媒体115とネットワーク116とで構成される。

【0054】

記録媒体115は、実行プログラムの提供に供されるサーバ114に保持されている。サーバ114は、インターネットなどのネットワーク116を介してエンジニアリングワークステーションなどのコンピュータ装置110に接続される。

【0055】

記録媒体115に格納されている実行プログラムは、ネットワーク116を介してコンピュータ装置110にダウンロードされる。ダウンロードされたプログラムは、コンピュータ装置110のローカルなハードディスク或はメモリなどにストアされて実行処理を行う構成になっている。記録媒体115に格納されている実行プログラムは、図7に後述する処理を行うものであり、コンピュータ装置110で、各々シリアルに処理を行う構成になっている。

【0056】

図5は、本発明の実施の形態1に係る自動レイアウトシステムの機能ブロック図である。この自動レイアウトシステム100は、主に図4のコンピュータ装置110においプログラムが実行されることで実現されている。

【0057】

図5に示すように、この自動レイアウトシステム100は、制御部200と記憶部210を備えている。例えば、制御部200は、コンピュータ装置110におけるCPU等の制御装置からなり、記憶部210は、コンピュータ装置110のメモリやハードディスク等の記憶装置からなる。

【0058】

そして、記憶部210に、サーバ114からダウンロードされた実行プログラムが格納されており、制御部200がプログラムを実行することで、各ブロックが実現される。

【0059】

記憶部210には、レイアウトデータ212及びライブラリ213を含む自動レイアウト設計タイミング調整入力情報211が格納されている。なお、記憶部210には、自動レイアウトシステム100、制御部200の処理に必要な各種データが記憶されている。

【0060】

レイアウトデータ212は、半導体装置のレイアウト面における配置配線データであり、配置されるセル・回路の位置、セル・回路間を接続する配線の位置等が含まれている。

【0061】

ライブラリ213は、ゲート遅延情報やセルに関する情報が含まれている。セルに関する情報として、各セルの構造、特性、サイズ、端子位置等が記述されている。ライブラリ212には、特に、本発明の配線構造セルHSCの情報が含まれている。例えば、ライブラリ212は、サーバ114からダウンロードされて格納される。

【0062】

制御部200は、クロックTREE構成部201、データパス時定数算出部202、配線構造セル配置配線部203、タイミング検証部204を備えている。なお、制御部200には、その他、回路を自動配置する自動配置配線部(自動レイアウトツール)など、自動レイアウトに必要な構成が含まれている。

【0063】

クロックTREE構成部201は、クロックの入力から複数のフリップフロップまでの接続経路であるクロックTREEを構成する。データパス時定数算出部202は、データの入力から複数のフリップフロップまでの接続経路であるデータパスについて時定数を算出する。

【0064】

配線構造セル配置配線部203は、データパスの時定数が所定水準を満たすように、データパスに配線構造セルHSCを配置配線する。

【0065】

ここで、水準とは、温度や電源電圧が異なる半導体装置の動作条件であり、高速で動作可能な水準と低速で動作可能な水準が規定される。図6は、本発明で用いる水準の水準表を示している。図6に示すように、この例では、水準1を電圧高(1.1V)、トランジスタの閾値小、温度低(−40度)とし、水準2を電圧中(1.0V)、トランジスタの閾値中、温度中(25度)とし、水準3を電圧低(0.9V)、トランジスタの閾値高、温度高(110度)としている。水準1は、半導体装置が最も高速に動作可能な条件であり、水準3は、半導体装置が最も低速に動作可能な条件である。これらの水準において、必要な時定数を満たすように配線構造セルHSCを配置する。最も動作条件の良い水準1の場合と、最も動作条件の悪い水準3の場合とで、タイミング制約を満たすことができれば、中間の水準である水準2の場合でも、タイミング制約を満たすことになるため、以下では、水準1と水準3を考慮した例について説明するが、水準2やその他の水準を考慮してタイミング調整を行ってもよい。

【0066】

タイミング検証部204は、配線構造セルHSCが配置配線されたレイアウトについて、タイミング制約を満たすかどうかタイミング検証を行う。

【0067】

次に、自動レイアウトシステム100の動作について説明する。まず、図7を用いて、自動レイアウトシステム100により実行される自動レイアウト設計処理(タイミング調整処理)の流れを説明する。

【0068】

図7に示すように、自動レイアウトシステム100において、自動レイアウト設計処理(タイミング調整処理)が開始されると、クロックTREE構成部201は、レイアウトデータ212及びライブラリ213を含む自動レイアウト設計タイミング調整入力情報211を入力情報として、タイミング調整が必要な複数のフリップフロップに到達するまでのクロックパス遅延時間が同じになるようなクロックTREE構造を構成する(ステップS10)。

【0069】

次に、データパス時定数算出部202は、確定させたクロック信号遅延に合わせ込むデータパスの遅延時間を実現する時定数を算出する(ステップS20)。すなわち、クロックTREEとデータパスの遅延時間を合わせるため、構築したクロックTREEの遅延時間に基づいて、異なる水準でもデータパスの遅延時間を満たすために必要となる時定数を算出する。例えば、クロックTREEの配線の時定数とデータパスの配線の時定数を同じにすれば、クロックTREEとデータパスの遅延時間を合わせることができる。また、クロックTREEのインバータとデータパスのインバータの駆動能力を考慮してもよい。一般にデータパスのインバータは駆動能力が低いため、データパスの時定数も同じ比率で低くすることで、さらに遅延時間を合わせることができる。

【0070】

次に、配線構造セル配置配線部203は、必要な時定数を満たすために本発明の配線構造セルHSCをデータパスに必要な個数をアレイ配置し、上位階層で必要な箇所に配線を追加したレイアウトを構成する(ステップS30)。すなわち、図2A〜図2C,図3A〜図3Cで示したように、配線構造セルHSCの配列数、追加配線の配置箇所により、抵抗値及び容量値を調整し、各水準のデータパスに必要となる時定数を実現するように、配線構造セルHSCを配置配線する。

【0071】

次に、一旦各パス遅延時間検証(タイミング検証)を実施し、タイミング的に問題ないかを判定する(ステップS40)。タイミング検証において問題があった場合は、データパス遅延時間を遅らせるか早めるかの判断をタイミング検証結果レポートを元に行い、その遅延時間を実現する時定数を実現する配線セルに変更して再度タイミング検証を実施し、タイミング検証で問題がなくなるまで繰り返して、タイミング調整が完了したレイアウトデータ212とライブラリ213を自動レイアウト設計タイミング調整出力情報211に出力して完了する

【0072】

一般的には1度目のタイミング検証にてデータパスの時定数と遅延時間の関係が把握でき、必要であれば補正係数を考慮することができ、2回目以降は微調整で対応できるためタイミング調整回数は2〜3回程度で収束することが可能である。

【0073】

ここで、本発明の動作を詳細に理解するため、従来技術を用いてクロックパスとデータパスのタイミング調整を行った参考例と、本発明を用いてクロックパスとデータパスのタイミング調整を行った場合の具体例とを説明する。

【0074】

図8は、従来技術を用いてクロックパスとデータパスのタイミングを調整した参考例のレイアウトイメージを示している。

【0075】

図8に示すように、フリップフロップ40のクロックCKに対し、クロックCK1を供給するクロックパス(クロックTREE)53が構築され、フリップフロップ40のデータDに対し、データD1を供給するデータパス63が構築される。クロックパス53では、インバータとして4個のクロックパス用インバータINV51がクロックパス配線52により接続されており、データパス63では、インバータとして4個のデータパス用インバータINV61がデータパス配線62により接続されている。

【0076】

タイミング制約を満たすためクロックパス53とデータパス63の遅延時間を合わせる必要がある。例えば、図6の水準1の条件ではクロックパス遅延時間を300ps、データパス遅延時間を300psに合わせる必要があり、この場合、ゲート段数の合わせこみとデータパス用インバータINV61の駆動能力を調整することで、遅延時間を合わせることができる。

【0077】

しかし、図6の水準3では最も低速な動作条件となり動作時間にばらつきが生じるため、遅延時間が大きくずれる。この例では、クロックパスの遅延時間が450psであり、データパスの遅延時間が350psであるため、データパスの遅延時間を450psに合わせる必要が生じる。この水準ばらつきによる遅延変動は、ゲート遅延変動分と配線部遅延変動の総和で決まるものである。このため、図8の従来技術のようにゲート段数を合わせても配線分遅延変動分を吸収することができない。

【0078】

また、低い周波数帯(10KHz〜100MHz)においては、クロックに対するフリップフロップのセットアップとホールドの推移可能範囲(以降WINDOW幅と記す)はある程度ゲート段数追加や冗長素子追加などで対応できていた。しかし、近年動作周波数は向上してきており、高周波帯(500MHz〜1GHz)においては、従来のようにゲート段数での調整方法では、調整単位が大きくなるため遅延時間の調整が難しくなってきている。

【0079】

そこで、本発明では、上述の配線構造セルHSCを用いることで、近年の高周波製品において、上述したWINDOW幅を満たすようなタイミング調整を可能にする。

【0080】

図9は、図7で説明した本発明の実施の形態1の自動レイアウト設計処理によりクロックパスとデータパスのタイミングを配線構造セルHSCにより調整したレイアウトイメージを示している。

【0081】

図9は、図8と同様、フリップフロップ40のクロックCKとデータDの入力に対し、クロックCK1とデータD1がクロックパス用インバータINV51、データパス用インバータINV61を4個経由して接続された例であり、図7の流れに沿って動作を説明する。

【0082】

ステップS10におけるクロックTREE構造の構成では、具体的に、図9のフリップフロップ40のクロックCKへのクロックパス(クロックTREE)53を構成する。複数のフリップフロップへのクロック信号遅延を合わせる時定数を求め、クロックパス53では、クロックCK1のクロックパス用インバータINV51への最初の入力からフリップフロップ40のクロックCKへ到達するまで、4段のクロックパス用インバータINV51をクロックパス配線52により接続する。

【0083】

次に、ステップS20におけるデータパスの時定数の算出では、具体的に、ステップS10で求めたクロックパス配線52から算出した時定数に基づき、クロックパスとデータパスの遅延時間を合わせるため、データパス配線62に必要な時定数を求める。最も高速な水準1と最も低速な水準3とで、クロックパスとデータパスの遅延時間が合うような時定数を求める。クロックパス53の時定数は、水準1で300ps、水準3で450psの遅延となる時定数であり、データパス63の時定数も、同様に、水準1で300ps、水準3で450psの遅延となる時定数とする。このとき、クロックパス配線の時定数をデータパス配線の時定数とし、さらに、クロックパス用インバータINVとデータパス用インバータINVの駆動能力の比に応じた時定数をデータパス配線の時定数とする。

【0084】

次に、ステップS30における配線構造セルHSCの配置配線では、具体的に、クロックパスで定まる時定数は水準1で300ps、水準3で450psの遅延となる時定数であり、これに合わせて、データパスの時定数が水準1で300ps、水準3で450psの遅延となる時定数になるよう、データパス配線67に配線構造セルHSCの配列数、接続箇所を決定し配置配線する。上記、図2A〜図2C、図3A〜図3Cの算出例で説明したように、配線構造セルHSCの配列数、接続箇所により、抵抗値及び容量値を複数選択できるため、ステップS20で算出した時定数となるように配線構造セルの配置・接続構成を決定する。

【0085】

このようにして、本発明の配線構造セルHSCを配置し水準を考慮してタイミングを調整することができる。

【0086】

さらに、図10及び図11を用いて、本発明の配線構造セルHSCを自動レイアウト素子配置イメージに配置した状態(レイアウト平面)の具体例について説明する。図10及び図11における各符号は、図9に対応している。

【0087】

図10及び図11では、2つのデータパス用インバータINV61の間を、回路層よりも上位の配線層のダミー配線セル66(配線構造セルHSC)により接続する。データパス用インバータINV61の間に複数のダミー配線セル66(配線構造セルHSC)を配置し、ダミー配線セル66間を配線セル間追加配線65(M2層32、M4層31)により接続する。なお、この配線構造セルHSCの配置と接続については、図2A〜図2Cや図3A〜図3Cと同様である。図1A〜図1C、図2A〜図2C、図3A〜図3Cでは、配線構造セルHSCをX方向に配置接続する例を説明したが、M2層、M4層をY方向に配線して図10のようにY方向に配置接続することも可能である。

【0088】

図10では、データパス用インバータINV61aとデータパス用インバータINV61b、データパス用インバータINV61bとデータパス用インバータINV61cの間がY方向に4セルのセルピッチ分離れている。なお、ここでは、自動レイアウトセル配置位置8の幅が、セルピッチとなっている。

【0089】

データパス用インバータINV61aとデータパス用インバータINV61bは、Y方向に並ぶ4つのダミー配線セル66を介して接続され、さらに、データパス用インバータINV61bとデータパス用インバータINV61cも、Y方向に並ぶ4つのダミー配線セル66を介して折り返し接続されている。データパス用インバータINV61aとデータパス用インバータINV61bを接続するダミー配線セル66の層と、データパス用インバータINV61bとデータパス用インバータINV61cを接続するダミー配線セル66の層とは、同じ配線層であり、自動配置セル7の上位層に形成されている。

【0090】

また、図11では、データパス用インバータINV61aとデータパス用インバータINV61b、データパス用インバータINV61bとデータパス用インバータINV61cの間がY方向に2セルのセルピッチ分離れている。

【0091】

データパス用インバータINV61aとデータパス用インバータINV61bは、X方向に並ぶ4つのダミー配線セル66を介して接続され、さらに、データパス用インバータINV61bとデータパス用インバータINV61cも、X方向に並ぶ4つのダミー配線セル66を介して接続されている。この場合も、データパス用インバータINV61aとデータパス用インバータINV61bを接続するダミー配線セル66の層と、データパス用インバータINV61bとデータパス用インバータINV61cを接続するダミー配線セル66の層とは、同じ配線層であり、自動配置セル7の上位層に形成されている。

【0092】

なお、図11では、データパス用インバータINV61aから、X方向に4つのダミー配線セル66を経由し、さらに、Y方向に1つのダミー配線セル66を跨いで、データパス用インバータINV61bに接続される。さらに、データパス用インバータINV61bから、X方向に4つのダミー配線セル66を経由し、さらに、Y方向に1つのダミー配線セル66を跨いで、データパス用インバータINV61cに接続される。Y方向に1つのダミー配線セル66を跨いで接続するため、ダミー配線セル66のさらに上層に配線を形成し、この上層配線により接続する。図11では、4つのダミー配線セル66と4つのダミー配線セル66とを隣接して配置するため、レイアウト面積が小さいが、寄生容量成分が大きくなる可能性がある。例えば、寄生容量の影響を低く抑える必要がある場合、図10のレイアウトを採用し、レイアウト面積を小さくする必要がある場合、図11のレイアウトを採用する。

【0093】

図10及び図11のように、自動レイアウト設計により自動配置セル7に部品セルが配置され、この自動配置セル7よりも上の層に、本発明の配線構造セルHSCを配置する。これにより、配線構造セルの下層の領域に部品セルを配置できる領域として有効利用することができ、面積を増加させることなく、水準ばらつきを考慮したタイミング調整を実現できる。

【0094】

また、同じ遅延調整が必要な箇所に対しては、従来技術ではフラット階層でのレイアウト設計で数十箇所に対して全ての箇所に同じレイアウト修正を行っていたが、図1A〜図1Cに示す配線構造セルHSCをセル化して配置することでセルの差し替えにて一括修正対応可能なため、自動レイアウト設計において大幅な工数削減を実現できる。

【0095】

以上のように本実施形態では、図1A〜図1Cの配線構造セルHSCを用いて、図2A〜図2C、図3A〜図3Cのように配置配線することで、同一面積内で抵抗値、容量値を可変に設定することができる。このため、クロックパスとデータパスの遅延時間を合わせる際に、複数の水準に必要となる時定数を満たすように、配線構造セルHSCを配置配線し、複数の水準でもタイミング制約を満たすようにタイミングを調整することができる。

【0096】

したがって、自動レイアウト設計での水準ばらつき時の遅延調整を冗長素子配置なしで面積最小化かつ短TAT(Turn Around Time)で容易に実現が可能となる。

【0097】

(本発明の実施の形態2)

以下、図面を参照して本発明の実施の形態2について説明する。実施の形態1の配線構造セルは図1A〜図1Cに示す基本の配線構造セルHSCを複数アレイし、接続配線をその後追加した処理であったが、本実施形態では、予め複数の配線構造セルと接続配線を組み合わせた配線構造セル群HSCAを設けておき、レイアウト設計では配線構造セル群を入れ替える処理のみとした点が異なる。

【0098】

図12A〜図12Cは、本発明の実施の形態2に係る配線構造セル群HSCAの構成を示している。この配線構造セル群HSCAは、図2A〜図2Cと同じM2層〜M3層〜M4層の3層構造をセル化した配線構造であり、M4層31(最上位層)とM2層32(最下位層)のパターンを変更することにより、同一面積内で寄生抵抗と寄生容量の調整が実現できる構造である。図12A〜図12Cの配線構造セルの構成は、図2A〜図2Cと同様であり、セル階層が異なるだけあるため、説明を省略する。なお、実施の形態1と同様にM2層32、M4層31の数は任意に可能である。

【0099】

図12A〜図12Cの基本となる配線構造セル群において、M3層12をGND電位に接続し、M2層13とM4層11に信号線を接続した配線セルを本発明の実施の形態に係るレイアウト設計に適用する。

【0100】

図13は、本発明の実施の形態2に係る配線構造セル群を用いてタイミング調整を行うフローチャートである。実施の形態1との違いは、ステップS31において、指定された時定数を実現するダミー配線セル群(配線構造セル群)を配置する。具体的には、図9で示したようなクロックパス配線52から算出した時定数にデータパス配線62で決まる時定数を合わせ込むための配線構造セル群HSCAをデータパス配線62の箇所に配置するレイアウト構成となる。

【0101】

図14及び図15は、図12A〜図12Cの配線構造セル群HSCAを配置した状態を示している。実施の形態1では、図10及び図11のように、複数のダミー配線セル66によりタイミング調整を行った。

【0102】

本実施形態では、図14に示すように、図11でY方向に複数配置されたダミー配線セル66に代えて、縦置きのダミー配線セル群τを配置する。このダミー配線セル群τは、予め4つの配線構造セルをY方向に接続した状態のセルである。時定数の異なるダミー配線セル群τ1、τ2、τ3を用意しておき、ダミー配線セル群τを差し替えることでタイミング調整を行う。

【0103】

また、本実施形態では、図15に示すように、図12でX方向に複数配置されたダミー配線セル66に代えて、横置きのダミー配線セル群τを配置する。このダミー配線セル群τは、予め4つの配線構造セルをX方向に接続した状態のセルである。時定数の異なるダミー配線セル群τ1、τ2、τ3を用意しておき、ダミー配線セル群τを差し替えることでタイミング調整を行う。

【0104】

本実施形態のタイミング調整方法は図13に示すように時定数の変更方法が実施の形態1と異なっているが、タイミング調整回数削減効果、レイアウト設計工数削減効果、面積削減効果は実施の形態1と同様である。

【0105】

本実施形態では、実施の形態1の配線構造セルアレイ配置および上位階層配線によるタイミング調整とは異なり、図12A〜図12Cの配線構造セル群の差し替えでタイミング調整を実現する。これにより、複数の水準に必要となる時定数を満たすように、配線構造セル群HSCAを配置配線することで、複数の水準でもタイミング制約を満たすようにタイミングを調整することができる。複数の配線構造セルを含む配線構造セル群HSCAごとに配置できるため、抵抗・容量を一括で変更でき、設計工数をさらに削減することができる。

【0106】

(本発明の実施の形態3)

以下、図面を参照して本発明の実施の形態3について説明する。実施の形態1、2の配線構造セルは3層構造であったが、本実施の形態では、配線構造セルを4層構造とし、同一面積で更に大きな抵抗値と寄生容量値を調整可能とした点が異なる。

【0107】

図16A〜図16Cは、本発明の実施の形態3に係る配線構造セルHSCの構造を示している。図16A(1)は、全レイアウト層を平面表示し、図16A(2)は、M5層を平面表示し、図16A(3)は、M4層を平面表示し、図16A(4)は、M3層を平面表示し、図16A(5)は、M2層を平面表示している。

【0108】

図16A〜図16Cに示すように、この配線構造セルHSCは、M2層〜M3層〜M4層〜M5層の4層構造である。配線構造セルHSCでは、図16Bに示すように、図16A(5)のM2層13の上にVIA2層16が形成され、その上に図16A(4)のM3層19及びM3層12が形成され、その上に図16A(4)のVIA3層15が形成され、その上に図16A(3)のM4層20及びM4層11が形成され、その上に図16A(2)のVIA4層14が形成され、その上に図16A(2)のM5層18が形成されている。

【0109】

M4層11とM3層12で示す中間層をGND電位にすることで、図16Cの等価回路となり、端子Taから端子Tbへの配線に次の式4の抵抗・容量が付加される。

M2r+3VIAr+M4r+4C (ここでVIAr>>M2r、M4rとなる)・・・(式4)

このように、図16A〜図16Cの4層構造の配線構造セルでは、図1A〜図1Cの3層構造よりも同一面積内でより大きい寄生容量及び寄生抵抗値の制御が実現でき、効果として遅延変動量を増やすことが可能である。なお、その他、タイミング調整方法等については、実施の形態1と同様の動作であるため省略する。

【0110】

実施の形態1では中間層をM3層の1層とし、本実施の形態では中間層をM3層、M4層の2層としたが、中間層をさらに増やすことで、同一面積内での抵抗値・容量値の設定範囲をさらに増加することが出来、より様々な条件における時定数に対応してタイミングを調整することができる。

【0111】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0112】

11 M4層

12 M3層

13 M2層

14 VIA4層

15 VIA3層

16 VIA2層

18 M5層

19 M3層(VIA層直下)

20 M4層(VIA層直下)

31 M4層(上位階層配線)

32 M2層(上位階層配線)

40 フリップフロップ

52 クロックパス配線

53 クロックパス

62 データパス配線

63 データパス

65 配線セル間追加配線

66 ダミー配線セル

67 データパス配線

7 自動配置セル

8 自動レイアウトセル配置位置

100 自動レイアウトシステム

110 コンピュータ装置

114 サーバ

115 記録媒体

116 ネットワーク

200 制御部

201 クロックTREE構成部

202 データパス時定数算出部

203 配線構造セル配置配線部

204 タイミング検証部

210 記憶部

211 自動レイアウト設計タイミング調整入力情報

212 レイアウトデータ

213 ライブラリ

HSC(HSC1〜5) 配線構造セル

HSCA 配線構造セル群

INV51 クロックパス用インバータ

INV61 データパス用インバータ

【特許請求の範囲】

【請求項1】

半導体基板上に複数の配線層及びビアを積層して構成された半導体装置の配線構造セルであって、

前記複数の配線層の中間層に、平面形状が第1プロセス基準値を満たす四辺からなる矩形に形成された第1配線と、

前記中間層に前記第1配線の四辺から前記第1プロセス基準値を満たすよう離間し、平面形状が口字型に形成された第2配線と、

前記第1配線の上に前記第1配線に接して、平面形状が第2プロセス基準値を満たす四辺からなる矩形に形成された第1ビアと、

前記中間層の上層に前記第1ビアに接して、平面形状が前記第1プロセス基準値を満たす幅で前記第1配線の中心線に沿って伸長した矩形に形成された第3配線と、

前記第1配線の下に前記第1配線に接して、前記第1ビアと同じ平面形状に形成された第2ビアと、

前記中間層の下層に前記第2ビアに接して、前記第3配線と同じ平面形状に形成された第4配線と、を有し、

前記第2配線の対抗して延在する第1及び第2の直線部の第1及び第2の中心線間を前記配線構造セルのセルピッチとし、

前記第3配線及び前記第4配線の伸長方向の両端は、前記第1及び第2の中心線から前記口字型の内側へ前記第1プロセス基準値の半分を満たす第1及び第2の位置に形成されている、

半導体装置の配線構造セル。

【請求項2】

前記第1プロセス基準値は、前記第2プロセス基準値よりも大きく、

前記第1配線は、平面形状が前記第1ビア及び前記第2ビアを囲むように形成されている、

請求項1に記載の半導体装置の配線構造セル。

【請求項3】

複数の前記配線構造セルを前記セルピッチの間隔で配列し、

隣接する前記配線構造セル間において、前記上層で前記第3配線同士を接続するか、もしくは前記下層で前記第4配線同士を接続する接続配線を有する、

請求項1または2に記載の半導体装置の配線構造セル。

【請求項4】

請求項1乃至3のいずれか一項に記載の配線構造セルを配置する半導体装置のレイアウト設計タイミング調整方法であって、

クロック及びデータを入力する複数のフリップフロップを配置し、

前記複数のフリップフロップに到達するクロックの遅延時間を同じにするクロックツリーを構成し、

前記クロックツリーの遅延時間に基づき、当該クロックツリーに接続される前記フリップフロップに対するデータパスの遅延時間を算出し、

前記算出したデータパスの遅延時間に基づき、前記第2配線をGND電位に接続し、前記第1配線と前記第2配線との間の発生する寄生容量を容量素子とし、前記第1ビア及び第2ビアを抵抗素子とする前記配線構造セルを、当該データパス上に配置し、

前記フリップフロップのタイミングを検証する、

半導体装置のレイアウト設計タイミング調整方法

【請求項5】

前記配線構造セルのデータパス上への配置では、

前記配線構造セルを複数配置し、前記複数配置した配線構造セル間を接続する前記上層もしくは前記下層の配線を配置する、

請求項4に記載の半導体装置のレイアウト設計タイミング調整方法

【請求項1】

半導体基板上に複数の配線層及びビアを積層して構成された半導体装置の配線構造セルであって、

前記複数の配線層の中間層に、平面形状が第1プロセス基準値を満たす四辺からなる矩形に形成された第1配線と、

前記中間層に前記第1配線の四辺から前記第1プロセス基準値を満たすよう離間し、平面形状が口字型に形成された第2配線と、

前記第1配線の上に前記第1配線に接して、平面形状が第2プロセス基準値を満たす四辺からなる矩形に形成された第1ビアと、

前記中間層の上層に前記第1ビアに接して、平面形状が前記第1プロセス基準値を満たす幅で前記第1配線の中心線に沿って伸長した矩形に形成された第3配線と、

前記第1配線の下に前記第1配線に接して、前記第1ビアと同じ平面形状に形成された第2ビアと、

前記中間層の下層に前記第2ビアに接して、前記第3配線と同じ平面形状に形成された第4配線と、を有し、

前記第2配線の対抗して延在する第1及び第2の直線部の第1及び第2の中心線間を前記配線構造セルのセルピッチとし、

前記第3配線及び前記第4配線の伸長方向の両端は、前記第1及び第2の中心線から前記口字型の内側へ前記第1プロセス基準値の半分を満たす第1及び第2の位置に形成されている、

半導体装置の配線構造セル。

【請求項2】

前記第1プロセス基準値は、前記第2プロセス基準値よりも大きく、

前記第1配線は、平面形状が前記第1ビア及び前記第2ビアを囲むように形成されている、

請求項1に記載の半導体装置の配線構造セル。

【請求項3】

複数の前記配線構造セルを前記セルピッチの間隔で配列し、

隣接する前記配線構造セル間において、前記上層で前記第3配線同士を接続するか、もしくは前記下層で前記第4配線同士を接続する接続配線を有する、

請求項1または2に記載の半導体装置の配線構造セル。

【請求項4】

請求項1乃至3のいずれか一項に記載の配線構造セルを配置する半導体装置のレイアウト設計タイミング調整方法であって、

クロック及びデータを入力する複数のフリップフロップを配置し、

前記複数のフリップフロップに到達するクロックの遅延時間を同じにするクロックツリーを構成し、

前記クロックツリーの遅延時間に基づき、当該クロックツリーに接続される前記フリップフロップに対するデータパスの遅延時間を算出し、

前記算出したデータパスの遅延時間に基づき、前記第2配線をGND電位に接続し、前記第1配線と前記第2配線との間の発生する寄生容量を容量素子とし、前記第1ビア及び第2ビアを抵抗素子とする前記配線構造セルを、当該データパス上に配置し、

前記フリップフロップのタイミングを検証する、

半導体装置のレイアウト設計タイミング調整方法

【請求項5】

前記配線構造セルのデータパス上への配置では、

前記配線構造セルを複数配置し、前記複数配置した配線構造セル間を接続する前記上層もしくは前記下層の配線を配置する、

請求項4に記載の半導体装置のレイアウト設計タイミング調整方法

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図12C】

【図13】

【図14】

【図15】

【図16A】

【図16B】

【図16C】

【図17】

【図18】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図12C】

【図13】

【図14】

【図15】

【図16A】

【図16B】

【図16C】

【図17】

【図18】

【公開番号】特開2013−114305(P2013−114305A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257357(P2011−257357)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]