半導体装置を製造するプラズマ処理装置及びプラズマ処理方法

【課題】半導体装置の製造を安定して効率よく行うため、処理室内壁の堆積物の状態やプラズマ内部をリアルタイムでモニタを行い、常時管理しながら処理する方法を提供する。

【解決手段】プラズマ処理室の内壁状態やプラズマの内部状態を把握するために、プラズマ処理室の内壁にプローブ基盤219を配置し、このプローブ基盤219にパルス化したバイアス電力を掛け、コンデンサ222の電圧変化を解析することにより、処理室内壁状態とプラズマ内部状態をリアルタイムでモニタし、そのデータ値からプラズマ処理装置を制御することにより、効率の良い処理を行い、且つ処理室内のプラズマを直接管理して、安定した半導体装置の製造を行う。

【解決手段】プラズマ処理室の内壁状態やプラズマの内部状態を把握するために、プラズマ処理室の内壁にプローブ基盤219を配置し、このプローブ基盤219にパルス化したバイアス電力を掛け、コンデンサ222の電圧変化を解析することにより、処理室内壁状態とプラズマ内部状態をリアルタイムでモニタし、そのデータ値からプラズマ処理装置を制御することにより、効率の良い処理を行い、且つ処理室内のプラズマを直接管理して、安定した半導体装置の製造を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置を製造するプラズマ処理装置及びこのプラズマ処理装置を用いたプラズマ処理方法に関する。

【背景技術】

【0002】

半導体装置はイオン打ち込み、スパッタ装置、プラズマCVD装置による成膜、マスクパターンの露光現像によるレジストマスクへの転写、プラズマエッチングによる薄膜の加工、および洗浄の組み合わせにより製造される。近年半導体装置の高速化に伴い、半導体装置はより微細化となり加工による僅かなズレが無視できなくなっている。

【0003】

半導体製造の成膜装置やドライエッチング装置では、プラズマ処理を行うためウエハの処理枚数と共に、装置内壁面の状態が堆積物付着やエッチングにより変化する(経時変化)。このため、処理時間を管理して、消耗品の交換や内壁面の洗浄を行っている。

【0004】

装置の内壁面は、処理時間と共に連続的に変化しているため、初期状態(洗浄直後)と洗浄直前では、成膜装置では薄膜の膜厚、特性が僅かに異なり、ドライエッチング装置では、形状寸法や深さやマスク選択比が僅かに異なってくる。そのためプラズマ処理を行う際は、処理室内の内壁状態やプラズマ自身をモニタリングして常に同じ環境を保たなければならない。

【0005】

一方、半導体装置の微細化の進展に伴い、レジストの薄膜化に伴うエッチング時のレジスト消耗速度低減(レジスト選択比向上)、下地膜のエッチング速度低減(下地膜選択比向上)、高アスペクト比ホールへの十分なエッチャント供給などの要求から、堆積性の強いガス処理ガスが多用されることが予想される。

【0006】

しかしながら、堆積性の強い処理ガスを用いると、プラズマ処理室内には堆積物が付着する。この堆積物がプラズマ処理室内の内壁に過剰に付着すると剥離する。この堆積物が剥離した場合には、半導体装置上に付着し異物粒子として半導体製造ラインを汚染し、歩留まり低下を引き起こすことになる。

【0007】

このため、プラズマ処理室内の長期安定性の観点から、処理室内の内壁状態を常にモニタし、堆積物がプラズマ処理室内の内壁から剥離する前に全掃するタイミングを見極めることは極めて重要である。

【0008】

このような背景から、プラズマ処理装置内部の内壁状態やプラズマの状態変化を検出し、その検出結果をプラズマ処理装置に反映してウエハ処理を行い、一定の処理結果が得られるようにするなどの工夫がなされてきた。

【0009】

非特許文献1と非特許文献2では、半導体製造のプラズマ処理装置の内壁や天板にプローブ基盤を配置し、このプローブ基盤にパルス化したバイアス電力を供給することによりプローブ基盤表面の状態をモニタし制御することによりプラズマ処理室の内部を制御する方法を開示している。

【0010】

特許文献1では、半導体製造のプラズマ処理装置の内壁に平面プローブ基盤を2つ配置し、これらのプローブ基盤にパルス化した電力を供給しプラズマの内部状態を測定し制御する方法を開示している。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特表2007−502519号

【非特許文献】

【0012】

【非特許文献1】2007Dry Process International Symposium 3−03

【非特許文献2】2008Dry Process International Symposium P1−21

【発明の概要】

【発明が解決しようとする課題】

【0013】

プラズマプロセスを使用した半導体製造装置は、装置内壁面の状態が堆積物付着やパーツのエッチングにより経時的に変化する。また同様な変化として、消耗品パーツの交換や内壁面の洗浄の前後で変化が見られる。これらの変化によりプラズマエッチングにおいて所望のエッチング結果を得られなかったり、プラズマCVDにおいて膜質が変質したり均一にならない、という製品の品質低下を招くことになる。

【0014】

このような変動は、プラズマ内部の変動のため半導体製造装置に備えられた各種センサ(圧力計、流量計、高周波電力計、温度計)では正確な測定を行うことが難しく、各種センサが所望の値を示しているにもかかわらず、実際の製品は所望の結果とは異なる事がある。このような場合は、各種センサが正常なためにプロセスが正常に行われていないにもかかわらず、半導体装置の製造が継続されたりして製品の低下に繋がる。

【0015】

また、プロセスの結果より異常に気付いても、原因となるパラメータが分かないため、携わったエンジニアの経験により解決されるために装置の復旧に多大な時間を要する。

【0016】

このように、プラズマプロセスの進行に影響を与えるパラメータは、装置センサを監視するだけでは不十分であり、チャンバー内の時々刻々と変化するパラメータを制御することにより安定したプラズマプロセスを行うことが可能となる。

【0017】

非特許文献1及び非特許文献2では、プローブ基盤のデータからプラズマ内部のパラメータのモニタはできる。しかしながらこのモニタでは基盤周辺のプラズマ状態のみであり、且つプローブ基盤の材質が処理室内壁の素材と異なるため、実際の処理室の内壁状態を反映しているとは限らない。

【0018】

プローブ基盤への堆積は、基盤の材質・温度・静電容量などが処理室内壁と同等でないと堆積膜厚が異なってしまう。そのためプローブ基盤を処理室内壁と異なる状態でモニタしプラズマの制御を行うと、安定したプラズマ処理ができない。

【0019】

処理室内のプラズマ処理をモニタし再現よく安定して制御するには。プラズマ状態を乱さず装置の内壁状態と同等な測定環境が必要となる。

【0020】

特許文献1では、2つの平面プローブ基盤のデータからプラズマの内部状態のモニタとプラズマの制御はできる。しかしながら基盤の温度制御や経時変化を含む表面状態の制御を考慮していないため、測定環境が変動し安定したプラズマ処理のプロセス制御まではできない。

【0021】

本発明の目的は、半導体装置の製造を安定して効率よく行うため、処理室内壁の堆積物の状態やプラズマ内部について直接モニタを行い、常時管理をしながら処理する方法を提供することである。

【課題を解決するための手段】

【0022】

上記目的を達成するために、本発明では半導体装置を製造するプラズマ処理装置の内壁にプローブ基盤を配置する。この基盤にパルス化したバイアス電力を掛け、コンデンサの電圧変化を解析することにより、処理室内壁状態とプラズマの内部状態がリアルタイムでモニタできる、そのデータ値からプラズマ処理装置の処理方法を制御する。

【0023】

(1)本発明は、プローブ基盤直下に静電容量を調節するコンデンサに接続するスイッチを配置することにより、基盤は処理室内壁と同様な静電容量が再現される。また基盤中へヒータを内蔵することにより、基盤は処理室内壁と同様な温度の再現が得られる。よってプローブ基盤は静電容量と温度に関して処理室内壁と同等になることから適格な内壁状態のモニタを行う。

【0024】

(2)本発明は、量産時のドライクリーニングの処理方法において、処理室内壁の表面状態とプラズマ内部状態をリアルタイムでモニタすることにより処理室内のクリーニング状況が明確になり、効率の良い量産が可能となる。またプローブ基盤を高さ方向に複数配置することにより、処理室内部の高さ方向のクリーニング状況が明確になるためクリーニング条件のパラメータを適宜変更し効率の良いクリーニング処理を行う。

【0025】

(3)本発明は、全掃直後の量産に向けてのシーズニング処理方法と量産中の堆積物の影響による全掃判断において、プローブ基盤から処理室内壁の表面状態とプラズマの内部状態をリアルタイムでモニタすることにより処理室内の環境が管理されるため、安定的な半導体装置の製造を行う。

【0026】

(4)本発明は、全掃時による消耗品や交換品の組み付け状況において、シーズニングによるプラズマから直接処理室内の状態が判断できるため、容易に処理室内の環境管理を行う。

【発明の効果】

【0027】

本発明によれば、プラズマの処理中にプローブ基盤にパルス電圧を掛けることにより、コンデンサが充電と放電を繰り返し、コンデンサの放電レートよりVdc、飽和イオン電流、電子温度が算出できるため、処理室内壁の堆積物の状態やプラズマ内部をリアルタイムでモニタできる。そのため装置内の内壁状態の常時管理を行いながら処理を行うため、安定した半導体装置を製造することができる。

【図面の簡単な説明】

【0028】

【図1】図1は本発明に使用するプローブ基盤を説明する図である。

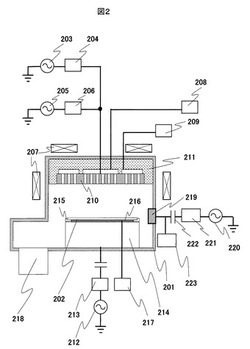

【図2】図2は本発明に使用するプラズマエッチング処理装置を説明する図である。

【図3】図3は本発明に係るプローブ基盤にバイアス電力を印加した時の時間と電圧の関係を示す。

【図4】図4は図3を拡大した図である。

【図5】図5は本発明に係るプローブ基盤上の電圧と電流の関係(I−V曲線)を示す図である。

【図6】図6は本発明の実施例1に係るプローブ基盤に印加するバイアス電力の回路を示す図である

【図7】図7は本発明の実施例1に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図8】図8は本発明に係るプローブ基盤上で測定した時間とプラズマパラメータの関係を示す図であり、(a)は時間とVdc、(b)は時間と飽和イオン電流、電子温度の関係を示す。

【図9】図9は本発明の実施例2に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図10】図10は本発明に係るプローブ基盤上の堆積膜厚とプラズマパラメータの関係を示す図であり、(a)は堆積膜厚とVdc、(b)は堆積膜厚と飽和イオン電流、電子温度の関係を示す。

【図11】図11は本発明の実施例2に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図12】図12は本発明の実施例3に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図13】図13は本発明の実施例4に使用するプラズマエッチング処理装置を説明する図である。

【図14】図14は本発明の実施例4に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図15】図15は本発明の実施例5に使用するプラズマエッチング処理装置を説明する図である。

【図16】図16は本発明の実施例5に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図17】図17は本発明の実施例6に使用するプローブ基盤の設置箇所を説明する図である。

【図18】図18は本発明の実施例6に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図19】図19は本発明の実施例7に使用するプラズマエッチング処理装置を説明する図である。

【発明を実施するための形態】

【0029】

(装置の具体例)

以下、図面を参照して、本発明の実施の形態について詳述する。

【0030】

図1に本発明の処理室の側壁をモニタするプローブ基盤119の概略図を示す。プローブ基盤119は、面積が1〜10cm2の導体101の表面上に処理室側壁表面の絶縁膜と同様な電気的に絶縁性である膜102が0〜100μmで形成されている。膜厚に関しては用途に応じて変更する。このプローブ基盤119は処理室側壁と同温度になるように制御するためヒータ103が装備されている。プローブ基盤119は処理室の壁面、内壁104と絶縁体105と真空ギャップ106を介しているため絶縁分離されている。

【0031】

図2は、エッチング処理で用いることを想定したプラズマ処理装置の形態を示す。図2は本発明におけるプラズマ処理装置の基本構成であり、第一のガス導入手段208および第二のガス導入手段209と真空排気手段を有する真空容器201に電磁コイル207が配置されており、同軸ケーブルによりアンテナ210に導入される電磁波と誘電磁コイル207による磁場の相互作用で真空容器201内に導入されたガスをプラズマ化する。

【0032】

この時、バイアス用電源212により発振された電磁波を整合器213とブロッキングコンデンサを用いて試料設置電極216に印加することで、高速に被処理体202のプラズマ処理を行うことができる。

【0033】

本実施の形態におけるアンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205の2つの周波数が印加されている。被処理体202は8〜20インチ径であり、該被処理体とアンテナ210の間隔は3〜10cmとなっている。アンテナ210はシリコンで形成されており、また該シリコンの表面に形成した複数の孔から原料ガスが真空容器201に導入される構成となっている。

【0034】

なお、原料ガスを真空容器内に導入するための複数の孔は、アンテナ中心部と外周部で分離されており、アンテナ中心部からは第一のガス導入手段208により供給された原料ガス、アンテナ外周部からは第二のガス導入手段209により供給された原料ガスを独立に供給することができる。

【0035】

また、処理室内201を所定の圧力に減圧するため、例えば、ターボ分子ポンプなどの排気手段218と、処理室内を所定の圧力値に調節するためのバルブなど(図示せず)が該排気手段の前段に設置されている。13.56MHzの第二の電源205の電磁波はアンテナ210表面とプラズマとの間で形成される電位を調節する機能を持つ。該13.56MHzの第二の電源205の出力を調整することでシリコン表面の電位が任意に調節でき、アンテナ210とプラズマ内活性種の反応が制御できる。

【0036】

処理室内には被処理体202を載置するためのステージ214が設置されている。該載置台には被処理体202を吸着するための試料設置電極216と被処理体を上に持ち上げるためのプッシャーピン(図示せず)とフォーカスリング215が設置されている。また、試料設置電極216には温調装置217が接続されており、電極温度をコントロールすることが出来る。

【0037】

処理室側壁のモニタは、図1で示したプローブ基盤219を処理室側壁に設置している。プローブ基盤219の表面の堆積被膜の状態については、処理室内でプラズマが生成している時に、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加し、バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。算出方法は以下に記す。

【0038】

(モニタ方法の具体例)

図3は処理室内でプラズマが生成している時に、プローブ基盤219にバイアス電力を2msecのパルス波で印加した時の時間と電圧の関係を示す。301の実線は電圧を示し、302の破線はプローブ基盤に印加したバイアス電力を示す。この図3の電圧の変化からプラズマ生成時の処理室内の側壁状態をモニタする。

【0039】

図4は、図3のバイアス電力を印加した際の2パルス分の電圧の変化を示す。401の電圧差はプローブ基盤にバイアス電圧を印加しており、コンデンサ:Cp222には負の電荷が充電される。よって、プローブ基盤上は負に帯電するためこの電圧差401は基盤上のVdcを示している。プローブ基盤上に堆積する被膜は電気的に絶縁性のため、基盤表面状態が変化することによりVdcの値も変化する。

【0040】

402の直線(破線)は、コンデンサに充電された電荷が時間ともに放電している電圧変化を示しており、この直線の傾きを示す放電レート(dVbias/dt)は[数1]で示される。

【数1】

eは素電荷、Aはプローブ基盤面積、Cpはコンデンサの容量

【0041】

放電後Γe(Vbias)はゼロに近づくことから、直線の傾きは飽和イオン電流(ICF:Ion Current Flux)に依存する[数2]。

【数2】

【0042】

直線(破線)403の傾き(放電レート:dVbias/dt)はプローブ基盤上近傍のプラズマの電子温度(kT/e)に依存する。電子温度の算出方法は下記に示す。[数1]より放電レート:dVbias/dtにコンデンサ:Cpの容量を掛けることにより電流を算出する[数3]。算出された電流値からI−V曲線を作成する。

【数3】

【0043】

図5はプローブ基盤上の電圧と電流の関係(I−V曲線)を示す。実線のI−V曲線 501は[数3]より算出された実測値の電流:Iと放電電圧の関係を示し、破線のI−V曲線 502は[数4]よりマクスウェル分布を仮定しで算出した予測値の電流:Iと放電電圧の関係を示す。

【数4】

【0044】

図5の実測値の電流を用いたI−V曲線501と予測値の電流を用いたI−V曲線 502の相関性を確認しながら、I−V曲線502の[数4]から電子温度を算出する。

【実施例1】

【0045】

(第一の実施の形態)

図6は、プローブ基盤619に印加するバイアス電力の回路を示す。601は切り替えスイッチであり、602側に接続した際はコンデンサ:Cw603を介してグランドに接地する。コンデンサ:Cw603の容量は、処理装置の側壁に溶射されている絶縁性の膜と同等の静電容量とする。このためプローブ基盤と処理装置側壁の表面状態の静電容量は同等となる。601のスイッチを604側に接続した際はバイアス電源側と接続し、バイアス電力が印加される。

【0046】

図7は、本発明の第一の実施の形態における処理手順を説明するフローチャートである。最初にプローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS71)。ここでのプローブ基盤と処理室側壁の表面状態の静電容量は同等であり、またプローブ基盤はヒータが内蔵されているため基盤の温度も処理室側壁と同等になるよう温調する。次に量産が開始され、製造ウエハの処理が行われる(ステップS72)。

【0047】

製造ウエハの処理を行うプロセスガスは、C4F8,C5F8などのCF系のガスを使用すると処理室側壁上とプローブ基盤上にCF系のデポが堆積する。次にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS73)。

【0048】

その後ダミーウエハを用いて処理室内のクリーニングステップを行う。クリーニングステップは堆積物のCF系のデポの除去を行うため、O2ガスを中心とした条件を使用する。クリーニングステップ中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp 222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS74)。

【0049】

図8の(a)は、プローブ基盤上のVdcの時間依存性を示す。時間の増加とともにVdcの値が減少し一定値に近づく。これは、クリーニング開始時にはプローブ基盤上にデポが堆積しているが、時間とともに堆積物が除去されるため一定値に近づいている。図8bは飽和イオン電流:ICF◆と電子温度□の時間依存性を示す。

【0050】

両者とも、時間の増加とともに増加し一定値に近づいている。これはVdc値と同様でクリーニング開始時はプローブ基盤上にデポが堆積しているが、時間とともに堆積物が除去されるため一定値に近づいている。この各値が一定値になる時間t0(ステップS75)がクリーニングステップの終了(ステップS76)となる。

【実施例2】

【0051】

(第二の実施の形態)

図9は本発明の処理手順を説明するフローチャートである。この処理では基盤上の堆積物の膜厚と各プラズマパラメータの相関を確認する。最初にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS91)。

【0052】

次に、量産条件でダミーウエハを用いて処理を行う。処理時間はt0時間とする。放電時間t0時の際にプローブ基盤にバイアス電力を数秒間供給し、コンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流:ICF、Vdc、電子温度を算出する(ステップS92)。

【0053】

次にプローブ基盤を取り外し、基盤上に堆積した膜厚:D0nmを膜厚計やSEMなどを用いて測定する(ステップS93)。ステップS91〜ステップS93を繰り返し行い放電時間tn時の飽和イオン電流:ICF、Vdc、電子温度を算出し、膜厚:Dnnmを測定する。

【0054】

図10は各膜厚での飽和イオン電流:ICF、Vdc、電子温度を示す。図10の(a)は膜厚とVdcの相関を示し、膜厚の増加とともにVdcの値も増加している。そのため膜厚:xdとVdc:yvdcの関係は[数5]となる。

【0055】

図10の(b)は、各膜厚での飽和イオン電流:ICF、電子温度を示す。膜厚の増加とともにICFは増加し、電子温度は減少している。そのため膜厚:xdとICF:yICFの関係は[数6]となり、電子温度:ykTeの関係は[数7]となる。またこれらの結果より、各膜厚:ydを飽和イオン電流:ICF x1、Vdc:x2、電子温度を用いて重回帰分析を行い、重回帰式での表現も可能となる[数8]。

【数5】

avdcは膜厚とVdcの相関、bvdcはオフセット

【数6】

aICFは膜厚とICFの相関、bICFはオフセット

【数7】

akTeは膜厚とkTeの相関、bkTeはオフセット

【数8】

dはオフセット

【0056】

これらの関係から、各膜厚での飽和イオン電流:ICF、Vdc、電子温度の相関式[数5−8]を算出する(ステップS94)。ここで得られた基盤上の堆積膜厚は、処理室側壁に堆積した膜厚と同等である。

【0057】

図11は、本発明の第二の実施の形態における処理手順を説明するフローチャートである。本発明はメンテナンスや長期アイドル時間からの復帰に関しての処理方法である。最初に全掃によるメンテナンス終了や6時間以上の長期アイドル時間の状態から開始する(ステップS111)。プローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS112)。

【0058】

次に、量産条件でシーズニング(ダミー)ウエハの処理を開始する。ウエハ毎もしくは定期的に決めたウエハ(例えばロットの最後のウエハ)で、各条件の放電終了の数秒前にプローブ基盤をバイアス電源側(スイッチ604)に接続する。接続後プローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。

【0059】

図9で得られた膜厚との相関式から、プローブ基盤上の堆積物の膜厚を算出する(ステップS113)。この膜厚は処理装置側壁の堆積物の膜厚になるため、この膜厚値に閾値を設けて製品ウエハ処理の開始を判断する(ステップS114)。処理室側壁の堆積膜厚が閾値Dnm以上であれば、製品ウエハの処理を開始する(ステップS115)。

【0060】

処理室側壁の堆積膜厚が閾値Dnm未満であれば、ステップ S112に戻り、シーズニングを継続する。

【実施例3】

【0061】

(第三の実施の形態)

図12は本発明の第三の実施の形態における処理手順を説明するフローチャートである。本発明は製品ウエハの処理を行いながら、堆積物の影響によるメンテナンスの周期を判断する処理方法である。

【0062】

最初にプローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS121)。次に量産条件で製品ウエハの処理を開始する。ウエハ毎もしくは定期的に決めたウエハ(例えばロットの最後のウエハ)で、各条件の放電終了の数秒前にプローブ基盤をバイアス電源側(スイッチ604)に接続する。

【0063】

接続後、プローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧をモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。図9で得られた膜厚との相関[数5−9]から、プローブ基盤上の堆積物の膜厚を算出する(ステップS122)。

【0064】

この膜厚は処理装置側壁の堆積物の膜厚になるため、この膜厚に閾値を設けてメンテナンスのタイミングを判断する(ステップS123)。処理室側壁の堆積膜厚が閾値Dnm以上であれば、処理室を大気開放してメンテナンスを開始する(ステップS124)。処理室側壁の堆積膜厚が閾値Dnm未満であれば、ステップS121に戻り製品ウエハの処理を継続する。

【実施例4】

【0065】

(第四の実施の形態)

これまで処理装置側壁部の堆積物の除去と堆積の制御の例であるが、更なる応用例としてアンテナ部分の堆積物制御に関して説明する。

【0066】

図13の処理装置は、図2に示したと同様に、第一のガス導入手段208および第二のガス導入手段209と真空排気手段218を有する真空容器201に電磁コイル207が配置されている。上部電極部は、アンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205が配置されている。

【0067】

下部電極部は被処理体202を載置するためのステージ214が設置され、該載置台には被処理体202を吸着するための試料設置電極216が設置され、温調装置217が接続されている。被処理体202のプラズマ処理を行うためにバイアス用電源212、整合器213とブロッキングコンデンサが配置されている。

【0068】

アンテナ部の堆積物のモニタは、処理室内でプラズマが生成している時に、スイッチをバイアス電源側1301に切り替え、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加する。バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。

【0069】

図14は、本発明の第四の実施の形態における処理手順を説明するフローチャートである。最初に図2と同様にアンテナを電源205側に取り付け、量産条件で製品ウエハの処理を行う(ステップS141)。この際アンテナ表面には、デポが堆積する。

【0070】

次に、ダミーウエハを用いて処理室内のO2ガスをベースとしたクリーニングステップを行う。クリーニングステップの放電中にアンテナをバイアス電源側のスイッチ1301に接続する。接続後アンテナにバイアス電力を供給しながらコンデンサ:Cp 222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。(ステップS142)。

【0071】

第一の実施例と同様に、堆積物は時間とともに除去されるため、各値が一定値に近づく。この各値が一定値になる時間(ステップS143)がクリーニングステップの終了(ステップS144)となる。

【実施例5】

【0072】

(第五の実施の形態)

図15は、エッチング処理で用いることを想定したマイクロ波ECR方式のプラズマ処理装置の形態を示す。

【0073】

この装置は、内壁1501、1511やマイクロ波導入窓1506で覆われた真空処理室1517があり、その外部には3つのソレノイドコイル1512、1513および1514と、鉄製のヨーク1515、1516が設置され、真空処理室1517上部には、マイクロ波を共振させる共振器1505があり、さらに共振器1505上部には、マイクロ波導波管1505、高周波整合器1504、マグネトロン1503が設置されている。

【0074】

真空処理室1517内には、高周波バイアスが印加および温度調整機構がある処理台1508があり、処理台1508表面に形成した静電チャックを介してウエハ1507が固定できるようになっている。ウエハは、搬送ポートのバルブ1510を開閉して搬送される。

【0075】

この装置に、エッチングガスをシャワープレート1502より真空処理室1517に導入し、ガス圧力を調圧バルブ1509で制御する。マグネトロン1503で約2.45GHz高周波を発生させ、高周波マッチング装置1504、導波管1505、空洞共振器1518、マイクロ波導入窓1506を通って真空処理室に導入させる。

【0076】

さらに、ソレノイドコイル1512、1513および1514に直流電流を印加し、真空処理室内の一部が所望の磁場になるようにコイル電流を調整する。導入したガスとマイクロ波およびコイル磁場によりプラズマを生成する。

【0077】

処理室側壁状態をモニタするプローブ基盤は、内壁1501、1511上に複数取り付ける1519a,

1519b,1519c,1519d。プローブ基盤を複数取り付けるのは、高さ方向によって堆積物の膜厚が異なるためモニタする必要が有る。

【0078】

図16は、本発明の第五の実施の形態における処理手順を説明するフローチャートである。最初に処理室側壁部に取り付けた全てのプローブ基盤をコンデンサCw側(スイッチ602)に接地する(ステップS161)。次に量産が開始され、製造ウエハの処理が行われる(ステップS162)。

【0079】

ここで、全てのプローブ基盤にデポは堆積するが、高さ方向でデポの堆積膜厚が異なる。次にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS163)。その後ダミーウエハを用いて処理室内のクリーニングステップを行う。クリーニングステップ中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS164)。

【0080】

第一の実施例と同様に堆積物は時間とともに除去されるため、各値が一定値に近づく。但し、各プローブ基盤の堆積膜厚は異なり、且つクリーニングによるデポの除去率が高さ方向によって異なるためソレノイドコイル1512、1513および1514に直流電流を印加し、真空処理室内の一部が所望の磁場になるようにコイル電流を調整してECR面を制御しながらクリーニングを行う。全てのプローブ基盤の各値が一定値になる時間(ステップ S165)がクリーニングステップの終了(ステップS166)となる。

【実施例6】

【0081】

(第六の実施の形態)

図17は、エッチング処理で用いることを想定したプラズマ処理装置へのプローブ基盤の取りつけ方の一例を示す。この時のプラズマ処理装置は図2の構成であってもいいし、図15の構成でもよい。

【0082】

プローブ基盤1719a,1719b,1719c,1719dの数は2個以上左右(上下)対称に配置する。取り付ける箇所は、処理室側壁であり高さ方向は該載置台上の被処理体より低い部分が望ましい。プローブ基盤を取り付ける箇所の壁材は導体で有ってもいいし絶縁体であってもよい。

【0083】

図18は、本発明の第六の実施の形態における処理手順を説明するフローチャートである。最初に全掃やパーツ交換をしたようなメンテナンスを行う(ステップS181)。ここでのパーツとは処理室内のパーツであり、全掃時に交換するパーツや消耗品パーツであり素材はSi、石英、導体(表面加工されたパーツ含)のリングである。

【0084】

その後、処理室側壁部に取り付けた全てのプローブ基盤をバイアス電源側(スイッチ604)に接地する(ステップS182)。次に、ダミーウエハを用いて量産条件で仮シーズニングの処理を行う。シーズニング処理の放電中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS183)。

【0085】

次に、算出された各基盤の各値と時間依存による電圧変化の波形を比較する(ステップ S184)。全てのプローブ基盤もしくは対称面同士のプローブ基盤の値が一致したならば、プラズマには偏りが無いことを示している。よって設置したパーツの組み合わせは問題ないと判断され、本シーズニングの処理が行われる(ステップS185)。

【0086】

逆に、全てのプローブ基盤もしくは対称面同士のプローブ基盤の値が一致しないならば、プラズマに偏りがあることからパーツの組み合わせにズレが生じていることになる。そのため再度処理室内のパーツの再組み合わせが必要となる(ステップS186)。パーツを組み合わせた後、(ステップS182)に戻り再度仮シーズニング処理を行い、パーツの組み合わせを確認する。

【実施例7】

【0087】

(第七の実施の形態)

本発明の第七の実施の形態では、処理装置側壁部の堆積物の除去と堆積の制御と、アンテナ部分の堆積物制御が可能である。

【0088】

図19の処理装置は、図13に示したと同様に、第一のガス導入手段208および第二のガス導入手段209と真空排気手段218を有する真空容器201に電磁コイル207が配置されている。上部電極部は、アンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205が配置されている。

【0089】

下部電極部は被処理体202を載置するためのステージ214が設置され、該載置台には被処理体202を吸着するための試料設置電極216が設置され、温調装置217が接続されている。被処理体202のプラズマ処理を行うためにバイアス用電源212、整合器213とブロッキングコンデンサが配置されている。

【0090】

アンテナ部の堆積物のモニタは、処理室内でプラズマが生成している時に、スイッチをバイアス電源側1901に切り替え、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加する。バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。

【0091】

また、図19の処理装置は、図15,図17に示したと同様に、処理室側壁状態をモニタする複数のプローブ基盤1919が、内壁201上の異なる位置に複数取り付ける。プローブ基盤を異なる高さに複数取り付けるのは、高さ方向によって堆積物の膜厚が異なるためモニタする必要が有るからである。

【0092】

また、プローブ基盤1919を2個以上、左右(上下)に配置する。取り付ける箇所は、処理室側壁の異なる位置に取り付ける。全てのプローブ基盤にデポは堆積するが、異なる位置と異なる高さ方向でデポの堆積膜厚が異なる場合があるからである。プローブ基盤1919を取り付ける箇所の壁材は導体で有ってもいいし絶縁体であってもよい。

【0093】

以上に記載した本発明方法で半導体装置を製造するプラズマ処理装置のプラズマをモニタするプローブ基盤を用いることにより、処理室内のプラズマ中の飽和イオン電流、Vdc、電子温度の算出が可能となり、そのデータを用いて処理を行うことによりプラズマ処理装置の安定稼動ができる。また、それらの装置を使用することにより安定した半導体装置が製造できる。

【符号の説明】

【0094】

101 導体

102 絶縁被膜

103 ヒータ

104 処理室の内壁

105 絶縁体

106 真空ギャップ

119 プローブ基盤

201 チャンバー(処理容器)

202 被処理体

203 第一の電源

204 第一の整合器

205 第二の電源

206 第二の整合器

207 磁場コイル

208 第一のガス供給手段

209 第二のガス供給手段

210 アンテナ

211 アンテナ裏誘電体

212 バイアス用電源

213 第三の整合器

214 ステージ

215 フォーカスリング

216 試料設置電極

217 温調装置

218 排気手段

219 プローブ基盤

220 パルス電源

221 第四の整合器

222 コンデンサ

223 PC(オシロスコープ)

301 電圧

302 バイアス電力

401 Vdc

402 放電レート(ICF算出)

403 放電レート(電子温度算出)

501 実測値(I−V曲線)

502 予測値(I−V曲線)

601 切り替えスイッチ

602 グランド側

603 コンデンサCw側

604 バイアス電源側

619 プローブ基盤

1301 バイアス電源側スイッチ

1501 上部内壁

1502 シャワープレート

1503 マグネトロン

1504 高周波整合器

1505 導波管

1506 マイクロ波導入窓

1507 ウエハ(被処理体)

1508 処理台

1509 長圧バルブ

1510 搬送ポートバルブ

1511 下部内壁

1512 上ソレノイドコイル

1513 中ソレノイドコイル

1514 下ソレノイドコイル

1515 ヨーク

1516 ヨーク

1517 真空処理室

1518 空洞共振器

1519 プローブ基盤

1719 プローブ基盤

1919 プローブ基盤

【技術分野】

【0001】

本発明は、半導体装置を製造するプラズマ処理装置及びこのプラズマ処理装置を用いたプラズマ処理方法に関する。

【背景技術】

【0002】

半導体装置はイオン打ち込み、スパッタ装置、プラズマCVD装置による成膜、マスクパターンの露光現像によるレジストマスクへの転写、プラズマエッチングによる薄膜の加工、および洗浄の組み合わせにより製造される。近年半導体装置の高速化に伴い、半導体装置はより微細化となり加工による僅かなズレが無視できなくなっている。

【0003】

半導体製造の成膜装置やドライエッチング装置では、プラズマ処理を行うためウエハの処理枚数と共に、装置内壁面の状態が堆積物付着やエッチングにより変化する(経時変化)。このため、処理時間を管理して、消耗品の交換や内壁面の洗浄を行っている。

【0004】

装置の内壁面は、処理時間と共に連続的に変化しているため、初期状態(洗浄直後)と洗浄直前では、成膜装置では薄膜の膜厚、特性が僅かに異なり、ドライエッチング装置では、形状寸法や深さやマスク選択比が僅かに異なってくる。そのためプラズマ処理を行う際は、処理室内の内壁状態やプラズマ自身をモニタリングして常に同じ環境を保たなければならない。

【0005】

一方、半導体装置の微細化の進展に伴い、レジストの薄膜化に伴うエッチング時のレジスト消耗速度低減(レジスト選択比向上)、下地膜のエッチング速度低減(下地膜選択比向上)、高アスペクト比ホールへの十分なエッチャント供給などの要求から、堆積性の強いガス処理ガスが多用されることが予想される。

【0006】

しかしながら、堆積性の強い処理ガスを用いると、プラズマ処理室内には堆積物が付着する。この堆積物がプラズマ処理室内の内壁に過剰に付着すると剥離する。この堆積物が剥離した場合には、半導体装置上に付着し異物粒子として半導体製造ラインを汚染し、歩留まり低下を引き起こすことになる。

【0007】

このため、プラズマ処理室内の長期安定性の観点から、処理室内の内壁状態を常にモニタし、堆積物がプラズマ処理室内の内壁から剥離する前に全掃するタイミングを見極めることは極めて重要である。

【0008】

このような背景から、プラズマ処理装置内部の内壁状態やプラズマの状態変化を検出し、その検出結果をプラズマ処理装置に反映してウエハ処理を行い、一定の処理結果が得られるようにするなどの工夫がなされてきた。

【0009】

非特許文献1と非特許文献2では、半導体製造のプラズマ処理装置の内壁や天板にプローブ基盤を配置し、このプローブ基盤にパルス化したバイアス電力を供給することによりプローブ基盤表面の状態をモニタし制御することによりプラズマ処理室の内部を制御する方法を開示している。

【0010】

特許文献1では、半導体製造のプラズマ処理装置の内壁に平面プローブ基盤を2つ配置し、これらのプローブ基盤にパルス化した電力を供給しプラズマの内部状態を測定し制御する方法を開示している。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特表2007−502519号

【非特許文献】

【0012】

【非特許文献1】2007Dry Process International Symposium 3−03

【非特許文献2】2008Dry Process International Symposium P1−21

【発明の概要】

【発明が解決しようとする課題】

【0013】

プラズマプロセスを使用した半導体製造装置は、装置内壁面の状態が堆積物付着やパーツのエッチングにより経時的に変化する。また同様な変化として、消耗品パーツの交換や内壁面の洗浄の前後で変化が見られる。これらの変化によりプラズマエッチングにおいて所望のエッチング結果を得られなかったり、プラズマCVDにおいて膜質が変質したり均一にならない、という製品の品質低下を招くことになる。

【0014】

このような変動は、プラズマ内部の変動のため半導体製造装置に備えられた各種センサ(圧力計、流量計、高周波電力計、温度計)では正確な測定を行うことが難しく、各種センサが所望の値を示しているにもかかわらず、実際の製品は所望の結果とは異なる事がある。このような場合は、各種センサが正常なためにプロセスが正常に行われていないにもかかわらず、半導体装置の製造が継続されたりして製品の低下に繋がる。

【0015】

また、プロセスの結果より異常に気付いても、原因となるパラメータが分かないため、携わったエンジニアの経験により解決されるために装置の復旧に多大な時間を要する。

【0016】

このように、プラズマプロセスの進行に影響を与えるパラメータは、装置センサを監視するだけでは不十分であり、チャンバー内の時々刻々と変化するパラメータを制御することにより安定したプラズマプロセスを行うことが可能となる。

【0017】

非特許文献1及び非特許文献2では、プローブ基盤のデータからプラズマ内部のパラメータのモニタはできる。しかしながらこのモニタでは基盤周辺のプラズマ状態のみであり、且つプローブ基盤の材質が処理室内壁の素材と異なるため、実際の処理室の内壁状態を反映しているとは限らない。

【0018】

プローブ基盤への堆積は、基盤の材質・温度・静電容量などが処理室内壁と同等でないと堆積膜厚が異なってしまう。そのためプローブ基盤を処理室内壁と異なる状態でモニタしプラズマの制御を行うと、安定したプラズマ処理ができない。

【0019】

処理室内のプラズマ処理をモニタし再現よく安定して制御するには。プラズマ状態を乱さず装置の内壁状態と同等な測定環境が必要となる。

【0020】

特許文献1では、2つの平面プローブ基盤のデータからプラズマの内部状態のモニタとプラズマの制御はできる。しかしながら基盤の温度制御や経時変化を含む表面状態の制御を考慮していないため、測定環境が変動し安定したプラズマ処理のプロセス制御まではできない。

【0021】

本発明の目的は、半導体装置の製造を安定して効率よく行うため、処理室内壁の堆積物の状態やプラズマ内部について直接モニタを行い、常時管理をしながら処理する方法を提供することである。

【課題を解決するための手段】

【0022】

上記目的を達成するために、本発明では半導体装置を製造するプラズマ処理装置の内壁にプローブ基盤を配置する。この基盤にパルス化したバイアス電力を掛け、コンデンサの電圧変化を解析することにより、処理室内壁状態とプラズマの内部状態がリアルタイムでモニタできる、そのデータ値からプラズマ処理装置の処理方法を制御する。

【0023】

(1)本発明は、プローブ基盤直下に静電容量を調節するコンデンサに接続するスイッチを配置することにより、基盤は処理室内壁と同様な静電容量が再現される。また基盤中へヒータを内蔵することにより、基盤は処理室内壁と同様な温度の再現が得られる。よってプローブ基盤は静電容量と温度に関して処理室内壁と同等になることから適格な内壁状態のモニタを行う。

【0024】

(2)本発明は、量産時のドライクリーニングの処理方法において、処理室内壁の表面状態とプラズマ内部状態をリアルタイムでモニタすることにより処理室内のクリーニング状況が明確になり、効率の良い量産が可能となる。またプローブ基盤を高さ方向に複数配置することにより、処理室内部の高さ方向のクリーニング状況が明確になるためクリーニング条件のパラメータを適宜変更し効率の良いクリーニング処理を行う。

【0025】

(3)本発明は、全掃直後の量産に向けてのシーズニング処理方法と量産中の堆積物の影響による全掃判断において、プローブ基盤から処理室内壁の表面状態とプラズマの内部状態をリアルタイムでモニタすることにより処理室内の環境が管理されるため、安定的な半導体装置の製造を行う。

【0026】

(4)本発明は、全掃時による消耗品や交換品の組み付け状況において、シーズニングによるプラズマから直接処理室内の状態が判断できるため、容易に処理室内の環境管理を行う。

【発明の効果】

【0027】

本発明によれば、プラズマの処理中にプローブ基盤にパルス電圧を掛けることにより、コンデンサが充電と放電を繰り返し、コンデンサの放電レートよりVdc、飽和イオン電流、電子温度が算出できるため、処理室内壁の堆積物の状態やプラズマ内部をリアルタイムでモニタできる。そのため装置内の内壁状態の常時管理を行いながら処理を行うため、安定した半導体装置を製造することができる。

【図面の簡単な説明】

【0028】

【図1】図1は本発明に使用するプローブ基盤を説明する図である。

【図2】図2は本発明に使用するプラズマエッチング処理装置を説明する図である。

【図3】図3は本発明に係るプローブ基盤にバイアス電力を印加した時の時間と電圧の関係を示す。

【図4】図4は図3を拡大した図である。

【図5】図5は本発明に係るプローブ基盤上の電圧と電流の関係(I−V曲線)を示す図である。

【図6】図6は本発明の実施例1に係るプローブ基盤に印加するバイアス電力の回路を示す図である

【図7】図7は本発明の実施例1に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図8】図8は本発明に係るプローブ基盤上で測定した時間とプラズマパラメータの関係を示す図であり、(a)は時間とVdc、(b)は時間と飽和イオン電流、電子温度の関係を示す。

【図9】図9は本発明の実施例2に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図10】図10は本発明に係るプローブ基盤上の堆積膜厚とプラズマパラメータの関係を示す図であり、(a)は堆積膜厚とVdc、(b)は堆積膜厚と飽和イオン電流、電子温度の関係を示す。

【図11】図11は本発明の実施例2に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図12】図12は本発明の実施例3に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図13】図13は本発明の実施例4に使用するプラズマエッチング処理装置を説明する図である。

【図14】図14は本発明の実施例4に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図15】図15は本発明の実施例5に使用するプラズマエッチング処理装置を説明する図である。

【図16】図16は本発明の実施例5に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図17】図17は本発明の実施例6に使用するプローブ基盤の設置箇所を説明する図である。

【図18】図18は本発明の実施例6に係るプローブ基盤を用いた半導体製造装置の処理方法を示すフローチャートである。

【図19】図19は本発明の実施例7に使用するプラズマエッチング処理装置を説明する図である。

【発明を実施するための形態】

【0029】

(装置の具体例)

以下、図面を参照して、本発明の実施の形態について詳述する。

【0030】

図1に本発明の処理室の側壁をモニタするプローブ基盤119の概略図を示す。プローブ基盤119は、面積が1〜10cm2の導体101の表面上に処理室側壁表面の絶縁膜と同様な電気的に絶縁性である膜102が0〜100μmで形成されている。膜厚に関しては用途に応じて変更する。このプローブ基盤119は処理室側壁と同温度になるように制御するためヒータ103が装備されている。プローブ基盤119は処理室の壁面、内壁104と絶縁体105と真空ギャップ106を介しているため絶縁分離されている。

【0031】

図2は、エッチング処理で用いることを想定したプラズマ処理装置の形態を示す。図2は本発明におけるプラズマ処理装置の基本構成であり、第一のガス導入手段208および第二のガス導入手段209と真空排気手段を有する真空容器201に電磁コイル207が配置されており、同軸ケーブルによりアンテナ210に導入される電磁波と誘電磁コイル207による磁場の相互作用で真空容器201内に導入されたガスをプラズマ化する。

【0032】

この時、バイアス用電源212により発振された電磁波を整合器213とブロッキングコンデンサを用いて試料設置電極216に印加することで、高速に被処理体202のプラズマ処理を行うことができる。

【0033】

本実施の形態におけるアンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205の2つの周波数が印加されている。被処理体202は8〜20インチ径であり、該被処理体とアンテナ210の間隔は3〜10cmとなっている。アンテナ210はシリコンで形成されており、また該シリコンの表面に形成した複数の孔から原料ガスが真空容器201に導入される構成となっている。

【0034】

なお、原料ガスを真空容器内に導入するための複数の孔は、アンテナ中心部と外周部で分離されており、アンテナ中心部からは第一のガス導入手段208により供給された原料ガス、アンテナ外周部からは第二のガス導入手段209により供給された原料ガスを独立に供給することができる。

【0035】

また、処理室内201を所定の圧力に減圧するため、例えば、ターボ分子ポンプなどの排気手段218と、処理室内を所定の圧力値に調節するためのバルブなど(図示せず)が該排気手段の前段に設置されている。13.56MHzの第二の電源205の電磁波はアンテナ210表面とプラズマとの間で形成される電位を調節する機能を持つ。該13.56MHzの第二の電源205の出力を調整することでシリコン表面の電位が任意に調節でき、アンテナ210とプラズマ内活性種の反応が制御できる。

【0036】

処理室内には被処理体202を載置するためのステージ214が設置されている。該載置台には被処理体202を吸着するための試料設置電極216と被処理体を上に持ち上げるためのプッシャーピン(図示せず)とフォーカスリング215が設置されている。また、試料設置電極216には温調装置217が接続されており、電極温度をコントロールすることが出来る。

【0037】

処理室側壁のモニタは、図1で示したプローブ基盤219を処理室側壁に設置している。プローブ基盤219の表面の堆積被膜の状態については、処理室内でプラズマが生成している時に、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加し、バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。算出方法は以下に記す。

【0038】

(モニタ方法の具体例)

図3は処理室内でプラズマが生成している時に、プローブ基盤219にバイアス電力を2msecのパルス波で印加した時の時間と電圧の関係を示す。301の実線は電圧を示し、302の破線はプローブ基盤に印加したバイアス電力を示す。この図3の電圧の変化からプラズマ生成時の処理室内の側壁状態をモニタする。

【0039】

図4は、図3のバイアス電力を印加した際の2パルス分の電圧の変化を示す。401の電圧差はプローブ基盤にバイアス電圧を印加しており、コンデンサ:Cp222には負の電荷が充電される。よって、プローブ基盤上は負に帯電するためこの電圧差401は基盤上のVdcを示している。プローブ基盤上に堆積する被膜は電気的に絶縁性のため、基盤表面状態が変化することによりVdcの値も変化する。

【0040】

402の直線(破線)は、コンデンサに充電された電荷が時間ともに放電している電圧変化を示しており、この直線の傾きを示す放電レート(dVbias/dt)は[数1]で示される。

【数1】

eは素電荷、Aはプローブ基盤面積、Cpはコンデンサの容量

【0041】

放電後Γe(Vbias)はゼロに近づくことから、直線の傾きは飽和イオン電流(ICF:Ion Current Flux)に依存する[数2]。

【数2】

【0042】

直線(破線)403の傾き(放電レート:dVbias/dt)はプローブ基盤上近傍のプラズマの電子温度(kT/e)に依存する。電子温度の算出方法は下記に示す。[数1]より放電レート:dVbias/dtにコンデンサ:Cpの容量を掛けることにより電流を算出する[数3]。算出された電流値からI−V曲線を作成する。

【数3】

【0043】

図5はプローブ基盤上の電圧と電流の関係(I−V曲線)を示す。実線のI−V曲線 501は[数3]より算出された実測値の電流:Iと放電電圧の関係を示し、破線のI−V曲線 502は[数4]よりマクスウェル分布を仮定しで算出した予測値の電流:Iと放電電圧の関係を示す。

【数4】

【0044】

図5の実測値の電流を用いたI−V曲線501と予測値の電流を用いたI−V曲線 502の相関性を確認しながら、I−V曲線502の[数4]から電子温度を算出する。

【実施例1】

【0045】

(第一の実施の形態)

図6は、プローブ基盤619に印加するバイアス電力の回路を示す。601は切り替えスイッチであり、602側に接続した際はコンデンサ:Cw603を介してグランドに接地する。コンデンサ:Cw603の容量は、処理装置の側壁に溶射されている絶縁性の膜と同等の静電容量とする。このためプローブ基盤と処理装置側壁の表面状態の静電容量は同等となる。601のスイッチを604側に接続した際はバイアス電源側と接続し、バイアス電力が印加される。

【0046】

図7は、本発明の第一の実施の形態における処理手順を説明するフローチャートである。最初にプローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS71)。ここでのプローブ基盤と処理室側壁の表面状態の静電容量は同等であり、またプローブ基盤はヒータが内蔵されているため基盤の温度も処理室側壁と同等になるよう温調する。次に量産が開始され、製造ウエハの処理が行われる(ステップS72)。

【0047】

製造ウエハの処理を行うプロセスガスは、C4F8,C5F8などのCF系のガスを使用すると処理室側壁上とプローブ基盤上にCF系のデポが堆積する。次にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS73)。

【0048】

その後ダミーウエハを用いて処理室内のクリーニングステップを行う。クリーニングステップは堆積物のCF系のデポの除去を行うため、O2ガスを中心とした条件を使用する。クリーニングステップ中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp 222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS74)。

【0049】

図8の(a)は、プローブ基盤上のVdcの時間依存性を示す。時間の増加とともにVdcの値が減少し一定値に近づく。これは、クリーニング開始時にはプローブ基盤上にデポが堆積しているが、時間とともに堆積物が除去されるため一定値に近づいている。図8bは飽和イオン電流:ICF◆と電子温度□の時間依存性を示す。

【0050】

両者とも、時間の増加とともに増加し一定値に近づいている。これはVdc値と同様でクリーニング開始時はプローブ基盤上にデポが堆積しているが、時間とともに堆積物が除去されるため一定値に近づいている。この各値が一定値になる時間t0(ステップS75)がクリーニングステップの終了(ステップS76)となる。

【実施例2】

【0051】

(第二の実施の形態)

図9は本発明の処理手順を説明するフローチャートである。この処理では基盤上の堆積物の膜厚と各プラズマパラメータの相関を確認する。最初にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS91)。

【0052】

次に、量産条件でダミーウエハを用いて処理を行う。処理時間はt0時間とする。放電時間t0時の際にプローブ基盤にバイアス電力を数秒間供給し、コンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流:ICF、Vdc、電子温度を算出する(ステップS92)。

【0053】

次にプローブ基盤を取り外し、基盤上に堆積した膜厚:D0nmを膜厚計やSEMなどを用いて測定する(ステップS93)。ステップS91〜ステップS93を繰り返し行い放電時間tn時の飽和イオン電流:ICF、Vdc、電子温度を算出し、膜厚:Dnnmを測定する。

【0054】

図10は各膜厚での飽和イオン電流:ICF、Vdc、電子温度を示す。図10の(a)は膜厚とVdcの相関を示し、膜厚の増加とともにVdcの値も増加している。そのため膜厚:xdとVdc:yvdcの関係は[数5]となる。

【0055】

図10の(b)は、各膜厚での飽和イオン電流:ICF、電子温度を示す。膜厚の増加とともにICFは増加し、電子温度は減少している。そのため膜厚:xdとICF:yICFの関係は[数6]となり、電子温度:ykTeの関係は[数7]となる。またこれらの結果より、各膜厚:ydを飽和イオン電流:ICF x1、Vdc:x2、電子温度を用いて重回帰分析を行い、重回帰式での表現も可能となる[数8]。

【数5】

avdcは膜厚とVdcの相関、bvdcはオフセット

【数6】

aICFは膜厚とICFの相関、bICFはオフセット

【数7】

akTeは膜厚とkTeの相関、bkTeはオフセット

【数8】

dはオフセット

【0056】

これらの関係から、各膜厚での飽和イオン電流:ICF、Vdc、電子温度の相関式[数5−8]を算出する(ステップS94)。ここで得られた基盤上の堆積膜厚は、処理室側壁に堆積した膜厚と同等である。

【0057】

図11は、本発明の第二の実施の形態における処理手順を説明するフローチャートである。本発明はメンテナンスや長期アイドル時間からの復帰に関しての処理方法である。最初に全掃によるメンテナンス終了や6時間以上の長期アイドル時間の状態から開始する(ステップS111)。プローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS112)。

【0058】

次に、量産条件でシーズニング(ダミー)ウエハの処理を開始する。ウエハ毎もしくは定期的に決めたウエハ(例えばロットの最後のウエハ)で、各条件の放電終了の数秒前にプローブ基盤をバイアス電源側(スイッチ604)に接続する。接続後プローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。

【0059】

図9で得られた膜厚との相関式から、プローブ基盤上の堆積物の膜厚を算出する(ステップS113)。この膜厚は処理装置側壁の堆積物の膜厚になるため、この膜厚値に閾値を設けて製品ウエハ処理の開始を判断する(ステップS114)。処理室側壁の堆積膜厚が閾値Dnm以上であれば、製品ウエハの処理を開始する(ステップS115)。

【0060】

処理室側壁の堆積膜厚が閾値Dnm未満であれば、ステップ S112に戻り、シーズニングを継続する。

【実施例3】

【0061】

(第三の実施の形態)

図12は本発明の第三の実施の形態における処理手順を説明するフローチャートである。本発明は製品ウエハの処理を行いながら、堆積物の影響によるメンテナンスの周期を判断する処理方法である。

【0062】

最初にプローブ基盤をコンデンサ:Cw側(スイッチ602)に接地する(ステップS121)。次に量産条件で製品ウエハの処理を開始する。ウエハ毎もしくは定期的に決めたウエハ(例えばロットの最後のウエハ)で、各条件の放電終了の数秒前にプローブ基盤をバイアス電源側(スイッチ604)に接続する。

【0063】

接続後、プローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧をモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。図9で得られた膜厚との相関[数5−9]から、プローブ基盤上の堆積物の膜厚を算出する(ステップS122)。

【0064】

この膜厚は処理装置側壁の堆積物の膜厚になるため、この膜厚に閾値を設けてメンテナンスのタイミングを判断する(ステップS123)。処理室側壁の堆積膜厚が閾値Dnm以上であれば、処理室を大気開放してメンテナンスを開始する(ステップS124)。処理室側壁の堆積膜厚が閾値Dnm未満であれば、ステップS121に戻り製品ウエハの処理を継続する。

【実施例4】

【0065】

(第四の実施の形態)

これまで処理装置側壁部の堆積物の除去と堆積の制御の例であるが、更なる応用例としてアンテナ部分の堆積物制御に関して説明する。

【0066】

図13の処理装置は、図2に示したと同様に、第一のガス導入手段208および第二のガス導入手段209と真空排気手段218を有する真空容器201に電磁コイル207が配置されている。上部電極部は、アンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205が配置されている。

【0067】

下部電極部は被処理体202を載置するためのステージ214が設置され、該載置台には被処理体202を吸着するための試料設置電極216が設置され、温調装置217が接続されている。被処理体202のプラズマ処理を行うためにバイアス用電源212、整合器213とブロッキングコンデンサが配置されている。

【0068】

アンテナ部の堆積物のモニタは、処理室内でプラズマが生成している時に、スイッチをバイアス電源側1301に切り替え、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加する。バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。

【0069】

図14は、本発明の第四の実施の形態における処理手順を説明するフローチャートである。最初に図2と同様にアンテナを電源205側に取り付け、量産条件で製品ウエハの処理を行う(ステップS141)。この際アンテナ表面には、デポが堆積する。

【0070】

次に、ダミーウエハを用いて処理室内のO2ガスをベースとしたクリーニングステップを行う。クリーニングステップの放電中にアンテナをバイアス電源側のスイッチ1301に接続する。接続後アンテナにバイアス電力を供給しながらコンデンサ:Cp 222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する。(ステップS142)。

【0071】

第一の実施例と同様に、堆積物は時間とともに除去されるため、各値が一定値に近づく。この各値が一定値になる時間(ステップS143)がクリーニングステップの終了(ステップS144)となる。

【実施例5】

【0072】

(第五の実施の形態)

図15は、エッチング処理で用いることを想定したマイクロ波ECR方式のプラズマ処理装置の形態を示す。

【0073】

この装置は、内壁1501、1511やマイクロ波導入窓1506で覆われた真空処理室1517があり、その外部には3つのソレノイドコイル1512、1513および1514と、鉄製のヨーク1515、1516が設置され、真空処理室1517上部には、マイクロ波を共振させる共振器1505があり、さらに共振器1505上部には、マイクロ波導波管1505、高周波整合器1504、マグネトロン1503が設置されている。

【0074】

真空処理室1517内には、高周波バイアスが印加および温度調整機構がある処理台1508があり、処理台1508表面に形成した静電チャックを介してウエハ1507が固定できるようになっている。ウエハは、搬送ポートのバルブ1510を開閉して搬送される。

【0075】

この装置に、エッチングガスをシャワープレート1502より真空処理室1517に導入し、ガス圧力を調圧バルブ1509で制御する。マグネトロン1503で約2.45GHz高周波を発生させ、高周波マッチング装置1504、導波管1505、空洞共振器1518、マイクロ波導入窓1506を通って真空処理室に導入させる。

【0076】

さらに、ソレノイドコイル1512、1513および1514に直流電流を印加し、真空処理室内の一部が所望の磁場になるようにコイル電流を調整する。導入したガスとマイクロ波およびコイル磁場によりプラズマを生成する。

【0077】

処理室側壁状態をモニタするプローブ基盤は、内壁1501、1511上に複数取り付ける1519a,

1519b,1519c,1519d。プローブ基盤を複数取り付けるのは、高さ方向によって堆積物の膜厚が異なるためモニタする必要が有る。

【0078】

図16は、本発明の第五の実施の形態における処理手順を説明するフローチャートである。最初に処理室側壁部に取り付けた全てのプローブ基盤をコンデンサCw側(スイッチ602)に接地する(ステップS161)。次に量産が開始され、製造ウエハの処理が行われる(ステップS162)。

【0079】

ここで、全てのプローブ基盤にデポは堆積するが、高さ方向でデポの堆積膜厚が異なる。次にプローブ基盤をバイアス電源側(スイッチ604)に接続する(ステップS163)。その後ダミーウエハを用いて処理室内のクリーニングステップを行う。クリーニングステップ中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS164)。

【0080】

第一の実施例と同様に堆積物は時間とともに除去されるため、各値が一定値に近づく。但し、各プローブ基盤の堆積膜厚は異なり、且つクリーニングによるデポの除去率が高さ方向によって異なるためソレノイドコイル1512、1513および1514に直流電流を印加し、真空処理室内の一部が所望の磁場になるようにコイル電流を調整してECR面を制御しながらクリーニングを行う。全てのプローブ基盤の各値が一定値になる時間(ステップ S165)がクリーニングステップの終了(ステップS166)となる。

【実施例6】

【0081】

(第六の実施の形態)

図17は、エッチング処理で用いることを想定したプラズマ処理装置へのプローブ基盤の取りつけ方の一例を示す。この時のプラズマ処理装置は図2の構成であってもいいし、図15の構成でもよい。

【0082】

プローブ基盤1719a,1719b,1719c,1719dの数は2個以上左右(上下)対称に配置する。取り付ける箇所は、処理室側壁であり高さ方向は該載置台上の被処理体より低い部分が望ましい。プローブ基盤を取り付ける箇所の壁材は導体で有ってもいいし絶縁体であってもよい。

【0083】

図18は、本発明の第六の実施の形態における処理手順を説明するフローチャートである。最初に全掃やパーツ交換をしたようなメンテナンスを行う(ステップS181)。ここでのパーツとは処理室内のパーツであり、全掃時に交換するパーツや消耗品パーツであり素材はSi、石英、導体(表面加工されたパーツ含)のリングである。

【0084】

その後、処理室側壁部に取り付けた全てのプローブ基盤をバイアス電源側(スイッチ604)に接地する(ステップS182)。次に、ダミーウエハを用いて量産条件で仮シーズニングの処理を行う。シーズニング処理の放電中にプローブ基盤にバイアス電力を供給しながらコンデンサ:Cp222の放電電圧のモニタを行い、そのモニタ値から飽和イオン電流、Vdc、電子温度を算出する(ステップS183)。

【0085】

次に、算出された各基盤の各値と時間依存による電圧変化の波形を比較する(ステップ S184)。全てのプローブ基盤もしくは対称面同士のプローブ基盤の値が一致したならば、プラズマには偏りが無いことを示している。よって設置したパーツの組み合わせは問題ないと判断され、本シーズニングの処理が行われる(ステップS185)。

【0086】

逆に、全てのプローブ基盤もしくは対称面同士のプローブ基盤の値が一致しないならば、プラズマに偏りがあることからパーツの組み合わせにズレが生じていることになる。そのため再度処理室内のパーツの再組み合わせが必要となる(ステップS186)。パーツを組み合わせた後、(ステップS182)に戻り再度仮シーズニング処理を行い、パーツの組み合わせを確認する。

【実施例7】

【0087】

(第七の実施の形態)

本発明の第七の実施の形態では、処理装置側壁部の堆積物の除去と堆積の制御と、アンテナ部分の堆積物制御が可能である。

【0088】

図19の処理装置は、図13に示したと同様に、第一のガス導入手段208および第二のガス導入手段209と真空排気手段218を有する真空容器201に電磁コイル207が配置されている。上部電極部は、アンテナ210には第一の整合器204を介し200MHzのプラズマ生成用の第一の電源203と、第二の整合器206を介し、13.56MHzの第二の電源205が配置されている。

【0089】

下部電極部は被処理体202を載置するためのステージ214が設置され、該載置台には被処理体202を吸着するための試料設置電極216が設置され、温調装置217が接続されている。被処理体202のプラズマ処理を行うためにバイアス用電源212、整合器213とブロッキングコンデンサが配置されている。

【0090】

アンテナ部の堆積物のモニタは、処理室内でプラズマが生成している時に、スイッチをバイアス電源側1901に切り替え、2MHzのパルスバイアス電源220により10W以下のバイアス電力をパルス化し整合器221を介して印加する。バイアス電力ON時に5nFのコンデンサ:Cp222に負電荷が充電され、OFF時に放電するため、その時間による放電時の電圧をPC(オシロスコープ)223でモニタを行う。時間変化による電圧値からプラズマ中のVdc、飽和イオン電流、電子温度を算出する。

【0091】

また、図19の処理装置は、図15,図17に示したと同様に、処理室側壁状態をモニタする複数のプローブ基盤1919が、内壁201上の異なる位置に複数取り付ける。プローブ基盤を異なる高さに複数取り付けるのは、高さ方向によって堆積物の膜厚が異なるためモニタする必要が有るからである。

【0092】

また、プローブ基盤1919を2個以上、左右(上下)に配置する。取り付ける箇所は、処理室側壁の異なる位置に取り付ける。全てのプローブ基盤にデポは堆積するが、異なる位置と異なる高さ方向でデポの堆積膜厚が異なる場合があるからである。プローブ基盤1919を取り付ける箇所の壁材は導体で有ってもいいし絶縁体であってもよい。

【0093】

以上に記載した本発明方法で半導体装置を製造するプラズマ処理装置のプラズマをモニタするプローブ基盤を用いることにより、処理室内のプラズマ中の飽和イオン電流、Vdc、電子温度の算出が可能となり、そのデータを用いて処理を行うことによりプラズマ処理装置の安定稼動ができる。また、それらの装置を使用することにより安定した半導体装置が製造できる。

【符号の説明】

【0094】

101 導体

102 絶縁被膜

103 ヒータ

104 処理室の内壁

105 絶縁体

106 真空ギャップ

119 プローブ基盤

201 チャンバー(処理容器)

202 被処理体

203 第一の電源

204 第一の整合器

205 第二の電源

206 第二の整合器

207 磁場コイル

208 第一のガス供給手段

209 第二のガス供給手段

210 アンテナ

211 アンテナ裏誘電体

212 バイアス用電源

213 第三の整合器

214 ステージ

215 フォーカスリング

216 試料設置電極

217 温調装置

218 排気手段

219 プローブ基盤

220 パルス電源

221 第四の整合器

222 コンデンサ

223 PC(オシロスコープ)

301 電圧

302 バイアス電力

401 Vdc

402 放電レート(ICF算出)

403 放電レート(電子温度算出)

501 実測値(I−V曲線)

502 予測値(I−V曲線)

601 切り替えスイッチ

602 グランド側

603 コンデンサCw側

604 バイアス電源側

619 プローブ基盤

1301 バイアス電源側スイッチ

1501 上部内壁

1502 シャワープレート

1503 マグネトロン

1504 高周波整合器

1505 導波管

1506 マイクロ波導入窓

1507 ウエハ(被処理体)

1508 処理台

1509 長圧バルブ

1510 搬送ポートバルブ

1511 下部内壁

1512 上ソレノイドコイル

1513 中ソレノイドコイル

1514 下ソレノイドコイル

1515 ヨーク

1516 ヨーク

1517 真空処理室

1518 空洞共振器

1519 プローブ基盤

1719 プローブ基盤

1919 プローブ基盤

【特許請求の範囲】

【請求項1】

処理室と該処理室に処理ガスを供給する手段と、該処理室を減圧する真空排気手段と、被処理体を載置する処理体載置台と、プラズマ生成のための高周波電源とを有するプラズマ処理装置であって、

前記処理室の側壁に1つ以上のプローブ基盤が設置され、前記プローブ基盤の表面は絶縁性の被膜に覆われ、且つ、温度制御が可能となり、前記プローブ基盤の後段は装置内壁被膜の誘電率と同等なコンデンサが設置されている回路と、パルス電源、コンデンサ、及び計測系が設置されている回路とを選択できるスイッチが設置さていることを特徴とするプラズマ処理装置。

【請求項2】

請求項1に記載のプラズマ処理装置において、前記プローブ基盤の後段のパルス電源、コンデンサ、及び計測系が設置されている回路をアンテナに設置していることを特徴とするプラズマ処理装置。

【請求項3】

請求項1又は請求項2に記載のプラズマ処理装置において、前記プローブ基盤を高さ方向に複数取り付けることを特徴とするプラズマ処理装置。

【請求項4】

請求項1ないし請求項3のいずれかの請求項に記載のプラズマ処理装置において、複数の前記プローブ基盤を対称面に取り付けることを特徴とするプラズマ処理装置。

【請求項5】

処理室と該処理室に処理ガスを供給する手段と、該処理室を減圧する真空排気手段と、被処理体を載置する処理体載置台と、プラズマ生成のための高周波電源とを有するプラズマ処理装置を用いた被処理体のプラズマ処理方法であって、

前記処理室の側壁に1つ以上のプローブ基盤が設置され、前記プローブ基盤の表面は絶縁性の被膜に覆われ、且つ、温度制御が可能となり、前記プローブ基盤の後段は装置内壁被膜の誘電率と同等なコンデンサが設置されている回路と、パルス電源、コンデンサ、及び計測系が設置されている回路とを選択できるスイッチが設置され、後者の回路を選択しリアルタイムで計測を行いながらプラズマ処理を行うことを特徴とするプラズマ処理方法。

【請求項6】

請求項5に記載のプラズマ処理方法において、半導体装置の製造時に、処理室内のクリーニングプロセスを制御することを特徴とするプラズマ処理方法。

【請求項7】

請求項5に記載のプラズマ処理方法において、プラズマ装置の側壁に堆積する膜厚を制御することを特徴とするプラズマ処理方法。

【請求項8】

請求項5又は請求項7に記載のプラズマ処理方法において、全掃後のシーズニングの量を制御することを特徴とするプラズマ処理方法。

【請求項9】

請求項5又は請求項7に記載のプラズマ処理方法において、メンテナンスを行うか否かの判断を制御することを特徴とするプラズマ処理方法。

【請求項10】

請求項5に記載のプラズマ処理方法において、プローブ基盤の後段のパルス電源、コンデンサ、及び計測系が設置されている回路をアンテナに設置し、該アンテナのクリーニングを制御することを特徴とするプラズマ処理方法。

【請求項11】

請求項5又は請求項6に記載のプラズマ処理方法において、前記プローブ基盤を高さ方向に複数取り付け、その高さの位置のクリーニングに応じて処理条件を変更しながら制御することを特徴とするプラズマ処理方法。

【請求項12】

請求項5に記載のプラズマ処理方法において、複数の前記プローブ基盤を前記処理室の対称面に取り付け、メンテナンス後の前記処理室内の各装置の組み合わせを確認することを特徴とするプラズマ処理方法。

【請求項1】

処理室と該処理室に処理ガスを供給する手段と、該処理室を減圧する真空排気手段と、被処理体を載置する処理体載置台と、プラズマ生成のための高周波電源とを有するプラズマ処理装置であって、

前記処理室の側壁に1つ以上のプローブ基盤が設置され、前記プローブ基盤の表面は絶縁性の被膜に覆われ、且つ、温度制御が可能となり、前記プローブ基盤の後段は装置内壁被膜の誘電率と同等なコンデンサが設置されている回路と、パルス電源、コンデンサ、及び計測系が設置されている回路とを選択できるスイッチが設置さていることを特徴とするプラズマ処理装置。

【請求項2】

請求項1に記載のプラズマ処理装置において、前記プローブ基盤の後段のパルス電源、コンデンサ、及び計測系が設置されている回路をアンテナに設置していることを特徴とするプラズマ処理装置。

【請求項3】

請求項1又は請求項2に記載のプラズマ処理装置において、前記プローブ基盤を高さ方向に複数取り付けることを特徴とするプラズマ処理装置。

【請求項4】

請求項1ないし請求項3のいずれかの請求項に記載のプラズマ処理装置において、複数の前記プローブ基盤を対称面に取り付けることを特徴とするプラズマ処理装置。

【請求項5】

処理室と該処理室に処理ガスを供給する手段と、該処理室を減圧する真空排気手段と、被処理体を載置する処理体載置台と、プラズマ生成のための高周波電源とを有するプラズマ処理装置を用いた被処理体のプラズマ処理方法であって、

前記処理室の側壁に1つ以上のプローブ基盤が設置され、前記プローブ基盤の表面は絶縁性の被膜に覆われ、且つ、温度制御が可能となり、前記プローブ基盤の後段は装置内壁被膜の誘電率と同等なコンデンサが設置されている回路と、パルス電源、コンデンサ、及び計測系が設置されている回路とを選択できるスイッチが設置され、後者の回路を選択しリアルタイムで計測を行いながらプラズマ処理を行うことを特徴とするプラズマ処理方法。

【請求項6】

請求項5に記載のプラズマ処理方法において、半導体装置の製造時に、処理室内のクリーニングプロセスを制御することを特徴とするプラズマ処理方法。

【請求項7】

請求項5に記載のプラズマ処理方法において、プラズマ装置の側壁に堆積する膜厚を制御することを特徴とするプラズマ処理方法。

【請求項8】

請求項5又は請求項7に記載のプラズマ処理方法において、全掃後のシーズニングの量を制御することを特徴とするプラズマ処理方法。

【請求項9】

請求項5又は請求項7に記載のプラズマ処理方法において、メンテナンスを行うか否かの判断を制御することを特徴とするプラズマ処理方法。

【請求項10】

請求項5に記載のプラズマ処理方法において、プローブ基盤の後段のパルス電源、コンデンサ、及び計測系が設置されている回路をアンテナに設置し、該アンテナのクリーニングを制御することを特徴とするプラズマ処理方法。

【請求項11】

請求項5又は請求項6に記載のプラズマ処理方法において、前記プローブ基盤を高さ方向に複数取り付け、その高さの位置のクリーニングに応じて処理条件を変更しながら制御することを特徴とするプラズマ処理方法。

【請求項12】

請求項5に記載のプラズマ処理方法において、複数の前記プローブ基盤を前記処理室の対称面に取り付け、メンテナンス後の前記処理室内の各装置の組み合わせを確認することを特徴とするプラズマ処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2011−228386(P2011−228386A)

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願番号】特願2010−94923(P2010−94923)

【出願日】平成22年4月16日(2010.4.16)

【出願人】(501387839)株式会社日立ハイテクノロジーズ (4,325)

【Fターム(参考)】

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願日】平成22年4月16日(2010.4.16)

【出願人】(501387839)株式会社日立ハイテクノロジーズ (4,325)

【Fターム(参考)】

[ Back to top ]