半導体装置及びこれを備える半導体システム並びにその動作方法

【課題】内部でデータ基準電圧を生成する半導体装置を提供すること。

【解決手段】本発明の半導体装置は、設定されたデータパターンを有する比較データを外部から印加されて設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分して格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、外部から印加されるレベルテストコードに応答してその電圧レベルが決定されるデータ基準電圧のレベルに基づいて、設定された時間ごとに前記設定されたデータパターンを有する状態で外部から印加されるテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較してテスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、を備える。

【解決手段】本発明の半導体装置は、設定されたデータパターンを有する比較データを外部から印加されて設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分して格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、外部から印加されるレベルテストコードに応答してその電圧レベルが決定されるデータ基準電圧のレベルに基づいて、設定された時間ごとに前記設定されたデータパターンを有する状態で外部から印加されるテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較してテスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体設計技術に関し、具体的には内部でデータ基準電圧を生成する半導体装置及びこれを備える半導体システム並びにその動作方法に関する。

【背景技術】

【0002】

DDR4のような低電力(low power)の高速動作(high speed)半導体装置では、データ入力バッファの基準電圧レベルを定義するためのデータ基準電圧VREF_DQのトレーニング(training)テストを半導体装置の内部で行う。

【0003】

このために、半導体コントローラでは、6ビットのレベルトレーニングコードを半導体装置に伝達し、半導体装置では、6ビットのレベルトレーニングコードに応答して、内部でデータ基準電圧VREF_DQのレベルを調節する方式で生成する。

【0004】

一方、従来では、半導体コントローラからデータ基準電圧VREF_DQを生成して、半導体装置に伝達する方式で動作したので必要なかったが、前記のような構成では、半導体装置の内部で生成されるデータ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間をトレーニングテスト結果が分かるパラメータ(parameter)として外部で測定しなければならない必要性がある。

【0005】

しかしながら、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間をトレーニングテスト結果が分かるパラメータとして直接的に半導体装置の外部で測定するとき、モニターリングパッドと測定装備のキャパシティブ(capacitive)及びローディング(loading)成分により、その正確度に問題が発生する可能性がある。

【0006】

すなわち、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間のようなパラメータは、ナノセカンド(nanosecond)単位のような極めて微細な単位でその正確度が決定されなければならないが、このように微細な単位を半導体装置の外部で正確に測定することはほとんど不可能であるという問題点がある。

【0007】

これによって、半導体装置の内部でデータ基準電圧VREF_DQを正常に生成できない場合にも、これを正確にキャッチ(catch)できないという問題が発生する可能性がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】大韓民国特許出願公開第2010−0076656号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、上述の従来の技術の問題点を解決するために提案されたものであって、その目的は、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを極めて正確に測定できるように動作する半導体装置及びこれを備える半導体システム並びにその動作方法を提供することにある。

【0010】

特に、半導体装置の動作周波数が極めて高い場合にも、安定した測定動作が行われうる半導体装置及びこれを備える半導体システム並びにその動作方法を提供することにその目的がある。

【課題を解決するための手段】

【0011】

上記の目的を達成すべく、本発明の一側面によれば、外部から印加された入力データを、設定された電圧レベル差を有してスイングさせことによって、その論理レベルを区分して比較データとして格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、レベルテストコードに応答して周期的にテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較して、テスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部とを備える半導体装置を提供する。

【0012】

また、上記の目的を達成すべく、本発明の他の側面によれば、テスト準備動作区間の間に設定されたデータパターンを有する比較データとテスト動作区間の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードと前記設定されたデータパターンを有するテストデータとを出力し、半導体装置から出力される信号に応答して、前記レベルテストコードがターゲット値に到達する時間を測定する半導体コントローラと、前記テスト準備動作区間の間に前記比較データの論理レベルを格納した後、前記テスト動作区間の間に前記レベルテストコードに応答して、データ基準電圧のレベルを決定し、前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後、前記比較データの論理レベルと比較して出力信号を生成する半導体装置とを備える半導体システムを提供する。

【0013】

また、上記の目的を達成すべく、本発明のさらに他の側面によれば、半導体コントローラからテスト準備進入コマンド、設定されたデータパターンを有する比較データ、及びテスト準備脱出コマンドを順次に出力し、これを半導体装置から受け取ってテスト準備動作区間に進入した後に前記比較データの論理レベルを調節して格納し、続いてテスト準備動作区間から脱出するステップと、半導体コントローラからテスト進入コマンドを出力し、続いて設定された時間ごとにその値が変動するレベルテストコードと前記設定されたデータパターンを有するテストデータを設定された回数分だけ出力した後に、テスト脱出コマンドを出力するテスト動作ステップと、前記半導体装置から前記テスト進入コマンド及びテスト脱出コマンドにより定義されたテスト動作区間の間に前記レベルテストコード及びテストデータが出力されることに応答して、設定された時間ごとにデータ基準電圧のレベルを決定し、決定されたデータ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後に、前記比較データの論理レベルと比較してテスト動作測定信号を出力するステップと、前記テスト動作測定信号に応答して、半導体コントローラで前記レベルテストコードがターゲット値に到達する時間を測定するステップとを含む半導体システムの動作方法を提供する。

【発明の効果】

【0014】

本発明によれば、内部でデータ基準電圧VREF_DQを生成して、印加されるデータの論理レベルを判断する半導体装置において、データ基準電圧VREF_DQのレベル変動をトレーニングテストした結果を出力パルスのアクティブ区間長に換算して半導体装置の外部に出力できるという効果がある。

【0015】

これによって、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを測定するとき、半導体装置から出力されるパルスのアクティブ区間長を測定すれば良いので、半導体装置の外部で極めて正確に測定できるという効果がある。

【0016】

また、測定動作周波数が高ければ高いほど、より微細な単位で測定動作を行うことができるので、半導体システムの動作周波数が極めて高い場合にも、安定した測定動作が行われうるようにするという効果がある。

【図面の簡単な説明】

【0017】

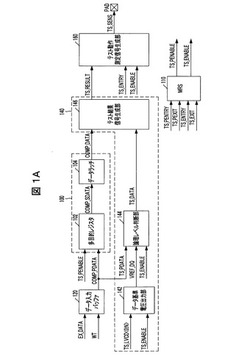

【図1A】本発明の実施の形態に係る半導体装置の構成を示すブロック図である。

【図1B】本発明の実施の形態に係る半導体装置の構成を示すブロック図である。

【図1C】図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト結果信号生成部を詳細に示す回路図である。

【図1D】図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト動作測定信号生成部を詳細に示す回路図である。

【図2】図1A〜図1Dに示す本発明の実施の形態に係る半導体装置の動作を説明するために示すタイミング図である。

【図3A】図1A〜図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【図3B】図1A〜図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【発明を実施するための形態】

【0018】

以下、添付された図面を参照して本発明の好ましい実施の形態を説明する。しかしながら、本発明は、以下で開示される実施の形態に限定されず、互いに異なる様々な形態で構成されることができ、但し本実施の形態は、本発明の開示が完全になるようにし、通常の知識を有した者に本発明の範ちゅうを完全に知らせるために提供されるものである。

【0019】

図1A及び図1Bは、本発明の実施の形態に係る半導体装置の構成を示すブロック図である。図1Cは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト結果信号生成部を詳細に示す回路図である。図1Dは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト動作測定信号生成部を詳細に示す回路図である。

【0020】

図1Aに示すように、本発明の実施の形態に係る半導体装置は、データ格納部100、テスト動作部140、テスト動作測定信号生成部160、データ入力バッファ120、及びモードレジスタセット(Mode Register Set;MRS)110を備えて構成される。

【0021】

モードレジスタセット110は、外部から印加されるテスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITとに応答して、そのアクティブ有無が決定されるテスト準備イネーブル信号TS_PENABLEを生成してテスト準備動作区間を定義し、外部から印加されるテスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITとに応答して、そのアクティブ有無が決定されるテストイネーブル信号TS_ENABLEを生成してテスト動作区間を定義する。

【0022】

データ入力バッファ120は、外部から印加されるデータ入力コマンドWTに応答して、外部から印加されるデータEX_DATAをバッファリングする。このとき、データ入力バッファ120からバッファリングされて出力されるデータは、テスト準備動作区間において比較データCOMP_PDATAとなり、テスト動作区間においてテストデータTS_PDATAとなる。

【0023】

すなわち、比較データCOMP_PDATAと外部から印加されるテストデータTS_PDATAとは、外部から印加される時点がいつなのかによって区分されるだけであり、実際には同じデータパターンを有するデータである。

【0024】

データ格納部100は、設定されたデータパターンを有する比較データCOMP_PDATAを外部から印加されて、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを区分して格納する。

【0025】

さらに詳細に、データ格納部100は、多目的レジスタ102とデータラッチ104とを備えて構成される。

【0026】

多目的レジスタ102は、テスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITにより定義されるテスト準備動作区間(TS_PENABLEのアクティブ区間)において設定されたデータパターンを有する状態で外部から印加される比較データCOMP_PDATAを格納して比較データCOMP_SDATAを出力する。

【0027】

データラッチ104は、多目的レジスタ102に格納された比較データCOMP_SDATAを外部電源電圧VDDレベルと外部接地電圧VSSレベルとの間でスイングする状態でラッチして、その論理レベルを明確に区分する。

【0028】

参考に、比較データは、外部から印加される比較データCOMP_PDATA、多目的レジスタ102に格納される比較データCOMP_SDATA、及びデータラッチ104を介してラッチされた比較データCOMP_DATAに区分されうるが、これは、動作ステップによって信号名を区分するためのもので、その値は同一なので、以下の説明では比較データCOMP_DATAと統一する。また、比較データCOMP_DATAは、複数のビットを含む信号になりうる。

【0029】

そして、テスト動作部140は、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEのアクティブ区間)の間に外部から印加されるレベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが決定されるデータ基準電圧VREF_DQのレベルに基づいて設定された時間ごとに設定されたデータパターンを有する状態でテストデータTS_PDATAの論理レベルを決定し、論理レベルの決定されたテストデータTS_DATAの論理レベルと比較データCOMP_DATAの論理レベルとを比較して、テスト結果信号TS_RESULTを生成する。

【0030】

さらに詳細には、テスト動作部140は、データ基準電圧出力部142、論理レベル判断部144、及びテスト結果信号生成部146を備えて構成される。

【0031】

データ基準電圧出力部142は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に外部から印加されるレベルテストコードTS_LVCD<0:N>に応答して、データ基準電圧VREF_DQのレベルを、外部接地電圧VSSレベルより高い設定可能な最低電圧レベルと外部電源電圧レベルより低い設定可能な最大電圧レベルとの間で可変的に決定する。例えば、レベルテストコードTS_LVCD<0:N>が6ビットコードTS_LVCD<0:5>からなっており、最低値を有する状態TS_LVCD<0:5>=‘000000’であれば、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベルとして設定して生成し、レベルテストコードTS_LVCD<0:5>が最高値を有する状態TS_LVCD<0:5>=‘111111’であれば、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルとして設定して生成し、レベルテストコードTS_LVCD<0:5>が最低値と最高値の中間値を有する状態TS_LVCD<0:5>=‘011111’であれば、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルと最低電圧レベルとの間を半分した電圧レベルを有する状態に設定して生成する。

【0032】

テスト動作部140の構成要素のうち、論理レベル判断部144は、テスト動作区間(TS_ENABLEのアクティブ区間)で設定された時間ごとに印加されるテストデータTS_PDATAの論理レベルをデータ基準電圧VREF_DQのレベルに基づいて判断する。

【0033】

すなわち、論理レベル判断部144では、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより高い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ハイ」(High)に設定し、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより低い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ロー」(Low)に設定する方式で動作する。

【0034】

前述したデータ基準電圧出力部142と論理レベル判断部144の動作を共に述べると、データ基準電圧出力部142は、外部から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するに伴い、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部144は、データ基準電圧VREF_DQの電圧レベルに基づいて外部から印加されるテストデータTS_DATAの論理レベルを判断するようになる。

【0035】

したがって、外部から印加されるテストデータTS_DATAが常に一定の電圧レベルパターンを有する状態であっても、外部から印加されるレベルテストコードTS_LVCD<0:N>の値によって、判断される論理レベルは異なりうる。

【0036】

参考に、テストデータは、外部から印加されるテストデータTS_PDATAと論理レベル判断部144でその論理レベルの決定されたテストデータTS_DATAとに区分されうるが、これは動作ステップによって信号名を区分するためであり、その値は同様なので、以下の説明ではテストデータTS_DATAに統一する。また、テストデータTS_DATAは、複数のビットを含む信号になりうる。

【0037】

そして、テスト結果信号生成部146は、論理レベル判断部144から出力されるテストデータTS_DATAとデータ格納部100に格納されている比較データCOMP_DATAとが互いに同じ論理レベルを有することに対応して、アクティブになるテスト結果信号TS_RESULTを生成する。

【0038】

図1Cを参照すれば、テスト結果信号生成部146の詳細な回路が分かる。すなわち、テスト結果信号生成部146は、テストデータTS_DATAの各ビットTS_DATA<1>、TS_DATA<2>、TS_DATA<3>、TS_DATA<4>、TS_DATA<5>、TS_DATA<6>、TS_DATA<7>、TS_DATA<8>の論理レベルと比較データCOMP_DATAの各ビットCOMP_DATA<1>、COMP_DATA<2>、COMP_DATA<3>、COMP_DATA<4>、COMP_DATA<5>、COMP_DATA<6>、COMP_DATA<7>、COMP_DATA<8>の論理レベルとが完全に一致するとき、非アクティブ状態に初期化されていたテスト結果信号TS_RESULTをアクティブにする。

【0039】

参考に、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAとがそれぞれ8ビットからなる信号であることを例に挙げて示した図に過ぎず、テストデータTS_DATAと比較データCOMP_DATAとが8ビットより多いビット又は8ビットより少ないビットからなる場合に、その回路は変わりうる。

【0040】

また、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAの各ビットを直接比較する方式で示されているが、直接比較する方式でない場合でもテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較できる方式であれば、本発明の範ちゅうに含まれると見なすことができる。例えば、複数のビットからなるテストデータTS_DATAを圧縮した結果と複数のビットからなる比較データCOMP_DATAを圧縮した結果とを比較する方式によりテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較する場合も、本発明の範ちゅうに含まれうる。

【0041】

前述したデータ基準電圧出力部142、論理レベル判断部144及びテスト結果信号生成部146の動作を共に述べると、データ基準電圧出力部142は、外部から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するに伴い、データ基準電圧VREF_DQの電圧レベルも共に変動させ、論理レベル判断部144は、データ基準電圧VREF_DQの電圧レベルに基づいて外部から印加されるテストデータTS_DATAの論理レベルを判断し、テスト結果信号生成部146では、論理レベルの判断されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、両データが同じ論理レベルを有するとき、テスト結果信号TS_RESULTをアクティブにする。

【0042】

このとき、上述のように、データ入力バッファ120を介してテストデータTS_DATAと比較データCOMP_DATAが外部から入力される時には、互いに同じデータパターンを有する。したがって、外部から印加されるテストデータTS_DATAと比較データCOMP_DATAの電圧レベルスイングパターンを単純比較すると、完全に一致する状態になるはずである。

【0043】

しかしながら、比較データCOMP_DATAは、その電圧レベルスイングが電源電圧VDDレベルと接地電圧VSSレベルとの間でなされるために、その論理レベルが正確に判断されうることに対し、テストデータTS_DATAは、レベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが変動するデータ基準電圧VREF_DQのレベルに基づいてその論理レベルが判断されるので、レベルテストコードTS_LVCD<0:N>の値によってその論理レベルの判断が変わりうる。

【0044】

したがって、外部から入力される時には互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに異なる論理レベルを有する場合、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが誤った状態であることを意味する。反対に、外部から入力される時には互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに同じ論理レベルを有する場合、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが正常な状態であることを意味する。

【0045】

すなわち、テスト結果信号生成部146から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが正常なレベルを有する状態を意味する。

【0046】

言い換えれば、テスト結果信号生成部146から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、レベルテストコードTS_LVCD<0:N>が誤った値を有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、レベルテストコードTS_LVCD<0:N>が正常な値を有する状態を意味する。

【0047】

そして、テスト動作測定信号生成部160は、テスト進入コマンドTS_ENTRYに応答してアクティブになり、テスト結果信号TS_RESULTに応答して非アクティブになるテスト動作測定信号TS_SENSを生成する。

【0048】

図1Dを参照すれば、テスト動作測定信号生成部160の詳細な回路構成が分かる。具体的に、テスト動作測定信号生成部160は、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト結果信号TS_RESULTに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになるのを決定するためのPMOSトランジスタP1、P2と、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト進入コマンドTS_ENTRYに応答して、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるのを決定するためのNMOSトランジスタN1、N2とを備えて構成されることが分かる。

【0049】

したがって、テスト動作測定信号生成部160は、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグル(toggle)することに応答して、初期化状態でロジック「ハイ」に非アクティブになっていたテスト動作測定信号TS_SENSをロジック「ロー」(Low)にアクティブにし、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにする。

【0050】

このとき、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態から正常なレベルを有する状態に転換したことを意味する。

【0051】

言い換えれば、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、レベルテストコードTS_LVCD<0:N>が誤った値を有する状態から正常な値を有する状態に転換したことを意味する。

【0052】

そして、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルする時点でテスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるという点を想起してみれば、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになる時点からロジック「ハイ」に非アクティブになる時点までの区間は、レベルテストコードTS_LVCD<0:N>の値及びデータ基準電圧VREF_DQのレベルをトレーニングテストする区間という意味を有するようになる。

【0053】

このとき、レベルテストコードTS_LVCD<0:N>の値をトレーニングテストするということは、レベルテストコードTS_LVCD<0:N>の値を設定可能な特定範囲の値内で順次に変動させながら、どのような値を有する場合が正常な値を有する状態になるかが分かるための目的でテストを行うということを意味する。

【0054】

同様に、データ基準電圧VREF_DQのレベルをトレーニングテストするということは、データ基準電圧VREF_DQのレベルを設定可能な特定範囲の電圧レベル内で順次に変動させながら、どのような電圧レベルを有する場合が正常な電圧レベルを有する状態になるかが分かるための目的でテストを行うということを意味する。

【0055】

結論的に、テスト動作測定信号生成部160から生成されるテスト動作測定信号TS_SENSのアクティブ区間長は、トレーニングテスト動作を介してデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するのにかかる時間と同じパラメータになりうる。

【0056】

そして、テスト動作測定信号TS_SENSの長さを測定する方法は、以下のような2種類の方式を例に挙げることができる。

【0057】

まず、テスト動作測定信号TS_SENSを、図1Aに示すように設定された出力パッド(PAD)を介して外部に直に出力する方式がありうる。このとき、外部では特定テスト装備によりテスト動作測定信号TS_SENSの長さを測定する。

【0058】

そして、図1Bに示すように、アクティブ区間カウンタ190を介してテスト動作測定信号TS_SENSのアクティブ区間の間のソースクロックCLKのトグル回数をカウントした後、カウントした値を設定された出力パッド(PAD)を介して外部に出力する方式がありうる。このとき、外部ではカウントした値を介してテスト動作測定信号TS_SENSの長さを演算する。

【0059】

図2は、図1A〜図1Dに示す本発明の実施の形態に係る半導体装置の動作を説明するために示すタイミング図である。

【0060】

図2に示すように、図1A〜図1Dに示す本発明の実施の形態に係る半導体装置は、テスト準備進入コマンドTS_PENTRYがトグルすることに応答して、テスト準備動作区間(TS_PENABLEがアクティブになる区間)に進入し、テスト準備脱出コマンドTS_PEXITがトグルすることに応答して、テスト準備動作区間(TS_PENABLEがアクティブになる区間)から脱出する。

【0061】

このように、テスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITにより定義されるテスト準備動作区間(TS_PENABLEがアクティブになる区間)においてデータ入力コマンドWTがトグルすることに応答して、比較データCOMP_DATAがデータ入力バッファ120を介して印加される。

【0062】

そして、テスト進入コマンドTS_ENTRYがトグルすることに応答して、テスト動作区間(TS_ENABLEがアクティブになる区間)に進入し、テスト脱出コマンドTS_EXITがトグルすることに応答して、テスト動作区間(TS_ENABLEがアクティブになる区間)から脱出する。

【0063】

このように、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEがアクティブになる区間)において設定された時間ごとにデータ入力コマンドWTがトグルすることに応答して、テストデータTS_DATAがデータ入力バッファ120を介して印加される。

【0064】

また、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEがアクティブになる区間)においてデータ基準電圧VREF_DQのレベルが上昇する。すなわち、直接的に示されていないが、レベルテストコードTS_LVCD<0:N>値が最低値からターゲット値に向けて順次増加することによって、データ基準電圧VREF_DQのレベルも、設定された最低レベルからターゲットレベルに向けて上昇するようになる。

【0065】

また、データ基準電圧VREF_DQのレベルに基づいてテストデータTS_DATAの論理レベルを判断するようになるが、データ基準電圧VREF_DQのレベルが設定可能な最低レベルに近い状態では、テストデータTS_DATAの論理レベルを正常に判断できない。しかしながら、データ基準電圧VREF_DQのレベルが上昇し続けながらターゲットレベルに近づくことによって、ますますテストデータTS_DATAの論理レベルを正常に判断できるようになり、ターゲットレベルに到達すると、すべてのテストデータTS_DATAの論理レベルを正確に判断できるようになる。

【0066】

一方、テスト動作測定信号TS_SENSは、リセット信号RESETに応答してロジック「ハイ」に初期化された後、テスト進入コマンドTS_ENTRYに応答してロジック「ロー」にアクティブになる。すなわち、データ基準電圧VREF_DQのレベルが増加し始める時点と同じ時点でテスト進入コマンドTS_ENTRYがロジック「ロー」にアクティブになる。

【0067】

以後、データ基準電圧VREF_DQのレベルが十分に増加してターゲットレベルに到達することに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになる。すなわち、データ基準電圧VREF_DQのレベルがターゲットレベルに到達してテストデータTS_DATAの論理レベルを正常に判断する時点以後になって、テストデータTS_DATAと比較データCOMP_DATAとが互いに同じ論理レベルを有する状態になる時に、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになる。

【0068】

したがって、テスト動作測定信号TS_SENSのアクティブ区間は、データ基準電圧VREF_DQのレベルが変動する時点からデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでの区間になることが分かる。

【0069】

言い換えれば、テスト動作測定信号TS_SENSのアクティブ区間は、レベルテストコードTS_LVCD<0:N>の値が変動する時点からレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するまでの区間になることが分かる。

【0070】

参考に、図示のテスト動作測定信号TS_SENSのアクティブ区間長がA区間とB区間とに分けられることが分かる。ここで、B区間は、データ入力コマンドWTが印加されることに応答して、テストデータTS_DATAが実際入力されるまでかかる遅延量を表現したことであり、予め計算できる値である。

【0071】

そのため、正確に述べると、データ基準電圧VREF_DQのレベルが変動する時点からデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでの実際区間は、テスト動作測定信号TS_SENSのアクティブ区間長からB区間に該当する長さ分だけを引いた区間になる。

【0072】

言い換えれば、テスト動作測定信号TS_SENSのアクティブ区間は、レベルテストコードTS_LVCD<0:N>の値が変動する時点からレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するまでの実際区間であって、テスト動作測定信号TS_SENSのアクティブ区間長からB区間に該当する長さ分だけを引いた区間になる。

【0073】

図3A及び図3Bは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【0074】

図3Aに示すように、本発明の実施の形態に係る半導体システムは、半導体コントローラ300及び半導体装置320を備えて構成される。ここで、半導体コントローラ300は、データ生成部302、コマンド生成部304、コード生成部306、及び測定部308を備えて構成される。そして、半導体装置320は、データ格納部321、テスト動作部324、テスト動作測定信号生成部326、データ入力バッファ322、及びモードレジスタセット323を備えて構成される。

【0075】

半導体コントローラ300は、テスト準備動作区間(TS_PENABLEがアクティブになる区間)の間に設定されたデータパターンを有する比較データCOMP_DATAを出力し、テスト動作区間(TS_ENABLEがアクティブになる区間)の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードTS_LVCD<0:N>と設定されたデータパターンを有するテストデータTS_DATAとを出力し、半導体装置320から出力される信号TS_SENSに応答して、レベルテストコードTS_LVCD<0:N>がターゲット値に到達する時間を測定する。

【0076】

半導体コントローラ300のコマンド生成部304からテスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITとを生成して半導体装置320に伝達すると、半導体装置320に備えられたモードレジスタセット323でそれに応答して、テスト準備イネーブル信号TS_PENABLEのアクティブ有無を決定することによって、テスト準備動作区間を定義するようになる。

【0077】

同様に、半導体コントローラ300のコマンド生成部304からテスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITとを生成して半導体装置320に伝達すると、半導体装置320に備えられたモードレジスタセット323でそれに応答して、テストイネーブル信号TS_ENABLEのアクティブ有無を決定することによって、テスト動作区間を定義するようになる。

【0078】

また、半導体コントローラ300のコマンド生成部304からデータ入力コマンドWTを半導体装置320に伝達しながらデータ生成部302から生成されたデータEX_DATAを半導体装置320に伝達すると、半導体装置320のデータ入力バッファ322でこれを受け取ってバッファリングする。このとき、半導体装置320のデータ入力バッファ322でバッファリングされて出力されるデータは、テスト準備動作区間(TS_PENABLEがアクティブになる区間)において比較データCOMP_PDATAとなり、テスト動作区間(TS_ENABLEがアクティブになる区間)においてテストデータTS_PDATAとなる。すなわち、半導体コントローラ300から印加される比較データCOMP_PDATAと半導体コントローラ300から印加されるテストデータTS_PDATAとは、半導体コントローラ300から印加される時点がいつなのかによって区分されるだけであり、実際には同じデータパターンを有するデータである。

【0079】

半導体コントローラ300のコード生成部306は、レベルテストコードTS_LVCD<0:N>を生成して半導体装置320に伝達するが、このとき、その値を変動させる方式には、以下のような例がある。

【0080】

まず、半導体コントローラ300のコード生成部306でレベルテストコードTS_LVCD<0:N>を最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させて半導体装置320に伝達できる。このような場合に、半導体装置320のデータ基準電圧出力部3242では、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベル(外部接地電圧VSSレベルより高い)からターゲット電圧レベル(外部電源電圧VDDレベルより低い)まで変動させるようになる。

【0081】

また、半導体コントローラ300のコード生成部306でレベルテストコードTS_LVCD<0:N>を最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させて半導体装置320に伝達できる。このような場合に、半導体装置320のデータ基準電圧出力部3242では、データ基準電圧VREF_DQのレベルを設定可能な最大電圧レベル(外部電源電圧VDDレベルより低い)からターゲット電圧レベル(外部接地電圧VSSレベルより高い)まで変動させるようになる。

【0082】

半導体コントローラ300の測定部308は、コマンド生成部304から生成されるテスト進入コマンドTS_ENTRYと半導体装置320から出力されるテスト動作測定信号TS_SENSとに応答して、レベルテストコードTS_LVCD<0:N>が最小値又は最大値からターゲット値まで到達するのにかかる時間を測定できる。その測定方法は、例えば動作クロックのトグルに基づいて測定するか、又は動作クロックよりより速い周波数を有する任意のクロックを生成して、そのトグルに基づいて測定するようになる。

【0083】

半導体装置320のデータ格納部321は、テスト準備動作区間(TS_PENABLEがアクティブになる区間)において半導体コントローラ300から比較データCOMP_DATAを印加されて、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分し格納する。

【0084】

ここで、データ格納部321は、多目的レジスタ3212とデータラッチ3214とを備えて構成される。

【0085】

半導体装置320のデータ格納部321の構成要素のうち、多目的レジスタ3212は、テスト準備動作区間(TS_PENABLEのアクティブ区間)において半導体コントローラ300から印加される比較データCOMP_PDATAを格納する。

【0086】

半導体装置320のデータ格納部321の構成要素のうち、データラッチ3214は、多目的レジスタ3212に格納されたデータを外部電源電圧VDDレベルと外部接地電圧VSSレベルとの間でスイングする状態でラッチして、その論理レベルを明確に区分する。

【0087】

参考に、比較データは、半導体コントローラ300から印加される比較データCOMP_PDATA、半導体装置320の多目的レジスタ3212に格納される比較データCOMP_SDATA、及び半導体装置320のデータラッチ3214を介してラッチされた比較データCOMP_DATAに区分されうるが、これは、動作ステップによって信号名を区分するためであり、その値は同一なので、以下の説明では比較データCOMP_DATAに統一する。また、比較データCOMP_DATAは、複数のビットを含む信号になりうる。

【0088】

半導体装置320のテスト動作部324は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>に応答して、その電圧レベルが決定されるデータ基準電圧VREF_DQのレベルに基づいて設定された時間ごとに外部から印加されるテストデータTS_PDATAの論理レベルを決定し、論理レベルの決定されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、テスト結果信号TS_RESULTを生成する。

【0089】

テスト動作部324は、データ基準電圧出力部3242、論理レベル判断部3244、及びテスト結果信号生成部3246を備えて構成される。

【0090】

半導体装置320のテスト動作部324の構成要素のうち、データ基準電圧出力部3242は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>に応答して、データ基準電圧VREF_DQのレベルを外部接地電圧VSSレベルより高い設定可能な最低電圧レベルと外部電源電圧VDDレベルより低い設定可能な最大電圧レベルとの間で決定する。例えば、レベルテストコードTS_LVCD<0:N>が6ビットコードTS_LVCD<0:5>からなっており、最低値を有する状態TS_LVCD<0:5>=‘000000’であると、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベルに設定して生成し、レベルテストコードTS_LVCD<0:5>が最高値を有する状態TS_LVCD<0:5>=‘111111’であると、データ基準電圧VREF_DQのレベルを設定可能な最高電圧電圧レベルに設定して生成し、レベルテストコードTS_LVCD<0:5>が最低値と最高値の中間値を有する状態TS_LVCD<0:5>=‘011111’であると、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルと最低電圧レベルとの間を半分した電圧レベルを有する状態に設定して生成する。

【0091】

半導体装置320のテスト動作部324の構成要素のうち、論理レベル判断部3244は、テスト動作区間(TS_ENABLEのアクティブ区間)において設定された時間ごとに印加されるテストデータTS_PDATAの論理レベルをデータ基準電圧VREF_DQのレベルに基づいて判断する。

【0092】

すなわち、論理レベル判断部3244では、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより高い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ハイ」に設定し、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより低い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ロー」に設定する方式で動作する。

【0093】

前述した半導体装置320のデータ基準電圧出力部3242と論理レベル判断部3244の動作を共に述べると、データ基準電圧出力部3242は、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するにつれて、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部3244は、データ基準電圧VREF_DQの電圧レベルに基づいて半導体コントローラ300から印加されるテストデータTS_DATAの論理レベルを判断するようになる。

【0094】

したがって、半導体コントローラ300から印加されるテストデータTS_DATAが常に一定の電圧レベルパターンを有する状態であっても、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>の値によって、判断される論理レベルは異なりうる。

【0095】

参考に、テストデータは、半導体コントローラ300から印加されるテストデータTS_PDATAと論理レベル判断部3244でその論理レベルの決定されたテストデータTS_DATAとに区分されうるが、これは、動作ステップによって信号名を区分するためであり、その値は同様なので、以下の説明では、テストデータTS_DATAに統一する。また、テストデータTS_DATAは、複数のビットを含む信号になりうる。

【0096】

半導体装置320のテスト結果信号生成部3246は、論理レベル判断部3244から出力されるテストデータTS_DATAとデータ格納部321に格納されている比較データCOMP_DATAとが互いに同じ論理レベルを有することに対応して、アクティブになるテスト結果信号TS_RESULTを生成する。参考に、図1Cを参照すれば、テスト結果信号生成部3246の詳細な回路が分かる。すなわち、テスト結果信号生成部3246は、テストデータTS_DATAの各ビットTS_DATA<1>、TS_DATA<2>、TS_DATA<3>、TS_DATA<4>、TS_DATA<5>、TS_DATA<6>、TS_DATA<7>、TS_DATA<8>と比較データCOMP_DATAの各ビットCOMP_DATA<1>、COMP_DATA<2>、COMP_DATA<3>、COMP_DATA<4>、COMP_DATA<5>、COMP_DATA<6>、COMP_DATA<7>、COMP_DATA<8>の論理レベルが完全に一致する時に、非アクティブ状態に初期化されていたテスト結果信号TS_RESULTをアクティブにする。

【0097】

参考に、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAとがそれぞれ8ビットからなる信号であることを例に挙げて示した図であり、テストデータTS_DATAと比較データCOMP_DATAとが8ビットより多いビット又は8ビットより少ないビットからなる場合に、その回路が変わりうる。

【0098】

また、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAの各ビットを直接比較する方式で示されたが、直接比較する方式でない場合でもテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較できる方式であると、本発明の範ちゅうに含まれると見なすことができる。例えば、複数のビットからなるテストデータTS_DATAを圧縮した結果と複数のビットからなる比較データCOMP_DATAを圧縮した結果とを比較する方式により、テストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較する場合も、本発明の範ちゅうに含まれうる。

【0099】

前述したデータ基準電圧出力部3242、論理レベル判断部3244、及びテスト結果信号生成部3246の動作を共に述べると、データ基準電圧出力部3242は、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するにつれて、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部3244は、データ基準電圧VREF_DQの電圧レベルに基づいて半導体コントローラ300から印加されるテストデータTS_DATAの論理レベルを判断するようになり、テスト結果信号生成部3246では、論理レベルの判断されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、両データが同じ論理レベルを有する時にテスト結果信号TS_RESULTをアクティブにする。

【0100】

このとき、上述したように、データ入力バッファ322を介してテストデータTS_DATAと比較データCOMP_DATAとが半導体コントローラ300から入力される時には、互いに同じデータパターンを有する。したがって、半導体コントローラ300から印加されるテストデータTS_DATAと比較データCOMP_DATAの電圧レベルスイングパターンを単純比較すると、完全に一致する状態になるはずである。

【0101】

しかしながら、比較データCOMP_DATAは、その電圧レベルスイングが電源電圧VDDレベルと接地電圧VSSレベルとの間でなされるために、その論理レベルが正確に判断されうることに対し、テストデータTS_DATAは、レベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが変動するデータ基準電圧VREF_DQのレベルに基づいてその論理レベルが判断されるので、レベルテストコードTS_LVCD<0:N>の値によって、その論理レベルの判断が変わりうる。

【0102】

したがって、半導体コントローラ300から入力される時には、互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに異なる論理レベルを有する場合であると、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが誤った状態であることを意味する。反対に、半導体コントローラ300から入力される時には、互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに同じ論理レベルを有する場合であると、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが正常な状態であることを意味する。

【0103】

すなわち、半導体装置320のテスト結果信号生成部3246から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが正常なレベルを有する状態を意味する。

【0104】

そして、半導体装置320のテスト動作測定信号生成部326は、テスト進入コマンドTS_ENTRYに応答してアクティブになり、テスト結果信号TS_RESULTに応答して非アクティブになるテスト動作測定信号TS_SENSを生成する。

【0105】

図1Dを参照すれば、テスト動作測定信号生成部326の詳細な回路構成が分かる。具体的に、テスト動作測定信号生成部326は、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト結果信号TS_RESULTに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになるのを決定するためのPMOSトランジスタP1、P2と、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト進入コマンドTS_ENTRYに応答して、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるのを決定するためのNMOSトランジスタN1、N2を備えて構成されることが分かる。

【0106】

したがって、テスト動作測定信号生成部326は、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルすることに応答して、初期化状態でロジック「ハイ」に非アクティブになっていたテスト動作測定信号TS_SENSをロジック「ロー」にアクティブにし、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにする。

【0107】

このとき、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態から正常なレベルを有する状態に転換したことを意味する。

【0108】

そして、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルする時点でテスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるという点を想起してみれば、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになる時点からロジック「ハイ」非アクティブになる時点までの区間は、レベルテストコードTS_LVCD<0:N>の値及びデータ基準電圧VREF_DQのレベルをトレーニングテストする区間という意味を有するようになる。

【0109】

このとき、レベルテストコードTS_LVCD<0:N>の値をトレーニングテストするということは、レベルテストコードTS_LVCD<0:N>の値を設定可能な特定範囲の値内で順次に変動させながら、どのような値を有する時が正常な値を有する状態になるかが分かるための目的でテストを行うことを意味する。

【0110】

同様に、データ基準電圧VREF_DQのレベルをトレーニングテストするということは、データ基準電圧VREF_DQのレベルを設定可能な特定範囲の電圧レベル内で順次変動させながら、どのような電圧レベルを有する時が正常な電圧レベルを有する状態になるかが分かるための目的でテストを行うことを意味する。

【0111】

結論的に、テスト動作測定信号生成部326から生成されるテスト動作測定信号TS_SENSのアクティブ区間長は、トレーニングテスト動作を介してデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するのにかかる時間と同じパラメータになりうる。

【0112】

そして、図3Bに示す半導体システムの構成と図3Aに示す半導体システムの構成はほとんど一致する。ただし、半導体装置320にアクティブ区間カウンタ329がさらに備えられ、半導体コントローラ300には測定部308がなくなる代わりにカウント−時間テーブル309が備えられる構成であることが分かる。

【0113】

具体的に、半導体装置320のアクティブ区間カウンタ329は、テスト動作測定信号生成部326から生成されるテスト動作測定信号TS_SENSのアクティブ区間の間にソースクロックCLKのトグル回数をカウントした後、カウントした値TS_CNTを設定された出力パッド(PAD)を介して半導体コントローラ300に出力する。

【0114】

そして、半導体コントローラ300のカウント−時間テーブル309には、半導体装置320から伝達されるカウント値TS_CNTごとにレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するのにかかる時間が予め測定されて格納されており、半導体装置320からカウント値TS_CNTが伝達されると、直ちにレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するのにかかる時間を演算できる。

【0115】

以上述べたように、本発明の実施の形態を適用すれば、内部でデータ基準電圧VREF_DQを生成して印加されるデータの論理レベルを判断する半導体装置において、データ基準電圧VREF_DQのレベル変動をトレーニングテストした結果を出力パルスのアクティブ区間長に換算して半導体装置の外部に出力できる。

【0116】

すなわち、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを半導体装置の外部で測定する時に半導体装置から出力されるパルスのアクティブ区間長を測定しさえすればよいので、測定結果がモニターリングパッドと測定装備のキャパシティブ及びローディング成分に影響を受けないようになる。

【0117】

したがって、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを半導体装置の外部で極めて正確に測定できる。

【0118】

また、半導体装置から出力されるパルスのアクティブ区間長を測定するとき、測定動作周波数が高ければ高いほど、より微細な単位まで測定可能なので、半導体システムの動作周波数が極めて高い場合にも安定した測定動作が行われうる。

【0119】

以上説明した本発明は、上記の実施の形態及び添付された図面により限定されるものではなく、本発明に係る技術的思想から逸脱しない範囲内で様々な変更が可能であり、それらも本発明の技術的範囲に属する。

【0120】

例えば、前述した実施の形態において例示した論理ゲート及びトランジスタは、入力される信号の極性によってその位置及び種類が異なるように具現化されなければならない。

【符号の説明】

【0121】

300 半導体コントローラ

320 半導体装置

120、322 データ入力バッファ

100、321 データ格納部

140、324 テスト動作部

160、326 テスト動作測定信号生成部

110、323 モードレジスタセット、MRS

102、3212 多目的レジスタ

104、3214 データラッチ

142、3242 データ基準電圧出力部

144、3244 論理レベル判断部

146、3246 テスト結果信号生成部

190、329 アクティブ区間カウンタ

302 データ生成部

304 コマンド生成部

306 コード生成部

308 測定部

309 カウント−時間テーブル

【技術分野】

【0001】

本発明は、半導体設計技術に関し、具体的には内部でデータ基準電圧を生成する半導体装置及びこれを備える半導体システム並びにその動作方法に関する。

【背景技術】

【0002】

DDR4のような低電力(low power)の高速動作(high speed)半導体装置では、データ入力バッファの基準電圧レベルを定義するためのデータ基準電圧VREF_DQのトレーニング(training)テストを半導体装置の内部で行う。

【0003】

このために、半導体コントローラでは、6ビットのレベルトレーニングコードを半導体装置に伝達し、半導体装置では、6ビットのレベルトレーニングコードに応答して、内部でデータ基準電圧VREF_DQのレベルを調節する方式で生成する。

【0004】

一方、従来では、半導体コントローラからデータ基準電圧VREF_DQを生成して、半導体装置に伝達する方式で動作したので必要なかったが、前記のような構成では、半導体装置の内部で生成されるデータ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間をトレーニングテスト結果が分かるパラメータ(parameter)として外部で測定しなければならない必要性がある。

【0005】

しかしながら、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間をトレーニングテスト結果が分かるパラメータとして直接的に半導体装置の外部で測定するとき、モニターリングパッドと測定装備のキャパシティブ(capacitive)及びローディング(loading)成分により、その正確度に問題が発生する可能性がある。

【0006】

すなわち、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間のようなパラメータは、ナノセカンド(nanosecond)単位のような極めて微細な単位でその正確度が決定されなければならないが、このように微細な単位を半導体装置の外部で正確に測定することはほとんど不可能であるという問題点がある。

【0007】

これによって、半導体装置の内部でデータ基準電圧VREF_DQを正常に生成できない場合にも、これを正確にキャッチ(catch)できないという問題が発生する可能性がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】大韓民国特許出願公開第2010−0076656号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、上述の従来の技術の問題点を解決するために提案されたものであって、その目的は、データ基準電圧VREF_DQがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを極めて正確に測定できるように動作する半導体装置及びこれを備える半導体システム並びにその動作方法を提供することにある。

【0010】

特に、半導体装置の動作周波数が極めて高い場合にも、安定した測定動作が行われうる半導体装置及びこれを備える半導体システム並びにその動作方法を提供することにその目的がある。

【課題を解決するための手段】

【0011】

上記の目的を達成すべく、本発明の一側面によれば、外部から印加された入力データを、設定された電圧レベル差を有してスイングさせことによって、その論理レベルを区分して比較データとして格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、レベルテストコードに応答して周期的にテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較して、テスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部とを備える半導体装置を提供する。

【0012】

また、上記の目的を達成すべく、本発明の他の側面によれば、テスト準備動作区間の間に設定されたデータパターンを有する比較データとテスト動作区間の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードと前記設定されたデータパターンを有するテストデータとを出力し、半導体装置から出力される信号に応答して、前記レベルテストコードがターゲット値に到達する時間を測定する半導体コントローラと、前記テスト準備動作区間の間に前記比較データの論理レベルを格納した後、前記テスト動作区間の間に前記レベルテストコードに応答して、データ基準電圧のレベルを決定し、前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後、前記比較データの論理レベルと比較して出力信号を生成する半導体装置とを備える半導体システムを提供する。

【0013】

また、上記の目的を達成すべく、本発明のさらに他の側面によれば、半導体コントローラからテスト準備進入コマンド、設定されたデータパターンを有する比較データ、及びテスト準備脱出コマンドを順次に出力し、これを半導体装置から受け取ってテスト準備動作区間に進入した後に前記比較データの論理レベルを調節して格納し、続いてテスト準備動作区間から脱出するステップと、半導体コントローラからテスト進入コマンドを出力し、続いて設定された時間ごとにその値が変動するレベルテストコードと前記設定されたデータパターンを有するテストデータを設定された回数分だけ出力した後に、テスト脱出コマンドを出力するテスト動作ステップと、前記半導体装置から前記テスト進入コマンド及びテスト脱出コマンドにより定義されたテスト動作区間の間に前記レベルテストコード及びテストデータが出力されることに応答して、設定された時間ごとにデータ基準電圧のレベルを決定し、決定されたデータ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後に、前記比較データの論理レベルと比較してテスト動作測定信号を出力するステップと、前記テスト動作測定信号に応答して、半導体コントローラで前記レベルテストコードがターゲット値に到達する時間を測定するステップとを含む半導体システムの動作方法を提供する。

【発明の効果】

【0014】

本発明によれば、内部でデータ基準電圧VREF_DQを生成して、印加されるデータの論理レベルを判断する半導体装置において、データ基準電圧VREF_DQのレベル変動をトレーニングテストした結果を出力パルスのアクティブ区間長に換算して半導体装置の外部に出力できるという効果がある。

【0015】

これによって、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを測定するとき、半導体装置から出力されるパルスのアクティブ区間長を測定すれば良いので、半導体装置の外部で極めて正確に測定できるという効果がある。

【0016】

また、測定動作周波数が高ければ高いほど、より微細な単位で測定動作を行うことができるので、半導体システムの動作周波数が極めて高い場合にも、安定した測定動作が行われうるようにするという効果がある。

【図面の簡単な説明】

【0017】

【図1A】本発明の実施の形態に係る半導体装置の構成を示すブロック図である。

【図1B】本発明の実施の形態に係る半導体装置の構成を示すブロック図である。

【図1C】図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト結果信号生成部を詳細に示す回路図である。

【図1D】図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト動作測定信号生成部を詳細に示す回路図である。

【図2】図1A〜図1Dに示す本発明の実施の形態に係る半導体装置の動作を説明するために示すタイミング図である。

【図3A】図1A〜図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【図3B】図1A〜図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【発明を実施するための形態】

【0018】

以下、添付された図面を参照して本発明の好ましい実施の形態を説明する。しかしながら、本発明は、以下で開示される実施の形態に限定されず、互いに異なる様々な形態で構成されることができ、但し本実施の形態は、本発明の開示が完全になるようにし、通常の知識を有した者に本発明の範ちゅうを完全に知らせるために提供されるものである。

【0019】

図1A及び図1Bは、本発明の実施の形態に係る半導体装置の構成を示すブロック図である。図1Cは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト結果信号生成部を詳細に示す回路図である。図1Dは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置の構成要素のうち、テスト動作測定信号生成部を詳細に示す回路図である。

【0020】

図1Aに示すように、本発明の実施の形態に係る半導体装置は、データ格納部100、テスト動作部140、テスト動作測定信号生成部160、データ入力バッファ120、及びモードレジスタセット(Mode Register Set;MRS)110を備えて構成される。

【0021】

モードレジスタセット110は、外部から印加されるテスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITとに応答して、そのアクティブ有無が決定されるテスト準備イネーブル信号TS_PENABLEを生成してテスト準備動作区間を定義し、外部から印加されるテスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITとに応答して、そのアクティブ有無が決定されるテストイネーブル信号TS_ENABLEを生成してテスト動作区間を定義する。

【0022】

データ入力バッファ120は、外部から印加されるデータ入力コマンドWTに応答して、外部から印加されるデータEX_DATAをバッファリングする。このとき、データ入力バッファ120からバッファリングされて出力されるデータは、テスト準備動作区間において比較データCOMP_PDATAとなり、テスト動作区間においてテストデータTS_PDATAとなる。

【0023】

すなわち、比較データCOMP_PDATAと外部から印加されるテストデータTS_PDATAとは、外部から印加される時点がいつなのかによって区分されるだけであり、実際には同じデータパターンを有するデータである。

【0024】

データ格納部100は、設定されたデータパターンを有する比較データCOMP_PDATAを外部から印加されて、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを区分して格納する。

【0025】

さらに詳細に、データ格納部100は、多目的レジスタ102とデータラッチ104とを備えて構成される。

【0026】

多目的レジスタ102は、テスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITにより定義されるテスト準備動作区間(TS_PENABLEのアクティブ区間)において設定されたデータパターンを有する状態で外部から印加される比較データCOMP_PDATAを格納して比較データCOMP_SDATAを出力する。

【0027】

データラッチ104は、多目的レジスタ102に格納された比較データCOMP_SDATAを外部電源電圧VDDレベルと外部接地電圧VSSレベルとの間でスイングする状態でラッチして、その論理レベルを明確に区分する。

【0028】

参考に、比較データは、外部から印加される比較データCOMP_PDATA、多目的レジスタ102に格納される比較データCOMP_SDATA、及びデータラッチ104を介してラッチされた比較データCOMP_DATAに区分されうるが、これは、動作ステップによって信号名を区分するためのもので、その値は同一なので、以下の説明では比較データCOMP_DATAと統一する。また、比較データCOMP_DATAは、複数のビットを含む信号になりうる。

【0029】

そして、テスト動作部140は、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEのアクティブ区間)の間に外部から印加されるレベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが決定されるデータ基準電圧VREF_DQのレベルに基づいて設定された時間ごとに設定されたデータパターンを有する状態でテストデータTS_PDATAの論理レベルを決定し、論理レベルの決定されたテストデータTS_DATAの論理レベルと比較データCOMP_DATAの論理レベルとを比較して、テスト結果信号TS_RESULTを生成する。

【0030】

さらに詳細には、テスト動作部140は、データ基準電圧出力部142、論理レベル判断部144、及びテスト結果信号生成部146を備えて構成される。

【0031】

データ基準電圧出力部142は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に外部から印加されるレベルテストコードTS_LVCD<0:N>に応答して、データ基準電圧VREF_DQのレベルを、外部接地電圧VSSレベルより高い設定可能な最低電圧レベルと外部電源電圧レベルより低い設定可能な最大電圧レベルとの間で可変的に決定する。例えば、レベルテストコードTS_LVCD<0:N>が6ビットコードTS_LVCD<0:5>からなっており、最低値を有する状態TS_LVCD<0:5>=‘000000’であれば、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベルとして設定して生成し、レベルテストコードTS_LVCD<0:5>が最高値を有する状態TS_LVCD<0:5>=‘111111’であれば、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルとして設定して生成し、レベルテストコードTS_LVCD<0:5>が最低値と最高値の中間値を有する状態TS_LVCD<0:5>=‘011111’であれば、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルと最低電圧レベルとの間を半分した電圧レベルを有する状態に設定して生成する。

【0032】

テスト動作部140の構成要素のうち、論理レベル判断部144は、テスト動作区間(TS_ENABLEのアクティブ区間)で設定された時間ごとに印加されるテストデータTS_PDATAの論理レベルをデータ基準電圧VREF_DQのレベルに基づいて判断する。

【0033】

すなわち、論理レベル判断部144では、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより高い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ハイ」(High)に設定し、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより低い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ロー」(Low)に設定する方式で動作する。

【0034】

前述したデータ基準電圧出力部142と論理レベル判断部144の動作を共に述べると、データ基準電圧出力部142は、外部から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するに伴い、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部144は、データ基準電圧VREF_DQの電圧レベルに基づいて外部から印加されるテストデータTS_DATAの論理レベルを判断するようになる。

【0035】

したがって、外部から印加されるテストデータTS_DATAが常に一定の電圧レベルパターンを有する状態であっても、外部から印加されるレベルテストコードTS_LVCD<0:N>の値によって、判断される論理レベルは異なりうる。

【0036】

参考に、テストデータは、外部から印加されるテストデータTS_PDATAと論理レベル判断部144でその論理レベルの決定されたテストデータTS_DATAとに区分されうるが、これは動作ステップによって信号名を区分するためであり、その値は同様なので、以下の説明ではテストデータTS_DATAに統一する。また、テストデータTS_DATAは、複数のビットを含む信号になりうる。

【0037】

そして、テスト結果信号生成部146は、論理レベル判断部144から出力されるテストデータTS_DATAとデータ格納部100に格納されている比較データCOMP_DATAとが互いに同じ論理レベルを有することに対応して、アクティブになるテスト結果信号TS_RESULTを生成する。

【0038】

図1Cを参照すれば、テスト結果信号生成部146の詳細な回路が分かる。すなわち、テスト結果信号生成部146は、テストデータTS_DATAの各ビットTS_DATA<1>、TS_DATA<2>、TS_DATA<3>、TS_DATA<4>、TS_DATA<5>、TS_DATA<6>、TS_DATA<7>、TS_DATA<8>の論理レベルと比較データCOMP_DATAの各ビットCOMP_DATA<1>、COMP_DATA<2>、COMP_DATA<3>、COMP_DATA<4>、COMP_DATA<5>、COMP_DATA<6>、COMP_DATA<7>、COMP_DATA<8>の論理レベルとが完全に一致するとき、非アクティブ状態に初期化されていたテスト結果信号TS_RESULTをアクティブにする。

【0039】

参考に、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAとがそれぞれ8ビットからなる信号であることを例に挙げて示した図に過ぎず、テストデータTS_DATAと比較データCOMP_DATAとが8ビットより多いビット又は8ビットより少ないビットからなる場合に、その回路は変わりうる。

【0040】

また、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAの各ビットを直接比較する方式で示されているが、直接比較する方式でない場合でもテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較できる方式であれば、本発明の範ちゅうに含まれると見なすことができる。例えば、複数のビットからなるテストデータTS_DATAを圧縮した結果と複数のビットからなる比較データCOMP_DATAを圧縮した結果とを比較する方式によりテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較する場合も、本発明の範ちゅうに含まれうる。

【0041】

前述したデータ基準電圧出力部142、論理レベル判断部144及びテスト結果信号生成部146の動作を共に述べると、データ基準電圧出力部142は、外部から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するに伴い、データ基準電圧VREF_DQの電圧レベルも共に変動させ、論理レベル判断部144は、データ基準電圧VREF_DQの電圧レベルに基づいて外部から印加されるテストデータTS_DATAの論理レベルを判断し、テスト結果信号生成部146では、論理レベルの判断されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、両データが同じ論理レベルを有するとき、テスト結果信号TS_RESULTをアクティブにする。

【0042】

このとき、上述のように、データ入力バッファ120を介してテストデータTS_DATAと比較データCOMP_DATAが外部から入力される時には、互いに同じデータパターンを有する。したがって、外部から印加されるテストデータTS_DATAと比較データCOMP_DATAの電圧レベルスイングパターンを単純比較すると、完全に一致する状態になるはずである。

【0043】

しかしながら、比較データCOMP_DATAは、その電圧レベルスイングが電源電圧VDDレベルと接地電圧VSSレベルとの間でなされるために、その論理レベルが正確に判断されうることに対し、テストデータTS_DATAは、レベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが変動するデータ基準電圧VREF_DQのレベルに基づいてその論理レベルが判断されるので、レベルテストコードTS_LVCD<0:N>の値によってその論理レベルの判断が変わりうる。

【0044】

したがって、外部から入力される時には互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに異なる論理レベルを有する場合、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが誤った状態であることを意味する。反対に、外部から入力される時には互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに同じ論理レベルを有する場合、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが正常な状態であることを意味する。

【0045】

すなわち、テスト結果信号生成部146から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが正常なレベルを有する状態を意味する。

【0046】

言い換えれば、テスト結果信号生成部146から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、レベルテストコードTS_LVCD<0:N>が誤った値を有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、レベルテストコードTS_LVCD<0:N>が正常な値を有する状態を意味する。

【0047】

そして、テスト動作測定信号生成部160は、テスト進入コマンドTS_ENTRYに応答してアクティブになり、テスト結果信号TS_RESULTに応答して非アクティブになるテスト動作測定信号TS_SENSを生成する。

【0048】

図1Dを参照すれば、テスト動作測定信号生成部160の詳細な回路構成が分かる。具体的に、テスト動作測定信号生成部160は、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト結果信号TS_RESULTに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになるのを決定するためのPMOSトランジスタP1、P2と、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト進入コマンドTS_ENTRYに応答して、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるのを決定するためのNMOSトランジスタN1、N2とを備えて構成されることが分かる。

【0049】

したがって、テスト動作測定信号生成部160は、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグル(toggle)することに応答して、初期化状態でロジック「ハイ」に非アクティブになっていたテスト動作測定信号TS_SENSをロジック「ロー」(Low)にアクティブにし、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにする。

【0050】

このとき、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態から正常なレベルを有する状態に転換したことを意味する。

【0051】

言い換えれば、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、レベルテストコードTS_LVCD<0:N>が誤った値を有する状態から正常な値を有する状態に転換したことを意味する。

【0052】

そして、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルする時点でテスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるという点を想起してみれば、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになる時点からロジック「ハイ」に非アクティブになる時点までの区間は、レベルテストコードTS_LVCD<0:N>の値及びデータ基準電圧VREF_DQのレベルをトレーニングテストする区間という意味を有するようになる。

【0053】

このとき、レベルテストコードTS_LVCD<0:N>の値をトレーニングテストするということは、レベルテストコードTS_LVCD<0:N>の値を設定可能な特定範囲の値内で順次に変動させながら、どのような値を有する場合が正常な値を有する状態になるかが分かるための目的でテストを行うということを意味する。

【0054】

同様に、データ基準電圧VREF_DQのレベルをトレーニングテストするということは、データ基準電圧VREF_DQのレベルを設定可能な特定範囲の電圧レベル内で順次に変動させながら、どのような電圧レベルを有する場合が正常な電圧レベルを有する状態になるかが分かるための目的でテストを行うということを意味する。

【0055】

結論的に、テスト動作測定信号生成部160から生成されるテスト動作測定信号TS_SENSのアクティブ区間長は、トレーニングテスト動作を介してデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するのにかかる時間と同じパラメータになりうる。

【0056】

そして、テスト動作測定信号TS_SENSの長さを測定する方法は、以下のような2種類の方式を例に挙げることができる。

【0057】

まず、テスト動作測定信号TS_SENSを、図1Aに示すように設定された出力パッド(PAD)を介して外部に直に出力する方式がありうる。このとき、外部では特定テスト装備によりテスト動作測定信号TS_SENSの長さを測定する。

【0058】

そして、図1Bに示すように、アクティブ区間カウンタ190を介してテスト動作測定信号TS_SENSのアクティブ区間の間のソースクロックCLKのトグル回数をカウントした後、カウントした値を設定された出力パッド(PAD)を介して外部に出力する方式がありうる。このとき、外部ではカウントした値を介してテスト動作測定信号TS_SENSの長さを演算する。

【0059】

図2は、図1A〜図1Dに示す本発明の実施の形態に係る半導体装置の動作を説明するために示すタイミング図である。

【0060】

図2に示すように、図1A〜図1Dに示す本発明の実施の形態に係る半導体装置は、テスト準備進入コマンドTS_PENTRYがトグルすることに応答して、テスト準備動作区間(TS_PENABLEがアクティブになる区間)に進入し、テスト準備脱出コマンドTS_PEXITがトグルすることに応答して、テスト準備動作区間(TS_PENABLEがアクティブになる区間)から脱出する。

【0061】

このように、テスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITにより定義されるテスト準備動作区間(TS_PENABLEがアクティブになる区間)においてデータ入力コマンドWTがトグルすることに応答して、比較データCOMP_DATAがデータ入力バッファ120を介して印加される。

【0062】

そして、テスト進入コマンドTS_ENTRYがトグルすることに応答して、テスト動作区間(TS_ENABLEがアクティブになる区間)に進入し、テスト脱出コマンドTS_EXITがトグルすることに応答して、テスト動作区間(TS_ENABLEがアクティブになる区間)から脱出する。

【0063】

このように、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEがアクティブになる区間)において設定された時間ごとにデータ入力コマンドWTがトグルすることに応答して、テストデータTS_DATAがデータ入力バッファ120を介して印加される。

【0064】

また、テスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITにより定義されるテスト動作区間(TS_ENABLEがアクティブになる区間)においてデータ基準電圧VREF_DQのレベルが上昇する。すなわち、直接的に示されていないが、レベルテストコードTS_LVCD<0:N>値が最低値からターゲット値に向けて順次増加することによって、データ基準電圧VREF_DQのレベルも、設定された最低レベルからターゲットレベルに向けて上昇するようになる。

【0065】

また、データ基準電圧VREF_DQのレベルに基づいてテストデータTS_DATAの論理レベルを判断するようになるが、データ基準電圧VREF_DQのレベルが設定可能な最低レベルに近い状態では、テストデータTS_DATAの論理レベルを正常に判断できない。しかしながら、データ基準電圧VREF_DQのレベルが上昇し続けながらターゲットレベルに近づくことによって、ますますテストデータTS_DATAの論理レベルを正常に判断できるようになり、ターゲットレベルに到達すると、すべてのテストデータTS_DATAの論理レベルを正確に判断できるようになる。

【0066】

一方、テスト動作測定信号TS_SENSは、リセット信号RESETに応答してロジック「ハイ」に初期化された後、テスト進入コマンドTS_ENTRYに応答してロジック「ロー」にアクティブになる。すなわち、データ基準電圧VREF_DQのレベルが増加し始める時点と同じ時点でテスト進入コマンドTS_ENTRYがロジック「ロー」にアクティブになる。

【0067】

以後、データ基準電圧VREF_DQのレベルが十分に増加してターゲットレベルに到達することに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになる。すなわち、データ基準電圧VREF_DQのレベルがターゲットレベルに到達してテストデータTS_DATAの論理レベルを正常に判断する時点以後になって、テストデータTS_DATAと比較データCOMP_DATAとが互いに同じ論理レベルを有する状態になる時に、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになる。

【0068】

したがって、テスト動作測定信号TS_SENSのアクティブ区間は、データ基準電圧VREF_DQのレベルが変動する時点からデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでの区間になることが分かる。

【0069】

言い換えれば、テスト動作測定信号TS_SENSのアクティブ区間は、レベルテストコードTS_LVCD<0:N>の値が変動する時点からレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するまでの区間になることが分かる。

【0070】

参考に、図示のテスト動作測定信号TS_SENSのアクティブ区間長がA区間とB区間とに分けられることが分かる。ここで、B区間は、データ入力コマンドWTが印加されることに応答して、テストデータTS_DATAが実際入力されるまでかかる遅延量を表現したことであり、予め計算できる値である。

【0071】

そのため、正確に述べると、データ基準電圧VREF_DQのレベルが変動する時点からデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでの実際区間は、テスト動作測定信号TS_SENSのアクティブ区間長からB区間に該当する長さ分だけを引いた区間になる。

【0072】

言い換えれば、テスト動作測定信号TS_SENSのアクティブ区間は、レベルテストコードTS_LVCD<0:N>の値が変動する時点からレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するまでの実際区間であって、テスト動作測定信号TS_SENSのアクティブ区間長からB区間に該当する長さ分だけを引いた区間になる。

【0073】

図3A及び図3Bは、図1A及び図1Bに示す本発明の実施の形態に係る半導体装置を備える半導体システムを示すブロック図である。

【0074】

図3Aに示すように、本発明の実施の形態に係る半導体システムは、半導体コントローラ300及び半導体装置320を備えて構成される。ここで、半導体コントローラ300は、データ生成部302、コマンド生成部304、コード生成部306、及び測定部308を備えて構成される。そして、半導体装置320は、データ格納部321、テスト動作部324、テスト動作測定信号生成部326、データ入力バッファ322、及びモードレジスタセット323を備えて構成される。

【0075】

半導体コントローラ300は、テスト準備動作区間(TS_PENABLEがアクティブになる区間)の間に設定されたデータパターンを有する比較データCOMP_DATAを出力し、テスト動作区間(TS_ENABLEがアクティブになる区間)の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードTS_LVCD<0:N>と設定されたデータパターンを有するテストデータTS_DATAとを出力し、半導体装置320から出力される信号TS_SENSに応答して、レベルテストコードTS_LVCD<0:N>がターゲット値に到達する時間を測定する。

【0076】

半導体コントローラ300のコマンド生成部304からテスト準備進入コマンドTS_PENTRYとテスト準備脱出コマンドTS_PEXITとを生成して半導体装置320に伝達すると、半導体装置320に備えられたモードレジスタセット323でそれに応答して、テスト準備イネーブル信号TS_PENABLEのアクティブ有無を決定することによって、テスト準備動作区間を定義するようになる。

【0077】

同様に、半導体コントローラ300のコマンド生成部304からテスト進入コマンドTS_ENTRYとテスト脱出コマンドTS_EXITとを生成して半導体装置320に伝達すると、半導体装置320に備えられたモードレジスタセット323でそれに応答して、テストイネーブル信号TS_ENABLEのアクティブ有無を決定することによって、テスト動作区間を定義するようになる。

【0078】

また、半導体コントローラ300のコマンド生成部304からデータ入力コマンドWTを半導体装置320に伝達しながらデータ生成部302から生成されたデータEX_DATAを半導体装置320に伝達すると、半導体装置320のデータ入力バッファ322でこれを受け取ってバッファリングする。このとき、半導体装置320のデータ入力バッファ322でバッファリングされて出力されるデータは、テスト準備動作区間(TS_PENABLEがアクティブになる区間)において比較データCOMP_PDATAとなり、テスト動作区間(TS_ENABLEがアクティブになる区間)においてテストデータTS_PDATAとなる。すなわち、半導体コントローラ300から印加される比較データCOMP_PDATAと半導体コントローラ300から印加されるテストデータTS_PDATAとは、半導体コントローラ300から印加される時点がいつなのかによって区分されるだけであり、実際には同じデータパターンを有するデータである。

【0079】

半導体コントローラ300のコード生成部306は、レベルテストコードTS_LVCD<0:N>を生成して半導体装置320に伝達するが、このとき、その値を変動させる方式には、以下のような例がある。

【0080】

まず、半導体コントローラ300のコード生成部306でレベルテストコードTS_LVCD<0:N>を最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させて半導体装置320に伝達できる。このような場合に、半導体装置320のデータ基準電圧出力部3242では、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベル(外部接地電圧VSSレベルより高い)からターゲット電圧レベル(外部電源電圧VDDレベルより低い)まで変動させるようになる。

【0081】

また、半導体コントローラ300のコード生成部306でレベルテストコードTS_LVCD<0:N>を最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させて半導体装置320に伝達できる。このような場合に、半導体装置320のデータ基準電圧出力部3242では、データ基準電圧VREF_DQのレベルを設定可能な最大電圧レベル(外部電源電圧VDDレベルより低い)からターゲット電圧レベル(外部接地電圧VSSレベルより高い)まで変動させるようになる。

【0082】

半導体コントローラ300の測定部308は、コマンド生成部304から生成されるテスト進入コマンドTS_ENTRYと半導体装置320から出力されるテスト動作測定信号TS_SENSとに応答して、レベルテストコードTS_LVCD<0:N>が最小値又は最大値からターゲット値まで到達するのにかかる時間を測定できる。その測定方法は、例えば動作クロックのトグルに基づいて測定するか、又は動作クロックよりより速い周波数を有する任意のクロックを生成して、そのトグルに基づいて測定するようになる。

【0083】

半導体装置320のデータ格納部321は、テスト準備動作区間(TS_PENABLEがアクティブになる区間)において半導体コントローラ300から比較データCOMP_DATAを印加されて、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分し格納する。

【0084】

ここで、データ格納部321は、多目的レジスタ3212とデータラッチ3214とを備えて構成される。

【0085】

半導体装置320のデータ格納部321の構成要素のうち、多目的レジスタ3212は、テスト準備動作区間(TS_PENABLEのアクティブ区間)において半導体コントローラ300から印加される比較データCOMP_PDATAを格納する。

【0086】

半導体装置320のデータ格納部321の構成要素のうち、データラッチ3214は、多目的レジスタ3212に格納されたデータを外部電源電圧VDDレベルと外部接地電圧VSSレベルとの間でスイングする状態でラッチして、その論理レベルを明確に区分する。

【0087】

参考に、比較データは、半導体コントローラ300から印加される比較データCOMP_PDATA、半導体装置320の多目的レジスタ3212に格納される比較データCOMP_SDATA、及び半導体装置320のデータラッチ3214を介してラッチされた比較データCOMP_DATAに区分されうるが、これは、動作ステップによって信号名を区分するためであり、その値は同一なので、以下の説明では比較データCOMP_DATAに統一する。また、比較データCOMP_DATAは、複数のビットを含む信号になりうる。

【0088】

半導体装置320のテスト動作部324は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>に応答して、その電圧レベルが決定されるデータ基準電圧VREF_DQのレベルに基づいて設定された時間ごとに外部から印加されるテストデータTS_PDATAの論理レベルを決定し、論理レベルの決定されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、テスト結果信号TS_RESULTを生成する。

【0089】

テスト動作部324は、データ基準電圧出力部3242、論理レベル判断部3244、及びテスト結果信号生成部3246を備えて構成される。

【0090】

半導体装置320のテスト動作部324の構成要素のうち、データ基準電圧出力部3242は、テスト動作区間(TS_ENABLEのアクティブ区間)の間に半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>に応答して、データ基準電圧VREF_DQのレベルを外部接地電圧VSSレベルより高い設定可能な最低電圧レベルと外部電源電圧VDDレベルより低い設定可能な最大電圧レベルとの間で決定する。例えば、レベルテストコードTS_LVCD<0:N>が6ビットコードTS_LVCD<0:5>からなっており、最低値を有する状態TS_LVCD<0:5>=‘000000’であると、データ基準電圧VREF_DQのレベルを設定可能な最低電圧レベルに設定して生成し、レベルテストコードTS_LVCD<0:5>が最高値を有する状態TS_LVCD<0:5>=‘111111’であると、データ基準電圧VREF_DQのレベルを設定可能な最高電圧電圧レベルに設定して生成し、レベルテストコードTS_LVCD<0:5>が最低値と最高値の中間値を有する状態TS_LVCD<0:5>=‘011111’であると、データ基準電圧VREF_DQのレベルを設定可能な最高電圧レベルと最低電圧レベルとの間を半分した電圧レベルを有する状態に設定して生成する。

【0091】

半導体装置320のテスト動作部324の構成要素のうち、論理レベル判断部3244は、テスト動作区間(TS_ENABLEのアクティブ区間)において設定された時間ごとに印加されるテストデータTS_PDATAの論理レベルをデータ基準電圧VREF_DQのレベルに基づいて判断する。

【0092】

すなわち、論理レベル判断部3244では、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより高い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ハイ」に設定し、設定された時間ごとに印加されるテストデータTS_PDATAの電圧レベルがデータ基準電圧VREF_DQのレベルより低い状態であると、出力されるテストデータTS_DATAの論理レベルをロジック「ロー」に設定する方式で動作する。

【0093】

前述した半導体装置320のデータ基準電圧出力部3242と論理レベル判断部3244の動作を共に述べると、データ基準電圧出力部3242は、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するにつれて、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部3244は、データ基準電圧VREF_DQの電圧レベルに基づいて半導体コントローラ300から印加されるテストデータTS_DATAの論理レベルを判断するようになる。

【0094】

したがって、半導体コントローラ300から印加されるテストデータTS_DATAが常に一定の電圧レベルパターンを有する状態であっても、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:N>の値によって、判断される論理レベルは異なりうる。

【0095】

参考に、テストデータは、半導体コントローラ300から印加されるテストデータTS_PDATAと論理レベル判断部3244でその論理レベルの決定されたテストデータTS_DATAとに区分されうるが、これは、動作ステップによって信号名を区分するためであり、その値は同様なので、以下の説明では、テストデータTS_DATAに統一する。また、テストデータTS_DATAは、複数のビットを含む信号になりうる。

【0096】

半導体装置320のテスト結果信号生成部3246は、論理レベル判断部3244から出力されるテストデータTS_DATAとデータ格納部321に格納されている比較データCOMP_DATAとが互いに同じ論理レベルを有することに対応して、アクティブになるテスト結果信号TS_RESULTを生成する。参考に、図1Cを参照すれば、テスト結果信号生成部3246の詳細な回路が分かる。すなわち、テスト結果信号生成部3246は、テストデータTS_DATAの各ビットTS_DATA<1>、TS_DATA<2>、TS_DATA<3>、TS_DATA<4>、TS_DATA<5>、TS_DATA<6>、TS_DATA<7>、TS_DATA<8>と比較データCOMP_DATAの各ビットCOMP_DATA<1>、COMP_DATA<2>、COMP_DATA<3>、COMP_DATA<4>、COMP_DATA<5>、COMP_DATA<6>、COMP_DATA<7>、COMP_DATA<8>の論理レベルが完全に一致する時に、非アクティブ状態に初期化されていたテスト結果信号TS_RESULTをアクティブにする。

【0097】

参考に、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAとがそれぞれ8ビットからなる信号であることを例に挙げて示した図であり、テストデータTS_DATAと比較データCOMP_DATAとが8ビットより多いビット又は8ビットより少ないビットからなる場合に、その回路が変わりうる。

【0098】

また、図1Cでは、テストデータTS_DATAと比較データCOMP_DATAの各ビットを直接比較する方式で示されたが、直接比較する方式でない場合でもテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較できる方式であると、本発明の範ちゅうに含まれると見なすことができる。例えば、複数のビットからなるテストデータTS_DATAを圧縮した結果と複数のビットからなる比較データCOMP_DATAを圧縮した結果とを比較する方式により、テストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較する場合も、本発明の範ちゅうに含まれうる。

【0099】

前述したデータ基準電圧出力部3242、論理レベル判断部3244、及びテスト結果信号生成部3246の動作を共に述べると、データ基準電圧出力部3242は、半導体コントローラ300から印加されるレベルテストコードTS_LVCD<0:Nの値が変動するにつれて、データ基準電圧VREF_DQの電圧レベルも共に変動させるようになり、論理レベル判断部3244は、データ基準電圧VREF_DQの電圧レベルに基づいて半導体コントローラ300から印加されるテストデータTS_DATAの論理レベルを判断するようになり、テスト結果信号生成部3246では、論理レベルの判断されたテストデータTS_DATAと比較データCOMP_DATAの論理レベルを比較して、両データが同じ論理レベルを有する時にテスト結果信号TS_RESULTをアクティブにする。

【0100】

このとき、上述したように、データ入力バッファ322を介してテストデータTS_DATAと比較データCOMP_DATAとが半導体コントローラ300から入力される時には、互いに同じデータパターンを有する。したがって、半導体コントローラ300から印加されるテストデータTS_DATAと比較データCOMP_DATAの電圧レベルスイングパターンを単純比較すると、完全に一致する状態になるはずである。

【0101】

しかしながら、比較データCOMP_DATAは、その電圧レベルスイングが電源電圧VDDレベルと接地電圧VSSレベルとの間でなされるために、その論理レベルが正確に判断されうることに対し、テストデータTS_DATAは、レベルテストコードTS_LVCD<0:N>に応答して、電圧レベルが変動するデータ基準電圧VREF_DQのレベルに基づいてその論理レベルが判断されるので、レベルテストコードTS_LVCD<0:N>の値によって、その論理レベルの判断が変わりうる。

【0102】

したがって、半導体コントローラ300から入力される時には、互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに異なる論理レベルを有する場合であると、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが誤った状態であることを意味する。反対に、半導体コントローラ300から入力される時には、互いに同じ電圧レベルスイングパターンを有していた比較データCOMP_DATAとテストデータTS_DATAとが互いに同じ論理レベルを有する場合であると、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQのレベルが正常な状態であることを意味する。

【0103】

すなわち、半導体装置320のテスト結果信号生成部3246から出力されるテスト結果信号TS_RESULTが非アクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態を意味し、テスト結果信号TS_RESULTがアクティブになった状態は、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが正常なレベルを有する状態を意味する。

【0104】

そして、半導体装置320のテスト動作測定信号生成部326は、テスト進入コマンドTS_ENTRYに応答してアクティブになり、テスト結果信号TS_RESULTに応答して非アクティブになるテスト動作測定信号TS_SENSを生成する。

【0105】

図1Dを参照すれば、テスト動作測定信号生成部326の詳細な回路構成が分かる。具体的に、テスト動作測定信号生成部326は、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト結果信号TS_RESULTに応答して、テスト動作測定信号TS_SENSがロジック「ハイ」に非アクティブになるのを決定するためのPMOSトランジスタP1、P2と、テスト動作区間(TS_ENABLEのアクティブ区間)においてテスト進入コマンドTS_ENTRYに応答して、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるのを決定するためのNMOSトランジスタN1、N2を備えて構成されることが分かる。

【0106】

したがって、テスト動作測定信号生成部326は、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルすることに応答して、初期化状態でロジック「ハイ」に非アクティブになっていたテスト動作測定信号TS_SENSをロジック「ロー」にアクティブにし、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにする。

【0107】

このとき、テスト結果信号TS_RESULTがロジック「ロー」にアクティブになることに応答して、テスト動作測定信号TS_SENSをロジック「ハイ」に非アクティブにするから、テスト動作測定信号TS_SENSがロジック「ロー」のアクティブ状態からロジック「ハイ」の非アクティブ状態に遷移することは、テストデータTS_DATAの論理レベルを判断するためのデータ基準電圧VREF_DQが誤ったレベルを有する状態から正常なレベルを有する状態に転換したことを意味する。

【0108】

そして、テスト進入コマンドTS_ENTRYがロジック「ハイ」にトグルする時点でテスト動作測定信号TS_SENSがロジック「ロー」にアクティブになるという点を想起してみれば、テスト動作測定信号TS_SENSがロジック「ロー」にアクティブになる時点からロジック「ハイ」非アクティブになる時点までの区間は、レベルテストコードTS_LVCD<0:N>の値及びデータ基準電圧VREF_DQのレベルをトレーニングテストする区間という意味を有するようになる。

【0109】

このとき、レベルテストコードTS_LVCD<0:N>の値をトレーニングテストするということは、レベルテストコードTS_LVCD<0:N>の値を設定可能な特定範囲の値内で順次に変動させながら、どのような値を有する時が正常な値を有する状態になるかが分かるための目的でテストを行うことを意味する。

【0110】

同様に、データ基準電圧VREF_DQのレベルをトレーニングテストするということは、データ基準電圧VREF_DQのレベルを設定可能な特定範囲の電圧レベル内で順次変動させながら、どのような電圧レベルを有する時が正常な電圧レベルを有する状態になるかが分かるための目的でテストを行うことを意味する。

【0111】

結論的に、テスト動作測定信号生成部326から生成されるテスト動作測定信号TS_SENSのアクティブ区間長は、トレーニングテスト動作を介してデータ基準電圧VREF_DQのレベルがターゲットレベルに到達するのにかかる時間と同じパラメータになりうる。

【0112】

そして、図3Bに示す半導体システムの構成と図3Aに示す半導体システムの構成はほとんど一致する。ただし、半導体装置320にアクティブ区間カウンタ329がさらに備えられ、半導体コントローラ300には測定部308がなくなる代わりにカウント−時間テーブル309が備えられる構成であることが分かる。

【0113】

具体的に、半導体装置320のアクティブ区間カウンタ329は、テスト動作測定信号生成部326から生成されるテスト動作測定信号TS_SENSのアクティブ区間の間にソースクロックCLKのトグル回数をカウントした後、カウントした値TS_CNTを設定された出力パッド(PAD)を介して半導体コントローラ300に出力する。

【0114】

そして、半導体コントローラ300のカウント−時間テーブル309には、半導体装置320から伝達されるカウント値TS_CNTごとにレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するのにかかる時間が予め測定されて格納されており、半導体装置320からカウント値TS_CNTが伝達されると、直ちにレベルテストコードTS_LVCD<0:N>の値がターゲット値に到達するのにかかる時間を演算できる。

【0115】

以上述べたように、本発明の実施の形態を適用すれば、内部でデータ基準電圧VREF_DQを生成して印加されるデータの論理レベルを判断する半導体装置において、データ基準電圧VREF_DQのレベル変動をトレーニングテストした結果を出力パルスのアクティブ区間長に換算して半導体装置の外部に出力できる。

【0116】

すなわち、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを半導体装置の外部で測定する時に半導体装置から出力されるパルスのアクティブ区間長を測定しさえすればよいので、測定結果がモニターリングパッドと測定装備のキャパシティブ及びローディング成分に影響を受けないようになる。

【0117】

したがって、データ基準電圧VREF_DQのレベルがターゲットレベルに到達するまでかかる時間のような極めて微細な単位のパラメータを半導体装置の外部で極めて正確に測定できる。

【0118】

また、半導体装置から出力されるパルスのアクティブ区間長を測定するとき、測定動作周波数が高ければ高いほど、より微細な単位まで測定可能なので、半導体システムの動作周波数が極めて高い場合にも安定した測定動作が行われうる。

【0119】

以上説明した本発明は、上記の実施の形態及び添付された図面により限定されるものではなく、本発明に係る技術的思想から逸脱しない範囲内で様々な変更が可能であり、それらも本発明の技術的範囲に属する。

【0120】

例えば、前述した実施の形態において例示した論理ゲート及びトランジスタは、入力される信号の極性によってその位置及び種類が異なるように具現化されなければならない。

【符号の説明】

【0121】

300 半導体コントローラ

320 半導体装置

120、322 データ入力バッファ

100、321 データ格納部

140、324 テスト動作部

160、326 テスト動作測定信号生成部

110、323 モードレジスタセット、MRS

102、3212 多目的レジスタ

104、3214 データラッチ

142、3242 データ基準電圧出力部

144、3244 論理レベル判断部

146、3246 テスト結果信号生成部

190、329 アクティブ区間カウンタ

302 データ生成部

304 コマンド生成部

306 コード生成部

308 測定部

309 カウント−時間テーブル

【特許請求の範囲】

【請求項1】

外部から印加された入力データを、設定された電圧レベル差を有してスイングさせことによって、その論理レベルを区分して比較データとして格納するデータ格納部と、

テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、レベルテストコードに応答して周期的にテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較して、テスト結果信号を生成するテスト動作部と、

前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、

を備える半導体装置。

【請求項2】

前記テスト動作測定信号を出力するための設定された出力パッドをさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするためのアクティブ区間カウンタと、

前記アクティブ区間カウンタのカウント値を出力するための設定された出力パッドと、

をさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記データ格納部は、

テスト準備進入/脱出コマンドにより定義されるテスト準備動作区間において印加される前記入力データを格納するための多目的レジスタと、

前記多目的レジスタに格納されたデータを外部電源電圧レベルと外部接地電圧レベルとの間でラッチして、前記比較データを出力するデータラッチと、

を備えることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記テスト動作部は、

前記テスト動作区間の間に外部から印加される前記レベルテストコードに応答して、前記データ基準電圧のレベルを設定可能な最低電圧レベルと設定可能な最大電圧レベルとの間で決定するデータ基準電圧出力部と、

前記テスト動作区間において周期的に印加される前記テストデータの論理レベルを前記データ基準電圧のレベルに基づいて判断するための論理レベル判断部と、

前記論理レベル判断部の出力データと前記比較データとが互いに同じ論理レベルを有することに対応して、アクティブになる前記テスト結果信号を生成するためのテスト結果信号生成部と、

を備えることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記設定可能な最低電圧レベルは、外部接地電圧レベルより高く、前記設定可能な最大電圧レベルは、外部電源電圧レベルより低いことを特徴とする請求項5に記載の半導体装置。

【請求項7】

テスト準備動作区間の間に設定されたデータパターンを有する比較データを出力し、テスト動作区間の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードと前記設定されたデータパターンを有するテストデータとを出力し、半導体装置から出力される信号に応答して、前記レベルテストコードがターゲット値に到達する時間を測定する半導体コントローラと、

前記テスト準備動作区間の間に前記比較データの論理レベルを格納した後、前記テスト動作区間の間に前記レベルテストコードに応答して、データ基準電圧のレベルを決定し、前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後、前記比較データの論理レベルと比較して出力信号を生成する半導体装置と、

を備える半導体システム。

【請求項8】

前記半導体コントローラは、

テスト準備進入/脱出コマンドを生成した後、前記半導体装置に伝達して前記テスト準備動作区間を定義し、

テスト進入/脱出コマンドを生成した後、前記半導体装置に伝達して前記テスト動作区間を定義することを特徴とする請求項7に記載の半導体システム。

【請求項9】

前記半導体装置は、

前記テスト準備動作区間において前記比較データを受け取って、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを区分して格納するデータ格納部と、

前記テスト動作区間の間に、前記レベルテストコードに応答して、前記データ基準電圧のレベルを決定した後、決定された前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断して、前記比較データとその論理レベルを比較することによってテスト結果信号を生成するテスト動作部と、

テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を出力信号として生成するためのテスト動作測定信号生成部と、

を備えることを特徴とする請求項7に記載の半導体システム。

【請求項10】

前記半導体装置は、

前記テスト動作測定信号を前記半導体システムに伝達するための設定された出力パッドをさらに備えることを特徴とする請求項9に記載の半導体システム。

【請求項11】

前記半導体システムは、

前記テスト進入コマンドの生成時点から前記半導体装置に伝達される前記テスト動作測定信号が非アクティブになる時点までの時間を測定して、前記レベルテストコードがターゲット値に到達する時間として設定することを特徴とする請求項10に記載の半導体システム。

【請求項12】

前記半導体装置は、

前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするためのアクティブ区間カウンタと、

前記アクティブ区間カウンタのカウント値を前記半導体システムに伝達するための設定された出力パッドと、

をさらに備えることを特徴とする請求項9に記載の半導体システム。

【請求項13】

前記半導体システムは、

その値が予め決定されているカウント−時間テーブルに基づいて前記半導体装置から伝達されるカウント値に対応して、前記レベルテストコードがターゲット値に到達する時間を演算することを特徴とする請求項11に記載の半導体システム。

【請求項14】

前記データ格納部は、

前記テスト準備動作区間の間に前記半導体コントローラから印加される前記比較データを格納するための多目的レジスタと、

前記多目的レジスタに格納されたデータを外部電源電圧レベルと外部接地電圧レベルとの間でラッチして、その論理レベルを明確に区分するデータラッチと、

を備えることを特徴とする請求項9に記載の半導体システム。

【請求項15】

前記テスト動作部は、

前記テスト動作区間の間に前記半導体コントローラから印加される前記レベルテストコードの値が変動するごとに前記データ基準電圧のレベルを変動して出力するデータ基準電圧出力部と、

前記テスト動作区間の間に設定された時間ごとに前記半導体コントローラから印加される前記テストデータの論理レベルを前記データ基準電圧出力部から出力される前記データ基準電圧のレベルに基づいて判断するための論理レベル判断部と、

前記論理レベル判断部の出力データと前記比較データとが互いに同じ論理レベルを有することに対応してアクティブになる前記テスト結果信号を生成するためのテスト結果信号生成部と、

を備えることを特徴とする請求項9に記載の半導体システム。

【請求項16】

前記半導体コントローラが前記レベルテストコードを最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させることに対応して、

前記データ基準電圧出力部は、前記データ基準電圧のレベルを設定可能な最低電圧レベル(外部接地電圧レベルより高い)からターゲット電圧レベル(外部電源電圧レベルより低い)まで変動させることを特徴とする請求項15に記載の半導体システム。

【請求項17】

前記半導体コントローラが前記レベルテストコードを最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させることに対応して、

前記データ基準電圧出力部は、前記データ基準電圧のレベルを設定可能な最大電圧レベル(外部電源電圧レベルより低い)からターゲット電圧レベル(外部接地電圧レベルより高い)まで変動させることを特徴とする請求項15に記載の半導体システム。

【請求項18】

半導体コントローラからテスト準備進入コマンド、設定されたデータパターンを有する比較データ、及びテスト準備脱出コマンドを順次に出力し、これを半導体装置から受け取ってテスト準備動作区間に進入した後に前記比較データの論理レベルを調節して格納し、続いてテスト準備動作区間から脱出するステップと、

半導体コントローラからテスト進入コマンドを出力し、続いて設定された時間ごとにその値が変動するレベルテストコードと前記設定されたデータパターンを有するテストデータを設定された回数分だけ出力した後に、テスト脱出コマンドを出力するテスト動作ステップと、

前記半導体装置から前記テスト進入コマンド及びテスト脱出コマンドにより定義されたテスト動作区間の間に前記レベルテストコード及びテストデータが出力されることに応答して、設定された時間ごとにデータ基準電圧のレベルを決定し、決定されたデータ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後に、前記比較データの論理レベルと比較してテスト動作測定信号を出力するステップと、

前記テスト動作測定信号に応答して、半導体コントローラで前記レベルテストコードがターゲット値に到達する時間を測定するステップと、

を含む半導体システムの動作方法。

【請求項19】

前記比較するステップは、

前記半導体コントローラで前記レベルテストコードの値が変動するごとに、前記半導体装置で前記データ基準電圧のレベルを変動するステップと、

前記半導体装置で前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断するステップと、

前記半導体装置で前記テストデータと前記比較データとが互いに同じ論理レベルを有することに対応してアクティブになるテスト結果信号を生成するステップと、

前記半導体装置で前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになる前記テスト動作測定信号を生成するステップと、

を含むことを特徴とする請求項18に記載の半導体システムの動作方法。

【請求項20】

前記比較するステップは、

前記テスト動作測定信号を設定された出力パッドを介して前記半導体コントローラに伝達するステップをさらに含むことを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項21】

前記測定するステップは、

前記半導体コントローラで前記テスト進入コマンドが生成される時点から前記半導体装置から前記テスト動作測定信号が非アクティブになって伝達される時点までの時間を測定して、前記レベルテストコードがターゲット値に到達する時間として設定することを特徴とする請求項20に記載の半導体システムの動作方法。

【請求項22】

前記比較するステップは、

前記半導体装置で前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするステップと、

前記半導体装置で前記カウントするステップの動作結果生成されるカウント値を設定された出力パッドを介して前記半導体コントローラに伝達するステップと、

をさらに含むことを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項23】

前記測定するステップは、

その値が予め決定されているカウント−時間テーブルに基づいて、前記半導体装置から出力される前記カウント値に対応して前記レベルテストコードがターゲット値に到達する時間を演算することを特徴とする請求項22に記載の半導体システムの動作方法。

【請求項24】

前記データ基準電圧のレベルを変動するステップは、

前記半導体コントローラで前記レベルテストコードを最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させることに対応して、前記半導体装置では前記データ基準電圧のレベルを設定可能な最低電圧レベル(外部接地電圧レベルより高い)からターゲット電圧レベル(外部電源電圧レベルより低い)まで変動させることを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項25】

前記データ基準電圧のレベルを変動するステップは、

前記半導体コントローラで前記レベルテストコードを最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させることに対応して、前記半導体装置では前記データ基準電圧のレベルを設定可能な最大電圧レベル(外部電源電圧レベルより低い)からターゲット電圧レベル(外部接地電圧レベルより高い)まで変動させることを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項1】

外部から印加された入力データを、設定された電圧レベル差を有してスイングさせことによって、その論理レベルを区分して比較データとして格納するデータ格納部と、

テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、レベルテストコードに応答して周期的にテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較して、テスト結果信号を生成するテスト動作部と、

前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、

を備える半導体装置。

【請求項2】

前記テスト動作測定信号を出力するための設定された出力パッドをさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするためのアクティブ区間カウンタと、

前記アクティブ区間カウンタのカウント値を出力するための設定された出力パッドと、

をさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記データ格納部は、

テスト準備進入/脱出コマンドにより定義されるテスト準備動作区間において印加される前記入力データを格納するための多目的レジスタと、

前記多目的レジスタに格納されたデータを外部電源電圧レベルと外部接地電圧レベルとの間でラッチして、前記比較データを出力するデータラッチと、

を備えることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記テスト動作部は、

前記テスト動作区間の間に外部から印加される前記レベルテストコードに応答して、前記データ基準電圧のレベルを設定可能な最低電圧レベルと設定可能な最大電圧レベルとの間で決定するデータ基準電圧出力部と、

前記テスト動作区間において周期的に印加される前記テストデータの論理レベルを前記データ基準電圧のレベルに基づいて判断するための論理レベル判断部と、

前記論理レベル判断部の出力データと前記比較データとが互いに同じ論理レベルを有することに対応して、アクティブになる前記テスト結果信号を生成するためのテスト結果信号生成部と、

を備えることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記設定可能な最低電圧レベルは、外部接地電圧レベルより高く、前記設定可能な最大電圧レベルは、外部電源電圧レベルより低いことを特徴とする請求項5に記載の半導体装置。

【請求項7】

テスト準備動作区間の間に設定されたデータパターンを有する比較データを出力し、テスト動作区間の間に設定された時間ごとにそのレベル値を変動させるレベルテストコードと前記設定されたデータパターンを有するテストデータとを出力し、半導体装置から出力される信号に応答して、前記レベルテストコードがターゲット値に到達する時間を測定する半導体コントローラと、

前記テスト準備動作区間の間に前記比較データの論理レベルを格納した後、前記テスト動作区間の間に前記レベルテストコードに応答して、データ基準電圧のレベルを決定し、前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後、前記比較データの論理レベルと比較して出力信号を生成する半導体装置と、

を備える半導体システム。

【請求項8】

前記半導体コントローラは、

テスト準備進入/脱出コマンドを生成した後、前記半導体装置に伝達して前記テスト準備動作区間を定義し、

テスト進入/脱出コマンドを生成した後、前記半導体装置に伝達して前記テスト動作区間を定義することを特徴とする請求項7に記載の半導体システム。

【請求項9】

前記半導体装置は、

前記テスト準備動作区間において前記比較データを受け取って、設定された電圧レベル差を有してスイングさせることによって、その論理レベルを区分して格納するデータ格納部と、

前記テスト動作区間の間に、前記レベルテストコードに応答して、前記データ基準電圧のレベルを決定した後、決定された前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断して、前記比較データとその論理レベルを比較することによってテスト結果信号を生成するテスト動作部と、

テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を出力信号として生成するためのテスト動作測定信号生成部と、

を備えることを特徴とする請求項7に記載の半導体システム。

【請求項10】

前記半導体装置は、

前記テスト動作測定信号を前記半導体システムに伝達するための設定された出力パッドをさらに備えることを特徴とする請求項9に記載の半導体システム。

【請求項11】

前記半導体システムは、

前記テスト進入コマンドの生成時点から前記半導体装置に伝達される前記テスト動作測定信号が非アクティブになる時点までの時間を測定して、前記レベルテストコードがターゲット値に到達する時間として設定することを特徴とする請求項10に記載の半導体システム。

【請求項12】

前記半導体装置は、

前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするためのアクティブ区間カウンタと、

前記アクティブ区間カウンタのカウント値を前記半導体システムに伝達するための設定された出力パッドと、

をさらに備えることを特徴とする請求項9に記載の半導体システム。

【請求項13】

前記半導体システムは、

その値が予め決定されているカウント−時間テーブルに基づいて前記半導体装置から伝達されるカウント値に対応して、前記レベルテストコードがターゲット値に到達する時間を演算することを特徴とする請求項11に記載の半導体システム。

【請求項14】

前記データ格納部は、

前記テスト準備動作区間の間に前記半導体コントローラから印加される前記比較データを格納するための多目的レジスタと、

前記多目的レジスタに格納されたデータを外部電源電圧レベルと外部接地電圧レベルとの間でラッチして、その論理レベルを明確に区分するデータラッチと、

を備えることを特徴とする請求項9に記載の半導体システム。

【請求項15】

前記テスト動作部は、

前記テスト動作区間の間に前記半導体コントローラから印加される前記レベルテストコードの値が変動するごとに前記データ基準電圧のレベルを変動して出力するデータ基準電圧出力部と、

前記テスト動作区間の間に設定された時間ごとに前記半導体コントローラから印加される前記テストデータの論理レベルを前記データ基準電圧出力部から出力される前記データ基準電圧のレベルに基づいて判断するための論理レベル判断部と、

前記論理レベル判断部の出力データと前記比較データとが互いに同じ論理レベルを有することに対応してアクティブになる前記テスト結果信号を生成するためのテスト結果信号生成部と、

を備えることを特徴とする請求項9に記載の半導体システム。

【請求項16】

前記半導体コントローラが前記レベルテストコードを最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させることに対応して、

前記データ基準電圧出力部は、前記データ基準電圧のレベルを設定可能な最低電圧レベル(外部接地電圧レベルより高い)からターゲット電圧レベル(外部電源電圧レベルより低い)まで変動させることを特徴とする請求項15に記載の半導体システム。

【請求項17】

前記半導体コントローラが前記レベルテストコードを最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させることに対応して、

前記データ基準電圧出力部は、前記データ基準電圧のレベルを設定可能な最大電圧レベル(外部電源電圧レベルより低い)からターゲット電圧レベル(外部接地電圧レベルより高い)まで変動させることを特徴とする請求項15に記載の半導体システム。

【請求項18】

半導体コントローラからテスト準備進入コマンド、設定されたデータパターンを有する比較データ、及びテスト準備脱出コマンドを順次に出力し、これを半導体装置から受け取ってテスト準備動作区間に進入した後に前記比較データの論理レベルを調節して格納し、続いてテスト準備動作区間から脱出するステップと、

半導体コントローラからテスト進入コマンドを出力し、続いて設定された時間ごとにその値が変動するレベルテストコードと前記設定されたデータパターンを有するテストデータを設定された回数分だけ出力した後に、テスト脱出コマンドを出力するテスト動作ステップと、

前記半導体装置から前記テスト進入コマンド及びテスト脱出コマンドにより定義されたテスト動作区間の間に前記レベルテストコード及びテストデータが出力されることに応答して、設定された時間ごとにデータ基準電圧のレベルを決定し、決定されたデータ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断した後に、前記比較データの論理レベルと比較してテスト動作測定信号を出力するステップと、

前記テスト動作測定信号に応答して、半導体コントローラで前記レベルテストコードがターゲット値に到達する時間を測定するステップと、

を含む半導体システムの動作方法。

【請求項19】

前記比較するステップは、

前記半導体コントローラで前記レベルテストコードの値が変動するごとに、前記半導体装置で前記データ基準電圧のレベルを変動するステップと、

前記半導体装置で前記データ基準電圧のレベルに基づいて前記テストデータの論理レベルを判断するステップと、

前記半導体装置で前記テストデータと前記比較データとが互いに同じ論理レベルを有することに対応してアクティブになるテスト結果信号を生成するステップと、

前記半導体装置で前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになる前記テスト動作測定信号を生成するステップと、

を含むことを特徴とする請求項18に記載の半導体システムの動作方法。

【請求項20】

前記比較するステップは、

前記テスト動作測定信号を設定された出力パッドを介して前記半導体コントローラに伝達するステップをさらに含むことを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項21】

前記測定するステップは、

前記半導体コントローラで前記テスト進入コマンドが生成される時点から前記半導体装置から前記テスト動作測定信号が非アクティブになって伝達される時点までの時間を測定して、前記レベルテストコードがターゲット値に到達する時間として設定することを特徴とする請求項20に記載の半導体システムの動作方法。

【請求項22】

前記比較するステップは、

前記半導体装置で前記テスト動作測定信号のアクティブ区間の間にソースクロックのトグル回数をカウントするステップと、

前記半導体装置で前記カウントするステップの動作結果生成されるカウント値を設定された出力パッドを介して前記半導体コントローラに伝達するステップと、

をさらに含むことを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項23】

前記測定するステップは、

その値が予め決定されているカウント−時間テーブルに基づいて、前記半導体装置から出力される前記カウント値に対応して前記レベルテストコードがターゲット値に到達する時間を演算することを特徴とする請求項22に記載の半導体システムの動作方法。

【請求項24】

前記データ基準電圧のレベルを変動するステップは、

前記半導体コントローラで前記レベルテストコードを最小値からそれより大きなターゲット値(最大値と同一又はそれより小さな値を有する)まで順次に増加させることに対応して、前記半導体装置では前記データ基準電圧のレベルを設定可能な最低電圧レベル(外部接地電圧レベルより高い)からターゲット電圧レベル(外部電源電圧レベルより低い)まで変動させることを特徴とする請求項19に記載の半導体システムの動作方法。

【請求項25】

前記データ基準電圧のレベルを変動するステップは、

前記半導体コントローラで前記レベルテストコードを最大値からそれより小さなターゲット値(最小値と同一又はそれより大きな値を有する)まで順次に減少させることに対応して、前記半導体装置では前記データ基準電圧のレベルを設定可能な最大電圧レベル(外部電源電圧レベルより低い)からターゲット電圧レベル(外部接地電圧レベルより高い)まで変動させることを特徴とする請求項19に記載の半導体システムの動作方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図2】

【図3A】

【図3B】

【図1B】

【図1C】

【図1D】

【図2】

【図3A】

【図3B】

【公開番号】特開2013−101738(P2013−101738A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−105111(P2012−105111)

【出願日】平成24年5月2日(2012.5.2)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成24年5月2日(2012.5.2)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]