半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びこれを用いた情報処理システムに関し、特に、互いに位相の異なる多相クロック信号を使用する半導体装置及びこれを用いた情報処理システムに関する。

【背景技術】

【0002】

半導体装置の多くはクロック信号に同期して動作するタイプの半導体装置であるが、中には、互いに位相の異なる多相クロック信号を用いるものが存在する。多相クロック信号の相間隔は、基準となるクロック信号の周期よりも短いため、このような多相クロック信号をどのような方法で生成するかが問題となる。

【0003】

相間隔の短い多相クロック信号を生成する回路として、特許文献1には、異なる遅延量を有する複数種類の遅延素子を縦列接続した回路が開示されている。特許文献1に記載された多相クロック生成回路によれば、多相クロック信号の相間隔を遅延素子1段分の最小遅延時間よりも短くすることが可能となる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−16545号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載された多相クロック生成回路では、多相クロック信号の一つを生成するために多数の遅延素子が必要である。このため、全体としてかなり多くの遅延素子を用いる必要があり、回路規模が非常に大きくなるというデメリットがあった。

【0006】

半導体装置が処理すべきデータ量は年々大きくなり、その処理速度は高速化する傾向にある。本発明はそのような膨大なデータ量を高速に処理し、且つ必要となる回路規模が小さく抑えられた情報処理システム、及びそのシステムに含まれる半導体装置を提供することを課題とするものである。

【課題を解決するための手段】

【0007】

本発明の一側面による半導体装置は、互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路とを備えることを特徴とする。

【0008】

本発明による情報処理システムは、第1及び第2の半導体装置と、前記第1の半導体装置と前記第2の半導体装置を接続するデータ配線とを備え、前記第1及び第2の半導体装置はいずれも上述の半導体装置であり、前記第1の半導体装置の内部でパラレルに伝送される前記複数のデータ信号は、前記第1の半導体装置に設けられた前記データ処理回路によってシリアルに変換されて前記データ配線に出力され、前記データ配線を介して前記第2の半導体装置にシリアルに供給される前記複数のデータ信号は、前記第2の半導体装置に設けられた前記データ処理回路によってパラレルに変換されることを特徴とする。

【0009】

本発明の他の側面による半導体装置は、縦列接続されたn個の遅延回路からなり、入力クロック信号をk周期遅延させるディレイラインと、前記n個の遅延回路からそれぞれ出力されるn個の出力クロック信号の少なくとも一部に基づいて、互いに位相の異なる多相クロック信号を生成するルーティング回路と、を備え、前記n及びkはいずれも2以上の整数であり、最大公約数が1であることを特徴とする。

【発明の効果】

【0010】

本発明によれば、短い相間隔を有する多相クロック信号をしていることから、生成された多相クロック信号をタイミング信号として用いれば、高速なデータ転送が可能となる。特に、kを2以上の整数値とし、且つ、nとは異なる値に設定すれば、遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の好ましい実施形態による情報処理システム2の構成を示すブロック図である。

【図2】マルチプレクサMUX0の一部分を示す回路図である。

【図3】マルチプレクサMUX0の動作を説明するためのタイミング図である。

【図4】情報処理システム2のリード動作を説明するためのタイミング図である。

【図5】半導体装置10の全体構成を示すブロック図である。

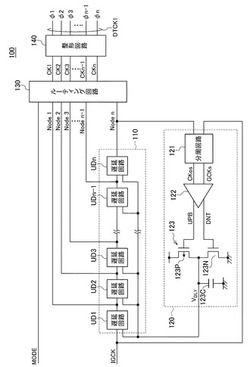

【図6】DLL回路100の回路図である。

【図7】遅延回路UD1の回路図である。

【図8】制御電圧VDLYと遅延回路UD1の遅延量δとの関係を示すグラフである。

【図9】分周回路121の一部を示す回路図である。

【図10】位相判定回路122の回路図である。

【図11】DLL回路100の動作を説明するためのタイミング図である。

【図12】ルーティング回路130の機能を説明するための配線図である。

【図13】割り当てを変更可能なルーティング回路130の機能を説明するための模式図である。

【図14】図13に示す領域Xの回路図である。

【図15】整形回路140の回路図である。

【図16】整形回路140の動作波形図である。

【発明を実施するための形態】

【0012】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0013】

図1は、本発明の好ましい実施形態による情報処理システム2の構成を示すブロック図である。

【0014】

図1に示す情報処理システム2は、半導体装置4と半導体装置10がデータ配線TLDT,TLDB及びアドレスコマンド配線TLACT,TLACBを介して接続された構成を有している。特に限定されるものではないが、半導体装置10はDRAM(Dynamic Random Access Memory)などのメモリデバイスであり、半導体装置4はこれを制御するコントローラである。半導体装置4,10には、クロックジェネレータ6からグローバルクロック信号GCKが共通に供給される。グローバルクロック信号GCKは、本実施形態による情報処理システム2の基準クロックとして用いられる信号である。

【0015】

図1に示すように、DRAMを構成する半導体装置10には、主回路部MCR、インターフェース回路部IFC1及びクロック生成部CKGEN1が含まれている。主回路部MCRは、メモリセルアレイ、デコーダなどDRAMに含まれるバックエンド回路である。同様に、コントローラを構成する半導体装置4には、主回路部LCR、インターフェース回路部IFC2及びクロック生成部CKGEN2が含まれている。主回路部LCRは、ロジック回路などコントローラに含まれるバックエンド回路である。

【0016】

半導体装置10に含まれるインターフェース回路部IFC1と、半導体装置4に含まれるインターフェース回路部IFC2は、互いに同様の回路構成を有している。具体的に説明すると、半導体装置10のインターフェース回路部IFC1には、データ用のマルチプレクサMUX0及びデマルチプレクサDMUX0と、アドレスコマンド用のデマルチプレクサDMUXacが設けられており、半導体装置4のインターフェース回路部IFC2には、データ用のマルチプレクサMUX0c及びデマルチプレクサDMUX0cと、アドレスコマンド用のマルチプレクサMUXacが設けられている。本発明においては、マルチプレクサ及びデマルチプレクサを「データ処理回路」と呼ぶことがある。

【0017】

データ用のマルチプレクサMUX0は、データバスDBUS1を介して主回路部MCRからパラレルに供給されるnビットのデータ信号をシリアル変換する回路であり、シリアルに変化されたデータ信号は、一対のデータ配線TLDT,TLDBを介して半導体装置4に入力される。半導体装置4に入力されたシリアルなデータ信号は、データ用のデマルチプレクサDMUX0cによってパラレル変換される。パラレルに変換されたデータ信号は、データバスDBUS2を介して主回路部LCRに供給される。

【0018】

同様に、データ用のマルチプレクサMUX0cは、データバスDBUS2を介して主回路部LCRからパラレルに供給されるnビットのデータ信号をシリアル変換する回路であり、シリアルに変化されたデータ信号は、一対のデータ配線TLDT,TLDBを介して半導体装置10に入力される。半導体装置10に入力されたシリアルなデータ信号は、データ用のデマルチプレクサDMUX0によってパラレル変換される。パラレルに変換されたデータ信号は、データバスDBUS1を介して主回路部MCRに供給される。

【0019】

一方、アドレスコマンド用のマルチプレクサMUXacは、アドレスコマンドバスACBUS2を介して主回路部LCRからパラレルに供給されるmビットのアドレスコマンド信号をシリアル変換する回路であり、シリアルに変化されたアドレスコマンド信号は、一対のアドレスコマンド配線TLACT,TLACBを介して半導体装置10に入力される。半導体装置10に入力されたシリアルなアドレスコマンド信号は、アドレスコマンド用のデマルチプレクサDMUXacによってパラレル変換される。パラレルに変換されたアドレスコマンド信号は、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。

【0020】

このように、本実施形態による情報処理システム2においては、半導体装置4と半導体装置10との間で送受信されるnビットのデータ信号は、送信側においてシリアル変換され、データ配線TLDT,TLDBを介してシリアルに転送される。そして、シリアルに転送されたデータ信号は、受信側においてパラレル変換される。同様に、半導体装置4から半導体装置10に供給されるmビットのアドレスコマンド信号は、送信側である半導体装置4においてシリアル変換され、アドレスコマンド配線TLACT,TLACBを介してシリアルに転送される。そして、シリアルに転送されたアドレスコマンド信号は、受信側である半導体装置10においてパラレル変換される。このようなシリアル転送を行っているのは、複数ビットからなる信号(本例では、nビットのデータ信号やmビットのアドレスコマンド信号)をパラレルに高速転送すると、送信側及び受信側においてビット間の同期を取ることが困難となるからである。

【0021】

尚、図1に示す例では、データ信号及びアドレスコマンド信号をいずれも一対の信号線を用いてディファレンシャル形式で転送しているが、本発明がこれに限定されるものではない。したがって、1ビット当たり1本の信号線を用いてシングルエンド形式で転送を行っても構わない。但し、高速な信号転送においては、ディファレンシャル形式を採用することが好ましい。

【0022】

また、図1に示す例では、データ信号及びアドレスコマンド信号をいずれも1ビットずつ転送する回路構成であるが、本発明がこれに限定されるものではない。したがって、例えばデータ配線を複数対使用し、複数ビットずつ転送しても構わない。

【0023】

インターフェース回路部IFC1に含まれるマルチプレクサMUX0、デマルチプレクサDMUX0及びデマルチプレクサDMUXacは、クロック生成部CKGEN1に含まれるDLL回路100,101,102から出力される多相クロック信号DTCK1,DRCK1,ARCK1によってそれぞれ制御される。これらDLL回路100,101,102は、それぞれディレイ回路200,201,202によってタイミング調整されたグローバルクロック信号GCKを受け、これに基づいて多相クロック信号DTCK1,DRCK1,ARCK1をそれぞれ生成する。本例では、DLL回路100,101が生成する多相クロック信号DTCK1,DRCK1はn相の多相クロック信号であり、DLL回路102が生成する多相クロック信号ARCK1はm相の多相クロック信号である。n相の多相クロック信号は、互いに位相の異なるn個のクロック信号φ1〜φnからなり、各クロック信号φ1〜φnの周期がグローバルクロック信号GCKの周期と等しい。m相の多相クロック信号は、互いに位相の異なるm個のクロック信号φ1〜φmからなり、各クロック信号φ1〜φmの周期がグローバルクロック信号GCKの周期と等しい。

【0024】

同様に、インターフェース回路部IFC2に含まれるマルチプレクサMUX0c、デマルチプレクサDMUX0c及びマルチプレクサMUXacは、クロック生成部CKGEN2に含まれるDLL回路300,301,302から出力される多相クロック信号DTCK2,DRCK2,ARCK2によってそれぞれ制御される。これらDLL回路300,301,302は、それぞれディレイ回路400,401,402によってタイミング調整されたグローバルクロック信号GCKを受け、これに基づいて多相クロック信号DTCK2,DRCK2,ARCK2をそれぞれ生成する。本例では、DLL回路300,301が生成する多相クロック信号DTCK2,DRCK2はn相の多相クロック信号であり、DLL回路302が生成する多相クロック信号ARCK2はm相の多相クロック信号である。

【0025】

図2は、マルチプレクサMUX0の一部分を示す回路図である。

【0026】

図2には、データバスDBUS1を介して供給されるパラレルなnビットのデータ信号をシリアルな非反転信号DT(トゥルー信号)に変換する回路部分が示されている。その他、マルチプレクサMUX0には、nビットのデータ信号をシリアルな反転信号(バー信号)に変換する回路部分も含まれているが、これについては図示を省略する。

【0027】

図2に示す回路部分は、n個の入力ノードN1〜Nnと1個の出力ノードN0を有しており、各入力ノードN1〜Nnと出力ノードN0との間にそれぞれ対応するn個のスイッチSW1〜SWnが挿入された構成を有している。スイッチSW1〜SWnは、多相クロック信号DTCK1を構成するn相のクロック信号φ1〜φnによってそれぞれ制御される。入力ノードN1〜Nnは、データバスDBUS1を構成する複数の配線にそれぞれ接続されるノードである。また、出力ノードN0は、データ配線TLDTに接続されるノードである。

【0028】

図3は、マルチプレクサMUX0の動作を説明するためのタイミング図である。

【0029】

図3に示すように、多相クロック信号DTCK1を構成するn相のクロック信号φ1〜φnは、互いに位相がずれており、且つ、ハイレベルの期間が互いに重複しない波形を有している。各クロック信号φ1〜φnの周期はいずれもグローバルクロック信号GCKの周期と同じである。これにより、図2に示した入力ノードN1〜Nnにパラレルに入力されるデータ信号は、n相のクロック信号φ1〜φnに同期して出力ノードN0に順次送出される。その結果、グローバルクロック信号GCKの1サイクルごとに、パラレルなnビットのデータ信号がシリアルに変換されることになる。

【0030】

デマルチプレクサDMUX0の回路構成は、入力側と出力側が逆になる他は図2に示した回路と同様である。したがって、1個の入力ノードN0とn個の出力ノードN1〜Nnを有し、入力ノードN0と各出力ノードN1〜Nnとの間にそれぞれ対応するn個のスイッチSW1〜SWnが挿入される。これにより、入力ノードN0にシリアルに入力されるデータ信号は、n相のクロック信号φ1〜φnに同期して出力ノードN1〜Nnに順次送出される。その結果、グローバルクロック信号GCKの1サイクルごとに、シリアルなnビットのデータ信号がパラレルに変換されることになる。

【0031】

図4は、本実施形態による情報処理システム2のリード動作を説明するためのタイミング図である。

【0032】

リード動作は、コントローラである半導体装置4からDRAMである半導体装置10に対してリードコマンドを発行し、これに応答してDRAMである半導体装置10からコントローラである半導体装置4に対してリードデータを供給する動作である。図4に示す例では、時刻t11〜t13の期間において、アドレスコマンドバスACBUS2上のパラレルなアドレスコマンド信号がマルチプレクサMUXacによってシリアルに変換されている。かかるアドレスコマンド信号は少なくともアクティブコマンド及びロウアドレスを含んでおり、図4においては「Row」と表記されている。シリアルに変換されたアドレスコマンド信号Rowは、アドレスコマンド配線TLACT,TLACBを介して半導体装置4から半導体装置10に転送される。

【0033】

半導体装置10側においては、時刻t12〜t14の期間において、アドレスコマンド配線TLACT,TLACBから転送されるシリアルなアドレスコマンド信号RowがデマルチプレクサDMUXacによってパラレルに変換される。時刻t12,t14は、アドレスコマンド配線TLACT,TLACBを介した転送時間を考慮して、それぞれ時刻t11,t13に対して僅かな遅れを有している。かかる遅れは、ディレイ回路202,402によって調整される。このようにして再生されたパラレルなアドレスコマンド信号Rowは、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。主回路部MCRは、これに応答して図示しないメモリセルアレイに対してロウアクセスを行う。

【0034】

時刻t13から所定の時間が経過した後、時刻t21〜t23の期間において、アドレスコマンドバスACBUS2上のパラレルなアドレスコマンド信号がマルチプレクサMUXacによってシリアルに変換される。かかるアドレスコマンド信号は少なくともリードコマンド及びカラムアドレスを含んでおり、図4においては「Column」と表記されている。シリアルに変換されたアドレスコマンド信号Columnは、アドレスコマンド配線TLACT,TLACBを介して半導体装置4から半導体装置10に転送される。

【0035】

半導体装置10側においては、時刻t22〜t24の期間において、アドレスコマンド配線TLACT,TLACBから転送されるシリアルなアドレスコマンド信号ColumnがデマルチプレクサDMUXacによってパラレルに変換される。時刻t22,t24は、それぞれ時刻t21,t23に対して僅かな遅れを有しており、かかる遅れはディレイ回路202,402によって調整される。このようにして再生されたパラレルなアドレスコマンド信号Columnは、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。主回路部MCRは、これに応答して図示しないメモリセルアレイに対してカラムアクセスを行う。

【0036】

メモリセルアレイに対してロウアクセス及びカラムアクセスをこの順で行うと、当該ロウアドレス及びカラムアドレスによって指定されるメモリセルから読み出されたnビットのリードデータが主回路部MCRから出力される。主回路部MCRから出力されるnビットのリードデータは、データバスDBUS1を介してマルチプレクサMUX0にパラレルに供給される。図4においては、リードデータを「ReadData」と表記している。

【0037】

時刻t24から所定の時間が経過した後、時刻t31〜t33の期間において、データバスDBUS1上のパラレルなリードデータReadDataがマルチプレクサMUX0によってシリアルに変換される。シリアルに変換されたリードデータReadDataは、データ配線TLDT,TLDBを介して半導体装置10から半導体装置4に転送される。

【0038】

半導体装置4側においては、時刻t32〜t34の期間において、データ配線TLDT,TLDBから転送されるシリアルなリードデータReadDataがデマルチプレクサDMUXcによってパラレルに変換される。時刻t32,t34は、それぞれ時刻t31,t33に対して僅かな遅れを有しており、かかる遅れはディレイ回路200,401によって調整される。このようにして再生されたパラレルなリードデータReadDataは、データバスDBUS2を介して主回路部LCRに供給される。これにより、一連のリード動作が完了する。

【0039】

ライト動作は、データ信号の転送方向が半導体装置4から半導体装置10に変わる他は、上述したリード動作と基本的に同じである。この場合、半導体装置4がライトデータの送信を開始するタイミング及び終了するタイミングに対して、半導体装置10がライトデータの受信を開始するタイミング及び終了するタイミングが僅かに遅延される。かかる遅れはディレイ回路201,400によって調整される。

【0040】

図5は、半導体装置10の全体構成を示すブロック図である。

【0041】

半導体装置10は上述の通り例えばDRAMであり、メモリセルアレイ11を有している。メモリセルアレイ11は、複数のワード線WLと複数のビット線BLを備え、これらの交点にメモリセルMCが配置された構成を有している。ワード線WLの選択はロウデコーダ12によって行われ、ビット線BLの選択はカラムデコーダ13によって行われる。

【0042】

図5に示すように、半導体装置10には外部端子としてアドレスコマンド端子ACT,ACB、クロック端子CK、データ端子DQ(DQ0T/B〜DQpT/B)及び電源端子Vが設けられている。

【0043】

アドレスコマンド端子ACT,ACBは、それぞれアドレスコマンド配線TLACT,TLACBに接続される端子であり、半導体装置4からアドレスコマンド信号が入力される。アドレスコマンド端子ACT,ACBに入力されたシリアルなアドレスコマンド信号は、デマルチプレクサDMUXacによってパラレルなアドレス信号ADDとパラレルなコマンド信号CMDに変換される。図5に示す例では、アドレス信号ADDはr+1ビットのアドレスビットA0〜Arからなる。また、コマンド信号CMDはロウアドレスストローブ信号RASB、カラムアドレスストローブ信号CASB、ライトイネーブル信号WEBなどの信号の組み合わせからなる。

【0044】

アドレス信号ADDは、アドレスラッチ回路21にラッチされる。アドレスラッチ回路21にラッチされたアドレス信号A0〜Arは、ロウデコーダ12、カラムデコーダ13又はモードレジスタ14に供給される。モードレジスタ14は、半導体装置10の動作モードを示すパラメータが設定される回路である。

【0045】

コマンド信号CMDは、コマンドデコード回路22に供給される。コマンドデコード回路22は、コマンド信号CMDをデコードすることによって各種内部コマンドを生成する回路である。内部コマンドとしては、アクティブ信号IACT、カラム信号ICOL、リフレッシュ信号IREF、モードレジスタセット信号MRSなどがある。

【0046】

アクティブ信号IACTは、コマンド信号CMDがロウアクセス(アクティブコマンド)を示している場合に活性化される信号である。アクティブ信号IACTが活性化すると、アドレスラッチ回路21にラッチされたアドレス信号ADDがロウデコーダ12に供給される。これにより、当該アドレス信号ADDにより指定されるワード線WLが選択される。

【0047】

カラム信号ICOLは、コマンド信号CMDがカラムアクセス(リードコマンド又はライトコマンド)を示している場合に活性化される信号である。内部カラム信号ICOLが活性化すると、アドレスラッチ回路21にラッチされたアドレス信号ADDがカラムデコーダ13に供給される。これにより、当該アドレス信号ADDにより指定されるビット線BLが選択される。

【0048】

したがって、アクティブコマンド及びリードコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力すれば、これらロウアドレス及びカラムアドレスによって指定されるメモリセルMCからリードデータが読み出される。リードデータは、データバスDBUS1−0〜DBUS1−pを介して、マルチプレクサMUX0〜MUXpに供給される。マルチプレクサMUX0〜MUXpは、多相クロック信号DTCK1に同期してパラレルなリードデータをシリアル変換し、それぞれ対応するデータ端子対DQ0T/B〜DQpT/Bに出力する。データ端子対DQ0T/B〜DQpT/Bは、それぞれ対応するデータ配線(TLDT0,TLDB0,TLDT1,TLDB1・・)に接続されている。

【0049】

一方、アクティブコマンド及びライトコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力し、その後、データ端子対DQ0T/B〜DQpT/Bにライトデータをシリアルに入力すれば、多相クロック信号DRCK1に同期してシリアルなライトデータがマルチプレクサDMUX0〜DMUXpによりパラレルに変換される。パラレルに変換されたライトデータは、データバスDBUS1−0〜DBUS1−pを介してメモリセルアレイ11に供給され、ロウアドレス及びカラムアドレスによって指定されるメモリセルMCに書き込まれる。

【0050】

リフレッシュ信号IREFは、コマンド信号CMDがリフレッシュコマンドを示している場合に活性化される信号である。リフレッシュ信号IREFが活性化するとリフレッシュ制御回路23によってロウアクセスが行われ、所定のワード線WLが選択される。これにより、選択されたワード線WLに接続された複数のメモリセルMCがリフレッシュされる。ワード線WLの選択は、リフレッシュ制御回路23に含まれる図示しないリフレッシュカウンタによって行われる。

【0051】

モードレジスタセット信号MRSは、コマンド信号CMDがモードレジスタセットコマンドを示している場合に活性化される信号である。したがって、モードレジスタセットコマンドを入力するとともに、これに同期してアドレスコマンド端子ACT,ACBからモード信号を入力すれば、モードレジスタ14の設定値を書き換えることができる。

【0052】

クロック端子CNは、グローバルクロック信号GCKが入力される端子である。半導体装置10に取り込まれたグローバルクロック信号GCKは、半導体装置10の内部における基本クロック信号として用いられ、本明細書においては内部グローバルクロック信号IGCKと表記する。内部グローバルクロック信号IGCKは、コマンドデコード回路22に供給される他、ディレイ回路200〜202に供給される。ディレイ回路200〜202は、内部グローバルクロック信号IGCKのタイミングを微調整するための回路であり、その出力はそれぞれDLL回路100〜102に供給される。

【0053】

DLL回路100〜102は、タイミング調整された内部グローバルクロック信号IGCKに基づいて、それぞれ多相クロック信号DTCK1,DRCK1,ARCK1を生成する回路である。多相クロック信号DTCK1はマルチプレクサMUX0〜MUXpに供給され、パラレルなリードデータをシリアル変換するタイミングを規定する同期信号として用いられる。多相クロック信号DRCK1はデマルチプレクサDMUX0〜DMUXpに供給され、シリアルなライトデータをパラレル変換するタイミングを規定する同期信号として用いられる。多相クロック信号ARCK1はデマルチプレクサDMUXacに供給され、シリアルなアドレスコマンド信号をパラレル変換するタイミングを規定する同期信号として用いられる。

【0054】

電源端子Vは、電源電位VDD,VSSが供給される端子である。電源端子Vに供給される電源電位VDD,VSSは内部電源発生回路24に供給される。内部電源発生回路24は、電源電位VDD,VSSに基づいて各種の内部電位VPP,VPERD,VPERIなどを発生させる。内部電位VPPは主にロウデコーダ12において使用される電位であり、内部電位VPERDは主にDLL回路100〜102において使用される電位であり、内部電位VPERIは他の多くの回路ブロックにおいて使用される電位である。

【0055】

図6は、DLL回路100の回路図である。

【0056】

図6に示すように、DLL回路100は、ディレイライン110と、ディレイライン110の遅延量を制御する制御回路120と、ディレイライン110から出力される出力クロック信号Node1〜Nodenを並べ替えるルーティング回路130と、ルーティング回路130から出力される多相クロック信号CK1〜CKnの波形を整形することにより多相クロック信号DTCK1を生成する整形回路140とを備える。

【0057】

ディレイライン110は、縦列接続されたn個の遅延回路UD1〜UDnからなり、その初段である遅延回路UD1には、タイミング調整された内部グローバルクロック信号IGCKが入力される。本発明においては、遅延回路UD1に入力される内部グローバルクロック信号IGCKを「入力クロック信号」と呼ぶことがある。これらn個の遅延回路UD1〜UDnは縦列接続されているため、これら遅延回路UD1〜UDnから出力される出力クロック信号Node1〜Nodenは、この順に位相が遅れる。本例では、出力クロック信号Node1〜Nodenが全てルーティング回路130に入力されているが、出力クロック信号Node1〜Nodenの一部のみをルーティング回路130に入力しても構わない。

【0058】

最終段の遅延回路UDnから出力される出力クロック信号Nodenの位相は、初段の遅延回路UD1に入力される内部グローバルクロック信号IGCKに対して、正確にk周期遅れている。かかる制御は、制御回路120によって行われる。図6に示すように、制御回路120は、分周回路121、位相判定回路122及び制御電圧生成回路123を備えている。

【0059】

分周回路121は、出力クロック信号Noden及び内部グローバルクロック信号IGCKをk分周する回路である。分周回路121から出力される分周クロック信号GCKsは、内部グローバルクロック信号IGCKをk分周した信号であり、分周回路121から出力される分周クロック信号CKosは、出力クロック信号Nodenをk分周した信号である。これら分周クロック信号GCKs,CKosは位相判定回路122に供給され、両者の位相が判定される。判定の結果、分周クロック信号CKosの位相が分周クロック信号GCKsに対して遅れている場合(つまりディレイライン110の遅延量が大きすぎる場合)、位相判定回路122はアップ信号UPBをローレベルに活性化させる。このとき、ダウン信号DNTはローレベルに非活性化される。これにより、制御電圧生成回路123に含まれるPチャンネル型MOSトランジスタ123Pがオンするため、キャパシタ123Cにチャージされる制御電圧VDLYが上昇する。後述するように、制御電圧VDLYが上昇するとディレイライン110の遅延量は少なくなる。

【0060】

逆に、分周クロック信号CKosの位相が分周クロック信号GCKsに対して進んでいる場合(つまりディレイライン110の遅延量が小さすぎる場合)、位相判定回路122はダウン信号DNTをハイレベルに活性化させる。このとき、アップ信号UPBはハイレベルに非活性化される。これにより、制御電圧生成回路123に含まれるNチャンネル型MOSトランジスタ123Nがオンするため、キャパシタ123Cにチャージされる制御電圧VDLYが低下する。後述するように、制御電圧VDLYが低下するとディレイライン110の遅延量は大きくなる。

【0061】

このようなフィードバック制御により、出力クロック信号Nodenの位相が内部グローバルクロック信号IGCKに対して正確にk周期遅れるよう、ディレイライン110の遅延量が調整される。

【0062】

図7は、遅延回路UD1の回路図である。他の遅延回路UD2〜UDnも図7に示す遅延回路UD1と同じ回路構成を有している。

【0063】

図7に示すように、遅延回路UD1は、直列接続された2段のインバータINV1,INV2からなる。インバータINV1,INV2の低位側電源ノードVNと接地電位VSSとの間には、調整トランジスタTDLYが挿入されており、そのゲート電極には制御電圧VDLYが供給される。このため、インバータINV1,INV2のスイッチング速度は制御電圧VDLYに依存する。具体的には、制御電圧VDLYが高いほどインバータINV1,INV2のスイッチング速度が早くなるため、遅延回路UD1による遅延量は低下する。逆に、制御電圧VDLYが低いほどインバータINV1,INV2のスイッチング速度が遅くなるため、遅延回路UD1による遅延量は増大する。

【0064】

図8は、制御電圧VDLYと遅延回路UD1の遅延量δとの関係を示すグラフである。

【0065】

図8に示す遅延量δは、入力クロック信号(内部グローバルクロック信号IGCK)と出力クロック信号(Node1)との時間差である。図8に示すように、制御電圧VDLYが高くなれば基本的に遅延量δは小さくなるが、遅延量δを無限に小さくできるわけではなく、最小の遅延量δMINが存在する。つまり、制御電圧VDLYをいくら大きくしても、遅延回路UD1の遅延量をδMIN未満とすることはできない。このことは、出力クロック信号Node1〜Nodenをこの順に並べた場合、相間隔の最小値がδMINとなることを意味する。したがって、k=1であるとすると、多相クロック信号DTCK1の相間隔の最小値もδMINに制限される。しかしながら、本実施形態においてはkが2以上の整数値であり、且つ、ディレイライン110を構成する遅延回路の段数nとは異なる値に設定されるため、多相クロック信号DTCK1の相間隔をδMIN未満とすることが可能とされている。その詳細については後述する。

【0066】

図9は、分周回路121の一部を示す回路図である。

【0067】

図9に示す回路は、内部グローバルクロック信号IGCKから分周クロック信号GCKsを生成する回路部分を示しており、一例として、k=3である場合の回路図である。図9に示す例では、JK型のフリップフロップ回路FF1,FF2が循環接続された構成を有している。フリップフロップ回路FF1,FF2のクロックノードには内部グローバルクロック信号IGCKが供給されており、これにより、内部グローバルクロック信号IGCKの立ち上がりエッジが3回入力される度に、分周クロック信号GCKsの立ち上がりエッジが1回生成される。

【0068】

図10は、位相判定回路122の回路図である。

【0069】

図10に示す位相判定回路122は、データラッチ型のフリップフロップ回路FF3,FF4を備えている。フリップフロップ回路FF3のクロックノードには分周クロック信号GCKsが入力され、フリップフロップ回路FF4のクロックノードには分周クロック信号CKosが入力される。そして、フリップフロップ回路FF3,FF4がそれぞれセット状態及びリセット状態であればアップ信号UPBがローレベルに活性化し、フリップフロップ回路FF3,FF4がそれぞれリセット状態及びセット状態であればダウン信号DNTがハイレベルに活性化する。これにより、分周クロック信号GCKs,CKosのいずれの立ち上がりエッジが先に到来するかによって、アップ信号UPB及びダウン信号DNTのいずれか一方が活性化する。フリップフロップ回路FF3,FF4の両方がセットされると、これらフリップフロップ回路FF3,FF4はリセットされる。

【0070】

以上がDLL回路100の回路構成である。他のDLL回路101,102についてもDLL回路100と同じ回路構成を有している。以下、n=5,k=3である場合を例に、DLL回路100の動作を説明する。上述の通り、nとはディレイライン110を構成する遅延回路UD1〜UDnの数であり、kとは分周回路121の分周数である。追って説明するが、nの値とkの値はいずれも2以上の整数であり、且つ、最大公約数が1であることが好ましい。以下説明するn=5,k=3の例は、この条件を満たしている。

【0071】

図11はDLL回路100の動作を説明するためのタイミング図であり、n=5,k=3である場合を示している。

【0072】

図11に示す例ではn=5であることから、最終段の遅延回路UD5から出力される出力クロック信号Node5は、初段の遅延回路UD1に入力される内部グローバルクロック信号IGCKに対して正確に3周期分遅延する。そして、3周期分の遅延を発生させるために5段の遅延回路UD1〜UD5を経由することから、出力クロック信号Node1〜Node5をこの順に並べた場合、相間隔は3GCK/5となる。ここでいう「GCK」とは内部グローバルクロック信号IGCKの1サイクルを意味する。

【0073】

具体的に説明すると、時刻t40における内部グローバルクロック信号IGCKの立ち上がりエッジは、遅延回路UD1によって3GCK/5だけ遅延され、これにより時刻t40から3GCK/5だけ遅延した時刻t41において出力クロック信号Node1の立ち上がりエッジが現れる。時刻t41における出力クロック信号Node1の立ち上がりエッジは、遅延回路UD2によってさらに3GCK/5だけ遅延され、これにより時刻t40から6GCK/5だけ遅延した時刻t42において出力クロック信号Node2の立ち上がりエッジが現れる。時刻t42における出力クロック信号Node2の立ち上がりエッジは、遅延回路UD3によってさらに3GCK/5だけ遅延され、これにより時刻t40から9GCK/5だけ遅延した時刻t43において出力クロック信号Node3の立ち上がりエッジが現れる。時刻t43における出力クロック信号Node3の立ち上がりエッジは、遅延回路UD4によってさらに3GCK/5だけ遅延され、これにより時刻t40から12GCK/5だけ遅延した時刻t44において出力クロック信号Node4の立ち上がりエッジが現れる。そして、時刻t44における出力クロック信号Node4の立ち上がりエッジは、遅延回路UD5によってさらに3GCK/5だけ遅延され、これにより時刻t40から3GCKだけ遅延した時刻t45において出力クロック信号Node5の立ち上がりエッジが現れる。

【0074】

ここで、内部グローバルクロック信号IGCKの図11に示す最後の1サイクル(時刻t51〜時刻45)に注目すると、この期間内に出力クロック信号Node1〜Node5の立ち上がりエッジが全て出現していることが分かる。具体的には、時刻t51に出力クロック信号Node5の立ち上がりエッジが出現し、時刻t51からGCK/5だけ遅れた時刻t52に出力クロック信号Node2の立ち上がりエッジが出現し、時刻t52からさらにGCK/5だけ遅れた時刻t44に出力クロック信号Node4の立ち上がりエッジが出現し、時刻t44からさらにGCK/5だけ遅れた時刻t54に出力クロック信号Node1の立ち上がりエッジが出現し、時刻t54からさらにGCK/5だけ遅れた時刻t55に出力クロック信号Node3の立ち上がりエッジが出現している。

【0075】

したがって、出力クロック信号Node1〜Node5を上記の順番で並べ替えれば、相間隔がGCK/5に縮小されることになる。このことは、最小の遅延量δMINがk×GCK/n(3GCK/5)であっても、より小さい相間隔(GCK/5)が得られることを意味する。出力クロック信号Node1〜Node5の並べ替えは、ルーティング回路130によって行われる。

【0076】

図12は、ルーティング回路130の機能を説明するための配線図である。

【0077】

図12に示す配線図では、出力クロック信号Node1〜Node5がそれぞれ多相クロック信号CK4,CK2,CK5,CK3,CK1に割り当てられる。このようなルーティングは、固定的な配線を用いて実現することが可能である。この場合、ルーティング回路130は単なる配線によって構成することができる。但し、nの値やkの値を可変とするためには、ルーティング回路130を固定的な配線によって構成するのではなく、割り当てを変更可能とする必要がある。

【0078】

図13は、割り当てを変更可能なルーティング回路130の機能を説明するための模式図である。

【0079】

図13においては、出力クロック信号Node1〜Node5の配線が横方向に延在し、多相クロック信号CK1〜CK5の配線が縦方向に延在している。そして、黒丸で示された交点は横方向の配線と縦方向の配線が接続されていることを意味し、白丸で示された交点は横方向の配線と縦方向の配線が接続されていないことを意味する。図13に示す例においても、出力クロック信号Node1〜Node5がそれぞれ多相クロック信号CK4,CK2,CK5,CK3,CK1に割り当てられており、結果としては図12に示すルーティング回路130と同じである。しかしながら、出力クロック信号Node1〜Node5をそれぞれどの多相クロック信号CK1〜CK5として使用するか、切り替えることが可能である点において、図12に示したルーティング回路130と相違する。

【0080】

図14は、図13に示す領域Xの回路図である。

【0081】

図14に示す例では、各交点にトランスファゲートTGが設けられている。これにより、横方向の配線と縦方向の配線との接続の有無を切り替え可能とされている。トランスファゲートTGの切り替えは、モードレジスタ14から供給されるモード信号MODEによって行うことができる。このような回路構成とすれば、出力クロック信号Node1〜Node5を任意の多相クロック信号CK1〜CK5に割り当てることが可能となる。

【0082】

図15は整形回路140の回路図であり、図16は整形回路140の動作波形図である。

【0083】

図16に示すように、多相クロック信号CK1〜CK5は内部グローバルクロック信号IGCKと同じデューティを有しているため、そのままではハイレベルの期間が重複してしまう。図15に示す整形回路140は、多相クロック信号CK1〜CK5のうち、位相の隣接する2つの多相クロック信号が同時にハイレベルとなるのを禁止する。これにより、多相クロック信号φ1〜φ5のそれぞれは、対応する多相クロック信号CK1〜CK5の立ち上がりエッジに連動して立ち上がり、次の多相クロック信号の立ち上がりエッジに連動して立ち下がる波形となる。その結果、図16に示すように、多相クロック信号φ1〜φ5は、互いにハイレベルとなる期間が除去された波形となる。

【0084】

このようにして生成された多相クロック信号DTCK1は、図5に示したマルチプレクサMUX0〜MUXpに供給され、そのタイミング信号として用いられる。以上、DLL回路100に着目して説明を進めたが、他のDLL回路101,102回路構成及び動作もDLL回路100と同様である。

【0085】

本実施形態においては、基本となる内部グローバルクロック信号IGCKをn個の遅延回路UD1〜UDnによってkサイクル遅延させていることから、1つの遅延回路における最小の遅延量δMINよりも小さい相間隔を有する多相クロック信号を簡単な回路構成で生成することが可能となる。より具体的には、nとkの最大公約数をGCM、内部グローバルクロック信号IGCKの1サイクルをGCK、多相クロック信号の相間隔をUIとした場合、相間隔UIの長さを、

UI=GCK×GCM/n

とすることができる。これにより、マルチプレクサ及びデマルチプレクサは、内部グローバルクロック信号IGCKのGCM/nサイクル毎にデータ信号を順次取り込むことができる。このことは、内部グローバルクロック信号IGCKの1サイクルでnビットのデータ信号を取り込めることを意味する。上述した実施形態では、GCM=1、n=5であることから、

UI=GCK/5

となる。これにより、マルチプレクサ及びデマルチプレクサは、内部グローバルクロック信号IGCKの1/5サイクル毎にデータ信号を順次取り込むことができることから、内部グローバルクロック信号IGCKの1サイクルで5ビットのデータ信号を取り込むことが可能となる。

【0086】

相間隔UIをより小さくするためにはnの値を大きくすればよいが、nとkの最大公約数GCMが2以上であると相間隔UIが大きくなることから、最大公約数GCMについては1とすることが好ましい。最大公約数GCMが2以上である場合、遅延回路UD1〜UDnから出力されるn個の出力クロック信号Node1〜Nodenの一部の位相が重複するからである。これに対し、最大公約数GCMが1であれば、遅延回路UD1〜UDnから出力されるn個の出力クロック信号Node1〜Nodenは互いに異なる位相となる。

【0087】

最大公約数GCMが1となるnとkの組み合わせについては任意であり、上記の例(n=5,k=3)のように両方が奇数であっても構わないし、n=34,k=3のように一方が偶数であっても構わない。

【0088】

また、図11を用いて説明したように、遅延回路UD1〜UDnの1個あたりの遅延量k×GCK/nは、遅延量の最小値δMIN以上である必要がある。つまり、

δMIN≦k×GCK/n

を満足する必要がある。したがって、相間隔UIをより小さくするためにnの値を大きくする場合には、上記の式を満足するようkの値を設定する必要がある。

【0089】

nとkの大小関係については特に限定されないが、n>kであることが好ましい。最大公約数GCMが1である限り、kの値は相間隔UIとは無関係であるが、kの値が大きくなるとディレイライン110の全体の遅延量も大きくなるため、遅延回路UD1〜UDnの1個あたりの遅延量を大きくする必要がある。この場合、遅延回路UD1〜UDnによる波形の鈍りが大きくなり、クロックの精度が低下するおそれがある。この点を考慮すれば、

δMIN≦k×GCK/n

を満足する範囲内で、kの値はできる限り小さく設定することが好ましい。

【0090】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0091】

例えば、生成した多相クロック信号φ1〜φnの全てをマルチプレクサ又はデマルチプレクサにて使用することは必須でなく、一部のみを使用しても構わない。例えば、上記実施形態のように多相クロック信号φ1〜φ5が5相のクロック信号である場合であっても、このうち4つの多相クロック信号φ1〜φ4のみをマルチプレクサ又はデマルチプレクサに供給しても構わない。

【0092】

また、上述した実施形態では、3種類の多相クロック信号(例えばDTCK1,DRCK1,ARCK1)をそれぞれ別個のDLL回路によって生成しているが、1つのDLL回路の出力をこれら多相クロック信号として共用しても構わない。これによれば、チップ上におけるDLL回路の占有面積が削減されるため、各多相クロック信号の位相を微調整する必要がない場合には好適である。

【符号の説明】

【0093】

2 情報処理システム

4,10 半導体装置

6 クロックジェネレータ

11 メモリセルアレイ

12 ロウデコーダ

13 カラムデコーダ

14 モードレジスタ

21 アドレスラッチ回路

22 コマンドデコード回路

23 リフレッシュ制御回路

24 内部電源発生回路

100〜102,300〜302 DLL回路

200〜202,400〜402 ディレイ回路

110 ディレイライン

120 制御回路

121 分周回路

122 位相判定回路

123 制御電圧生成回路

123C キャパシタ

123N,123P トランジスタ

130 ルーティング回路

140 整形回路

ACBUS1,ACBUS2 アドレスコマンドバス

ACT,ACB アドレスコマンド端子

DTCK1,DRCK1,ARCK1,DTCK2,DRCK2,ARCK2 多相クロック信号

CKGEN1,CKGEN2 クロック生成部

CN クロック端子

DBUS1,DBUS2 データバス

DMUX0,DMUX0c,DMUXac デマルチプレクサ

DQ データ端子

GCK グローバルクロック信号

GCKs,CKos 分周クロック信号

IFC1,IFC2 インターフェース回路部

IGCK 内部グローバルクロック信号

LCR,MCR 主回路部

MUX0,MUX0c,MUXac マルチプレクサ

Node1〜Noden 出力クロック信号

TLACT,TLACB アドレスコマンド配線

TLDT,TLDB データ配線

UD1〜UDn 遅延回路

V 電源端子

【技術分野】

【0001】

本発明は半導体装置及びこれを用いた情報処理システムに関し、特に、互いに位相の異なる多相クロック信号を使用する半導体装置及びこれを用いた情報処理システムに関する。

【背景技術】

【0002】

半導体装置の多くはクロック信号に同期して動作するタイプの半導体装置であるが、中には、互いに位相の異なる多相クロック信号を用いるものが存在する。多相クロック信号の相間隔は、基準となるクロック信号の周期よりも短いため、このような多相クロック信号をどのような方法で生成するかが問題となる。

【0003】

相間隔の短い多相クロック信号を生成する回路として、特許文献1には、異なる遅延量を有する複数種類の遅延素子を縦列接続した回路が開示されている。特許文献1に記載された多相クロック生成回路によれば、多相クロック信号の相間隔を遅延素子1段分の最小遅延時間よりも短くすることが可能となる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−16545号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載された多相クロック生成回路では、多相クロック信号の一つを生成するために多数の遅延素子が必要である。このため、全体としてかなり多くの遅延素子を用いる必要があり、回路規模が非常に大きくなるというデメリットがあった。

【0006】

半導体装置が処理すべきデータ量は年々大きくなり、その処理速度は高速化する傾向にある。本発明はそのような膨大なデータ量を高速に処理し、且つ必要となる回路規模が小さく抑えられた情報処理システム、及びそのシステムに含まれる半導体装置を提供することを課題とするものである。

【課題を解決するための手段】

【0007】

本発明の一側面による半導体装置は、互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路とを備えることを特徴とする。

【0008】

本発明による情報処理システムは、第1及び第2の半導体装置と、前記第1の半導体装置と前記第2の半導体装置を接続するデータ配線とを備え、前記第1及び第2の半導体装置はいずれも上述の半導体装置であり、前記第1の半導体装置の内部でパラレルに伝送される前記複数のデータ信号は、前記第1の半導体装置に設けられた前記データ処理回路によってシリアルに変換されて前記データ配線に出力され、前記データ配線を介して前記第2の半導体装置にシリアルに供給される前記複数のデータ信号は、前記第2の半導体装置に設けられた前記データ処理回路によってパラレルに変換されることを特徴とする。

【0009】

本発明の他の側面による半導体装置は、縦列接続されたn個の遅延回路からなり、入力クロック信号をk周期遅延させるディレイラインと、前記n個の遅延回路からそれぞれ出力されるn個の出力クロック信号の少なくとも一部に基づいて、互いに位相の異なる多相クロック信号を生成するルーティング回路と、を備え、前記n及びkはいずれも2以上の整数であり、最大公約数が1であることを特徴とする。

【発明の効果】

【0010】

本発明によれば、短い相間隔を有する多相クロック信号をしていることから、生成された多相クロック信号をタイミング信号として用いれば、高速なデータ転送が可能となる。特に、kを2以上の整数値とし、且つ、nとは異なる値に設定すれば、遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の好ましい実施形態による情報処理システム2の構成を示すブロック図である。

【図2】マルチプレクサMUX0の一部分を示す回路図である。

【図3】マルチプレクサMUX0の動作を説明するためのタイミング図である。

【図4】情報処理システム2のリード動作を説明するためのタイミング図である。

【図5】半導体装置10の全体構成を示すブロック図である。

【図6】DLL回路100の回路図である。

【図7】遅延回路UD1の回路図である。

【図8】制御電圧VDLYと遅延回路UD1の遅延量δとの関係を示すグラフである。

【図9】分周回路121の一部を示す回路図である。

【図10】位相判定回路122の回路図である。

【図11】DLL回路100の動作を説明するためのタイミング図である。

【図12】ルーティング回路130の機能を説明するための配線図である。

【図13】割り当てを変更可能なルーティング回路130の機能を説明するための模式図である。

【図14】図13に示す領域Xの回路図である。

【図15】整形回路140の回路図である。

【図16】整形回路140の動作波形図である。

【発明を実施するための形態】

【0012】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0013】

図1は、本発明の好ましい実施形態による情報処理システム2の構成を示すブロック図である。

【0014】

図1に示す情報処理システム2は、半導体装置4と半導体装置10がデータ配線TLDT,TLDB及びアドレスコマンド配線TLACT,TLACBを介して接続された構成を有している。特に限定されるものではないが、半導体装置10はDRAM(Dynamic Random Access Memory)などのメモリデバイスであり、半導体装置4はこれを制御するコントローラである。半導体装置4,10には、クロックジェネレータ6からグローバルクロック信号GCKが共通に供給される。グローバルクロック信号GCKは、本実施形態による情報処理システム2の基準クロックとして用いられる信号である。

【0015】

図1に示すように、DRAMを構成する半導体装置10には、主回路部MCR、インターフェース回路部IFC1及びクロック生成部CKGEN1が含まれている。主回路部MCRは、メモリセルアレイ、デコーダなどDRAMに含まれるバックエンド回路である。同様に、コントローラを構成する半導体装置4には、主回路部LCR、インターフェース回路部IFC2及びクロック生成部CKGEN2が含まれている。主回路部LCRは、ロジック回路などコントローラに含まれるバックエンド回路である。

【0016】

半導体装置10に含まれるインターフェース回路部IFC1と、半導体装置4に含まれるインターフェース回路部IFC2は、互いに同様の回路構成を有している。具体的に説明すると、半導体装置10のインターフェース回路部IFC1には、データ用のマルチプレクサMUX0及びデマルチプレクサDMUX0と、アドレスコマンド用のデマルチプレクサDMUXacが設けられており、半導体装置4のインターフェース回路部IFC2には、データ用のマルチプレクサMUX0c及びデマルチプレクサDMUX0cと、アドレスコマンド用のマルチプレクサMUXacが設けられている。本発明においては、マルチプレクサ及びデマルチプレクサを「データ処理回路」と呼ぶことがある。

【0017】

データ用のマルチプレクサMUX0は、データバスDBUS1を介して主回路部MCRからパラレルに供給されるnビットのデータ信号をシリアル変換する回路であり、シリアルに変化されたデータ信号は、一対のデータ配線TLDT,TLDBを介して半導体装置4に入力される。半導体装置4に入力されたシリアルなデータ信号は、データ用のデマルチプレクサDMUX0cによってパラレル変換される。パラレルに変換されたデータ信号は、データバスDBUS2を介して主回路部LCRに供給される。

【0018】

同様に、データ用のマルチプレクサMUX0cは、データバスDBUS2を介して主回路部LCRからパラレルに供給されるnビットのデータ信号をシリアル変換する回路であり、シリアルに変化されたデータ信号は、一対のデータ配線TLDT,TLDBを介して半導体装置10に入力される。半導体装置10に入力されたシリアルなデータ信号は、データ用のデマルチプレクサDMUX0によってパラレル変換される。パラレルに変換されたデータ信号は、データバスDBUS1を介して主回路部MCRに供給される。

【0019】

一方、アドレスコマンド用のマルチプレクサMUXacは、アドレスコマンドバスACBUS2を介して主回路部LCRからパラレルに供給されるmビットのアドレスコマンド信号をシリアル変換する回路であり、シリアルに変化されたアドレスコマンド信号は、一対のアドレスコマンド配線TLACT,TLACBを介して半導体装置10に入力される。半導体装置10に入力されたシリアルなアドレスコマンド信号は、アドレスコマンド用のデマルチプレクサDMUXacによってパラレル変換される。パラレルに変換されたアドレスコマンド信号は、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。

【0020】

このように、本実施形態による情報処理システム2においては、半導体装置4と半導体装置10との間で送受信されるnビットのデータ信号は、送信側においてシリアル変換され、データ配線TLDT,TLDBを介してシリアルに転送される。そして、シリアルに転送されたデータ信号は、受信側においてパラレル変換される。同様に、半導体装置4から半導体装置10に供給されるmビットのアドレスコマンド信号は、送信側である半導体装置4においてシリアル変換され、アドレスコマンド配線TLACT,TLACBを介してシリアルに転送される。そして、シリアルに転送されたアドレスコマンド信号は、受信側である半導体装置10においてパラレル変換される。このようなシリアル転送を行っているのは、複数ビットからなる信号(本例では、nビットのデータ信号やmビットのアドレスコマンド信号)をパラレルに高速転送すると、送信側及び受信側においてビット間の同期を取ることが困難となるからである。

【0021】

尚、図1に示す例では、データ信号及びアドレスコマンド信号をいずれも一対の信号線を用いてディファレンシャル形式で転送しているが、本発明がこれに限定されるものではない。したがって、1ビット当たり1本の信号線を用いてシングルエンド形式で転送を行っても構わない。但し、高速な信号転送においては、ディファレンシャル形式を採用することが好ましい。

【0022】

また、図1に示す例では、データ信号及びアドレスコマンド信号をいずれも1ビットずつ転送する回路構成であるが、本発明がこれに限定されるものではない。したがって、例えばデータ配線を複数対使用し、複数ビットずつ転送しても構わない。

【0023】

インターフェース回路部IFC1に含まれるマルチプレクサMUX0、デマルチプレクサDMUX0及びデマルチプレクサDMUXacは、クロック生成部CKGEN1に含まれるDLL回路100,101,102から出力される多相クロック信号DTCK1,DRCK1,ARCK1によってそれぞれ制御される。これらDLL回路100,101,102は、それぞれディレイ回路200,201,202によってタイミング調整されたグローバルクロック信号GCKを受け、これに基づいて多相クロック信号DTCK1,DRCK1,ARCK1をそれぞれ生成する。本例では、DLL回路100,101が生成する多相クロック信号DTCK1,DRCK1はn相の多相クロック信号であり、DLL回路102が生成する多相クロック信号ARCK1はm相の多相クロック信号である。n相の多相クロック信号は、互いに位相の異なるn個のクロック信号φ1〜φnからなり、各クロック信号φ1〜φnの周期がグローバルクロック信号GCKの周期と等しい。m相の多相クロック信号は、互いに位相の異なるm個のクロック信号φ1〜φmからなり、各クロック信号φ1〜φmの周期がグローバルクロック信号GCKの周期と等しい。

【0024】

同様に、インターフェース回路部IFC2に含まれるマルチプレクサMUX0c、デマルチプレクサDMUX0c及びマルチプレクサMUXacは、クロック生成部CKGEN2に含まれるDLL回路300,301,302から出力される多相クロック信号DTCK2,DRCK2,ARCK2によってそれぞれ制御される。これらDLL回路300,301,302は、それぞれディレイ回路400,401,402によってタイミング調整されたグローバルクロック信号GCKを受け、これに基づいて多相クロック信号DTCK2,DRCK2,ARCK2をそれぞれ生成する。本例では、DLL回路300,301が生成する多相クロック信号DTCK2,DRCK2はn相の多相クロック信号であり、DLL回路302が生成する多相クロック信号ARCK2はm相の多相クロック信号である。

【0025】

図2は、マルチプレクサMUX0の一部分を示す回路図である。

【0026】

図2には、データバスDBUS1を介して供給されるパラレルなnビットのデータ信号をシリアルな非反転信号DT(トゥルー信号)に変換する回路部分が示されている。その他、マルチプレクサMUX0には、nビットのデータ信号をシリアルな反転信号(バー信号)に変換する回路部分も含まれているが、これについては図示を省略する。

【0027】

図2に示す回路部分は、n個の入力ノードN1〜Nnと1個の出力ノードN0を有しており、各入力ノードN1〜Nnと出力ノードN0との間にそれぞれ対応するn個のスイッチSW1〜SWnが挿入された構成を有している。スイッチSW1〜SWnは、多相クロック信号DTCK1を構成するn相のクロック信号φ1〜φnによってそれぞれ制御される。入力ノードN1〜Nnは、データバスDBUS1を構成する複数の配線にそれぞれ接続されるノードである。また、出力ノードN0は、データ配線TLDTに接続されるノードである。

【0028】

図3は、マルチプレクサMUX0の動作を説明するためのタイミング図である。

【0029】

図3に示すように、多相クロック信号DTCK1を構成するn相のクロック信号φ1〜φnは、互いに位相がずれており、且つ、ハイレベルの期間が互いに重複しない波形を有している。各クロック信号φ1〜φnの周期はいずれもグローバルクロック信号GCKの周期と同じである。これにより、図2に示した入力ノードN1〜Nnにパラレルに入力されるデータ信号は、n相のクロック信号φ1〜φnに同期して出力ノードN0に順次送出される。その結果、グローバルクロック信号GCKの1サイクルごとに、パラレルなnビットのデータ信号がシリアルに変換されることになる。

【0030】

デマルチプレクサDMUX0の回路構成は、入力側と出力側が逆になる他は図2に示した回路と同様である。したがって、1個の入力ノードN0とn個の出力ノードN1〜Nnを有し、入力ノードN0と各出力ノードN1〜Nnとの間にそれぞれ対応するn個のスイッチSW1〜SWnが挿入される。これにより、入力ノードN0にシリアルに入力されるデータ信号は、n相のクロック信号φ1〜φnに同期して出力ノードN1〜Nnに順次送出される。その結果、グローバルクロック信号GCKの1サイクルごとに、シリアルなnビットのデータ信号がパラレルに変換されることになる。

【0031】

図4は、本実施形態による情報処理システム2のリード動作を説明するためのタイミング図である。

【0032】

リード動作は、コントローラである半導体装置4からDRAMである半導体装置10に対してリードコマンドを発行し、これに応答してDRAMである半導体装置10からコントローラである半導体装置4に対してリードデータを供給する動作である。図4に示す例では、時刻t11〜t13の期間において、アドレスコマンドバスACBUS2上のパラレルなアドレスコマンド信号がマルチプレクサMUXacによってシリアルに変換されている。かかるアドレスコマンド信号は少なくともアクティブコマンド及びロウアドレスを含んでおり、図4においては「Row」と表記されている。シリアルに変換されたアドレスコマンド信号Rowは、アドレスコマンド配線TLACT,TLACBを介して半導体装置4から半導体装置10に転送される。

【0033】

半導体装置10側においては、時刻t12〜t14の期間において、アドレスコマンド配線TLACT,TLACBから転送されるシリアルなアドレスコマンド信号RowがデマルチプレクサDMUXacによってパラレルに変換される。時刻t12,t14は、アドレスコマンド配線TLACT,TLACBを介した転送時間を考慮して、それぞれ時刻t11,t13に対して僅かな遅れを有している。かかる遅れは、ディレイ回路202,402によって調整される。このようにして再生されたパラレルなアドレスコマンド信号Rowは、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。主回路部MCRは、これに応答して図示しないメモリセルアレイに対してロウアクセスを行う。

【0034】

時刻t13から所定の時間が経過した後、時刻t21〜t23の期間において、アドレスコマンドバスACBUS2上のパラレルなアドレスコマンド信号がマルチプレクサMUXacによってシリアルに変換される。かかるアドレスコマンド信号は少なくともリードコマンド及びカラムアドレスを含んでおり、図4においては「Column」と表記されている。シリアルに変換されたアドレスコマンド信号Columnは、アドレスコマンド配線TLACT,TLACBを介して半導体装置4から半導体装置10に転送される。

【0035】

半導体装置10側においては、時刻t22〜t24の期間において、アドレスコマンド配線TLACT,TLACBから転送されるシリアルなアドレスコマンド信号ColumnがデマルチプレクサDMUXacによってパラレルに変換される。時刻t22,t24は、それぞれ時刻t21,t23に対して僅かな遅れを有しており、かかる遅れはディレイ回路202,402によって調整される。このようにして再生されたパラレルなアドレスコマンド信号Columnは、アドレスコマンドバスACBUS1を介して主回路部MCRに供給される。主回路部MCRは、これに応答して図示しないメモリセルアレイに対してカラムアクセスを行う。

【0036】

メモリセルアレイに対してロウアクセス及びカラムアクセスをこの順で行うと、当該ロウアドレス及びカラムアドレスによって指定されるメモリセルから読み出されたnビットのリードデータが主回路部MCRから出力される。主回路部MCRから出力されるnビットのリードデータは、データバスDBUS1を介してマルチプレクサMUX0にパラレルに供給される。図4においては、リードデータを「ReadData」と表記している。

【0037】

時刻t24から所定の時間が経過した後、時刻t31〜t33の期間において、データバスDBUS1上のパラレルなリードデータReadDataがマルチプレクサMUX0によってシリアルに変換される。シリアルに変換されたリードデータReadDataは、データ配線TLDT,TLDBを介して半導体装置10から半導体装置4に転送される。

【0038】

半導体装置4側においては、時刻t32〜t34の期間において、データ配線TLDT,TLDBから転送されるシリアルなリードデータReadDataがデマルチプレクサDMUXcによってパラレルに変換される。時刻t32,t34は、それぞれ時刻t31,t33に対して僅かな遅れを有しており、かかる遅れはディレイ回路200,401によって調整される。このようにして再生されたパラレルなリードデータReadDataは、データバスDBUS2を介して主回路部LCRに供給される。これにより、一連のリード動作が完了する。

【0039】

ライト動作は、データ信号の転送方向が半導体装置4から半導体装置10に変わる他は、上述したリード動作と基本的に同じである。この場合、半導体装置4がライトデータの送信を開始するタイミング及び終了するタイミングに対して、半導体装置10がライトデータの受信を開始するタイミング及び終了するタイミングが僅かに遅延される。かかる遅れはディレイ回路201,400によって調整される。

【0040】

図5は、半導体装置10の全体構成を示すブロック図である。

【0041】

半導体装置10は上述の通り例えばDRAMであり、メモリセルアレイ11を有している。メモリセルアレイ11は、複数のワード線WLと複数のビット線BLを備え、これらの交点にメモリセルMCが配置された構成を有している。ワード線WLの選択はロウデコーダ12によって行われ、ビット線BLの選択はカラムデコーダ13によって行われる。

【0042】

図5に示すように、半導体装置10には外部端子としてアドレスコマンド端子ACT,ACB、クロック端子CK、データ端子DQ(DQ0T/B〜DQpT/B)及び電源端子Vが設けられている。

【0043】

アドレスコマンド端子ACT,ACBは、それぞれアドレスコマンド配線TLACT,TLACBに接続される端子であり、半導体装置4からアドレスコマンド信号が入力される。アドレスコマンド端子ACT,ACBに入力されたシリアルなアドレスコマンド信号は、デマルチプレクサDMUXacによってパラレルなアドレス信号ADDとパラレルなコマンド信号CMDに変換される。図5に示す例では、アドレス信号ADDはr+1ビットのアドレスビットA0〜Arからなる。また、コマンド信号CMDはロウアドレスストローブ信号RASB、カラムアドレスストローブ信号CASB、ライトイネーブル信号WEBなどの信号の組み合わせからなる。

【0044】

アドレス信号ADDは、アドレスラッチ回路21にラッチされる。アドレスラッチ回路21にラッチされたアドレス信号A0〜Arは、ロウデコーダ12、カラムデコーダ13又はモードレジスタ14に供給される。モードレジスタ14は、半導体装置10の動作モードを示すパラメータが設定される回路である。

【0045】

コマンド信号CMDは、コマンドデコード回路22に供給される。コマンドデコード回路22は、コマンド信号CMDをデコードすることによって各種内部コマンドを生成する回路である。内部コマンドとしては、アクティブ信号IACT、カラム信号ICOL、リフレッシュ信号IREF、モードレジスタセット信号MRSなどがある。

【0046】

アクティブ信号IACTは、コマンド信号CMDがロウアクセス(アクティブコマンド)を示している場合に活性化される信号である。アクティブ信号IACTが活性化すると、アドレスラッチ回路21にラッチされたアドレス信号ADDがロウデコーダ12に供給される。これにより、当該アドレス信号ADDにより指定されるワード線WLが選択される。

【0047】

カラム信号ICOLは、コマンド信号CMDがカラムアクセス(リードコマンド又はライトコマンド)を示している場合に活性化される信号である。内部カラム信号ICOLが活性化すると、アドレスラッチ回路21にラッチされたアドレス信号ADDがカラムデコーダ13に供給される。これにより、当該アドレス信号ADDにより指定されるビット線BLが選択される。

【0048】

したがって、アクティブコマンド及びリードコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力すれば、これらロウアドレス及びカラムアドレスによって指定されるメモリセルMCからリードデータが読み出される。リードデータは、データバスDBUS1−0〜DBUS1−pを介して、マルチプレクサMUX0〜MUXpに供給される。マルチプレクサMUX0〜MUXpは、多相クロック信号DTCK1に同期してパラレルなリードデータをシリアル変換し、それぞれ対応するデータ端子対DQ0T/B〜DQpT/Bに出力する。データ端子対DQ0T/B〜DQpT/Bは、それぞれ対応するデータ配線(TLDT0,TLDB0,TLDT1,TLDB1・・)に接続されている。

【0049】

一方、アクティブコマンド及びライトコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力し、その後、データ端子対DQ0T/B〜DQpT/Bにライトデータをシリアルに入力すれば、多相クロック信号DRCK1に同期してシリアルなライトデータがマルチプレクサDMUX0〜DMUXpによりパラレルに変換される。パラレルに変換されたライトデータは、データバスDBUS1−0〜DBUS1−pを介してメモリセルアレイ11に供給され、ロウアドレス及びカラムアドレスによって指定されるメモリセルMCに書き込まれる。

【0050】

リフレッシュ信号IREFは、コマンド信号CMDがリフレッシュコマンドを示している場合に活性化される信号である。リフレッシュ信号IREFが活性化するとリフレッシュ制御回路23によってロウアクセスが行われ、所定のワード線WLが選択される。これにより、選択されたワード線WLに接続された複数のメモリセルMCがリフレッシュされる。ワード線WLの選択は、リフレッシュ制御回路23に含まれる図示しないリフレッシュカウンタによって行われる。

【0051】

モードレジスタセット信号MRSは、コマンド信号CMDがモードレジスタセットコマンドを示している場合に活性化される信号である。したがって、モードレジスタセットコマンドを入力するとともに、これに同期してアドレスコマンド端子ACT,ACBからモード信号を入力すれば、モードレジスタ14の設定値を書き換えることができる。

【0052】

クロック端子CNは、グローバルクロック信号GCKが入力される端子である。半導体装置10に取り込まれたグローバルクロック信号GCKは、半導体装置10の内部における基本クロック信号として用いられ、本明細書においては内部グローバルクロック信号IGCKと表記する。内部グローバルクロック信号IGCKは、コマンドデコード回路22に供給される他、ディレイ回路200〜202に供給される。ディレイ回路200〜202は、内部グローバルクロック信号IGCKのタイミングを微調整するための回路であり、その出力はそれぞれDLL回路100〜102に供給される。

【0053】

DLL回路100〜102は、タイミング調整された内部グローバルクロック信号IGCKに基づいて、それぞれ多相クロック信号DTCK1,DRCK1,ARCK1を生成する回路である。多相クロック信号DTCK1はマルチプレクサMUX0〜MUXpに供給され、パラレルなリードデータをシリアル変換するタイミングを規定する同期信号として用いられる。多相クロック信号DRCK1はデマルチプレクサDMUX0〜DMUXpに供給され、シリアルなライトデータをパラレル変換するタイミングを規定する同期信号として用いられる。多相クロック信号ARCK1はデマルチプレクサDMUXacに供給され、シリアルなアドレスコマンド信号をパラレル変換するタイミングを規定する同期信号として用いられる。

【0054】

電源端子Vは、電源電位VDD,VSSが供給される端子である。電源端子Vに供給される電源電位VDD,VSSは内部電源発生回路24に供給される。内部電源発生回路24は、電源電位VDD,VSSに基づいて各種の内部電位VPP,VPERD,VPERIなどを発生させる。内部電位VPPは主にロウデコーダ12において使用される電位であり、内部電位VPERDは主にDLL回路100〜102において使用される電位であり、内部電位VPERIは他の多くの回路ブロックにおいて使用される電位である。

【0055】

図6は、DLL回路100の回路図である。

【0056】

図6に示すように、DLL回路100は、ディレイライン110と、ディレイライン110の遅延量を制御する制御回路120と、ディレイライン110から出力される出力クロック信号Node1〜Nodenを並べ替えるルーティング回路130と、ルーティング回路130から出力される多相クロック信号CK1〜CKnの波形を整形することにより多相クロック信号DTCK1を生成する整形回路140とを備える。

【0057】

ディレイライン110は、縦列接続されたn個の遅延回路UD1〜UDnからなり、その初段である遅延回路UD1には、タイミング調整された内部グローバルクロック信号IGCKが入力される。本発明においては、遅延回路UD1に入力される内部グローバルクロック信号IGCKを「入力クロック信号」と呼ぶことがある。これらn個の遅延回路UD1〜UDnは縦列接続されているため、これら遅延回路UD1〜UDnから出力される出力クロック信号Node1〜Nodenは、この順に位相が遅れる。本例では、出力クロック信号Node1〜Nodenが全てルーティング回路130に入力されているが、出力クロック信号Node1〜Nodenの一部のみをルーティング回路130に入力しても構わない。

【0058】

最終段の遅延回路UDnから出力される出力クロック信号Nodenの位相は、初段の遅延回路UD1に入力される内部グローバルクロック信号IGCKに対して、正確にk周期遅れている。かかる制御は、制御回路120によって行われる。図6に示すように、制御回路120は、分周回路121、位相判定回路122及び制御電圧生成回路123を備えている。

【0059】

分周回路121は、出力クロック信号Noden及び内部グローバルクロック信号IGCKをk分周する回路である。分周回路121から出力される分周クロック信号GCKsは、内部グローバルクロック信号IGCKをk分周した信号であり、分周回路121から出力される分周クロック信号CKosは、出力クロック信号Nodenをk分周した信号である。これら分周クロック信号GCKs,CKosは位相判定回路122に供給され、両者の位相が判定される。判定の結果、分周クロック信号CKosの位相が分周クロック信号GCKsに対して遅れている場合(つまりディレイライン110の遅延量が大きすぎる場合)、位相判定回路122はアップ信号UPBをローレベルに活性化させる。このとき、ダウン信号DNTはローレベルに非活性化される。これにより、制御電圧生成回路123に含まれるPチャンネル型MOSトランジスタ123Pがオンするため、キャパシタ123Cにチャージされる制御電圧VDLYが上昇する。後述するように、制御電圧VDLYが上昇するとディレイライン110の遅延量は少なくなる。

【0060】

逆に、分周クロック信号CKosの位相が分周クロック信号GCKsに対して進んでいる場合(つまりディレイライン110の遅延量が小さすぎる場合)、位相判定回路122はダウン信号DNTをハイレベルに活性化させる。このとき、アップ信号UPBはハイレベルに非活性化される。これにより、制御電圧生成回路123に含まれるNチャンネル型MOSトランジスタ123Nがオンするため、キャパシタ123Cにチャージされる制御電圧VDLYが低下する。後述するように、制御電圧VDLYが低下するとディレイライン110の遅延量は大きくなる。

【0061】

このようなフィードバック制御により、出力クロック信号Nodenの位相が内部グローバルクロック信号IGCKに対して正確にk周期遅れるよう、ディレイライン110の遅延量が調整される。

【0062】

図7は、遅延回路UD1の回路図である。他の遅延回路UD2〜UDnも図7に示す遅延回路UD1と同じ回路構成を有している。

【0063】

図7に示すように、遅延回路UD1は、直列接続された2段のインバータINV1,INV2からなる。インバータINV1,INV2の低位側電源ノードVNと接地電位VSSとの間には、調整トランジスタTDLYが挿入されており、そのゲート電極には制御電圧VDLYが供給される。このため、インバータINV1,INV2のスイッチング速度は制御電圧VDLYに依存する。具体的には、制御電圧VDLYが高いほどインバータINV1,INV2のスイッチング速度が早くなるため、遅延回路UD1による遅延量は低下する。逆に、制御電圧VDLYが低いほどインバータINV1,INV2のスイッチング速度が遅くなるため、遅延回路UD1による遅延量は増大する。

【0064】

図8は、制御電圧VDLYと遅延回路UD1の遅延量δとの関係を示すグラフである。

【0065】

図8に示す遅延量δは、入力クロック信号(内部グローバルクロック信号IGCK)と出力クロック信号(Node1)との時間差である。図8に示すように、制御電圧VDLYが高くなれば基本的に遅延量δは小さくなるが、遅延量δを無限に小さくできるわけではなく、最小の遅延量δMINが存在する。つまり、制御電圧VDLYをいくら大きくしても、遅延回路UD1の遅延量をδMIN未満とすることはできない。このことは、出力クロック信号Node1〜Nodenをこの順に並べた場合、相間隔の最小値がδMINとなることを意味する。したがって、k=1であるとすると、多相クロック信号DTCK1の相間隔の最小値もδMINに制限される。しかしながら、本実施形態においてはkが2以上の整数値であり、且つ、ディレイライン110を構成する遅延回路の段数nとは異なる値に設定されるため、多相クロック信号DTCK1の相間隔をδMIN未満とすることが可能とされている。その詳細については後述する。

【0066】

図9は、分周回路121の一部を示す回路図である。

【0067】

図9に示す回路は、内部グローバルクロック信号IGCKから分周クロック信号GCKsを生成する回路部分を示しており、一例として、k=3である場合の回路図である。図9に示す例では、JK型のフリップフロップ回路FF1,FF2が循環接続された構成を有している。フリップフロップ回路FF1,FF2のクロックノードには内部グローバルクロック信号IGCKが供給されており、これにより、内部グローバルクロック信号IGCKの立ち上がりエッジが3回入力される度に、分周クロック信号GCKsの立ち上がりエッジが1回生成される。

【0068】

図10は、位相判定回路122の回路図である。

【0069】

図10に示す位相判定回路122は、データラッチ型のフリップフロップ回路FF3,FF4を備えている。フリップフロップ回路FF3のクロックノードには分周クロック信号GCKsが入力され、フリップフロップ回路FF4のクロックノードには分周クロック信号CKosが入力される。そして、フリップフロップ回路FF3,FF4がそれぞれセット状態及びリセット状態であればアップ信号UPBがローレベルに活性化し、フリップフロップ回路FF3,FF4がそれぞれリセット状態及びセット状態であればダウン信号DNTがハイレベルに活性化する。これにより、分周クロック信号GCKs,CKosのいずれの立ち上がりエッジが先に到来するかによって、アップ信号UPB及びダウン信号DNTのいずれか一方が活性化する。フリップフロップ回路FF3,FF4の両方がセットされると、これらフリップフロップ回路FF3,FF4はリセットされる。

【0070】

以上がDLL回路100の回路構成である。他のDLL回路101,102についてもDLL回路100と同じ回路構成を有している。以下、n=5,k=3である場合を例に、DLL回路100の動作を説明する。上述の通り、nとはディレイライン110を構成する遅延回路UD1〜UDnの数であり、kとは分周回路121の分周数である。追って説明するが、nの値とkの値はいずれも2以上の整数であり、且つ、最大公約数が1であることが好ましい。以下説明するn=5,k=3の例は、この条件を満たしている。

【0071】

図11はDLL回路100の動作を説明するためのタイミング図であり、n=5,k=3である場合を示している。

【0072】

図11に示す例ではn=5であることから、最終段の遅延回路UD5から出力される出力クロック信号Node5は、初段の遅延回路UD1に入力される内部グローバルクロック信号IGCKに対して正確に3周期分遅延する。そして、3周期分の遅延を発生させるために5段の遅延回路UD1〜UD5を経由することから、出力クロック信号Node1〜Node5をこの順に並べた場合、相間隔は3GCK/5となる。ここでいう「GCK」とは内部グローバルクロック信号IGCKの1サイクルを意味する。

【0073】

具体的に説明すると、時刻t40における内部グローバルクロック信号IGCKの立ち上がりエッジは、遅延回路UD1によって3GCK/5だけ遅延され、これにより時刻t40から3GCK/5だけ遅延した時刻t41において出力クロック信号Node1の立ち上がりエッジが現れる。時刻t41における出力クロック信号Node1の立ち上がりエッジは、遅延回路UD2によってさらに3GCK/5だけ遅延され、これにより時刻t40から6GCK/5だけ遅延した時刻t42において出力クロック信号Node2の立ち上がりエッジが現れる。時刻t42における出力クロック信号Node2の立ち上がりエッジは、遅延回路UD3によってさらに3GCK/5だけ遅延され、これにより時刻t40から9GCK/5だけ遅延した時刻t43において出力クロック信号Node3の立ち上がりエッジが現れる。時刻t43における出力クロック信号Node3の立ち上がりエッジは、遅延回路UD4によってさらに3GCK/5だけ遅延され、これにより時刻t40から12GCK/5だけ遅延した時刻t44において出力クロック信号Node4の立ち上がりエッジが現れる。そして、時刻t44における出力クロック信号Node4の立ち上がりエッジは、遅延回路UD5によってさらに3GCK/5だけ遅延され、これにより時刻t40から3GCKだけ遅延した時刻t45において出力クロック信号Node5の立ち上がりエッジが現れる。

【0074】

ここで、内部グローバルクロック信号IGCKの図11に示す最後の1サイクル(時刻t51〜時刻45)に注目すると、この期間内に出力クロック信号Node1〜Node5の立ち上がりエッジが全て出現していることが分かる。具体的には、時刻t51に出力クロック信号Node5の立ち上がりエッジが出現し、時刻t51からGCK/5だけ遅れた時刻t52に出力クロック信号Node2の立ち上がりエッジが出現し、時刻t52からさらにGCK/5だけ遅れた時刻t44に出力クロック信号Node4の立ち上がりエッジが出現し、時刻t44からさらにGCK/5だけ遅れた時刻t54に出力クロック信号Node1の立ち上がりエッジが出現し、時刻t54からさらにGCK/5だけ遅れた時刻t55に出力クロック信号Node3の立ち上がりエッジが出現している。

【0075】

したがって、出力クロック信号Node1〜Node5を上記の順番で並べ替えれば、相間隔がGCK/5に縮小されることになる。このことは、最小の遅延量δMINがk×GCK/n(3GCK/5)であっても、より小さい相間隔(GCK/5)が得られることを意味する。出力クロック信号Node1〜Node5の並べ替えは、ルーティング回路130によって行われる。

【0076】

図12は、ルーティング回路130の機能を説明するための配線図である。

【0077】

図12に示す配線図では、出力クロック信号Node1〜Node5がそれぞれ多相クロック信号CK4,CK2,CK5,CK3,CK1に割り当てられる。このようなルーティングは、固定的な配線を用いて実現することが可能である。この場合、ルーティング回路130は単なる配線によって構成することができる。但し、nの値やkの値を可変とするためには、ルーティング回路130を固定的な配線によって構成するのではなく、割り当てを変更可能とする必要がある。

【0078】

図13は、割り当てを変更可能なルーティング回路130の機能を説明するための模式図である。

【0079】

図13においては、出力クロック信号Node1〜Node5の配線が横方向に延在し、多相クロック信号CK1〜CK5の配線が縦方向に延在している。そして、黒丸で示された交点は横方向の配線と縦方向の配線が接続されていることを意味し、白丸で示された交点は横方向の配線と縦方向の配線が接続されていないことを意味する。図13に示す例においても、出力クロック信号Node1〜Node5がそれぞれ多相クロック信号CK4,CK2,CK5,CK3,CK1に割り当てられており、結果としては図12に示すルーティング回路130と同じである。しかしながら、出力クロック信号Node1〜Node5をそれぞれどの多相クロック信号CK1〜CK5として使用するか、切り替えることが可能である点において、図12に示したルーティング回路130と相違する。

【0080】

図14は、図13に示す領域Xの回路図である。

【0081】

図14に示す例では、各交点にトランスファゲートTGが設けられている。これにより、横方向の配線と縦方向の配線との接続の有無を切り替え可能とされている。トランスファゲートTGの切り替えは、モードレジスタ14から供給されるモード信号MODEによって行うことができる。このような回路構成とすれば、出力クロック信号Node1〜Node5を任意の多相クロック信号CK1〜CK5に割り当てることが可能となる。

【0082】

図15は整形回路140の回路図であり、図16は整形回路140の動作波形図である。

【0083】

図16に示すように、多相クロック信号CK1〜CK5は内部グローバルクロック信号IGCKと同じデューティを有しているため、そのままではハイレベルの期間が重複してしまう。図15に示す整形回路140は、多相クロック信号CK1〜CK5のうち、位相の隣接する2つの多相クロック信号が同時にハイレベルとなるのを禁止する。これにより、多相クロック信号φ1〜φ5のそれぞれは、対応する多相クロック信号CK1〜CK5の立ち上がりエッジに連動して立ち上がり、次の多相クロック信号の立ち上がりエッジに連動して立ち下がる波形となる。その結果、図16に示すように、多相クロック信号φ1〜φ5は、互いにハイレベルとなる期間が除去された波形となる。

【0084】

このようにして生成された多相クロック信号DTCK1は、図5に示したマルチプレクサMUX0〜MUXpに供給され、そのタイミング信号として用いられる。以上、DLL回路100に着目して説明を進めたが、他のDLL回路101,102回路構成及び動作もDLL回路100と同様である。

【0085】

本実施形態においては、基本となる内部グローバルクロック信号IGCKをn個の遅延回路UD1〜UDnによってkサイクル遅延させていることから、1つの遅延回路における最小の遅延量δMINよりも小さい相間隔を有する多相クロック信号を簡単な回路構成で生成することが可能となる。より具体的には、nとkの最大公約数をGCM、内部グローバルクロック信号IGCKの1サイクルをGCK、多相クロック信号の相間隔をUIとした場合、相間隔UIの長さを、

UI=GCK×GCM/n

とすることができる。これにより、マルチプレクサ及びデマルチプレクサは、内部グローバルクロック信号IGCKのGCM/nサイクル毎にデータ信号を順次取り込むことができる。このことは、内部グローバルクロック信号IGCKの1サイクルでnビットのデータ信号を取り込めることを意味する。上述した実施形態では、GCM=1、n=5であることから、

UI=GCK/5

となる。これにより、マルチプレクサ及びデマルチプレクサは、内部グローバルクロック信号IGCKの1/5サイクル毎にデータ信号を順次取り込むことができることから、内部グローバルクロック信号IGCKの1サイクルで5ビットのデータ信号を取り込むことが可能となる。

【0086】

相間隔UIをより小さくするためにはnの値を大きくすればよいが、nとkの最大公約数GCMが2以上であると相間隔UIが大きくなることから、最大公約数GCMについては1とすることが好ましい。最大公約数GCMが2以上である場合、遅延回路UD1〜UDnから出力されるn個の出力クロック信号Node1〜Nodenの一部の位相が重複するからである。これに対し、最大公約数GCMが1であれば、遅延回路UD1〜UDnから出力されるn個の出力クロック信号Node1〜Nodenは互いに異なる位相となる。

【0087】

最大公約数GCMが1となるnとkの組み合わせについては任意であり、上記の例(n=5,k=3)のように両方が奇数であっても構わないし、n=34,k=3のように一方が偶数であっても構わない。

【0088】

また、図11を用いて説明したように、遅延回路UD1〜UDnの1個あたりの遅延量k×GCK/nは、遅延量の最小値δMIN以上である必要がある。つまり、

δMIN≦k×GCK/n

を満足する必要がある。したがって、相間隔UIをより小さくするためにnの値を大きくする場合には、上記の式を満足するようkの値を設定する必要がある。

【0089】

nとkの大小関係については特に限定されないが、n>kであることが好ましい。最大公約数GCMが1である限り、kの値は相間隔UIとは無関係であるが、kの値が大きくなるとディレイライン110の全体の遅延量も大きくなるため、遅延回路UD1〜UDnの1個あたりの遅延量を大きくする必要がある。この場合、遅延回路UD1〜UDnによる波形の鈍りが大きくなり、クロックの精度が低下するおそれがある。この点を考慮すれば、

δMIN≦k×GCK/n

を満足する範囲内で、kの値はできる限り小さく設定することが好ましい。

【0090】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0091】

例えば、生成した多相クロック信号φ1〜φnの全てをマルチプレクサ又はデマルチプレクサにて使用することは必須でなく、一部のみを使用しても構わない。例えば、上記実施形態のように多相クロック信号φ1〜φ5が5相のクロック信号である場合であっても、このうち4つの多相クロック信号φ1〜φ4のみをマルチプレクサ又はデマルチプレクサに供給しても構わない。

【0092】

また、上述した実施形態では、3種類の多相クロック信号(例えばDTCK1,DRCK1,ARCK1)をそれぞれ別個のDLL回路によって生成しているが、1つのDLL回路の出力をこれら多相クロック信号として共用しても構わない。これによれば、チップ上におけるDLL回路の占有面積が削減されるため、各多相クロック信号の位相を微調整する必要がない場合には好適である。

【符号の説明】

【0093】

2 情報処理システム

4,10 半導体装置

6 クロックジェネレータ

11 メモリセルアレイ

12 ロウデコーダ

13 カラムデコーダ

14 モードレジスタ

21 アドレスラッチ回路

22 コマンドデコード回路

23 リフレッシュ制御回路

24 内部電源発生回路

100〜102,300〜302 DLL回路

200〜202,400〜402 ディレイ回路

110 ディレイライン

120 制御回路

121 分周回路

122 位相判定回路

123 制御電圧生成回路

123C キャパシタ

123N,123P トランジスタ

130 ルーティング回路

140 整形回路

ACBUS1,ACBUS2 アドレスコマンドバス

ACT,ACB アドレスコマンド端子

DTCK1,DRCK1,ARCK1,DTCK2,DRCK2,ARCK2 多相クロック信号

CKGEN1,CKGEN2 クロック生成部

CN クロック端子

DBUS1,DBUS2 データバス

DMUX0,DMUX0c,DMUXac デマルチプレクサ

DQ データ端子

GCK グローバルクロック信号

GCKs,CKos 分周クロック信号

IFC1,IFC2 インターフェース回路部

IGCK 内部グローバルクロック信号

LCR,MCR 主回路部

MUX0,MUX0c,MUXac マルチプレクサ

Node1〜Noden 出力クロック信号

TLACT,TLACB アドレスコマンド配線

TLDT,TLDB データ配線

UD1〜UDn 遅延回路

V 電源端子

【特許請求の範囲】

【請求項1】

互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、

前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、

前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路と、を備えることを特徴とする半導体装置。

【請求項2】

前記複数の遅延回路による前記入力クロック信号の遅延量は、前記入力クロック信号の周期のk倍(kは2以上の整数であり、nとは異なる)であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記nと前記kの最大公約数が1であることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記nが前記kより大きいことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記複数のデータ信号は、それぞれ対応する複数の入力ノードを介して前記データ処理回路にパラレルに供給され、

前記データ処理回路は、前記n個の出力クロック信号に同期して取り込んだ前記複数のデータ信号を出力ノードにシリアルに出力することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

前記複数のデータ信号は、入力ノードを介して前記データ処理回路にシリアルに供給され、

前記データ処理回路は、前記n個の出力クロック信号に同期して取り込んだ前記複数のデータ信号をそれぞれ対応する複数の出力ノードにパラレルに出力することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項7】

前記複数のデータ信号はnビットであり、

前記nと前記kの最大公約数をGCMとした場合、前記データ処理回路は、前記入力クロック信号のGCM/n周期のタイミング毎に前記nビットのデータ信号を順次取り込むことを特徴とする請求項2乃至6のいずれか一項に記載の半導体装置。

【請求項8】

互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路とを備える第1及び第2の半導体装置と、

前記第1の半導体装置と前記第2の半導体装置を接続するデータ配線と、を備え、

前記第1の半導体装置の内部でパラレルに伝送される前記複数のデータ信号は、前記第1の半導体装置に設けられた前記データ処理回路によってシリアルに変換されて前記データ配線に出力され、

前記データ配線を介して前記第2の半導体装置にシリアルに供給される前記複数のデータ信号は、前記第2の半導体装置に設けられた前記データ処理回路によってパラレルに変換されることを特徴とする情報処理システム。

【請求項9】

前記第1及び第2の半導体装置の一方がメモリデバイスであり、前記第1及び第2の半導体装置の他方が前記メモリデバイスを制御するコントローラであることを特徴とする請求項8に記載の情報処理システム。

【請求項10】

縦列接続されたn個の遅延回路からなり、入力クロック信号をk周期遅延させるディレイラインと、

前記n個の遅延回路からそれぞれ出力されるn個の出力クロック信号の少なくとも一部に基づいて、互いに位相の異なる多相クロック信号を生成するルーティング回路と、を備え、

前記n及びkはいずれも2以上の整数であり、最大公約数が1であることを特徴とする半導体装置。

【請求項11】

前記nが前記kより大きいことを特徴とする請求項10に記載の半導体装置。

【請求項12】

前記多相クロック信号の相間隔は、前記遅延回路の最小遅延時間よりも小さいことを特徴とする請求項10又は11に記載の半導体装置。

【請求項13】

前記入力クロック信号及び前記ディレイラインから出力される出力クロック信号をk分周することによって、それぞれ第1及び第2の分周クロック信号を生成する分周回路と、

前記第1及び第2の分周クロック信号の位相に基づいて、前記n個の遅延回路の遅延量を制御する制御回路と、をさらに備えることを特徴とする請求項10乃至12のいずれか一項に記載の半導体装置。

【請求項1】

互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、

前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、

前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路と、を備えることを特徴とする半導体装置。

【請求項2】

前記複数の遅延回路による前記入力クロック信号の遅延量は、前記入力クロック信号の周期のk倍(kは2以上の整数であり、nとは異なる)であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記nと前記kの最大公約数が1であることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記nが前記kより大きいことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記複数のデータ信号は、それぞれ対応する複数の入力ノードを介して前記データ処理回路にパラレルに供給され、

前記データ処理回路は、前記n個の出力クロック信号に同期して取り込んだ前記複数のデータ信号を出力ノードにシリアルに出力することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

前記複数のデータ信号は、入力ノードを介して前記データ処理回路にシリアルに供給され、

前記データ処理回路は、前記n個の出力クロック信号に同期して取り込んだ前記複数のデータ信号をそれぞれ対応する複数の出力ノードにパラレルに出力することを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項7】

前記複数のデータ信号はnビットであり、

前記nと前記kの最大公約数をGCMとした場合、前記データ処理回路は、前記入力クロック信号のGCM/n周期のタイミング毎に前記nビットのデータ信号を順次取り込むことを特徴とする請求項2乃至6のいずれか一項に記載の半導体装置。

【請求項8】

互いに縦列接続され、その初段において入力クロック信号を受けるn個(nは2以上の整数)の遅延回路と、前記n個の遅延回路により其々出力されるn個の出力クロック信号が互いに異なる位相となるように前記n個の遅延回路の其々の遅延量を制御する制御回路と、前記n個の出力クロック信号及び複数のデータ信号を受け、前記複数のデータ信号を其々に対応する前記n個の出力クロック信号に同期して取り込むデータ処理回路とを備える第1及び第2の半導体装置と、

前記第1の半導体装置と前記第2の半導体装置を接続するデータ配線と、を備え、

前記第1の半導体装置の内部でパラレルに伝送される前記複数のデータ信号は、前記第1の半導体装置に設けられた前記データ処理回路によってシリアルに変換されて前記データ配線に出力され、

前記データ配線を介して前記第2の半導体装置にシリアルに供給される前記複数のデータ信号は、前記第2の半導体装置に設けられた前記データ処理回路によってパラレルに変換されることを特徴とする情報処理システム。

【請求項9】

前記第1及び第2の半導体装置の一方がメモリデバイスであり、前記第1及び第2の半導体装置の他方が前記メモリデバイスを制御するコントローラであることを特徴とする請求項8に記載の情報処理システム。

【請求項10】

縦列接続されたn個の遅延回路からなり、入力クロック信号をk周期遅延させるディレイラインと、

前記n個の遅延回路からそれぞれ出力されるn個の出力クロック信号の少なくとも一部に基づいて、互いに位相の異なる多相クロック信号を生成するルーティング回路と、を備え、

前記n及びkはいずれも2以上の整数であり、最大公約数が1であることを特徴とする半導体装置。

【請求項11】

前記nが前記kより大きいことを特徴とする請求項10に記載の半導体装置。

【請求項12】

前記多相クロック信号の相間隔は、前記遅延回路の最小遅延時間よりも小さいことを特徴とする請求項10又は11に記載の半導体装置。

【請求項13】

前記入力クロック信号及び前記ディレイラインから出力される出力クロック信号をk分周することによって、それぞれ第1及び第2の分周クロック信号を生成する分周回路と、

前記第1及び第2の分周クロック信号の位相に基づいて、前記n個の遅延回路の遅延量を制御する制御回路と、をさらに備えることを特徴とする請求項10乃至12のいずれか一項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−55575(P2013−55575A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−193625(P2011−193625)

【出願日】平成23年9月6日(2011.9.6)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月6日(2011.9.6)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]