半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその制御方法に関し、特に、DLL回路を備える半導体装置及びその制御方法に関する。

【背景技術】

【0002】

同期型のDRAM(Dynamic Random Access Memory)のようにクロック信号に同期した動作を行う半導体装置においては、位相制御された内部クロック信号が必要となることがある。位相制御された内部クロック信号は、主にDLL(Delay Locked Loop)回路によって生成される(特許文献1参照)。DLL回路には、内部クロック信号を遅延させるディレイラインが含まれており、その遅延量はカウンタ回路から出力されるカウント値よって定められる。

【0003】

一般的なDLL回路においては、制御対象となるレプリカクロック信号の立ち上がりエッジが基準となる入力クロック信号の立ち上がりエッジと一致するよう、カウント値のアップカウント又はダウンカウントが行われる。したがって、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がローレベルである場合、すなわちレプリカクロック信号の方が位相が進んでいる場合には、ディレイラインの遅延量を増大させる。逆に、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がハイレベルである場合、すなわちレプリカクロック信号の方が位相が遅れている場合には、ディレイラインの遅延量を減少させればよい。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−192164号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した一般的なDLL回路では、カウンタ回路による遅延量の調整可能範囲が最低でも1クロックサイクルに相当する範囲だけ必要となる。このため、ディレイラインの回路規模が大きくなるという問題があった。そこで、本発明者は、カウンタ回路による遅延量の調整可能範囲を縮小可能なDLL回路について研究を行った。その結果、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がハイレベルである場合には、レプリカクロック信号を反転させることにより、いずれのケースにおいてもディレイラインの遅延量を増大させる方向に制御可能なDLL回路を開発した。これによれば、カウンタ回路による遅延量の調整可能範囲が1/2クロックサイクル分で済むことから、ディレイラインの回路規模を縮小することが可能となる。この場合、カウンタ部のカウント値の初期値は中心値ではなく、最小値近傍にオフセットさせておき、アップカウントによってDLL回路をロックさせることになる。

【0006】

しかしながら、上記のDLL回路においては、入力クロック信号にジッタ成分が重畳している場合、レプリカクロック信号を反転させるか否かの判定を誤ることがあった。かかる判定を誤った場合、カウント値の初期値が中心値からオフセットされた値であることから、ダウンカウントを継続するとすぐに最小値に達してしまい、これ以上の位相制御が不可能になるという現象が生じることがあった。このため、本発明者は、このような現象が生じにくい半導体装置について鋭意研究を行った。

【課題を解決するための手段】

【0007】

本発明による半導体装置は、カウント値を生成するカウンタ部と、前記カウント値に応じて第1のクロック信号を遅延させることにより第2のクロック信号を生成するディレイラインと、前記第2のクロック信号を受け、その位相を反転させたクロック信号又は反転させないクロック信号のいずれか一方のクロック信号を選択して第3のクロック信号として出力する反転制御部と、前記第3のクロック信号に基づいて第4のクロック信号を生成するレプリカ出力部と、前記第1のクロック信号と前記第4のクロック信号の位相を比較することによって位相判定信号を生成する位相比較部と、リセット信号、反転制御信号、コード更新信号及びカウンタ更新信号を活性化させる制御部と、を備え、前記リセット信号に応答して、前記カウンタ部のカウント値は第1の初期値にリセットされ、且つ、前記反転制御部は前記反転させないクロック信号を選択するようにセットされ、前記反転制御部は、前記反転制御信号が活性化した際における前記位相判定信号の論理レベルに基づいて前記いずれか一方のクロック信号を選択し、前記カウンタ部のカウント値は、前記反転制御部が選択した後に前記コード更新信号に応答して前記第1の初期値から第2の初期値に更新され、前記カウンタ部のカウント値は、前記カウンタ更新信号が活性化した際の前記位相判定信号の論理レベルに基づいて前記第2の初期値からアップカウント又はダウンカウントされることを特徴とする。

【0008】

本発明による半導体装置の制御方法は、DLL回路に含まれるカウンタ回路のカウント値を第1の初期値にリセットして第1のクロック信号を前記第1の初期値に対応して遅延させた第2のクロック信号を出力し、前記第1のクロック信号の位相及び前記第2のクロック信号の位相を互いに比較し、前記比較の結果に応じて前記第2のクロック信号の位相を反転する制御及び反転しない制御の一方を行い、前記制御の後に、前記カウント値を前記第1の初期値から第2の初期値に更新し、前記更新の後に、前記第1のクロック信号の位相及び前記第2の初期値に対応する前記第2のクロック信号の位相を互いに比較し、比較結果に応じて前記カウント値を前記第2の初期値からアップカウント又はダウンカウントして前記第2のクロック信号の遅延量を調整することを特徴とする。

【発明の効果】

【0009】

本発明によれば、ジッタなどの影響によって第2のクロック信号を誤って反転させ、或いは誤って反転させなかった場合であっても、カウンタ部のカウント値を第1の初期値から第2の初期値にジャンプさせることによって、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることによって遅延量の調整可能範囲を縮小した場合であっても、DLL回路を正しくロックさせることが可能となる。

【図面の簡単な説明】

【0010】

【図1】本発明の好ましい実施形態による半導体装置10の全体構成を示すブロック図である。

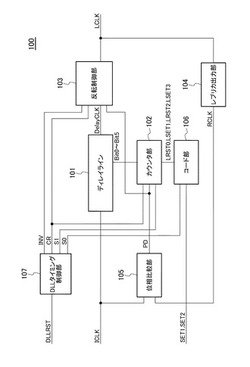

【図2】DLL回路100の構成を示すブロック図である。

【図3】位相比較部105の回路図である。

【図4】カウンタ部102の回路図である。

【図5】コード部106の回路図である。

【図6】反転制御部103の回路図である。

【図7】DLL回路100の動作を説明するためのタイミング図である。

【図8】反転制御部103によって内部クロック信号の反転信号/DelayCLKが選択されるケースを説明するためのタイミング図である。

【図9】反転制御部103によって内部クロック信号DelayCLKが選択されるケースを説明するためのタイミング図である。

【図10】ジッタの影響により反転されていない内部クロック信号DelayCLKが誤って選択されたケースを説明するためのタイミング図である。

【図11】ジッタの影響により反転された内部クロック信号/DelayCLKが誤って選択されたケースを説明するためのタイミング図である。

【図12】DLL回路100がロックする過程を説明するための模式的なタイミング図である。

【発明を実施するための形態】

【0011】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0012】

図1は、本発明の好ましい実施形態による半導体装置10の全体構成を示すブロック図である。

【0013】

本実施形態による半導体装置10はDRAMであり、メモリセルアレイ11を有している。メモリセルアレイ11は、複数のワード線WLと複数のビット線BLを備え、これらの交点にメモリセルMCが配置された構成を有している。ワード線WLの選択はロウデコーダ12によって行われ、ビット線BLの選択はカラムデコーダ13によって行われる。

【0014】

図1に示すように、半導体装置10には外部端子としてアドレス端子21、コマンド端子22、クロック端子23、データ端子24及び電源端子25が設けられている。

【0015】

アドレス端子21は、外部からアドレス信号ADDが入力される端子である。アドレス端子21に入力されたアドレス信号ADDは、アドレス入力回路31を介してアドレスラッチ回路32に供給され、アドレスラッチ回路32にラッチされる。アドレスラッチ回路32にラッチされたアドレス信号ADDは、ロウデコーダ12、カラムデコーダ13又はモードレジスタ14に供給される。モードレジスタ14は、半導体装置10の動作モードを示すパラメータが設定される回路である。

【0016】

コマンド端子22は、外部からコマンド信号CMDが入力される端子である。コマンド信号CMDは、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、リセット信号/RESETなどの複数の信号からなる。ここで、信号名の先頭にスラッシュ(/)が付されているのは、対応する信号の反転信号、或いは、当該信号がローアクティブな信号であることを意味する。コマンド端子22に入力されたコマンド信号CMDは、コマンド入力回路33を介してコマンドデコード回路34に供給される。コマンドデコード回路34は、コマンド信号CMDをデコードすることによって各種内部コマンドを生成する回路である。内部コマンドとしては、アクティブ信号IACT、カラム信号ICOL、リフレッシュ信号IREF、モードレジスタセット信号MRS、DLLリセット信号DLLRSTなどがある。

【0017】

アクティブ信号IACTは、コマンド信号CMDがロウアクセス(アクティブコマンド)を示している場合に活性化される信号である。アクティブ信号IACTが活性化すると、アドレスラッチ回路32にラッチされたアドレス信号ADDがロウデコーダ12に供給される。これにより、当該アドレス信号ADDにより指定されるワード線WLが選択される。

【0018】

カラム信号ICOLは、コマンド信号CMDがカラムアクセス(リードコマンド又はライトコマンド)を示している場合に活性化される信号である。内部カラム信号ICOLが活性化すると、アドレスラッチ回路32にラッチされたアドレス信号ADDがカラムデコーダ13に供給される。これにより、当該アドレス信号ADDにより指定されるビット線BLが選択される。

【0019】

したがって、アクティブコマンド及びリードコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力すれば、これらロウアドレス及びカラムアドレスによって指定されるメモリセルMCからリードデータが読み出される。リードデータDQは、FIFO回路15及び入出力回路16を介して、データ端子24から外部に出力される。一方、アクティブコマンド及びライトコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力し、その後、データ端子24にライトデータDQを入力すれば、ライトデータDQは入出力回路16及びFIFO回路15を介してメモリセルアレイ11に供給され、ロウアドレス及びカラムアドレスによって指定されるメモリセルMCに書き込まれる。FIFO回路15及び入出力回路16の動作は、内部クロック信号LCLKに同期して行われる。内部クロック信号LCLKは、後述するDLL回路100によって生成される。特に、入出力回路16にはリードデータDQを出力する出力回路16aが含まれており、リードデータDQの出力は内部クロック信号LCLKに同期して行われる。

【0020】

リフレッシュ信号IREFは、コマンド信号CMDがリフレッシュコマンドを示している場合に活性化される信号である。リフレッシュ信号IREFが活性化するとリフレッシュ制御回路35によってロウアクセスが行われ、所定のワード線WLが選択される。これにより、選択されたワード線WLに接続された複数のメモリセルMCがリフレッシュされる。ワード線WLの選択は、リフレッシュ制御回路35に含まれる図示しないリフレッシュカウンタによって行われる。

【0021】

モードレジスタセット信号MRSは、コマンド信号CMDがモードレジスタセットコマンドを示している場合に活性化される信号である。したがって、モードレジスタセットコマンドを入力するとともに、これに同期してアドレス端子21からモード信号を入力すれば、モードレジスタ14の設定値を書き換えることができる。

【0022】

クロック端子23は、外部クロック信号CK,/CKが入力される端子である。外部クロック信号CKと外部クロック信号/CKは互いに相補の信号であり、いずれもクロック入力回路36に供給される。クロック入力回路36は、外部クロック信号CK,/CKに基づいて内部クロック信号ICLKを生成する。内部クロック信号ICLKは、半導体装置10の内部における基本クロック信号であり、本発明においては「第1のクロック信号」と呼ぶことがある。内部クロック信号ICLKは、タイミングジェネレータ37に供給され、これによって各種内部クロック信号が生成される。タイミングジェネレータ37によって生成される各種内部クロック信号は、アドレスラッチ回路32やコマンドデコード回路34などの回路ブロックに供給され、これら回路ブロックの動作タイミングを規定する。

【0023】

内部クロック信号ICLKは、DLL回路100にも供給される。DLL回路100は、内部クロック信号ICLKに基づいて内部クロック信号LCLKを生成する回路である。内部クロック信号LCLKは位相制御されたクロック信号であり、本発明においては「第3のクロック信号」と呼ぶことがある。上述の通り、内部クロック信号LCLKはFIFO回路15及び入出力回路16に供給される。これにより、リードデータDQは内部クロック信号LCLKに同期して出力されることになる。

【0024】

DLL回路100は、コマンドデコード回路34から出力されるDLLリセット信号DLLRSTによってリセットされる。DLLリセット信号DLLRSTは、リセット信号/RESETや、DLLリセットコマンド(DLLRST)に応答して活性化される。リセット信号/RESETは電源投入時などに活性化される信号であり、DLLリセットコマンドはDLL回路100のリセットが必要な際に発行されるコマンドである。したがって、電源投入直後などにおいては、DLLリセット信号DLLRSTによってDLL回路100がリセットされることになる。

【0025】

電源端子25は、電源電位VDD,VSSが供給される端子である。電源端子25に供給される電源電位VDD,VSSは内部電源発生回路38に供給される。内部電源発生回路38は、電源電位VDD,VSSに基づいて各種の内部電位VPP,VPERD,VPERIなどを発生させる。内部電位VPPは主にロウデコーダ12において使用される電位であり、内部電位VPERDは主にDLL回路100において使用される電位であり、内部電位VPERIは他の多くの回路ブロックにおいて使用される電位である。

【0026】

図2は、DLL回路100の構成を示すブロック図である。

【0027】

図2に示すように、DLL回路100は、内部クロック信号ICLKを遅延させることによって内部クロック信号DelayCLKを生成するディレイライン101を備えている。ディレイライン101は、カウンタ部102のカウント値Bit0〜Bit5に応じた遅延を内部クロック信号ICLKに与えることによって、内部クロック信号DelayCLKを生成する回路である。

【0028】

内部クロック信号DelayCLKは、反転制御部103に供給される。反転制御部103は、内部クロック信号DelayCLKを反転させるか否かを制御する回路であり、後述するように、位相判定信号PD、反転制御信号INV及びカウンタリセット信号CRに基づき、内部クロック信号DelayCLKを反転させ又は反転させることなく出力する。本発明においては、内部クロック信号DelayCLKを「第2のクロック信号」と呼ぶことがある。

【0029】

反転制御部103から出力される内部クロック信号LCLKは、図1に示したFIFO回路15及び入出力回路16に供給されるとともに、レプリカ出力部104にも供給される。レプリカ出力部104は、内部クロック信号LCLKに基づいてレプリカである内部クロック信号RCLKを生成する回路であり、入出力回路16に含まれる出力回路16aと同一の特性を有している。上述の通り、出力回路16aは内部クロック信号LCLKに同期してリードデータDQを出力するものであることから、レプリカ出力部104から出力される内部クロック信号RCLKは、リードデータDQと正確に同期する。DRAMにおいては、リードデータDQが外部クロック信号CK,/CKに対して正確に同期している必要があり、両者の位相にずれが生じている場合にはこれを検出し、補正する必要がある。かかる検出は、位相比較部105によって行われ、その結果をカウンタ部102にフィードバックすることによって位相のずれが補正される。

【0030】

位相比較部105は、内部クロック信号ICLKと内部クロック信号RCLKの位相を比較し、その結果に基づいて位相判定信号PDを生成する回路である。ここで、内部クロック信号ICLKは外部クロック信号CK,/CKとタイミングが一致する信号であり、内部クロック信号RCLKはリードデータDQとタイミングが一致する信号であることから、位相比較部105は、外部クロック信号CK,/CKとリードデータDQの位相を間接的に比較していることになる。比較の結果、内部クロック信号RCLKが内部クロック信号ICLKに対して遅れていれば、位相判定信号PDを用いてカウンタ部102をカウントダウンし、これによりディレイライン101の遅延量を減少させる。逆に、内部クロック信号RCLKが内部クロック信号ICLKに対して進んでいれば、位相判定信号PDを用いてカウンタ部102をカウントアップし、これによりディレイライン101の遅延量を増加させる。このような動作を周期的に繰り返すことにより、内部クロック信号ICLKと内部クロック信号RCLKの位相を一致させれば、結果的に、リードデータDQと外部クロック信号CK,/CKの位相が一致することになる。本発明においては、レプリカである内部クロック信号RCLKを「第4のクロック信号」(又は「第2のクロック信号」)と呼ぶことがある。

【0031】

カウンタ部102のカウント値Bit0〜Bit5は、カウンタリセット信号CR及びコード部106から出力される初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされる。詳細については後述するが、カウンタリセット信号CRによってリセットされた場合のカウント値と、初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされた場合のカウント値は互いに異なる値である。本発明においては、カウンタリセット信号CRによってリセットされた場合のカウント値を「第1の初期値」と呼び、初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされた場合のカウント値を「第2の初期値」と呼ぶことがある。

【0032】

コード部106は、コード更新信号S0の活性化に応答して初期化信号LRST0,LSET1,LRST2,LSET3を所定の論理レベルに活性化させる。コード更新信号S0が活性化された場合に、初期化信号LRST0,LSET1,LRST2,LSET3をどのような論理レベルとするかは、設定信号SET1,SET2によって指定される。したがって、上述した第2の初期値は、設定信号SET1,SET2によって可変である。設定信号SET1,SET2は、図1に示したヒューズ回路39から出力される信号である。ヒューズ回路39は、設定信号SET1,SET2を不揮発的に記憶する不揮発性記憶回路であり、製造段階でプログラムされる。但し、本発明において上述した第2の初期値が可変であることは必須でなく、これを固定値とすることも可能である。この場合には、ヒューズ回路39は不要である。また、第2の初期値を可変とする場合であっても、ヒューズ回路39を用いることは必須でなく、他の不揮発性記憶回路を用いて設定信号SET1,SET2を記憶しても構わない。

【0033】

DLL回路100は、さらにDLLタイミング制御部107を備えている。DLLタイミング制御部107は、反転制御信号INV、カウンタリセット信号CR、コード更新信号S0及びカウンタ更新信号S1を生成する回路である。これら信号の活性化順序は予め定められており、DLLリセット信号DLLRSTが活性化すると、カウンタリセット信号CR、反転制御信号INV、コード更新信号S0及びカウンタ更新信号S1をこの順に活性化させる。カウンタ更新信号S1は、その後周期的に活性化される。

【0034】

次に、DLL回路100を構成する各回路ブロックの具体的な回路構成について説明する。

【0035】

図3は、位相比較部105の回路図である。

【0036】

図3に示すように、位相比較部105は、Pチャンネル型MOSトランジスタP1及びNチャンネル型MOSトランジスタN1と、Pチャンネル型MOSトランジスタP2及びNチャンネル型MOSトランジスタN2がクロスカップルされた構成を有している。トランジスタN1のソースには、内部クロック信号ICLKがハイレベルである期間にオンするNチャンネル型MOSトランジスタN3が接続され、トランジスタN2のソースには、内部クロック信号ICLKがローレベルである期間にオンするNチャンネル型MOSトランジスタN4が接続されている。トランジスタN3,N4のソースには、内部クロック信号RCLKがハイレベルである期間にオンするNチャンネル型MOSトランジスタN5が接続されている。

【0037】

かかる構成により、内部クロック信号RCLKの位相が内部クロック信号ICLKよりも遅れている場合には、トランジスタN5がオンする期間においてトランジスタN3がトランジスタN4よりも先にオンすることから、位相判定信号PDはハイレベルとなる。これに対し、内部クロック信号RCLKの位相が内部クロック信号ICLKよりも進んでいる場合には、トランジスタN5がオンする期間においてトランジスタN4がトランジスタN3よりも先にオンすることから、位相判定信号PDはローレベルとなる。

【0038】

これにより、位相比較部105は、クロックサイクルごとに内部クロック信号RCLKと内部クロック信号ICLKの位相を比較し、その結果を位相判定信号PDとして出力することができる。図2に示したように、位相判定信号PDはカウンタ部102及び反転制御部103に供給される。

【0039】

図4は、カウンタ部102の回路図である。

【0040】

図4に示すように、カウンタ部102は、縦続接続された6つのフリップフロップ回路FF0〜FF5を備えている。つまり、本実施形態においてはカウンタ部102のカウント値は6ビットで表される。カウント値の最小値は「000000」であり、十進数で0である。また、カウント値の最大値は「111111」であり、十進数で63である。したがって、本実施形態によるカウンタ部102は64段階のカウント値を出力することができる。但し、本発明においてカウンタ部102のビット数がこれに限定されるものではない。

【0041】

各フリップフロップ回路FF0〜FF5は、入力ノードD、出力ノードQ、クロックノードC、セットノードS及びリセットノード/Rを有している。その機能は一般的なフリップフロップ回路と同様であり、クロックノードCに供給される信号の立ち上がりエッジに応答して、入力ノードDに供給される信号をラッチし、ラッチした信号を出力ノードQから出力する。また、セットノードSに供給される信号がハイレベルに活性化した場合には、出力ノードQから出力される信号を強制的にハイレベルとし、リセットノード/Rに供給される信号がローレベルに活性化した場合には、出力ノードQから出力される信号を強制的にローレベルとする。

【0042】

図4に示すように、フリップフロップ回路FF0〜FF5はこの順に縦続接続されており、前段のフリップフロップ回路FFi(i=0〜4)の出力ノードQは、後段のフリップフロップ回路FFi+1の入力ノードDに接続されている。また、初段のフリップフロップ回路FF0の入力ノードDには、反転された位相判定信号PDが供給される。そして、フリップフロップ回路FF0〜FF5のクロックノードCには、カウンタ更新信号S1が供給に供給される。フリップフロップ回路FF0〜FF5の出力ノードQから出力される信号Bit0〜Bit5は、カウンタ部102のカウント値としてディレイライン101に供給される。ここで、信号Bit0はカウント値の最下位ビット(LSB)であり、信号Bit5はカウント値の最上位ビット(MSB)である。

【0043】

かかる構成により、カウンタ更新信号S1が活性化する度に、位相判定信号PDの論理レベルに基づいてカウント値Bit5〜Bit0がカウントアップ又はカウントダウンされることになる。カウント値Bit5〜Bit0が供給されるディレイライン101は、その値に応じた遅延を内部クロック信号ICLKに与え、これによって内部クロック信号DelayCLKを生成する。その遅延量は、カウント値Bit5〜Bit0が小さいほど小さく、カウント値Bit5〜Bit0が大きいほど大きくなる。

【0044】

また、各フリップフロップ回路FF0〜FF5には、カウンタリセット信号CRが供給される。具体的には、フリップフロップ回路FF0,FF2においては、カウンタリセット信号CRがセットノードSに供給される一方、残りのフリップフロップ回路FF1,FF3〜FF5においては、カウンタリセット信号CRの反転信号がリセットノード/Rに供給される。これにより、カウンタリセット信号CRがハイレベルに活性化すると、フリップフロップ回路FF0,FF2がセットされ、残りのフリップフロップ回路FF1,FF3〜FF5がリセットされることから、カウント値Bit5〜Bit0の値は「000101」となる。この値は十進数で5であり、上述した第1の初期値に相当する。このように、第1の初期値はカウント値の中心値から大きくオフセットしており、最小値の近傍に設計されている。このため、第1の初期値からカウントアップ可能な数は十分に確保される一方、カウントダウン可能な数は僅かである。

【0045】

さらに、フリップフロップ回路FF0〜FF3には、それぞれ初期化信号LRST0,LSET1,LRST2,LSET3が供給される。具体的には、初期化信号LRST0,LRST2についてはそれぞれフリップフロップ回路FF0,FF2のリセットノード/Rに供給され、初期化信号LSET1,LSET3についてはそれぞれフリップフロップ回路FF1,FF3のセットノードSに供給される。これら初期化信号LRST0,LSET1,LRST2,LSET3は、上述の通り、コード部106から供給される信号であり、その論理レベルは設定信号SET1,SET2によって指定される。

【0046】

図5は、コード部106の回路図である。

【0047】

図5に示すように、コード部106は、コード更新信号S0によって活性化される一種のデコード回路であり、設定信号SET1,SET2のデコード結果に基づいて初期化信号LRST0,LSET1,LRST2,LSET3を生成する。コード更新信号S0がローレベルである場合は、初期化信号LRST0,LRST2はハイレベル、初期化信号LSET1,LSET3はローレベルであることから、カウンタ部102に対して何らの影響も与えない。

【0048】

これに対し、コード更新信号S0がハイレベルになると、初期化信号LRST0,LSET1,LRST2,LSET3の1つ以上が活性化する。具体的には、設定信号SET1がローレベル、設定信号SET2がハイレベルである場合にコード更新信号S0が活性化すると、初期化信号LRST0がローレベルに活性化し、初期化信号LSET1がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF0がリセットされ、フリップフロップ回路FF1がセットされることから、カウント値は「000101」から「000110」にジャンプする。十進数で表記すると、カウント値が「5」から「6」へ1ピッチ分カウントアップされたことになる。

【0049】

また、設定信号SET1,SET2がいずれもローレベルである場合にコード更新信号S0が活性化すると、初期化信号LSET1がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF1がセットされることから、カウント値は「000101」から「000111」にジャンプする。十進数で表記すると、カウント値が「5」から「7」へ2ピッチ分カウントアップされたことになる。

【0050】

さらに、設定信号SET1がハイレベル、設定信号SET2がローレベルである場合にコード更新信号S0が活性化すると、初期化信号LRST0,LRST2がローレベルに活性化し、初期化信号LSET3がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF0,FF2がリセットされ、フリップフロップ回路FF3がセットされることから、カウント値は「000101」から「001000」にジャンプする。十進数で表記すると、カウント値が「5」から「8」へ3ピッチ分カウントアップされたことになる。

【0051】

そして、設定信号SET1,SET2がいずれもハイレベルである場合にコード更新信号S0が活性化すると、初期化信号LSET2がローレベルに活性化し、初期化信号LSET3がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF2がリセットされ、フリップフロップ回路FF3がセットされることから、カウント値は「000101」から「001001」にジャンプする。十進数で表記すると、カウント値が「5」から「9」へ4ピッチ分カウントアップされたことになる。

【0052】

このように、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップすることになる。後述するように、コード更新信号S0に応答して何ピッチ分ジャンプさせるかは、内部クロック信号ICLKに含まれるジッタ成分に大きさに合わせて選択すればよい。

【0053】

図6は、反転制御部103の回路図である。

【0054】

図6に示すように、反転制御部103は、内部クロック信号DelayCLK及びその反転信号/DelayCLKを受け、いずれか一方を出力するセレクタ回路110を備えている。セレクタ回路110による選択は、SRラッチ回路111の出力ノードQから出力される選択信号SELに基づいて行われる。セレクタ回路110は、選択信号SELがローレベルであれば反転されていない内部クロック信号DelayCLKを選択し、選択信号SELがハイレベルであれば反転された内部クロック信号/DelayCLKを選択する。

【0055】

SRラッチ回路111のセットノードSには、位相判定信号PD及び反転制御信号INVの論理積が入力され、リセットノードRには、カウンタリセット信号CRが入力される。かかる構成により、カウンタリセット信号CRが活性化した初期状態においては、反転されていない内部クロック信号DelayCLKが選択され、その後、反転制御信号INVがハイレベルに活性化したタイミングで位相判定信号PDの論理レベルがハイレベルであれば、SRラッチ回路111がセットされ、反転された内部クロック信号/DelayCLKが選択されることになる。

【0056】

以上がDLL回路100の具体的な回路構成である。次に、DLL回路100の動作について説明する。

【0057】

図7は、DLL回路100の動作を説明するためのタイミング図である。

【0058】

図7に示すように、外部からDLLリセットコマンドが発行され、これによりDLLリセット信号DLLRSTが活性化すると、DLLタイミング制御部107は、カウンタリセット信号CR、反転制御信号INV、コード更新信号S0及びカウンタ更新信号S1をこの順に活性化させる。これら信号を活性化させる間隔については任意であるが、カウント値の変化が内部クロック信号RCLKに正しく反映される時間を確保する必要がある。一例として、図7に示す期間T1〜T3は、いずれもカウンタ更新信号S1の活性化周期である期間T4以上であることが望ましい。

【0059】

まず、カウンタリセット信号CRが活性化すると、カウンタ部102のカウント値が第1の初期値である「000101」、つまり十進数で「5」にリセットされる。これにより、ディレイライン101の遅延量は、当該カウント値に応じた遅延を内部クロック信号ICLKに与え、これを内部クロック信号DelayCLKとして出力する。

【0060】

カウンタリセット信号CRの活性化から期間T1が経過すると、反転制御信号INVが活性化する。このタイミングで位相判定信号PDの論理レベルがローレベルであれば、SRラッチ回路111はセットされないため、反転されない内部クロック信号DelayCLKが選択され、これが内部クロック信号LCLKとして出力される。一方、このタイミングで位相判定信号PDの論理レベルがハイレベルであれば、SRラッチ回路111がセットされるため、反転された内部クロック信号/DelayCLKが選択され、これが内部クロック信号LCLKとして出力される。反転された内部クロック信号/DelayCLKを用いる意義については後述する。

【0061】

反転制御信号INVの活性化から期間T2が経過すると、コード更新信号S0が活性化する。これにより、カウンタ部102のカウント値は、第1の初期値から第2の初期値にジャンプする。第2の初期値の具体的な値については既に説明した通りである。図7に示す例では、カウント値が「000101」から「000111」へ2ピッチ分カウントアップされた例が示されている。

【0062】

コード更新信号S0の活性化から期間T3が経過すると、カウンタ更新信号S1が活性化する。カウンタ更新信号S1が活性化すると、図4を用いて説明したように、位相判定信号PDの論理レベルに基づいて、カウンタ部102のカウント値が1ピッチ分だけカウントアップ又はカウントダウンされる。これは、内部クロック信号RCLKの位相を内部クロック信号ICLKの位相により近づけるための動作である。図7に示す例では、カウント値が「000111」から「001000」へカウントアップされた例が示されている。

【0063】

その後は、期間T4ごとにカウンタ更新信号S1が周期的に活性化し、その都度、カウンタ部102のカウント値がカウントアップ又はカウントダウンされる。このような動作を繰り返すことにより、内部クロック信号RCLKの位相が内部クロック信号ICLKの位相とほぼ一致した状態となり、一致した後は、その状態が保たれる。つまり、DLL回路100がロックした状態となる。

【0064】

図8は、反転制御部103によって内部クロック信号の反転信号/DelayCLKが選択されるケースを説明するためのタイミング図であり、カウンタ部102のカウント値が第1の初期値に設定されている場合の位相を示している。

【0065】

図8において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)は反転された内部クロック信号/DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(d)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0066】

図8に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合、反転制御信号INVの活性化タイミングにおいて位相判定信号PDがハイレベルとなる。これに基づき、反転された内部クロック信号/DelayCLKが選択されることから内部クロック信号RCLKの波形は(c)の波形に反転する。つまり、内部クロック信号RCLKの立ち上がりエッジR2が1/2周期分移動することから、内部クロック信号ICLKの目標とする立ち上がりエッジR0までの位相差が減少する。

【0067】

ここで、反転された内部クロック信号/DelayCLKを使用せず、反転されていない内部クロック信号DelayCLKを内部クロック信号LCLKとして使用すると、(b)に示すように、一つ前の立ち上がりエッジRXを目標エッジとしてDLL回路100が動作してしまう。つまり、反転されていない内部クロック信号DelayCLKを使用すると、位相判定信号PDがハイレベルであるために、カウンタ部102はカウントダウンを進める必要がある。これを許容するためには、カウンタ部102の第1の初期値を中心値近傍に設定するとともに、カウント可能な数を本実施形態の約2倍に設計する必要があるが、この場合、カウンタ部102及びディレイライン101の回路規模が大きくなってしまう。これを避けるため、本実施形態ではカウンタ部102の第1の初期値をオフセットさせるとともに、カウント可能な数を少なく設計している。このため、第1の初期値からカウントダウンを何度も繰り返すことはできないが、本実施形態では、図8に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合には、反転された内部クロック信号/DelayCLKを内部クロック信号LCLKとして用いていることから、上記の問題が回避される。

【0068】

さらに、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされることから、図8の(d)に示すように、内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0により近くなる。これにより、その後カウンタ更新信号S1に同期して何回かのカウントアップ(場合によっては少数のカウントダウン)を行うことにより、DLL回路100をロックさせることが可能となる。

【0069】

図9は、反転制御部103によって内部クロック信号DelayCLKが選択されるケースを説明するためのタイミング図であり、カウンタ部102のカウント値が第1の初期値に設定されている場合の位相を示している。

【0070】

図9において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0071】

図9に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのローレベルの期間Bに現れる場合、反転制御信号INVの活性化タイミングにおいて位相判定信号PDがローレベルとなる。これに基づき、反転されない内部クロック信号DelayCLKが選択される。これにより、内部クロック信号ICLKの立ち上がりエッジR0を目標とした制御が行われる。

【0072】

さらに、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされることから、図9に示すように、内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0により近くなる。これにより、その後カウンタ更新信号S1に同期して何回かのカウントアップ(場合によっては少数のカウントダウン)を行うことにより、DLL回路100をロックさせることが可能となる。

【0073】

このように、本実施形態では、初期状態における位相がいずれの状態であっても、カウンタ部102を主にカウントアップすることによってDLL回路100がロックする。このため、カウンタ部102のカウント値が第1の初期値から繰り返しカウントダウンされる状態を想定する必要が無くなることから、カウンタ部102及びディレイライン101の回路規模を小さく設計することが可能となる。

【0074】

図10は、ジッタの影響により反転されていない内部クロック信号DelayCLKが誤って選択されたケースを説明するためのタイミング図であり、図8に対応している。図10において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0075】

図10に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合、本来であれば、図8を用いて説明したように、反転された内部クロック信号/DelayCLKが選択される。しかしながら、ジッタの影響により、反転制御信号INVが活性化するタイミングにおいて、内部クロック信号RCLKの立ち上がりエッジR1が内部クロック信号ICLKのローレベルの期間Bに偶然現れた場合、反転されない内部クロック信号DelayCLKが選択されることになる。このようにジッタの影響によって反転制御部103の動作が失敗した場合、内部クロック信号ICLKの一つ前の立ち上がりエッジRXを目標として位相制御動作が進行しようとする。

【0076】

しかしながら、本実施形態では、反転制御信号INVが活性化した後、コード更新信号S0が活性化し、これによってカウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされる。このため、図10に示すように、(c)に示すジャンプ後の内部クロック信号RCLKは、その立ち上がりエッジR3が内部クロック信号ICLKのローレベルの期間Bまで移動するため、内部クロック信号ICLKの立ち上がりエッジR0を目標としてカウンタ部102のカウントアップが行われることになる。これにより、内部クロック信号ICLKの一つ前の立ち上がりエッジRXを目標としてカウントダウンを繰り返すことによるカウンタ部102のスタックを防止することができる。

【0077】

したがって、コード更新信号S0に応答したカウント値のジャンプ量は、想定されるジッタを考慮して選択すればよい。つまり、内部クロック信号ICLKに含まれるジッタ成分に対応するカウント値の差よりも大きいジャンプ量となるよう、設定信号SET1,SET2を選択すればよい。実際には、想定されるジッタが十分に小さい場合にはジャンプ量を1ピッチとしても構わないが、ジッタの影響を確実に排除するためには、2ピッチ以上のジャンプ量に設定することが望ましい。

【0078】

図11は、ジッタの影響により反転された内部クロック信号/DelayCLKが誤って選択されたケースを説明するためのタイミング図であり、図9に対応している。図11において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)は反転された内部クロック信号/DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(d)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0079】

図11に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのローレベルの期間Bに現れる場合、本来であれば、図9を用いて説明したように、反転されない内部クロック信号DelayCLKが選択される。しかしながら、ジッタの影響により、反転制御信号INVが活性化するタイミングにおいて、内部クロック信号RCLKの立ち上がりエッジR1が内部クロック信号ICLKのハイレベルの期間Aに偶然現れた場合、反転された内部クロック信号/DelayCLKが選択されることになる。これにより、内部クロック信号RCLKの波形は、(c)のように反転する。その後、コード更新信号S0が活性化し、(d)に示すようにカウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされる。

【0080】

その結果、ジャンプ後の内部クロック信号RCLKは、その立ち上がりエッジR3が内部クロック信号ICLKのハイレベルの期間Aに位置することになるが、ジッタの影響による誤判定は、内部クロック信号ICLKの立ち下がりエッジF0と内部クロック信号RCLKの立ち上がりエッジR1が近接している場合に限られる。このため、ジャンプ後における内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0に対して位相が僅かに遅れているに過ぎない。このため、僅かな数のカウントダウンによってDLL回路100をロックすることができ、したがってカウンタ部102がスタックすることはない。

【0081】

図12は、DLL回路100がロックする過程を説明するための模式的なタイミング図である。

【0082】

図12に示す例では、カウンタリセット信号CRの活性化によって、カウンタ部102のカウント値が第1の初期値である「000101」にリセットされると、内部クロック信号RCLKの位相が内部クロック信号ICLKの位相よりも進んだ状態となっている。次に、コード更新信号S0の活性化によって、カウンタ部102のカウント値が第1の初期値である「000101」から第2の初期値である「001000」に2ピッチジャンプしている。その後、周期的に活性化するカウンタ更新信号S1に応答してカウント値が「001001」、「0001010」にカウントアップされ、次に、「001001」にカウントダウンされている。カウント値がこのような変化パターンを示した状態がDLL回路100のロック状態であり、内部クロック信号RCLKの位相は内部クロック信号ICLKの位相にほぼ一致したまま追従する。

【0083】

以上説明したように、本実施形態によれば、反転制御部103を用いて内部クロック信号DelayCLK又は反転された内部クロック信号/DelayCLKを選択していることから、カウンタ部102及びディレイライン101の回路規模を従来に比べて縮小することができる。しかも、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントアップしていることから、ジッタの影響によって反転制御部103が誤った選択を行った場合であっても、カウンタ部102がスタックすることが無く、DLL回路100を正しくロックさせることが可能となる。

【0084】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0085】

例えば、上記実施形態では、第1の初期値を最小値近傍の値とし、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントアップしているが、これとは逆に、第1の初期値を最大値近傍の値とし、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントダウンしても構わない。

【符号の説明】

【0086】

10 半導体装置

11 メモリセルアレイ

12 ロウデコーダ

13 カラムデコーダ

14 モードレジスタ

15 FIFO回路

16 入出力回路

16a 出力回路

21 アドレス端子

22 コマンド端子

23 クロック端子

24 データ端子

25 電源端子

31 アドレス入力回路

32 アドレスラッチ回路

33 コマンド入力回路

34 コマンドデコード回路

35 リフレッシュ制御回路

36 クロック入力回路

37 タイミングジェネレータ

38 内部電源発生回路

39 ヒューズ回路

100 DLL回路

101 ディレイライン

102 カウンタ部

103 反転制御部

104 レプリカ出力部

105 位相比較部

106 コード部

107 タイミング制御部

110 セレクタ回路

111 SRラッチ回路

ICLK 内部クロック信号(第1のクロック信号)

DelayCLK 内部クロック信号(第2のクロック信号)

/DelayCLK 内部クロック信号(反転された第2のクロック信号)

LCLK 内部クロック信号(第3のクロック信号)

RCLK 内部クロック信号(第4のクロック信号)

Bit0〜Bit5 カウント値

CR カウンタリセット信号

INV 反転制御信号

S0 コード更新信号

S1 カウンタ更新信号

【技術分野】

【0001】

本発明は半導体装置及びその制御方法に関し、特に、DLL回路を備える半導体装置及びその制御方法に関する。

【背景技術】

【0002】

同期型のDRAM(Dynamic Random Access Memory)のようにクロック信号に同期した動作を行う半導体装置においては、位相制御された内部クロック信号が必要となることがある。位相制御された内部クロック信号は、主にDLL(Delay Locked Loop)回路によって生成される(特許文献1参照)。DLL回路には、内部クロック信号を遅延させるディレイラインが含まれており、その遅延量はカウンタ回路から出力されるカウント値よって定められる。

【0003】

一般的なDLL回路においては、制御対象となるレプリカクロック信号の立ち上がりエッジが基準となる入力クロック信号の立ち上がりエッジと一致するよう、カウント値のアップカウント又はダウンカウントが行われる。したがって、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がローレベルである場合、すなわちレプリカクロック信号の方が位相が進んでいる場合には、ディレイラインの遅延量を増大させる。逆に、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がハイレベルである場合、すなわちレプリカクロック信号の方が位相が遅れている場合には、ディレイラインの遅延量を減少させればよい。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−192164号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した一般的なDLL回路では、カウンタ回路による遅延量の調整可能範囲が最低でも1クロックサイクルに相当する範囲だけ必要となる。このため、ディレイラインの回路規模が大きくなるという問題があった。そこで、本発明者は、カウンタ回路による遅延量の調整可能範囲を縮小可能なDLL回路について研究を行った。その結果、レプリカクロック信号の立ち上がりエッジが現れるタイミングにおいて入力クロック信号がハイレベルである場合には、レプリカクロック信号を反転させることにより、いずれのケースにおいてもディレイラインの遅延量を増大させる方向に制御可能なDLL回路を開発した。これによれば、カウンタ回路による遅延量の調整可能範囲が1/2クロックサイクル分で済むことから、ディレイラインの回路規模を縮小することが可能となる。この場合、カウンタ部のカウント値の初期値は中心値ではなく、最小値近傍にオフセットさせておき、アップカウントによってDLL回路をロックさせることになる。

【0006】

しかしながら、上記のDLL回路においては、入力クロック信号にジッタ成分が重畳している場合、レプリカクロック信号を反転させるか否かの判定を誤ることがあった。かかる判定を誤った場合、カウント値の初期値が中心値からオフセットされた値であることから、ダウンカウントを継続するとすぐに最小値に達してしまい、これ以上の位相制御が不可能になるという現象が生じることがあった。このため、本発明者は、このような現象が生じにくい半導体装置について鋭意研究を行った。

【課題を解決するための手段】

【0007】

本発明による半導体装置は、カウント値を生成するカウンタ部と、前記カウント値に応じて第1のクロック信号を遅延させることにより第2のクロック信号を生成するディレイラインと、前記第2のクロック信号を受け、その位相を反転させたクロック信号又は反転させないクロック信号のいずれか一方のクロック信号を選択して第3のクロック信号として出力する反転制御部と、前記第3のクロック信号に基づいて第4のクロック信号を生成するレプリカ出力部と、前記第1のクロック信号と前記第4のクロック信号の位相を比較することによって位相判定信号を生成する位相比較部と、リセット信号、反転制御信号、コード更新信号及びカウンタ更新信号を活性化させる制御部と、を備え、前記リセット信号に応答して、前記カウンタ部のカウント値は第1の初期値にリセットされ、且つ、前記反転制御部は前記反転させないクロック信号を選択するようにセットされ、前記反転制御部は、前記反転制御信号が活性化した際における前記位相判定信号の論理レベルに基づいて前記いずれか一方のクロック信号を選択し、前記カウンタ部のカウント値は、前記反転制御部が選択した後に前記コード更新信号に応答して前記第1の初期値から第2の初期値に更新され、前記カウンタ部のカウント値は、前記カウンタ更新信号が活性化した際の前記位相判定信号の論理レベルに基づいて前記第2の初期値からアップカウント又はダウンカウントされることを特徴とする。

【0008】

本発明による半導体装置の制御方法は、DLL回路に含まれるカウンタ回路のカウント値を第1の初期値にリセットして第1のクロック信号を前記第1の初期値に対応して遅延させた第2のクロック信号を出力し、前記第1のクロック信号の位相及び前記第2のクロック信号の位相を互いに比較し、前記比較の結果に応じて前記第2のクロック信号の位相を反転する制御及び反転しない制御の一方を行い、前記制御の後に、前記カウント値を前記第1の初期値から第2の初期値に更新し、前記更新の後に、前記第1のクロック信号の位相及び前記第2の初期値に対応する前記第2のクロック信号の位相を互いに比較し、比較結果に応じて前記カウント値を前記第2の初期値からアップカウント又はダウンカウントして前記第2のクロック信号の遅延量を調整することを特徴とする。

【発明の効果】

【0009】

本発明によれば、ジッタなどの影響によって第2のクロック信号を誤って反転させ、或いは誤って反転させなかった場合であっても、カウンタ部のカウント値を第1の初期値から第2の初期値にジャンプさせることによって、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることによって遅延量の調整可能範囲を縮小した場合であっても、DLL回路を正しくロックさせることが可能となる。

【図面の簡単な説明】

【0010】

【図1】本発明の好ましい実施形態による半導体装置10の全体構成を示すブロック図である。

【図2】DLL回路100の構成を示すブロック図である。

【図3】位相比較部105の回路図である。

【図4】カウンタ部102の回路図である。

【図5】コード部106の回路図である。

【図6】反転制御部103の回路図である。

【図7】DLL回路100の動作を説明するためのタイミング図である。

【図8】反転制御部103によって内部クロック信号の反転信号/DelayCLKが選択されるケースを説明するためのタイミング図である。

【図9】反転制御部103によって内部クロック信号DelayCLKが選択されるケースを説明するためのタイミング図である。

【図10】ジッタの影響により反転されていない内部クロック信号DelayCLKが誤って選択されたケースを説明するためのタイミング図である。

【図11】ジッタの影響により反転された内部クロック信号/DelayCLKが誤って選択されたケースを説明するためのタイミング図である。

【図12】DLL回路100がロックする過程を説明するための模式的なタイミング図である。

【発明を実施するための形態】

【0011】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0012】

図1は、本発明の好ましい実施形態による半導体装置10の全体構成を示すブロック図である。

【0013】

本実施形態による半導体装置10はDRAMであり、メモリセルアレイ11を有している。メモリセルアレイ11は、複数のワード線WLと複数のビット線BLを備え、これらの交点にメモリセルMCが配置された構成を有している。ワード線WLの選択はロウデコーダ12によって行われ、ビット線BLの選択はカラムデコーダ13によって行われる。

【0014】

図1に示すように、半導体装置10には外部端子としてアドレス端子21、コマンド端子22、クロック端子23、データ端子24及び電源端子25が設けられている。

【0015】

アドレス端子21は、外部からアドレス信号ADDが入力される端子である。アドレス端子21に入力されたアドレス信号ADDは、アドレス入力回路31を介してアドレスラッチ回路32に供給され、アドレスラッチ回路32にラッチされる。アドレスラッチ回路32にラッチされたアドレス信号ADDは、ロウデコーダ12、カラムデコーダ13又はモードレジスタ14に供給される。モードレジスタ14は、半導体装置10の動作モードを示すパラメータが設定される回路である。

【0016】

コマンド端子22は、外部からコマンド信号CMDが入力される端子である。コマンド信号CMDは、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、リセット信号/RESETなどの複数の信号からなる。ここで、信号名の先頭にスラッシュ(/)が付されているのは、対応する信号の反転信号、或いは、当該信号がローアクティブな信号であることを意味する。コマンド端子22に入力されたコマンド信号CMDは、コマンド入力回路33を介してコマンドデコード回路34に供給される。コマンドデコード回路34は、コマンド信号CMDをデコードすることによって各種内部コマンドを生成する回路である。内部コマンドとしては、アクティブ信号IACT、カラム信号ICOL、リフレッシュ信号IREF、モードレジスタセット信号MRS、DLLリセット信号DLLRSTなどがある。

【0017】

アクティブ信号IACTは、コマンド信号CMDがロウアクセス(アクティブコマンド)を示している場合に活性化される信号である。アクティブ信号IACTが活性化すると、アドレスラッチ回路32にラッチされたアドレス信号ADDがロウデコーダ12に供給される。これにより、当該アドレス信号ADDにより指定されるワード線WLが選択される。

【0018】

カラム信号ICOLは、コマンド信号CMDがカラムアクセス(リードコマンド又はライトコマンド)を示している場合に活性化される信号である。内部カラム信号ICOLが活性化すると、アドレスラッチ回路32にラッチされたアドレス信号ADDがカラムデコーダ13に供給される。これにより、当該アドレス信号ADDにより指定されるビット線BLが選択される。

【0019】

したがって、アクティブコマンド及びリードコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力すれば、これらロウアドレス及びカラムアドレスによって指定されるメモリセルMCからリードデータが読み出される。リードデータDQは、FIFO回路15及び入出力回路16を介して、データ端子24から外部に出力される。一方、アクティブコマンド及びライトコマンドをこの順に入力するとともに、これらに同期してロウアドレス及びカラムアドレスを入力し、その後、データ端子24にライトデータDQを入力すれば、ライトデータDQは入出力回路16及びFIFO回路15を介してメモリセルアレイ11に供給され、ロウアドレス及びカラムアドレスによって指定されるメモリセルMCに書き込まれる。FIFO回路15及び入出力回路16の動作は、内部クロック信号LCLKに同期して行われる。内部クロック信号LCLKは、後述するDLL回路100によって生成される。特に、入出力回路16にはリードデータDQを出力する出力回路16aが含まれており、リードデータDQの出力は内部クロック信号LCLKに同期して行われる。

【0020】

リフレッシュ信号IREFは、コマンド信号CMDがリフレッシュコマンドを示している場合に活性化される信号である。リフレッシュ信号IREFが活性化するとリフレッシュ制御回路35によってロウアクセスが行われ、所定のワード線WLが選択される。これにより、選択されたワード線WLに接続された複数のメモリセルMCがリフレッシュされる。ワード線WLの選択は、リフレッシュ制御回路35に含まれる図示しないリフレッシュカウンタによって行われる。

【0021】

モードレジスタセット信号MRSは、コマンド信号CMDがモードレジスタセットコマンドを示している場合に活性化される信号である。したがって、モードレジスタセットコマンドを入力するとともに、これに同期してアドレス端子21からモード信号を入力すれば、モードレジスタ14の設定値を書き換えることができる。

【0022】

クロック端子23は、外部クロック信号CK,/CKが入力される端子である。外部クロック信号CKと外部クロック信号/CKは互いに相補の信号であり、いずれもクロック入力回路36に供給される。クロック入力回路36は、外部クロック信号CK,/CKに基づいて内部クロック信号ICLKを生成する。内部クロック信号ICLKは、半導体装置10の内部における基本クロック信号であり、本発明においては「第1のクロック信号」と呼ぶことがある。内部クロック信号ICLKは、タイミングジェネレータ37に供給され、これによって各種内部クロック信号が生成される。タイミングジェネレータ37によって生成される各種内部クロック信号は、アドレスラッチ回路32やコマンドデコード回路34などの回路ブロックに供給され、これら回路ブロックの動作タイミングを規定する。

【0023】

内部クロック信号ICLKは、DLL回路100にも供給される。DLL回路100は、内部クロック信号ICLKに基づいて内部クロック信号LCLKを生成する回路である。内部クロック信号LCLKは位相制御されたクロック信号であり、本発明においては「第3のクロック信号」と呼ぶことがある。上述の通り、内部クロック信号LCLKはFIFO回路15及び入出力回路16に供給される。これにより、リードデータDQは内部クロック信号LCLKに同期して出力されることになる。

【0024】

DLL回路100は、コマンドデコード回路34から出力されるDLLリセット信号DLLRSTによってリセットされる。DLLリセット信号DLLRSTは、リセット信号/RESETや、DLLリセットコマンド(DLLRST)に応答して活性化される。リセット信号/RESETは電源投入時などに活性化される信号であり、DLLリセットコマンドはDLL回路100のリセットが必要な際に発行されるコマンドである。したがって、電源投入直後などにおいては、DLLリセット信号DLLRSTによってDLL回路100がリセットされることになる。

【0025】

電源端子25は、電源電位VDD,VSSが供給される端子である。電源端子25に供給される電源電位VDD,VSSは内部電源発生回路38に供給される。内部電源発生回路38は、電源電位VDD,VSSに基づいて各種の内部電位VPP,VPERD,VPERIなどを発生させる。内部電位VPPは主にロウデコーダ12において使用される電位であり、内部電位VPERDは主にDLL回路100において使用される電位であり、内部電位VPERIは他の多くの回路ブロックにおいて使用される電位である。

【0026】

図2は、DLL回路100の構成を示すブロック図である。

【0027】

図2に示すように、DLL回路100は、内部クロック信号ICLKを遅延させることによって内部クロック信号DelayCLKを生成するディレイライン101を備えている。ディレイライン101は、カウンタ部102のカウント値Bit0〜Bit5に応じた遅延を内部クロック信号ICLKに与えることによって、内部クロック信号DelayCLKを生成する回路である。

【0028】

内部クロック信号DelayCLKは、反転制御部103に供給される。反転制御部103は、内部クロック信号DelayCLKを反転させるか否かを制御する回路であり、後述するように、位相判定信号PD、反転制御信号INV及びカウンタリセット信号CRに基づき、内部クロック信号DelayCLKを反転させ又は反転させることなく出力する。本発明においては、内部クロック信号DelayCLKを「第2のクロック信号」と呼ぶことがある。

【0029】

反転制御部103から出力される内部クロック信号LCLKは、図1に示したFIFO回路15及び入出力回路16に供給されるとともに、レプリカ出力部104にも供給される。レプリカ出力部104は、内部クロック信号LCLKに基づいてレプリカである内部クロック信号RCLKを生成する回路であり、入出力回路16に含まれる出力回路16aと同一の特性を有している。上述の通り、出力回路16aは内部クロック信号LCLKに同期してリードデータDQを出力するものであることから、レプリカ出力部104から出力される内部クロック信号RCLKは、リードデータDQと正確に同期する。DRAMにおいては、リードデータDQが外部クロック信号CK,/CKに対して正確に同期している必要があり、両者の位相にずれが生じている場合にはこれを検出し、補正する必要がある。かかる検出は、位相比較部105によって行われ、その結果をカウンタ部102にフィードバックすることによって位相のずれが補正される。

【0030】

位相比較部105は、内部クロック信号ICLKと内部クロック信号RCLKの位相を比較し、その結果に基づいて位相判定信号PDを生成する回路である。ここで、内部クロック信号ICLKは外部クロック信号CK,/CKとタイミングが一致する信号であり、内部クロック信号RCLKはリードデータDQとタイミングが一致する信号であることから、位相比較部105は、外部クロック信号CK,/CKとリードデータDQの位相を間接的に比較していることになる。比較の結果、内部クロック信号RCLKが内部クロック信号ICLKに対して遅れていれば、位相判定信号PDを用いてカウンタ部102をカウントダウンし、これによりディレイライン101の遅延量を減少させる。逆に、内部クロック信号RCLKが内部クロック信号ICLKに対して進んでいれば、位相判定信号PDを用いてカウンタ部102をカウントアップし、これによりディレイライン101の遅延量を増加させる。このような動作を周期的に繰り返すことにより、内部クロック信号ICLKと内部クロック信号RCLKの位相を一致させれば、結果的に、リードデータDQと外部クロック信号CK,/CKの位相が一致することになる。本発明においては、レプリカである内部クロック信号RCLKを「第4のクロック信号」(又は「第2のクロック信号」)と呼ぶことがある。

【0031】

カウンタ部102のカウント値Bit0〜Bit5は、カウンタリセット信号CR及びコード部106から出力される初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされる。詳細については後述するが、カウンタリセット信号CRによってリセットされた場合のカウント値と、初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされた場合のカウント値は互いに異なる値である。本発明においては、カウンタリセット信号CRによってリセットされた場合のカウント値を「第1の初期値」と呼び、初期化信号LRST0,LSET1,LRST2,LSET3によってリセットされた場合のカウント値を「第2の初期値」と呼ぶことがある。

【0032】

コード部106は、コード更新信号S0の活性化に応答して初期化信号LRST0,LSET1,LRST2,LSET3を所定の論理レベルに活性化させる。コード更新信号S0が活性化された場合に、初期化信号LRST0,LSET1,LRST2,LSET3をどのような論理レベルとするかは、設定信号SET1,SET2によって指定される。したがって、上述した第2の初期値は、設定信号SET1,SET2によって可変である。設定信号SET1,SET2は、図1に示したヒューズ回路39から出力される信号である。ヒューズ回路39は、設定信号SET1,SET2を不揮発的に記憶する不揮発性記憶回路であり、製造段階でプログラムされる。但し、本発明において上述した第2の初期値が可変であることは必須でなく、これを固定値とすることも可能である。この場合には、ヒューズ回路39は不要である。また、第2の初期値を可変とする場合であっても、ヒューズ回路39を用いることは必須でなく、他の不揮発性記憶回路を用いて設定信号SET1,SET2を記憶しても構わない。

【0033】

DLL回路100は、さらにDLLタイミング制御部107を備えている。DLLタイミング制御部107は、反転制御信号INV、カウンタリセット信号CR、コード更新信号S0及びカウンタ更新信号S1を生成する回路である。これら信号の活性化順序は予め定められており、DLLリセット信号DLLRSTが活性化すると、カウンタリセット信号CR、反転制御信号INV、コード更新信号S0及びカウンタ更新信号S1をこの順に活性化させる。カウンタ更新信号S1は、その後周期的に活性化される。

【0034】

次に、DLL回路100を構成する各回路ブロックの具体的な回路構成について説明する。

【0035】

図3は、位相比較部105の回路図である。

【0036】

図3に示すように、位相比較部105は、Pチャンネル型MOSトランジスタP1及びNチャンネル型MOSトランジスタN1と、Pチャンネル型MOSトランジスタP2及びNチャンネル型MOSトランジスタN2がクロスカップルされた構成を有している。トランジスタN1のソースには、内部クロック信号ICLKがハイレベルである期間にオンするNチャンネル型MOSトランジスタN3が接続され、トランジスタN2のソースには、内部クロック信号ICLKがローレベルである期間にオンするNチャンネル型MOSトランジスタN4が接続されている。トランジスタN3,N4のソースには、内部クロック信号RCLKがハイレベルである期間にオンするNチャンネル型MOSトランジスタN5が接続されている。

【0037】

かかる構成により、内部クロック信号RCLKの位相が内部クロック信号ICLKよりも遅れている場合には、トランジスタN5がオンする期間においてトランジスタN3がトランジスタN4よりも先にオンすることから、位相判定信号PDはハイレベルとなる。これに対し、内部クロック信号RCLKの位相が内部クロック信号ICLKよりも進んでいる場合には、トランジスタN5がオンする期間においてトランジスタN4がトランジスタN3よりも先にオンすることから、位相判定信号PDはローレベルとなる。

【0038】

これにより、位相比較部105は、クロックサイクルごとに内部クロック信号RCLKと内部クロック信号ICLKの位相を比較し、その結果を位相判定信号PDとして出力することができる。図2に示したように、位相判定信号PDはカウンタ部102及び反転制御部103に供給される。

【0039】

図4は、カウンタ部102の回路図である。

【0040】

図4に示すように、カウンタ部102は、縦続接続された6つのフリップフロップ回路FF0〜FF5を備えている。つまり、本実施形態においてはカウンタ部102のカウント値は6ビットで表される。カウント値の最小値は「000000」であり、十進数で0である。また、カウント値の最大値は「111111」であり、十進数で63である。したがって、本実施形態によるカウンタ部102は64段階のカウント値を出力することができる。但し、本発明においてカウンタ部102のビット数がこれに限定されるものではない。

【0041】

各フリップフロップ回路FF0〜FF5は、入力ノードD、出力ノードQ、クロックノードC、セットノードS及びリセットノード/Rを有している。その機能は一般的なフリップフロップ回路と同様であり、クロックノードCに供給される信号の立ち上がりエッジに応答して、入力ノードDに供給される信号をラッチし、ラッチした信号を出力ノードQから出力する。また、セットノードSに供給される信号がハイレベルに活性化した場合には、出力ノードQから出力される信号を強制的にハイレベルとし、リセットノード/Rに供給される信号がローレベルに活性化した場合には、出力ノードQから出力される信号を強制的にローレベルとする。

【0042】

図4に示すように、フリップフロップ回路FF0〜FF5はこの順に縦続接続されており、前段のフリップフロップ回路FFi(i=0〜4)の出力ノードQは、後段のフリップフロップ回路FFi+1の入力ノードDに接続されている。また、初段のフリップフロップ回路FF0の入力ノードDには、反転された位相判定信号PDが供給される。そして、フリップフロップ回路FF0〜FF5のクロックノードCには、カウンタ更新信号S1が供給に供給される。フリップフロップ回路FF0〜FF5の出力ノードQから出力される信号Bit0〜Bit5は、カウンタ部102のカウント値としてディレイライン101に供給される。ここで、信号Bit0はカウント値の最下位ビット(LSB)であり、信号Bit5はカウント値の最上位ビット(MSB)である。

【0043】

かかる構成により、カウンタ更新信号S1が活性化する度に、位相判定信号PDの論理レベルに基づいてカウント値Bit5〜Bit0がカウントアップ又はカウントダウンされることになる。カウント値Bit5〜Bit0が供給されるディレイライン101は、その値に応じた遅延を内部クロック信号ICLKに与え、これによって内部クロック信号DelayCLKを生成する。その遅延量は、カウント値Bit5〜Bit0が小さいほど小さく、カウント値Bit5〜Bit0が大きいほど大きくなる。

【0044】

また、各フリップフロップ回路FF0〜FF5には、カウンタリセット信号CRが供給される。具体的には、フリップフロップ回路FF0,FF2においては、カウンタリセット信号CRがセットノードSに供給される一方、残りのフリップフロップ回路FF1,FF3〜FF5においては、カウンタリセット信号CRの反転信号がリセットノード/Rに供給される。これにより、カウンタリセット信号CRがハイレベルに活性化すると、フリップフロップ回路FF0,FF2がセットされ、残りのフリップフロップ回路FF1,FF3〜FF5がリセットされることから、カウント値Bit5〜Bit0の値は「000101」となる。この値は十進数で5であり、上述した第1の初期値に相当する。このように、第1の初期値はカウント値の中心値から大きくオフセットしており、最小値の近傍に設計されている。このため、第1の初期値からカウントアップ可能な数は十分に確保される一方、カウントダウン可能な数は僅かである。

【0045】

さらに、フリップフロップ回路FF0〜FF3には、それぞれ初期化信号LRST0,LSET1,LRST2,LSET3が供給される。具体的には、初期化信号LRST0,LRST2についてはそれぞれフリップフロップ回路FF0,FF2のリセットノード/Rに供給され、初期化信号LSET1,LSET3についてはそれぞれフリップフロップ回路FF1,FF3のセットノードSに供給される。これら初期化信号LRST0,LSET1,LRST2,LSET3は、上述の通り、コード部106から供給される信号であり、その論理レベルは設定信号SET1,SET2によって指定される。

【0046】

図5は、コード部106の回路図である。

【0047】

図5に示すように、コード部106は、コード更新信号S0によって活性化される一種のデコード回路であり、設定信号SET1,SET2のデコード結果に基づいて初期化信号LRST0,LSET1,LRST2,LSET3を生成する。コード更新信号S0がローレベルである場合は、初期化信号LRST0,LRST2はハイレベル、初期化信号LSET1,LSET3はローレベルであることから、カウンタ部102に対して何らの影響も与えない。

【0048】

これに対し、コード更新信号S0がハイレベルになると、初期化信号LRST0,LSET1,LRST2,LSET3の1つ以上が活性化する。具体的には、設定信号SET1がローレベル、設定信号SET2がハイレベルである場合にコード更新信号S0が活性化すると、初期化信号LRST0がローレベルに活性化し、初期化信号LSET1がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF0がリセットされ、フリップフロップ回路FF1がセットされることから、カウント値は「000101」から「000110」にジャンプする。十進数で表記すると、カウント値が「5」から「6」へ1ピッチ分カウントアップされたことになる。

【0049】

また、設定信号SET1,SET2がいずれもローレベルである場合にコード更新信号S0が活性化すると、初期化信号LSET1がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF1がセットされることから、カウント値は「000101」から「000111」にジャンプする。十進数で表記すると、カウント値が「5」から「7」へ2ピッチ分カウントアップされたことになる。

【0050】

さらに、設定信号SET1がハイレベル、設定信号SET2がローレベルである場合にコード更新信号S0が活性化すると、初期化信号LRST0,LRST2がローレベルに活性化し、初期化信号LSET3がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF0,FF2がリセットされ、フリップフロップ回路FF3がセットされることから、カウント値は「000101」から「001000」にジャンプする。十進数で表記すると、カウント値が「5」から「8」へ3ピッチ分カウントアップされたことになる。

【0051】

そして、設定信号SET1,SET2がいずれもハイレベルである場合にコード更新信号S0が活性化すると、初期化信号LSET2がローレベルに活性化し、初期化信号LSET3がハイレベルに活性化する。これにより、カウンタ部102のフリップフロップ回路FF2がリセットされ、フリップフロップ回路FF3がセットされることから、カウント値は「000101」から「001001」にジャンプする。十進数で表記すると、カウント値が「5」から「9」へ4ピッチ分カウントアップされたことになる。

【0052】

このように、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップすることになる。後述するように、コード更新信号S0に応答して何ピッチ分ジャンプさせるかは、内部クロック信号ICLKに含まれるジッタ成分に大きさに合わせて選択すればよい。

【0053】

図6は、反転制御部103の回路図である。

【0054】

図6に示すように、反転制御部103は、内部クロック信号DelayCLK及びその反転信号/DelayCLKを受け、いずれか一方を出力するセレクタ回路110を備えている。セレクタ回路110による選択は、SRラッチ回路111の出力ノードQから出力される選択信号SELに基づいて行われる。セレクタ回路110は、選択信号SELがローレベルであれば反転されていない内部クロック信号DelayCLKを選択し、選択信号SELがハイレベルであれば反転された内部クロック信号/DelayCLKを選択する。

【0055】

SRラッチ回路111のセットノードSには、位相判定信号PD及び反転制御信号INVの論理積が入力され、リセットノードRには、カウンタリセット信号CRが入力される。かかる構成により、カウンタリセット信号CRが活性化した初期状態においては、反転されていない内部クロック信号DelayCLKが選択され、その後、反転制御信号INVがハイレベルに活性化したタイミングで位相判定信号PDの論理レベルがハイレベルであれば、SRラッチ回路111がセットされ、反転された内部クロック信号/DelayCLKが選択されることになる。

【0056】

以上がDLL回路100の具体的な回路構成である。次に、DLL回路100の動作について説明する。

【0057】

図7は、DLL回路100の動作を説明するためのタイミング図である。

【0058】

図7に示すように、外部からDLLリセットコマンドが発行され、これによりDLLリセット信号DLLRSTが活性化すると、DLLタイミング制御部107は、カウンタリセット信号CR、反転制御信号INV、コード更新信号S0及びカウンタ更新信号S1をこの順に活性化させる。これら信号を活性化させる間隔については任意であるが、カウント値の変化が内部クロック信号RCLKに正しく反映される時間を確保する必要がある。一例として、図7に示す期間T1〜T3は、いずれもカウンタ更新信号S1の活性化周期である期間T4以上であることが望ましい。

【0059】

まず、カウンタリセット信号CRが活性化すると、カウンタ部102のカウント値が第1の初期値である「000101」、つまり十進数で「5」にリセットされる。これにより、ディレイライン101の遅延量は、当該カウント値に応じた遅延を内部クロック信号ICLKに与え、これを内部クロック信号DelayCLKとして出力する。

【0060】

カウンタリセット信号CRの活性化から期間T1が経過すると、反転制御信号INVが活性化する。このタイミングで位相判定信号PDの論理レベルがローレベルであれば、SRラッチ回路111はセットされないため、反転されない内部クロック信号DelayCLKが選択され、これが内部クロック信号LCLKとして出力される。一方、このタイミングで位相判定信号PDの論理レベルがハイレベルであれば、SRラッチ回路111がセットされるため、反転された内部クロック信号/DelayCLKが選択され、これが内部クロック信号LCLKとして出力される。反転された内部クロック信号/DelayCLKを用いる意義については後述する。

【0061】

反転制御信号INVの活性化から期間T2が経過すると、コード更新信号S0が活性化する。これにより、カウンタ部102のカウント値は、第1の初期値から第2の初期値にジャンプする。第2の初期値の具体的な値については既に説明した通りである。図7に示す例では、カウント値が「000101」から「000111」へ2ピッチ分カウントアップされた例が示されている。

【0062】

コード更新信号S0の活性化から期間T3が経過すると、カウンタ更新信号S1が活性化する。カウンタ更新信号S1が活性化すると、図4を用いて説明したように、位相判定信号PDの論理レベルに基づいて、カウンタ部102のカウント値が1ピッチ分だけカウントアップ又はカウントダウンされる。これは、内部クロック信号RCLKの位相を内部クロック信号ICLKの位相により近づけるための動作である。図7に示す例では、カウント値が「000111」から「001000」へカウントアップされた例が示されている。

【0063】

その後は、期間T4ごとにカウンタ更新信号S1が周期的に活性化し、その都度、カウンタ部102のカウント値がカウントアップ又はカウントダウンされる。このような動作を繰り返すことにより、内部クロック信号RCLKの位相が内部クロック信号ICLKの位相とほぼ一致した状態となり、一致した後は、その状態が保たれる。つまり、DLL回路100がロックした状態となる。

【0064】

図8は、反転制御部103によって内部クロック信号の反転信号/DelayCLKが選択されるケースを説明するためのタイミング図であり、カウンタ部102のカウント値が第1の初期値に設定されている場合の位相を示している。

【0065】

図8において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)は反転された内部クロック信号/DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(d)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0066】

図8に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合、反転制御信号INVの活性化タイミングにおいて位相判定信号PDがハイレベルとなる。これに基づき、反転された内部クロック信号/DelayCLKが選択されることから内部クロック信号RCLKの波形は(c)の波形に反転する。つまり、内部クロック信号RCLKの立ち上がりエッジR2が1/2周期分移動することから、内部クロック信号ICLKの目標とする立ち上がりエッジR0までの位相差が減少する。

【0067】

ここで、反転された内部クロック信号/DelayCLKを使用せず、反転されていない内部クロック信号DelayCLKを内部クロック信号LCLKとして使用すると、(b)に示すように、一つ前の立ち上がりエッジRXを目標エッジとしてDLL回路100が動作してしまう。つまり、反転されていない内部クロック信号DelayCLKを使用すると、位相判定信号PDがハイレベルであるために、カウンタ部102はカウントダウンを進める必要がある。これを許容するためには、カウンタ部102の第1の初期値を中心値近傍に設定するとともに、カウント可能な数を本実施形態の約2倍に設計する必要があるが、この場合、カウンタ部102及びディレイライン101の回路規模が大きくなってしまう。これを避けるため、本実施形態ではカウンタ部102の第1の初期値をオフセットさせるとともに、カウント可能な数を少なく設計している。このため、第1の初期値からカウントダウンを何度も繰り返すことはできないが、本実施形態では、図8に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合には、反転された内部クロック信号/DelayCLKを内部クロック信号LCLKとして用いていることから、上記の問題が回避される。

【0068】

さらに、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされることから、図8の(d)に示すように、内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0により近くなる。これにより、その後カウンタ更新信号S1に同期して何回かのカウントアップ(場合によっては少数のカウントダウン)を行うことにより、DLL回路100をロックさせることが可能となる。

【0069】

図9は、反転制御部103によって内部クロック信号DelayCLKが選択されるケースを説明するためのタイミング図であり、カウンタ部102のカウント値が第1の初期値に設定されている場合の位相を示している。

【0070】

図9において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0071】

図9に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのローレベルの期間Bに現れる場合、反転制御信号INVの活性化タイミングにおいて位相判定信号PDがローレベルとなる。これに基づき、反転されない内部クロック信号DelayCLKが選択される。これにより、内部クロック信号ICLKの立ち上がりエッジR0を目標とした制御が行われる。

【0072】

さらに、コード更新信号S0が活性化すると、カウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされることから、図9に示すように、内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0により近くなる。これにより、その後カウンタ更新信号S1に同期して何回かのカウントアップ(場合によっては少数のカウントダウン)を行うことにより、DLL回路100をロックさせることが可能となる。

【0073】

このように、本実施形態では、初期状態における位相がいずれの状態であっても、カウンタ部102を主にカウントアップすることによってDLL回路100がロックする。このため、カウンタ部102のカウント値が第1の初期値から繰り返しカウントダウンされる状態を想定する必要が無くなることから、カウンタ部102及びディレイライン101の回路規模を小さく設計することが可能となる。

【0074】

図10は、ジッタの影響により反転されていない内部クロック信号DelayCLKが誤って選択されたケースを説明するためのタイミング図であり、図8に対応している。図10において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0075】

図10に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのハイレベルの期間Aに現れる場合、本来であれば、図8を用いて説明したように、反転された内部クロック信号/DelayCLKが選択される。しかしながら、ジッタの影響により、反転制御信号INVが活性化するタイミングにおいて、内部クロック信号RCLKの立ち上がりエッジR1が内部クロック信号ICLKのローレベルの期間Bに偶然現れた場合、反転されない内部クロック信号DelayCLKが選択されることになる。このようにジッタの影響によって反転制御部103の動作が失敗した場合、内部クロック信号ICLKの一つ前の立ち上がりエッジRXを目標として位相制御動作が進行しようとする。

【0076】

しかしながら、本実施形態では、反転制御信号INVが活性化した後、コード更新信号S0が活性化し、これによってカウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされる。このため、図10に示すように、(c)に示すジャンプ後の内部クロック信号RCLKは、その立ち上がりエッジR3が内部クロック信号ICLKのローレベルの期間Bまで移動するため、内部クロック信号ICLKの立ち上がりエッジR0を目標としてカウンタ部102のカウントアップが行われることになる。これにより、内部クロック信号ICLKの一つ前の立ち上がりエッジRXを目標としてカウントダウンを繰り返すことによるカウンタ部102のスタックを防止することができる。

【0077】

したがって、コード更新信号S0に応答したカウント値のジャンプ量は、想定されるジッタを考慮して選択すればよい。つまり、内部クロック信号ICLKに含まれるジッタ成分に対応するカウント値の差よりも大きいジャンプ量となるよう、設定信号SET1,SET2を選択すればよい。実際には、想定されるジッタが十分に小さい場合にはジャンプ量を1ピッチとしても構わないが、ジッタの影響を確実に排除するためには、2ピッチ以上のジャンプ量に設定することが望ましい。

【0078】

図11は、ジッタの影響により反転された内部クロック信号/DelayCLKが誤って選択されたケースを説明するためのタイミング図であり、図9に対応している。図11において、(a)は内部クロック信号ICLKの波形を示し、(b)は内部クロック信号DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(c)は反転された内部クロック信号/DelayCLKに基づき生成された内部クロック信号RCLKの波形を示し、(d)はジャンプ後の内部クロック信号RCLKの波形を示している。

【0079】

図11に示すように、(b)に示す内部クロック信号RCLKの立ち上がりエッジR1が(a)に示す内部クロック信号ICLKのローレベルの期間Bに現れる場合、本来であれば、図9を用いて説明したように、反転されない内部クロック信号DelayCLKが選択される。しかしながら、ジッタの影響により、反転制御信号INVが活性化するタイミングにおいて、内部クロック信号RCLKの立ち上がりエッジR1が内部クロック信号ICLKのハイレベルの期間Aに偶然現れた場合、反転された内部クロック信号/DelayCLKが選択されることになる。これにより、内部クロック信号RCLKの波形は、(c)のように反転する。その後、コード更新信号S0が活性化し、(d)に示すようにカウンタ部102のカウント値が1ピッチ〜4ピッチ分だけ強制的にカウントアップされる。

【0080】

その結果、ジャンプ後の内部クロック信号RCLKは、その立ち上がりエッジR3が内部クロック信号ICLKのハイレベルの期間Aに位置することになるが、ジッタの影響による誤判定は、内部クロック信号ICLKの立ち下がりエッジF0と内部クロック信号RCLKの立ち上がりエッジR1が近接している場合に限られる。このため、ジャンプ後における内部クロック信号RCLKの立ち上がりエッジR3は、内部クロック信号ICLKの目標とする立ち上がりエッジR0に対して位相が僅かに遅れているに過ぎない。このため、僅かな数のカウントダウンによってDLL回路100をロックすることができ、したがってカウンタ部102がスタックすることはない。

【0081】

図12は、DLL回路100がロックする過程を説明するための模式的なタイミング図である。

【0082】

図12に示す例では、カウンタリセット信号CRの活性化によって、カウンタ部102のカウント値が第1の初期値である「000101」にリセットされると、内部クロック信号RCLKの位相が内部クロック信号ICLKの位相よりも進んだ状態となっている。次に、コード更新信号S0の活性化によって、カウンタ部102のカウント値が第1の初期値である「000101」から第2の初期値である「001000」に2ピッチジャンプしている。その後、周期的に活性化するカウンタ更新信号S1に応答してカウント値が「001001」、「0001010」にカウントアップされ、次に、「001001」にカウントダウンされている。カウント値がこのような変化パターンを示した状態がDLL回路100のロック状態であり、内部クロック信号RCLKの位相は内部クロック信号ICLKの位相にほぼ一致したまま追従する。

【0083】

以上説明したように、本実施形態によれば、反転制御部103を用いて内部クロック信号DelayCLK又は反転された内部クロック信号/DelayCLKを選択していることから、カウンタ部102及びディレイライン101の回路規模を従来に比べて縮小することができる。しかも、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントアップしていることから、ジッタの影響によって反転制御部103が誤った選択を行った場合であっても、カウンタ部102がスタックすることが無く、DLL回路100を正しくロックさせることが可能となる。

【0084】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0085】

例えば、上記実施形態では、第1の初期値を最小値近傍の値とし、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントアップしているが、これとは逆に、第1の初期値を最大値近傍の値とし、反転制御部103による選択を行った後、カウンタ部102のカウント値を強制的にカウントダウンしても構わない。

【符号の説明】

【0086】

10 半導体装置

11 メモリセルアレイ

12 ロウデコーダ

13 カラムデコーダ

14 モードレジスタ

15 FIFO回路

16 入出力回路

16a 出力回路

21 アドレス端子

22 コマンド端子

23 クロック端子

24 データ端子

25 電源端子

31 アドレス入力回路

32 アドレスラッチ回路

33 コマンド入力回路

34 コマンドデコード回路

35 リフレッシュ制御回路

36 クロック入力回路

37 タイミングジェネレータ

38 内部電源発生回路

39 ヒューズ回路

100 DLL回路

101 ディレイライン

102 カウンタ部

103 反転制御部

104 レプリカ出力部

105 位相比較部

106 コード部

107 タイミング制御部

110 セレクタ回路

111 SRラッチ回路

ICLK 内部クロック信号(第1のクロック信号)

DelayCLK 内部クロック信号(第2のクロック信号)

/DelayCLK 内部クロック信号(反転された第2のクロック信号)

LCLK 内部クロック信号(第3のクロック信号)

RCLK 内部クロック信号(第4のクロック信号)

Bit0〜Bit5 カウント値

CR カウンタリセット信号

INV 反転制御信号

S0 コード更新信号

S1 カウンタ更新信号

【特許請求の範囲】

【請求項1】

カウント値を生成するカウンタ部と、

前記カウント値に応じて第1のクロック信号を遅延させることにより第2のクロック信号を生成するディレイラインと、

前記第2のクロック信号を受け、その位相を反転させたクロック信号又は反転させないクロック信号のいずれか一方のクロック信号を選択して第3のクロック信号として出力する反転制御部と、

前記第3のクロック信号に基づいて第4のクロック信号を生成するレプリカ出力部と、

前記第1のクロック信号と前記第4のクロック信号の位相を比較することによって位相判定信号を生成する位相比較部と、

リセット信号、反転制御信号、コード更新信号及びカウンタ更新信号を活性化させる制御部と、を備え、

前記リセット信号に応答して、前記カウンタ部のカウント値は第1の初期値にリセットされ、且つ、前記反転制御部は前記反転させないクロック信号を選択するようにセットされ、

前記反転制御部は、前記反転制御信号が活性化した際における前記位相判定信号の論理レベルに基づいて前記いずれか一方のクロック信号を選択し、

前記カウンタ部のカウント値は、前記反転制御部が選択した後に前記コード更新信号に応答して前記第1の初期値から第2の初期値に更新され、

前記カウンタ部のカウント値は、前記カウンタ更新信号が活性化した際の前記位相判定信号の論理レベルに基づいて前記第2の初期値からアップカウント又はダウンカウントされる、ことを特徴とする半導体装置。

【請求項2】

前記第1の初期値に対応する位相と前記第2の初期値に対応する位相との間の位相差は、前記カウンタ更新信号の活性化に応答した前記カウンタ部のカウントピッチに対応する位相よりも大きいことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の初期値に対応する位相と前記第2の初期値に対応する位相との間の位相差は、前記第1のクロック信号に含まれるジッタ量よりも大きいことを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第1の初期値は、前記カウント値の中心値からオフセットしていることを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記第2の初期値は前記カウント値の中心値からオフセットしており、前記第2のカウント値のオフセット量は前記第1のカウント値のオフセット量よりも小さいことを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第2の初期値は設定信号によって可変であることを特徴とする請求項1乃至5のいずれか一項に記載の半導体装置。

【請求項7】

前記設定信号を不揮発的に記憶する不揮発性記憶回路をさらに備えることを特徴とする請求項6に記載の半導体装置。

【請求項8】

DLL回路に含まれるカウンタ回路のカウント値を第1の初期値にリセットして第1のクロック信号を前記第1の初期値に対応して遅延させた第2のクロック信号を出力し、

前記第1のクロック信号の位相及び前記第2のクロック信号の位相を互いに比較し、

前記比較の結果に応じて前記第2のクロック信号の位相を反転する制御及び反転しない制御の一方を行い、

前記制御の後に、前記カウント値を前記第1の初期値から第2の初期値に更新し、

前記更新の後に、前記第1のクロック信号の位相及び前記第2の初期値に対応する前記第2のクロック信号の位相を互いに比較し、比較結果に応じて前記カウント値を前記第2の初期値からアップカウント又はダウンカウントして前記第2のクロック信号の遅延量を調整する半導体装置の制御方法。

【請求項1】

カウント値を生成するカウンタ部と、

前記カウント値に応じて第1のクロック信号を遅延させることにより第2のクロック信号を生成するディレイラインと、

前記第2のクロック信号を受け、その位相を反転させたクロック信号又は反転させないクロック信号のいずれか一方のクロック信号を選択して第3のクロック信号として出力する反転制御部と、

前記第3のクロック信号に基づいて第4のクロック信号を生成するレプリカ出力部と、

前記第1のクロック信号と前記第4のクロック信号の位相を比較することによって位相判定信号を生成する位相比較部と、

リセット信号、反転制御信号、コード更新信号及びカウンタ更新信号を活性化させる制御部と、を備え、

前記リセット信号に応答して、前記カウンタ部のカウント値は第1の初期値にリセットされ、且つ、前記反転制御部は前記反転させないクロック信号を選択するようにセットされ、

前記反転制御部は、前記反転制御信号が活性化した際における前記位相判定信号の論理レベルに基づいて前記いずれか一方のクロック信号を選択し、

前記カウンタ部のカウント値は、前記反転制御部が選択した後に前記コード更新信号に応答して前記第1の初期値から第2の初期値に更新され、

前記カウンタ部のカウント値は、前記カウンタ更新信号が活性化した際の前記位相判定信号の論理レベルに基づいて前記第2の初期値からアップカウント又はダウンカウントされる、ことを特徴とする半導体装置。

【請求項2】

前記第1の初期値に対応する位相と前記第2の初期値に対応する位相との間の位相差は、前記カウンタ更新信号の活性化に応答した前記カウンタ部のカウントピッチに対応する位相よりも大きいことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の初期値に対応する位相と前記第2の初期値に対応する位相との間の位相差は、前記第1のクロック信号に含まれるジッタ量よりも大きいことを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第1の初期値は、前記カウント値の中心値からオフセットしていることを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記第2の初期値は前記カウント値の中心値からオフセットしており、前記第2のカウント値のオフセット量は前記第1のカウント値のオフセット量よりも小さいことを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第2の初期値は設定信号によって可変であることを特徴とする請求項1乃至5のいずれか一項に記載の半導体装置。

【請求項7】

前記設定信号を不揮発的に記憶する不揮発性記憶回路をさらに備えることを特徴とする請求項6に記載の半導体装置。

【請求項8】

DLL回路に含まれるカウンタ回路のカウント値を第1の初期値にリセットして第1のクロック信号を前記第1の初期値に対応して遅延させた第2のクロック信号を出力し、

前記第1のクロック信号の位相及び前記第2のクロック信号の位相を互いに比較し、

前記比較の結果に応じて前記第2のクロック信号の位相を反転する制御及び反転しない制御の一方を行い、

前記制御の後に、前記カウント値を前記第1の初期値から第2の初期値に更新し、

前記更新の後に、前記第1のクロック信号の位相及び前記第2の初期値に対応する前記第2のクロック信号の位相を互いに比較し、比較結果に応じて前記カウント値を前記第2の初期値からアップカウント又はダウンカウントして前記第2のクロック信号の遅延量を調整する半導体装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−21396(P2013−21396A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−150859(P2011−150859)

【出願日】平成23年7月7日(2011.7.7)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月7日(2011.7.7)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]