半導体装置及びその製造方法、集積回路、電気光学装置、電子機器

【課題】 薄膜トランジスタ等の半導体装置において半導体膜のエッジ部分における電界集中を回避して信頼性を向上させることを可能とする技術を提供すること。

【解決手段】 本発明の半導体装置の製造方法は、絶縁基板(10,11)の上に半導体膜(12)を島状に形成する第1の工程と、半導体膜(12)のエッジ部を含んで半導体膜(12)を第1の絶縁膜(13)で覆う第2の工程と、半導体膜(12)上部の第1の絶縁膜(13)を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも絶縁膜(13)の開口部の半導体膜(12)上に第1の絶縁膜(13)よりも相対的に薄い厚さの第2の絶縁膜(14)を形成する第4の工程と、第2の絶縁膜(14)上に電極配線膜(18)を形成する第5の工程と、を含む。

【解決手段】 本発明の半導体装置の製造方法は、絶縁基板(10,11)の上に半導体膜(12)を島状に形成する第1の工程と、半導体膜(12)のエッジ部を含んで半導体膜(12)を第1の絶縁膜(13)で覆う第2の工程と、半導体膜(12)上部の第1の絶縁膜(13)を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも絶縁膜(13)の開口部の半導体膜(12)上に第1の絶縁膜(13)よりも相対的に薄い厚さの第2の絶縁膜(14)を形成する第4の工程と、第2の絶縁膜(14)上に電極配線膜(18)を形成する第5の工程と、を含む。

【発明の詳細な説明】

【背景技術】

【0001】

近年、低温プロセスによって形成された結晶性半導体膜(例えば、多結晶シリコン膜)を用いて、電流駆動能力の高い薄膜トランジスタを形成する技術の研究、開発が進められている。一般に、多結晶シリコン膜は非晶質シリコン膜に対してレーザ照射を行って結晶化することにより形成される。ところが、このようにして形成される多結晶シリコン膜は、結晶化の際に各所で成長した結晶粒同士の境界(粒界)が隆起して突起状となり、表面の凹凸が大きくなる傾向にある。この多結晶シリコン膜の上側にゲート絶縁膜及びゲート電極を形成した電界効果型の薄膜トランジスタ(TFT)では、多結晶シリコン膜の表面の突起部分に電界が集中してゲート絶縁膜の絶縁破壊を生じやすい。このような問題に対して、特開2000−40828号公報(特許文献1)には、多結晶シリコン膜を成膜した後にその表面を研磨して平坦化することにより、薄膜トランジスタにおけるゲート絶縁膜の絶縁破壊を回避する技術が開示されている。

【0002】

ところで、薄膜トランジスタの微細化を進めるためにゲート絶縁膜の膜厚をより薄くした場合には、半導体膜のエッジ部分におけるゲート絶縁膜が薄くなりやすい。特に、スパッタ法やCVD法などの段差被覆性(ステップカバレッジ)が低い成膜法を用いてゲート絶縁膜を形成する場合にこの傾向が顕著となる。かかるエッジ部分を横切るようにゲート電極が形成されるとその部分で電界集中が生じ、絶縁破壊に至ることが多くなる。これにより、薄膜トランジスタの信頼性が低下するという不都合が生じる。上述した従来技術では、このような半導体膜のエッジ部分における電界集中の緩和を達成することは難しく、更なる改良技術が望まれていた。

【特許文献1】特開2000−40828号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

そこで、本発明は、薄膜トランジスタ等の半導体装置において半導体膜のエッジ部分におけるゲート絶縁膜の絶縁破壊やリークの発生を回避して半導体装置の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0004】

上記目的を達成するため本発明の半導体装置の製造方法は、絶縁基板の上に半導体膜を島状に形成する第1の工程と、上記半導体膜のエッジ部を含んで上記半導体膜を第1の絶縁膜で覆う第2の工程と、上記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも上記絶縁膜の開口部の半導体膜上に上記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、上記第2の絶縁膜上に電極配線膜を形成する第5の工程と、を含む。

【0005】

かかる製造工程によって半導体装置を製造することによって、ゲート絶縁膜中に電界が集中する部分をなくすことができ、ゲート絶縁膜の信頼性を向上することが可能となる。

【0006】

好ましくは、上記第1の工程は、上記絶縁基板に上記半導体膜を形成する工程と、熱処理によって上記半導体膜を多結晶化させる工程と、上記多結晶化した半導体の表面を平坦化する工程と、上記多結晶化した半導体膜を素子形成領域にパターニングする工程と、を含む。それにより、表面が平坦な多結晶性半導体膜を得ることが出来、該半導体膜表面の凹凸によってゲート絶縁膜中に電界が集中する部分が生ずることを回避することが出来る。

【0007】

好ましくは、上記第4の工程は、上記半導体膜上面の熱酸化によって上記第2の絶縁膜を形成する工程である。それにより、薄く絶縁性に優れたゲート絶縁膜を得ることが出来る。

【0008】

好ましくは、上記第4の工程は、上記半導体膜上に絶縁材料を堆積(成膜)させて上記第2の絶縁膜を形成する工程である。それにより、半導体膜の膜厚を減らすことなく、該半導体膜上にゲート絶縁膜を形成することが出来る。

【0009】

また、本発明の半導体装置は、絶縁基板上に島状に形成された半導体膜と、上記絶縁基板上に、上記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、少なくとも上記領域分離絶縁膜の開口部の上記半導体膜上面に上記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と、上記ゲート絶縁膜上に形成されるゲート電極と、を備える。

【0010】

かかる構成とすることによって、ゲート絶縁膜中に電界が集中する部分をなくしてゲート絶縁膜の信頼性を向上した半導体装置を得ることが出来る。

【0011】

好ましくは、上記ゲート絶縁膜は、上記半導体膜上面に該半導体膜のエッジ部から離れて形成されている。それにより、ゲート絶縁膜中に強電界となる部分が生じることを回避する。

【0012】

好ましくは、上記領域分離絶縁膜は、少なくとも上記ゲート絶縁膜の厚さの2倍以上の厚さに形成される。それにより、領域分離絶縁膜に十分な絶縁性を確保することが出来る。

【0013】

また、本発明の集積回路、電気光学装置及び電子機器は、上述した構成の半導体装置を備える。

【発明の効果】

【0014】

本発明によれば、ゲート絶縁膜は半導体膜のエッジ部を避けて形成されるので局所的な電界集中によるゲート絶縁膜の破壊が防止される。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施の形態について説明する。

【実施例1】

【0016】

図1は、本発明の実施形態の半導体装置としての薄膜トランジスタの構造を説明する平面図である。図2は、図1に示す薄膜トランジスタの同図中のII−II線方向(チャネル幅方向)における薄膜トランジスタの断面図である。両図において対応する部分には同一符号を付している。薄膜トランジスタは、後述のように、有機EL表示装置や液晶表示装置などの画素駆動素子等として用いられるものである。

【0017】

図1及び図2に示すように、薄膜トランジスタ1は、半導体膜、絶縁膜及び電極を積層した構造(MOS構造)を用いる電界効果型トランジスタであり、基板10上に絶縁膜11が形成された絶縁基板、島状に形成された半導体膜12、半導体膜を隔離する絶縁膜(第1の絶縁膜)13、ゲート絶縁膜(第2の絶縁膜)14、ゲート電極18、ソース電極20、ドレイン電極22、絶縁膜(保護膜)24を含んで構成されている。

【0018】

基板10は、例えば、ガラス、水晶ガラス、プラスチックなどの基板である。絶縁膜11は酸化シリコン膜や窒化シリコン膜などの下地絶縁膜である。絶縁膜11は半導体膜12の電気的絶縁と基板10から半導体膜12に不純物が侵入することを防止する。

【0019】

半導体膜12は、薄膜トランジスタの活性領域を担うものであり、結晶性半導体膜が用いられる。本実施形態では、半導体膜12として多結晶シリコン膜(ポリシリコン膜)を用いている。

【0020】

絶縁膜13は、基板10上に島状に形成されている島状の半導体膜12の周囲を囲む共もに図示しない他の半導体膜から半導体膜12を絶縁し、素子領域分離を行っている。また、絶縁膜13は当該半導体膜12のエッジ部12aを覆い、エッジ部12aの上面を露出(開口)するように形成されている。この絶縁膜13は、半導体膜12とほぼ同じ膜厚に形成されている。絶縁膜13としては、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが好適に用いられる。当該絶縁膜13は、比較的に厚膜に形成する必要がある反面、ゲート絶縁膜14ほどには絶縁耐圧、固定電荷密度等の特性を要求されないことから、高速成膜に適した製造条件を採用して形成することができる。

【0021】

ゲート絶縁膜14は、絶縁膜13の開口部に露出した半導体膜12上面を覆うようにして形成されている。この実施例では、プラズマ雰囲気下で露出した半導体膜12を酸化させて酸化シリコンの絶縁膜を形成し、ゲート絶縁膜14としている。ゲート絶縁膜16として、例えば、シリコン窒化物(Si3N4)膜等を形成しても良い。ゲート絶縁膜16は、厚膜に形成する必要性は少ないが、絶縁耐圧、固定電荷密度等について高い特性を要求されることから、より良好な膜質が得られる製造条件(一般には低速成膜)を採用して形成される。後述のように、ゲート絶縁膜14をCVDのような堆積プロセスによって行っても良い。

【0022】

ゲート絶縁膜14は、半導体膜12のエッジ部12aから離間しているのでエッジ部12a近傍の局所的な高電界の影響を受け難くなり、絶縁破壊が回避される。

【0023】

ゲート電極18は、絶縁膜13及びゲート絶縁膜14の上側であって、半導体膜12の所定位置の上側を通るように形成されている。より詳細には、ゲート電極18は、図1に示すように半導体膜12の平行な二辺を横切るように形成されている。このゲート電極18は、例えば、タンタル、クロム、アルミニウム等の導電体膜からなる。

【0024】

ソース電極20及びドレイン電極22は、それぞれともに、絶縁膜24を貫通して半導体膜12に接続されている。これらのソース電極20等は、例えば、アルミニウム等の導電体膜からなる。

【0025】

絶縁膜24は、ゲート電極18及び絶縁膜18等の上面を覆うようにして形成されている。この絶縁膜24は保護膜としての役割を担っており、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが用いられる。

【実施例2】

【0026】

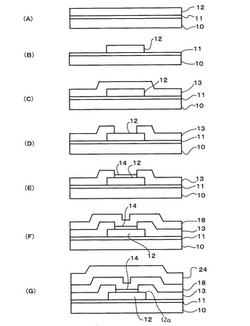

次に、上述した半導体装置の製造方法を図3に示す工程図を参照して説明する。

【0027】

(半導体膜形成)

まず、図3(A)に示すように、ガラス基板10上にプラズマCVD法等によって酸化シリコン(SiO2)の絶縁膜11を形成する。

【0028】

この上に、PECVD法、LPCVD法、常圧化学気相堆積法(APCVD法)、スパッタリング法などの成膜法によって半導体膜12として非晶質シリコン膜を成膜する。この非晶質シリコン膜に対してエキシマレーザ等を照射する処理(レーザアニール処理)を行うことにより、非晶質シリコン膜を多結晶シリコン膜に変換する。このとき、レーザ照射による結晶化処理を行って得られる多結晶シリコン膜の表面には、各結晶粒の境界(粒界)が隆起することによる凹凸30が生じることが多い。

【0029】

そこで、好ましくは、半導体膜12の表面の凹凸が平坦化されるまで半導体膜12を研磨する。本実施形態では、CMP法(化学的機械的研磨法)を採用して本工程を行う。CMP法による研磨の好適な条件としては、例えば、軟質ポリウレタン製のパッドと、アンモニア系又はアミン系のアルカリ溶液にシリカ粒子を分散させた研磨剤(スラリー)を組み合わせて用い、圧力30000Pa、回転数50回転/分、研磨剤の流量を200sccm、という条件を採用できる。

【0030】

次に、図3(B)に示すように、平坦化した半導体膜12にフォトレジスト塗布、パターン露光、現像、エッチング処理などからなるパターン形成処理(パターニング)を行うことにより、基板10上の予め定められた素子形成領域に多結晶シリコン膜からなる島状の半導体膜12を形成する。

【0031】

(第1の絶縁膜形成)

図3(C)に示すように、絶縁膜11及び半導体膜12上に素子分離の絶縁膜13を形成する。絶縁膜13は、例えば、PECVD法等によって酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などを形成することによって得られる。絶縁膜13は半導体膜12のエッジ部で後述の工程のゲート絶縁膜14よりも十分厚くなるように形成される。例えば、ゲート絶縁膜14の膜厚の2倍以上の膜厚となるように形成される。

【0032】

(第1の絶縁膜の開口)

図3(D)に示すように、絶縁膜13にパターニングを施し、半導体膜12のエッジ部を除く半導体膜上面を開口する。

【0033】

(第2の絶縁膜形成)

図3(E)に示すように、絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられ、薄くて高耐圧であることが必要である。絶縁膜14は、例えば、酸素を含むプラズマ雰囲気下で半導体膜12である多結晶シリコン膜の表面を熱酸化させることによって得られる。これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0034】

(電極膜形成)

図3(F)に示すように、絶縁膜13及びゲート絶縁膜14の上にタンタル、アルミニウム等の金属薄膜をスパッタリング法により形成した後、パターニングすることによって、ゲート絶縁膜16上の所定位置にゲート電極及び配線膜18を形成する。

【0035】

(ソース/ドレイン領域形成)

次に、ゲート電極18をマスクとして半導体膜12に対してドナーまたはアクセプターとなる不純物イオンを打ち込む。これにより、ゲート電極18の下側にチャネル形成領域が形成され、それ以外の部分(イオン注入がされた部分)にソース/ドレイン領域が形成される。更に熱処理を施して不純物元素の活性化を行う。

【0036】

(保護膜形成)

図3(G)に示すように、ゲート電極膜18及び絶縁膜13上に保護膜として絶縁膜24を形成する。絶縁膜24として、例えば、PECVD法で約500nmの酸化シリコン膜を形成する。

【0037】

(ソース・ドレイン電極配線形成)

更に、絶縁膜24を貫通し、半導体膜12のソース/ドレイン領域に至るコンタクトホール20、22を形成する。コンタクトホール20及び22は絶縁膜24上にコンタクトホール部を開口するマスクを形成し、絶縁膜24に異方性エッチングを行うことによって形成される。更に、当該コンタクトホール内及び絶縁膜24上にスパッタリング法によりアルミニウムを堆積し、パターニングすることにより、ソース電極20、ドレイン電極22及び接続配線を形成する。

【0038】

このように、本発明の実施の形態では、ゲート絶縁膜が半導体膜のエッジ部分あるいは段差部分に形成されないようにしたので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が段差部分を被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例3】

【0039】

本発明の半導体装置の製造方法の他の実施の形態について図4を参照して説明する。同図において図3と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0040】

この実施例においては、ゲート絶縁膜14の形成を堆積プロセスによって行っている。この実施例においても、まず、図4(A)乃至同図(D)に示すように、基板10上への半導体膜12の形成から絶縁膜13の開口までの工程を行う。これは前述した図3(A)乃至同図(D)に示した工程(半導体膜形成〜第2の絶縁膜形成)と同じであるのでその説明を省略する。

【0041】

続いて、図4(E)に示すように、絶縁膜13及び絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられるので薄くて高耐圧であることが必要である。絶縁膜14は、PECVD法等の堆積プロセスによって酸化シリコン膜からなるゲート絶縁膜16を形成する。例えば、原料ガスとしてテトラエトキシシラン(TEOS)及び酸素(O2)を用い、それぞれの流量を50sccm、5slmとし、雰囲気温度を350℃、RFパワーを1.3kW、圧力を200Paという条件にして酸化シリコン膜を成膜する。この場合には、成膜速度が30nm/min程度となり、ゲート絶縁膜に適した耐圧特性等を備える良好な酸化シリコン膜を得ることができる。

【0042】

これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0043】

次に、図4(F)及び同図(G)に示すように、既述した図3(F)及び同図(G)と同様の工程を行って、電極膜形成、ソース/ドレイン領域形成、保護膜形成、ソース・ドレイン電極配線形成を行って薄膜半導体を完成させる。

【0044】

このように、本発明の半導体装置の製造方法の第2の実施の形態においても、ゲート絶縁膜が半導体膜のエッジ部分12aに形成されないので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が半導体膜のエッジを被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例4】

【0045】

次に、上述した半導体装置を含んで構成される集積回路、電気光学装置、電子機器の具体例について説明する。

【0046】

図5は、半導体装置を含んで構成される電気光学装置100の回路図である。本実施形態の電気光学装置(表示装置)100は、各画素領域に電界発光効果により発光可能な発光層OELD、それを駆動するための電流を記憶する保持容量を備え、さらに本発明にかかる半導体装置(薄膜トランジスタT1〜T4)を備えて構成されている。ドライバ101からは、走査線Vsel及び発光制御線Vgpが各画素領域に供給されている。ドライバ102からは、データ線Idataおよび電源線Vddが各画素領域に供給されている。走査線Vselとデータ線Idataとを制御することにより、各画素領域に対する電流プログラムが行われ、発光部OELDによる発光が制御可能になっている。

【0047】

なお、上記駆動回路は、発光要素に電界発光素子を使用する場合の回路の一例であり他の回路構成も可能である。また、ドライバ101、102のそれぞれを構成する集積回路を本発明に係る半導体装置によって形成することも好適である。

【0048】

図6は、上述した電気光学装置を含んで構成される電子機器の具体例を説明する図である。図6(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明に係る電気光学装置は表示部として利用可能である。図6(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図6(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図6(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。なお、本発明にかかる半導体装置は、電気光学装置の構成部品として上記のような電子機器に含まれる場合の他に、単独で電子機器の構成部品としても適用し得る。

【0049】

また、上記例に限らず本発明にかかる半導体装置の製造方法は、種々の電子機器の製造に適用可能である。例えば、この他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、ICカードなどにも適用することができる。

【0050】

なお、本発明は上述した各実施形態に限定されることなく、本発明の要旨の範囲内で種々の変形実施が可能である。

【0051】

例えば、上述した実施形態では、半導体膜の一例として多結晶シリコン膜を採り上げて説明していたが、半導体膜はこれに限定されるものではなく、他の半導体材料を用いても良い。また、ポリシラザンを有機溶媒に溶かしたもの等の液体材料を用いて半導体膜(シリコン膜)や絶縁膜(酸化シリコン膜)を形成してもよい。

【0052】

また、上述した実施形態では、電界効果型の半導体素子の一例として薄膜トランジスタを採り上げていたが、他にも、単結晶SOI(silicon on insulator)トランジスタにおいて各トランジスタの相互間をエッチング等によって素子分離する構造の半導体装置などに対しても同様にして本発明を適用することが可能である。

【図面の簡単な説明】

【0053】

【図1】本実施形態の薄膜トランジスタの構造を説明する平面図である。

【図2】図1に示す薄膜トランジスタの図中II−II方向(チャネル幅方向)における断面図である。

【図3】薄膜トランジスタの製造方法を説明する図である。

【図4】薄膜トランジスタの他の製造方法を説明する図である。

【図5】半導体装置を含んで構成される電気光学装置の回路図である。

【図6】電子機器の具体例を説明する図である。

【符号の説明】

【0054】

1…薄膜トランジスタ、10…基板、11…下地絶縁膜、12…半導体膜、13…第1の絶縁膜(素子分離膜)、14…第2の絶縁膜(ゲート絶縁膜)、18…ゲート電極膜、20…ソース電極、22…ドレイン電極

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MOSトランジスタ等の電界効果型の半導体装置の改良技術に関する。

【背景技術】

【0002】

近年、低温プロセスによって形成された結晶性半導体膜(例えば、多結晶シリコン膜)を用いて、電流駆動能力の高い薄膜トランジスタを形成する技術の研究、開発が進められている。一般に、多結晶シリコン膜は非晶質シリコン膜に対してレーザ照射を行って結晶化することにより形成される。ところが、このようにして形成される多結晶シリコン膜は、結晶化の際に各所で成長した結晶粒同士の境界(粒界)が隆起して突起状となり、表面の凹凸が大きくなる傾向にある。この多結晶シリコン膜の上側にゲート絶縁膜及びゲート電極を形成した電界効果型の薄膜トランジスタ(TFT)では、多結晶シリコン膜の表面の突起部分に電界が集中してゲート絶縁膜の絶縁破壊を生じやすい。このような問題に対して、特開2000−40828号公報(特許文献1)には、多結晶シリコン膜を成膜した後にその表面を研磨して平坦化することにより、薄膜トランジスタにおけるゲート絶縁膜の絶縁破壊を回避する技術が開示されている。

【0003】

ところで、薄膜トランジスタの微細化を進めるためにゲート絶縁膜の膜厚をより薄くした場合には、半導体膜のエッジ部分におけるゲート絶縁膜が薄くなりやすい。特に、スパッタ法やCVD法などの段差被覆性(ステップカバレッジ)が低い成膜法を用いてゲート絶縁膜を形成する場合にこの傾向が顕著となる。かかるエッジ部分を横切るようにゲート電極が形成されるとその部分で電界集中が生じ、絶縁破壊に至ることが多くなる。これにより、薄膜トランジスタの信頼性が低下するという不都合が生じる。上述した従来技術では、このような半導体膜のエッジ部分における電界集中の緩和を達成することは難しく、更なる改良技術が望まれていた。

【特許文献1】特開2000−40828号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

そこで、本発明は、薄膜トランジスタ等の半導体装置において半導体膜のエッジ部分におけるゲート絶縁膜の絶縁破壊やリークの発生を回避して半導体装置の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するため本発明の半導体装置の製造方法は、絶縁基板の上に半導体膜を島状に形成する第1の工程と、上記半導体膜のエッジ部を含んで上記半導体膜を第1の絶縁膜で覆う第2の工程と、上記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも上記絶縁膜の開口部の半導体膜上に上記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、上記第2の絶縁膜上に電極配線膜を形成する第5の工程と、を含む。

【0006】

かかる製造工程によって半導体装置を製造することによって、ゲート絶縁膜中に電界が集中する部分をなくすことができ、ゲート絶縁膜の信頼性を向上することが可能となる。

【0007】

好ましくは、上記第1の工程は、上記絶縁基板に上記半導体膜を形成する工程と、熱処理によって上記半導体膜を多結晶化させる工程と、上記多結晶化した半導体の表面を平坦化する工程と、上記多結晶化した半導体膜を素子形成領域にパターニングする工程と、を含む。それにより、表面が平坦な多結晶性半導体膜を得ることが出来、該半導体膜表面の凹凸によってゲート絶縁膜中に電界が集中する部分が生ずることを回避することが出来る。

【0008】

好ましくは、上記第4の工程は、上記半導体膜上面の熱酸化によって上記第2の絶縁膜を形成する工程である。それにより、薄く絶縁性に優れたゲート絶縁膜を得ることが出来る。

【0009】

好ましくは、上記第4の工程は、上記半導体膜上に絶縁材料を堆積(成膜)させて上記第2の絶縁膜を形成する工程である。それにより、半導体膜の膜厚を減らすことなく、該半導体膜上にゲート絶縁膜を形成することが出来る。

【0010】

また、本発明の半導体装置は、絶縁基板上に島状に形成された半導体膜と、上記絶縁基板上に、上記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、少なくとも上記領域分離絶縁膜の開口部の上記半導体膜上面に上記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と、上記ゲート絶縁膜上に形成されるゲート電極と、を備える。

【0011】

かかる構成とすることによって、ゲート絶縁膜中に電界が集中する部分をなくしてゲート絶縁膜の信頼性を向上した半導体装置を得ることが出来る。

【0012】

好ましくは、上記ゲート絶縁膜は、上記半導体膜上面に該半導体膜のエッジ部から離れて形成されている。それにより、ゲート絶縁膜中に強電界となる部分が生じることを回避する。

【0013】

好ましくは、上記領域分離絶縁膜は、少なくとも上記ゲート絶縁膜の厚さの2倍以上の厚さに形成される。それにより、領域分離絶縁膜に十分な絶縁性を確保することが出来る。

【0014】

また、本発明の集積回路、電気光学装置及び電子機器は、上述した構成の半導体装置を備える。

【発明の効果】

【0015】

本発明によれば、ゲート絶縁膜は半導体膜のエッジ部を避けて形成されるので局所的な電界集中によるゲート絶縁膜の破壊が防止される。

【発明を実施するための最良の形態】

【0016】

以下、本発明の実施の形態について説明する。

【実施例1】

【0017】

図1は、本発明の実施形態の半導体装置としての薄膜トランジスタの構造を説明する平面図である。図2は、図1に示す薄膜トランジスタの同図中のII−II線方向(チャネル幅方向)における薄膜トランジスタの断面図である。両図において対応する部分には同一符号を付している。薄膜トランジスタは、後述のように、有機EL表示装置や液晶表示装置などの画素駆動素子等として用いられるものである。

【0018】

図1及び図2に示すように、薄膜トランジスタ1は、半導体膜、絶縁膜及び電極を積層した構造(MOS構造)を用いる電界効果型トランジスタであり、基板10上に絶縁膜11が形成された絶縁基板、島状に形成された半導体膜12、半導体膜を隔離する絶縁膜(第1の絶縁膜)13、ゲート絶縁膜(第2の絶縁膜)14、ゲート電極18、ソース電極20、ドレイン電極22、絶縁膜(保護膜)24を含んで構成されている。

【0019】

基板10は、例えば、ガラス、水晶ガラス、プラスチックなどの基板である。絶縁膜11は酸化シリコン膜や窒化シリコン膜などの下地絶縁膜である。絶縁膜11は半導体膜12の電気的絶縁と基板10から半導体膜12に不純物が侵入することを防止する。

【0020】

半導体膜12は、薄膜トランジスタの活性領域を担うものであり、結晶性半導体膜が用いられる。本実施形態では、半導体膜12として多結晶シリコン膜(ポリシリコン膜)を用いている。

【0021】

絶縁膜13は、基板10上に島状に形成されている島状の半導体膜12の周囲を囲む共もに図示しない他の半導体膜から半導体膜12を絶縁し、素子領域分離を行っている。また、絶縁膜13は当該半導体膜12のエッジ部12aを覆い、エッジ部12aの上面を露出(開口)するように形成されている。この絶縁膜13は、半導体膜12とほぼ同じ膜厚に形成されている。絶縁膜13としては、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが好適に用いられる。当該絶縁膜13は、比較的に厚膜に形成する必要がある反面、ゲート絶縁膜14ほどには絶縁耐圧、固定電荷密度等の特性を要求されないことから、高速成膜に適した製造条件を採用して形成することができる。

【0022】

ゲート絶縁膜14は、絶縁膜13の開口部に露出した半導体膜12上面を覆うようにして形成されている。この実施例では、プラズマ雰囲気下で露出した半導体膜12を酸化させて酸化シリコンの絶縁膜を形成し、ゲート絶縁膜14としている。ゲート絶縁膜16として、例えば、シリコン窒化物(Si3N4)膜等を形成しても良い。ゲート絶縁膜16は、厚膜に形成する必要性は少ないが、絶縁耐圧、固定電荷密度等について高い特性を要求されることから、より良好な膜質が得られる製造条件(一般には低速成膜)を採用して形成される。後述のように、ゲート絶縁膜14をCVDのような堆積プロセスによって行っても良い。

【0023】

ゲート絶縁膜14は、半導体膜12のエッジ部12aから離間しているのでエッジ部12a近傍の局所的な高電界の影響を受け難くなり、絶縁破壊が回避される。

【0024】

ゲート電極18は、絶縁膜13及びゲート絶縁膜14の上側であって、半導体膜12の所定位置の上側を通るように形成されている。より詳細には、ゲート電極18は、図1に示すように半導体膜12の平行な二辺を横切るように形成されている。このゲート電極18は、例えば、タンタル、クロム、アルミニウム等の導電体膜からなる。

【0025】

ソース電極20及びドレイン電極22は、それぞれともに、絶縁膜24を貫通して半導体膜12に接続されている。これらのソース電極20等は、例えば、アルミニウム等の導電体膜からなる。

【0026】

絶縁膜24は、ゲート電極18及び絶縁膜18等の上面を覆うようにして形成されている。この絶縁膜24は保護膜としての役割を担っており、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが用いられる。

【実施例2】

【0027】

次に、上述した半導体装置の製造方法を図3に示す工程図を参照して説明する。

【0028】

(半導体膜形成)

まず、図3(A)に示すように、ガラス基板10上にプラズマCVD法等によって酸化シリコン(SiO2)の絶縁膜11を形成する。

【0029】

この上に、PECVD法、LPCVD法、常圧化学気相堆積法(APCVD法)、スパッタリング法などの成膜法によって半導体膜12として非晶質シリコン膜を成膜する。この非晶質シリコン膜に対してエキシマレーザ等を照射する処理(レーザアニール処理)を行うことにより、非晶質シリコン膜を多結晶シリコン膜に変換する。このとき、レーザ照射による結晶化処理を行って得られる多結晶シリコン膜の表面には、各結晶粒の境界(粒界)が隆起することによる凹凸30が生じることが多い。

【0030】

そこで、好ましくは、半導体膜12の表面の凹凸が平坦化されるまで半導体膜12を研磨する。本実施形態では、CMP法(化学的機械的研磨法)を採用して本工程を行う。CMP法による研磨の好適な条件としては、例えば、軟質ポリウレタン製のパッドと、アンモニア系又はアミン系のアルカリ溶液にシリカ粒子を分散させた研磨剤(スラリー)を組み合わせて用い、圧力30000Pa、回転数50回転/分、研磨剤の流量を200sccm、という条件を採用できる。

【0031】

次に、図3(B)に示すように、平坦化した半導体膜12にフォトレジスト塗布、パターン露光、現像、エッチング処理などからなるパターン形成処理(パターニング)を行うことにより、基板10上の予め定められた素子形成領域に多結晶シリコン膜からなる島状の半導体膜12を形成する。

【0032】

(第1の絶縁膜形成)

図3(C)に示すように、絶縁膜11及び半導体膜12上に素子分離の絶縁膜13を形成する。絶縁膜13は、例えば、PECVD法等によって酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などを形成することによって得られる。絶縁膜13は半導体膜12のエッジ部で後述の工程のゲート絶縁膜14よりも十分厚くなるように形成される。例えば、ゲート絶縁膜14の膜厚の2倍以上の膜厚となるように形成される。

【0033】

(第1の絶縁膜の開口)

図3(D)に示すように、絶縁膜13にパターニングを施し、半導体膜12のエッジ部を除く半導体膜上面を開口する。

【0034】

(第2の絶縁膜形成)

図3(E)に示すように、絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられ、薄くて高耐圧であることが必要である。絶縁膜14は、例えば、酸素を含むプラズマ雰囲気下で半導体膜12である多結晶シリコン膜の表面を熱酸化させることによって得られる。これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0035】

(電極膜形成)

図3(F)に示すように、絶縁膜13及びゲート絶縁膜14の上にタンタル、アルミニウム等の金属薄膜をスパッタリング法により形成した後、パターニングすることによって、ゲート絶縁膜16上の所定位置にゲート電極及び配線膜18を形成する。

【0036】

(ソース/ドレイン領域形成)

次に、ゲート電極18をマスクとして半導体膜12に対してドナーまたはアクセプターとなる不純物イオンを打ち込む。これにより、ゲート電極18の下側にチャネル形成領域が形成され、それ以外の部分(イオン注入がされた部分)にソース/ドレイン領域が形成される。更に熱処理を施して不純物元素の活性化を行う。

【0037】

(保護膜形成)

図3(G)に示すように、ゲート電極膜18及び絶縁膜13上に保護膜として絶縁膜24を形成する。絶縁膜24として、例えば、PECVD法で約500nmの酸化シリコン膜を形成する。

【0038】

(ソース・ドレイン電極配線形成)

更に、絶縁膜24を貫通し、半導体膜12のソース/ドレイン領域に至るコンタクトホール20、22を形成する。コンタクトホール20及び22は絶縁膜24上にコンタクトホール部を開口するマスクを形成し、絶縁膜24に異方性エッチングを行うことによって形成される。更に、当該コンタクトホール内及び絶縁膜24上にスパッタリング法によりアルミニウムを堆積し、パターニングすることにより、ソース電極20、ドレイン電極22及び接続配線を形成する。

【0039】

このように、本発明の実施の形態では、ゲート絶縁膜が半導体膜のエッジ部分あるいは段差部分に形成されないようにしたので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が段差部分を被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例3】

【0040】

本発明の半導体装置の製造方法の他の実施の形態について図4を参照して説明する。同図において図3と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0041】

この実施例においては、ゲート絶縁膜14の形成を堆積プロセスによって行っている。この実施例においても、まず、図4(A)乃至同図(D)に示すように、基板10上への半導体膜12の形成から絶縁膜13の開口までの工程を行う。これは前述した図3(A)乃至同図(D)に示した工程(半導体膜形成〜第2の絶縁膜形成)と同じであるのでその説明を省略する。

【0042】

続いて、図4(E)に示すように、絶縁膜13及び絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられるので薄くて高耐圧であることが必要である。絶縁膜14は、PECVD法等の堆積プロセスによって酸化シリコン膜からなるゲート絶縁膜16を形成する。例えば、原料ガスとしてテトラエトキシシラン(TEOS)及び酸素(O2)を用い、それぞれの流量を50sccm、5slmとし、雰囲気温度を350℃、RFパワーを1.3kW、圧力を200Paという条件にして酸化シリコン膜を成膜する。この場合には、成膜速度が30nm/min程度となり、ゲート絶縁膜に適した耐圧特性等を備える良好な酸化シリコン膜を得ることができる。

【0043】

これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0044】

次に、図4(F)及び同図(G)に示すように、既述した図3(F)及び同図(G)と同様の工程を行って、電極膜形成、ソース/ドレイン領域形成、保護膜形成、ソース・ドレイン電極配線形成を行って薄膜半導体を完成させる。

【0045】

このように、本発明の半導体装置の製造方法の第2の実施の形態においても、ゲート絶縁膜が半導体膜のエッジ部分12aに形成されないので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が半導体膜のエッジを被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例4】

【0046】

次に、上述した半導体装置を含んで構成される集積回路、電気光学装置、電子機器の具体例について説明する。

【0047】

図5は、半導体装置を含んで構成される電気光学装置100の回路図である。本実施形態の電気光学装置(表示装置)100は、各画素領域に電界発光効果により発光可能な発光層OELD、それを駆動するための電流を記憶する保持容量を備え、さらに本発明にかかる半導体装置(薄膜トランジスタT1〜T4)を備えて構成されている。ドライバ101からは、走査線Vsel及び発光制御線Vgpが各画素領域に供給されている。ドライバ102からは、データ線Idataおよび電源線Vddが各画素領域に供給されている。走査線Vselとデータ線Idataとを制御することにより、各画素領域に対する電流プログラムが行われ、発光部OELDによる発光が制御可能になっている。

【0048】

なお、上記駆動回路は、発光要素に電界発光素子を使用する場合の回路の一例であり他の回路構成も可能である。また、ドライバ101、102のそれぞれを構成する集積回路を本発明に係る半導体装置によって形成することも好適である。

【0049】

図6は、上述した電気光学装置を含んで構成される電子機器の具体例を説明する図である。図6(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明に係る電気光学装置は表示部として利用可能である。図6(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図6(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図6(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。なお、本発明にかかる半導体装置は、電気光学装置の構成部品として上記のような電子機器に含まれる場合の他に、単独で電子機器の構成部品としても適用し得る。

【0050】

また、上記例に限らず本発明にかかる半導体装置の製造方法は、種々の電子機器の製造に適用可能である。例えば、この他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、ICカードなどにも適用することができる。

【0051】

なお、本発明は上述した各実施形態に限定されることなく、本発明の要旨の範囲内で種々の変形実施が可能である。

【0052】

例えば、上述した実施形態では、半導体膜の一例として多結晶シリコン膜を採り上げて説明していたが、半導体膜はこれに限定されるものではなく、他の半導体材料を用いても良い。また、ポリシラザンを有機溶媒に溶かしたもの等の液体材料を用いて半導体膜(シリコン膜)や絶縁膜(酸化シリコン膜)を形成してもよい。

【0053】

また、上述した実施形態では、電界効果型の半導体素子の一例として薄膜トランジスタを採り上げていたが、他にも、単結晶SOI(silicon oninsulator)トランジスタにおいて各トランジスタの相互間をエッチング等によって素子分離する構造の半導体装置などに対しても同様にして本発明を適用することが可能である。

【図面の簡単な説明】

【0054】

【図1】本実施形態の薄膜トランジスタの構造を説明する平面図である。

【図2】図1に示す薄膜トランジスタの図中II−II方向(チャネル幅方向)における断面図である。

【図3】薄膜トランジスタの製造方法を説明する図である。

【図4】薄膜トランジスタの他の製造方法を説明する図である。

【図5】半導体装置を含んで構成される電気光学装置の回路図である。

【図6】電子機器の具体例を説明する図である。

【符号の説明】

【0055】

1…薄膜トランジスタ、10…基板、11…下地絶縁膜、12…半導体膜、13…第1の絶縁膜(素子分離膜)、14…第2の絶縁膜(ゲート絶縁膜)、18…ゲート電極膜、20…ソース電極、22…ドレイン電極

【背景技術】

【0001】

近年、低温プロセスによって形成された結晶性半導体膜(例えば、多結晶シリコン膜)を用いて、電流駆動能力の高い薄膜トランジスタを形成する技術の研究、開発が進められている。一般に、多結晶シリコン膜は非晶質シリコン膜に対してレーザ照射を行って結晶化することにより形成される。ところが、このようにして形成される多結晶シリコン膜は、結晶化の際に各所で成長した結晶粒同士の境界(粒界)が隆起して突起状となり、表面の凹凸が大きくなる傾向にある。この多結晶シリコン膜の上側にゲート絶縁膜及びゲート電極を形成した電界効果型の薄膜トランジスタ(TFT)では、多結晶シリコン膜の表面の突起部分に電界が集中してゲート絶縁膜の絶縁破壊を生じやすい。このような問題に対して、特開2000−40828号公報(特許文献1)には、多結晶シリコン膜を成膜した後にその表面を研磨して平坦化することにより、薄膜トランジスタにおけるゲート絶縁膜の絶縁破壊を回避する技術が開示されている。

【0002】

ところで、薄膜トランジスタの微細化を進めるためにゲート絶縁膜の膜厚をより薄くした場合には、半導体膜のエッジ部分におけるゲート絶縁膜が薄くなりやすい。特に、スパッタ法やCVD法などの段差被覆性(ステップカバレッジ)が低い成膜法を用いてゲート絶縁膜を形成する場合にこの傾向が顕著となる。かかるエッジ部分を横切るようにゲート電極が形成されるとその部分で電界集中が生じ、絶縁破壊に至ることが多くなる。これにより、薄膜トランジスタの信頼性が低下するという不都合が生じる。上述した従来技術では、このような半導体膜のエッジ部分における電界集中の緩和を達成することは難しく、更なる改良技術が望まれていた。

【特許文献1】特開2000−40828号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

そこで、本発明は、薄膜トランジスタ等の半導体装置において半導体膜のエッジ部分におけるゲート絶縁膜の絶縁破壊やリークの発生を回避して半導体装置の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0004】

上記目的を達成するため本発明の半導体装置の製造方法は、絶縁基板の上に半導体膜を島状に形成する第1の工程と、上記半導体膜のエッジ部を含んで上記半導体膜を第1の絶縁膜で覆う第2の工程と、上記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも上記絶縁膜の開口部の半導体膜上に上記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、上記第2の絶縁膜上に電極配線膜を形成する第5の工程と、を含む。

【0005】

かかる製造工程によって半導体装置を製造することによって、ゲート絶縁膜中に電界が集中する部分をなくすことができ、ゲート絶縁膜の信頼性を向上することが可能となる。

【0006】

好ましくは、上記第1の工程は、上記絶縁基板に上記半導体膜を形成する工程と、熱処理によって上記半導体膜を多結晶化させる工程と、上記多結晶化した半導体の表面を平坦化する工程と、上記多結晶化した半導体膜を素子形成領域にパターニングする工程と、を含む。それにより、表面が平坦な多結晶性半導体膜を得ることが出来、該半導体膜表面の凹凸によってゲート絶縁膜中に電界が集中する部分が生ずることを回避することが出来る。

【0007】

好ましくは、上記第4の工程は、上記半導体膜上面の熱酸化によって上記第2の絶縁膜を形成する工程である。それにより、薄く絶縁性に優れたゲート絶縁膜を得ることが出来る。

【0008】

好ましくは、上記第4の工程は、上記半導体膜上に絶縁材料を堆積(成膜)させて上記第2の絶縁膜を形成する工程である。それにより、半導体膜の膜厚を減らすことなく、該半導体膜上にゲート絶縁膜を形成することが出来る。

【0009】

また、本発明の半導体装置は、絶縁基板上に島状に形成された半導体膜と、上記絶縁基板上に、上記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、少なくとも上記領域分離絶縁膜の開口部の上記半導体膜上面に上記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と、上記ゲート絶縁膜上に形成されるゲート電極と、を備える。

【0010】

かかる構成とすることによって、ゲート絶縁膜中に電界が集中する部分をなくしてゲート絶縁膜の信頼性を向上した半導体装置を得ることが出来る。

【0011】

好ましくは、上記ゲート絶縁膜は、上記半導体膜上面に該半導体膜のエッジ部から離れて形成されている。それにより、ゲート絶縁膜中に強電界となる部分が生じることを回避する。

【0012】

好ましくは、上記領域分離絶縁膜は、少なくとも上記ゲート絶縁膜の厚さの2倍以上の厚さに形成される。それにより、領域分離絶縁膜に十分な絶縁性を確保することが出来る。

【0013】

また、本発明の集積回路、電気光学装置及び電子機器は、上述した構成の半導体装置を備える。

【発明の効果】

【0014】

本発明によれば、ゲート絶縁膜は半導体膜のエッジ部を避けて形成されるので局所的な電界集中によるゲート絶縁膜の破壊が防止される。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施の形態について説明する。

【実施例1】

【0016】

図1は、本発明の実施形態の半導体装置としての薄膜トランジスタの構造を説明する平面図である。図2は、図1に示す薄膜トランジスタの同図中のII−II線方向(チャネル幅方向)における薄膜トランジスタの断面図である。両図において対応する部分には同一符号を付している。薄膜トランジスタは、後述のように、有機EL表示装置や液晶表示装置などの画素駆動素子等として用いられるものである。

【0017】

図1及び図2に示すように、薄膜トランジスタ1は、半導体膜、絶縁膜及び電極を積層した構造(MOS構造)を用いる電界効果型トランジスタであり、基板10上に絶縁膜11が形成された絶縁基板、島状に形成された半導体膜12、半導体膜を隔離する絶縁膜(第1の絶縁膜)13、ゲート絶縁膜(第2の絶縁膜)14、ゲート電極18、ソース電極20、ドレイン電極22、絶縁膜(保護膜)24を含んで構成されている。

【0018】

基板10は、例えば、ガラス、水晶ガラス、プラスチックなどの基板である。絶縁膜11は酸化シリコン膜や窒化シリコン膜などの下地絶縁膜である。絶縁膜11は半導体膜12の電気的絶縁と基板10から半導体膜12に不純物が侵入することを防止する。

【0019】

半導体膜12は、薄膜トランジスタの活性領域を担うものであり、結晶性半導体膜が用いられる。本実施形態では、半導体膜12として多結晶シリコン膜(ポリシリコン膜)を用いている。

【0020】

絶縁膜13は、基板10上に島状に形成されている島状の半導体膜12の周囲を囲む共もに図示しない他の半導体膜から半導体膜12を絶縁し、素子領域分離を行っている。また、絶縁膜13は当該半導体膜12のエッジ部12aを覆い、エッジ部12aの上面を露出(開口)するように形成されている。この絶縁膜13は、半導体膜12とほぼ同じ膜厚に形成されている。絶縁膜13としては、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが好適に用いられる。当該絶縁膜13は、比較的に厚膜に形成する必要がある反面、ゲート絶縁膜14ほどには絶縁耐圧、固定電荷密度等の特性を要求されないことから、高速成膜に適した製造条件を採用して形成することができる。

【0021】

ゲート絶縁膜14は、絶縁膜13の開口部に露出した半導体膜12上面を覆うようにして形成されている。この実施例では、プラズマ雰囲気下で露出した半導体膜12を酸化させて酸化シリコンの絶縁膜を形成し、ゲート絶縁膜14としている。ゲート絶縁膜16として、例えば、シリコン窒化物(Si3N4)膜等を形成しても良い。ゲート絶縁膜16は、厚膜に形成する必要性は少ないが、絶縁耐圧、固定電荷密度等について高い特性を要求されることから、より良好な膜質が得られる製造条件(一般には低速成膜)を採用して形成される。後述のように、ゲート絶縁膜14をCVDのような堆積プロセスによって行っても良い。

【0022】

ゲート絶縁膜14は、半導体膜12のエッジ部12aから離間しているのでエッジ部12a近傍の局所的な高電界の影響を受け難くなり、絶縁破壊が回避される。

【0023】

ゲート電極18は、絶縁膜13及びゲート絶縁膜14の上側であって、半導体膜12の所定位置の上側を通るように形成されている。より詳細には、ゲート電極18は、図1に示すように半導体膜12の平行な二辺を横切るように形成されている。このゲート電極18は、例えば、タンタル、クロム、アルミニウム等の導電体膜からなる。

【0024】

ソース電極20及びドレイン電極22は、それぞれともに、絶縁膜24を貫通して半導体膜12に接続されている。これらのソース電極20等は、例えば、アルミニウム等の導電体膜からなる。

【0025】

絶縁膜24は、ゲート電極18及び絶縁膜18等の上面を覆うようにして形成されている。この絶縁膜24は保護膜としての役割を担っており、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが用いられる。

【実施例2】

【0026】

次に、上述した半導体装置の製造方法を図3に示す工程図を参照して説明する。

【0027】

(半導体膜形成)

まず、図3(A)に示すように、ガラス基板10上にプラズマCVD法等によって酸化シリコン(SiO2)の絶縁膜11を形成する。

【0028】

この上に、PECVD法、LPCVD法、常圧化学気相堆積法(APCVD法)、スパッタリング法などの成膜法によって半導体膜12として非晶質シリコン膜を成膜する。この非晶質シリコン膜に対してエキシマレーザ等を照射する処理(レーザアニール処理)を行うことにより、非晶質シリコン膜を多結晶シリコン膜に変換する。このとき、レーザ照射による結晶化処理を行って得られる多結晶シリコン膜の表面には、各結晶粒の境界(粒界)が隆起することによる凹凸30が生じることが多い。

【0029】

そこで、好ましくは、半導体膜12の表面の凹凸が平坦化されるまで半導体膜12を研磨する。本実施形態では、CMP法(化学的機械的研磨法)を採用して本工程を行う。CMP法による研磨の好適な条件としては、例えば、軟質ポリウレタン製のパッドと、アンモニア系又はアミン系のアルカリ溶液にシリカ粒子を分散させた研磨剤(スラリー)を組み合わせて用い、圧力30000Pa、回転数50回転/分、研磨剤の流量を200sccm、という条件を採用できる。

【0030】

次に、図3(B)に示すように、平坦化した半導体膜12にフォトレジスト塗布、パターン露光、現像、エッチング処理などからなるパターン形成処理(パターニング)を行うことにより、基板10上の予め定められた素子形成領域に多結晶シリコン膜からなる島状の半導体膜12を形成する。

【0031】

(第1の絶縁膜形成)

図3(C)に示すように、絶縁膜11及び半導体膜12上に素子分離の絶縁膜13を形成する。絶縁膜13は、例えば、PECVD法等によって酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などを形成することによって得られる。絶縁膜13は半導体膜12のエッジ部で後述の工程のゲート絶縁膜14よりも十分厚くなるように形成される。例えば、ゲート絶縁膜14の膜厚の2倍以上の膜厚となるように形成される。

【0032】

(第1の絶縁膜の開口)

図3(D)に示すように、絶縁膜13にパターニングを施し、半導体膜12のエッジ部を除く半導体膜上面を開口する。

【0033】

(第2の絶縁膜形成)

図3(E)に示すように、絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられ、薄くて高耐圧であることが必要である。絶縁膜14は、例えば、酸素を含むプラズマ雰囲気下で半導体膜12である多結晶シリコン膜の表面を熱酸化させることによって得られる。これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0034】

(電極膜形成)

図3(F)に示すように、絶縁膜13及びゲート絶縁膜14の上にタンタル、アルミニウム等の金属薄膜をスパッタリング法により形成した後、パターニングすることによって、ゲート絶縁膜16上の所定位置にゲート電極及び配線膜18を形成する。

【0035】

(ソース/ドレイン領域形成)

次に、ゲート電極18をマスクとして半導体膜12に対してドナーまたはアクセプターとなる不純物イオンを打ち込む。これにより、ゲート電極18の下側にチャネル形成領域が形成され、それ以外の部分(イオン注入がされた部分)にソース/ドレイン領域が形成される。更に熱処理を施して不純物元素の活性化を行う。

【0036】

(保護膜形成)

図3(G)に示すように、ゲート電極膜18及び絶縁膜13上に保護膜として絶縁膜24を形成する。絶縁膜24として、例えば、PECVD法で約500nmの酸化シリコン膜を形成する。

【0037】

(ソース・ドレイン電極配線形成)

更に、絶縁膜24を貫通し、半導体膜12のソース/ドレイン領域に至るコンタクトホール20、22を形成する。コンタクトホール20及び22は絶縁膜24上にコンタクトホール部を開口するマスクを形成し、絶縁膜24に異方性エッチングを行うことによって形成される。更に、当該コンタクトホール内及び絶縁膜24上にスパッタリング法によりアルミニウムを堆積し、パターニングすることにより、ソース電極20、ドレイン電極22及び接続配線を形成する。

【0038】

このように、本発明の実施の形態では、ゲート絶縁膜が半導体膜のエッジ部分あるいは段差部分に形成されないようにしたので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が段差部分を被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例3】

【0039】

本発明の半導体装置の製造方法の他の実施の形態について図4を参照して説明する。同図において図3と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0040】

この実施例においては、ゲート絶縁膜14の形成を堆積プロセスによって行っている。この実施例においても、まず、図4(A)乃至同図(D)に示すように、基板10上への半導体膜12の形成から絶縁膜13の開口までの工程を行う。これは前述した図3(A)乃至同図(D)に示した工程(半導体膜形成〜第2の絶縁膜形成)と同じであるのでその説明を省略する。

【0041】

続いて、図4(E)に示すように、絶縁膜13及び絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられるので薄くて高耐圧であることが必要である。絶縁膜14は、PECVD法等の堆積プロセスによって酸化シリコン膜からなるゲート絶縁膜16を形成する。例えば、原料ガスとしてテトラエトキシシラン(TEOS)及び酸素(O2)を用い、それぞれの流量を50sccm、5slmとし、雰囲気温度を350℃、RFパワーを1.3kW、圧力を200Paという条件にして酸化シリコン膜を成膜する。この場合には、成膜速度が30nm/min程度となり、ゲート絶縁膜に適した耐圧特性等を備える良好な酸化シリコン膜を得ることができる。

【0042】

これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0043】

次に、図4(F)及び同図(G)に示すように、既述した図3(F)及び同図(G)と同様の工程を行って、電極膜形成、ソース/ドレイン領域形成、保護膜形成、ソース・ドレイン電極配線形成を行って薄膜半導体を完成させる。

【0044】

このように、本発明の半導体装置の製造方法の第2の実施の形態においても、ゲート絶縁膜が半導体膜のエッジ部分12aに形成されないので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が半導体膜のエッジを被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例4】

【0045】

次に、上述した半導体装置を含んで構成される集積回路、電気光学装置、電子機器の具体例について説明する。

【0046】

図5は、半導体装置を含んで構成される電気光学装置100の回路図である。本実施形態の電気光学装置(表示装置)100は、各画素領域に電界発光効果により発光可能な発光層OELD、それを駆動するための電流を記憶する保持容量を備え、さらに本発明にかかる半導体装置(薄膜トランジスタT1〜T4)を備えて構成されている。ドライバ101からは、走査線Vsel及び発光制御線Vgpが各画素領域に供給されている。ドライバ102からは、データ線Idataおよび電源線Vddが各画素領域に供給されている。走査線Vselとデータ線Idataとを制御することにより、各画素領域に対する電流プログラムが行われ、発光部OELDによる発光が制御可能になっている。

【0047】

なお、上記駆動回路は、発光要素に電界発光素子を使用する場合の回路の一例であり他の回路構成も可能である。また、ドライバ101、102のそれぞれを構成する集積回路を本発明に係る半導体装置によって形成することも好適である。

【0048】

図6は、上述した電気光学装置を含んで構成される電子機器の具体例を説明する図である。図6(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明に係る電気光学装置は表示部として利用可能である。図6(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図6(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図6(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。なお、本発明にかかる半導体装置は、電気光学装置の構成部品として上記のような電子機器に含まれる場合の他に、単独で電子機器の構成部品としても適用し得る。

【0049】

また、上記例に限らず本発明にかかる半導体装置の製造方法は、種々の電子機器の製造に適用可能である。例えば、この他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、ICカードなどにも適用することができる。

【0050】

なお、本発明は上述した各実施形態に限定されることなく、本発明の要旨の範囲内で種々の変形実施が可能である。

【0051】

例えば、上述した実施形態では、半導体膜の一例として多結晶シリコン膜を採り上げて説明していたが、半導体膜はこれに限定されるものではなく、他の半導体材料を用いても良い。また、ポリシラザンを有機溶媒に溶かしたもの等の液体材料を用いて半導体膜(シリコン膜)や絶縁膜(酸化シリコン膜)を形成してもよい。

【0052】

また、上述した実施形態では、電界効果型の半導体素子の一例として薄膜トランジスタを採り上げていたが、他にも、単結晶SOI(silicon on insulator)トランジスタにおいて各トランジスタの相互間をエッチング等によって素子分離する構造の半導体装置などに対しても同様にして本発明を適用することが可能である。

【図面の簡単な説明】

【0053】

【図1】本実施形態の薄膜トランジスタの構造を説明する平面図である。

【図2】図1に示す薄膜トランジスタの図中II−II方向(チャネル幅方向)における断面図である。

【図3】薄膜トランジスタの製造方法を説明する図である。

【図4】薄膜トランジスタの他の製造方法を説明する図である。

【図5】半導体装置を含んで構成される電気光学装置の回路図である。

【図6】電子機器の具体例を説明する図である。

【符号の説明】

【0054】

1…薄膜トランジスタ、10…基板、11…下地絶縁膜、12…半導体膜、13…第1の絶縁膜(素子分離膜)、14…第2の絶縁膜(ゲート絶縁膜)、18…ゲート電極膜、20…ソース電極、22…ドレイン電極

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MOSトランジスタ等の電界効果型の半導体装置の改良技術に関する。

【背景技術】

【0002】

近年、低温プロセスによって形成された結晶性半導体膜(例えば、多結晶シリコン膜)を用いて、電流駆動能力の高い薄膜トランジスタを形成する技術の研究、開発が進められている。一般に、多結晶シリコン膜は非晶質シリコン膜に対してレーザ照射を行って結晶化することにより形成される。ところが、このようにして形成される多結晶シリコン膜は、結晶化の際に各所で成長した結晶粒同士の境界(粒界)が隆起して突起状となり、表面の凹凸が大きくなる傾向にある。この多結晶シリコン膜の上側にゲート絶縁膜及びゲート電極を形成した電界効果型の薄膜トランジスタ(TFT)では、多結晶シリコン膜の表面の突起部分に電界が集中してゲート絶縁膜の絶縁破壊を生じやすい。このような問題に対して、特開2000−40828号公報(特許文献1)には、多結晶シリコン膜を成膜した後にその表面を研磨して平坦化することにより、薄膜トランジスタにおけるゲート絶縁膜の絶縁破壊を回避する技術が開示されている。

【0003】

ところで、薄膜トランジスタの微細化を進めるためにゲート絶縁膜の膜厚をより薄くした場合には、半導体膜のエッジ部分におけるゲート絶縁膜が薄くなりやすい。特に、スパッタ法やCVD法などの段差被覆性(ステップカバレッジ)が低い成膜法を用いてゲート絶縁膜を形成する場合にこの傾向が顕著となる。かかるエッジ部分を横切るようにゲート電極が形成されるとその部分で電界集中が生じ、絶縁破壊に至ることが多くなる。これにより、薄膜トランジスタの信頼性が低下するという不都合が生じる。上述した従来技術では、このような半導体膜のエッジ部分における電界集中の緩和を達成することは難しく、更なる改良技術が望まれていた。

【特許文献1】特開2000−40828号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

そこで、本発明は、薄膜トランジスタ等の半導体装置において半導体膜のエッジ部分におけるゲート絶縁膜の絶縁破壊やリークの発生を回避して半導体装置の信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するため本発明の半導体装置の製造方法は、絶縁基板の上に半導体膜を島状に形成する第1の工程と、上記半導体膜のエッジ部を含んで上記半導体膜を第1の絶縁膜で覆う第2の工程と、上記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、少なくとも上記絶縁膜の開口部の半導体膜上に上記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、上記第2の絶縁膜上に電極配線膜を形成する第5の工程と、を含む。

【0006】

かかる製造工程によって半導体装置を製造することによって、ゲート絶縁膜中に電界が集中する部分をなくすことができ、ゲート絶縁膜の信頼性を向上することが可能となる。

【0007】

好ましくは、上記第1の工程は、上記絶縁基板に上記半導体膜を形成する工程と、熱処理によって上記半導体膜を多結晶化させる工程と、上記多結晶化した半導体の表面を平坦化する工程と、上記多結晶化した半導体膜を素子形成領域にパターニングする工程と、を含む。それにより、表面が平坦な多結晶性半導体膜を得ることが出来、該半導体膜表面の凹凸によってゲート絶縁膜中に電界が集中する部分が生ずることを回避することが出来る。

【0008】

好ましくは、上記第4の工程は、上記半導体膜上面の熱酸化によって上記第2の絶縁膜を形成する工程である。それにより、薄く絶縁性に優れたゲート絶縁膜を得ることが出来る。

【0009】

好ましくは、上記第4の工程は、上記半導体膜上に絶縁材料を堆積(成膜)させて上記第2の絶縁膜を形成する工程である。それにより、半導体膜の膜厚を減らすことなく、該半導体膜上にゲート絶縁膜を形成することが出来る。

【0010】

また、本発明の半導体装置は、絶縁基板上に島状に形成された半導体膜と、上記絶縁基板上に、上記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、少なくとも上記領域分離絶縁膜の開口部の上記半導体膜上面に上記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と、上記ゲート絶縁膜上に形成されるゲート電極と、を備える。

【0011】

かかる構成とすることによって、ゲート絶縁膜中に電界が集中する部分をなくしてゲート絶縁膜の信頼性を向上した半導体装置を得ることが出来る。

【0012】

好ましくは、上記ゲート絶縁膜は、上記半導体膜上面に該半導体膜のエッジ部から離れて形成されている。それにより、ゲート絶縁膜中に強電界となる部分が生じることを回避する。

【0013】

好ましくは、上記領域分離絶縁膜は、少なくとも上記ゲート絶縁膜の厚さの2倍以上の厚さに形成される。それにより、領域分離絶縁膜に十分な絶縁性を確保することが出来る。

【0014】

また、本発明の集積回路、電気光学装置及び電子機器は、上述した構成の半導体装置を備える。

【発明の効果】

【0015】

本発明によれば、ゲート絶縁膜は半導体膜のエッジ部を避けて形成されるので局所的な電界集中によるゲート絶縁膜の破壊が防止される。

【発明を実施するための最良の形態】

【0016】

以下、本発明の実施の形態について説明する。

【実施例1】

【0017】

図1は、本発明の実施形態の半導体装置としての薄膜トランジスタの構造を説明する平面図である。図2は、図1に示す薄膜トランジスタの同図中のII−II線方向(チャネル幅方向)における薄膜トランジスタの断面図である。両図において対応する部分には同一符号を付している。薄膜トランジスタは、後述のように、有機EL表示装置や液晶表示装置などの画素駆動素子等として用いられるものである。

【0018】

図1及び図2に示すように、薄膜トランジスタ1は、半導体膜、絶縁膜及び電極を積層した構造(MOS構造)を用いる電界効果型トランジスタであり、基板10上に絶縁膜11が形成された絶縁基板、島状に形成された半導体膜12、半導体膜を隔離する絶縁膜(第1の絶縁膜)13、ゲート絶縁膜(第2の絶縁膜)14、ゲート電極18、ソース電極20、ドレイン電極22、絶縁膜(保護膜)24を含んで構成されている。

【0019】

基板10は、例えば、ガラス、水晶ガラス、プラスチックなどの基板である。絶縁膜11は酸化シリコン膜や窒化シリコン膜などの下地絶縁膜である。絶縁膜11は半導体膜12の電気的絶縁と基板10から半導体膜12に不純物が侵入することを防止する。

【0020】

半導体膜12は、薄膜トランジスタの活性領域を担うものであり、結晶性半導体膜が用いられる。本実施形態では、半導体膜12として多結晶シリコン膜(ポリシリコン膜)を用いている。

【0021】

絶縁膜13は、基板10上に島状に形成されている島状の半導体膜12の周囲を囲む共もに図示しない他の半導体膜から半導体膜12を絶縁し、素子領域分離を行っている。また、絶縁膜13は当該半導体膜12のエッジ部12aを覆い、エッジ部12aの上面を露出(開口)するように形成されている。この絶縁膜13は、半導体膜12とほぼ同じ膜厚に形成されている。絶縁膜13としては、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが好適に用いられる。当該絶縁膜13は、比較的に厚膜に形成する必要がある反面、ゲート絶縁膜14ほどには絶縁耐圧、固定電荷密度等の特性を要求されないことから、高速成膜に適した製造条件を採用して形成することができる。

【0022】

ゲート絶縁膜14は、絶縁膜13の開口部に露出した半導体膜12上面を覆うようにして形成されている。この実施例では、プラズマ雰囲気下で露出した半導体膜12を酸化させて酸化シリコンの絶縁膜を形成し、ゲート絶縁膜14としている。ゲート絶縁膜16として、例えば、シリコン窒化物(Si3N4)膜等を形成しても良い。ゲート絶縁膜16は、厚膜に形成する必要性は少ないが、絶縁耐圧、固定電荷密度等について高い特性を要求されることから、より良好な膜質が得られる製造条件(一般には低速成膜)を採用して形成される。後述のように、ゲート絶縁膜14をCVDのような堆積プロセスによって行っても良い。

【0023】

ゲート絶縁膜14は、半導体膜12のエッジ部12aから離間しているのでエッジ部12a近傍の局所的な高電界の影響を受け難くなり、絶縁破壊が回避される。

【0024】

ゲート電極18は、絶縁膜13及びゲート絶縁膜14の上側であって、半導体膜12の所定位置の上側を通るように形成されている。より詳細には、ゲート電極18は、図1に示すように半導体膜12の平行な二辺を横切るように形成されている。このゲート電極18は、例えば、タンタル、クロム、アルミニウム等の導電体膜からなる。

【0025】

ソース電極20及びドレイン電極22は、それぞれともに、絶縁膜24を貫通して半導体膜12に接続されている。これらのソース電極20等は、例えば、アルミニウム等の導電体膜からなる。

【0026】

絶縁膜24は、ゲート電極18及び絶縁膜18等の上面を覆うようにして形成されている。この絶縁膜24は保護膜としての役割を担っており、例えば、酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などが用いられる。

【実施例2】

【0027】

次に、上述した半導体装置の製造方法を図3に示す工程図を参照して説明する。

【0028】

(半導体膜形成)

まず、図3(A)に示すように、ガラス基板10上にプラズマCVD法等によって酸化シリコン(SiO2)の絶縁膜11を形成する。

【0029】

この上に、PECVD法、LPCVD法、常圧化学気相堆積法(APCVD法)、スパッタリング法などの成膜法によって半導体膜12として非晶質シリコン膜を成膜する。この非晶質シリコン膜に対してエキシマレーザ等を照射する処理(レーザアニール処理)を行うことにより、非晶質シリコン膜を多結晶シリコン膜に変換する。このとき、レーザ照射による結晶化処理を行って得られる多結晶シリコン膜の表面には、各結晶粒の境界(粒界)が隆起することによる凹凸30が生じることが多い。

【0030】

そこで、好ましくは、半導体膜12の表面の凹凸が平坦化されるまで半導体膜12を研磨する。本実施形態では、CMP法(化学的機械的研磨法)を採用して本工程を行う。CMP法による研磨の好適な条件としては、例えば、軟質ポリウレタン製のパッドと、アンモニア系又はアミン系のアルカリ溶液にシリカ粒子を分散させた研磨剤(スラリー)を組み合わせて用い、圧力30000Pa、回転数50回転/分、研磨剤の流量を200sccm、という条件を採用できる。

【0031】

次に、図3(B)に示すように、平坦化した半導体膜12にフォトレジスト塗布、パターン露光、現像、エッチング処理などからなるパターン形成処理(パターニング)を行うことにより、基板10上の予め定められた素子形成領域に多結晶シリコン膜からなる島状の半導体膜12を形成する。

【0032】

(第1の絶縁膜形成)

図3(C)に示すように、絶縁膜11及び半導体膜12上に素子分離の絶縁膜13を形成する。絶縁膜13は、例えば、PECVD法等によって酸化シリコン(SiO2)膜、シリコン窒化物(Si3N4)膜、リンシリケートガラス(PSG)膜などを形成することによって得られる。絶縁膜13は半導体膜12のエッジ部で後述の工程のゲート絶縁膜14よりも十分厚くなるように形成される。例えば、ゲート絶縁膜14の膜厚の2倍以上の膜厚となるように形成される。

【0033】

(第1の絶縁膜の開口)

図3(D)に示すように、絶縁膜13にパターニングを施し、半導体膜12のエッジ部を除く半導体膜上面を開口する。

【0034】

(第2の絶縁膜形成)

図3(E)に示すように、絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられ、薄くて高耐圧であることが必要である。絶縁膜14は、例えば、酸素を含むプラズマ雰囲気下で半導体膜12である多結晶シリコン膜の表面を熱酸化させることによって得られる。これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0035】

(電極膜形成)

図3(F)に示すように、絶縁膜13及びゲート絶縁膜14の上にタンタル、アルミニウム等の金属薄膜をスパッタリング法により形成した後、パターニングすることによって、ゲート絶縁膜16上の所定位置にゲート電極及び配線膜18を形成する。

【0036】

(ソース/ドレイン領域形成)

次に、ゲート電極18をマスクとして半導体膜12に対してドナーまたはアクセプターとなる不純物イオンを打ち込む。これにより、ゲート電極18の下側にチャネル形成領域が形成され、それ以外の部分(イオン注入がされた部分)にソース/ドレイン領域が形成される。更に熱処理を施して不純物元素の活性化を行う。

【0037】

(保護膜形成)

図3(G)に示すように、ゲート電極膜18及び絶縁膜13上に保護膜として絶縁膜24を形成する。絶縁膜24として、例えば、PECVD法で約500nmの酸化シリコン膜を形成する。

【0038】

(ソース・ドレイン電極配線形成)

更に、絶縁膜24を貫通し、半導体膜12のソース/ドレイン領域に至るコンタクトホール20、22を形成する。コンタクトホール20及び22は絶縁膜24上にコンタクトホール部を開口するマスクを形成し、絶縁膜24に異方性エッチングを行うことによって形成される。更に、当該コンタクトホール内及び絶縁膜24上にスパッタリング法によりアルミニウムを堆積し、パターニングすることにより、ソース電極20、ドレイン電極22及び接続配線を形成する。

【0039】

このように、本発明の実施の形態では、ゲート絶縁膜が半導体膜のエッジ部分あるいは段差部分に形成されないようにしたので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が段差部分を被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例3】

【0040】

本発明の半導体装置の製造方法の他の実施の形態について図4を参照して説明する。同図において図3と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0041】

この実施例においては、ゲート絶縁膜14の形成を堆積プロセスによって行っている。この実施例においても、まず、図4(A)乃至同図(D)に示すように、基板10上への半導体膜12の形成から絶縁膜13の開口までの工程を行う。これは前述した図3(A)乃至同図(D)に示した工程(半導体膜形成〜第2の絶縁膜形成)と同じであるのでその説明を省略する。

【0042】

続いて、図4(E)に示すように、絶縁膜13及び絶縁膜13の開口部に露出した半導体膜12上に第2の絶縁膜14を形成する。絶縁膜14はゲート絶縁膜として用いられるので薄くて高耐圧であることが必要である。絶縁膜14は、PECVD法等の堆積プロセスによって酸化シリコン膜からなるゲート絶縁膜16を形成する。例えば、原料ガスとしてテトラエトキシシラン(TEOS)及び酸素(O2)を用い、それぞれの流量を50sccm、5slmとし、雰囲気温度を350℃、RFパワーを1.3kW、圧力を200Paという条件にして酸化シリコン膜を成膜する。この場合には、成膜速度が30nm/min程度となり、ゲート絶縁膜に適した耐圧特性等を備える良好な酸化シリコン膜を得ることができる。

【0043】

これにより、開口部の半導体膜12上に絶縁膜13よりも相対的に薄い厚さのゲート絶縁膜14が形成される。ゲート絶縁膜14は半導体膜12のエッジ部12aから離れており、該エッジ部分には形成されていないため、絶縁膜14のカバレッジ(段差部の被覆性)に起因する膜厚の低下は問題とならない。

【0044】

次に、図4(F)及び同図(G)に示すように、既述した図3(F)及び同図(G)と同様の工程を行って、電極膜形成、ソース/ドレイン領域形成、保護膜形成、ソース・ドレイン電極配線形成を行って薄膜半導体を完成させる。

【0045】

このように、本発明の半導体装置の製造方法の第2の実施の形態においても、ゲート絶縁膜が半導体膜のエッジ部分12aに形成されないので、ゲート絶縁膜中に電界の集中する部分がなくゲート絶縁膜の信頼性が向上する。また、ゲート絶縁膜が半導体膜のエッジを被覆する構成ではないので、ゲート絶縁膜の形成に段差被覆率の悪い成膜あるいは堆積プロセスを使用することが出来る。

【実施例4】

【0046】

次に、上述した半導体装置を含んで構成される集積回路、電気光学装置、電子機器の具体例について説明する。

【0047】

図5は、半導体装置を含んで構成される電気光学装置100の回路図である。本実施形態の電気光学装置(表示装置)100は、各画素領域に電界発光効果により発光可能な発光層OELD、それを駆動するための電流を記憶する保持容量を備え、さらに本発明にかかる半導体装置(薄膜トランジスタT1〜T4)を備えて構成されている。ドライバ101からは、走査線Vsel及び発光制御線Vgpが各画素領域に供給されている。ドライバ102からは、データ線Idataおよび電源線Vddが各画素領域に供給されている。走査線Vselとデータ線Idataとを制御することにより、各画素領域に対する電流プログラムが行われ、発光部OELDによる発光が制御可能になっている。

【0048】

なお、上記駆動回路は、発光要素に電界発光素子を使用する場合の回路の一例であり他の回路構成も可能である。また、ドライバ101、102のそれぞれを構成する集積回路を本発明に係る半導体装置によって形成することも好適である。

【0049】

図6は、上述した電気光学装置を含んで構成される電子機器の具体例を説明する図である。図6(A)は携帯電話への適用例であり、当該携帯電話530はアンテナ部531、音声出力部532、音声入力部533、操作部534、および本発明の電気光学装置100を備えている。このように本発明に係る電気光学装置は表示部として利用可能である。図6(B)はビデオカメラへの適用例であり、当該ビデオカメラ540は受像部541、操作部542、音声入力部543、および本発明の電気光学装置100を備えている。図6(C)はテレビジョンへの適用例であり、当該テレビジョン550は本発明の電気光学装置100を備えている。なお、パーソナルコンピュータ等に用いられるモニタ装置に対しても同様に本発明に係る電気光学装置を適用し得る。図6(D)はロールアップ式テレビジョンへの適用例であり、当該ロールアップ式テレビジョン560は本発明の電気光学装置100を備えている。また、電子機器はこれらに限定されず、表示機能を有する各種の電子機器に適用可能である。例えばこれらの他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、電子手帳、電光掲示盤、宣伝公告用ディスプレイなども含まれる。なお、本発明にかかる半導体装置は、電気光学装置の構成部品として上記のような電子機器に含まれる場合の他に、単独で電子機器の構成部品としても適用し得る。

【0050】

また、上記例に限らず本発明にかかる半導体装置の製造方法は、種々の電子機器の製造に適用可能である。例えば、この他に、表示機能付きファックス装置、デジタルカメラのファインダ、携帯型TV、PDA、電子手帳、電光掲示盤、宣伝公告用ディスプレイ、ICカードなどにも適用することができる。

【0051】

なお、本発明は上述した各実施形態に限定されることなく、本発明の要旨の範囲内で種々の変形実施が可能である。

【0052】

例えば、上述した実施形態では、半導体膜の一例として多結晶シリコン膜を採り上げて説明していたが、半導体膜はこれに限定されるものではなく、他の半導体材料を用いても良い。また、ポリシラザンを有機溶媒に溶かしたもの等の液体材料を用いて半導体膜(シリコン膜)や絶縁膜(酸化シリコン膜)を形成してもよい。

【0053】

また、上述した実施形態では、電界効果型の半導体素子の一例として薄膜トランジスタを採り上げていたが、他にも、単結晶SOI(silicon oninsulator)トランジスタにおいて各トランジスタの相互間をエッチング等によって素子分離する構造の半導体装置などに対しても同様にして本発明を適用することが可能である。

【図面の簡単な説明】

【0054】

【図1】本実施形態の薄膜トランジスタの構造を説明する平面図である。

【図2】図1に示す薄膜トランジスタの図中II−II方向(チャネル幅方向)における断面図である。

【図3】薄膜トランジスタの製造方法を説明する図である。

【図4】薄膜トランジスタの他の製造方法を説明する図である。

【図5】半導体装置を含んで構成される電気光学装置の回路図である。

【図6】電子機器の具体例を説明する図である。

【符号の説明】

【0055】

1…薄膜トランジスタ、10…基板、11…下地絶縁膜、12…半導体膜、13…第1の絶縁膜(素子分離膜)、14…第2の絶縁膜(ゲート絶縁膜)、18…ゲート電極膜、20…ソース電極、22…ドレイン電極

【特許請求の範囲】

【請求項1】

絶縁基板の上に半導体膜を島状に形成する第1の工程と、

前記半導体膜のエッジ部を含んで前記半導体膜を第1の絶縁膜で覆う第2の工程と、

前記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、

少なくとも前記絶縁膜の開口部の半導体膜上に前記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、

前記第2の絶縁膜上に電極配線膜を形成する第5の工程と、

を含む半導体装置の製造方法。

【請求項2】

前記第1の工程は、

前記絶縁基板に前記半導体膜を形成する工程と、

熱処理によって前記半導体膜を多結晶化させる工程と、

前記多結晶化した半導体膜の表面を平坦化する工程と、

前記多結晶化した半導体膜を素子形成領域にパターニングする工程と、

を含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第4の工程は、前記半導体膜の熱酸化によって前記第2の絶縁膜を形成する工程である、請求項1に記載の半導体装置の製造方法。

【請求項4】

前記第4の工程は、前記半導体膜上に絶縁材料を堆積させて前記第2の絶縁膜を形成する工程である、請求項1に記載の半導体装置の製造方法。

【請求項5】

絶縁基板上に島状に形成された半導体膜と、

前記絶縁基板上に、前記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、

少なくとも前記領域分離絶縁膜の開口部の前記半導体膜上面に前記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と

前記ゲート絶縁膜上に形成されるゲート電極と、

を備える半導体装置。

【請求項6】

前記ゲート絶縁膜は、前記半導体膜上面に該半導体膜のエッジ部から離れて形成されている、請求項5に記載の半導体装置。

【請求項7】

前記領域分離絶縁膜は、少なくとも前記ゲート絶縁膜の厚さの2倍以上の厚さに形成される、請求項5記載の半導体装置。

【請求項8】

請求項5乃至7のいずれかに記載の半導体装置を備える集積回路。

【請求項9】

請求項5乃至7のいずれかに記載の半導体装置を備える電気光学装置。

【請求項10】

請求項5乃至7のいずれかに記載の半導体装置を備える電子機器。

【請求項1】

絶縁基板の上に半導体膜を島状に形成する第1の工程と、

前記半導体膜のエッジ部を含んで前記半導体膜を第1の絶縁膜で覆う第2の工程と、

前記半導体膜上部の第1の絶縁膜を該半導体膜のエッジ部を避けて開口する第3の工程と、

少なくとも前記絶縁膜の開口部の半導体膜上に前記第1の絶縁膜よりも相対的に薄い厚さの第2の絶縁膜を形成する第4の工程と、

前記第2の絶縁膜上に電極配線膜を形成する第5の工程と、

を含む半導体装置の製造方法。

【請求項2】

前記第1の工程は、

前記絶縁基板に前記半導体膜を形成する工程と、

熱処理によって前記半導体膜を多結晶化させる工程と、

前記多結晶化した半導体膜の表面を平坦化する工程と、

前記多結晶化した半導体膜を素子形成領域にパターニングする工程と、

を含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第4の工程は、前記半導体膜の熱酸化によって前記第2の絶縁膜を形成する工程である、請求項1に記載の半導体装置の製造方法。

【請求項4】

前記第4の工程は、前記半導体膜上に絶縁材料を堆積させて前記第2の絶縁膜を形成する工程である、請求項1に記載の半導体装置の製造方法。

【請求項5】

絶縁基板上に島状に形成された半導体膜と、

前記絶縁基板上に、前記半導体膜上面を開口し、該半導体膜のエッジ部を含む外周囲を取り囲んで形成される領域分離絶縁膜と、

少なくとも前記領域分離絶縁膜の開口部の前記半導体膜上面に前記領域分離絶縁膜よりも相対的に薄く形成されるゲート絶縁膜と

前記ゲート絶縁膜上に形成されるゲート電極と、

を備える半導体装置。

【請求項6】

前記ゲート絶縁膜は、前記半導体膜上面に該半導体膜のエッジ部から離れて形成されている、請求項5に記載の半導体装置。

【請求項7】

前記領域分離絶縁膜は、少なくとも前記ゲート絶縁膜の厚さの2倍以上の厚さに形成される、請求項5記載の半導体装置。

【請求項8】

請求項5乃至7のいずれかに記載の半導体装置を備える集積回路。

【請求項9】

請求項5乃至7のいずれかに記載の半導体装置を備える電気光学装置。

【請求項10】

請求項5乃至7のいずれかに記載の半導体装置を備える電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−41115(P2006−41115A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−217448(P2004−217448)

【出願日】平成16年7月26日(2004.7.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月26日(2004.7.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]