半導体装置及びその製造方法

【課題】 化合物半導体、シリコン半導体で形成したMIS型構造を備えた半導体装置及びその製造方法を提供する。

【解決手段】 半導体層と金属酸化物からなるゲート電極との界面に、金属酸化物から解離した酸素を含む層からなる絶縁層を備える。この絶縁層は、電極を形成した後、熱処理を行うことによって形成する。

【解決手段】 半導体層と金属酸化物からなるゲート電極との界面に、金属酸化物から解離した酸素を含む層からなる絶縁層を備える。この絶縁層は、電極を形成した後、熱処理を行うことによって形成する。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は半導体装置及びその製造方法に関し、特に、金属酸化物を電極とする半導体装置及びその製造方法に関する。

【0002】

【従来の技術】金属−絶縁膜−半導体(MIS)型構造の半導体装置を形成する際、半導体材料として化合物半導体を使用すると、化合物半導体は安定な酸化膜がないこと、表面準位が多いことなどの理由により、特性の優れたMIS型構造の半導体装置が得られなかった。一例として、P型ガリウム砒素基板上に二酸化シリコン膜、三酸化二アルミニウム膜を積層したMIS型構造の電界効果トランジスタを形成し、その容量電圧特性を測定した結果を図6に示す。図に示すように、周波数依存性があり、ヒステリシスも大きく、表面準位が多いことがわかる。

【0003】特性の優れた半導体装置を得るため、高抵抗の半導体層を絶縁膜として使用する方法が提案されている。従来提案されたガリウム砒素を使用したMIS型電界効果トランジスタの構造を図7に示す。図に示すように、半絶縁性GaAs基板10上にGaAsバッファ層11、n型GaAsチャネル層12、絶縁性のノンドープAlGaAs層13、高濃度のn型GaAsコンタクト層14が順次積層形成されており、ゲート電極15は、ノンドープAlGaAs13を介してn型チャネル層12に接触し、ソース電極16及びドレイン電極17は、高濃度のn型GaAsコンタクト層14に接続する構造となっている。

【0004】このような構造のMIS型電界効果トランジスタでは、GaAsバッファ層11、n型GaAsチャネル層12、ノンドープAlGaAs層13、n型GaAsコンタクト層14が、MBE法により積層形成されるため、エピタキシャル工程が複雑になるという問題点があった。また、n型GaAsチャネル層12が、高抵抗のノンドープAlGaAs層13を介してソース電極16及びドレイン電極17に接続するため、ソース抵抗、ドレイン抵抗が高くなり、特性の向上が図れないという問題点があった。

【0005】一方、シリコン半導体を使用する場合は、安定な酸化膜を得ることができるため、MIS型構造の半導体装置は広く用いられている。シリコンを使用したMIS型電界効果トランジスタは、次のように形成される。まず、シリコン半導体基板18表面にゲート酸化膜19及びゲート電極構成する金属膜20を積層形成する。ゲート電極の形成予定領域を覆うように、通常のホトレジスト21をパターニングする(図8)。ホトレジスト21をエッチングマスクとして使用し、ドライエッチングによりゲート電極22を形成する。次に、不純物イオンを注入し、ソース領域23及びドレイン領域24を形成し、ソース領域23及びドレイン領域24にそれぞれ接続するソース電極25及びドレイン電極26を形成し、MIS型電界効果トランジスタを形成することができる(図9)。

【0006】しかし、ゲート電極を構成する金属膜20をドライエッチングによりパターニングする方法では、エッチングに使用するプラズマの電荷がゲート酸化膜19に蓄積し、特性が劣化するという問題点があった。

【0007】

【発明が解決しようとする課題】このように従来の化合物半導体を用いたMIS型構造の半導体装置では、絶縁層として化合物半導体の酸化膜を使用することができず、高抵抗の半導体層を使用しているため、エピタキシャル工程が複雑になったり、特性の向上が図れないという問題点があった。また、シリコンを用いた半導体装置では、ゲート電極を形成する工程で、ゲート酸化膜に電荷が蓄積し、特性が劣化するという問題点があった。本発明は、上記問題点を解消し、特性の優れたMIS型構造の半導体装置及びその製造方法を提供することを目的とする。

【0008】

【課題を解決するための手段】上記目的を達成するため、第1の発明の半導体装置は、半導体層表面に絶縁層を介して電極を備えた半導体装置において、前記半導体層と金属酸化物からなる前記電極との界面に、前記金属酸化物から解離した酸素を含む絶縁層を備えたことを特徴とするものである。

【0009】又、第2の発明の半導体装置の製造方法は、半導体層上に金属酸化物からなる電極を形成する工程と、前記金属酸化物の酸素を解離させ、該解離した酸素によって前記半導体層を酸化する熱処理を行ない、前記電極と前記半導体層との界面に絶縁層を形成する工程とを含むことを特徴とするものである。

【0010】特に、上記第1、第2の発明において、金属酸化物が酸化ルテニウムであるとき、優れた特性のMIS型半導体装置を形成することができる。

【0011】

【発明の実施の形態】以下本発明の実施の形態について、図1乃至図3を用いて説明する。まず、ガリウム砒素半導体基板を用いた電界効果トランジスタを例にとり、第1の実施の形態を説明する。n型ガリウム砒素からなる半導体基板1の表面にCVD法あるいはスパッタ法によって、金属酸化物である酸化ルテニウム膜2を1000〜3000オングストローム形成する。次にゲート電極を形成するため、酸化ルテニウム膜2上のゲート電極形成予定領域を覆うように、ホトレジスト3をパターニングする(図1)。

【0012】このホトレジスト3をエッチングマスクとして使用し、酸化ルテニウム膜2をドライエッチングし、ゲート電極4を形成する。半導体基板1上にソース領域6及びドレイン領域7形成予定領域を開口するように別のホトレジストをパターニングして、イオン注入を行う。次に、注入したイオンの活性化のため、RTA法により、900℃、10秒の熱処理を行う。この熱処理によって、酸化ルテニウム膜の一部から酸素が解離し、解離した酸素によって半導体基板1が酸化される。その結果、ゲート電極4と半導体基板1界面に、絶縁層5が形成される(図2)。

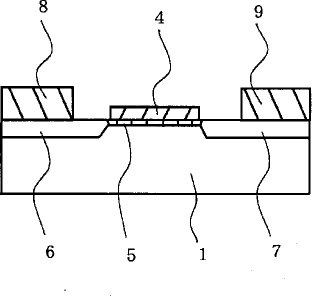

【0013】以下、通常の電界効果トランジスタの製造工程に従い、ソース電極8、ドレイン電極9を形成し、電界効果トランジスタを形成する(図3)。

【0014】このように、ゲート電極を構成する金属酸化物である酸化ルテニウムを熱処理することによって、酸化ルテニウムから解離した発生期の酸素が、半導体基板を酸化し、ゲート電極と半導体基板との界面に酸素を含む絶縁層を形成することができる。この絶縁膜は、ゲート−ソース間、ゲート−ドレイン間にそれぞれ1V印加したとき、10-10アンペア程度の電流しか流れず、良好な絶縁性を有することが確認された。

【0015】 ゲート電極と半導体基板との界面に酸素を含む層が形成されたことは、SIMS分析の結果から明らかである。図4に、界面状態を調べるため、ガリウム砒素基板上に酸化ルテニウムを形成したサンプルを形成し、900℃、10秒の熱処理前後の酸素濃度の分析結果を示す。図4から明らかなように、熱処理を行うことによって、酸素が深さ方向に拡散していることがわかる。この酸素の拡散によって、半導体基板とゲート電極との界面に絶縁層が形成される。なお、表面近傍の酸素濃度は、検出器の飽和のため、正確な値を示していない。

【0016】このように形成された絶縁膜の容量電圧特性のCVカーブを図5に示す。図に示すようにCVカーブのヒステリシスがないことがわかる。この結果からも、上記の方法で形成された絶縁膜は、表面準位の少ない良好な絶縁膜であることがわかる。

【0017】なお、酸化ルテニウム膜から酸素を解離させるための熱処理は、イオン注入後の活性化アニール工程、あるいは層間絶縁膜のリフロー工程の熱処理と兼ねることも可能であり、製造工程の増加を招くことはない。

【0018】次に、本発明の第2の実施の形態について、シリコン半導体からなる電界効果トランジスタを例にとり説明する。第1の実施の形態同様、半導体基板1の表面にCVD法あるいはスパッタ法によって、酸化ルテニウム膜14膜を1000〜3000オングストローム形成する。次にゲート電極を形成するため、酸化ルテニウム膜14上に、通常のホトレジスト15をパターニングする(図1)。

【0019】このホトレジスト15をエッチングマスクとして使用し、酸化ルテニウム膜14をドライエッチング除去し、半導体基板1を露出させる。露出した半導体基板1上にドレイン領域、ソース領域形成予定領域を開口するようにホトレジストをパターニングして、イオン注入を行い、ドレイン領域5、ソース領域6を形成する。次に、RTA法により、900℃、10秒の熱処理を行い、酸化ルテニウム膜から解離した酸素によって半導体基板1を酸化し、ゲート電極4と半導体基板1界面に、酸化膜からなる絶縁膜5を形成する(図2)。

【0020】以下、通常の電界効果トランジスタの製造工程に従い、ソース電極8、ドレイン電極9を形成し、電界効果トランジスタを形成する(図3)。

【0021】このように、ゲート電極を構成する金属酸化物である酸化ルテニウムを熱処理することによって発生する発生期の酸素によって、半導体基板を酸化し、ゲート電極と半導体基板との界面に絶縁膜を形成することができる。このように形成された絶縁膜は、従来のゲート酸化膜と同等の特性を備えている。従って、ゲート酸化膜形成工程を省略することが可能となる。

【0022】なお、酸化ルテニウム膜から酸素を解離させるための熱処理は、イオン注入後の活性化アニール工程、あるいは層間絶縁膜のリフロー工程の熱処理と兼ねることも可能であり、製造工程の増加を招くことはない。

【0023】また、ゲート電極を形成する際、酸化ルテニウム膜は直接シリコン半導体基板上に形成されるため、ドライエッチング時の電荷を半導体基板を通して半導体装置外へ逃がすことができる。そのため、従来問題となっていた、電荷がゲート酸化膜に蓄積し、ゲート特性に影響を与えることもなくなる。

【0024】以上、電界効果トランジスタの製造方法を例にとり、本発明の実施の形態について説明を行ってきたが、本発明はダイオード等の他の半導体装置に適用可能であることはいうまでもない。

【0025】

【発明の効果】以上説明したように本発明によれば、従来形成することができなかったガリウム砒素基板を用いてMIS型構造の半導体装置を形成することが可能となった。

【0026】また、シリコン半導体基板を用いた半導体装置においては、ゲート酸化膜に電荷が蓄積することもなく、特性の優れた半導体装置を形成することが可能となった。

【0027】本発明の製造方法は、半導体基板上に金属酸化膜を形成し、熱処理するのみでMIS型構造を形成することができ、非常に簡便な方法である。

【図面の簡単な説明】

【図1】本発明の実施の形態を説明する図である。

【図2】本発明の実施の形態を説明する図である。

【図3】本発明の実施の形態を説明する図である。

【図4】本発明の実施の形態を説明する図である。

【図5】本発明の実施の形態の容量電圧特性を示す図である。

【図6】従来のMIS型構造半導体装置の容量電圧特性を示す図である。

【図7】従来のMIS型電界効果トランジスタの構造を示す図である。

【図8】従来のMIS型電界効果トランジスタの製造方法を説明する図である。

【図9】従来のMIS型電界効果トランジスタの製造方法を説明する図である。

【符号の説明】

1 半導体基板

2 酸化ルテニウム膜

3 ホトレジスト

4 ゲート電極

5 絶縁層

6 ソース領域

7 ドレイン領域

8 ソース電極

9 ドレイン電極

10 半絶縁性GaAs基板

11 GaAsバッファ層

12 n型GaAsチャネル層

13 ノンドープAlGaAs層

14 n型GaAsコンタクト層

15 ゲート電極

16 ソース電極

17 ドレイン電極

18 シリコン半導体基板

19 ゲート酸化膜

20 金属膜

21 ホトレジスト

22 ゲート電極

23 ソース領域

24 ドレイン領域

25 ソース電極

26 ドレイン電極

【0001】

【発明の属する技術分野】本発明は半導体装置及びその製造方法に関し、特に、金属酸化物を電極とする半導体装置及びその製造方法に関する。

【0002】

【従来の技術】金属−絶縁膜−半導体(MIS)型構造の半導体装置を形成する際、半導体材料として化合物半導体を使用すると、化合物半導体は安定な酸化膜がないこと、表面準位が多いことなどの理由により、特性の優れたMIS型構造の半導体装置が得られなかった。一例として、P型ガリウム砒素基板上に二酸化シリコン膜、三酸化二アルミニウム膜を積層したMIS型構造の電界効果トランジスタを形成し、その容量電圧特性を測定した結果を図6に示す。図に示すように、周波数依存性があり、ヒステリシスも大きく、表面準位が多いことがわかる。

【0003】特性の優れた半導体装置を得るため、高抵抗の半導体層を絶縁膜として使用する方法が提案されている。従来提案されたガリウム砒素を使用したMIS型電界効果トランジスタの構造を図7に示す。図に示すように、半絶縁性GaAs基板10上にGaAsバッファ層11、n型GaAsチャネル層12、絶縁性のノンドープAlGaAs層13、高濃度のn型GaAsコンタクト層14が順次積層形成されており、ゲート電極15は、ノンドープAlGaAs13を介してn型チャネル層12に接触し、ソース電極16及びドレイン電極17は、高濃度のn型GaAsコンタクト層14に接続する構造となっている。

【0004】このような構造のMIS型電界効果トランジスタでは、GaAsバッファ層11、n型GaAsチャネル層12、ノンドープAlGaAs層13、n型GaAsコンタクト層14が、MBE法により積層形成されるため、エピタキシャル工程が複雑になるという問題点があった。また、n型GaAsチャネル層12が、高抵抗のノンドープAlGaAs層13を介してソース電極16及びドレイン電極17に接続するため、ソース抵抗、ドレイン抵抗が高くなり、特性の向上が図れないという問題点があった。

【0005】一方、シリコン半導体を使用する場合は、安定な酸化膜を得ることができるため、MIS型構造の半導体装置は広く用いられている。シリコンを使用したMIS型電界効果トランジスタは、次のように形成される。まず、シリコン半導体基板18表面にゲート酸化膜19及びゲート電極構成する金属膜20を積層形成する。ゲート電極の形成予定領域を覆うように、通常のホトレジスト21をパターニングする(図8)。ホトレジスト21をエッチングマスクとして使用し、ドライエッチングによりゲート電極22を形成する。次に、不純物イオンを注入し、ソース領域23及びドレイン領域24を形成し、ソース領域23及びドレイン領域24にそれぞれ接続するソース電極25及びドレイン電極26を形成し、MIS型電界効果トランジスタを形成することができる(図9)。

【0006】しかし、ゲート電極を構成する金属膜20をドライエッチングによりパターニングする方法では、エッチングに使用するプラズマの電荷がゲート酸化膜19に蓄積し、特性が劣化するという問題点があった。

【0007】

【発明が解決しようとする課題】このように従来の化合物半導体を用いたMIS型構造の半導体装置では、絶縁層として化合物半導体の酸化膜を使用することができず、高抵抗の半導体層を使用しているため、エピタキシャル工程が複雑になったり、特性の向上が図れないという問題点があった。また、シリコンを用いた半導体装置では、ゲート電極を形成する工程で、ゲート酸化膜に電荷が蓄積し、特性が劣化するという問題点があった。本発明は、上記問題点を解消し、特性の優れたMIS型構造の半導体装置及びその製造方法を提供することを目的とする。

【0008】

【課題を解決するための手段】上記目的を達成するため、第1の発明の半導体装置は、半導体層表面に絶縁層を介して電極を備えた半導体装置において、前記半導体層と金属酸化物からなる前記電極との界面に、前記金属酸化物から解離した酸素を含む絶縁層を備えたことを特徴とするものである。

【0009】又、第2の発明の半導体装置の製造方法は、半導体層上に金属酸化物からなる電極を形成する工程と、前記金属酸化物の酸素を解離させ、該解離した酸素によって前記半導体層を酸化する熱処理を行ない、前記電極と前記半導体層との界面に絶縁層を形成する工程とを含むことを特徴とするものである。

【0010】特に、上記第1、第2の発明において、金属酸化物が酸化ルテニウムであるとき、優れた特性のMIS型半導体装置を形成することができる。

【0011】

【発明の実施の形態】以下本発明の実施の形態について、図1乃至図3を用いて説明する。まず、ガリウム砒素半導体基板を用いた電界効果トランジスタを例にとり、第1の実施の形態を説明する。n型ガリウム砒素からなる半導体基板1の表面にCVD法あるいはスパッタ法によって、金属酸化物である酸化ルテニウム膜2を1000〜3000オングストローム形成する。次にゲート電極を形成するため、酸化ルテニウム膜2上のゲート電極形成予定領域を覆うように、ホトレジスト3をパターニングする(図1)。

【0012】このホトレジスト3をエッチングマスクとして使用し、酸化ルテニウム膜2をドライエッチングし、ゲート電極4を形成する。半導体基板1上にソース領域6及びドレイン領域7形成予定領域を開口するように別のホトレジストをパターニングして、イオン注入を行う。次に、注入したイオンの活性化のため、RTA法により、900℃、10秒の熱処理を行う。この熱処理によって、酸化ルテニウム膜の一部から酸素が解離し、解離した酸素によって半導体基板1が酸化される。その結果、ゲート電極4と半導体基板1界面に、絶縁層5が形成される(図2)。

【0013】以下、通常の電界効果トランジスタの製造工程に従い、ソース電極8、ドレイン電極9を形成し、電界効果トランジスタを形成する(図3)。

【0014】このように、ゲート電極を構成する金属酸化物である酸化ルテニウムを熱処理することによって、酸化ルテニウムから解離した発生期の酸素が、半導体基板を酸化し、ゲート電極と半導体基板との界面に酸素を含む絶縁層を形成することができる。この絶縁膜は、ゲート−ソース間、ゲート−ドレイン間にそれぞれ1V印加したとき、10-10アンペア程度の電流しか流れず、良好な絶縁性を有することが確認された。

【0015】 ゲート電極と半導体基板との界面に酸素を含む層が形成されたことは、SIMS分析の結果から明らかである。図4に、界面状態を調べるため、ガリウム砒素基板上に酸化ルテニウムを形成したサンプルを形成し、900℃、10秒の熱処理前後の酸素濃度の分析結果を示す。図4から明らかなように、熱処理を行うことによって、酸素が深さ方向に拡散していることがわかる。この酸素の拡散によって、半導体基板とゲート電極との界面に絶縁層が形成される。なお、表面近傍の酸素濃度は、検出器の飽和のため、正確な値を示していない。

【0016】このように形成された絶縁膜の容量電圧特性のCVカーブを図5に示す。図に示すようにCVカーブのヒステリシスがないことがわかる。この結果からも、上記の方法で形成された絶縁膜は、表面準位の少ない良好な絶縁膜であることがわかる。

【0017】なお、酸化ルテニウム膜から酸素を解離させるための熱処理は、イオン注入後の活性化アニール工程、あるいは層間絶縁膜のリフロー工程の熱処理と兼ねることも可能であり、製造工程の増加を招くことはない。

【0018】次に、本発明の第2の実施の形態について、シリコン半導体からなる電界効果トランジスタを例にとり説明する。第1の実施の形態同様、半導体基板1の表面にCVD法あるいはスパッタ法によって、酸化ルテニウム膜14膜を1000〜3000オングストローム形成する。次にゲート電極を形成するため、酸化ルテニウム膜14上に、通常のホトレジスト15をパターニングする(図1)。

【0019】このホトレジスト15をエッチングマスクとして使用し、酸化ルテニウム膜14をドライエッチング除去し、半導体基板1を露出させる。露出した半導体基板1上にドレイン領域、ソース領域形成予定領域を開口するようにホトレジストをパターニングして、イオン注入を行い、ドレイン領域5、ソース領域6を形成する。次に、RTA法により、900℃、10秒の熱処理を行い、酸化ルテニウム膜から解離した酸素によって半導体基板1を酸化し、ゲート電極4と半導体基板1界面に、酸化膜からなる絶縁膜5を形成する(図2)。

【0020】以下、通常の電界効果トランジスタの製造工程に従い、ソース電極8、ドレイン電極9を形成し、電界効果トランジスタを形成する(図3)。

【0021】このように、ゲート電極を構成する金属酸化物である酸化ルテニウムを熱処理することによって発生する発生期の酸素によって、半導体基板を酸化し、ゲート電極と半導体基板との界面に絶縁膜を形成することができる。このように形成された絶縁膜は、従来のゲート酸化膜と同等の特性を備えている。従って、ゲート酸化膜形成工程を省略することが可能となる。

【0022】なお、酸化ルテニウム膜から酸素を解離させるための熱処理は、イオン注入後の活性化アニール工程、あるいは層間絶縁膜のリフロー工程の熱処理と兼ねることも可能であり、製造工程の増加を招くことはない。

【0023】また、ゲート電極を形成する際、酸化ルテニウム膜は直接シリコン半導体基板上に形成されるため、ドライエッチング時の電荷を半導体基板を通して半導体装置外へ逃がすことができる。そのため、従来問題となっていた、電荷がゲート酸化膜に蓄積し、ゲート特性に影響を与えることもなくなる。

【0024】以上、電界効果トランジスタの製造方法を例にとり、本発明の実施の形態について説明を行ってきたが、本発明はダイオード等の他の半導体装置に適用可能であることはいうまでもない。

【0025】

【発明の効果】以上説明したように本発明によれば、従来形成することができなかったガリウム砒素基板を用いてMIS型構造の半導体装置を形成することが可能となった。

【0026】また、シリコン半導体基板を用いた半導体装置においては、ゲート酸化膜に電荷が蓄積することもなく、特性の優れた半導体装置を形成することが可能となった。

【0027】本発明の製造方法は、半導体基板上に金属酸化膜を形成し、熱処理するのみでMIS型構造を形成することができ、非常に簡便な方法である。

【図面の簡単な説明】

【図1】本発明の実施の形態を説明する図である。

【図2】本発明の実施の形態を説明する図である。

【図3】本発明の実施の形態を説明する図である。

【図4】本発明の実施の形態を説明する図である。

【図5】本発明の実施の形態の容量電圧特性を示す図である。

【図6】従来のMIS型構造半導体装置の容量電圧特性を示す図である。

【図7】従来のMIS型電界効果トランジスタの構造を示す図である。

【図8】従来のMIS型電界効果トランジスタの製造方法を説明する図である。

【図9】従来のMIS型電界効果トランジスタの製造方法を説明する図である。

【符号の説明】

1 半導体基板

2 酸化ルテニウム膜

3 ホトレジスト

4 ゲート電極

5 絶縁層

6 ソース領域

7 ドレイン領域

8 ソース電極

9 ドレイン電極

10 半絶縁性GaAs基板

11 GaAsバッファ層

12 n型GaAsチャネル層

13 ノンドープAlGaAs層

14 n型GaAsコンタクト層

15 ゲート電極

16 ソース電極

17 ドレイン電極

18 シリコン半導体基板

19 ゲート酸化膜

20 金属膜

21 ホトレジスト

22 ゲート電極

23 ソース領域

24 ドレイン領域

25 ソース電極

26 ドレイン電極

【特許請求の範囲】

【請求項1】 半導体層表面に絶縁層を介して電極を備えた半導体装置において、前記半導体層と金属酸化物からなる前記電極との界面に、前記金属酸化物から解離した酸素を含む絶縁層を備えたことを特徴とする半導体装置。

【請求項2】 請求項1記載の半導体装置において、前記金属酸化物が酸化ルテニウムであることを特徴とする半導体装置。

【請求項3】 半導体層上に金属酸化物からなる電極を形成する工程と、前記金属酸化物の酸素を解離させ、該解離した酸素によって前記半導体層を酸化する熱処理を行ない、前記電極と前記半導体層との界面に絶縁層を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項4】 請求項3記載の半導体装置の製造方法において、前記金属酸化物が酸化ルテニウムであることを特徴とする半導体装置の製造方法。

【請求項1】 半導体層表面に絶縁層を介して電極を備えた半導体装置において、前記半導体層と金属酸化物からなる前記電極との界面に、前記金属酸化物から解離した酸素を含む絶縁層を備えたことを特徴とする半導体装置。

【請求項2】 請求項1記載の半導体装置において、前記金属酸化物が酸化ルテニウムであることを特徴とする半導体装置。

【請求項3】 半導体層上に金属酸化物からなる電極を形成する工程と、前記金属酸化物の酸素を解離させ、該解離した酸素によって前記半導体層を酸化する熱処理を行ない、前記電極と前記半導体層との界面に絶縁層を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項4】 請求項3記載の半導体装置の製造方法において、前記金属酸化物が酸化ルテニウムであることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2001−44428(P2001−44428A)

【公開日】平成13年2月16日(2001.2.16)

【国際特許分類】

【出願番号】特願平11−219550

【出願日】平成11年8月3日(1999.8.3)

【出願人】(000191238)新日本無線株式会社 (569)

【Fターム(参考)】

【公開日】平成13年2月16日(2001.2.16)

【国際特許分類】

【出願日】平成11年8月3日(1999.8.3)

【出願人】(000191238)新日本無線株式会社 (569)

【Fターム(参考)】

[ Back to top ]