半導体装置及びその製造方法

【課題】本発明はスティフナを用いて強度を高めた半導体装置及びその製造方法に関し、反りの発生を有効に抑制することを課題とする。

【解決手段】基板12と、この基板12にフリップチップ接合された半導体素子13と、基板12の半導体素子13の外周位置に配置された第1のスティフナ14と、基板上12の半導体素子13と第1のティフナ14との間に配設された補強樹脂15とを有する半導体装置において、補強樹脂15を補強する第2のスティフナ16を第2のスティフナ16内に配設する。

【解決手段】基板12と、この基板12にフリップチップ接合された半導体素子13と、基板12の半導体素子13の外周位置に配置された第1のスティフナ14と、基板上12の半導体素子13と第1のティフナ14との間に配設された補強樹脂15とを有する半導体装置において、補強樹脂15を補強する第2のスティフナ16を第2のスティフナ16内に配設する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に係り、特にスティフナを用いて強度を高めた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、絶縁フィルムを半導体装置の基板として使用し、これに半導体チップを搭載した構造の半導体装置が提供されている。この半導体装置は、細密配線化及び素子搭載時における低背化を図れる等の利点があるものの、絶縁フィルムを使用するために素子搭載後における半導体装置に反りが発生するという問題がある。このため、基板上にスティフナ(補強のための板)を配設することにより基板の剛性を高め、これにより半導体装置に反りが発生することを抑制することが行われている(特許文献1参照)。

【0003】

図1は、スティフナを有する第1従来例である半導体装置1Aを示している。基板2は絶縁フィルムよりなる薄型基板であり、その厚さは約0.7mm程度である。この基板2には、図示しない配線パターンが形成されている。また、半導体素子3は、この基板2の中央位置にフリップチップ接合されている。尚、図示しないが、基板2の背面側(半導体素子3の搭載面と反対面)には、はんだポール等の外部接続端子が設けられる。

【0004】

このように、薄い基板2の中央に半導体素子3が搭載されたのみで構成では、半導体素子3のフリップチップ接合時、及び半導体装置1Aを電子装置等に実装する際に、基板2に大きな反りが発生してしまう。このため、基板2の半導体素子3を囲繞する位置には、スティフナ4が配設されている。このスティフナ4は、基板2よりも剛性が高い金属材料である。よって、スティフナ4を配設することにより、基板2はスティフナ4に補強され、反りが発生することを抑制することができる。

【0005】

図2は、スティフナを有する第2従来例である半導体装置1Bを示している。図1に示した半導体装置1Aは、半導体素子3とスティフナ4との間が離間している。このため、基板2の半導体素子3とスティフナ4との間で反りが発生するおそれがある。

【0006】

そこで、図2に示す半導体装置1Bでは、半導体素子3とスティフナ4との間に、基板2を補強する補強樹脂5を配設した構成とている。これにより、図1に示した半導体装置1Aに比べ、半導体装置1Bに反りが発生することを抑制することができる。

【特許文献1】特開2000−133741号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

この図1及び図2に示された半導体装置1A,1Bは、電子装置等に実装された後、冷却するために半導体素子3の上面に冷却装置が配設される。この際、基板2に反りが存在すると、半導体装置1A,1Bのコプラナリティが低下し、よって冷却装置が適正に半導体素子13に装着されず半導体素子13の冷却を十分に行うことができないおそれがある。

【0008】

また、半導体装置1A,1Bを携帯電話等の小型低背化を要求される小型電子機器に搭載する場合には、この小型電子機器に搭載できないおそれがある。

【0009】

従来の半導体装置1A,1Bでは、スティフナ4や補強樹脂5を設けることにより、基板2の反りを有る程度は抑えることができるが、上記した冷却装置や小型電子機器に対応できる程度に基板2に発生する反りを抑制することができないという問題点があった。

【0010】

本発明は上記の点に鑑みてなされたものであり、反りの発生を有効に抑制しうる半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記の課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

【0012】

請求項1記載の発明は、

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とするものである。

【0013】

上記発明によれば、第2のスティフナにより補強樹脂が補強されるため、半導体素子の実装位置と第1のスティフナの配設位置との間で基板に反りが発生することを防止することができる。

【0014】

また、請求項2記載の発明は、

請求項1記載の半導体装置において、

前記第2のスティフナは、金属材料であることを特徴とするものである。

【0015】

また、請求項3記載の発明は、

請求項1又は2記載の半導体装置において、

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とするものである。

【0016】

上記発明によれば、第1のスティフナ及び第2のスティフナを配設しても半導体素子の上面を外部に開放されるため、半導体素子の冷却を行いやすくなる。

【0017】

また、請求項4記載の発明は、

請求項1乃至3のいずれか1項に記載の半導体装置において、

前記第2のスティフナは、前記基板から離間した構成であることを特徴とするものである。

【0018】

上記発明によれば、第2のスティフナは基板から離間した状態となるため、第2のスティフナは補強樹脂のみを補強することができる。

【0019】

また、請求項5記載の発明に係る半導体装置の製造方法は、

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とするものである。

【0020】

上記発明によれば、補強用樹脂を形成する工程において補強用樹脂内に第2のスティフナを配設することができるため、第2のスティフナを設けても製造工程が複雑になるようなことはない。

【発明の効果】

【0021】

本発明によれば、第2のスティフナにより補強樹脂が補強されるため、半導体素子の実装位置と第1のスティフナの配設位置との間で基板に反りが発生することを防止することができる。

【発明を実施するための最良の形態】

【0022】

次に、本発明を実施するための最良の形態について図面と共に説明する。

【0023】

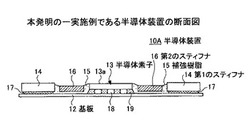

図3及び図4は、本発明の一実施例である半導体装置10Aを示している。図3は半導体装置10Aの断面図であり、図4は半導体装置10Aの平面図である。

【0024】

本実施例に係る半導体装置10Aは、大略すると基板12、半導体素子13、第1のスティフナ14、補強樹脂15、及び第2のスティフナ16等により構成されている。

【0025】

基板12は、ポリイミド等の絶縁性樹脂に銅により所定の配線パターン(図示せず)が形成された構成とされている。この基板12の厚さは0,1mm以上0.5mm以下の厚さとされており、よって基板12はプリント配線基板等に比べて極めて薄い基板とされている。このように、基板12を薄型化することにより、半導体装置10Aの薄型化及び配線パターンの高密度化を図ることができる。

【0026】

半導体素子13は、基板12の中央位置に搭載されている。本実施例では、半導体素子13を表面実装方法であるフリップチップ接続を用いて基板12に搭載している。これにより、半導体素子13の回路形成面に予め配設されたはんだバンプ18は、基板12に形成されたボンディングパッド(図示せず)に接続される。また、半導体素子13と基板12の間には、はんだバンプ18を保護するためにアンダーフィルレジン19が配設されている。

【0027】

第1のスティフナ14は、銅又はステンレス等の金属材料により形成されている。この第1のスティフナ14は、図4に示すように矩形で枠型形状を有している。また、第1のスティフナ14の外側の大きさは例えば□45mmで、内側(開口部分)の大きさは例えば□30mmとされている。この第1のスティフナ14は、接着剤17により基板12に固定される。よって、基板12は、第1のスティフナ14により、その反りが抑制される。しかしながら、この第1のスティフナ14のみだけでは、基板12に発生する反りを全て抑制することができないことは前述した通りである。

【0028】

補強樹脂15は、例えばエポキシ等の熱硬化性の樹脂である。この補強樹脂15は、半導体素子13と第1のスティフナ14との間に形成されている。このように、半導体素子13と第1のスティフナ14との間に補強樹脂15を形成することにより、基板12の半導体素子13と第1のスティフナ14との離間部分に発生する反りを抑制することができる。しかしながら、前記した第1のスティフナ14及び補強樹脂15を共に設けた構成でも、前述のように所望する程度に基板12に発生する反りを抑制することができなかった。

【0029】

第2のスティフナ16は、本実施例では第1のスティフナ14と同一材料により形成されている。即ち、第2のスティフナ16は、銅又はステンレス等の金属材料により形成されている。但し、第2のスティフナ16の材料は必ずしも第1のスティフナ14と同一材料とする必要はなく、後述するように補強樹脂15に必要とされる補強の程度に従い、適宜選定することが可能である。

【0030】

また、第2のスティフナ16は、半導体素子13と第1のスティフナ14との離間部分に配設されうる形状及び大きさとされている。本実施例では、図4に示すように、第2のスティフナ16は矩形で枠型の形状とされている。この第2のスティフナ16は、補強樹脂15内に配設された構成とされている。また、第2のスティフナ16が補強樹脂15内に配設された状態で、第2のスティフナ16の底面は基板12から離間した構成とされている。このため、第2のスティフナ16は、基板12を直接補強するのではなく、補強樹脂15のみを補強する構成となる。

【0031】

上記構成とされた半導体装置10Aは、第2のスティフナ16により補強樹脂15が補強されるため、半導体素子13の実装位置と第1のスティフナ14の配設位置との間で基板12に反りが発生することを防止することができる。

【0032】

図10は本発明者が実施した実験結果を示しており、半導体装置10Aに発生する反りを従来の半導体装置1A,1Bに発生する反りと共に示している。図10(A)に示すのは半導体装置1A(図1参照)に発生する反りを示しており、図10(B)に示すのは半導体装置1B(図2参照)に発生する反りを示しており、図10(C)は本実施例である半導体装置10A(図3及び図4参照)に発生する反りを示している。尚、図10(A)〜(C)で示す各特性は、いずれも同一の条件において発生したものである。また、図10では反りが発生した基板2,12を側面視した図である。

【0033】

いま、基板2,12に発生した反りの最上部と最下部の高さの差を反りの大きさ(ΔA〜ΔC)と定義すると、図10(A)に示す半導体装置1Aで発生する反りの大きさΔAは306.4μmであった。また、図10(B)に示す半導体装置1Bで発生する反りの大きさΔBは275.84μmであった。これに対し、本実施例に係る半導体装置10Aで発生する反りの大きさΔBは149.4μmであり、図10(A)に示した半導体装置1Aで発生する反りの大きさΔA(306.4μm)に比べ、約半分程度にまで反りの発生を抑制することができた。

【0034】

よって、本実施例に係る半導体装置10Aによれば、補強樹脂15内に第2のスティフナ16を設けることにより反りの発生を有効に抑制することができることが証明された。これにより、半導体装置10Aに冷却装置を搭載する場合でも確実な搭載が可能となり、また小型電子装置に対しても確実に搭載することが可能となる。

【0035】

また、本実施例では、第1のスティフナ14及び第2のスティフナ16の双方を矩形で枠型としたため、半導体素子13の上面13aは外部に露出した構成とされている。よって、第1及び第2のスティフナ15,16を設けた構成としても、半導体素子13の上面13aが外部に開放されるため、半導体素子13の冷却を行いやすくなる。また、冷却装置を半導体素子13の上面13aに装着することも、容易に行うことができる。

【0036】

尚、上記した実施例では、第2のスティフナ16を矩形で枠型の形状としたが、必ずしも第2のスティフナ16は矩形にする必要はなく、また枠型とする必要もない。例えば、半導体素子13と第1のスティフナ14の間において、特に応力が集中し反りが発生し易い部分がある場合には、その反りが発生し易い部位のみに第2のスティフナ16を設ける構成としてもよい。

【0037】

更に、第2のスティフナ16の補強樹脂15に対する補強の程度は、第2のスティフナ16の材質の特性(剛性、機械的強度等)及び形状(矩形、環状形状等)により変化する。このため、第2のスティフナ16の材質及び形状を適宜選定することにより、補強樹脂15(第2のスティフナ16が設けられた補強樹脂15)による基板12の補強の程度を調整することが可能となる。

【0038】

続いて、上記構成とされた半導体装置10Aの製造方法について説明する。図5乃至図9は、半導体装置10Aの製造方法の一実施例を説明するための図である。

【0039】

半導体装置10Aを製造するには、基板12を容易する(図5参照)。この基板12は、前記したようにポリイミドよりなる樹脂フィルムに、銅よりなる所定の配線パターンが形成された構成とされている。

【0040】

次に、第1のスティフナ14が基板12に配設される(図6参照)。第1のスティフナ14は銅又はステンレス等の金属材料であり、予め矩形で枠状の形状に成形されている。この第1のスティフナ14は、接着剤17を用いて基板12に固定される。

【0041】

次に、第1のスティフナ14が配設された基板12に半導体素子13を搭載する。具体的には、予め半導体素子13の回路形成面にはんだバンプ18を設けておき、これを基板12に形成されているボンディングパッド(図示せず)にフリップチップ接合する。また、半導体素子13が基板2に接合されると、続いて半導体素子13と基板12との間には、はんだバンプ18を保護するためにアンダーフィルレジン19が形成される(図7参照)。

尚、上記のフリップチップ接続に代えてワイヤボンディング接続を行うことも可能ではあるが、半導体装置10Aの薄型化を図る面からはフリップチップ接続の方が望ましい。

【0042】

次に、補強樹脂15が基板12上の半導体素子13と第1のスティフナ14との離間部分に形成される。この補強樹脂15は、例えばエポキシ樹脂を用いることができ、ポッティング等により上記離間部分に滴下される。このエポキシ樹脂は、その内部に強度を高めるための各種フィラーが混入されている。また、エポキシ樹脂は熱硬化性樹脂であり、熱硬化するまでの間は粘性を有した液状であるため、上記のようにポッティングを用いることができる。

【0043】

図8は、基板12上で半導体素子13と第1のスティフナ14との間に補強樹脂15が充填された状態を示している。この状態では、補強樹脂15は熱硬化されておらず、よって液状となっている。次に、この液状状態の補強樹脂15に対し、第2のスティフナ16を挿入する(図9参照)。この際、第2のスティフナ16が基板12に当接しないよう、即ち第2のスティフナ16が基板12から離間するよう、第2のスティフナ16を補強樹脂15内に挿入する。

【0044】

このようにして補強樹脂15内に第2のスティフナ16が装着されると、補強樹脂15を硬化するために加熱処理が行われ、これにより補強樹脂15が熱硬化すると共に第2のスティフナ16が補強樹脂15内に固定される。以上の工程を経ることにより、図3及び図4に示す半導体装置10Aが製造される。

【0045】

上記の製造方法によれば、補強用樹脂15を形成する工程において補強用樹脂15内に第2のスティフナ16を配設することができるため、第2のスティフナ16を設けても製造工程が複雑になるようなことはない。

【0046】

図11は、上記した実施例の変形例である半導体装置10Bを示している。本実施例に係る半導体装置10Bは、補強樹脂15内に装着される第2のスティフナ20のコーナ部分に面取り部20aを形成したことを特徴とするものである。

【0047】

補強樹脂15内に装着される第2のスティフナに角部が存在すると、この角部に応力集中が発生し、クラック等が発生するおそれがある。しかしながら、本変形例のように第2のスティフナ20に面取り部20aを形成することにより、応力集中が発生することを防止でき、半導体装置10Bの信頼性を高めることができる。

【0048】

以上の説明に関し、更に以下の項を開示する。

(付記1)

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とする半導体装置。

(付記2)

前記第2のスティフナは、金属材料であることを特徴とする付記1記載の半導体装置。

(付記3)

前記第2のスティフナは、銅又はステンレスよりなることを特徴とする付記2記載の半導体装置。

(付記4)

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とする付記1乃至3のいずれか1項に記載の半導体装置。

(付記5)

前記基板は、0,1mm以上0.5mm以下の厚さであることを特徴とする付記1乃至4のいずれか1項に記載の半導体装置。

(付記6)

前記第2のスティフナは、前記基板から離間した構成であることを特徴とする付記1乃至5のいずれか1項に記載の半導体装置。

(付記7)

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とする半導体装置の製造方法。

(付記8)

前記基板上の前記半導体素子と前記第1のスティフナとの間に先ず前記補強用樹脂を配設し、該補強用樹脂内に第2のスティフナを配設し、その後に前記補強用樹脂を硬化させることを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0049】

【図1】図1は、第1従来例である半導体装置の断面図である。

【図2】図2は、第2従来例である半導体装置の断面図である。

【図3】図3は、本発明の一実施例である半導体装置の断面図である。

【図4】図4は、本発明の一実施例である半導体装置の平面図である。

【図5】図5は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その1)

【図6】図6は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その2)

【図7】図7は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その3)

【図8】図8は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その4)

【図9】図9は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その5)

【図10】図10は、本発明の一実施例である半導体装置に発生する反りを従来と比較して示す図である。

【図11】図11は、図3及び図4に示す半導体装置の変形例を示す図である。

【符号の説明】

【0050】

10A,10B 半導体装置

12 基板

13 半導体素子

14 第1のスティフナ

15 補強樹脂

16 第2のスティフナ

19 アンダーフィルレジン

20 第2のスティフナ

20a 面取り部

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に係り、特にスティフナを用いて強度を高めた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、絶縁フィルムを半導体装置の基板として使用し、これに半導体チップを搭載した構造の半導体装置が提供されている。この半導体装置は、細密配線化及び素子搭載時における低背化を図れる等の利点があるものの、絶縁フィルムを使用するために素子搭載後における半導体装置に反りが発生するという問題がある。このため、基板上にスティフナ(補強のための板)を配設することにより基板の剛性を高め、これにより半導体装置に反りが発生することを抑制することが行われている(特許文献1参照)。

【0003】

図1は、スティフナを有する第1従来例である半導体装置1Aを示している。基板2は絶縁フィルムよりなる薄型基板であり、その厚さは約0.7mm程度である。この基板2には、図示しない配線パターンが形成されている。また、半導体素子3は、この基板2の中央位置にフリップチップ接合されている。尚、図示しないが、基板2の背面側(半導体素子3の搭載面と反対面)には、はんだポール等の外部接続端子が設けられる。

【0004】

このように、薄い基板2の中央に半導体素子3が搭載されたのみで構成では、半導体素子3のフリップチップ接合時、及び半導体装置1Aを電子装置等に実装する際に、基板2に大きな反りが発生してしまう。このため、基板2の半導体素子3を囲繞する位置には、スティフナ4が配設されている。このスティフナ4は、基板2よりも剛性が高い金属材料である。よって、スティフナ4を配設することにより、基板2はスティフナ4に補強され、反りが発生することを抑制することができる。

【0005】

図2は、スティフナを有する第2従来例である半導体装置1Bを示している。図1に示した半導体装置1Aは、半導体素子3とスティフナ4との間が離間している。このため、基板2の半導体素子3とスティフナ4との間で反りが発生するおそれがある。

【0006】

そこで、図2に示す半導体装置1Bでは、半導体素子3とスティフナ4との間に、基板2を補強する補強樹脂5を配設した構成とている。これにより、図1に示した半導体装置1Aに比べ、半導体装置1Bに反りが発生することを抑制することができる。

【特許文献1】特開2000−133741号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

この図1及び図2に示された半導体装置1A,1Bは、電子装置等に実装された後、冷却するために半導体素子3の上面に冷却装置が配設される。この際、基板2に反りが存在すると、半導体装置1A,1Bのコプラナリティが低下し、よって冷却装置が適正に半導体素子13に装着されず半導体素子13の冷却を十分に行うことができないおそれがある。

【0008】

また、半導体装置1A,1Bを携帯電話等の小型低背化を要求される小型電子機器に搭載する場合には、この小型電子機器に搭載できないおそれがある。

【0009】

従来の半導体装置1A,1Bでは、スティフナ4や補強樹脂5を設けることにより、基板2の反りを有る程度は抑えることができるが、上記した冷却装置や小型電子機器に対応できる程度に基板2に発生する反りを抑制することができないという問題点があった。

【0010】

本発明は上記の点に鑑みてなされたものであり、反りの発生を有効に抑制しうる半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記の課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

【0012】

請求項1記載の発明は、

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とするものである。

【0013】

上記発明によれば、第2のスティフナにより補強樹脂が補強されるため、半導体素子の実装位置と第1のスティフナの配設位置との間で基板に反りが発生することを防止することができる。

【0014】

また、請求項2記載の発明は、

請求項1記載の半導体装置において、

前記第2のスティフナは、金属材料であることを特徴とするものである。

【0015】

また、請求項3記載の発明は、

請求項1又は2記載の半導体装置において、

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とするものである。

【0016】

上記発明によれば、第1のスティフナ及び第2のスティフナを配設しても半導体素子の上面を外部に開放されるため、半導体素子の冷却を行いやすくなる。

【0017】

また、請求項4記載の発明は、

請求項1乃至3のいずれか1項に記載の半導体装置において、

前記第2のスティフナは、前記基板から離間した構成であることを特徴とするものである。

【0018】

上記発明によれば、第2のスティフナは基板から離間した状態となるため、第2のスティフナは補強樹脂のみを補強することができる。

【0019】

また、請求項5記載の発明に係る半導体装置の製造方法は、

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とするものである。

【0020】

上記発明によれば、補強用樹脂を形成する工程において補強用樹脂内に第2のスティフナを配設することができるため、第2のスティフナを設けても製造工程が複雑になるようなことはない。

【発明の効果】

【0021】

本発明によれば、第2のスティフナにより補強樹脂が補強されるため、半導体素子の実装位置と第1のスティフナの配設位置との間で基板に反りが発生することを防止することができる。

【発明を実施するための最良の形態】

【0022】

次に、本発明を実施するための最良の形態について図面と共に説明する。

【0023】

図3及び図4は、本発明の一実施例である半導体装置10Aを示している。図3は半導体装置10Aの断面図であり、図4は半導体装置10Aの平面図である。

【0024】

本実施例に係る半導体装置10Aは、大略すると基板12、半導体素子13、第1のスティフナ14、補強樹脂15、及び第2のスティフナ16等により構成されている。

【0025】

基板12は、ポリイミド等の絶縁性樹脂に銅により所定の配線パターン(図示せず)が形成された構成とされている。この基板12の厚さは0,1mm以上0.5mm以下の厚さとされており、よって基板12はプリント配線基板等に比べて極めて薄い基板とされている。このように、基板12を薄型化することにより、半導体装置10Aの薄型化及び配線パターンの高密度化を図ることができる。

【0026】

半導体素子13は、基板12の中央位置に搭載されている。本実施例では、半導体素子13を表面実装方法であるフリップチップ接続を用いて基板12に搭載している。これにより、半導体素子13の回路形成面に予め配設されたはんだバンプ18は、基板12に形成されたボンディングパッド(図示せず)に接続される。また、半導体素子13と基板12の間には、はんだバンプ18を保護するためにアンダーフィルレジン19が配設されている。

【0027】

第1のスティフナ14は、銅又はステンレス等の金属材料により形成されている。この第1のスティフナ14は、図4に示すように矩形で枠型形状を有している。また、第1のスティフナ14の外側の大きさは例えば□45mmで、内側(開口部分)の大きさは例えば□30mmとされている。この第1のスティフナ14は、接着剤17により基板12に固定される。よって、基板12は、第1のスティフナ14により、その反りが抑制される。しかしながら、この第1のスティフナ14のみだけでは、基板12に発生する反りを全て抑制することができないことは前述した通りである。

【0028】

補強樹脂15は、例えばエポキシ等の熱硬化性の樹脂である。この補強樹脂15は、半導体素子13と第1のスティフナ14との間に形成されている。このように、半導体素子13と第1のスティフナ14との間に補強樹脂15を形成することにより、基板12の半導体素子13と第1のスティフナ14との離間部分に発生する反りを抑制することができる。しかしながら、前記した第1のスティフナ14及び補強樹脂15を共に設けた構成でも、前述のように所望する程度に基板12に発生する反りを抑制することができなかった。

【0029】

第2のスティフナ16は、本実施例では第1のスティフナ14と同一材料により形成されている。即ち、第2のスティフナ16は、銅又はステンレス等の金属材料により形成されている。但し、第2のスティフナ16の材料は必ずしも第1のスティフナ14と同一材料とする必要はなく、後述するように補強樹脂15に必要とされる補強の程度に従い、適宜選定することが可能である。

【0030】

また、第2のスティフナ16は、半導体素子13と第1のスティフナ14との離間部分に配設されうる形状及び大きさとされている。本実施例では、図4に示すように、第2のスティフナ16は矩形で枠型の形状とされている。この第2のスティフナ16は、補強樹脂15内に配設された構成とされている。また、第2のスティフナ16が補強樹脂15内に配設された状態で、第2のスティフナ16の底面は基板12から離間した構成とされている。このため、第2のスティフナ16は、基板12を直接補強するのではなく、補強樹脂15のみを補強する構成となる。

【0031】

上記構成とされた半導体装置10Aは、第2のスティフナ16により補強樹脂15が補強されるため、半導体素子13の実装位置と第1のスティフナ14の配設位置との間で基板12に反りが発生することを防止することができる。

【0032】

図10は本発明者が実施した実験結果を示しており、半導体装置10Aに発生する反りを従来の半導体装置1A,1Bに発生する反りと共に示している。図10(A)に示すのは半導体装置1A(図1参照)に発生する反りを示しており、図10(B)に示すのは半導体装置1B(図2参照)に発生する反りを示しており、図10(C)は本実施例である半導体装置10A(図3及び図4参照)に発生する反りを示している。尚、図10(A)〜(C)で示す各特性は、いずれも同一の条件において発生したものである。また、図10では反りが発生した基板2,12を側面視した図である。

【0033】

いま、基板2,12に発生した反りの最上部と最下部の高さの差を反りの大きさ(ΔA〜ΔC)と定義すると、図10(A)に示す半導体装置1Aで発生する反りの大きさΔAは306.4μmであった。また、図10(B)に示す半導体装置1Bで発生する反りの大きさΔBは275.84μmであった。これに対し、本実施例に係る半導体装置10Aで発生する反りの大きさΔBは149.4μmであり、図10(A)に示した半導体装置1Aで発生する反りの大きさΔA(306.4μm)に比べ、約半分程度にまで反りの発生を抑制することができた。

【0034】

よって、本実施例に係る半導体装置10Aによれば、補強樹脂15内に第2のスティフナ16を設けることにより反りの発生を有効に抑制することができることが証明された。これにより、半導体装置10Aに冷却装置を搭載する場合でも確実な搭載が可能となり、また小型電子装置に対しても確実に搭載することが可能となる。

【0035】

また、本実施例では、第1のスティフナ14及び第2のスティフナ16の双方を矩形で枠型としたため、半導体素子13の上面13aは外部に露出した構成とされている。よって、第1及び第2のスティフナ15,16を設けた構成としても、半導体素子13の上面13aが外部に開放されるため、半導体素子13の冷却を行いやすくなる。また、冷却装置を半導体素子13の上面13aに装着することも、容易に行うことができる。

【0036】

尚、上記した実施例では、第2のスティフナ16を矩形で枠型の形状としたが、必ずしも第2のスティフナ16は矩形にする必要はなく、また枠型とする必要もない。例えば、半導体素子13と第1のスティフナ14の間において、特に応力が集中し反りが発生し易い部分がある場合には、その反りが発生し易い部位のみに第2のスティフナ16を設ける構成としてもよい。

【0037】

更に、第2のスティフナ16の補強樹脂15に対する補強の程度は、第2のスティフナ16の材質の特性(剛性、機械的強度等)及び形状(矩形、環状形状等)により変化する。このため、第2のスティフナ16の材質及び形状を適宜選定することにより、補強樹脂15(第2のスティフナ16が設けられた補強樹脂15)による基板12の補強の程度を調整することが可能となる。

【0038】

続いて、上記構成とされた半導体装置10Aの製造方法について説明する。図5乃至図9は、半導体装置10Aの製造方法の一実施例を説明するための図である。

【0039】

半導体装置10Aを製造するには、基板12を容易する(図5参照)。この基板12は、前記したようにポリイミドよりなる樹脂フィルムに、銅よりなる所定の配線パターンが形成された構成とされている。

【0040】

次に、第1のスティフナ14が基板12に配設される(図6参照)。第1のスティフナ14は銅又はステンレス等の金属材料であり、予め矩形で枠状の形状に成形されている。この第1のスティフナ14は、接着剤17を用いて基板12に固定される。

【0041】

次に、第1のスティフナ14が配設された基板12に半導体素子13を搭載する。具体的には、予め半導体素子13の回路形成面にはんだバンプ18を設けておき、これを基板12に形成されているボンディングパッド(図示せず)にフリップチップ接合する。また、半導体素子13が基板2に接合されると、続いて半導体素子13と基板12との間には、はんだバンプ18を保護するためにアンダーフィルレジン19が形成される(図7参照)。

尚、上記のフリップチップ接続に代えてワイヤボンディング接続を行うことも可能ではあるが、半導体装置10Aの薄型化を図る面からはフリップチップ接続の方が望ましい。

【0042】

次に、補強樹脂15が基板12上の半導体素子13と第1のスティフナ14との離間部分に形成される。この補強樹脂15は、例えばエポキシ樹脂を用いることができ、ポッティング等により上記離間部分に滴下される。このエポキシ樹脂は、その内部に強度を高めるための各種フィラーが混入されている。また、エポキシ樹脂は熱硬化性樹脂であり、熱硬化するまでの間は粘性を有した液状であるため、上記のようにポッティングを用いることができる。

【0043】

図8は、基板12上で半導体素子13と第1のスティフナ14との間に補強樹脂15が充填された状態を示している。この状態では、補強樹脂15は熱硬化されておらず、よって液状となっている。次に、この液状状態の補強樹脂15に対し、第2のスティフナ16を挿入する(図9参照)。この際、第2のスティフナ16が基板12に当接しないよう、即ち第2のスティフナ16が基板12から離間するよう、第2のスティフナ16を補強樹脂15内に挿入する。

【0044】

このようにして補強樹脂15内に第2のスティフナ16が装着されると、補強樹脂15を硬化するために加熱処理が行われ、これにより補強樹脂15が熱硬化すると共に第2のスティフナ16が補強樹脂15内に固定される。以上の工程を経ることにより、図3及び図4に示す半導体装置10Aが製造される。

【0045】

上記の製造方法によれば、補強用樹脂15を形成する工程において補強用樹脂15内に第2のスティフナ16を配設することができるため、第2のスティフナ16を設けても製造工程が複雑になるようなことはない。

【0046】

図11は、上記した実施例の変形例である半導体装置10Bを示している。本実施例に係る半導体装置10Bは、補強樹脂15内に装着される第2のスティフナ20のコーナ部分に面取り部20aを形成したことを特徴とするものである。

【0047】

補強樹脂15内に装着される第2のスティフナに角部が存在すると、この角部に応力集中が発生し、クラック等が発生するおそれがある。しかしながら、本変形例のように第2のスティフナ20に面取り部20aを形成することにより、応力集中が発生することを防止でき、半導体装置10Bの信頼性を高めることができる。

【0048】

以上の説明に関し、更に以下の項を開示する。

(付記1)

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とする半導体装置。

(付記2)

前記第2のスティフナは、金属材料であることを特徴とする付記1記載の半導体装置。

(付記3)

前記第2のスティフナは、銅又はステンレスよりなることを特徴とする付記2記載の半導体装置。

(付記4)

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とする付記1乃至3のいずれか1項に記載の半導体装置。

(付記5)

前記基板は、0,1mm以上0.5mm以下の厚さであることを特徴とする付記1乃至4のいずれか1項に記載の半導体装置。

(付記6)

前記第2のスティフナは、前記基板から離間した構成であることを特徴とする付記1乃至5のいずれか1項に記載の半導体装置。

(付記7)

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とする半導体装置の製造方法。

(付記8)

前記基板上の前記半導体素子と前記第1のスティフナとの間に先ず前記補強用樹脂を配設し、該補強用樹脂内に第2のスティフナを配設し、その後に前記補強用樹脂を硬化させることを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0049】

【図1】図1は、第1従来例である半導体装置の断面図である。

【図2】図2は、第2従来例である半導体装置の断面図である。

【図3】図3は、本発明の一実施例である半導体装置の断面図である。

【図4】図4は、本発明の一実施例である半導体装置の平面図である。

【図5】図5は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その1)

【図6】図6は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その2)

【図7】図7は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その3)

【図8】図8は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その4)

【図9】図9は、本発明の一実施例である半導体装置の製造方法を説明するための図である(その5)

【図10】図10は、本発明の一実施例である半導体装置に発生する反りを従来と比較して示す図である。

【図11】図11は、図3及び図4に示す半導体装置の変形例を示す図である。

【符号の説明】

【0050】

10A,10B 半導体装置

12 基板

13 半導体素子

14 第1のスティフナ

15 補強樹脂

16 第2のスティフナ

19 アンダーフィルレジン

20 第2のスティフナ

20a 面取り部

【特許請求の範囲】

【請求項1】

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とする半導体装置。

【請求項2】

前記第2のスティフナは、金属材料であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記第2のスティフナは、前記基板から離間した構成であることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とする半導体装置の製造方法。

【請求項1】

基板と、

該基板に表面実装された半導体素子と、

前記基板の前記半導体素子の外周位置に配置された第1のスティフナと、

前記基板上の前記半導体素子と前記第1のティフナとの間に配設された補強樹脂とを有する半導体装置において、

前記補強樹脂を補強する第2のスティフナを配設したことを特徴とする半導体装置。

【請求項2】

前記第2のスティフナは、金属材料であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第1のスティフナ及び第2のスティフナは、前記半導体素子の上面を外部に開放してなる構成であることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記第2のスティフナは、前記基板から離間した構成であることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

基板に第1のスティフナを接着する工程と、

該第1のスティフナが接着された前記基板上に半導体素子を表面実装する工程と、

前記基板上の前記半導体素子と前記第1のスティフナとの間に補強用樹脂を形成する工程とを有し、

前記基板上の前記半導体素子と前記第1のスティフナとの間に前記補強用樹脂を形成する工程において、該補強用樹脂内に第2のスティフナを配設することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2007−227550(P2007−227550A)

【公開日】平成19年9月6日(2007.9.6)

【国際特許分類】

【出願番号】特願2006−45625(P2006−45625)

【出願日】平成18年2月22日(2006.2.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成19年9月6日(2007.9.6)

【国際特許分類】

【出願日】平成18年2月22日(2006.2.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]