半導体装置及びその製造方法

【課題】微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能な半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に絶縁膜を介して形成された第1のゲート電極と、前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、を具備する。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に絶縁膜を介して形成された第1のゲート電極と、前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に係り、特に、シリサイドを用いた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年の微細化された半導体装置、特にMIS(metal insulator semiconductor)型のFET(field effect transistor)装置では、高速化、低消費電力化等の半導体装置の特性を向上させることが要求されている。半導体装置の高速化のためには、構成素子の電流駆動力を向上させることが必要である。これまでの半導体素子では、ゲート長の縮小に伴い電流駆動力は向上されてきたが、近年の微細化の進行に伴いゲート長の縮小だけでは電流駆動力の十分な向上が見込めなくなってきている。したがって、他の手法により電流駆動力を向上させることが求められてきており、例えば、FETのチャネル領域に応力を与えることによりキャリアの移動度を向上させる手法が用いられるようになってきている。

【0003】

CMOS(complimentary metal oxide semiconductor)半導体装置では、nチャネルMOSFET(以降、nMOSと表す)とpチャネルMOSFET(以降、pMOSと表す)とにおいて、それぞれのチャネル領域に逆向きの応力を与えることにより、半導体装置の電流駆動力を向上できることが知られている。

【0004】

従来のCMOS半導体装置では、素子の寄生抵抗を低減するために、nMOS及びpMOSのソース・ドレインのコンタクト領域表面にシリサイドを形成している。このシリサイドには、例えば、チタンシリサイド(TiSi2)、コバルトシリサイド(CoSi2)、ニッケルシリサイド(NiSi)が使用されている。これらのシリサイドは、いずれもシリコンに対して引っ張りの内部応力を有することが知られている。

【0005】

これらのシリサイドをMOSFETのソース・ドレインのコンタクト領域表面に形成した場合に、シリサイド直下のソース・ドレイン(シリコン基板)には、圧縮応力が与えられ、シリサイドの横方向に設けられたMOSFETのチャネル領域には、引っ張り応力が与えられる。引っ張り応力がチャネル領域に与えられると、nMOSではチャネルを流れるキャリア(電子)の移動度が大きくなり、電流駆動力の向上に寄与する。しかしながら、pMOSでは、チャネルを流れるキャリアは正孔であり、その移動度が小さくなるため、駆動電流が減少してしまうという問題を引き起こす。正孔の移動度を向上させるためには、圧縮応力を与えることが必要である。

【0006】

したがって、nMOSのチャネル領域には引っ張り応力を、pMOSには逆向きの圧縮応力をそれぞれ与えることにより、電流駆動力の向上が実現される。

【0007】

シリサイドを形成するための従来のサリサイド技術では、使用するシリサイドの種類によってシリコン基板に与えられる応力の方向は、一義的に決まってしまう。したがって、1種類のシリサイドを使用する場合には、上記のように、nMOS又はpMOSの一方の電流駆動力を向上できるが、他方の電流駆動力を低下させてしまうという問題点がある。2種類のシリサイドを使用するデュアルシリサイド構造にすることにより、nMOSとpMOSの両者にそれぞれ所望の方向の応力を与えることが可能になるが、製造プロセスが極めて複雑になるとうい問題がある。

【0008】

これらの問題を解決するために、特許文献1には、ソース/ドレインに1種類のシリサイドを形成後、引っ張り応力を有する第1のシリコン窒化膜(Si3N4膜)をnMOS領域に形成し、圧縮応力を有する第2のSi3N4膜をpMOS領域に形成する技術が、開示されている。これらのSi3N4膜によりnMOSとpMOSのチャネル領域に与えられる応力を逆向きに制御して、それぞれの電流駆動力を向上させている。この第1及び第2のSi3N4膜は、異なる製造方法により形成されるため、製造プロセスが複雑になる。また、第1及び第2のSi3N4膜が接する界面領域における応力の問題等、新たな問題が生ずる。

【特許文献1】特開2003−60076号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の目的は、微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能なCMOS半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0010】

上記の課題は、以下の本発明に係る半導体装置及びその製造方法によって解決される。

【0011】

本発明の1態様による半導体装置は、半導体基板上に絶縁膜を介して形成された第1のゲート電極と、前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、を具備する。

【0012】

本発明の他の1態様による半導体装置の製造方法は、半導体基板中に第1及び第2の半導体領域を形成する工程と、前記第1の半導体領域上に絶縁膜を介して第1のゲート電極を形成し、前記第2の半導体領域上に絶縁膜を介して第2のゲート電極を形成する工程と、前記第1のゲート電極を挟む前記半導体基板中に第1の拡散層を形成し、前記第2のゲート電極を挟む前記半導体基板中に第2の拡散層を形成する工程と、前記第1及び第2の拡散層に接触させて金属材料を堆積する工程と、第1のアニールにより前記金属材料と前記半導体基板とを反応させて前記第1及び第2の拡散層上に第1方向の内部応力を内在する第1相の第1及び第2の導電体層をそれぞれ形成する工程と、前記第2の半導体領域上に前記第1方向とは逆向きの第2方向の内部応力を内在する応力制御膜を形成する工程と、第2のアニールにより第1の半導体領域に前記第1方向の内部応力を内在する第2相の第1の導電体層を形成し、第2の半導体領域に前記第2方向の内部応力を内在する第2相の第2の導電体層を形成する工程と、を具備する。

【発明の効果】

【0013】

本発明により、微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能なCMOS半導体装置及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0014】

本発明の実施形態を、添付した図面を参照して以下に詳細に説明する。図では、対応する部分は、対応する参照符号で示している。以下の実施形態は、一例として示されたもので、本発明の精神から逸脱しない範囲で種々の変形をして実施することが可能である。

【0015】

本発明によれば、nMOSではそのチャネル領域に引っ張り応力を与えるシリサイド層を具備し、pMOSではそのチャネル領域に圧縮応力を与えるシリサイド層を具備する半導体装置及びその製造方法が提供される。上記のシリサイド層は、同じ元素により構成された1種類のシリサイドであり、従来の2種類のシリサイドを用いるデュアルシリサイドとは異なる。

【0016】

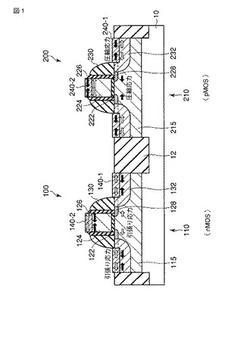

本発明の一実施形態の半導体装置の断面構造の一例を図1に示す。本実施形態の半導体装置は、nMOS100とpMOS200とにおいて同じ元素により構成されたシリサイド層140、240を有するが、シリサイドを形成するサリサイド工程において、それぞれが逆向きの内部応力を内在するようにシリサイド層140、240を形成したものである。図中に示した矢印は、内部応力の方向を表しており、外向きの矢印は、引っ張り応力を、内向きの矢印は、圧縮応力を表す。

【0017】

図1において、nMOS100では、ソース・ドレインのコンタクト領域132及びゲート電極124上に形成されたシリサイド層140−1,140−2は、引っ張りの内部応力を有する。周囲の応力を考慮する上で、シリサイド層140が引っ張り応力を有するということは、概念的に、シリコン基板10よりも小さな体積のシリサイド層140を埋め込んだことに相当する。したがって、シリサイド層140−1直下のシリコン基板10には、シリサイド層140−1とは逆向きの圧縮応力が与えられる。ところが、2つのシリサイド層140−1挟まれた、ゲート電極124直下のチャネル領域には、シリサイド層140−1と同じ向きの引っ張り応力が与えられる。

【0018】

一方、pMOS200では、ソース・ドレインのコンタクト領域232及びゲート電極224上に形成されたシリサイド層240−1,240−2は、nMOS100とは反対の圧縮の内部応力を有する。シリサイド層240が圧縮応力を有するということは、概念的に、シリコン基板10よりも大きな体積のシリサイド層240を埋め込んだことに相当する。同様に、このシリサイド層240−1の圧縮応力により、ゲート電極224直下のチャネル領域には、圧縮応力が与えられる。

【0019】

したがって、nMOSでは、チャネルにおける電子の移動度を改善でき、pMOSでは、正孔の移動度を改善できるため、半導体装置の電流駆動力を向上できる。

【0020】

nMOSとpMOSのシリサイド層140,240の内部応力は、下記に詳細に説明するように、シリサイド層を形成するサリサイド工程において、両者が逆向きの内部応力を持つように作り分けることができる。

【0021】

本発明の一実施形態の基本的な概念を図2に示した断面図を参照して、詳細に説明する。本実施形態の半導体装置は、2段階のシリサイド形成アニールを含むサリサイド工程を経て製造される。まず、図2(a)に示したように、シリコン基板10の表面にシリサイド用金属膜34、例えば、ニッケル(Ni)を堆積して第1のシリサイド化アニールを行う。第1のアニールは、完全にシリサイド化が行われないような低温、短時間のアニールである。第1のアニール後に、未反応のシリサイド用金属膜34を除去する。第1のアニールにより、図2(b)に示されたように、シリコン基板10表面には、第1相のシリサイド層36が形成される。第1相のシリサイド層36は、例えば、NixSi(1<x<2)の組成を有する中間段階のシリサイド層であり、引っ張りの内部応力を有する(図では、引っ張り応力を外向きの矢印で示している)。

【0022】

次に、図2(c)に示したように、第1相のシリサイド層36とは逆向きの内部応力(図では圧縮応力)を有する応力制御膜38を、第1相のシリサイド層36の一部の表面上に形成する(図では、圧縮内部応力を内向きの矢印で示している)。応力制御膜38の内部応力は、第1相のシリサイド層36の内部応力よりも大きな絶対値を有するように選択する。図2の例では、応力制御膜38として、大きな圧縮応力を有する窒化チタン膜(TiN膜)を使用している。

【0023】

その後、第2のシリサイド化アニールを行う。第2のアニールは、サーマルバジェットが、第1のアニールより大きなアニールである。第2のアニールにより第1相のシリサイド層36の金属が充分にシリコンと反応して第2相のシリサイド層40を形成する。すなわち、第2相のシリサイド層40は、例えば、NiSiの組成を有するモノシリサイドである。

【0024】

第2相のシリサイド層40の内部応力は、第2のアニール時の応力制御膜38の有無により制御することができる。

【0025】

応力制御膜38を形成しないで第2のアニールを行う場合には、図2(d)に示したように、第2相のシリサイド層40は、第1相のシリサイド層36よりもさらに大きな引っ張り応力を内部応力として有する。

【0026】

ところが、大きな圧縮応力を有する応力制御膜38を形成した状態で第2のアニールを行うと、図2(e)に示したように、この圧縮応力がシリサイド化反応中にシリサイド層内に凍結されて、圧縮応力を有する第2相のシリサイド層40’が形成される。

【0027】

このようにして、シリサイド層の内部応力の向きを制御することができる。

【0028】

本発明をCMOS半導体装置に応用した実施形態を、下記に説明する。チャネル中のキャリア移動度を大きくするためには、nMOSではチャネルに引っ張り応力を、pMOSでは圧縮応力を与えることが必要である。そこでソース/ドレインのコンタクト領域に、例えば、本来は引っ張り応力を有するシリサイドを形成する際に、pMOSにだけ大きな、例えば、圧縮応力を有する応力制御膜38を形成した状態で、第2のアニールを行う。その結果、pMOSのソース/ドレインのコンタクト領域に形成したシリサイド層には、圧縮の内部応力が凍結され、nMOSのシリサイド層には、引っ張りの内部応力が発生する。したがって、pMOSのチャネル領域には、圧縮応力を与えることができ、nMOSには、引っ張り応力を与えることができる。すなわち、互いに逆向きの内部応力を有するシリサイド層を同時に形成することが可能である。

【0029】

上記のように、互いに逆向きの内部応力を有するシリサイド層を形成することにより、nMOS及びpMOSにおいて、チャネル領域のキャリア移動度をそれぞれ向上させることができる。具体的には、nMOSではチャネル領域に引っ張り応力を与えることにより、チャネル領域の電子の移動度を向上でき、pMOSではチャネル領域に圧縮応力を与えることにより、チャネル領域の正孔の移動度を向上させることができる。これにより、nMOS,pMOSそれぞれの電流駆動力を向上できる。また、上記のシリサイド層は、本来の目的であるソース/ドレインの寄生抵抗を低減する。その結果、CMOS半導体装置の電流駆動力はnMOS、pMOSの各々に対して向上させることが可能となり、素子の性能を向上させることができる。さらに、本発明は、上記のように、サリサイド工程の途中に応力制御膜の形成を追加するだけで実現でき、製造プロセスは簡略である。

【0030】

以下に本実施形態の製造プロセスの一例を、図3から図6に示した工程断面図を参照して説明する。

【0031】

(1)先ず、図3(a)を参照して、半導体基板10、例えば、シリコン基板、に素子分離12を形成する。素子分離12は、例えば、シリコン基板10に浅い溝を形成し、その中をCVD(chemical vapor deposition)により形成したシリコン酸化膜(SiO2膜)で埋めたSTI(shallow trench isolation)を使用することができる。

【0032】

次に、nMOSを形成するnMOS領域110にp型不純物を深くドープしてp−ウェル115を、pMOSを形成するpMOS領域210にn型不純物を深くドープしてn−ウェル215を形成する。p型不純物としては、例えば、ホウ素(B)を使用することができ、n型不純物としては、例えば、リン(P)を使用することができる。

【0033】

その後、全面にゲート絶縁膜22を形成し、その上に導電体膜24を堆積する。ゲート絶縁膜22としては、例えば、SiO2膜、シリコン酸窒化膜(SiON膜)、を使用することができる。導電体膜24としては、例えば、ノンドープ若しくはリン又はホウ素を高濃度にドープした多結晶シリコンを使用することができる。

【0034】

そして、この積層膜をリソグラフィ及びエッチングによりパターニングして、ゲート電極124,224を形成する。

【0035】

(2)次に、ゲート電極124、224を覆うように全面に第1の絶縁膜26を形成する。第1の絶縁膜26としては、例えば、膜厚が2−10nmのシリコン窒化膜(Si3N4膜)を使用することができる。第1の絶縁膜26を異方性エッチングして、図3(b)に示したように、ゲート電極124,224の側面にのみ第1の絶縁膜26を残して、オフセットスペーサ126,226を形成する。ゲート電極124,224及びオフセットスペーサ126,226をマスクとして、イオン注入を行う。nMOS領域110には、n型不純物、例えば、ヒ素(As)をドープして、第1の拡散層128を形成し、pMOS領域210には、p型不純物、例えば、ホウ素(B)をドープして、第2の拡散層228を形成する。第1及び第2の拡散層128,228は、ソース/ドレインのエクステンションになる。

【0036】

(3)次に、オフセットスペーサ126,226を含むゲート電極124、224を覆うように全面に第2の絶縁膜30を形成する。第2の絶縁膜30としては、例えば、Si3N4膜を使用することができる。第2の絶縁膜30を異方性エッチングして、図4(a)に示したように、オフセットスペーサ126,226の側面にのみ第2の絶縁膜30を残して、ゲート側壁130,230を形成する。ゲート電極124,224及びゲート側壁130,230をマスクとして、第1及び第2の拡散層より深く高濃度のイオン注入を行う。nMOS領域110には、n型不純物、例えば、ヒ素(As)をドープして、第3の拡散層132を形成し、pMOS領域210には、p型不純物、例えば、ホウ素(B)をドープして、第4の拡散層232を形成する。第3及び第4の拡散層132,232は、ソース/ドレインのコンタクト領域になる。

【0037】

上記の工程(2)、(3)の第1と第3の拡散層128,132及び第2と第4の拡散層228,232のイオン注入時に、ゲート電極124,224にも同時にドーパントが導入される。

【0038】

(4)次に、図4(b)に示したように、ゲート電極124,224を覆って全面にシリサイド用金属膜34を形成する。シリサイド用金属34としては、例えば、膜厚が約10nmのニッケル(Ni)、コバルト(Co)、チタン(Ti)等を使用することができる。

【0039】

(5)その後、第1のシリサイド化アニールを行う。第1のシリサイド化アニールは、完全にシリサイド化が行われないような低温、短時間のアニールであり、例えば、350℃程度のRTA(rapid thermal annealing)である。この第1のアニールにより、図5(a)に示したように、シリサイド用金属膜34と接しているソース/ドレイン・コンタクト領域132,232及びゲート電極124,224の上面のシリコンが反応して第1相のシリサイド層136−1,236−1及び136−2,236−2が形成される。シリサイド用金属34としてNiを使用する場合、第1相のシリサイド層は、例えば、NixSi(1<x<2)の組成を有する中間的なシリサイドである。このシリサイド層は、図に外向きの矢印で示したように、引っ張りの内部応力を有する。第1のアニール時に、素子分離12上や、Si3N4膜のゲート側壁130,230上に堆積したシリサイド用金属は、反応せず、そこにはシリサイド層を形成しない。

【0040】

その後、硫酸過酸化水素水混合液やアンモニア過酸化水素水混合液等のエッチング液を用いて未反応のシリサイド用金属、例えば、Ni膜をエッチングして除去する。このとき第1相のシリサイド層136,236は、これらのエッチング液ではエッチングされずにそのまま残る。

【0041】

(6)次に、図5(b)に示したように、ゲート電極124,224を覆うように全面に応力制御膜38を形成する。そして、nMOS領域110上の応力制御膜38をリソグラフィ及びエッチングにより除去して、pMOS領域210上だけを応力制御膜38でキャップする。応力制御膜38は、第1相のシリサイド層136、236とは逆向きの内部応力を有し、内部応力の絶対値が大きな膜である。第1相のシリサイド層が、例えば、NixSi(引っ張り応力を有する)の場合には、圧縮応力(図では内向きの矢印)を有する膜、例えば、窒化チタン膜(TiN膜)を使用することができる。TiN膜38の選択的なエッチングには、例えば、過酸化水素水(H2O2)を使用することができる。

【0042】

(7)その後、第2のシリサイド化アニールを行う。第2のアニールは、第1相のシリサイド層136、236が充分にシリコンと反応するように行う。例えば、500℃程度のRTAであり、第2のアニールのサーマルバジェットは、第1のアニールよりも大きい。図6に示したように、この第2のアニールより、第1相のシリサイド層136,236(例えば、NixSi(1<x<2))は、第2相のシリサイド層140、240(例えば、ニッケルモノシリサイド(NiSi))に変化する。

【0043】

上記で使用する応力制御膜38、例えば、TiN膜は、安定な膜であるため、このアニールではシリサイド層とは反応しない。したがって、nMOS及びpMOSのシリサイド層140及び240の両者は、同じ元素により構成される。

【0044】

このようにして形成したnMOSとpMOSのシリサイド層140と240は、互いに逆向きの内部応力を有する。すなわち、応力制御膜38を形成しないで第2のアニールを行ったnMOS100では、第2相のシリサイド層140は、第1相のシリサイド層136よりもさらに大きな引っ張り応力を内部応力として内在する。ところが、大きな圧縮応力を有する応力制御膜38を形成した状態で第2のアニールを行ったpMOS200では、この圧縮応力がシリサイド化反応中にシリサイド層240内に凍結されて、圧縮応力を内在する第2相のシリサイド層240−1,240−2が形成される。

【0045】

第2のアニール後に、応力制御膜38を除去して、図6に示した構造を完成する。

【0046】

その後、図示しないが、第3及び第4の拡散層132,232上のシリサイド層140−1,240−1、及びゲート電極124,224上のシリサイド層140−2,240−2に接続する配線を形成する。さらに、多層配線等の半導体装置に必要な工程を行って、nMOS及びpMOSのそれぞれのシリサイド層を所望の向きの応力に制御し、素子特性を向上させたCMOS半導体装置を完成する。

【0047】

上記の第2のアニール時に、上記で説明したように、本来のシリサイド層の応力とは逆向きの内部応力を有する応力制御膜38でキャップしたpMOS領域210では、そこに形成される第2相のシリサイド層240−1,240−2が、応力制御膜38と同じ圧縮内部応力を内在するようにシリサイド化される。一方、nMOS領域110では、第2相のシリサイド層140−1,140−2は、本来の引っ張り内部応力を内在する。

【0048】

シリサイド層240−1が、圧縮応力を有するpMOSでは、隣接するチャネル領域にも圧縮応力が与えられる。同様に、シリサイド層140−1が、引っ張り応力を有するnMOSでは、隣接するチャネル領域にも引っ張り応力が与えられる。

【0049】

上記に例示したシリサイド用金属、ニッケル(Ni),コバルト(Co),チタン(Ti)によるシリサイド、ニッケルシリサイド(NiSi),コバルトシリサイド(CoSi2),チタンシリサイド(TiSi2)は、いずれも本来引っ張り応力を内在する。したがって、応力制御膜として大きな圧縮応力を有する上記のTiN膜を使用して、pMOSとnMOSとにおいて応力を逆向きに制御することができる。

【0050】

本実施形態において、シリサイド材料としてニッケルシリサイド(NiSi)を例に挙げたが、本発明はこれらの材料に限定するものではなく、シリサイド材料としては、上記のTiSi2、CoSi2の他に、例えば、プラチナシリサイド(PtSi)、パラジウムシリサイド(PdSi)、エルビウムシリサイド(ErSi2)のような、種々の金属シリサイドを用いることができる。

【0051】

またシリサイド層の内部応力の方向を制御する材料として、膜の内部応力が圧縮応力である窒化チタン膜を例に挙げたが、この材料についても窒化チタン膜に限定する必要はなく、同様にシリサイド層とは逆向きの内部応力を持つその他の導体膜、半導体膜、絶縁膜を用いることも可能である。

【0052】

本実施形態において、pMOS領域上にのみ圧縮内部応力を有する窒化チタン膜を堆積し第2のアニールによりシリサイド化を行った。これに加えて、nMOS領域上にも強い引っ張り応力を有する第2の応力制御膜を堆積し、nMOS上に形成されるシリサイド層の内部応力をさらに大きな引っ張り応力とすることができる。これにより、チャネル領域に加わる引っ張り応力をさらに大きくすることで、nMOSの素子性能をさらに向上させることも可能である。なおこれらの応力制御膜は、シリサイド化のための第2のアニール後に、除去される。

【0053】

上記のように、互いに逆向きの内部応力を有するシリサイド層を形成することにより、nMOS及びpMOSにおいて、チャネル領域のキャリア移動度をそれぞれ向上させることができる。すなわち、nMOSではチャネル領域に引っ張り応力を与えることにより、チャネル領域の電子の移動度を向上でき、pMOSではチャネル領域に圧縮応力を与えることにより、チャネル領域の正孔の移動度を向上させることができる。これにより、nMOS,pMOSそれぞれの電流駆動力を向上できる。また、上記のシリサイド層は、本来の目的であるソース/ドレインの寄生抵抗を低減する。その結果、MOSFET素子の電流駆動力はnMOSFET領域、pMOSFET領域各々に対して向上させることが可能となり、素子の性能を向上させることができる。さらに、本発明は、上記のように、サリサイド工程の途中に応力制御膜の形成を追加するだけで実現でき、製造プロセスは簡略である。

【0054】

本発明は、微細化された半導体装置の性能を向上に有効であり、特にゲート長が0.1μm以下のCMOS半導体装置の性能を向上させることができる。

【0055】

本発明は、上記の実施形態に限定されることなく、本発明の精神及び範囲から逸脱しないで、種々の変形を行って実施することができる。それゆえ、本発明は、ここに開示された実施形態に制限することを意図したものではなく、発明の趣旨を逸脱しない範囲において他の実施形態にも適用でき、広い範囲に適用されるものである。

【図面の簡単な説明】

【0056】

【図1】図1は、本発明の一実施形態の半導体装置を説明するために示す断面図である。

【図2】図2(a)から(e)は、本発明の一実施形態の原理を説明するために示す断面図である。

【図3】図3(a),(b)は、本実施形態にしたがった半導体装置の製造工程の一例を説明するために示す断面図である。

【図4】図4(a),(b)は、図3(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【図5】図5(a),(b)は、図4(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【図6】図6は、図5(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【符号の説明】

【0057】

100…nMOS,200…pMOS,10…半導体基板(シリコン基板),12…素子分離,24…導電体膜,26…第1の絶縁膜,30…第2の絶縁膜,34…シリサイド用金属,38…応力制御膜,110…nMOS領域,210…pMOS領域,115,215…ウェル,22,122,222…ゲート絶縁膜,124,224…ゲート電極,126,226…オフセットスペーサ,128…第1の拡散層,228…第2の拡散層,130,230…ゲート側壁,132…第3の拡散層,232…第4の拡散層,136,236…第1相のシリサイド層,140,240…第2相のシリサイド層。

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に係り、特に、シリサイドを用いた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年の微細化された半導体装置、特にMIS(metal insulator semiconductor)型のFET(field effect transistor)装置では、高速化、低消費電力化等の半導体装置の特性を向上させることが要求されている。半導体装置の高速化のためには、構成素子の電流駆動力を向上させることが必要である。これまでの半導体素子では、ゲート長の縮小に伴い電流駆動力は向上されてきたが、近年の微細化の進行に伴いゲート長の縮小だけでは電流駆動力の十分な向上が見込めなくなってきている。したがって、他の手法により電流駆動力を向上させることが求められてきており、例えば、FETのチャネル領域に応力を与えることによりキャリアの移動度を向上させる手法が用いられるようになってきている。

【0003】

CMOS(complimentary metal oxide semiconductor)半導体装置では、nチャネルMOSFET(以降、nMOSと表す)とpチャネルMOSFET(以降、pMOSと表す)とにおいて、それぞれのチャネル領域に逆向きの応力を与えることにより、半導体装置の電流駆動力を向上できることが知られている。

【0004】

従来のCMOS半導体装置では、素子の寄生抵抗を低減するために、nMOS及びpMOSのソース・ドレインのコンタクト領域表面にシリサイドを形成している。このシリサイドには、例えば、チタンシリサイド(TiSi2)、コバルトシリサイド(CoSi2)、ニッケルシリサイド(NiSi)が使用されている。これらのシリサイドは、いずれもシリコンに対して引っ張りの内部応力を有することが知られている。

【0005】

これらのシリサイドをMOSFETのソース・ドレインのコンタクト領域表面に形成した場合に、シリサイド直下のソース・ドレイン(シリコン基板)には、圧縮応力が与えられ、シリサイドの横方向に設けられたMOSFETのチャネル領域には、引っ張り応力が与えられる。引っ張り応力がチャネル領域に与えられると、nMOSではチャネルを流れるキャリア(電子)の移動度が大きくなり、電流駆動力の向上に寄与する。しかしながら、pMOSでは、チャネルを流れるキャリアは正孔であり、その移動度が小さくなるため、駆動電流が減少してしまうという問題を引き起こす。正孔の移動度を向上させるためには、圧縮応力を与えることが必要である。

【0006】

したがって、nMOSのチャネル領域には引っ張り応力を、pMOSには逆向きの圧縮応力をそれぞれ与えることにより、電流駆動力の向上が実現される。

【0007】

シリサイドを形成するための従来のサリサイド技術では、使用するシリサイドの種類によってシリコン基板に与えられる応力の方向は、一義的に決まってしまう。したがって、1種類のシリサイドを使用する場合には、上記のように、nMOS又はpMOSの一方の電流駆動力を向上できるが、他方の電流駆動力を低下させてしまうという問題点がある。2種類のシリサイドを使用するデュアルシリサイド構造にすることにより、nMOSとpMOSの両者にそれぞれ所望の方向の応力を与えることが可能になるが、製造プロセスが極めて複雑になるとうい問題がある。

【0008】

これらの問題を解決するために、特許文献1には、ソース/ドレインに1種類のシリサイドを形成後、引っ張り応力を有する第1のシリコン窒化膜(Si3N4膜)をnMOS領域に形成し、圧縮応力を有する第2のSi3N4膜をpMOS領域に形成する技術が、開示されている。これらのSi3N4膜によりnMOSとpMOSのチャネル領域に与えられる応力を逆向きに制御して、それぞれの電流駆動力を向上させている。この第1及び第2のSi3N4膜は、異なる製造方法により形成されるため、製造プロセスが複雑になる。また、第1及び第2のSi3N4膜が接する界面領域における応力の問題等、新たな問題が生ずる。

【特許文献1】特開2003−60076号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の目的は、微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能なCMOS半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0010】

上記の課題は、以下の本発明に係る半導体装置及びその製造方法によって解決される。

【0011】

本発明の1態様による半導体装置は、半導体基板上に絶縁膜を介して形成された第1のゲート電極と、前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、を具備する。

【0012】

本発明の他の1態様による半導体装置の製造方法は、半導体基板中に第1及び第2の半導体領域を形成する工程と、前記第1の半導体領域上に絶縁膜を介して第1のゲート電極を形成し、前記第2の半導体領域上に絶縁膜を介して第2のゲート電極を形成する工程と、前記第1のゲート電極を挟む前記半導体基板中に第1の拡散層を形成し、前記第2のゲート電極を挟む前記半導体基板中に第2の拡散層を形成する工程と、前記第1及び第2の拡散層に接触させて金属材料を堆積する工程と、第1のアニールにより前記金属材料と前記半導体基板とを反応させて前記第1及び第2の拡散層上に第1方向の内部応力を内在する第1相の第1及び第2の導電体層をそれぞれ形成する工程と、前記第2の半導体領域上に前記第1方向とは逆向きの第2方向の内部応力を内在する応力制御膜を形成する工程と、第2のアニールにより第1の半導体領域に前記第1方向の内部応力を内在する第2相の第1の導電体層を形成し、第2の半導体領域に前記第2方向の内部応力を内在する第2相の第2の導電体層を形成する工程と、を具備する。

【発明の効果】

【0013】

本発明により、微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能なCMOS半導体装置及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0014】

本発明の実施形態を、添付した図面を参照して以下に詳細に説明する。図では、対応する部分は、対応する参照符号で示している。以下の実施形態は、一例として示されたもので、本発明の精神から逸脱しない範囲で種々の変形をして実施することが可能である。

【0015】

本発明によれば、nMOSではそのチャネル領域に引っ張り応力を与えるシリサイド層を具備し、pMOSではそのチャネル領域に圧縮応力を与えるシリサイド層を具備する半導体装置及びその製造方法が提供される。上記のシリサイド層は、同じ元素により構成された1種類のシリサイドであり、従来の2種類のシリサイドを用いるデュアルシリサイドとは異なる。

【0016】

本発明の一実施形態の半導体装置の断面構造の一例を図1に示す。本実施形態の半導体装置は、nMOS100とpMOS200とにおいて同じ元素により構成されたシリサイド層140、240を有するが、シリサイドを形成するサリサイド工程において、それぞれが逆向きの内部応力を内在するようにシリサイド層140、240を形成したものである。図中に示した矢印は、内部応力の方向を表しており、外向きの矢印は、引っ張り応力を、内向きの矢印は、圧縮応力を表す。

【0017】

図1において、nMOS100では、ソース・ドレインのコンタクト領域132及びゲート電極124上に形成されたシリサイド層140−1,140−2は、引っ張りの内部応力を有する。周囲の応力を考慮する上で、シリサイド層140が引っ張り応力を有するということは、概念的に、シリコン基板10よりも小さな体積のシリサイド層140を埋め込んだことに相当する。したがって、シリサイド層140−1直下のシリコン基板10には、シリサイド層140−1とは逆向きの圧縮応力が与えられる。ところが、2つのシリサイド層140−1挟まれた、ゲート電極124直下のチャネル領域には、シリサイド層140−1と同じ向きの引っ張り応力が与えられる。

【0018】

一方、pMOS200では、ソース・ドレインのコンタクト領域232及びゲート電極224上に形成されたシリサイド層240−1,240−2は、nMOS100とは反対の圧縮の内部応力を有する。シリサイド層240が圧縮応力を有するということは、概念的に、シリコン基板10よりも大きな体積のシリサイド層240を埋め込んだことに相当する。同様に、このシリサイド層240−1の圧縮応力により、ゲート電極224直下のチャネル領域には、圧縮応力が与えられる。

【0019】

したがって、nMOSでは、チャネルにおける電子の移動度を改善でき、pMOSでは、正孔の移動度を改善できるため、半導体装置の電流駆動力を向上できる。

【0020】

nMOSとpMOSのシリサイド層140,240の内部応力は、下記に詳細に説明するように、シリサイド層を形成するサリサイド工程において、両者が逆向きの内部応力を持つように作り分けることができる。

【0021】

本発明の一実施形態の基本的な概念を図2に示した断面図を参照して、詳細に説明する。本実施形態の半導体装置は、2段階のシリサイド形成アニールを含むサリサイド工程を経て製造される。まず、図2(a)に示したように、シリコン基板10の表面にシリサイド用金属膜34、例えば、ニッケル(Ni)を堆積して第1のシリサイド化アニールを行う。第1のアニールは、完全にシリサイド化が行われないような低温、短時間のアニールである。第1のアニール後に、未反応のシリサイド用金属膜34を除去する。第1のアニールにより、図2(b)に示されたように、シリコン基板10表面には、第1相のシリサイド層36が形成される。第1相のシリサイド層36は、例えば、NixSi(1<x<2)の組成を有する中間段階のシリサイド層であり、引っ張りの内部応力を有する(図では、引っ張り応力を外向きの矢印で示している)。

【0022】

次に、図2(c)に示したように、第1相のシリサイド層36とは逆向きの内部応力(図では圧縮応力)を有する応力制御膜38を、第1相のシリサイド層36の一部の表面上に形成する(図では、圧縮内部応力を内向きの矢印で示している)。応力制御膜38の内部応力は、第1相のシリサイド層36の内部応力よりも大きな絶対値を有するように選択する。図2の例では、応力制御膜38として、大きな圧縮応力を有する窒化チタン膜(TiN膜)を使用している。

【0023】

その後、第2のシリサイド化アニールを行う。第2のアニールは、サーマルバジェットが、第1のアニールより大きなアニールである。第2のアニールにより第1相のシリサイド層36の金属が充分にシリコンと反応して第2相のシリサイド層40を形成する。すなわち、第2相のシリサイド層40は、例えば、NiSiの組成を有するモノシリサイドである。

【0024】

第2相のシリサイド層40の内部応力は、第2のアニール時の応力制御膜38の有無により制御することができる。

【0025】

応力制御膜38を形成しないで第2のアニールを行う場合には、図2(d)に示したように、第2相のシリサイド層40は、第1相のシリサイド層36よりもさらに大きな引っ張り応力を内部応力として有する。

【0026】

ところが、大きな圧縮応力を有する応力制御膜38を形成した状態で第2のアニールを行うと、図2(e)に示したように、この圧縮応力がシリサイド化反応中にシリサイド層内に凍結されて、圧縮応力を有する第2相のシリサイド層40’が形成される。

【0027】

このようにして、シリサイド層の内部応力の向きを制御することができる。

【0028】

本発明をCMOS半導体装置に応用した実施形態を、下記に説明する。チャネル中のキャリア移動度を大きくするためには、nMOSではチャネルに引っ張り応力を、pMOSでは圧縮応力を与えることが必要である。そこでソース/ドレインのコンタクト領域に、例えば、本来は引っ張り応力を有するシリサイドを形成する際に、pMOSにだけ大きな、例えば、圧縮応力を有する応力制御膜38を形成した状態で、第2のアニールを行う。その結果、pMOSのソース/ドレインのコンタクト領域に形成したシリサイド層には、圧縮の内部応力が凍結され、nMOSのシリサイド層には、引っ張りの内部応力が発生する。したがって、pMOSのチャネル領域には、圧縮応力を与えることができ、nMOSには、引っ張り応力を与えることができる。すなわち、互いに逆向きの内部応力を有するシリサイド層を同時に形成することが可能である。

【0029】

上記のように、互いに逆向きの内部応力を有するシリサイド層を形成することにより、nMOS及びpMOSにおいて、チャネル領域のキャリア移動度をそれぞれ向上させることができる。具体的には、nMOSではチャネル領域に引っ張り応力を与えることにより、チャネル領域の電子の移動度を向上でき、pMOSではチャネル領域に圧縮応力を与えることにより、チャネル領域の正孔の移動度を向上させることができる。これにより、nMOS,pMOSそれぞれの電流駆動力を向上できる。また、上記のシリサイド層は、本来の目的であるソース/ドレインの寄生抵抗を低減する。その結果、CMOS半導体装置の電流駆動力はnMOS、pMOSの各々に対して向上させることが可能となり、素子の性能を向上させることができる。さらに、本発明は、上記のように、サリサイド工程の途中に応力制御膜の形成を追加するだけで実現でき、製造プロセスは簡略である。

【0030】

以下に本実施形態の製造プロセスの一例を、図3から図6に示した工程断面図を参照して説明する。

【0031】

(1)先ず、図3(a)を参照して、半導体基板10、例えば、シリコン基板、に素子分離12を形成する。素子分離12は、例えば、シリコン基板10に浅い溝を形成し、その中をCVD(chemical vapor deposition)により形成したシリコン酸化膜(SiO2膜)で埋めたSTI(shallow trench isolation)を使用することができる。

【0032】

次に、nMOSを形成するnMOS領域110にp型不純物を深くドープしてp−ウェル115を、pMOSを形成するpMOS領域210にn型不純物を深くドープしてn−ウェル215を形成する。p型不純物としては、例えば、ホウ素(B)を使用することができ、n型不純物としては、例えば、リン(P)を使用することができる。

【0033】

その後、全面にゲート絶縁膜22を形成し、その上に導電体膜24を堆積する。ゲート絶縁膜22としては、例えば、SiO2膜、シリコン酸窒化膜(SiON膜)、を使用することができる。導電体膜24としては、例えば、ノンドープ若しくはリン又はホウ素を高濃度にドープした多結晶シリコンを使用することができる。

【0034】

そして、この積層膜をリソグラフィ及びエッチングによりパターニングして、ゲート電極124,224を形成する。

【0035】

(2)次に、ゲート電極124、224を覆うように全面に第1の絶縁膜26を形成する。第1の絶縁膜26としては、例えば、膜厚が2−10nmのシリコン窒化膜(Si3N4膜)を使用することができる。第1の絶縁膜26を異方性エッチングして、図3(b)に示したように、ゲート電極124,224の側面にのみ第1の絶縁膜26を残して、オフセットスペーサ126,226を形成する。ゲート電極124,224及びオフセットスペーサ126,226をマスクとして、イオン注入を行う。nMOS領域110には、n型不純物、例えば、ヒ素(As)をドープして、第1の拡散層128を形成し、pMOS領域210には、p型不純物、例えば、ホウ素(B)をドープして、第2の拡散層228を形成する。第1及び第2の拡散層128,228は、ソース/ドレインのエクステンションになる。

【0036】

(3)次に、オフセットスペーサ126,226を含むゲート電極124、224を覆うように全面に第2の絶縁膜30を形成する。第2の絶縁膜30としては、例えば、Si3N4膜を使用することができる。第2の絶縁膜30を異方性エッチングして、図4(a)に示したように、オフセットスペーサ126,226の側面にのみ第2の絶縁膜30を残して、ゲート側壁130,230を形成する。ゲート電極124,224及びゲート側壁130,230をマスクとして、第1及び第2の拡散層より深く高濃度のイオン注入を行う。nMOS領域110には、n型不純物、例えば、ヒ素(As)をドープして、第3の拡散層132を形成し、pMOS領域210には、p型不純物、例えば、ホウ素(B)をドープして、第4の拡散層232を形成する。第3及び第4の拡散層132,232は、ソース/ドレインのコンタクト領域になる。

【0037】

上記の工程(2)、(3)の第1と第3の拡散層128,132及び第2と第4の拡散層228,232のイオン注入時に、ゲート電極124,224にも同時にドーパントが導入される。

【0038】

(4)次に、図4(b)に示したように、ゲート電極124,224を覆って全面にシリサイド用金属膜34を形成する。シリサイド用金属34としては、例えば、膜厚が約10nmのニッケル(Ni)、コバルト(Co)、チタン(Ti)等を使用することができる。

【0039】

(5)その後、第1のシリサイド化アニールを行う。第1のシリサイド化アニールは、完全にシリサイド化が行われないような低温、短時間のアニールであり、例えば、350℃程度のRTA(rapid thermal annealing)である。この第1のアニールにより、図5(a)に示したように、シリサイド用金属膜34と接しているソース/ドレイン・コンタクト領域132,232及びゲート電極124,224の上面のシリコンが反応して第1相のシリサイド層136−1,236−1及び136−2,236−2が形成される。シリサイド用金属34としてNiを使用する場合、第1相のシリサイド層は、例えば、NixSi(1<x<2)の組成を有する中間的なシリサイドである。このシリサイド層は、図に外向きの矢印で示したように、引っ張りの内部応力を有する。第1のアニール時に、素子分離12上や、Si3N4膜のゲート側壁130,230上に堆積したシリサイド用金属は、反応せず、そこにはシリサイド層を形成しない。

【0040】

その後、硫酸過酸化水素水混合液やアンモニア過酸化水素水混合液等のエッチング液を用いて未反応のシリサイド用金属、例えば、Ni膜をエッチングして除去する。このとき第1相のシリサイド層136,236は、これらのエッチング液ではエッチングされずにそのまま残る。

【0041】

(6)次に、図5(b)に示したように、ゲート電極124,224を覆うように全面に応力制御膜38を形成する。そして、nMOS領域110上の応力制御膜38をリソグラフィ及びエッチングにより除去して、pMOS領域210上だけを応力制御膜38でキャップする。応力制御膜38は、第1相のシリサイド層136、236とは逆向きの内部応力を有し、内部応力の絶対値が大きな膜である。第1相のシリサイド層が、例えば、NixSi(引っ張り応力を有する)の場合には、圧縮応力(図では内向きの矢印)を有する膜、例えば、窒化チタン膜(TiN膜)を使用することができる。TiN膜38の選択的なエッチングには、例えば、過酸化水素水(H2O2)を使用することができる。

【0042】

(7)その後、第2のシリサイド化アニールを行う。第2のアニールは、第1相のシリサイド層136、236が充分にシリコンと反応するように行う。例えば、500℃程度のRTAであり、第2のアニールのサーマルバジェットは、第1のアニールよりも大きい。図6に示したように、この第2のアニールより、第1相のシリサイド層136,236(例えば、NixSi(1<x<2))は、第2相のシリサイド層140、240(例えば、ニッケルモノシリサイド(NiSi))に変化する。

【0043】

上記で使用する応力制御膜38、例えば、TiN膜は、安定な膜であるため、このアニールではシリサイド層とは反応しない。したがって、nMOS及びpMOSのシリサイド層140及び240の両者は、同じ元素により構成される。

【0044】

このようにして形成したnMOSとpMOSのシリサイド層140と240は、互いに逆向きの内部応力を有する。すなわち、応力制御膜38を形成しないで第2のアニールを行ったnMOS100では、第2相のシリサイド層140は、第1相のシリサイド層136よりもさらに大きな引っ張り応力を内部応力として内在する。ところが、大きな圧縮応力を有する応力制御膜38を形成した状態で第2のアニールを行ったpMOS200では、この圧縮応力がシリサイド化反応中にシリサイド層240内に凍結されて、圧縮応力を内在する第2相のシリサイド層240−1,240−2が形成される。

【0045】

第2のアニール後に、応力制御膜38を除去して、図6に示した構造を完成する。

【0046】

その後、図示しないが、第3及び第4の拡散層132,232上のシリサイド層140−1,240−1、及びゲート電極124,224上のシリサイド層140−2,240−2に接続する配線を形成する。さらに、多層配線等の半導体装置に必要な工程を行って、nMOS及びpMOSのそれぞれのシリサイド層を所望の向きの応力に制御し、素子特性を向上させたCMOS半導体装置を完成する。

【0047】

上記の第2のアニール時に、上記で説明したように、本来のシリサイド層の応力とは逆向きの内部応力を有する応力制御膜38でキャップしたpMOS領域210では、そこに形成される第2相のシリサイド層240−1,240−2が、応力制御膜38と同じ圧縮内部応力を内在するようにシリサイド化される。一方、nMOS領域110では、第2相のシリサイド層140−1,140−2は、本来の引っ張り内部応力を内在する。

【0048】

シリサイド層240−1が、圧縮応力を有するpMOSでは、隣接するチャネル領域にも圧縮応力が与えられる。同様に、シリサイド層140−1が、引っ張り応力を有するnMOSでは、隣接するチャネル領域にも引っ張り応力が与えられる。

【0049】

上記に例示したシリサイド用金属、ニッケル(Ni),コバルト(Co),チタン(Ti)によるシリサイド、ニッケルシリサイド(NiSi),コバルトシリサイド(CoSi2),チタンシリサイド(TiSi2)は、いずれも本来引っ張り応力を内在する。したがって、応力制御膜として大きな圧縮応力を有する上記のTiN膜を使用して、pMOSとnMOSとにおいて応力を逆向きに制御することができる。

【0050】

本実施形態において、シリサイド材料としてニッケルシリサイド(NiSi)を例に挙げたが、本発明はこれらの材料に限定するものではなく、シリサイド材料としては、上記のTiSi2、CoSi2の他に、例えば、プラチナシリサイド(PtSi)、パラジウムシリサイド(PdSi)、エルビウムシリサイド(ErSi2)のような、種々の金属シリサイドを用いることができる。

【0051】

またシリサイド層の内部応力の方向を制御する材料として、膜の内部応力が圧縮応力である窒化チタン膜を例に挙げたが、この材料についても窒化チタン膜に限定する必要はなく、同様にシリサイド層とは逆向きの内部応力を持つその他の導体膜、半導体膜、絶縁膜を用いることも可能である。

【0052】

本実施形態において、pMOS領域上にのみ圧縮内部応力を有する窒化チタン膜を堆積し第2のアニールによりシリサイド化を行った。これに加えて、nMOS領域上にも強い引っ張り応力を有する第2の応力制御膜を堆積し、nMOS上に形成されるシリサイド層の内部応力をさらに大きな引っ張り応力とすることができる。これにより、チャネル領域に加わる引っ張り応力をさらに大きくすることで、nMOSの素子性能をさらに向上させることも可能である。なおこれらの応力制御膜は、シリサイド化のための第2のアニール後に、除去される。

【0053】

上記のように、互いに逆向きの内部応力を有するシリサイド層を形成することにより、nMOS及びpMOSにおいて、チャネル領域のキャリア移動度をそれぞれ向上させることができる。すなわち、nMOSではチャネル領域に引っ張り応力を与えることにより、チャネル領域の電子の移動度を向上でき、pMOSではチャネル領域に圧縮応力を与えることにより、チャネル領域の正孔の移動度を向上させることができる。これにより、nMOS,pMOSそれぞれの電流駆動力を向上できる。また、上記のシリサイド層は、本来の目的であるソース/ドレインの寄生抵抗を低減する。その結果、MOSFET素子の電流駆動力はnMOSFET領域、pMOSFET領域各々に対して向上させることが可能となり、素子の性能を向上させることができる。さらに、本発明は、上記のように、サリサイド工程の途中に応力制御膜の形成を追加するだけで実現でき、製造プロセスは簡略である。

【0054】

本発明は、微細化された半導体装置の性能を向上に有効であり、特にゲート長が0.1μm以下のCMOS半導体装置の性能を向上させることができる。

【0055】

本発明は、上記の実施形態に限定されることなく、本発明の精神及び範囲から逸脱しないで、種々の変形を行って実施することができる。それゆえ、本発明は、ここに開示された実施形態に制限することを意図したものではなく、発明の趣旨を逸脱しない範囲において他の実施形態にも適用でき、広い範囲に適用されるものである。

【図面の簡単な説明】

【0056】

【図1】図1は、本発明の一実施形態の半導体装置を説明するために示す断面図である。

【図2】図2(a)から(e)は、本発明の一実施形態の原理を説明するために示す断面図である。

【図3】図3(a),(b)は、本実施形態にしたがった半導体装置の製造工程の一例を説明するために示す断面図である。

【図4】図4(a),(b)は、図3(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【図5】図5(a),(b)は、図4(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【図6】図6は、図5(b)に続く本実施形態の半導体装置の製造工程の一例を説明するために示す断面図である。

【符号の説明】

【0057】

100…nMOS,200…pMOS,10…半導体基板(シリコン基板),12…素子分離,24…導電体膜,26…第1の絶縁膜,30…第2の絶縁膜,34…シリサイド用金属,38…応力制御膜,110…nMOS領域,210…pMOS領域,115,215…ウェル,22,122,222…ゲート絶縁膜,124,224…ゲート電極,126,226…オフセットスペーサ,128…第1の拡散層,228…第2の拡散層,130,230…ゲート側壁,132…第3の拡散層,232…第4の拡散層,136,236…第1相のシリサイド層,140,240…第2相のシリサイド層。

【特許請求の範囲】

【請求項1】

半導体基板上に絶縁膜を介して形成された第1のゲート電極と、

前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、

前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、

前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、

前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、

前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、

を具備することを特徴とする半導体装置。

【請求項2】

前記第1の半導体素子はnMOSFETであり、前記第1方向の内部応力は引っ張り応力であり、前記第2の半導体素子はpMOSFETであり、前記第2方向の内部応力は圧縮応力であることを特徴とする、請求項1に記載の半導体装置。

【請求項3】

前記第1及び第2の導電体層は、ニッケル、コバルト、チタニウム、プラチナ、パラジウム、エルビウム、のうち少なくとも1つの金属を含む金属シリサイドあることを特徴とする、請求項1若しくは2に記載の半導体装置。

【請求項4】

前記第1及び第2方向の内部応力は、前記第1及び第2の導電体層を形成する際に同時に形成されることを特徴とする、請求項1ないし3のいずれか1に記載の半導体装置。

【請求項5】

半導体基板中に第1及び第2の半導体領域を形成する工程と、

前記第1の半導体領域上に絶縁膜を介して第1のゲート電極を形成し、前記第2の半導体領域上に絶縁膜を介して第2のゲート電極を形成する工程と、

前記第1のゲート電極を挟む前記半導体基板中に第1の拡散層を形成し、前記第2のゲート電極を挟む前記半導体基板中に第2の拡散層を形成する工程と、

前記第1及び第2の拡散層に接触させて金属材料を堆積する工程と、

第1のアニールにより前記金属材料と前記半導体基板とを反応させて前記第1及び第2の拡散層上に第1方向の内部応力を内在する第1相の第1及び第2の導電体層をそれぞれ形成する工程と、

前記第2の半導体領域上に前記第1方向とは逆向きの第2方向の内部応力を内在する応力制御膜を形成する工程と、

第2のアニールにより第1の半導体領域に前記第1方向の内部応力を内在する第2相の第1の導電体層を形成し、第2の半導体領域に前記第2方向の内部応力を内在する第2相の第2の導電体層を形成する工程と、

を具備することを特徴とする、半導体装置の製造方法。

【請求項1】

半導体基板上に絶縁膜を介して形成された第1のゲート電極と、

前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、

前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、

前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、

前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、

前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、

を具備することを特徴とする半導体装置。

【請求項2】

前記第1の半導体素子はnMOSFETであり、前記第1方向の内部応力は引っ張り応力であり、前記第2の半導体素子はpMOSFETであり、前記第2方向の内部応力は圧縮応力であることを特徴とする、請求項1に記載の半導体装置。

【請求項3】

前記第1及び第2の導電体層は、ニッケル、コバルト、チタニウム、プラチナ、パラジウム、エルビウム、のうち少なくとも1つの金属を含む金属シリサイドあることを特徴とする、請求項1若しくは2に記載の半導体装置。

【請求項4】

前記第1及び第2方向の内部応力は、前記第1及び第2の導電体層を形成する際に同時に形成されることを特徴とする、請求項1ないし3のいずれか1に記載の半導体装置。

【請求項5】

半導体基板中に第1及び第2の半導体領域を形成する工程と、

前記第1の半導体領域上に絶縁膜を介して第1のゲート電極を形成し、前記第2の半導体領域上に絶縁膜を介して第2のゲート電極を形成する工程と、

前記第1のゲート電極を挟む前記半導体基板中に第1の拡散層を形成し、前記第2のゲート電極を挟む前記半導体基板中に第2の拡散層を形成する工程と、

前記第1及び第2の拡散層に接触させて金属材料を堆積する工程と、

第1のアニールにより前記金属材料と前記半導体基板とを反応させて前記第1及び第2の拡散層上に第1方向の内部応力を内在する第1相の第1及び第2の導電体層をそれぞれ形成する工程と、

前記第2の半導体領域上に前記第1方向とは逆向きの第2方向の内部応力を内在する応力制御膜を形成する工程と、

第2のアニールにより第1の半導体領域に前記第1方向の内部応力を内在する第2相の第1の導電体層を形成し、第2の半導体領域に前記第2方向の内部応力を内在する第2相の第2の導電体層を形成する工程と、

を具備することを特徴とする、半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2007−81330(P2007−81330A)

【公開日】平成19年3月29日(2007.3.29)

【国際特許分類】

【出願番号】特願2005−270773(P2005−270773)

【出願日】平成17年9月16日(2005.9.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成19年3月29日(2007.3.29)

【国際特許分類】

【出願日】平成17年9月16日(2005.9.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]