半導体装置及びその製造方法

【課題】COF等のフリップチップやILBによるベアチップ実装において、配線基板の寸法変化に起因する半導体素子の電極との間の位置ずれを緩和する。

【解決手段】配線基板1は、導体配線2が延在して形成され、半導体素子4の領域の外側から半導体素子の第1素子電極列5と各々接合された第1接合用配線列9と、半導体素子領域の外側から半導体素子の第2素子電極列7と各々接合された第2接合用配線列10とを備える。第1接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第1素子電極列のピッチより広く、半導体素子の中心側の先端では第1素子電極列のピッチより狭くなるように連続的に変化しており、第2接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第2素子電極列のピッチより狭く、半導体素子の中心側の先端では第2素子電極列のピッチより広くなるように連続的に変化している。

【解決手段】配線基板1は、導体配線2が延在して形成され、半導体素子4の領域の外側から半導体素子の第1素子電極列5と各々接合された第1接合用配線列9と、半導体素子領域の外側から半導体素子の第2素子電極列7と各々接合された第2接合用配線列10とを備える。第1接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第1素子電極列のピッチより広く、半導体素子の中心側の先端では第1素子電極列のピッチより狭くなるように連続的に変化しており、第2接合用配線列を構成する各々の導体配線のピッチは、半導体素子領域の外側では第2素子電極列のピッチより狭く、半導体素子の中心側の先端では第2素子電極列のピッチより広くなるように連続的に変化している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子が配線基板に接合された構成を有する半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

配線基板上に半導体素子を載置し、配線基板上に形成された接合用配線と半導体素子上の素子電極とを接合した半導体装置、及びその製造方法が知られている。配線基板には、主に価格が安い有機機材が用いられることが多い。有機基材は一般的に、シリコンやガラス等の無機材料と比較して、温度や湿度の変化による寸法変化が大きい。そのことが、シリコン等からなる半導体素子や、ガラス等からなる液晶パネル等との接合ピッチを微細化する妨げとなっている。例えば、現在比較的微細接合が進んでいる液晶用のCOFパッケージにおいて、ポリイミドからなる配線基板と半導体素子との接合ピッチは30μm程度、液晶パネルとの接合ピッチは50μm程度が量産可能な水準である。それ以下のピッチでの接合のためには、配線基板の寸法変化を吸収する工夫が必要である。このため、温度や湿度による寸法調整の他、接合部の構造により寸法変化を吸収する工夫が考案されてきた(例えば特許文献1参照)。

【0003】

以下、従来の半導体装置とその製造方法について、図11を参照しながら説明する。図11(a)において、配線基板44は、絶縁性基材41、絶縁性基材41上に形成された導体配線42、及び接合用配線列43からなる。接合用配線列43は、導体配線42を延在して形成されている。配線基板44に搭載された半導体素子45の主面上には、素子電極46が形成されている。素子電極46は半導体素子45の中心から外に向かって傾けて形成されており、接合用配線列43と交差して接合されている。

【0004】

従来の半導体装置では図11(b)に示すように、配線基板44のY方向の寸法が設計値Y0より2yだけ延び、接合用配線列43のピッチが広くなった場合でも、接合用配線列43が素子電極46と交差している。そのため、接合用配線列43が素子電極46から外れる事無く接合することができる。配線基板44のY方向の寸法が、設計値Y0より縮んだ場合も同様である。

【特許文献1】特許第3357296号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら上記従来の半導体装置では、図11(c)に示すように、配線基板44のY方向の寸法が図11(b)の場合よりも更に大きい寸法2y’延びた場合、接合用配線列43が素子電極46と交差しなくなるため、接合用配線列43が素子電極46と接合できなくなるという課題があった。

【0006】

本発明は、上記従来の問題を解決するものであり、原理的に配線基板の寸法変化量による制限を受けず、接合用配線列と素子電極列の間にずれを生じることなく接合できる半導体装置、及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の第1の構成の半導体装置は、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、前記配線基板上に載置された半導体素子と、前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備える。前記第1接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように連続的に変化しており、前記第2接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように連続的に変化している。

【0008】

また、本発明の半導体装置の製造方法は、第1辺に沿って設けられた第1素子電極列と、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列とが主面上に形成された半導体素子を準備する工程と、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有し、前記導体配線を延在させて、前記半導体素子を載置する半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように形成した第1接合用配線列と、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように形成した第2接合用配線列を備えた配線基板を準備する工程と、前記半導体素子を前記配線基板に載置する際に、前記配線基板の前記半導体素子の前記第1辺に平行な方向に寸法変化があった場合、前記半導体素子を前記第1辺と直交する方向に沿って、同方向における基準位置から前記寸法変化分に比例した距離を移動させて、前記第1接合用配線列のピッチが前記第1素子電極列のピッチと等しくなり、かつ前記第2接合用配線列のピッチが前記第2素子電極列のピッチと等しくなる位置で、前記第1接合用配線列と前記第1素子電極列及び、前記第2接合用配線列と前記第2素子電極列とを接合する工程とを含む。

【0009】

本発明の第2の構成の半導体装置は、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、前記配線基板上に載置された半導体素子と、前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備える。前記第1接合用配線列及び前記第2接合用配線列を構成する各導体配線のピッチは均一であり、前記第1素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第1接合用配線列を構成する各導体配線のピッチより広く、前記半導体素子の中心側の先端では前記各導体配線のピッチより狭くなるように連続的に変化しており、前記第2素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第2接合用配線列を構成する各導体配線のピッチより狭く、前記半導体素子の中心側の先端では前記各導体配線のピッチより広くなるように連続的に変化している。

【0010】

本発明の第3の構成の半導体装置は、第1絶縁性基材、前記第1絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第1絶縁性基材の一端に配列して形成された第1外部電極列を有する第1配線基板と、前記第1配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子と、第2絶縁性基材、前記第2絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第2絶縁性基材の一端に配列して形成された第2外部電極列とを有する第2配線基板とを備え、前記第1外部電極列のピッチは前記第1配線基板の中央から前記第1外部電極列が形成された一辺に向かって広くなるように形成され、前記第2外部電極列のピッチは前記第2配線基板の中央から前記第2外部電極列が形成された一辺に向かって狭くなるように形成され、前記第1配線基板の前記第1外部電極列を形成した一辺と、前記第2配線基板の前記第2外部電極列を形成した一辺とが相対し、前記第1外部電極列と前記第2外部電極列とが同一ピッチとなる部分で接合されている。

【0011】

本発明の第4の構成の半導体装置は、絶縁性基材と、前記絶縁性基材上に形成された複数本の導体配線、及び前記複数の導体配線を延在して形成された検査用電極列を備えた配線基板と、前記配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子とを備え、前記検査用電極列のピッチは前記配線基板の電気特性を検査するための検査用プローブと接触する基準位置では前記検査用プローブのピッチと等しく、前記基準位置から一方に離れるに従い前記検査用プローブのピッチよりも広く形成されており、前記基準位置から前記検査用電極列のピッチが広く形成されている方向と逆方向に離れるに従い狭く形成されている。

【発明の効果】

【0012】

本発明の半導体装置及びその製造方法によれば、接合用配線列のピッチが半導体素子電極のピッチに対して広い部分と狭い部分を連続的に有しており、また、半導体素子の2辺に対し、接合用配線列のピッチ変化の方向が同一である。それにより、半導体素子を配線基板に載置する際に第1辺に平行な方向に寸法変化があった場合、第1辺と直交する方向に沿って寸法変化分に比例した距離を移動させることで、接合用配線列のピッチと素子電極列のピッチとを等しくできるため、原理的に配線基板の寸法変化量による制限を受けず、接合用配線列と素子電極列とをずれを生じずに接合することが可能である。

【発明を実施するための最良の形態】

【0013】

本発明は上記構成を基本として、以下のような態様をとることができる。

【0014】

すなわち、第1の構成の半導体装置において、前記第1接合用配線列及び前記第2接合用配線列は、各々前記第1素子電極列及び前記第2素子電極列と各々接合された位置から、更に前記半導体素子の中心に向かって延在する構成とすることができる。

【0015】

また、前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度の関係が、いずれか一方の角度が他方の角度よりも小さく設定されている構成とすることができる。

【0016】

また、前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度が等しく設定されている構成とすることができる。

【0017】

また、前記第1素子電極列及び第2素子電極列を構成する個々の素子電極は円柱状の突起電極である構成とすることができる。

【0018】

また、半導体装置の製造方法において、前記配線基板上に、前記半導体素子の前記第1辺に沿った方向において基準距離を隔てて第1認識マーク及び第2認識マークを設け、前記配線基板の前記半導体素子の前記第1辺に平行な方向の寸法変化を、前記第1認識マークと前記第2認識マーク間の前記第1辺に沿った方向の前記基準距離からの変移により求めることができる。

【0019】

以下、本発明の実施形態について図面を参照しながら説明する。

【0020】

(第1の実施形態)

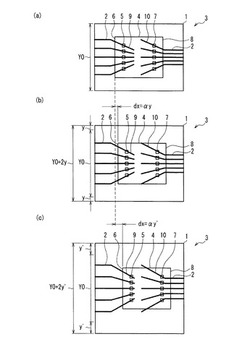

図1(a)は、本発明の第1の実施形態にかかる半導体装置の平面図である。図1(a)において、配線基板3は、絶縁性基材1と、絶縁性基材1の表面に形成された導体配線2とを有する。配線基板3には更に、第1接合用配線列9、及び第2接合用配線列10が設けられている。配線基板3に載置された半導体素子4の主面上には、半導体素子4の第1辺6に沿って第1素子電極列5が配列され、第1辺6と対向する第2辺8に沿って第2素子電極列7が配列されている。

【0021】

第1接合用配線列9は、導体配線2を延在して形成され、絶縁性基材1上の半導体素子4が載置された領域の外側から、半導体素子4の第1辺6を横切り第1素子電極列5と各々接合され、更に半導体素子4の中心に向かって延在している。

【0022】

第2接合用配線列10は、導体配線2を延在して形成され、絶縁性基材1上の半導体素子4が載置された領域の外側から半導体素子4の第2辺8を横切り第2素子電極列7と各々接合され、更に半導体素子4の中心に向かって延在している。

【0023】

第1接合用配線列9を構成する各々の導体配線2のピッチは、半導体素子4が載置された領域の外側では第1素子電極列5のピッチより広く、第1素子電極列5との接合箇所では第1素子電極列5のピッチと等しく、第1素子電極列5との接合箇所より半導体素子4の中心側では第1素子電極列5のピッチより狭くなるように、連続的に変化させて形成されている。

【0024】

一方、第2接合用配線列10を構成する各々の導体配線2のピッチは、半導体素子4が載置された領域の外側では第2素子電極列7のピッチより狭く、第2素子電極列7との接合箇所では第2素子電極列7のピッチと等しく、第2素子電極列7との接合箇所より半導体素子4の中心側では第2素子電極列7のピッチより広くなるように、連続的に変化させて形成されている。

【0025】

ここでは、一般的な液晶用パッケージに用いられるCOF(Chip On Film)パッケージとして、例えば絶縁性基材1は厚み40μm程度のポリイミド、導体配線2は厚み8μm、幅15μm程度のCu上に無電解Snめっきを形成したもの、素子電極列5、7は高さ15μm程度の電解Auめっきバンプを用いた場合を例としている。

【0026】

次に、本実施の形態に係る半導体装置の製造方法について、図1(b)、(c)を参照しながら説明する。図1(b)、(c)において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号が付されている。なお、半導体素子4の第1辺6に平行な方向をY方向、直交する方向をX方向とする。

【0027】

図1(b)は、図1(a)に比較して、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交するX方向に沿って、図1(a)の位置(基準位置)からY方向の寸法変化であるyに比例した距離dx=αyだけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しい位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することができる。

【0028】

図1(c)は、図1(b)に比較して、配線基板3のY方向の寸法が更に延びた場合を示す。この場合でも、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図1(a)の位置からY方向の寸法変化であるy’に比例した距離dx=αy’だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しくなる位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することがでる。

【0029】

以上のように本実施形態によれば、原理的に配線基板のY方向の寸法変化量による制限を受けることなく、第1及び第2接合用配線列9、10と、第1及び第2素子電極列5、7とを、ずれを解消して接合することができる。

【0030】

ここで、一般的には、Y方向の寸法変化であるy、y’は配線基板の製造ロット内では大きな差異では無い為、配線基板の出荷検査もしくは受け入れ検査時の寸法測定結果から、移動量dxをロット毎に設定することができる。

【0031】

なお、図1の例は、第1接合用配線列9及び第2接合用配線列10の対応する位置の導体配線の角度が、互いに等しい構成を示したものである。これは、Y方向には寸法の変化があるが、X方向には寸法の変化が実質的に無いと考えられる場合の態様である。後述するように、X方向にも寸法の変化が実質的に発生する場合には、それに応じて第1接合用配線列9及び第2接合用配線列10の角度を調整する必要がある。

【0032】

(第2の実施形態)

図2(a)、(b)は、本発明の第2の実施形態にかかる半導体装置の平面図である。同図において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。

【0033】

本実施形態の第1の実施形態との相違点は、図2(a)に示すように、第1接合用配線列9を構成する任意の第1導体配線9aが半導体素子の第1辺6と交差する第1角度θ1が、第2接合用配線列10を構成し第1導体配線9aと対向する位置に形成された第2導体配線10aが半導体素子4の第2辺8と交差する第2角度θ2よりも小さいことである。

【0034】

配線基板3の寸法変化は、一般的にはY方向にもX方向にも発生する。図2(b)に示すように、配線基板3のY方向の寸法が2y延びると同時に、配線基板3のX方向の寸法がx延びた場合には、半導体素子4を第1辺6と直交する方向に沿って図2(a)の位置からyに比例した距離だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しくなる位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを適切な相互関係で接合することができる。

【0035】

すなわち、本発明の第2の実施形態にかかる半導体装置では、配線基板3のX方向の寸法変化にも対応して、第1及び第2接合用配線列9、10と第1及び第2素子電極列5、7とをずれを解消して接合することができる。

【0036】

ここで比較の為に、配線基板3のX方向の寸法変化に対応していない本発明の第1の実施形態にかかる半導体装置について、図2(b)と同様にX方向の寸法がxだけ延びた場合を、同一の縮尺で図2(c)に図示する。第1接合用配線列9が第1素子電極列5のピッチと合う位置に半導体素子4を移動させた場合は、第2接合用配線列10が第2素子電極列7とずれてしまい、接合できないことが判る。

【0037】

なお、第1角度θ1と第2角度θ2の大きさの関係は、上記構成と逆であってもよい。その場合は、半導体素子4の基準位置、及び移動させる向きを上記構成に対して左右反転させればよい。

【0038】

(第3の実施形態)

図3は、本発明の第3の実施形態にかかる半導体装置の平面図、図4は図3の要部拡大図である。図3、図4において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。但し、図3、図4においては、第1素子電極5a及び第2素子電極7aが、円柱形状となっている点が、図1(a)に示した半導体装置とは相違する。

【0039】

第1の実施形態の場合、第1及び第2素子電極5a、7aと第1及び第2接合用配線列9、10の交差角度は、図1(a)〜(c)に示したように半導体素子の配置位置で変化する。これに対して、本実施形態の第1及び第2素子電極5a,7aのように円柱形状とすることで、図4の(a)、(b)に示すように、第1素子電極5aと第1接合用配線列9との交差角度によらず、第1素子電極5aと第1接合用配線列9との接合面積(斜線部分)は、第1素子電極5aを構成する円柱の直径と第1接合用配線列9の幅で決定される。

【0040】

このため、図4に図示するように全ての位置で接合面積を同一にすることもできるが、例えば図5に示す様に、接合後に印加される応力が大きい半導体素子4の端部に向かうに従い、円柱の直径を大きくすることで接合面積を増加させて、接合強度を確保することもできる。

【0041】

なお、電解Auめっきを用いれば、露光マスク形状を円形にすることで、第1素子電極5a、第2素子電極7aを容易に円柱形状に形成することができる。

【0042】

(第4の実施形態)

図6は、本発明の第4の実施形態にかかる半導体装置の製造方法を示す平面図である。図6において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。本実施形態の構成では、配線基板1上に、第1認識マーク11、第2認識マーク12が形成されている。半導体素子4の第1辺6に沿った方向における、第1認識マーク11と第2認識マーク12間の距離はW0である。

【0043】

図6(b)は図6(a)に比較し、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4の第1辺6に沿った方向の第1認識マーク11と認識マーク12間の距離はW1となり、配線基板3の半導体素子4の第1辺6に平行な方向の寸法変化yは、(W1−W0)に比例する。

【0044】

従って、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図6(a)の位置からY方向の寸法変化であるyに比例した距離dx=αy=α’(W1−W0)だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しい位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することができる。

【0045】

この第4の実施形態によれば、実際に接合に用いる配線基板3の第1及び第2認識マーク11、12の距離の変移(W1−W0)に応じて、半導体素子4の移動距離dxを最適な値に設定することができる。そのため、ロット毎にdxを設定していた第1の実施形態と比較し、更に接合の位置精度を向上させることができる。

【0046】

なお、第1〜第3の実施形態においては、配線基板3上の第1及び第2接合用配線列9、10に角度を持たせた形態としたのに対して、図7に示すように、半導体素子4上の第1及び第2素子電極5、7に角度を持たせた形態としても良い。

【0047】

すなわち図7(a)に示すように、導体配線2は均一のピッチで直線状に延在して形成され、半導体素子4が載置された領域の左右の外側から、それぞれ半導体素子4の第1辺6および第2辺8を横切り、第1素子電極列5及び第2素子電極列7と各々接合されている。第1素子電極列5及び第2素子電極列7を構成する各素子電極は、第1辺6及び第2辺8を横切る方向を長手方向とする細長い形状を有する。

【0048】

第1素子電極列5を構成する各素子電極のピッチは、半導体素子4の外縁近傍では導体配線2のピッチより広く、導体配線2との接合箇所では導体配線2のピッチと等しく、導体配線2との接合箇所より半導体素子4の中心側では導体配線2のピッチより狭くなるように、連続的に変化している。

【0049】

一方、第2素子電極列7を構成する各素子電極のピッチは、半導体素子4の外縁近傍では導体配線2のピッチより狭く、導体配線2との接合箇所では導体配線2のピッチと等しく、導体配線2との接合箇所より半導体素子4の中心側では導体配線2のピッチより広くなるように、連続的に変化している。

【0050】

図7(b)は、図7(a)に比較して、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図7(a)の位置からY方向の寸法変化であるyに比例した距離dx=αyだけ移動する。それにより、第1素子電極列5及び第2素子電極列7のピッチが、導体配線2のピッチと等しい位置関係に調整することができる。その結果、導体配線2と第1素子電極列5及び第2素子電極列7とを、適切な相互関係で接合することができる。

【0051】

この場合、配線基板3上の導体配線2の側に突起電極13を設ける必要があるが、例えば図8に示す様に、導体配線2を横切り、導体配線2の両側の絶縁基材1上に亘って形成された突起電極13(特許第3565835号公報参照)を用いても良い。

【0052】

(第5の実施形態)

図9は、本発明の第5の実施形態にかかる半導体装置を示す平面図である。図9において、第1配線基板24は、第1絶縁性基材21、第1絶縁性基材21上に形成された導体配線22、及び第1外部電極列23からなる。第1外部電極列23は、複数の導体配線22を延在させて、第1絶縁性基材21の一端に配列して形成されている。第2配線基板28は、第2絶縁性基材25、第2絶縁性基材25上に形成された導体配線26、及び第2外部電極列27からなる。第2外部電極列27は、複数の導体配線26を延在させて、第2絶縁性基材25の一端に配列して形成されている。

【0053】

第1外部電極列23のピッチは、第1配線基板24の中央から第1外部電極列23が形成された一辺に向かって広くなるように設定されている。第2外部電極列27のピッチは、第2配線基板28の中央から第2外部電極列27が形成された一辺に向かって狭くなるように設定されている。第1配線基板24の第1外部電極列23を形成した一辺と、第2配線基板28の第2外部電極列27を形成した一辺とが相対向し、第1外部電極列23と第2外部電極列27とが同一ピッチとなる部分で接合されている。

【0054】

本実施形態では、第1配線基板24がポリイミドで形成された液晶用COFパッケージ、第2配線基板が液晶用ガラス基板である場合を例としている。第1外部電極列23としてCu箔上にSnめっきを形成し、第2外部電極列27としてAlを用い、各々をACF(Anisotropic Conductive Film)を用いて接合する。

【0055】

なお、本実施形態は、第1配線基板24を液晶用ガラス基板、第2配線基板を液晶用COFパッケージと置き換えても、全く同様に適用して同一の機能を持たせることができる。

【0056】

本実施の形態に係る半導体装置の製造方法の特徴は、第1の実施形態と同様であり、図9(b)は、図9(a)と比較して、配線基板24のY方向の寸法が2yだけ延びた場合を示す。図9(c)は、図9(a)と比較して、配線基板24のY方向の寸法が2y’だけ縮んだ場合を示す。

【0057】

いずれの場合も、配線基板24のX方向の位置をY方向の寸法変化に比例した距離dx=βy、あるいはdx’=βy’だけ移動することで、第1外部電極列23と第2外部電極列27とが同一ピッチとなる部分で接合することができる。

【0058】

本実施形態の場合は第1〜第4の実施形態と異なり、第1外部電極列23と第2外部電極列27のいずれにも突起電極を設ける必要は無く、前述のようにCOF等のパッケージと液晶ガラス基板との接合に用いることができる。

【0059】

(第6の実施形態)

図10は、本発明の第6の実施形態にかかる半導体装置を示す平面図である。図10において、配線基板34は、絶縁性基材31、絶縁性基材31上に形成された導体配線32、及び検査用電極列33を備えている。検査用電極列33は、複数の導体配線32を延在させて形成されている。35は、検査用電極列33に接触させる検査用プローブである。

【0060】

検査用電極列33のピッチは、検査用プローブ35と接触する位置では検査用プローブ35のピッチと等しく、検査用プローブ35と接触する位置から一方に離れるに従い検査用プローブ35のピッチよりも広く形成されており、その逆方向に離れるに従い狭く形成されている。

【0061】

本実施形態では、配線基板34が液晶用COFパッケージを構成する一部分である場合を例としている。検査用電極列33としてCu箔上にSnめっきを形成し、検査用プローブ35としてタングステンを用いて電気的検査を実施する。

【0062】

本実施の形態に係る半導体装置の検査方法において、検査用電極列33に対して検査用プローブ35を整合させて接触させる方法は、第1の実施形態において、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係に整合させる方法と同様である。すなわち、図10(b)は図10(a)と比較し、配線基板34のY方向の寸法が2yだけ延びた場合、図10(c)は図10(a)と比較し、配線基板34のY方向の寸法が2y’だけ縮んだ場合を示す。

【0063】

いずれの場合も、配線基板34のX方向の位置を、Y方向の寸法変化に比例した距離dxだけ移動させることで、検査用電極列33と検査用プローブ35とが同一ピッチとなる部分で両者を接触させることができる。

【産業上の利用可能性】

【0064】

本発明の半導体装置は、寸法変化の比較的大きな有機基材上に形成されたパターンへの精密な位置合わせ技術として有用である。

【図面の簡単な説明】

【0065】

【図1】本発明の第1の実施形態における半導体装置を示す平面図

【図2】(a)、(b)は、本発明の第2の実施形態における半導体装置を示す平面図、(c)は比較のために従来例の半導体装置を示す平面図

【図3】本発明の第3の実施形態における半導体装置を示す平面図

【図4】同実施形態における半導体装置を示す要部拡大図

【図5】同実施形態における半導体装置を示す平面図

【図6】本発明の第4の実施形態における半導体装置を示す平面図

【図7】本発明の第5の実施形態における半導体装置を示す平面図

【図8】同実施形態で用いられる突起電極の例を示す斜視図

【図9】本発明の第6の実施形態における半導体装置を示す平面図

【図10】本発明の第7の実施形態における半導体装置を示す平面図

【図11】従来の半導体装置を示す平面図

【符号の説明】

【0066】

1 絶縁性基材

2 導体配線

3 配線基板

4 半導体素子

5、5a 第1素子電極列

6 第1辺

7、7a 第2素子電極列

8 第2辺

9 第1接合用配線列

9a 第1導体配線

10 第2接合用配線列

10a 第2導体配線

11 第1認識マーク

12 第2認識マーク

13 突起電極

21 第1絶縁性基材

22 第1導体配線

23 第1外部電極列

24 第1配線基板

25 第2絶縁性基材

26 第2導体配線

27 第2外部電極列

28 第2配線基板

31 絶縁性基材

32 導体配線

33 検査用電極列

34 配線基板

35 検査用プローブ

41 絶縁性基材

42 導体配線

43 接合用配線列

44 配線基板

45 半導体素子

46 素子電極

【技術分野】

【0001】

本発明は、半導体素子が配線基板に接合された構成を有する半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

配線基板上に半導体素子を載置し、配線基板上に形成された接合用配線と半導体素子上の素子電極とを接合した半導体装置、及びその製造方法が知られている。配線基板には、主に価格が安い有機機材が用いられることが多い。有機基材は一般的に、シリコンやガラス等の無機材料と比較して、温度や湿度の変化による寸法変化が大きい。そのことが、シリコン等からなる半導体素子や、ガラス等からなる液晶パネル等との接合ピッチを微細化する妨げとなっている。例えば、現在比較的微細接合が進んでいる液晶用のCOFパッケージにおいて、ポリイミドからなる配線基板と半導体素子との接合ピッチは30μm程度、液晶パネルとの接合ピッチは50μm程度が量産可能な水準である。それ以下のピッチでの接合のためには、配線基板の寸法変化を吸収する工夫が必要である。このため、温度や湿度による寸法調整の他、接合部の構造により寸法変化を吸収する工夫が考案されてきた(例えば特許文献1参照)。

【0003】

以下、従来の半導体装置とその製造方法について、図11を参照しながら説明する。図11(a)において、配線基板44は、絶縁性基材41、絶縁性基材41上に形成された導体配線42、及び接合用配線列43からなる。接合用配線列43は、導体配線42を延在して形成されている。配線基板44に搭載された半導体素子45の主面上には、素子電極46が形成されている。素子電極46は半導体素子45の中心から外に向かって傾けて形成されており、接合用配線列43と交差して接合されている。

【0004】

従来の半導体装置では図11(b)に示すように、配線基板44のY方向の寸法が設計値Y0より2yだけ延び、接合用配線列43のピッチが広くなった場合でも、接合用配線列43が素子電極46と交差している。そのため、接合用配線列43が素子電極46から外れる事無く接合することができる。配線基板44のY方向の寸法が、設計値Y0より縮んだ場合も同様である。

【特許文献1】特許第3357296号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら上記従来の半導体装置では、図11(c)に示すように、配線基板44のY方向の寸法が図11(b)の場合よりも更に大きい寸法2y’延びた場合、接合用配線列43が素子電極46と交差しなくなるため、接合用配線列43が素子電極46と接合できなくなるという課題があった。

【0006】

本発明は、上記従来の問題を解決するものであり、原理的に配線基板の寸法変化量による制限を受けず、接合用配線列と素子電極列の間にずれを生じることなく接合できる半導体装置、及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の第1の構成の半導体装置は、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、前記配線基板上に載置された半導体素子と、前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備える。前記第1接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように連続的に変化しており、前記第2接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように連続的に変化している。

【0008】

また、本発明の半導体装置の製造方法は、第1辺に沿って設けられた第1素子電極列と、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列とが主面上に形成された半導体素子を準備する工程と、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有し、前記導体配線を延在させて、前記半導体素子を載置する半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように形成した第1接合用配線列と、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように形成した第2接合用配線列を備えた配線基板を準備する工程と、前記半導体素子を前記配線基板に載置する際に、前記配線基板の前記半導体素子の前記第1辺に平行な方向に寸法変化があった場合、前記半導体素子を前記第1辺と直交する方向に沿って、同方向における基準位置から前記寸法変化分に比例した距離を移動させて、前記第1接合用配線列のピッチが前記第1素子電極列のピッチと等しくなり、かつ前記第2接合用配線列のピッチが前記第2素子電極列のピッチと等しくなる位置で、前記第1接合用配線列と前記第1素子電極列及び、前記第2接合用配線列と前記第2素子電極列とを接合する工程とを含む。

【0009】

本発明の第2の構成の半導体装置は、絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、前記配線基板上に載置された半導体素子と、前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備える。前記第1接合用配線列及び前記第2接合用配線列を構成する各導体配線のピッチは均一であり、前記第1素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第1接合用配線列を構成する各導体配線のピッチより広く、前記半導体素子の中心側の先端では前記各導体配線のピッチより狭くなるように連続的に変化しており、前記第2素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第2接合用配線列を構成する各導体配線のピッチより狭く、前記半導体素子の中心側の先端では前記各導体配線のピッチより広くなるように連続的に変化している。

【0010】

本発明の第3の構成の半導体装置は、第1絶縁性基材、前記第1絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第1絶縁性基材の一端に配列して形成された第1外部電極列を有する第1配線基板と、前記第1配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子と、第2絶縁性基材、前記第2絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第2絶縁性基材の一端に配列して形成された第2外部電極列とを有する第2配線基板とを備え、前記第1外部電極列のピッチは前記第1配線基板の中央から前記第1外部電極列が形成された一辺に向かって広くなるように形成され、前記第2外部電極列のピッチは前記第2配線基板の中央から前記第2外部電極列が形成された一辺に向かって狭くなるように形成され、前記第1配線基板の前記第1外部電極列を形成した一辺と、前記第2配線基板の前記第2外部電極列を形成した一辺とが相対し、前記第1外部電極列と前記第2外部電極列とが同一ピッチとなる部分で接合されている。

【0011】

本発明の第4の構成の半導体装置は、絶縁性基材と、前記絶縁性基材上に形成された複数本の導体配線、及び前記複数の導体配線を延在して形成された検査用電極列を備えた配線基板と、前記配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子とを備え、前記検査用電極列のピッチは前記配線基板の電気特性を検査するための検査用プローブと接触する基準位置では前記検査用プローブのピッチと等しく、前記基準位置から一方に離れるに従い前記検査用プローブのピッチよりも広く形成されており、前記基準位置から前記検査用電極列のピッチが広く形成されている方向と逆方向に離れるに従い狭く形成されている。

【発明の効果】

【0012】

本発明の半導体装置及びその製造方法によれば、接合用配線列のピッチが半導体素子電極のピッチに対して広い部分と狭い部分を連続的に有しており、また、半導体素子の2辺に対し、接合用配線列のピッチ変化の方向が同一である。それにより、半導体素子を配線基板に載置する際に第1辺に平行な方向に寸法変化があった場合、第1辺と直交する方向に沿って寸法変化分に比例した距離を移動させることで、接合用配線列のピッチと素子電極列のピッチとを等しくできるため、原理的に配線基板の寸法変化量による制限を受けず、接合用配線列と素子電極列とをずれを生じずに接合することが可能である。

【発明を実施するための最良の形態】

【0013】

本発明は上記構成を基本として、以下のような態様をとることができる。

【0014】

すなわち、第1の構成の半導体装置において、前記第1接合用配線列及び前記第2接合用配線列は、各々前記第1素子電極列及び前記第2素子電極列と各々接合された位置から、更に前記半導体素子の中心に向かって延在する構成とすることができる。

【0015】

また、前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度の関係が、いずれか一方の角度が他方の角度よりも小さく設定されている構成とすることができる。

【0016】

また、前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度が等しく設定されている構成とすることができる。

【0017】

また、前記第1素子電極列及び第2素子電極列を構成する個々の素子電極は円柱状の突起電極である構成とすることができる。

【0018】

また、半導体装置の製造方法において、前記配線基板上に、前記半導体素子の前記第1辺に沿った方向において基準距離を隔てて第1認識マーク及び第2認識マークを設け、前記配線基板の前記半導体素子の前記第1辺に平行な方向の寸法変化を、前記第1認識マークと前記第2認識マーク間の前記第1辺に沿った方向の前記基準距離からの変移により求めることができる。

【0019】

以下、本発明の実施形態について図面を参照しながら説明する。

【0020】

(第1の実施形態)

図1(a)は、本発明の第1の実施形態にかかる半導体装置の平面図である。図1(a)において、配線基板3は、絶縁性基材1と、絶縁性基材1の表面に形成された導体配線2とを有する。配線基板3には更に、第1接合用配線列9、及び第2接合用配線列10が設けられている。配線基板3に載置された半導体素子4の主面上には、半導体素子4の第1辺6に沿って第1素子電極列5が配列され、第1辺6と対向する第2辺8に沿って第2素子電極列7が配列されている。

【0021】

第1接合用配線列9は、導体配線2を延在して形成され、絶縁性基材1上の半導体素子4が載置された領域の外側から、半導体素子4の第1辺6を横切り第1素子電極列5と各々接合され、更に半導体素子4の中心に向かって延在している。

【0022】

第2接合用配線列10は、導体配線2を延在して形成され、絶縁性基材1上の半導体素子4が載置された領域の外側から半導体素子4の第2辺8を横切り第2素子電極列7と各々接合され、更に半導体素子4の中心に向かって延在している。

【0023】

第1接合用配線列9を構成する各々の導体配線2のピッチは、半導体素子4が載置された領域の外側では第1素子電極列5のピッチより広く、第1素子電極列5との接合箇所では第1素子電極列5のピッチと等しく、第1素子電極列5との接合箇所より半導体素子4の中心側では第1素子電極列5のピッチより狭くなるように、連続的に変化させて形成されている。

【0024】

一方、第2接合用配線列10を構成する各々の導体配線2のピッチは、半導体素子4が載置された領域の外側では第2素子電極列7のピッチより狭く、第2素子電極列7との接合箇所では第2素子電極列7のピッチと等しく、第2素子電極列7との接合箇所より半導体素子4の中心側では第2素子電極列7のピッチより広くなるように、連続的に変化させて形成されている。

【0025】

ここでは、一般的な液晶用パッケージに用いられるCOF(Chip On Film)パッケージとして、例えば絶縁性基材1は厚み40μm程度のポリイミド、導体配線2は厚み8μm、幅15μm程度のCu上に無電解Snめっきを形成したもの、素子電極列5、7は高さ15μm程度の電解Auめっきバンプを用いた場合を例としている。

【0026】

次に、本実施の形態に係る半導体装置の製造方法について、図1(b)、(c)を参照しながら説明する。図1(b)、(c)において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号が付されている。なお、半導体素子4の第1辺6に平行な方向をY方向、直交する方向をX方向とする。

【0027】

図1(b)は、図1(a)に比較して、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交するX方向に沿って、図1(a)の位置(基準位置)からY方向の寸法変化であるyに比例した距離dx=αyだけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しい位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することができる。

【0028】

図1(c)は、図1(b)に比較して、配線基板3のY方向の寸法が更に延びた場合を示す。この場合でも、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図1(a)の位置からY方向の寸法変化であるy’に比例した距離dx=αy’だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しくなる位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することがでる。

【0029】

以上のように本実施形態によれば、原理的に配線基板のY方向の寸法変化量による制限を受けることなく、第1及び第2接合用配線列9、10と、第1及び第2素子電極列5、7とを、ずれを解消して接合することができる。

【0030】

ここで、一般的には、Y方向の寸法変化であるy、y’は配線基板の製造ロット内では大きな差異では無い為、配線基板の出荷検査もしくは受け入れ検査時の寸法測定結果から、移動量dxをロット毎に設定することができる。

【0031】

なお、図1の例は、第1接合用配線列9及び第2接合用配線列10の対応する位置の導体配線の角度が、互いに等しい構成を示したものである。これは、Y方向には寸法の変化があるが、X方向には寸法の変化が実質的に無いと考えられる場合の態様である。後述するように、X方向にも寸法の変化が実質的に発生する場合には、それに応じて第1接合用配線列9及び第2接合用配線列10の角度を調整する必要がある。

【0032】

(第2の実施形態)

図2(a)、(b)は、本発明の第2の実施形態にかかる半導体装置の平面図である。同図において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。

【0033】

本実施形態の第1の実施形態との相違点は、図2(a)に示すように、第1接合用配線列9を構成する任意の第1導体配線9aが半導体素子の第1辺6と交差する第1角度θ1が、第2接合用配線列10を構成し第1導体配線9aと対向する位置に形成された第2導体配線10aが半導体素子4の第2辺8と交差する第2角度θ2よりも小さいことである。

【0034】

配線基板3の寸法変化は、一般的にはY方向にもX方向にも発生する。図2(b)に示すように、配線基板3のY方向の寸法が2y延びると同時に、配線基板3のX方向の寸法がx延びた場合には、半導体素子4を第1辺6と直交する方向に沿って図2(a)の位置からyに比例した距離だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しくなる位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを適切な相互関係で接合することができる。

【0035】

すなわち、本発明の第2の実施形態にかかる半導体装置では、配線基板3のX方向の寸法変化にも対応して、第1及び第2接合用配線列9、10と第1及び第2素子電極列5、7とをずれを解消して接合することができる。

【0036】

ここで比較の為に、配線基板3のX方向の寸法変化に対応していない本発明の第1の実施形態にかかる半導体装置について、図2(b)と同様にX方向の寸法がxだけ延びた場合を、同一の縮尺で図2(c)に図示する。第1接合用配線列9が第1素子電極列5のピッチと合う位置に半導体素子4を移動させた場合は、第2接合用配線列10が第2素子電極列7とずれてしまい、接合できないことが判る。

【0037】

なお、第1角度θ1と第2角度θ2の大きさの関係は、上記構成と逆であってもよい。その場合は、半導体素子4の基準位置、及び移動させる向きを上記構成に対して左右反転させればよい。

【0038】

(第3の実施形態)

図3は、本発明の第3の実施形態にかかる半導体装置の平面図、図4は図3の要部拡大図である。図3、図4において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。但し、図3、図4においては、第1素子電極5a及び第2素子電極7aが、円柱形状となっている点が、図1(a)に示した半導体装置とは相違する。

【0039】

第1の実施形態の場合、第1及び第2素子電極5a、7aと第1及び第2接合用配線列9、10の交差角度は、図1(a)〜(c)に示したように半導体素子の配置位置で変化する。これに対して、本実施形態の第1及び第2素子電極5a,7aのように円柱形状とすることで、図4の(a)、(b)に示すように、第1素子電極5aと第1接合用配線列9との交差角度によらず、第1素子電極5aと第1接合用配線列9との接合面積(斜線部分)は、第1素子電極5aを構成する円柱の直径と第1接合用配線列9の幅で決定される。

【0040】

このため、図4に図示するように全ての位置で接合面積を同一にすることもできるが、例えば図5に示す様に、接合後に印加される応力が大きい半導体素子4の端部に向かうに従い、円柱の直径を大きくすることで接合面積を増加させて、接合強度を確保することもできる。

【0041】

なお、電解Auめっきを用いれば、露光マスク形状を円形にすることで、第1素子電極5a、第2素子電極7aを容易に円柱形状に形成することができる。

【0042】

(第4の実施形態)

図6は、本発明の第4の実施形態にかかる半導体装置の製造方法を示す平面図である。図6において、図1(a)に示した半導体装置の要素と同一の要素には、同一の参照符号を付して、説明の繰り返しを省略する。本実施形態の構成では、配線基板1上に、第1認識マーク11、第2認識マーク12が形成されている。半導体素子4の第1辺6に沿った方向における、第1認識マーク11と第2認識マーク12間の距離はW0である。

【0043】

図6(b)は図6(a)に比較し、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4の第1辺6に沿った方向の第1認識マーク11と認識マーク12間の距離はW1となり、配線基板3の半導体素子4の第1辺6に平行な方向の寸法変化yは、(W1−W0)に比例する。

【0044】

従って、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図6(a)の位置からY方向の寸法変化であるyに比例した距離dx=αy=α’(W1−W0)だけ移動させる。それにより、第1接合用配線列9のピッチが第1素子電極列5のピッチと等しく、かつ第2接合用配線列10のピッチが第2素子電極列7のピッチと等しい位置関係に調整することができる。その結果、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係で接合することができる。

【0045】

この第4の実施形態によれば、実際に接合に用いる配線基板3の第1及び第2認識マーク11、12の距離の変移(W1−W0)に応じて、半導体素子4の移動距離dxを最適な値に設定することができる。そのため、ロット毎にdxを設定していた第1の実施形態と比較し、更に接合の位置精度を向上させることができる。

【0046】

なお、第1〜第3の実施形態においては、配線基板3上の第1及び第2接合用配線列9、10に角度を持たせた形態としたのに対して、図7に示すように、半導体素子4上の第1及び第2素子電極5、7に角度を持たせた形態としても良い。

【0047】

すなわち図7(a)に示すように、導体配線2は均一のピッチで直線状に延在して形成され、半導体素子4が載置された領域の左右の外側から、それぞれ半導体素子4の第1辺6および第2辺8を横切り、第1素子電極列5及び第2素子電極列7と各々接合されている。第1素子電極列5及び第2素子電極列7を構成する各素子電極は、第1辺6及び第2辺8を横切る方向を長手方向とする細長い形状を有する。

【0048】

第1素子電極列5を構成する各素子電極のピッチは、半導体素子4の外縁近傍では導体配線2のピッチより広く、導体配線2との接合箇所では導体配線2のピッチと等しく、導体配線2との接合箇所より半導体素子4の中心側では導体配線2のピッチより狭くなるように、連続的に変化している。

【0049】

一方、第2素子電極列7を構成する各素子電極のピッチは、半導体素子4の外縁近傍では導体配線2のピッチより狭く、導体配線2との接合箇所では導体配線2のピッチと等しく、導体配線2との接合箇所より半導体素子4の中心側では導体配線2のピッチより広くなるように、連続的に変化している。

【0050】

図7(b)は、図7(a)に比較して、配線基板3のY方向の寸法が2yだけ延びた場合を示す。この場合、半導体素子4を配線基板3に載置する際に、半導体素子4を第1辺6と直交する方向に沿って、図7(a)の位置からY方向の寸法変化であるyに比例した距離dx=αyだけ移動する。それにより、第1素子電極列5及び第2素子電極列7のピッチが、導体配線2のピッチと等しい位置関係に調整することができる。その結果、導体配線2と第1素子電極列5及び第2素子電極列7とを、適切な相互関係で接合することができる。

【0051】

この場合、配線基板3上の導体配線2の側に突起電極13を設ける必要があるが、例えば図8に示す様に、導体配線2を横切り、導体配線2の両側の絶縁基材1上に亘って形成された突起電極13(特許第3565835号公報参照)を用いても良い。

【0052】

(第5の実施形態)

図9は、本発明の第5の実施形態にかかる半導体装置を示す平面図である。図9において、第1配線基板24は、第1絶縁性基材21、第1絶縁性基材21上に形成された導体配線22、及び第1外部電極列23からなる。第1外部電極列23は、複数の導体配線22を延在させて、第1絶縁性基材21の一端に配列して形成されている。第2配線基板28は、第2絶縁性基材25、第2絶縁性基材25上に形成された導体配線26、及び第2外部電極列27からなる。第2外部電極列27は、複数の導体配線26を延在させて、第2絶縁性基材25の一端に配列して形成されている。

【0053】

第1外部電極列23のピッチは、第1配線基板24の中央から第1外部電極列23が形成された一辺に向かって広くなるように設定されている。第2外部電極列27のピッチは、第2配線基板28の中央から第2外部電極列27が形成された一辺に向かって狭くなるように設定されている。第1配線基板24の第1外部電極列23を形成した一辺と、第2配線基板28の第2外部電極列27を形成した一辺とが相対向し、第1外部電極列23と第2外部電極列27とが同一ピッチとなる部分で接合されている。

【0054】

本実施形態では、第1配線基板24がポリイミドで形成された液晶用COFパッケージ、第2配線基板が液晶用ガラス基板である場合を例としている。第1外部電極列23としてCu箔上にSnめっきを形成し、第2外部電極列27としてAlを用い、各々をACF(Anisotropic Conductive Film)を用いて接合する。

【0055】

なお、本実施形態は、第1配線基板24を液晶用ガラス基板、第2配線基板を液晶用COFパッケージと置き換えても、全く同様に適用して同一の機能を持たせることができる。

【0056】

本実施の形態に係る半導体装置の製造方法の特徴は、第1の実施形態と同様であり、図9(b)は、図9(a)と比較して、配線基板24のY方向の寸法が2yだけ延びた場合を示す。図9(c)は、図9(a)と比較して、配線基板24のY方向の寸法が2y’だけ縮んだ場合を示す。

【0057】

いずれの場合も、配線基板24のX方向の位置をY方向の寸法変化に比例した距離dx=βy、あるいはdx’=βy’だけ移動することで、第1外部電極列23と第2外部電極列27とが同一ピッチとなる部分で接合することができる。

【0058】

本実施形態の場合は第1〜第4の実施形態と異なり、第1外部電極列23と第2外部電極列27のいずれにも突起電極を設ける必要は無く、前述のようにCOF等のパッケージと液晶ガラス基板との接合に用いることができる。

【0059】

(第6の実施形態)

図10は、本発明の第6の実施形態にかかる半導体装置を示す平面図である。図10において、配線基板34は、絶縁性基材31、絶縁性基材31上に形成された導体配線32、及び検査用電極列33を備えている。検査用電極列33は、複数の導体配線32を延在させて形成されている。35は、検査用電極列33に接触させる検査用プローブである。

【0060】

検査用電極列33のピッチは、検査用プローブ35と接触する位置では検査用プローブ35のピッチと等しく、検査用プローブ35と接触する位置から一方に離れるに従い検査用プローブ35のピッチよりも広く形成されており、その逆方向に離れるに従い狭く形成されている。

【0061】

本実施形態では、配線基板34が液晶用COFパッケージを構成する一部分である場合を例としている。検査用電極列33としてCu箔上にSnめっきを形成し、検査用プローブ35としてタングステンを用いて電気的検査を実施する。

【0062】

本実施の形態に係る半導体装置の検査方法において、検査用電極列33に対して検査用プローブ35を整合させて接触させる方法は、第1の実施形態において、第1接合用配線列9と第1素子電極列5及び、第2接合用配線列10と第2素子電極列7とを、適切な相互関係に整合させる方法と同様である。すなわち、図10(b)は図10(a)と比較し、配線基板34のY方向の寸法が2yだけ延びた場合、図10(c)は図10(a)と比較し、配線基板34のY方向の寸法が2y’だけ縮んだ場合を示す。

【0063】

いずれの場合も、配線基板34のX方向の位置を、Y方向の寸法変化に比例した距離dxだけ移動させることで、検査用電極列33と検査用プローブ35とが同一ピッチとなる部分で両者を接触させることができる。

【産業上の利用可能性】

【0064】

本発明の半導体装置は、寸法変化の比較的大きな有機基材上に形成されたパターンへの精密な位置合わせ技術として有用である。

【図面の簡単な説明】

【0065】

【図1】本発明の第1の実施形態における半導体装置を示す平面図

【図2】(a)、(b)は、本発明の第2の実施形態における半導体装置を示す平面図、(c)は比較のために従来例の半導体装置を示す平面図

【図3】本発明の第3の実施形態における半導体装置を示す平面図

【図4】同実施形態における半導体装置を示す要部拡大図

【図5】同実施形態における半導体装置を示す平面図

【図6】本発明の第4の実施形態における半導体装置を示す平面図

【図7】本発明の第5の実施形態における半導体装置を示す平面図

【図8】同実施形態で用いられる突起電極の例を示す斜視図

【図9】本発明の第6の実施形態における半導体装置を示す平面図

【図10】本発明の第7の実施形態における半導体装置を示す平面図

【図11】従来の半導体装置を示す平面図

【符号の説明】

【0066】

1 絶縁性基材

2 導体配線

3 配線基板

4 半導体素子

5、5a 第1素子電極列

6 第1辺

7、7a 第2素子電極列

8 第2辺

9 第1接合用配線列

9a 第1導体配線

10 第2接合用配線列

10a 第2導体配線

11 第1認識マーク

12 第2認識マーク

13 突起電極

21 第1絶縁性基材

22 第1導体配線

23 第1外部電極列

24 第1配線基板

25 第2絶縁性基材

26 第2導体配線

27 第2外部電極列

28 第2配線基板

31 絶縁性基材

32 導体配線

33 検査用電極列

34 配線基板

35 検査用プローブ

41 絶縁性基材

42 導体配線

43 接合用配線列

44 配線基板

45 半導体素子

46 素子電極

【特許請求の範囲】

【請求項1】

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、

前記配線基板上に載置された半導体素子と、

前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、

前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、

前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、

前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備え、

前記第1接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように連続的に変化しており、

前記第2接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように連続的に変化していることを特徴とする半導体装置。

【請求項2】

前記第1接合用配線列及び前記第2接合用配線列は、各々前記第1素子電極列及び前記第2素子電極列と各々接合された位置から、更に前記半導体素子の中心に向かって延在している請求項1記載の半導体装置。

【請求項3】

前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度の関係が、いずれか一方の角度が他方の角度よりも小さく設定されている請求項1記載の半導体装置。

【請求項4】

前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度が等しく設定されている請求項1記載の半導体装置。

【請求項5】

前記第1素子電極列及び第2素子電極列を構成する個々の素子電極は円柱状の突起電極である請求項1〜4のいずれか1項記載の半導体装置。

【請求項6】

第1辺に沿って設けられた第1素子電極列と、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列とが主面上に形成された半導体素子を準備する工程と、

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有し、前記導体配線を延在させて、前記半導体素子を載置する半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように形成した第1接合用配線列と、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように形成した第2接合用配線列を備えた配線基板を準備する工程と、

前記半導体素子を前記配線基板に載置する際に、前記配線基板の前記半導体素子の前記第1辺に平行な方向に寸法変化があった場合、前記半導体素子を前記第1辺と直交する方向に沿って、同方向における基準位置から前記寸法変化分に比例した距離を移動させて、前記第1接合用配線列のピッチが前記第1素子電極列のピッチと等しくなり、かつ前記第2接合用配線列のピッチが前記第2素子電極列のピッチと等しくなる位置で、前記第1接合用配線列と前記第1素子電極列及び、前記第2接合用配線列と前記第2素子電極列とを接合する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項7】

前記配線基板上に、前記半導体素子の前記第1辺に沿った方向において基準距離を隔てて第1認識マーク及び第2認識マークを設け、

前記配線基板の前記半導体素子の前記第1辺に平行な方向の寸法変化を、前記第1認識マークと前記第2認識マーク間の前記第1辺に沿った方向の前記基準距離からの変移により求める請求項6記載の半導体装置の製造方法。

【請求項8】

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、

前記配線基板上に載置された半導体素子と、

前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、

前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、

前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、

前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備え、

前記第1接合用配線列及び前記第2接合用配線列を構成する各導体配線のピッチは均一であり、

前記第1素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第1接合用配線列を構成する各導体配線のピッチより広く、前記半導体素子の中心側の先端では前記各導体配線のピッチより狭くなるように連続的に変化しており、

前記第2素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第2接合用配線列を構成する各導体配線のピッチより狭く、前記半導体素子の中心側の先端では前記各導体配線のピッチより広くなるように連続的に変化していることを特徴とする半導体装置。

【請求項9】

第1絶縁性基材、前記第1絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第1絶縁性基材の一端に配列して形成された第1外部電極列を有する第1配線基板と、

前記第1配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子と、

第2絶縁性基材、前記第2絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第2絶縁性基材の一端に配列して形成された第2外部電極列とを有する第2配線基板とを備え、

前記第1外部電極列のピッチは前記第1配線基板の中央から前記第1外部電極列が形成された一辺に向かって広くなるように形成され、前記第2外部電極列のピッチは前記第2配線基板の中央から前記第2外部電極列が形成された一辺に向かって狭くなるように形成され、

前記第1配線基板の前記第1外部電極列を形成した一辺と、前記第2配線基板の前記第2外部電極列を形成した一辺とが相対し、前記第1外部電極列と前記第2外部電極列とが同一ピッチとなる部分で接合されていることを特徴とする半導体装置。

【請求項10】

絶縁性基材、前記絶縁性基材上に形成された複数本の導体配線、及び前記複数の導体配線を延在して形成された検査用電極列を備えた配線基板と、

前記配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子とを備え、

前記検査用電極列のピッチは前記配線基板の電気特性を検査するための検査用プローブと接触する基準位置では前記検査用プローブのピッチと等しく、前記基準位置から一方に離れるに従い前記検査用プローブのピッチよりも広く形成されており、前記基準位置から前記検査用電極列のピッチが広く形成されている方向と逆方向に離れるに従い狭く形成されていることを特徴とする半導体装置。

【請求項1】

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、

前記配線基板上に載置された半導体素子と、

前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、

前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、

前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、

前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備え、

前記第1接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように連続的に変化しており、

前記第2接合用配線列を構成する各々の導体配線のピッチは、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように連続的に変化していることを特徴とする半導体装置。

【請求項2】

前記第1接合用配線列及び前記第2接合用配線列は、各々前記第1素子電極列及び前記第2素子電極列と各々接合された位置から、更に前記半導体素子の中心に向かって延在している請求項1記載の半導体装置。

【請求項3】

前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度の関係が、いずれか一方の角度が他方の角度よりも小さく設定されている請求項1記載の半導体装置。

【請求項4】

前記第1接合用配線列を構成する任意の第1導体配線が前記半導体素子の前記第1辺と交差する第1角度と、前記第2接合用配線列を構成し前記第1導体配線と対向する位置に形成された第2導体配線が前記半導体素子の前記第2辺と交差する第2角度が等しく設定されている請求項1記載の半導体装置。

【請求項5】

前記第1素子電極列及び第2素子電極列を構成する個々の素子電極は円柱状の突起電極である請求項1〜4のいずれか1項記載の半導体装置。

【請求項6】

第1辺に沿って設けられた第1素子電極列と、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列とが主面上に形成された半導体素子を準備する工程と、

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有し、前記導体配線を延在させて、前記半導体素子を載置する半導体素子領域の外側では前記第1素子電極列のピッチより広く、前記半導体素子の中心側の先端では前記第1素子電極列のピッチより狭くなるように形成した第1接合用配線列と、前記半導体素子領域の外側では前記第2素子電極列のピッチより狭く、前記半導体素子の中心側の先端では前記第2素子電極列のピッチより広くなるように形成した第2接合用配線列を備えた配線基板を準備する工程と、

前記半導体素子を前記配線基板に載置する際に、前記配線基板の前記半導体素子の前記第1辺に平行な方向に寸法変化があった場合、前記半導体素子を前記第1辺と直交する方向に沿って、同方向における基準位置から前記寸法変化分に比例した距離を移動させて、前記第1接合用配線列のピッチが前記第1素子電極列のピッチと等しくなり、かつ前記第2接合用配線列のピッチが前記第2素子電極列のピッチと等しくなる位置で、前記第1接合用配線列と前記第1素子電極列及び、前記第2接合用配線列と前記第2素子電極列とを接合する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項7】

前記配線基板上に、前記半導体素子の前記第1辺に沿った方向において基準距離を隔てて第1認識マーク及び第2認識マークを設け、

前記配線基板の前記半導体素子の前記第1辺に平行な方向の寸法変化を、前記第1認識マークと前記第2認識マーク間の前記第1辺に沿った方向の前記基準距離からの変移により求める請求項6記載の半導体装置の製造方法。

【請求項8】

絶縁性基材及び前記絶縁性基材の表面に形成された複数本の導体配線を有する配線基板と、

前記配線基板上に載置された半導体素子と、

前記半導体素子の主面上に、前記半導体素子の第1辺に沿って設けられた第1素子電極列と、

前記半導体素子の主面上に、前記第1辺と対向する第2辺に沿って設けられた第2素子電極列と、

前記導体配線が延在して形成され、前記絶縁性基材上の前記半導体素子が載置された半導体素子領域の外側から前記半導体素子の前記第1辺を横切り前記第1素子電極列と各々接合された第1接合用配線列と、

前記導体配線が延在して形成され、前記半導体素子領域の外側から前記半導体素子の前記第2辺を横切り前記第2素子電極列と各々接合された第2接合用配線列とを備え、

前記第1接合用配線列及び前記第2接合用配線列を構成する各導体配線のピッチは均一であり、

前記第1素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第1接合用配線列を構成する各導体配線のピッチより広く、前記半導体素子の中心側の先端では前記各導体配線のピッチより狭くなるように連続的に変化しており、

前記第2素子電極列を構成する各素子電極は、前記第1辺及び前記第2辺を横切る方向を長手方向とする細長い形状を有し、前記各素子電極間のピッチは、前記半導体素子の外縁側では前記第2接合用配線列を構成する各導体配線のピッチより狭く、前記半導体素子の中心側の先端では前記各導体配線のピッチより広くなるように連続的に変化していることを特徴とする半導体装置。

【請求項9】

第1絶縁性基材、前記第1絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第1絶縁性基材の一端に配列して形成された第1外部電極列を有する第1配線基板と、

前記第1配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子と、

第2絶縁性基材、前記第2絶縁性基材の表面に形成された複数本の導体配線、及び前記複数の導体配線を延在して前記第2絶縁性基材の一端に配列して形成された第2外部電極列とを有する第2配線基板とを備え、

前記第1外部電極列のピッチは前記第1配線基板の中央から前記第1外部電極列が形成された一辺に向かって広くなるように形成され、前記第2外部電極列のピッチは前記第2配線基板の中央から前記第2外部電極列が形成された一辺に向かって狭くなるように形成され、

前記第1配線基板の前記第1外部電極列を形成した一辺と、前記第2配線基板の前記第2外部電極列を形成した一辺とが相対し、前記第1外部電極列と前記第2外部電極列とが同一ピッチとなる部分で接合されていることを特徴とする半導体装置。

【請求項10】

絶縁性基材、前記絶縁性基材上に形成された複数本の導体配線、及び前記複数の導体配線を延在して形成された検査用電極列を備えた配線基板と、

前記配線基材上に搭載され、素子電極が前記複数の導体配線と電気的に接続された半導体素子とを備え、

前記検査用電極列のピッチは前記配線基板の電気特性を検査するための検査用プローブと接触する基準位置では前記検査用プローブのピッチと等しく、前記基準位置から一方に離れるに従い前記検査用プローブのピッチよりも広く形成されており、前記基準位置から前記検査用電極列のピッチが広く形成されている方向と逆方向に離れるに従い狭く形成されていることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2009−147019(P2009−147019A)

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願番号】特願2007−321210(P2007−321210)

【出願日】平成19年12月12日(2007.12.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願日】平成19年12月12日(2007.12.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]