半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、金属ゲート電極を用いた半導体装置、及びその製造方法に関する。

【背景技術】

【0002】

半導体デバイスの高性能化、高集積化に伴う実効的なゲート絶縁膜薄膜化の要求を満たすためには、今後メタルゲート電極と高誘電率(high-k)ゲート絶縁膜の技術導入が必須である。メタルゲート/high-kゲート絶縁膜を用いたMISトランジスタにおいて適正な性能を得るためには、メタルゲート材料の実効仕事関数φeffがnチャネル型MISトランジスタにおいては3.9〜4.3eV程度、pチャネル型MISトランジスタにおいては4.8〜5.2eV程度であることが必要である(例えば、特許文献1参照)。

【0003】

しかしながら、nチャネル型MISトランジスタに適した低い仕事関数を有する金属は、一般にトランジスタ形成工程に必須な熱工程に対して安定でなく、特にhigh-kゲート絶縁膜上で、トランジスタ形成後にミッドギャップ(mid-gap)付近(4.6eV近傍)のφeffとなり、nチャネル型MISトランジスタに適した3.9〜4.3eV程度のφeffを実現することが困難である。そのため、nチャネル型MISトランジスタの閾値電圧を十分低くすることが出来ず、このことはメタルゲート電極/high-kゲート絶縁膜の技術導入に当たって大きな問題となっている。

【特許文献1】特開2007−173412号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

前述のように、high-kゲート絶縁膜/メタルゲート電極を用いた場合に、nチャネル型MISトランジスタにおいて低い閾値電圧を実現できないという問題が生じていた。本発明は、これを解決すべくなされたもので、nチャネル型MISトランジスタの閾値電圧が低減された半導体装置と、容易なプロセスを用いてこれを形成できる製造方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

上記課題を解決するために、本発明の半導体装置の第1は、半導体基板と、前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、前記半導体基板上に形成され、前記n型半導体領域とp型半導体領域とを露出するように夫々形成された第1と第2のトレンチを有する第1の絶縁層と、前記第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、前記第1のトレンチの側壁と底部に沿って形成され、前記ゲート絶縁膜を介して形成された第1の金属層と、前記第2のトレンチの側壁と底部に沿って形成され、前記ゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、前記第2の金属層上に内張りされたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層とを具備することを特徴とする。

【0006】

本発明の半導体装置の第2は、半導体基板と、前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、前記n型半導体層領域に形成された第1のゲート絶縁膜と、前記p型半導体層領域上に形成された第2のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の金属層と、前記第2のゲート絶縁膜上に、1モノレイヤー以上で1.5nm以下の厚さに形成された第2の金属層と、前記第2の金属層上に形成されたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層とを具備し、前記金属元素が前記p型半導体領域の前記ゲート絶縁膜中に存在することを特徴とする。

【0007】

本発明の半導体製造方法の第1は、素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の、前記n型半導体層領域に第1ダミーゲートを形成するとともに、前記p型半導体領域に第2ダミーゲートを形成する工程と、前記第1ダミーゲートの両側の前記n型半導体領域に、p型拡散層を形成する工程と、前記第2ダミーゲートの両側の前記p型半導体領域に、n型拡散層を形成する工程と、前記n型拡散層及び前記p型拡散層を覆うように、前記第1及び第2ダミーゲートの側部に絶縁膜を形成する工程と、前記第1及び第2ダミーゲートを除去することにより、前記絶縁層に第1及び第2のトレンチを形成する工程と、前記第1及び第2のトレンチの少なくとも底部に、第1と第2のゲート絶縁膜を夫々形成する工程と、前記第1のゲート絶縁膜上に第1の金属層を、前記第2のゲート絶縁膜上に第2の金属層を、1モノレイヤー以上1.5nm以下の厚さで夫々形成する工程と、前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程とを有することを特徴とする。

【0008】

本発明の半導体装置の製造方法の第2は、素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の前記n型半導体層領域及び前記p型半導体領域上に、第1と第2のゲート絶縁膜を夫々形成する工程と、前記第1と第2のゲート絶縁膜上に、第1の金属層と第2の金属層を1モノレイヤー以上で1.5nm以下に夫々形成する工程と、前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程と、前記第1のゲート絶縁膜、第1のl金属層と、第2のゲート絶縁膜、第2、第3の金属層とを加工し、第1と第2のゲート電極を夫々加工する工程と、前記第1と第2のゲート電極を夫々挟む前記n型半導体領域とp型半導体領域に、第1と第2のソース/ドレイン領域を形成する工程とを有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、メタルゲート電極を用いたnチャネル型MISトランジスタを含む半導体装置において、低い閾値電圧のnチャネル型MISトランジスタが実現され、容易なプロセスでこれを製造できる製造方法が提供される。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して本発明の実施形態について説明する。

【0011】

(第1の実施形態)

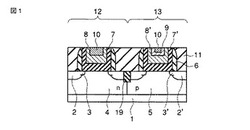

図1は、本発明の第1の実施形態に係るCMOS半導体装置の断面図である。Si基板1の表面領域には、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。前記n型及びp型半導体領域4,5は、所謂ウエルとして形成される。

【0012】

n型及びp型半導体領域4,5の表面上には、例えばHfSiONといった高誘電率(high-k)ゲート絶縁膜7及び7´が形成されている。n型半導体領域のゲート絶縁膜7上及びp型半導体領域上のゲート絶縁膜7´の上には、TaCxからなるゲート電極8及びTaCxを母体とするゲート電極8´が1モノレイヤー以上1.5nm以下に、夫々形成されている。ゲート電極8´やゲート絶縁膜7´はアルカリ土類金属元素、III族元素(例えば、Sc、Y、ランタノイド、アクチノイド)に属する元素を含有していてもよい。

【0013】

また、本実施形態においてゲート絶縁膜に接する形で形成されるゲート電極層を「下層ゲート電極」と記載することとする。なお、ここでゲート絶縁膜7及び7´、ゲート電極8及び8´と記載したのは、後の工程により結果的にn型半導体領域上の下層ゲート電極とp型半導体領域上の下層ゲート電極及びゲート絶縁膜に違いが生じる可能性があるためであり、n型、p型半導体領域上に夫々別々にゲート絶縁膜や下層ゲート電極を形成するプロセスを必要とするものではない。

【0014】

ゲート電極8´の上には、アルカリ土類金属元素、III族元素(例えば、Sc、Y、ランタノイド、アクチノイド)の少なくともいずれが1つの金属元素の単体、窒化物、炭化物、あるいは酸化物を含む層9が形成されている。トランジスタ形成工程を経ることでこの金属元素を含む層9から、p型半導体領域5の下層ゲート電極8´中やゲート絶縁膜7´中にアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素が拡散する可能性があるが、本実施形態の効果を得るために、p型半導体領域5の下層ゲート電極8´中やゲート絶縁膜7´中へのアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素の拡散が、必ずしも必要なわけではない。

【0015】

n型半導体領域4上のゲート電極8及びp型半導体領域上の層9の上には、さらにTiNx 、TaCx 、Wなどの高融点金属やポリシリコン、若しくはこれらの積層構造からなる層10が形成されている。なお、参照番号6は側壁絶縁膜、11は層間絶縁膜、19はSTI(shallow trench isolation)による素子分離領域である。以上のように、第1の実施形態の半導体装置は、所謂ゲートリプレースメントプロセス(ゲート作り替えプロセス)にて形成したデバイス特有の構造を持つ。

【0016】

図2は、TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施して作製されたMISキャパシタのCV特性と、TaC/Y,ErまたはTb/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施して作製されたMISキャパシタのCV特性とを比較したものである。ゲート電極中にY,Er若しくはTbからなる層を形成した場合には、ゲート電極がTaC単層からなる場合に比べCVが負方向に400mV程度シフトする。すなわち、フラットバンド電圧Vfbが−400mV程変調される。

【0017】

図3は、Er、YまたはYbを積層することによって得られる、Vfbシフト量のHfSiON膜厚依存性を示したものである。Vfbシフト量は以下の式

ΔVfb=(Vfb(TaC/Y, Er or Tb/TaC/HfSiON/Si))−(Vfb(TaC/HfSiON/Si))

で表わされる。

【0018】

図3に依れば、HfSiON膜厚にかかわらず、−400mV程度のVfb変調が、Y、ErもしくはTb積層により得られており、ゲート電極の仕事関数φeffが、3〜3.5eVほどの低い仕事関数を有する希土類元素Y、Er若しくはTbによって400mV程度低い方向に変調されたことを示している。このようにφeff変調を得るには、希土類元素はゲート絶縁膜/ゲート電極界面から、ある程度近い距離にあるゲート電極中に存在することが必要である。

【0019】

図4は、Er積層によるVfb変調量を、下層ゲート電極として形成したTaCx層の膜厚に対してプロットしたものである。下層ゲートTaCx層が1.5nm以下の領域でφeff変調量が急激に増加しており、希土類元素がゲート絶縁膜/ゲート電極界面から1.5nm以内の距離にあるゲート電極中に存在することにより、十分なφeff低下効果が得られることが分かる。すなわち、希土類元素を含む層が、1.5nm以下のTaCx上に形成されていれば、本実施形態の効果を得ることができる。

【0020】

上記の効果を得る手段としては、本実施形態のように薄い下層TaCx上に希土類元素からなる層を形成する方法のみでなく、ゲート絶縁膜表面上に直接希土類元素を含む金属層を形成する方法も挙げられるが、nチャネル型MISFETの閾値電圧低減効果を有する希土類含有層は、pチャネル型MISFETにおいて存在してはならず、そのため、pチャネル型MISFET領域の希土類含有層剥離工程を要する。ゲート絶縁膜表面の剥離工程は、ゲート絶縁膜の変質を引き起こし、電気特性に多大な影響を及ぼす危険性がある。

【0021】

これに比べ、下層メタルゲート上の希土類含有層剥離は、ゲート絶縁膜に接することの無い工程であるため、電気特性に対する影響が少なく、プロセス上の困難度が低い。その意味で、本実施形態の半導体装置は望ましい構造を有する。

【0022】

また、このプロセスメリットを得るためには、下層ゲート電極はゲート絶縁膜上に連続膜として存在していればよく、その意味で1モノレイヤー以上あればよい。また、ここでは下層ゲート電極8、8´としてTaCxを用いて説明したが、他のメタルゲート材料でも同様の効果を得ることが出来る。しかしながら、ゲート絶縁膜7、7´が剥離工程に曝されないというプロセスメリットを得るためには、下層ゲート電極8,8´はウェット剥離工程に耐性があることが求められる。TaCxは金属の中でも最も難溶解性の材料の1つである。この点で、下層ゲート電極としてTaCxは望ましい。

【0023】

ところで、前述のように、アルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む層9は、これら金属元素以外に、例えばSi,C,N,Oといった非金属元素を含んでいてもよい。然しながら、層9として金属元素とSiを含む層を、下層ゲート電極としてTaCx を用いる場合、金属元素とSiとの結合エネルギーよりも、金属元素とCとの結合エネルギーが大きいために、層9中においてSiと結合していた金属元素が、下層ゲート電極であるTaCx 中の余剰なCと結合し直すことによって、Si層が析出する虞がある。Si層は半導体であり、ゲート電極の抵抗増大を招く。そのため、下層ゲート電極がTaCx からなる場合、層9はSiを含まないものが望ましい。

【0024】

なお、金属元素とNの結合エネルギーや、金属元素とOの結合エネルギーは、金属元素とCの結合エネルギーよりも大きいため、層9がNとOを含んでいても層9の金属元素とN若しくはOとの結合が、下層TaCx 中の余剰Cとの結合にとって代わられることはない。また、Cは希土類金属との結合エネルギーがSiのそれより大きく、安定な金属化合物を形成する。

【0025】

また、この効果はY、ErもしくはTbといった元素に限り得られるものではなく、ランタノイド、アクチノイド及びアルカリ土類金属元素を含む層が、下層ゲートTaCx層上に形成されていればよい。図5に、TaC/HfSiON/Si及びTaC/希土類金属/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施した場合の、ゲート電極のVfbを示す。Efは用いたSi基板のフェルミエネルギーである。Y,Er若しくはTb以外の希土類元素でも、Vfb低下効果が得られることがわかる。

【0026】

なお、理由は後述するが、本実施形態に示す構造による限り、すなわち、ゲート電極の仕事関数φeff低下に伴うVfb低下効果によりnチャネル型MISトランジスタの閾値低減を得る場合、ゲートファーストプロセス(ゲート先作りプロセス)のように、ゲートスタック構造を1000℃程度の高温環境に曝してはならない。そのため、本実施形態はリプレースメントゲートプロセスによって形成されていなければならず、その結果、図1に示すようにリプレースメントゲートプロセスに特有の構造を持つ。

【0027】

また、本発明により−400mV程度のVfb変調効果が得られるため、下層ゲートのTaCxの仕事関数が4.7eV以下であれば、nチャネル型MISトランジスタに適した低いφeffを実現することが出来る。

【0028】

図6は、TaCxの組成と仕事関数との関係を示す図であるが、4.7eV以下の仕事関数を有するためには、TaCxのC原子密度は85atomic%以下であることが望ましい。

【0029】

図7に、実際に本発明による効果が得られた、TaC/Er/TaC/HfSiON構造形成後に450℃のフォーミングガスアニールを施したサンプルの、断面TEM像に示す。図7に記載した元素は、EELS(Electron Energy Loss Spectroscopy)スペクトルやEDX(Energy Dispersive X-ray Analysis)によりその箇所に存在することが確認されている。

【0030】

図8は、EELS,EDXで確認されたHf,Ta,O,Erの深さ方向のプロファイルを示す。図8にあわせて示すHAADF(high-angle annular dark field)の強度は、原子番号の二乗に比例するものであり、図7に示したTEM像におけるコントラストと対応している。HAADF強度と各元素のプロファイルの比較により、図7のTEM像に記載した元素とその箇所との対応が確認される。

【0031】

また、EELS測定では検出できない微量の元素は、SIMS分析による検出することが可能である。図9に、実際に本発明による効果が得られた、TaC/Er/TaC/HfSiON構造形成後に、450℃のフォーミングガスアニールを施したサンプルにおけるErプロファイルを、SIMS分析によって調べた結果を示す。

【0032】

ここでは、Si基板を剥離し、HfSiON/Si界面SiO2層側から分析する所謂バックサイドSIMS(Back-side-SIMS)を用いた。下層TaC電極上に形成されたEr層からErが拡散し、下層TaC中やHfSiON中にもErが存在する。このように、ゲートスタック構造中の希土類元素や、アルカリ土類元素は、TEM−EELSや裏面SIMSといった方法により検出可能である。

【0033】

本実施形態の半導体装置の製造方法は、トランジスタ製造に所謂リプレースメントゲートプロセスを用い、その製造工程を図10乃至図14に示す。まず、図10に示すように、半導体基板1に、STI構造の素子分離層19によって分離されたn型ウエル領域4及びp型ウエル領域5を形成する。続いて、n型ウエル領域4及びp型ウエル領域5にそれぞれダミーゲート(図示せず)を形成し、上記ダミーゲートをマスクとして、n型ウエル領域4にp型不純物を注入してp型エクステンション層3を形成するとともに、p型ウエル領域5にn型不純物を注入してn型エクステンション層3´を形成する。

【0034】

その後、上記ダミーゲートの側部にサイドウオール層6を形成する。そしてダミーゲート及びサイドウオール層13をマスクとしてn型ウエル領域4にp型不純物を注入してp型拡散層2を形成するとともに、p型ウエル領域5にn型不純物を注入してn型拡散層2´を形成する。

【0035】

続いて、層間絶縁膜11を堆積し、この層間絶縁膜11を平坦化する。その後、上記ダミーゲートを除去することにより図10に示す構造を得る。図10から分かるように、ダミーゲートが除去された後に、溝17が形成される。なお、拡散層2,2´上にサリサイド層が形成されていてもよい。

【0036】

次に、図11に示すように、例えばMOCVD(metal organic chemical vapor deposition)法により、ゲート絶縁層7を形成する。ここでは、ゲート絶縁層7としてHfSiONを用いる。次に、図12に示すように、例えば、スパッタ法やCVD法などの成膜方法を用いて、ゲート絶縁層7上に下層ゲート電極8を1モノレイヤー以上1.5nm以下に形成する。ここではスパッタ法によりTaCx 層を1.5nm形成する。

【0037】

次に、図13に示すように、n型半導体領域4上に酸化シリコンからなるマスク材18を形成する。その後、スパッタ法やCVD法などの成膜方法を用いて、下層ゲート電極8上及びマスク18上にアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む層9を形成し、リフトオフ法によりマスク材18とともにマスク材18上の層9を剥離する。これにより図14に示す構造を得る。

【0038】

その後は、n型半導体領域上の露出された下層ゲート電極8上及び層9上に、TaCx、W、TiNxなどの高融点金属やポリシリコン電極、若しくはこれらの積層構造からなる上層ゲート電極10を、溝17を埋め込むように堆積して形成する。ここでは、TaCx層をスパッタ法により形成する。この後、通常の化学機械研磨(CMP)プロセスによって、上層ゲート電極10を平坦化することにより図1に示す構造を得る。前述のように、p型半導体領域5上のゲート絶縁膜7や下層ゲート電極8には、その後のトランジスタ形成プロセス時に経る熱工程により、層9から拡散した金属が含まれる可能性がある。

【0039】

以上、第1の実施形態に依れば、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む金属層を設けることにより、プロセス上の困難性が少ない製造方法にて、低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現することが可能になる。

【0040】

(第1の変形例)

第1の実施形態では、ソース/ドレイン領域として高濃度不純物拡散層を用いる場合について説明したが、無論、ソース/ドレイン領域としてソース/ドレイン電極を用いる所謂ショットキートランジスタでもかまわない。

【0041】

ソース/ドレイン電極の金属材料としては、例えば、Niシリサイド、Ptシリサイド、Coシリサイド、希土類シリサイド等の単体、化合物もしくは積層などが用いられる。

【0042】

形成方法としては、ゲート電極を挟むSi領域上にNi,Pt,Co,希土類等の金属層を堆積させた後に、熱処理(例えば、300℃以上600℃以下程度)を行い、シリサイド化させる方法が一般的である。

【0043】

なお、ソース/ドレイン電極とSi領域との界面に不純物が偏析していてもかまわない。不純物の偏析はシリサイド化の前若しくは後に不純物を導入させることにより行なう。

【0044】

(第2の実施形態)

図15は、本発明の第2の実施形態に係る半導体装置の断面図である。半導体基板としてのSi基板1の表面領域には、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。前記n型、p型半導体領域4,5は、所謂ウエルとして形成される。

【0045】

n型半導体領域4の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜7が、p型半導体領域5の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜を母体とし、アルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドの少なくともいずれか1つの金属元素を含むゲート絶縁膜7´が形成されている。

【0046】

なお、ここでゲート絶縁膜7及び7´と記載したのは、後の工程により結果的にn型半導体領域のゲート絶縁膜とp型半導体領域のゲート絶縁膜に違いが生じるためであり、n型、p型半導体領域にそれぞれ別々にゲート絶縁膜を形成するプロセスを必要とするものではない。

【0047】

n型半導体領域上のゲート絶縁7の上には、例えばTaCxからなる下層ゲート電極8が形成されており、p型領域上のゲート絶縁膜7´の上には、例えばTaCxを母体とするゲート電極8´が形成されている。ここでゲート絶縁膜8及び8´と記載したのは、後の工程により結果的にn型半導体領域の下層ゲート電極とp型半導体領域の下層ゲート電極に違いが生じる可能性があるためであり、n、p型半導体領域にそれぞれ別々に下層ゲート電極を形成するプロセスを必要とするものではない。

【0048】

p型半導体領域領域のゲート電極8´上にはアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドの少なくともいずれが1つの金属元素を含むゲート電極9が形成されている。ゲート電極8及びゲート電極9の上には、さらに、TaCx、Wなどの高融点金属やポリシリコン電極もしくは、これらの積層構造による上層ゲート電極10が形成されている。

【0049】

図16は、TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaCx/Y/TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性とを比較したものである。Yからなる層を2つのTaCx層で挟んでゲート電極を形成した場合には、形成しない場合(TaCx)に比べCVが負方向に250mV程度シフトする。すなわち、フラットバンド電圧Vfbが−250mV程変調される。

【0050】

図17は、ゲート電極中にYを介在させることによって得られるVfbシフト量の、HfSiON膜厚依存性を示したものである。ここで、Vfbシフト量=ΔVfbは、以下の式

ΔVfb=(Vfb(TaCx/Y /TaCx/HfSiON/Si))−(Vfb(TaCx/HfSiON/Si))

で表わされる。

【0051】

前述の450℃のフォーミングガスアニールのみを施したMISキャパシタの結果と異なり、HfSiONが薄い場合に得られるVfbシフトは、HfSiONが厚い場合には得られない。これは、HfSiONが薄い場合に得られるVfbシフトが、φeff変化によるものではなく、HfSiON/界面層との界面近傍若しくはそれよりSi基板側、すなわちゲート絶縁膜構造中の、Si基板とゲート絶縁膜との界面からの距離が、少なくとも1nm以下の領域内にYが存在することによるものであることを示している。これは下層ゲートTaCx層上に形成されたYが高温熱処理により拡散することにより得られる。

【0052】

図18は、TaCx/Er/TaCx/HfSiON/Si構造を形成後に、450〜1000℃のアニールを施した場合のVfbのHfSiON依存性について示したものである。熱処理温度が450〜900℃までは、VfbがHfSiON膜厚によらず上昇しており、これはY積層によるφeff低下効果が低減してしまうことを意味する。これが、前述した、第1の実施形態が高温環境に曝されないリプレースメントゲートプロセスにより形成されねばならない理由である。

【0053】

一方1000℃アニール後には、HfSiONが薄いときのみ再度Vfbが低下しており、これは、前述したように、高温熱処理によるErのHfSiON/界面層の界面近傍若しくはそれよりSi基板側への拡散が、新たなVfb低下をもたらすことを示す結果である。

【0054】

この効果を得る方法としては、本実施形態のように下層TaCx上にYからなる層を形成し、後の熱処理によりYを拡散させる方法のみでなく、ゲート絶縁膜表面上に直接希土類元素からなる層を形成し、そこから希土類元素を拡散させる方法、若しくはゲート絶縁膜中に、もともと希土類元素からなる層を形成する方法があげられるが、nチャネル型MISFETの閾値電圧低減効果を有する希土類層は、pチャネル型MISFETにおいて存在してはならず、そのため、pチャネル型MISFET領域の希土類層剥離工程を要する。HfSiON中やHfSiON表面の剥離工程は、電気特性に多大な影響を及ぼす危険性があり、製造プロセス上困難度が非常に高い。

【0055】

これに比べ、下層メタルゲート上の希土類層を剥離する工程は、電気特性に対する影響が少ないため、プロセス上の困難度が低い。そのため、下層TaCx上に希土類元素からなる層が形成されており、その層から希土類元素が絶縁膜構造中に拡散しているデバイスが最も望ましく、その意味で、本実施形態は、結果的に図15に示す構造となる。また、このプロセスメリットを得るためには、下層ゲート電極はゲート絶縁膜上に連続膜として存在していればよく、1モノレイヤー以上あればよい。

【0056】

また、ここでは下層ゲート電極としてTaCxを用いて説明したが、他のメタルゲート材料でも同様の効果を得ることが出来る。しかしながら、ゲート絶縁膜が剥離工程に曝されないというプロセスメリットを得るためには、下層ゲート電極はウェット剥離工程に耐性があることが求められる。TaCxは金属の中でも最も難溶解性の材料の1つであり、この点で、下層ゲート電極としてTaCxは望ましい。

【0057】

図19は、TaCx/Er/TaCx/HfSiON/Si構造を形成後に、1000℃のアニールと、それに続く450℃のフォーミングガスアニールを施した場合のEr積層によるVfb変調量(Vfb(TaC/Er/TaC)-Vfb(TaC))を、HfSiON直上に下層ゲート電極として形成したTaCの膜厚に対してプロットしたものである。下層TaC層が1.5nm以下の膜厚になると、Vfb変調量が臨界的に増大しており、下層TaC層が1.5nm以下であれば、希土類元素がHfSiON/界面層との界面近傍若しくはそれよりSi基板側まで拡散によって十分な量に到達することを示している。すなわち、希土類元素を含む層が、1.5nm以下のTaCx上に形成されていれば、本実施形態の効果を得ることができる。

【0058】

以上ではTaCx層上に形成される層として、YやErからなる層を用いて説明したが、本実施形態の効果はこれに限られるものではなく、ランタノイド、アクチノイド及びアルカリ土類金属元素のうちいずれか1つを含む層がTaCx層上に形成されていればよい。

【0059】

図20に、TaC/HfSiON/Si、及びTaC/希土類金属若しくはアルカリ土類金属原子を含む層/TaC/HfSiON/Si構造を形成後に、1000℃アニールと、それに続く450℃のフォーミングガスアニールを施して作製されたMISキャパシタで得られたVfbを示す。Efは用いたSi基板のフェルミエネルギーである。YもしくはEr以外の希土類元素を積層した場合でも、φeff低下効果が得られていることが分かる。

【0060】

なお、Yb若しくはMgの場合には、他の元素に比べφeff低下効果が大きい。これは、YbやMgが拡散しやすい元素であり、Vfb低下効果を齎しているHfSiON/界面層との界面近傍若しくはそれよりSi基板側の、希土類元素若しくはアルカリ土類金属元素の量が多くなるためであると思われる。

【0061】

また、本実施形態により−250mV以上のVfb変調効果が得られるため、下層ゲート電極の仕事関数が4.55eV以下であれば、nチャネル型MISFETに適した低いφeffに相当するVfbを実現することが出来る。図6に示したTaCxの組成と仕事関数との関係より、4.55eV以下の仕事関数を有するためには、TaCxのC原子密度は65atomic%以下であることが望ましいといえる。

【0062】

なお、図21は、実際に本実施形態による効果が得られたTaC/Er/TaC/HfSiON構造形成後に、1000℃アニールとそれに続く450℃のフォーミングガスアニールを施したサンプルの断面TEM像である。

【0063】

図21に記載した元素は、図22に示すEELS、EDX及びHAADFの測定データにより、その箇所に存在することが確認されている。また、図23及び図24に、TaC/希土類金属/TaC/HfSiON構造形成後に、1000℃アニールとそれに続く450℃のフォーミングガスアニールを施すことで得た、実際にVfb低下効果が得られたサンプルのバックサイドSIMSにより判明した希土類元素のプロファイルを、希土類元素がEr及びYbの場合について示す。

【0064】

これにより、Er及びYbは、HfSiON/SiO2界面近傍に偏析していることが分かる。また、HfSiON/SiO2界面近傍のErの強度は、TaCx 層上のEr層の強度の4.5%程度であるのに対し、HfSiON/SiO2界面近傍のYbの強度は、TaC層上のYb層の強度の10%程度である。これは、Ybの方が拡散が速いために、より多くの量がHfSiON/SiO2界面近傍に存在することを示しており、これが前述のようにYbで特に大きなVfb低下効果が得られることの一因であると考えられる。このように、ゲートスタック構造中の希土類元素や、アルカリ土類金属元素は、TEM−EELS、EDXやSIMSといった分析により検出可能である。

【0065】

図25は、TaC/Yb/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニール(FGA)を施したMISキャパシタ及び、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS(Back-side XPS)分析により得られたYb4dスペクトルである。バックサイドXPSとは、Si基板を除去後に、HfSiON/Si界面の界面層であるSiO2越しに行うXPS(X-ray Photoemission Spectroscopy)のことである。

【0066】

図25に示したスペクトルは、光電子検出角度(TOA)が15°の場合のものである。TOA=15°という低い検出角度でのXPS測定は、サンプル表面(ここではSi基板側)に非常に敏感であり、ゲート電極側の情報をほとんど含んでおらず、1000℃アニールを施した場合に、Yb2O3のピーク面積が増加していることは、1000℃アニールによりYbがHfSiON側へ、より拡散していることを示している。

【0067】

また、Hf,Si,O,N,Ta及びYbのXPSスペクトルピーク面積を、各元素の感度係数を用いて相対原子数に換算したところ、図26に示す結果を得た。ゲート絶縁膜中の金属原子(Hf,Si,Yb)数に対してYb原子が占める割合は0.4atomic%程度である。前述のように、Yb積層サンプルでは他の希土類金属元素に比べても大きな400mVほどのVfb変調が得られている。すなわち、他の希土類元素で確認されている250mV程度のVfb変調を得るには、ゲートスタック絶縁膜に存在する希土類元素やアルカリ土類金属元素が、ゲート絶縁膜中の金属元素に対して0.25atomic%以上を占めていればよい。

【0068】

次に、本実施形態の半導体装置の製造方法を説明する。本製造方法は、トランジスタ製造に所謂ゲートファーストプロセス(ゲート先作りプロセス)を用いたものであるが、その製造工程を図27〜29に示す。

【0069】

まず、図27に示すように、半導体基板1に、STI構造の素子分離層19によって分離されたn型半導体領域4及びp型半導体領域5にゲート絶縁膜7を形成し、その後ゲート絶縁膜7上に下層ゲート電極8を1モノレイヤー以上1.5nm形成する。ここでは、ゲート絶縁膜7としてHfSiONをMOCVD法により、下層ゲート電極8としてTaCX をスパッタ法により形成する。

【0070】

ここで、下層ゲート電極8の厚さを1.5nm以下と規定したのは、下層ゲート電極8が1.5nm以下でないと、1000℃アニール後に本実施形態の効果が十分に得られないためである。これは、下層ゲート電極8が厚すぎるとランタノイド、アクチノイド及びアルカリ土類金属元素といった元素のゲート絶縁膜への拡散が阻害されてしまうためである。

【0071】

次に、図28に示すように、n型半導体領域4上の下層ゲート電極8上に、酸化シリコンからなるマスク材18を形成する。その後、スパッタ法やCVD法などの成膜方法を用いて、下層ゲート電極8上及びマスク材18上にアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素を含む層9を形成し、リフトオフ法によりマスク材18とともにマスク材18上の層9を剥離する。ここでは、スパッタ法によりYからなる層9を形成する。これにより図29に示す構造を得る。

【0072】

その後は、n型半導体領域上の露出された下層ゲート電極8上及び層9上に、TaCx、TiN,Wなどの高融点金属やポリシリコン電極若しくはこれらの積層構造からなるゲート電極10を形成する。ここでは、ゲート電極10としてTaCxをスパッタ法により堆積する。その後、リソグラフィー及びRIE等のエッチングにより、ゲート電極及びゲート絶縁膜を加工し、通常の半導体プロセスにより拡散層3、3´、エクステンション領域2、2´、サイドウオール層6及び層間絶縁膜11を形成し、最終的に図15に示す構造を得る。なお、図15において、p型半導体領域5上のゲート絶縁膜及び下層ゲート電極をそれぞれ7´及び8´と記載したのは、ゲートスタック形成後の熱工程で、層9から拡散する金属原子が含有されることにより、n型半導体基板5上のゲート絶縁膜及び下層ゲート電極を、それぞれ7及び8と違いが生じる、若しくは違いが生じる可能性があるためである。

【0073】

以上、第2の実施形態によっても、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つをを設けることにより、プロセス上の困難性が少ない製造方法にて、低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現することが可能になる。

【0074】

(第2の変形例)

第2の実施形態では、ソース/ドレイン領域として高濃度不純物拡散層を用いる場合について説明したが、無論、ソース/ドレイン領域としてソース/ドレイン電極を用いる所謂ショットキートランジスタでもかまわない。ソース/ドレイン電極の具体的構成については第1の変形例と同様である。

【0075】

ここで、ソース/ドレイン電極の熱プロセスは通常600℃以下であるため、2通りの実施方法が考えられる。第一は、ゲートファーストプロセスを採るものの、第1の実施形態で説明したゲート電極の仕事関数変調を利用して閾値電圧を低減する方法。第二は、第3の金属層形成後ソース/ドレイン電極前に熱処理を行い、ゲート絶縁膜中に拡散させた金属元素を利用して閾値電圧を低減する方法である。なお、このときの熱処理温度としては、1000℃以上が好ましい。図18に示すように、本効果が発現した温度が1000℃だったためである。なお、上限としては、一般的なゲート絶縁膜/ゲート電極の耐熱性温度である1100℃以下が適当である。

【0076】

(第3の実施形態)

pチャネル型MISFETの閾値低減方法として、high-kゲート絶縁膜中にAlを添加する方法が知られているが(例えば、K.L.Lee et al., VLSI Tech. Symp. P. 202(2006)、H-S. Jung et al., VLSI Tech. Symp. p.196 (2007)、M. Kadoshima et al., VLSI Tech. Symp. p.66 (2007)、P. Sivasubramani et al., VLSI Tech. Symp. p.68 (2007)、K. Iwamoto et al., VLSI Tech. Symp. p.70 (2007))、本発明はこれらの技術と組み合わせた場合にも効果を得ることが可能である。第3の実施形態では、このような実施形態について説明する。

【0077】

図30は、第3の実施形態に係る半導体装置の断面図である。半導体基板としてSi基板1の表面領域は、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。n型、p型半導体領域4,5は、所謂ウエルとして形成される。

【0078】

n型半導体領域4の表面上には、例えば,HfSiONといったhigh-kゲート絶縁膜の一部、若しくは全体にAlを含有する7´´が、p型半導体領域5の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜の一部若しくは全体にAlが添加された膜7´´´が形成されている。

【0079】

なお、ここでゲート絶縁膜7´´及び7´´´と記載したのは、後の工程により結果的にn型半導体領域のゲート絶縁膜とp型半導体領域のゲート絶縁膜に違いが生じるためであり、n型、p型半導体領域にそれぞれ別々にゲート絶縁膜を形成するプロセスを必要とするものではない。

【0080】

n型半導体領域4上のゲート絶縁7´´の上には、例えばTaCxからなる下層ゲート電極8が形成されており、p型半導体領域5上のゲート絶縁膜7´´´の上には、例えばTaCxを母体とするゲート電極8´が形成されている。ここでゲート絶縁膜8及び8´と記載したのは、後の工程により結果的にn型半導体領域4の下層ゲート電極とp型半導体領域5の下層ゲート電極に違いが生じる可能性があるためであり、n型、p型半導体領域にそれぞれ別々に下層ゲート電極を形成するプロセスを必要とするものではない。

【0081】

p型半導体領域5のゲート電極8´上にはアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含むゲート電極9が形成されている。ゲート電極8´及びゲート電極9の上には、さらに、TaCx、TiNもしくはWなどの高融点金属やポリシリコン電極、若しくはこれらの積層構造によるゲート電極10が形成されている。

【0082】

図31及び図32にTaC/HfSiON/Al2O3/SiO2/Si構造及びTaC/Yb/TaC/HfSiON/Al2O3/SiO2/Si構造を形成した後に、1000℃アニールと、それに続く450℃のフォーミングガスアニールを施して得たMISキャパシタのCV特性の比較、及びVfb値の変化の様子を摸式的に示す。Efは用いたSi基板のフェルミエネルギーである。

【0083】

ゲート電極をTaC/Yb/TaCとする場合、ゲート電極がTaC単層である場合に比べ、CV特性は負方向に600mVほどシフトする。HfSiON/SiO2界面近傍にAlを配すことによるVfb変調量は、正方向に200mVである為、pチャネル型MISFET閾値低減技術が施されている場合にも、Ybによる400mVほどの負方向へのVfb変調効果が保たれていることが分かる。

【0084】

HfSiON/SiO2界面近傍にAlを配する方法としては、high-kゲート絶縁膜/SiO2界面にAl2O3を挿入する方法や、high-kゲート絶縁膜上にAl2O3を形成し、その後の熱工程によってAlを拡散させる方法があるが、通常は、nチャネル型MISFETの閾値を増加させない為に、nチャネル型MISFETの領域に形成されたAL2O3を剥離する必要がある。しかしながら、本発明をnチャネル型MISFET閾値低減方法として用いれば、このAl2O3剥離工程を経ずとも、nチャネル型MISFETの閾値を十分低くすることが出来る。

【0085】

上記のように、第3の実施形態に依れば、pチャネル型MISFETの閾値低減方法として、high-kゲート絶縁膜中にAlを添加する方法を用いた場合でも、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つをを含む金属層を設けることにより、低い閾値電圧のCMOS半導体装置を実現することが可能になる。

【0086】

以上、本発明を実施形態を通じて説明したが、本発明は上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々な発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態に亘る構成要素を適宜組み合わせても良い。

【図面の簡単な説明】

【0087】

【図1】第1の実施例に関わるCMOS半導体装置の断面図。

【図2】TaC/HfSiON/Si構造を形成後に450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaC/Y,Er若しくはTb/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施したMISキャパシタのCV特性を比較した図。

【図3】450℃、30分のフォーミングガスアニールを施した場合に、希土類金属層を形成することによって得られるVbシフト量のHfSiON膜厚依存性を示す図。

【図4】450℃、30分のフォーミングガスアニールを施した場合のEr積層によるΔVfbの下層TaC膜厚依存性を示す図。

【図5】TaC/HfSiON/Si構造を形成後に450℃のフォーミングガスアニールを施したMISキャパシタのVfbと、TaC/希土類金属含有層/TaC/HfSiON/Si構造を形成後に450℃、30分のフォーミングガスアニールを施したMISキャパシタのVfbとに、用いたSi基板のフェルミエネルギーEfを加えて比較した図。

【図6】TaCxの仕事関数と組成との関係を示す図。

【図7】TaC/Er/TaC/HfSiON/Si構造を形成後に450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEM像。

【図8】TaC/Er/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEMに、EELS,EDXから判明した各元素の深さ方向分布及びHAADF強度分布を示す図。

【図9】TaC/Er/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタのBack-side SIMS分析により判明したEr,Ta及びSiのプロファイル。

【図10】第1の実施形態に係るCMOS半導体装置製造工程を説明する為の断面図。

【図11】図10に続く工程における断面図。

【図12】図11に続く工程における断面図。

【図13】図12に続く工程における断面図。

【図14】図13に続く工程における断面図。

【図15】第2の実施形態に係るCMOS半導体装置の断面図。

【図16】TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaCx/Y/TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性とを比較した図。

【図17】1000℃アニールと、それに続く450℃のフォーミングガスアニールを施した場合に、Er層を形成することによって得られるVfbシフト量の、HfSiON膜厚依存性を示す図。

【図18】TaCx/Er/TaCx/HfSiON/Si構造を形成後に、450〜1000℃のアニールを施した場合の、Er積層によるΔVfbのHfSiON依存性を示す図。

【図19】1000℃アニールと、それに続く450℃のフォーミングガスアニールを施した場合の、Er積層によるΔVfbの下層TaC膜厚依存性を示す図。

【図20】TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのVfbと、TaC/希土類金属、若しくはアルカリ土類金属含有層/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの(Vfb+Ef)値を比較する図。

【図21】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEM像。

【図22】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEMに、EELS,EDXから判明した各元素の深さ方向分布及びHAADF強度分布を示す図。

【図23】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドSIMS分析により判明したEr、Ta及びSiプロファイル。

【図24】図23と同様な、Yb、Ta及びSiのプロファイル。

【図25】TaC/Yb/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタ及び、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS分析により得られたYb4dスペクトル。

【図26】TaC/Yb/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS分析により得られた、各元素のスペクトルのピーク面積を、各元素の感度係数を用いて相対原子数に換算した値。

【図27】第2の実施形態に係るCMOS半導体装置製造工程を説明するための断面図。

【図28】図27に続く工程における断面図。

【図29】図28に続く工程における断面図。

【図30】第3の実施形態に係るCMOS半導体装置の断面図。

【図31】TaC/HfSiON/Al2O3/SiO2/Si構造及びTaC/Yb/TaC/HfSiON/Al2O3/SiO2/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのCV特性。

【図32】図31のMISキャパシタの(Vfb+Ef)に対する、Al,Ybの効果を説明する為の図。

【符号の説明】

【0088】

1…Si半導体基板

2、2´…拡散層

3、3´…エクステンション領域

4…n型半導体領域

5…p型半導体領域

6…サイドウオール層

7、7´…ゲート絶縁膜

8、8´…下層ゲート電極

9…アルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素を含む層

10…上層ゲート電極

11…層間絶縁膜

12…pチャネルMISトランジスタ

13…nチャネルMISトランジスタ

18…マスク材

19…STI(素子分離領域)

【技術分野】

【0001】

本発明は、金属ゲート電極を用いた半導体装置、及びその製造方法に関する。

【背景技術】

【0002】

半導体デバイスの高性能化、高集積化に伴う実効的なゲート絶縁膜薄膜化の要求を満たすためには、今後メタルゲート電極と高誘電率(high-k)ゲート絶縁膜の技術導入が必須である。メタルゲート/high-kゲート絶縁膜を用いたMISトランジスタにおいて適正な性能を得るためには、メタルゲート材料の実効仕事関数φeffがnチャネル型MISトランジスタにおいては3.9〜4.3eV程度、pチャネル型MISトランジスタにおいては4.8〜5.2eV程度であることが必要である(例えば、特許文献1参照)。

【0003】

しかしながら、nチャネル型MISトランジスタに適した低い仕事関数を有する金属は、一般にトランジスタ形成工程に必須な熱工程に対して安定でなく、特にhigh-kゲート絶縁膜上で、トランジスタ形成後にミッドギャップ(mid-gap)付近(4.6eV近傍)のφeffとなり、nチャネル型MISトランジスタに適した3.9〜4.3eV程度のφeffを実現することが困難である。そのため、nチャネル型MISトランジスタの閾値電圧を十分低くすることが出来ず、このことはメタルゲート電極/high-kゲート絶縁膜の技術導入に当たって大きな問題となっている。

【特許文献1】特開2007−173412号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

前述のように、high-kゲート絶縁膜/メタルゲート電極を用いた場合に、nチャネル型MISトランジスタにおいて低い閾値電圧を実現できないという問題が生じていた。本発明は、これを解決すべくなされたもので、nチャネル型MISトランジスタの閾値電圧が低減された半導体装置と、容易なプロセスを用いてこれを形成できる製造方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

上記課題を解決するために、本発明の半導体装置の第1は、半導体基板と、前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、前記半導体基板上に形成され、前記n型半導体領域とp型半導体領域とを露出するように夫々形成された第1と第2のトレンチを有する第1の絶縁層と、前記第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、前記第1のトレンチの側壁と底部に沿って形成され、前記ゲート絶縁膜を介して形成された第1の金属層と、前記第2のトレンチの側壁と底部に沿って形成され、前記ゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、前記第2の金属層上に内張りされたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層とを具備することを特徴とする。

【0006】

本発明の半導体装置の第2は、半導体基板と、前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、前記n型半導体層領域に形成された第1のゲート絶縁膜と、前記p型半導体層領域上に形成された第2のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の金属層と、前記第2のゲート絶縁膜上に、1モノレイヤー以上で1.5nm以下の厚さに形成された第2の金属層と、前記第2の金属層上に形成されたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層とを具備し、前記金属元素が前記p型半導体領域の前記ゲート絶縁膜中に存在することを特徴とする。

【0007】

本発明の半導体製造方法の第1は、素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の、前記n型半導体層領域に第1ダミーゲートを形成するとともに、前記p型半導体領域に第2ダミーゲートを形成する工程と、前記第1ダミーゲートの両側の前記n型半導体領域に、p型拡散層を形成する工程と、前記第2ダミーゲートの両側の前記p型半導体領域に、n型拡散層を形成する工程と、前記n型拡散層及び前記p型拡散層を覆うように、前記第1及び第2ダミーゲートの側部に絶縁膜を形成する工程と、前記第1及び第2ダミーゲートを除去することにより、前記絶縁層に第1及び第2のトレンチを形成する工程と、前記第1及び第2のトレンチの少なくとも底部に、第1と第2のゲート絶縁膜を夫々形成する工程と、前記第1のゲート絶縁膜上に第1の金属層を、前記第2のゲート絶縁膜上に第2の金属層を、1モノレイヤー以上1.5nm以下の厚さで夫々形成する工程と、前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程とを有することを特徴とする。

【0008】

本発明の半導体装置の製造方法の第2は、素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の前記n型半導体層領域及び前記p型半導体領域上に、第1と第2のゲート絶縁膜を夫々形成する工程と、前記第1と第2のゲート絶縁膜上に、第1の金属層と第2の金属層を1モノレイヤー以上で1.5nm以下に夫々形成する工程と、前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程と、前記第1のゲート絶縁膜、第1のl金属層と、第2のゲート絶縁膜、第2、第3の金属層とを加工し、第1と第2のゲート電極を夫々加工する工程と、前記第1と第2のゲート電極を夫々挟む前記n型半導体領域とp型半導体領域に、第1と第2のソース/ドレイン領域を形成する工程とを有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、メタルゲート電極を用いたnチャネル型MISトランジスタを含む半導体装置において、低い閾値電圧のnチャネル型MISトランジスタが実現され、容易なプロセスでこれを製造できる製造方法が提供される。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して本発明の実施形態について説明する。

【0011】

(第1の実施形態)

図1は、本発明の第1の実施形態に係るCMOS半導体装置の断面図である。Si基板1の表面領域には、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。前記n型及びp型半導体領域4,5は、所謂ウエルとして形成される。

【0012】

n型及びp型半導体領域4,5の表面上には、例えばHfSiONといった高誘電率(high-k)ゲート絶縁膜7及び7´が形成されている。n型半導体領域のゲート絶縁膜7上及びp型半導体領域上のゲート絶縁膜7´の上には、TaCxからなるゲート電極8及びTaCxを母体とするゲート電極8´が1モノレイヤー以上1.5nm以下に、夫々形成されている。ゲート電極8´やゲート絶縁膜7´はアルカリ土類金属元素、III族元素(例えば、Sc、Y、ランタノイド、アクチノイド)に属する元素を含有していてもよい。

【0013】

また、本実施形態においてゲート絶縁膜に接する形で形成されるゲート電極層を「下層ゲート電極」と記載することとする。なお、ここでゲート絶縁膜7及び7´、ゲート電極8及び8´と記載したのは、後の工程により結果的にn型半導体領域上の下層ゲート電極とp型半導体領域上の下層ゲート電極及びゲート絶縁膜に違いが生じる可能性があるためであり、n型、p型半導体領域上に夫々別々にゲート絶縁膜や下層ゲート電極を形成するプロセスを必要とするものではない。

【0014】

ゲート電極8´の上には、アルカリ土類金属元素、III族元素(例えば、Sc、Y、ランタノイド、アクチノイド)の少なくともいずれが1つの金属元素の単体、窒化物、炭化物、あるいは酸化物を含む層9が形成されている。トランジスタ形成工程を経ることでこの金属元素を含む層9から、p型半導体領域5の下層ゲート電極8´中やゲート絶縁膜7´中にアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素が拡散する可能性があるが、本実施形態の効果を得るために、p型半導体領域5の下層ゲート電極8´中やゲート絶縁膜7´中へのアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素の拡散が、必ずしも必要なわけではない。

【0015】

n型半導体領域4上のゲート電極8及びp型半導体領域上の層9の上には、さらにTiNx 、TaCx 、Wなどの高融点金属やポリシリコン、若しくはこれらの積層構造からなる層10が形成されている。なお、参照番号6は側壁絶縁膜、11は層間絶縁膜、19はSTI(shallow trench isolation)による素子分離領域である。以上のように、第1の実施形態の半導体装置は、所謂ゲートリプレースメントプロセス(ゲート作り替えプロセス)にて形成したデバイス特有の構造を持つ。

【0016】

図2は、TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施して作製されたMISキャパシタのCV特性と、TaC/Y,ErまたはTb/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施して作製されたMISキャパシタのCV特性とを比較したものである。ゲート電極中にY,Er若しくはTbからなる層を形成した場合には、ゲート電極がTaC単層からなる場合に比べCVが負方向に400mV程度シフトする。すなわち、フラットバンド電圧Vfbが−400mV程変調される。

【0017】

図3は、Er、YまたはYbを積層することによって得られる、Vfbシフト量のHfSiON膜厚依存性を示したものである。Vfbシフト量は以下の式

ΔVfb=(Vfb(TaC/Y, Er or Tb/TaC/HfSiON/Si))−(Vfb(TaC/HfSiON/Si))

で表わされる。

【0018】

図3に依れば、HfSiON膜厚にかかわらず、−400mV程度のVfb変調が、Y、ErもしくはTb積層により得られており、ゲート電極の仕事関数φeffが、3〜3.5eVほどの低い仕事関数を有する希土類元素Y、Er若しくはTbによって400mV程度低い方向に変調されたことを示している。このようにφeff変調を得るには、希土類元素はゲート絶縁膜/ゲート電極界面から、ある程度近い距離にあるゲート電極中に存在することが必要である。

【0019】

図4は、Er積層によるVfb変調量を、下層ゲート電極として形成したTaCx層の膜厚に対してプロットしたものである。下層ゲートTaCx層が1.5nm以下の領域でφeff変調量が急激に増加しており、希土類元素がゲート絶縁膜/ゲート電極界面から1.5nm以内の距離にあるゲート電極中に存在することにより、十分なφeff低下効果が得られることが分かる。すなわち、希土類元素を含む層が、1.5nm以下のTaCx上に形成されていれば、本実施形態の効果を得ることができる。

【0020】

上記の効果を得る手段としては、本実施形態のように薄い下層TaCx上に希土類元素からなる層を形成する方法のみでなく、ゲート絶縁膜表面上に直接希土類元素を含む金属層を形成する方法も挙げられるが、nチャネル型MISFETの閾値電圧低減効果を有する希土類含有層は、pチャネル型MISFETにおいて存在してはならず、そのため、pチャネル型MISFET領域の希土類含有層剥離工程を要する。ゲート絶縁膜表面の剥離工程は、ゲート絶縁膜の変質を引き起こし、電気特性に多大な影響を及ぼす危険性がある。

【0021】

これに比べ、下層メタルゲート上の希土類含有層剥離は、ゲート絶縁膜に接することの無い工程であるため、電気特性に対する影響が少なく、プロセス上の困難度が低い。その意味で、本実施形態の半導体装置は望ましい構造を有する。

【0022】

また、このプロセスメリットを得るためには、下層ゲート電極はゲート絶縁膜上に連続膜として存在していればよく、その意味で1モノレイヤー以上あればよい。また、ここでは下層ゲート電極8、8´としてTaCxを用いて説明したが、他のメタルゲート材料でも同様の効果を得ることが出来る。しかしながら、ゲート絶縁膜7、7´が剥離工程に曝されないというプロセスメリットを得るためには、下層ゲート電極8,8´はウェット剥離工程に耐性があることが求められる。TaCxは金属の中でも最も難溶解性の材料の1つである。この点で、下層ゲート電極としてTaCxは望ましい。

【0023】

ところで、前述のように、アルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む層9は、これら金属元素以外に、例えばSi,C,N,Oといった非金属元素を含んでいてもよい。然しながら、層9として金属元素とSiを含む層を、下層ゲート電極としてTaCx を用いる場合、金属元素とSiとの結合エネルギーよりも、金属元素とCとの結合エネルギーが大きいために、層9中においてSiと結合していた金属元素が、下層ゲート電極であるTaCx 中の余剰なCと結合し直すことによって、Si層が析出する虞がある。Si層は半導体であり、ゲート電極の抵抗増大を招く。そのため、下層ゲート電極がTaCx からなる場合、層9はSiを含まないものが望ましい。

【0024】

なお、金属元素とNの結合エネルギーや、金属元素とOの結合エネルギーは、金属元素とCの結合エネルギーよりも大きいため、層9がNとOを含んでいても層9の金属元素とN若しくはOとの結合が、下層TaCx 中の余剰Cとの結合にとって代わられることはない。また、Cは希土類金属との結合エネルギーがSiのそれより大きく、安定な金属化合物を形成する。

【0025】

また、この効果はY、ErもしくはTbといった元素に限り得られるものではなく、ランタノイド、アクチノイド及びアルカリ土類金属元素を含む層が、下層ゲートTaCx層上に形成されていればよい。図5に、TaC/HfSiON/Si及びTaC/希土類金属/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施した場合の、ゲート電極のVfbを示す。Efは用いたSi基板のフェルミエネルギーである。Y,Er若しくはTb以外の希土類元素でも、Vfb低下効果が得られることがわかる。

【0026】

なお、理由は後述するが、本実施形態に示す構造による限り、すなわち、ゲート電極の仕事関数φeff低下に伴うVfb低下効果によりnチャネル型MISトランジスタの閾値低減を得る場合、ゲートファーストプロセス(ゲート先作りプロセス)のように、ゲートスタック構造を1000℃程度の高温環境に曝してはならない。そのため、本実施形態はリプレースメントゲートプロセスによって形成されていなければならず、その結果、図1に示すようにリプレースメントゲートプロセスに特有の構造を持つ。

【0027】

また、本発明により−400mV程度のVfb変調効果が得られるため、下層ゲートのTaCxの仕事関数が4.7eV以下であれば、nチャネル型MISトランジスタに適した低いφeffを実現することが出来る。

【0028】

図6は、TaCxの組成と仕事関数との関係を示す図であるが、4.7eV以下の仕事関数を有するためには、TaCxのC原子密度は85atomic%以下であることが望ましい。

【0029】

図7に、実際に本発明による効果が得られた、TaC/Er/TaC/HfSiON構造形成後に450℃のフォーミングガスアニールを施したサンプルの、断面TEM像に示す。図7に記載した元素は、EELS(Electron Energy Loss Spectroscopy)スペクトルやEDX(Energy Dispersive X-ray Analysis)によりその箇所に存在することが確認されている。

【0030】

図8は、EELS,EDXで確認されたHf,Ta,O,Erの深さ方向のプロファイルを示す。図8にあわせて示すHAADF(high-angle annular dark field)の強度は、原子番号の二乗に比例するものであり、図7に示したTEM像におけるコントラストと対応している。HAADF強度と各元素のプロファイルの比較により、図7のTEM像に記載した元素とその箇所との対応が確認される。

【0031】

また、EELS測定では検出できない微量の元素は、SIMS分析による検出することが可能である。図9に、実際に本発明による効果が得られた、TaC/Er/TaC/HfSiON構造形成後に、450℃のフォーミングガスアニールを施したサンプルにおけるErプロファイルを、SIMS分析によって調べた結果を示す。

【0032】

ここでは、Si基板を剥離し、HfSiON/Si界面SiO2層側から分析する所謂バックサイドSIMS(Back-side-SIMS)を用いた。下層TaC電極上に形成されたEr層からErが拡散し、下層TaC中やHfSiON中にもErが存在する。このように、ゲートスタック構造中の希土類元素や、アルカリ土類元素は、TEM−EELSや裏面SIMSといった方法により検出可能である。

【0033】

本実施形態の半導体装置の製造方法は、トランジスタ製造に所謂リプレースメントゲートプロセスを用い、その製造工程を図10乃至図14に示す。まず、図10に示すように、半導体基板1に、STI構造の素子分離層19によって分離されたn型ウエル領域4及びp型ウエル領域5を形成する。続いて、n型ウエル領域4及びp型ウエル領域5にそれぞれダミーゲート(図示せず)を形成し、上記ダミーゲートをマスクとして、n型ウエル領域4にp型不純物を注入してp型エクステンション層3を形成するとともに、p型ウエル領域5にn型不純物を注入してn型エクステンション層3´を形成する。

【0034】

その後、上記ダミーゲートの側部にサイドウオール層6を形成する。そしてダミーゲート及びサイドウオール層13をマスクとしてn型ウエル領域4にp型不純物を注入してp型拡散層2を形成するとともに、p型ウエル領域5にn型不純物を注入してn型拡散層2´を形成する。

【0035】

続いて、層間絶縁膜11を堆積し、この層間絶縁膜11を平坦化する。その後、上記ダミーゲートを除去することにより図10に示す構造を得る。図10から分かるように、ダミーゲートが除去された後に、溝17が形成される。なお、拡散層2,2´上にサリサイド層が形成されていてもよい。

【0036】

次に、図11に示すように、例えばMOCVD(metal organic chemical vapor deposition)法により、ゲート絶縁層7を形成する。ここでは、ゲート絶縁層7としてHfSiONを用いる。次に、図12に示すように、例えば、スパッタ法やCVD法などの成膜方法を用いて、ゲート絶縁層7上に下層ゲート電極8を1モノレイヤー以上1.5nm以下に形成する。ここではスパッタ法によりTaCx 層を1.5nm形成する。

【0037】

次に、図13に示すように、n型半導体領域4上に酸化シリコンからなるマスク材18を形成する。その後、スパッタ法やCVD法などの成膜方法を用いて、下層ゲート電極8上及びマスク18上にアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む層9を形成し、リフトオフ法によりマスク材18とともにマスク材18上の層9を剥離する。これにより図14に示す構造を得る。

【0038】

その後は、n型半導体領域上の露出された下層ゲート電極8上及び層9上に、TaCx、W、TiNxなどの高融点金属やポリシリコン電極、若しくはこれらの積層構造からなる上層ゲート電極10を、溝17を埋め込むように堆積して形成する。ここでは、TaCx層をスパッタ法により形成する。この後、通常の化学機械研磨(CMP)プロセスによって、上層ゲート電極10を平坦化することにより図1に示す構造を得る。前述のように、p型半導体領域5上のゲート絶縁膜7や下層ゲート電極8には、その後のトランジスタ形成プロセス時に経る熱工程により、層9から拡散した金属が含まれる可能性がある。

【0039】

以上、第1の実施形態に依れば、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む金属層を設けることにより、プロセス上の困難性が少ない製造方法にて、低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現することが可能になる。

【0040】

(第1の変形例)

第1の実施形態では、ソース/ドレイン領域として高濃度不純物拡散層を用いる場合について説明したが、無論、ソース/ドレイン領域としてソース/ドレイン電極を用いる所謂ショットキートランジスタでもかまわない。

【0041】

ソース/ドレイン電極の金属材料としては、例えば、Niシリサイド、Ptシリサイド、Coシリサイド、希土類シリサイド等の単体、化合物もしくは積層などが用いられる。

【0042】

形成方法としては、ゲート電極を挟むSi領域上にNi,Pt,Co,希土類等の金属層を堆積させた後に、熱処理(例えば、300℃以上600℃以下程度)を行い、シリサイド化させる方法が一般的である。

【0043】

なお、ソース/ドレイン電極とSi領域との界面に不純物が偏析していてもかまわない。不純物の偏析はシリサイド化の前若しくは後に不純物を導入させることにより行なう。

【0044】

(第2の実施形態)

図15は、本発明の第2の実施形態に係る半導体装置の断面図である。半導体基板としてのSi基板1の表面領域には、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。前記n型、p型半導体領域4,5は、所謂ウエルとして形成される。

【0045】

n型半導体領域4の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜7が、p型半導体領域5の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜を母体とし、アルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドの少なくともいずれか1つの金属元素を含むゲート絶縁膜7´が形成されている。

【0046】

なお、ここでゲート絶縁膜7及び7´と記載したのは、後の工程により結果的にn型半導体領域のゲート絶縁膜とp型半導体領域のゲート絶縁膜に違いが生じるためであり、n型、p型半導体領域にそれぞれ別々にゲート絶縁膜を形成するプロセスを必要とするものではない。

【0047】

n型半導体領域上のゲート絶縁7の上には、例えばTaCxからなる下層ゲート電極8が形成されており、p型領域上のゲート絶縁膜7´の上には、例えばTaCxを母体とするゲート電極8´が形成されている。ここでゲート絶縁膜8及び8´と記載したのは、後の工程により結果的にn型半導体領域の下層ゲート電極とp型半導体領域の下層ゲート電極に違いが生じる可能性があるためであり、n、p型半導体領域にそれぞれ別々に下層ゲート電極を形成するプロセスを必要とするものではない。

【0048】

p型半導体領域領域のゲート電極8´上にはアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドの少なくともいずれが1つの金属元素を含むゲート電極9が形成されている。ゲート電極8及びゲート電極9の上には、さらに、TaCx、Wなどの高融点金属やポリシリコン電極もしくは、これらの積層構造による上層ゲート電極10が形成されている。

【0049】

図16は、TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaCx/Y/TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性とを比較したものである。Yからなる層を2つのTaCx層で挟んでゲート電極を形成した場合には、形成しない場合(TaCx)に比べCVが負方向に250mV程度シフトする。すなわち、フラットバンド電圧Vfbが−250mV程変調される。

【0050】

図17は、ゲート電極中にYを介在させることによって得られるVfbシフト量の、HfSiON膜厚依存性を示したものである。ここで、Vfbシフト量=ΔVfbは、以下の式

ΔVfb=(Vfb(TaCx/Y /TaCx/HfSiON/Si))−(Vfb(TaCx/HfSiON/Si))

で表わされる。

【0051】

前述の450℃のフォーミングガスアニールのみを施したMISキャパシタの結果と異なり、HfSiONが薄い場合に得られるVfbシフトは、HfSiONが厚い場合には得られない。これは、HfSiONが薄い場合に得られるVfbシフトが、φeff変化によるものではなく、HfSiON/界面層との界面近傍若しくはそれよりSi基板側、すなわちゲート絶縁膜構造中の、Si基板とゲート絶縁膜との界面からの距離が、少なくとも1nm以下の領域内にYが存在することによるものであることを示している。これは下層ゲートTaCx層上に形成されたYが高温熱処理により拡散することにより得られる。

【0052】

図18は、TaCx/Er/TaCx/HfSiON/Si構造を形成後に、450〜1000℃のアニールを施した場合のVfbのHfSiON依存性について示したものである。熱処理温度が450〜900℃までは、VfbがHfSiON膜厚によらず上昇しており、これはY積層によるφeff低下効果が低減してしまうことを意味する。これが、前述した、第1の実施形態が高温環境に曝されないリプレースメントゲートプロセスにより形成されねばならない理由である。

【0053】

一方1000℃アニール後には、HfSiONが薄いときのみ再度Vfbが低下しており、これは、前述したように、高温熱処理によるErのHfSiON/界面層の界面近傍若しくはそれよりSi基板側への拡散が、新たなVfb低下をもたらすことを示す結果である。

【0054】

この効果を得る方法としては、本実施形態のように下層TaCx上にYからなる層を形成し、後の熱処理によりYを拡散させる方法のみでなく、ゲート絶縁膜表面上に直接希土類元素からなる層を形成し、そこから希土類元素を拡散させる方法、若しくはゲート絶縁膜中に、もともと希土類元素からなる層を形成する方法があげられるが、nチャネル型MISFETの閾値電圧低減効果を有する希土類層は、pチャネル型MISFETにおいて存在してはならず、そのため、pチャネル型MISFET領域の希土類層剥離工程を要する。HfSiON中やHfSiON表面の剥離工程は、電気特性に多大な影響を及ぼす危険性があり、製造プロセス上困難度が非常に高い。

【0055】

これに比べ、下層メタルゲート上の希土類層を剥離する工程は、電気特性に対する影響が少ないため、プロセス上の困難度が低い。そのため、下層TaCx上に希土類元素からなる層が形成されており、その層から希土類元素が絶縁膜構造中に拡散しているデバイスが最も望ましく、その意味で、本実施形態は、結果的に図15に示す構造となる。また、このプロセスメリットを得るためには、下層ゲート電極はゲート絶縁膜上に連続膜として存在していればよく、1モノレイヤー以上あればよい。

【0056】

また、ここでは下層ゲート電極としてTaCxを用いて説明したが、他のメタルゲート材料でも同様の効果を得ることが出来る。しかしながら、ゲート絶縁膜が剥離工程に曝されないというプロセスメリットを得るためには、下層ゲート電極はウェット剥離工程に耐性があることが求められる。TaCxは金属の中でも最も難溶解性の材料の1つであり、この点で、下層ゲート電極としてTaCxは望ましい。

【0057】

図19は、TaCx/Er/TaCx/HfSiON/Si構造を形成後に、1000℃のアニールと、それに続く450℃のフォーミングガスアニールを施した場合のEr積層によるVfb変調量(Vfb(TaC/Er/TaC)-Vfb(TaC))を、HfSiON直上に下層ゲート電極として形成したTaCの膜厚に対してプロットしたものである。下層TaC層が1.5nm以下の膜厚になると、Vfb変調量が臨界的に増大しており、下層TaC層が1.5nm以下であれば、希土類元素がHfSiON/界面層との界面近傍若しくはそれよりSi基板側まで拡散によって十分な量に到達することを示している。すなわち、希土類元素を含む層が、1.5nm以下のTaCx上に形成されていれば、本実施形態の効果を得ることができる。

【0058】

以上ではTaCx層上に形成される層として、YやErからなる層を用いて説明したが、本実施形態の効果はこれに限られるものではなく、ランタノイド、アクチノイド及びアルカリ土類金属元素のうちいずれか1つを含む層がTaCx層上に形成されていればよい。

【0059】

図20に、TaC/HfSiON/Si、及びTaC/希土類金属若しくはアルカリ土類金属原子を含む層/TaC/HfSiON/Si構造を形成後に、1000℃アニールと、それに続く450℃のフォーミングガスアニールを施して作製されたMISキャパシタで得られたVfbを示す。Efは用いたSi基板のフェルミエネルギーである。YもしくはEr以外の希土類元素を積層した場合でも、φeff低下効果が得られていることが分かる。

【0060】

なお、Yb若しくはMgの場合には、他の元素に比べφeff低下効果が大きい。これは、YbやMgが拡散しやすい元素であり、Vfb低下効果を齎しているHfSiON/界面層との界面近傍若しくはそれよりSi基板側の、希土類元素若しくはアルカリ土類金属元素の量が多くなるためであると思われる。

【0061】

また、本実施形態により−250mV以上のVfb変調効果が得られるため、下層ゲート電極の仕事関数が4.55eV以下であれば、nチャネル型MISFETに適した低いφeffに相当するVfbを実現することが出来る。図6に示したTaCxの組成と仕事関数との関係より、4.55eV以下の仕事関数を有するためには、TaCxのC原子密度は65atomic%以下であることが望ましいといえる。

【0062】

なお、図21は、実際に本実施形態による効果が得られたTaC/Er/TaC/HfSiON構造形成後に、1000℃アニールとそれに続く450℃のフォーミングガスアニールを施したサンプルの断面TEM像である。

【0063】

図21に記載した元素は、図22に示すEELS、EDX及びHAADFの測定データにより、その箇所に存在することが確認されている。また、図23及び図24に、TaC/希土類金属/TaC/HfSiON構造形成後に、1000℃アニールとそれに続く450℃のフォーミングガスアニールを施すことで得た、実際にVfb低下効果が得られたサンプルのバックサイドSIMSにより判明した希土類元素のプロファイルを、希土類元素がEr及びYbの場合について示す。

【0064】

これにより、Er及びYbは、HfSiON/SiO2界面近傍に偏析していることが分かる。また、HfSiON/SiO2界面近傍のErの強度は、TaCx 層上のEr層の強度の4.5%程度であるのに対し、HfSiON/SiO2界面近傍のYbの強度は、TaC層上のYb層の強度の10%程度である。これは、Ybの方が拡散が速いために、より多くの量がHfSiON/SiO2界面近傍に存在することを示しており、これが前述のようにYbで特に大きなVfb低下効果が得られることの一因であると考えられる。このように、ゲートスタック構造中の希土類元素や、アルカリ土類金属元素は、TEM−EELS、EDXやSIMSといった分析により検出可能である。

【0065】

図25は、TaC/Yb/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニール(FGA)を施したMISキャパシタ及び、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS(Back-side XPS)分析により得られたYb4dスペクトルである。バックサイドXPSとは、Si基板を除去後に、HfSiON/Si界面の界面層であるSiO2越しに行うXPS(X-ray Photoemission Spectroscopy)のことである。

【0066】

図25に示したスペクトルは、光電子検出角度(TOA)が15°の場合のものである。TOA=15°という低い検出角度でのXPS測定は、サンプル表面(ここではSi基板側)に非常に敏感であり、ゲート電極側の情報をほとんど含んでおらず、1000℃アニールを施した場合に、Yb2O3のピーク面積が増加していることは、1000℃アニールによりYbがHfSiON側へ、より拡散していることを示している。

【0067】

また、Hf,Si,O,N,Ta及びYbのXPSスペクトルピーク面積を、各元素の感度係数を用いて相対原子数に換算したところ、図26に示す結果を得た。ゲート絶縁膜中の金属原子(Hf,Si,Yb)数に対してYb原子が占める割合は0.4atomic%程度である。前述のように、Yb積層サンプルでは他の希土類金属元素に比べても大きな400mVほどのVfb変調が得られている。すなわち、他の希土類元素で確認されている250mV程度のVfb変調を得るには、ゲートスタック絶縁膜に存在する希土類元素やアルカリ土類金属元素が、ゲート絶縁膜中の金属元素に対して0.25atomic%以上を占めていればよい。

【0068】

次に、本実施形態の半導体装置の製造方法を説明する。本製造方法は、トランジスタ製造に所謂ゲートファーストプロセス(ゲート先作りプロセス)を用いたものであるが、その製造工程を図27〜29に示す。

【0069】

まず、図27に示すように、半導体基板1に、STI構造の素子分離層19によって分離されたn型半導体領域4及びp型半導体領域5にゲート絶縁膜7を形成し、その後ゲート絶縁膜7上に下層ゲート電極8を1モノレイヤー以上1.5nm形成する。ここでは、ゲート絶縁膜7としてHfSiONをMOCVD法により、下層ゲート電極8としてTaCX をスパッタ法により形成する。

【0070】

ここで、下層ゲート電極8の厚さを1.5nm以下と規定したのは、下層ゲート電極8が1.5nm以下でないと、1000℃アニール後に本実施形態の効果が十分に得られないためである。これは、下層ゲート電極8が厚すぎるとランタノイド、アクチノイド及びアルカリ土類金属元素といった元素のゲート絶縁膜への拡散が阻害されてしまうためである。

【0071】

次に、図28に示すように、n型半導体領域4上の下層ゲート電極8上に、酸化シリコンからなるマスク材18を形成する。その後、スパッタ法やCVD法などの成膜方法を用いて、下層ゲート電極8上及びマスク材18上にアルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素を含む層9を形成し、リフトオフ法によりマスク材18とともにマスク材18上の層9を剥離する。ここでは、スパッタ法によりYからなる層9を形成する。これにより図29に示す構造を得る。

【0072】

その後は、n型半導体領域上の露出された下層ゲート電極8上及び層9上に、TaCx、TiN,Wなどの高融点金属やポリシリコン電極若しくはこれらの積層構造からなるゲート電極10を形成する。ここでは、ゲート電極10としてTaCxをスパッタ法により堆積する。その後、リソグラフィー及びRIE等のエッチングにより、ゲート電極及びゲート絶縁膜を加工し、通常の半導体プロセスにより拡散層3、3´、エクステンション領域2、2´、サイドウオール層6及び層間絶縁膜11を形成し、最終的に図15に示す構造を得る。なお、図15において、p型半導体領域5上のゲート絶縁膜及び下層ゲート電極をそれぞれ7´及び8´と記載したのは、ゲートスタック形成後の熱工程で、層9から拡散する金属原子が含有されることにより、n型半導体基板5上のゲート絶縁膜及び下層ゲート電極を、それぞれ7及び8と違いが生じる、若しくは違いが生じる可能性があるためである。

【0073】

以上、第2の実施形態によっても、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つをを設けることにより、プロセス上の困難性が少ない製造方法にて、低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現することが可能になる。

【0074】

(第2の変形例)

第2の実施形態では、ソース/ドレイン領域として高濃度不純物拡散層を用いる場合について説明したが、無論、ソース/ドレイン領域としてソース/ドレイン電極を用いる所謂ショットキートランジスタでもかまわない。ソース/ドレイン電極の具体的構成については第1の変形例と同様である。

【0075】

ここで、ソース/ドレイン電極の熱プロセスは通常600℃以下であるため、2通りの実施方法が考えられる。第一は、ゲートファーストプロセスを採るものの、第1の実施形態で説明したゲート電極の仕事関数変調を利用して閾値電圧を低減する方法。第二は、第3の金属層形成後ソース/ドレイン電極前に熱処理を行い、ゲート絶縁膜中に拡散させた金属元素を利用して閾値電圧を低減する方法である。なお、このときの熱処理温度としては、1000℃以上が好ましい。図18に示すように、本効果が発現した温度が1000℃だったためである。なお、上限としては、一般的なゲート絶縁膜/ゲート電極の耐熱性温度である1100℃以下が適当である。

【0076】

(第3の実施形態)

pチャネル型MISFETの閾値低減方法として、high-kゲート絶縁膜中にAlを添加する方法が知られているが(例えば、K.L.Lee et al., VLSI Tech. Symp. P. 202(2006)、H-S. Jung et al., VLSI Tech. Symp. p.196 (2007)、M. Kadoshima et al., VLSI Tech. Symp. p.66 (2007)、P. Sivasubramani et al., VLSI Tech. Symp. p.68 (2007)、K. Iwamoto et al., VLSI Tech. Symp. p.70 (2007))、本発明はこれらの技術と組み合わせた場合にも効果を得ることが可能である。第3の実施形態では、このような実施形態について説明する。

【0077】

図30は、第3の実施形態に係る半導体装置の断面図である。半導体基板としてSi基板1の表面領域は、n型半導体領域4とp型半導体領域5が設けられ、それぞれの領域にpチャネル型MISFET12、nチャネル型MISFET13が形成されている。n型、p型半導体領域4,5は、所謂ウエルとして形成される。

【0078】

n型半導体領域4の表面上には、例えば,HfSiONといったhigh-kゲート絶縁膜の一部、若しくは全体にAlを含有する7´´が、p型半導体領域5の表面上には、例えばHfSiONといったhigh-kゲート絶縁膜の一部若しくは全体にAlが添加された膜7´´´が形成されている。

【0079】

なお、ここでゲート絶縁膜7´´及び7´´´と記載したのは、後の工程により結果的にn型半導体領域のゲート絶縁膜とp型半導体領域のゲート絶縁膜に違いが生じるためであり、n型、p型半導体領域にそれぞれ別々にゲート絶縁膜を形成するプロセスを必要とするものではない。

【0080】

n型半導体領域4上のゲート絶縁7´´の上には、例えばTaCxからなる下層ゲート電極8が形成されており、p型半導体領域5上のゲート絶縁膜7´´´の上には、例えばTaCxを母体とするゲート電極8´が形成されている。ここでゲート絶縁膜8及び8´と記載したのは、後の工程により結果的にn型半導体領域4の下層ゲート電極とp型半導体領域5の下層ゲート電極に違いが生じる可能性があるためであり、n型、p型半導体領域にそれぞれ別々に下層ゲート電極を形成するプロセスを必要とするものではない。

【0081】

p型半導体領域5のゲート電極8´上にはアルカリ土類金属元素、III族元素(Sc、Y、ランタノイド、アクチノイド)の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含むゲート電極9が形成されている。ゲート電極8´及びゲート電極9の上には、さらに、TaCx、TiNもしくはWなどの高融点金属やポリシリコン電極、若しくはこれらの積層構造によるゲート電極10が形成されている。

【0082】

図31及び図32にTaC/HfSiON/Al2O3/SiO2/Si構造及びTaC/Yb/TaC/HfSiON/Al2O3/SiO2/Si構造を形成した後に、1000℃アニールと、それに続く450℃のフォーミングガスアニールを施して得たMISキャパシタのCV特性の比較、及びVfb値の変化の様子を摸式的に示す。Efは用いたSi基板のフェルミエネルギーである。

【0083】

ゲート電極をTaC/Yb/TaCとする場合、ゲート電極がTaC単層である場合に比べ、CV特性は負方向に600mVほどシフトする。HfSiON/SiO2界面近傍にAlを配すことによるVfb変調量は、正方向に200mVである為、pチャネル型MISFET閾値低減技術が施されている場合にも、Ybによる400mVほどの負方向へのVfb変調効果が保たれていることが分かる。

【0084】

HfSiON/SiO2界面近傍にAlを配する方法としては、high-kゲート絶縁膜/SiO2界面にAl2O3を挿入する方法や、high-kゲート絶縁膜上にAl2O3を形成し、その後の熱工程によってAlを拡散させる方法があるが、通常は、nチャネル型MISFETの閾値を増加させない為に、nチャネル型MISFETの領域に形成されたAL2O3を剥離する必要がある。しかしながら、本発明をnチャネル型MISFET閾値低減方法として用いれば、このAl2O3剥離工程を経ずとも、nチャネル型MISFETの閾値を十分低くすることが出来る。

【0085】

上記のように、第3の実施形態に依れば、pチャネル型MISFETの閾値低減方法として、high-kゲート絶縁膜中にAlを添加する方法を用いた場合でも、nチャネル型MISトランジスタの下層ゲート電極上にアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つをを含む金属層を設けることにより、低い閾値電圧のCMOS半導体装置を実現することが可能になる。

【0086】

以上、本発明を実施形態を通じて説明したが、本発明は上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々な発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態に亘る構成要素を適宜組み合わせても良い。

【図面の簡単な説明】

【0087】

【図1】第1の実施例に関わるCMOS半導体装置の断面図。

【図2】TaC/HfSiON/Si構造を形成後に450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaC/Y,Er若しくはTb/TaC/HfSiON/Si構造を形成後に、450℃のフォーミングガスアニールを施したMISキャパシタのCV特性を比較した図。

【図3】450℃、30分のフォーミングガスアニールを施した場合に、希土類金属層を形成することによって得られるVbシフト量のHfSiON膜厚依存性を示す図。

【図4】450℃、30分のフォーミングガスアニールを施した場合のEr積層によるΔVfbの下層TaC膜厚依存性を示す図。

【図5】TaC/HfSiON/Si構造を形成後に450℃のフォーミングガスアニールを施したMISキャパシタのVfbと、TaC/希土類金属含有層/TaC/HfSiON/Si構造を形成後に450℃、30分のフォーミングガスアニールを施したMISキャパシタのVfbとに、用いたSi基板のフェルミエネルギーEfを加えて比較した図。

【図6】TaCxの仕事関数と組成との関係を示す図。

【図7】TaC/Er/TaC/HfSiON/Si構造を形成後に450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEM像。

【図8】TaC/Er/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEMに、EELS,EDXから判明した各元素の深さ方向分布及びHAADF強度分布を示す図。

【図9】TaC/Er/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタのBack-side SIMS分析により判明したEr,Ta及びSiのプロファイル。

【図10】第1の実施形態に係るCMOS半導体装置製造工程を説明する為の断面図。

【図11】図10に続く工程における断面図。

【図12】図11に続く工程における断面図。

【図13】図12に続く工程における断面図。

【図14】図13に続く工程における断面図。

【図15】第2の実施形態に係るCMOS半導体装置の断面図。

【図16】TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性と、TaCx/Y/TaCx/HfSiON/Si構造を形成後に1000℃アニールを施し、その後さらに450℃のフォーミングガスアニールを施したMISキャパシタのCV特性とを比較した図。

【図17】1000℃アニールと、それに続く450℃のフォーミングガスアニールを施した場合に、Er層を形成することによって得られるVfbシフト量の、HfSiON膜厚依存性を示す図。

【図18】TaCx/Er/TaCx/HfSiON/Si構造を形成後に、450〜1000℃のアニールを施した場合の、Er積層によるΔVfbのHfSiON依存性を示す図。

【図19】1000℃アニールと、それに続く450℃のフォーミングガスアニールを施した場合の、Er積層によるΔVfbの下層TaC膜厚依存性を示す図。

【図20】TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのVfbと、TaC/希土類金属、若しくはアルカリ土類金属含有層/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの(Vfb+Ef)値を比較する図。

【図21】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEM像。

【図22】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタの断面TEMに、EELS,EDXから判明した各元素の深さ方向分布及びHAADF強度分布を示す図。

【図23】TaC/Er/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドSIMS分析により判明したEr、Ta及びSiプロファイル。

【図24】図23と同様な、Yb、Ta及びSiのプロファイル。

【図25】TaC/Yb/TaC/HfSiON/Si構造を形成後に、450℃、30分のフォーミングガスアニールを施したMISキャパシタ及び、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS分析により得られたYb4dスペクトル。

【図26】TaC/Yb/TaC/HfSiON/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのバックサイドXPS分析により得られた、各元素のスペクトルのピーク面積を、各元素の感度係数を用いて相対原子数に換算した値。

【図27】第2の実施形態に係るCMOS半導体装置製造工程を説明するための断面図。

【図28】図27に続く工程における断面図。

【図29】図28に続く工程における断面図。

【図30】第3の実施形態に係るCMOS半導体装置の断面図。

【図31】TaC/HfSiON/Al2O3/SiO2/Si構造及びTaC/Yb/TaC/HfSiON/Al2O3/SiO2/Si構造を形成後に、1000℃アニールとそれに続く450℃、30分のフォーミングガスアニールを施したMISキャパシタのCV特性。

【図32】図31のMISキャパシタの(Vfb+Ef)に対する、Al,Ybの効果を説明する為の図。

【符号の説明】

【0088】

1…Si半導体基板

2、2´…拡散層

3、3´…エクステンション領域

4…n型半導体領域

5…p型半導体領域

6…サイドウオール層

7、7´…ゲート絶縁膜

8、8´…下層ゲート電極

9…アルカリ土類金属元素、Sc、Y、ランタノイド、アクチノイドに属する元素を含む層

10…上層ゲート電極

11…層間絶縁膜

12…pチャネルMISトランジスタ

13…nチャネルMISトランジスタ

18…マスク材

19…STI(素子分離領域)

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、

前記半導体基板上に形成され、前記n型半導体領域とp型半導体領域とを露出するように夫々形成された第1と第2のトレンチを有する第1の絶縁層と、

前記第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、

前記第1のトレンチの側壁と底部に沿って、前記ゲート絶縁膜を介して設けられた第1の金属層と、

前記第2のトレンチの側壁と底部に沿って、前記ゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、

前記第2の金属層上に内張りされたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層と、

前記ゲート絶縁膜を挟む前記n型半導体領域とp型半導体領域に、夫々形成された第1と第2のソース/ドレイン領域と、

を具備することを特徴とする半導体装置。

【請求項2】

前記第2の金属層を構成する元素のうち、前記第3の金属層に含まれる前記金属元素を除いた材料の仕事関数が4.7eV以下であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の金属層は、タンタルカーバイド及び前記第3の金属層に含まれる前記金属元素を有することを特徴とする請求項1又は2のいずれかに記載の半導体装置。

【請求項4】

前記タンタルカーバイドのC原子濃度が85 atomic %以下であることを特徴とする請求項3に記載の半導体装置。

【請求項5】

半導体基板と、

前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、

前記n型半導体層領域上に形成された第1のゲート絶縁膜と、

前記p型半導体層領域上に形成された第2のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1の金属層と、

前記第2のゲート絶縁膜上に、1モノレイヤー以上で1.5nm以下の厚さに形成された第2の金属層と、

前記第2の金属層上に形成されたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層と、

前記第1のゲート絶縁膜を挟む前記n型半導体領域に形成された第1のソース/ドレイン領域と、

前記2のゲート絶縁膜を挟む前記p型半導体領域に形成された第2のソース/ドレイン領域と、

を具備することを特徴とする半導体装置。

【請求項6】

前記第1のソース/ドレイン領域がp型高濃度不純物領域であり、前記第2のソース/ドレイン領域がn型高濃度不純物領域であり、前記金属元素が前記第2のゲート絶縁膜中に存在することを特徴とする請求項5に記載の半導体装置。

【請求項7】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であり、前記金属元素が前記第2のゲート絶縁膜中に存在することを特徴とする請求項5に記載の半導体装置。

【請求項8】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項5に記載の半導体装置。

【請求項9】

前記金属元素が、前記第2のゲート絶縁膜のうち、前記p型半導体領域と前記ゲート絶縁膜の界面からの距離が少なくとも1.5nm以下の領域内に存在することを特徴とする請求項6または7に記載の半導体装置。

【請求項10】

前記第2のゲート絶縁膜中に存在する前記金属元素が占める割合が0.25 atomic %以上であることを特徴とする請求項6,7及び9のいずれかに記載の半導体装置。

【請求項11】

前記第2のゲート絶縁膜における前記金属元素の分布が極大値を持つことを特徴とする請求項6,7,9及び10のいずれかに記載の半導体装置。

【請求項12】

前記第2の金属層を構成する元素のうち、前記第3の金属層に含まれる前記金属元素を除いた材料の仕事関数が4.55eV以下であることを特徴とする請求項5乃至11のいずれかに記載の半導体装置。

【請求項13】

前記第2の金属層は、タンタルカーバイドと前記第3の金属層に含まれる前記金属元素を有することを特徴とする請求項5乃至12のいずれかに記載の半導体装置。

【請求項14】

前記タンタルカーバイドのC原子濃度が65 atomic %以下であることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記第1のゲート絶縁膜が、Alを含むことを特徴とする請求項5乃至14のいずれかに記載の半導体装置。

【請求項16】

素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の、前記n型半導体層領域に第1ダミーゲートを形成するとともに、前記p型半導体領域に第2ダミーゲートを形成する工程と、

前記第1ダミーゲートの両側の前記n型半導体領域に、第1のソース/ドレイン領域を形成する工程と、

前記第2ダミーゲートの両側の前記p型半導体領域に、第2のソース/ドレイン領域を形成する工程と、

前記n型拡散層及び前記p型拡散層を覆うように、前記第1及び第2ダミーゲートの側部に絶縁膜を形成する工程と、

前記第1及び第2ダミーゲートを除去することにより、前記絶縁層に第1及び第2のトレンチを形成する工程と、

前記第1及び第2のトレンチの少なくとも底部に、第1と第2のゲート絶縁膜を夫々形成する工程と、

前記第1のゲート絶縁膜上に第1の金属層を、前記第2のゲート絶縁膜上に第2の金属層を、1モノレイヤー以上1.5nm以下の厚さで夫々形成する工程と、

前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくともいずれか1つを含む第3の金属層を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項17】

前記第2の金属層がタンタルカーバイドであることを特徴とする請求項16に記載の半導体装置の製造方法。

【請求項18】

前記タンタルカーバイドのC原子濃度が85 atomic %以下であることを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の前記n型半導体層領域及び前記p型半導体領域上に、第1と第2のゲート絶縁膜を夫々形成する工程と、

前記第1と第2のゲート絶縁膜上に、第1の金属層と第2の金属層を1モノレイヤー以上で1.5nm以下に夫々形成する工程と、

前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程と、

前記第1のゲート絶縁膜、第1のl金属層と、第2のゲート絶縁膜、第2、第3の金属層とを加工し、第1と第2のゲート電極を夫々加工する工程と、

前記第1と第2のゲート電極を夫々挟む前記n型半導体領域とp型半導体領域に、第1と第2のソース/ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項20】

前記第1と第2のソース/ドレイン領域を形成する工程は、

前記第1のゲート電極を挟む前記n型半導体領域にp型不純物を導入する工程と、

前記第2のゲート電極を挟む前記p型半導体領域にn型不純物を導入する工程と、

前記n型、p型不純物を活性化させるとともに、前記金属元素を第2のゲート絶縁膜中に拡散させる熱処理を行う工程と、

を有することを特徴とする請求項19に記載の半導体装置。

【請求項21】

前記第1と第2のゲート電極を形成する工程の後、第1と第2のソース/ドレイン領域を形成する工程の前に、前記金属元素を第2のゲート絶縁膜中に拡散させる熱処理工程を具備し、

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項19に記載の半導体装置。

【請求項22】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項19に記載の半導体装置。

【請求項23】

前記第2の金属層がタンタルカーバイドであることを特徴とする請求項19乃至22のいずれかに記載の半導体装置の製造方法。

【請求項24】

前記タンタルカーバイドのC原子濃度が65 atomic %以下であることを特徴とする請求項23に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、

前記半導体基板上に形成され、前記n型半導体領域とp型半導体領域とを露出するように夫々形成された第1と第2のトレンチを有する第1の絶縁層と、

前記第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、

前記第1のトレンチの側壁と底部に沿って、前記ゲート絶縁膜を介して設けられた第1の金属層と、

前記第2のトレンチの側壁と底部に沿って、前記ゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、

前記第2の金属層上に内張りされたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層と、

前記ゲート絶縁膜を挟む前記n型半導体領域とp型半導体領域に、夫々形成された第1と第2のソース/ドレイン領域と、

を具備することを特徴とする半導体装置。

【請求項2】

前記第2の金属層を構成する元素のうち、前記第3の金属層に含まれる前記金属元素を除いた材料の仕事関数が4.7eV以下であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の金属層は、タンタルカーバイド及び前記第3の金属層に含まれる前記金属元素を有することを特徴とする請求項1又は2のいずれかに記載の半導体装置。

【請求項4】

前記タンタルカーバイドのC原子濃度が85 atomic %以下であることを特徴とする請求項3に記載の半導体装置。

【請求項5】

半導体基板と、

前記半導体基板の主面に互いに離隔して形成されたn型半導体領域とp型半導体領域と、

前記n型半導体層領域上に形成された第1のゲート絶縁膜と、

前記p型半導体層領域上に形成された第2のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1の金属層と、

前記第2のゲート絶縁膜上に、1モノレイヤー以上で1.5nm以下の厚さに形成された第2の金属層と、

前記第2の金属層上に形成されたアルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層と、

前記第1のゲート絶縁膜を挟む前記n型半導体領域に形成された第1のソース/ドレイン領域と、

前記2のゲート絶縁膜を挟む前記p型半導体領域に形成された第2のソース/ドレイン領域と、

を具備することを特徴とする半導体装置。

【請求項6】

前記第1のソース/ドレイン領域がp型高濃度不純物領域であり、前記第2のソース/ドレイン領域がn型高濃度不純物領域であり、前記金属元素が前記第2のゲート絶縁膜中に存在することを特徴とする請求項5に記載の半導体装置。

【請求項7】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であり、前記金属元素が前記第2のゲート絶縁膜中に存在することを特徴とする請求項5に記載の半導体装置。

【請求項8】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項5に記載の半導体装置。

【請求項9】

前記金属元素が、前記第2のゲート絶縁膜のうち、前記p型半導体領域と前記ゲート絶縁膜の界面からの距離が少なくとも1.5nm以下の領域内に存在することを特徴とする請求項6または7に記載の半導体装置。

【請求項10】

前記第2のゲート絶縁膜中に存在する前記金属元素が占める割合が0.25 atomic %以上であることを特徴とする請求項6,7及び9のいずれかに記載の半導体装置。

【請求項11】

前記第2のゲート絶縁膜における前記金属元素の分布が極大値を持つことを特徴とする請求項6,7,9及び10のいずれかに記載の半導体装置。

【請求項12】

前記第2の金属層を構成する元素のうち、前記第3の金属層に含まれる前記金属元素を除いた材料の仕事関数が4.55eV以下であることを特徴とする請求項5乃至11のいずれかに記載の半導体装置。

【請求項13】

前記第2の金属層は、タンタルカーバイドと前記第3の金属層に含まれる前記金属元素を有することを特徴とする請求項5乃至12のいずれかに記載の半導体装置。

【請求項14】

前記タンタルカーバイドのC原子濃度が65 atomic %以下であることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記第1のゲート絶縁膜が、Alを含むことを特徴とする請求項5乃至14のいずれかに記載の半導体装置。

【請求項16】

素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の、前記n型半導体層領域に第1ダミーゲートを形成するとともに、前記p型半導体領域に第2ダミーゲートを形成する工程と、

前記第1ダミーゲートの両側の前記n型半導体領域に、第1のソース/ドレイン領域を形成する工程と、

前記第2ダミーゲートの両側の前記p型半導体領域に、第2のソース/ドレイン領域を形成する工程と、

前記n型拡散層及び前記p型拡散層を覆うように、前記第1及び第2ダミーゲートの側部に絶縁膜を形成する工程と、

前記第1及び第2ダミーゲートを除去することにより、前記絶縁層に第1及び第2のトレンチを形成する工程と、

前記第1及び第2のトレンチの少なくとも底部に、第1と第2のゲート絶縁膜を夫々形成する工程と、

前記第1のゲート絶縁膜上に第1の金属層を、前記第2のゲート絶縁膜上に第2の金属層を、1モノレイヤー以上1.5nm以下の厚さで夫々形成する工程と、

前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくともいずれか1つを含む第3の金属層を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項17】

前記第2の金属層がタンタルカーバイドであることを特徴とする請求項16に記載の半導体装置の製造方法。

【請求項18】

前記タンタルカーバイドのC原子濃度が85 atomic %以下であることを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

素子分離されたn型半導体領域及びp型半導体領域を有する半導体基板の前記n型半導体層領域及び前記p型半導体領域上に、第1と第2のゲート絶縁膜を夫々形成する工程と、

前記第1と第2のゲート絶縁膜上に、第1の金属層と第2の金属層を1モノレイヤー以上で1.5nm以下に夫々形成する工程と、

前記n型半導体領域の前記第1の金属層をマスクしつつ、前記p型半導体領域の前記第2の金属層上に、アルカリ土類金属元素、III族元素の内の少なくとも1つの金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つを含む第3の金属層を形成する工程と、

前記第1のゲート絶縁膜、第1のl金属層と、第2のゲート絶縁膜、第2、第3の金属層とを加工し、第1と第2のゲート電極を夫々加工する工程と、

前記第1と第2のゲート電極を夫々挟む前記n型半導体領域とp型半導体領域に、第1と第2のソース/ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項20】

前記第1と第2のソース/ドレイン領域を形成する工程は、

前記第1のゲート電極を挟む前記n型半導体領域にp型不純物を導入する工程と、

前記第2のゲート電極を挟む前記p型半導体領域にn型不純物を導入する工程と、

前記n型、p型不純物を活性化させるとともに、前記金属元素を第2のゲート絶縁膜中に拡散させる熱処理を行う工程と、

を有することを特徴とする請求項19に記載の半導体装置。

【請求項21】

前記第1と第2のゲート電極を形成する工程の後、第1と第2のソース/ドレイン領域を形成する工程の前に、前記金属元素を第2のゲート絶縁膜中に拡散させる熱処理工程を具備し、

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項19に記載の半導体装置。

【請求項22】

前記第1と第2のソース/ドレイン領域が第1と第2のソース/ドレイン電極であることを特徴とする請求項19に記載の半導体装置。

【請求項23】

前記第2の金属層がタンタルカーバイドであることを特徴とする請求項19乃至22のいずれかに記載の半導体装置の製造方法。

【請求項24】

前記タンタルカーバイドのC原子濃度が65 atomic %以下であることを特徴とする請求項23に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【公開番号】特開2009−164207(P2009−164207A)

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願番号】特願2007−339944(P2007−339944)

【出願日】平成19年12月28日(2007.12.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願日】平成19年12月28日(2007.12.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]