半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に金属材料からなるゲート電極を有するMISFET(Metal Insulator Semiconductor Field Effect Transistor)を備えた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体集積回路装置の高集積化及び高速化に伴い、MISFETの微細化が進められている。MISFETの微細化によるゲート絶縁膜の極薄膜化に伴い、ポリシリコンゲート電極の空乏容量の顕在化及びボロンのチャネル領域への突き抜けという問題がある。この問題の解決策として、n型MISFET(以下、「n型MISトランジスタ」と称す)のゲート電極として金属材料からなるメタルゲート電極を用いると共に、p型MISFET(以下、「p型MISトランジスタ」と称す)のゲート電極として金属材料からなるメタルゲート電極を用いたデュアルメタルゲート構造の半導体装置が検討されている。

【0003】

デュアルメタルゲート構造の半導体装置の場合、n型MISトランジスタのゲート電極と、p型MISトランジスタのゲート電極とが互いに異なる金属材料からなることが必要とされる。例えば、n型MISトランジスタのゲート電極は、4.05eV以上で4.6eV以下の仕事関数を有する金属材料からなる一方、p型MISトランジスタのゲート電極は、4.6eV以上で5.15eV以下の仕事関数を有する金属材料からなることが必要とされる。

【0004】

デュアルメタルゲート構造の半導体装置の製造方法としては、例えば、第1の従来の半導体装置の製造方法(例えば非特許文献1参照)、及び第2の従来の半導体装置の製造方法(例えば非特許文献2参照)が提案されている。

【非特許文献1】Z.B.Zhang et al., “Integration of Dual Metal Gate CMOS withTaSiN(NMOS) and Ru(PMOS) Gate Electrodes on HfO2 Gate Dielectric”, VLSI2005

【非特許文献2】S.C.Song et al., “Highly Manufacturable 45nm LSTP CMOSFETs Using Novel Dual High-k and Dual Metal Gate CMOS Integration”, VLSI2006

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、第1,第2の従来の半導体装置の製造方法では、以下に示す問題がある。

【0006】

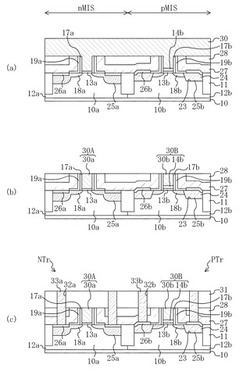

以下に、第1の従来の半導体装置の製造方法及びその問題点について順に説明する。第1の従来の半導体装置の製造方法について、図13を参照しながら説明する。図13は、第1の従来の半導体装置の製造方法を示すゲート幅方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0007】

まず、半導体基板100の上部に素子分離領域101を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域101に囲まれた第1の活性領域100aが形成され、p型MIS形成領域には、素子分離領域101に囲まれた第2の活性領域100bが形成される。その後、半導体基板100におけるn型MIS形成領域にp型ウェル領域102aを形成する一方、半導体基板100におけるp型MIS形成領域にn型ウェル領域102bを形成する。

【0008】

次に、半導体基板100上に、ゲート絶縁膜形成膜、n型MISトランジスタ用のゲート電極材料(以下、「nMIS用金属材料」と称す)からなる第1の金属膜、p型MISトランジスタ用のゲート電極材料(以下、「pMIS用金属材料」と称す)からなる第2の金属膜、及びシリコン膜を順次形成する。

【0009】

このようにして、図13に示すように、第1の活性領域100a上に、ゲート絶縁膜形成膜103a、第1の金属膜104a、第2の金属膜105a、及びシリコン膜106aが順次形成された第1のパターニング部107Aを形成すると共に、第2の活性領域100b上に、ゲート絶縁膜形成膜103b、第2の金属膜105b、及びシリコン膜106bが順次形成された第2のパターニング部107Bを形成する。

【0010】

その後、図示しないが、シリコン膜106a,106b上に形成されたゲートパターン形状を有するレジストをマスクにして、ドライエッチング法により、第1のパターニング部107Aをパターニングして、ゲート絶縁膜形成膜103aからなる第1のゲート絶縁膜、並びに第1の金属膜104a、第2の金属膜105a、及びシリコン膜106aからなる第1のゲート電極を形成すると共に、第2のパターニング部107Bをパターニングして、ゲート絶縁膜形成膜103bからなる第2のゲート絶縁膜、並びに第2の金属膜105b及びシリコン膜106bからなる第2のゲート電極を形成する。

【0011】

ここで、第1の従来の半導体装置の製造方法における問題点について説明する。第1の従来の半導体装置の製造方法では、図13に示すように、第1のパターニング部107Aと第2のパターニング部107Bとは、互いに構成が異なるにも拘わらず(詳細には、第1のパターニング部107Aの構成は4層構成であるのに対し、第2のパターニング部107Bの構成は3層構成である)、互いに同一の工程において、すなわち、互いに同一のエッチング条件の下、パターニングされるため、第1のゲート電極及び第2のゲート電極の双方を精度良く形成することができないという問題がある。例えば、エッチング条件を、第2のゲート電極が精度良く形成されるエッチング条件にした場合、第1のパターニング部107Aにおける第1の金属膜104a及びゲート絶縁膜形成膜103aがエッチングされずに残存するため、第1のゲート電極を精度良く形成することができない。一方、例えば、エッチング条件を、第1のゲート電極が精度良く形成されるエッチング条件にした場合、p型MIS形成領域の半導体基板100及び素子分離領域101中にエッチング削れが発生するので、第2のゲート電極を精度良く形成することができない。

【0012】

以下に、第2の従来の半導体装置の製造方法及びその問題点について順に説明する。第2の従来の半導体装置の製造方法について、図14(a) 〜(e) を参照しながら説明する。図14(a) 〜(e) は、第2の従来の半導体装置の製造方法を工程順に示すゲート幅方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0013】

まず、半導体基板200の上部に素子分離領域201を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域201に囲まれた第1の活性領域200aが形成され、p型MIS形成領域には、素子分離領域201に囲まれた第2の活性領域200bが形成される。その後、半導体基板200におけるn型MIS形成領域にp型ウェル領域202aを形成する一方、半導体基板200におけるp型MIS形成領域にn型ウェル領域202bを形成する。

【0014】

次に、半導体基板200上に、n型MISトランジスタ用のゲート絶縁膜材料(以下、「nMIS用絶縁材料」と称す)からなる第1のゲート絶縁膜形成膜、nMIS用金属材料からなる第1の金属膜、及び第1のマスク膜を順次形成する。その後、図14(a) に示すように、フォトリソグラフィ法により、第1のマスク膜上にn型MIS形成領域を覆うレジストマスク206を形成する。

【0015】

次に、レジストマスク206をマスクにして、第1のマスク膜をエッチングして、第1のマスク膜205aを形成した後、レジストマスク206を除去する。その後、第1のマスク膜205aをマスクにして、第1の金属膜204、及び第1のゲート絶縁膜形成膜203を順次エッチングする。

【0016】

次に、図14(b) に示すように、半導体基板200上に、p型MISトランジスタ用のゲート絶縁膜材料(以下、「pMIS用絶縁材料」と称す)からなる第2のゲート絶縁膜形成膜207、pMIS用金属材料からなる第2の金属膜208、及び第2のマスク膜209を順次形成する。その後、フォトリソグラフィ法により、第2のマスク膜209上にp型MIS形成領域を覆うレジストマスク210を形成する。

【0017】

次に、図14(c) に示すように、レジストマスク210をマスクにして、第2のマスク膜209をエッチングして、第2のマスク膜209bを形成した後、レジストマスク210を除去する。その後、第2のマスク膜209bをマスクにして、第2の金属膜208、及び第2のゲート絶縁膜形成膜207を順次エッチングする。

【0018】

次に、図14(d) に示すように、第1,第2のマスク膜205a,209bを除去した後、第1の金属膜204及び第2の金属膜208上に、シリコン膜211を形成する。

【0019】

このようにして、図14(d) に示すように、第1の活性領域200a上に、第1のゲート絶縁膜形成膜203、第1の金属膜204、及びシリコン膜211が順次形成された第1のパターニング部を形成すると共に、第2の活性領域200b上に、第2のゲート絶縁膜形成膜207、第2の金属膜208、及びシリコン膜211が順次形成された第2のパターニング部を形成する。

【0020】

次に、図14(e) に示すように、フォトリソグラフィ法により、シリコン膜211上にゲートパターン形状を有するレジスト(図示せず)を形成した後、レジストをマスクにして、エッチング法により、第1のパターニング部をパターニングして、第1のゲート絶縁膜203a、並びに第1の金属膜204a及び第1のシリコン膜211aからなる第1のゲート電極212Aを形成すると共に、第2のパターニング部をパターニングして、第2のゲート絶縁膜207b、並びに第2の金属膜208b及び第2のシリコン膜211bからなる第2のゲート電極212Bを形成する。

【0021】

ここで、第2の従来の半導体装置の製造方法における問題点について、図15を参照しながら説明する。図15は、第2の従来の半導体装置の製造方法における問題点について示す平面図である。なお、図15に示すXIVe-XIVe線は、図14(e) に示す断面図の断面線に相当する。

【0022】

p型MIS形成領域を覆うレジストマスク210が、ゲート幅方向にずれて形成されて、図14(b) に示すように、レジストマスク210のゲート幅方向の端部が、n型MIS形成領域側に位置すると、図14(d) に示すように、素子分離領域201上に、第1のマスク膜205aの残部205c、第2のゲート絶縁膜形成膜207の残部207c、及び第2の金属膜208の残部208cからなる残部rが突出して形成される。

【0023】

この残部rが形成された状態でパターニングを行うと、図15に示すように、素子分離領域201上に、ゲート長方向に伸びるように、パターニングされた残部rp(なお、パターニングされた残部rpは、図14(e) に示すように、パターニングされた残部205cpと、パターニングされた残部207cpと、パターニングされた残部208cpとからなる)が残存する。加えて、パターニングされた残部rpのゲート幅方向の側面上に、シリコン膜211からなる側壁絶縁膜211cが形成される。

【0024】

パターニングされた残部rp(又は側壁絶縁膜211c)により、第1,第2のゲート電極212A,212Bが、第1,第2のゲート電極212A,212Bとゲート長方向に沿って隣り合う他の第1,第2のゲート電極(図示せず)と電気的に接続するため、第1,第2のゲート電極212A,212Bはゲート電極としての機能を果たさない。このように、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極212A,212Bを形成することができないという問題がある。

【0025】

なお、この問題の要因として、p型MIS形成領域を覆うレジストマスク210がn型MIS形成領域側にずれて形成される場合を具体例に挙げて説明したが、仮にレジストマスク210がn型MIS形成領域側にずれて形成されることがなくとも、n型MIS形成領域を覆うレジストマスク206がp型MIS形成領域側にずれて形成されることにより、上記と同様の問題が生じる。すなわち、図14(a) に示す工程において、レジストマスク206が、p型MIS形成領域側にずれて形成された場合、図16に示すように、素子分離領域201上に残部rが突出して形成される。

【0026】

ここで、上記の問題は、素子分離領域201のゲート幅方向の幅を拡げることで回避することが可能である。すなわち、素子分離領域201に予め合わせマージン(余裕領域)を設けて、素子分離領域201のゲート幅方向の幅を拡げることで、図14(a) に示す工程において、レジストマスク206の形成の際に、レジストマスク206がゲート幅方向にずれて形成されることがあっても、レジストマスク206のゲート幅方向の端部を、p型MIS形成領域側に位置させずに、n型MIS形成領域側に位置させることができる。それと共に、図14(b) に示す工程において、レジストマスク210の形成の際に、レジストマスク210がゲート幅方向にずれて形成されることがあっても、レジストマスク210のゲート幅方向の端部を、n型MIS形成領域側に位置させずに、p型MIS形成領域側に位置させることができる。しかしながら、この場合、次に示す問題がある。すなわち、レジストマスク206の形成、及びレジストマスク210の形成の際に、素子分離領域201に合わせマージンが必要とされるため、素子分離領域201のゲート幅方向の幅を縮小化することができないという問題がある。

【0027】

さらに、第2の従来の半導体装置の製造方法では、図14(d) に示すように、第1のパターニング部と第2のパターニング部とは、互いに構成が異なるにも拘わらず(詳細には、第1,第2のパターニング部は、互いに同一のシリコン膜211を有するものの、互いに異なる第1,第2のゲート絶縁膜形成膜203,207及び第1,第2の金属膜204,208を有する)、言い換えれば、互いにエッチング特性が異なるにも拘わらず、互いに同一のエッチング条件の下、パターニングされるため、第1,第2のゲート電極の双方を精度良く形成することができないという問題もある。

【0028】

このように、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極を形成することは可能なものの、第1,第2のゲート電極の双方を精度良く形成することはできず、さらに、素子分離領域201のゲート幅方向の幅を縮小化することができないという問題がある。

【0029】

以上のように、第1の従来の半導体装置の製造方法では、第1,第2のゲート電極の双方を精度良く形成することができないという問題がある。一方、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極の双方を精度良く形成することができないだけでなく、さらに、素子分離領域のゲート幅方向の幅を縮小化することができないという問題がある。

【0030】

前記に鑑み、本発明の目的は、互いに異なる金属材料からなるゲート電極を有するn型,p型MISトランジスタを備えた半導体装置において、精度良く形成されたn型,p型MISトランジスタのゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現することである。

【課題を解決するための手段】

【0031】

前記の目的を達成するために、本発明に係る半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板における第1の活性領域上に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第2の金属膜からなる第1のゲート電極と、第1のゲート電極の側面上から第1の活性領域における第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜とを備え、第2のMISトランジスタは、半導体基板における第2の活性領域上に形成された第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成され第1の金属膜と第1の金属膜上に形成された導電膜とからなる第2のゲート電極と、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1のゲート電極及び第2のゲート電極の各上面上には、絶縁膜が形成されていないことを特徴とする。

【0032】

本発明に係る半導体装置によると、精度良く形成された第1,第2のゲート電極を実現することができる。加えて、ゲート幅方向の幅が縮小化された素子分離領域を実現することができるので、半導体装置の微細化を図ることができる。

【0033】

本発明に係る半導体装置において、第1の金属膜は、第2の金属膜に比べて膜厚が薄いことが好ましい。

【0034】

本発明に係る半導体装置において、第1の金属膜と第2の金属膜とは、互いに仕事関数が異なっていることが好ましい。

【0035】

本発明に係る半導体装置において、絶縁膜の膜厚は、第1のゲート電極の膜厚に比べて薄いことが好ましい。

【0036】

本発明に係る半導体装置において、導電膜は、第2の金属膜からなることが好ましい。

【0037】

本発明に係る半導体装置において、導電膜は、シリコン膜からなり、シリコン膜上に形成された金属シリサイド膜をさらに備えていることが好ましい。

【0038】

本発明に係る半導体装置において、第1のゲート絶縁膜は、第2のゲート絶縁膜と同じ絶縁材料からなることが好ましい。

【0039】

本発明に係る半導体装置において、第1のゲート絶縁膜は、第2のゲート絶縁膜と異なる絶縁材料からなることが好ましい。

【0040】

本発明に係る半導体装置において、第1のゲート電極の側面上に形成された断面形状がL字状の第1の内側サイドウォールと、第2のゲート電極の側面上に形成された断面形状がL字状の第2の内側サイドウォールとをさらに備え、絶縁膜は、第1の内側サイドウォール及び第2の内側サイドウォールの上に接して形成されていることが好ましい。

【0041】

本発明に係る半導体装置において、絶縁膜は、第1の活性領域におけるチャネル領域のゲート長方向に第1の応力を生じさせる応力絶縁膜であることが好ましい。

【0042】

このようにすると、応力絶縁膜により、第1の活性領域におけるチャネル領域のゲート長方向に第1の応力を印加して、第1のMISトランジスタの駆動能力を向上させることができる。

【0043】

本発明に係る半導体装置において、第1のMISトランジスタは、n型MISトランジスタであり、絶縁膜は、シリコン窒化膜からなり、第1の応力は、引っ張り応力であることが好ましい。

【0044】

本発明に係る半導体装置において、第2の活性領域における第2のゲート電極の外側方下に形成されたソースドレイン領域をさらに備え、ソースドレイン領域は、第2の活性領域に設けられたトレンチ内に形成され、第2の活性領域におけるチャネル領域のゲート長方向に第2の応力を生じさせるシリコン混晶層を含むことが好ましい。

【0045】

このようにすると、シリコン混晶層により、第2の活性領域におけるチャネル領域のゲート長方向に第2の応力を印加して、第2のMISトランジスタの駆動能力を向上させることができる。

【0046】

本発明に係る半導体装置において、第2のMISトランジスタは、p型MISトランジスタであり、シリコン混晶層は、SiGe層からなり、第2の応力は、圧縮応力であることが好ましい。

【0047】

本発明に係る半導体装置において、第1のゲート絶縁膜及び第2のゲート絶縁膜は、比誘電率が10以上の金属酸化物からなる高誘電率膜を含むことが好ましい。

【0048】

前記の目的を達成するために、本発明に係る半導体装置の製造方法は、半導体基板における第1の活性領域上に形成された第1のMISトランジスタと、半導体基板における第2の活性領域上に形成された第2のMISトランジスタとを有する半導体装置の製造方法であって、第1の活性領域上に第1のゲート絶縁膜、第1の金属膜及び第1のシリコン膜を有する第1のゲート電極形成部を形成すると共に、第2の活性領域上に第2のゲート絶縁膜、第1の金属膜及び第2のシリコン膜を有する第2のゲート電極形成部を形成する工程(a)と、工程(a)の後に、半導体基板上に第1のゲート電極形成部及び第2のゲート電極形成部を覆う絶縁膜を形成する工程(b)と、第1のゲート電極形成部及び第2のゲート電極形成部の上に形成されている絶縁膜を除去して、第1のゲート電極形成部における第1のシリコン膜及び第2のゲート電極形成部における第2のシリコン膜の各上面を露出する工程(c)と、工程(c)の後に、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して、第1の活性領域上に絶縁膜に囲まれた第1の凹部を形成する工程(d)と、第1の凹部内に第2の金属膜を形成する工程(e)とを備え、第1のMISトランジスタの第1のゲート電極は、第2の金属膜からなり、第2のMISトランジスタの第2のゲート電極は、第2のゲート電極形成部における第1の金属膜を含むことを特徴とする。

【0049】

本発明に係る半導体装置の製造方法によると、互いに同一の工程において、第1,第2のゲート電極形成部を形成した後、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して形成された第1の凹部内に、第2の金属膜を形成して、第2の金属膜からなる第1のゲート電極を形成する。一方、第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成する。そのため、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を、第2の金属膜に置換するに当たっては、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の際には、素子分離領域に合わせマージンは必要とされない。従って、素子分離領域に合わせマージンが必要とされる工程数を削減することができるため、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域のゲート幅方向の幅を縮小化することができるので、半導体装置の微細化を図ることができる。

【0050】

加えて、互いに同一の工程において、互いに同一の構成の第1,第2のゲート電極形成部(言い換えれば、互いに同一のエッチング特性の第1,第2のゲート電極形成部)を形成するため、第1,第2のゲート電極形成部を容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部における第1の金属膜及び第1のシリコン膜を、第2の金属膜と置換して、第2の金属膜からなる第1のゲート電極を形成することができる。一方、精度良く形成された第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成することができるため、精度良く形成された第1,第2のゲート電極を実現することができる。

【0051】

本発明に係る半導体装置の製造方法において、工程(d)は、第1の活性領域上に第1のゲート絶縁膜が底面に露出する第1の凹部を形成すると共に、第2のゲート電極形成部における第2のシリコン膜を除去して、第2の活性領域上に絶縁膜に囲まれ、第1の金属膜が底面に露出する第2の凹部を形成する工程を含み、工程(e)は、第1の凹部内における第1のゲート絶縁膜上に第2の金属膜を形成すると共に、第2の凹部内における第1の金属膜上に第2の金属膜を形成する工程を含み、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜と、第1の金属膜上に形成された第2の金属膜とからなることが好ましい。

【0052】

このようにすると、第1のゲート電極形成部における第1の金属膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0053】

本発明に係る半導体装置の製造方法において、工程(d)は、第1の活性領域上に第1のゲート絶縁膜が底面に露出する第1の凹部を形成する工程を含み、工程(e)は、第1の凹部内における第1のゲート絶縁膜上に第2の金属膜を形成する工程を含み、工程(e)の後に、第2のシリコン膜上に金属シリサイド膜を形成する工程(f)をさらに備え、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜及び第2のシリコン膜からなることが好ましい。

【0054】

このようにすると、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0055】

本発明に係る半導体装置の製造方法において、工程(d)は、第1のゲート電極形成部における第1のシリコン膜、第1の金属膜及び第1のゲート絶縁膜を順次除去して、第1の活性領域上に第1の活性領域が底面に露出する第1の凹部を形成する工程を含み、工程(e)は、第1の凹部内に第3のゲート絶縁膜を形成すると共に、第3のゲート絶縁膜上に第2の金属膜を形成する工程を含み、工程(e)の後に、第2のシリコン膜上に金属シリサイド膜を形成する工程(f)をさらに備え、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜及び第2のシリコン膜からなることが好ましい。

【0056】

このようにすると、第1のゲート電極形成部における第1のシリコン膜、第1の金属膜及び第1のゲート絶縁膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0057】

本発明に係る半導体装置の製造方法において、工程(a)の後で、工程(b)の前に、第1のゲート電極形成部の側面上に断面形状がL字状の第1の内側サイドウォールを形成すると共に、第2のゲート電極形成部の側面上に断面形状がL字状の第2の内側サイドウォールを形成する工程(g)をさらに備え、工程(b)において、絶縁膜を、第1の内側サイドウォール及び第2の内側サイドウォールの上に接して形成することが好ましい。

【0058】

本発明に係る半導体装置の製造方法において、工程(a)の後で、工程(b)の前に、第2の活性領域における第2のゲート電極形成部の外側方下にトレンチを形成する工程(h)と、トレンチ内に、第2の活性領域におけるチャネル領域のゲート長方向に応力を生じさせるシリコン混晶層を形成する工程(i)とをさらに備えていることが好ましい。

【発明の効果】

【0059】

本発明に係る半導体装置及びその製造方法によると、互いに同一の工程において、第1,第2のゲート電極形成部を形成した後、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して形成された第1の凹部内に、第2の金属膜を形成して、第2の金属膜からなる第1のゲート電極を形成する。一方、第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成する。そのため、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を、第2の金属膜に置換するに当たっては、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の際には、素子分離領域に合わせマージンは必要とされない。従って、素子分離領域に合わせマージンが必要とされる工程数を削減することができるため、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域のゲート幅方向の幅を縮小化することができるので、半導体装置の微細化を図ることができる。

【0060】

加えて、互いに同一の工程において、互いに同一の構成の第1,第2のゲート電極形成部を形成するため、第1,第2のゲート電極形成部を容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部における第1の金属膜及び第1のシリコン膜を、第2の金属膜と置換して、第2の金属膜からなる第1のゲート電極を形成することができる。一方、精度良く形成された第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成することができるため、精度良く形成された第1,第2のゲート電極を実現することができる。

【発明を実施するための最良の形態】

【0061】

以下に、本発明の各実施形態について、図面を参照しながら説明する。

【0062】

(第1の実施形態)

本発明の第1の実施形態に係る半導体装置及びその製造方法について図面を参照しながら説明する。

【0063】

以下に、本発明の第1の実施形態に係る半導体装置の製造方法について、図1(a) 〜(d) 、図2(a) 〜(d) 、図3(a) 〜(d) 、図4(a) 〜(c) 及び図5(a) 〜(c) を参照しながら説明する。図1(a) 〜図5(c) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0064】

まず、図1(a) に示すように、例えば埋め込み素子分離(Shallow Trench Isolation:STI)法により、例えばp型シリコンからなる半導体基板10の上部に、トレンチ内に絶縁膜が埋め込まれた素子分離領域11を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域11に囲まれた半導体基板10からなる第1の活性領域10aが形成され、p型MIS形成領域には、素子分離領域11に囲まれた半導体基板10からなる第2の活性領域10bが形成される。その後、リソグラフィ法及びイオン注入法により、半導体基板10におけるn型MIS形成領域に、例えばB(ホウ素)等のp型不純物を注入する一方、半導体基板10におけるp型MIS形成領域に、例えばP(リン)等のn型不純物を注入した後、半導体基板10に対して例えば850℃,30秒間の熱処理を施すことにより、半導体基板10におけるn型MIS形成領域に、p型ウェル領域12aを形成する一方、半導体基板10におけるp型MIS形成領域に、n型ウェル領域12bを形成する。

【0065】

次に、図1(b) に示すように、例えば希釈フッ酸処理により、半導体基板10の表面を洗浄した後、例えばISSG(In-Situ Steam Generation)酸化法により、第1の活性領域10a及び第2の活性領域10b上に、例えば膜厚が0.8〜1nm程度のシリコン酸化膜からなる下地膜(図示せず)を形成する。その後、例えば有機金属気相堆積(Metal Organic Chemical Vapor Deposition:MOCVD)法により、下地膜上に、例えば膜厚が2nmの高誘電率膜からなるゲート絶縁膜形成膜13を堆積する。ここで、ゲート絶縁膜形成膜13としては、比誘電率が10以上の金属酸化物からなる高誘電率膜を含むことが望ましい。

【0066】

その後、例えばCVD(Chemical Vapor Deposition)法、ALD(Atomic Layer Deposition)法、又はスパッタ法等により、例えば窒化チタン(TiN)からなる第1の金属膜14を堆積する。ここで、第1の金属膜14としては、p型MISトランジスタ用に最適化された金属材料又は金属化合物材料(以下、「pMIS用金属材料」と称す)からなり、4.6eV以上で5.15eV以下の仕事関数を有することが望ましい。そして、第1の金属膜14の具体例としては、TiN膜の他に、例えば、チタン(Ti)、ルテニウム(Ru)、白金(Pt)若しくはタングステン(W)等の金属、又はTi、Ru、Pt及びWのうち少なくとも1種以上の金属を含む窒化物、炭素窒化物若しくは珪素窒化物等が挙げられる。その後、例えばCVD法により、第1の金属膜14上に、例えば膜厚が100nmのポリシリコン膜からなるシリコン膜15を堆積した後、例えばCVD法により、シリコン膜15上に、例えば膜厚が30nmのシリコン酸化膜からなる保護膜16を堆積する。

【0067】

次に、図1(c) に示すように、フォトリソグラフィ法により、保護膜16上に、ゲートパターン形状を有するレジスト(図示せず)を形成する。その後、レジストをマスクにして、ドライエッチング法により、保護膜16、シリコン膜15、第1の金属膜14及びゲート絶縁膜形成膜13を順次パターニングする。これにより、第1の活性領域10a上に、第1のゲート絶縁膜13a、第1の金属膜14a、第1のシリコン膜15a及び第1の保護膜16aを順次形成すると共に、第2の活性領域10b上に、第2のゲート絶縁膜13b、第1の金属膜14b、第2のシリコン膜15b及び第2の保護膜16bを順次形成する。

【0068】

このようにして、第1の活性領域10a上に第1のゲート絶縁膜13a、第1の金属膜14a及び第1のシリコン膜15aを有する第1のゲート電極形成部14Aを形成すると共に、第2の活性領域10b上に第2のゲート絶縁膜13b、第1の金属膜14b及び第2のシリコン膜15bを有する第2のゲート電極形成部14Bを形成する。

【0069】

次に、図1(d) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなるオフセットスペーサ用絶縁膜を堆積した後、オフセットスペーサ用絶縁膜に対して異方性エッチングを行う。これにより、第1のゲート電極形成部14Aの側面上に第1のオフセットスペーサ17aを形成すると共に、第2のゲート電極形成部14Bの側面上に第2のオフセットスペーサ17bを形成する。

【0070】

その後、半導体基板10上にn型MIS形成領域を開口しp型MIS形成領域を覆うレジスト(図示せず)を形成した後、第1の活性領域10aに、第1のゲート電極形成部14Aをマスクにして、例えばAs(ヒ素)等のn型不純物を注入することにより、第1の活性領域10aにおける第1のゲート電極形成部14Aの側方下に接合深さが比較的浅いn型ソースドレイン領域(LDD領域又はエクステンション領域)18aを自己整合的に形成する。一方、半導体基板10上にn型MIS形成領域を覆いp型MIS形成領域を開口するレジスト(図示せず)を形成した後、第2の活性領域10bに、第2のゲート電極形成部14Bをマスクにして、例えばBF2等のp型不純物を注入することにより、第2の活性領域10bにおける第2のゲート電極形成部14Bの側方下に接合深さが比較的浅いp型ソースドレイン領域(LDD領域又はエクステンション領域)18bを自己整合的に形成する。

【0071】

次に、図2(a) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなる第1の絶縁膜、及び膜厚が30nmのシリコン窒化膜からなる第2の絶縁膜を順次堆積した後、第1の絶縁膜及び第2の絶縁膜に対して異方性エッチングを行う。これにより、第1のゲート電極形成部14Aの側面上に、第1のオフセットスペーサ17aを介して、断面形状がL字状の第1の絶縁膜からなる第1の内側サイドウォール19aと第1の内側サイドウォール19a上に形成された第2の絶縁膜からなる第1の外側サイドウォール20aとで構成された第1のサイドウォール20Aを形成すると共に、第2のゲート電極形成部14Bの側面上に、第2のオフセットスペーサ17bを介して、断面形状がL字状の第1の絶縁膜からなる第2の内側サイドウォール19bと第2の内側サイドウォール19b上に形成された第2の絶縁膜からなる第2の外側サイドウォール20bとで構成された第2のサイドウォール20Bを形成する。

【0072】

次に、図2(b) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなる表面保護膜21を堆積する。

【0073】

次に、図2(c) に示すように、表面保護膜21上に、n型MIS形成領域を覆いp型MIS形成領域を開口するレジストマスク22を形成した後、第2の外側サイドウォール20b(シリコン窒化膜)と選択比のある異方性ドライエッチング法を用いて、p型MIS形成領域に形成されている表面保護膜21を除去して、n型MIS形成領域に表面保護膜21aを残存させる。これにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下の領域、すなわち、ソースドレイン形成領域の表面を露出させる。

【0074】

次に、図2(d) に示すように、レジストマスク22を除去した後、表面保護膜21a(シリコン酸化膜)、第2の保護膜16b(シリコン酸化膜)、第2のオフセットスペーサ17b(シリコン酸化膜)、第2の内側サイドウォール19b(シリコン酸化膜)及び第2の外側サイドウォール20b(シリコン窒化膜)と選択比のあるドライエッチング法を用いる、又はこれらの膜と選択比のあるドライエッチング法及びウェットエッチング法を順次組み合わせて用いて、表面に露出されている第2の活性領域10bをエッチングする。これにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下の領域(すなわちソースドレイン形成領域)に、例えば深さが60nmのトレンチ23を形成する。このとき、第1の活性領域10aの表面は表面保護膜21aで覆われているため、第1の活性領域10aはエッチングされない。また、第1のシリコン膜15aの上面は第1の保護膜16a及び表面保護膜21aで順次覆われている一方、第2のシリコン膜15bの上面は第2の保護膜16bで覆われているため、第1,第2のシリコン膜15a,15bはエッチングされない。

【0075】

次に、図3(a) に示すように、例えばフッ酸処理により、トレンチ23内のエッチング残渣及び自然酸化膜等を除去した後、例えばCVD法により、例えばシランガス(SiH4)及びゲルマンガス(GeH4)を、例えばジボランガス(B2H6)等のp型ドーパントガスと共に例えば650〜700℃の温度で供給することにより、トレンチ23内を充填するようにp型SiGe層からなるシリコン混晶層24をエピタキシャル成長させる。このとき、第1の活性領域10aの表面は表面保護膜21aで覆われているため、第1の活性領域10a上にSiGe層はエピタキシャル成長されない。また、第1のシリコン膜15aの上面は第1の保護膜16a及び表面保護膜21aで順次覆われている一方、第2のシリコン膜15bの上面は第2の保護膜16bで覆われているため、第1,第2のシリコン膜15a,15b上にSiGe層はエピタキシャル成長されない。

【0076】

その後、半導体基板10及び第1の外側サイドウォール20a(シリコン窒化膜)と選択比のあるドライエッチング法を用いる、又はこれらの膜と選択比のあるドライエッチング法及びウェットエッチング法を順次組み合わせて用いて、n型MIS形成領域に形成されている表面保護膜21aを除去して、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下の領域、すなわち、ソースドレイン形成領域の表面を露出させる。

【0077】

このように図2(b) 〜図3(a) に示す工程を順次経ることにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に形成されたトレンチ23内に、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を生じさせるシリコン混晶層24を形成する。

【0078】

次に、図3(b) に示すように、リソグラフィ法及びイオン注入法により、第1の活性領域10aに、第1のゲート電極形成部14A、第1のオフセットスペーサ17a及び第1のサイドウォール20Aをマスクにして、例えばAs(ヒ素)等のn型不純物を注入することにより、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に、浅いn型ソースドレイン領域18aよりも深い接合深さを有し、接合深さが比較的深いn型ソースドレイン領域25aを自己整合的に形成する。一方、第2の活性領域10bに、第2のゲート電極形成部14B、第2のオフセットスペーサ17b及び第2のサイドウォール20Bをマスクにして、例えばB(ボロン)等のp型不純物を注入することにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に、浅いp型ソースドレイン領域18bよりも深い接合深さを有し、接合深さが比較的深いp型ソースドレイン領域25bを自己整合的に形成する。その後、熱処理により、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bに含まれる不純物を活性化させる。

【0079】

このように、深いp型ソースドレイン領域25bは、第2の活性領域10bに設けられたトレンチ23内に形成されたシリコン混晶層24を含むように形成される。

【0080】

次に、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bの表面に形成されている自然酸化膜(図示せず)を除去した後、例えばスパッタ法により、半導体基板10上の全面に、例えば膜厚が10nmのニッケルからなる金属膜(図示せず)を堆積する。その後、例えば窒素雰囲気中、320℃の下、1回目のRTA(Rapid Thermal Annealing)処理により、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bのSiと金属膜のNiとを反応させて、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bの上部に、ニッケルシリサイドからなる第1,第2の金属シリサイド膜26a,26bを形成する。

【0081】

その後、硫酸と過酸化水素水との混合液からなるエッチング液中に半導体基板10を浸漬することにより、素子分離領域11、第1,第2のオフセットスペーサ17a,17b及び第1,第2のサイドウォール20A,20B等の上に残存する未反応の金属膜を除去した後、1回目のRTA処理での温度よりも高い温度(例えば550℃)の下、2回目のRTA処理により、第1,第2の金属シリサイド膜26a,26bのシリサイド組成比を安定化させる。

【0082】

次に、図3(c) に示すように、例えば、第1,第2の内側サイドウォール19a,19b(シリコン酸化膜)と選択比のあるドライエッチング法を用いて、第1の外側サイドウォール20a(シリコン窒化膜)及び第2の外側サイドウォール20b(シリコン窒化膜)を除去する。

【0083】

次に、図3(d) に示すように、例えばプラズマCVD法により、半導体基板10上の全面に、例えば膜厚50nmのシリコン窒化膜からなる絶縁膜27を堆積する。

【0084】

このように、絶縁膜27は、表面に第1の保護膜16aが形成された第1のゲート電極形成部14A、及び表面に第2の保護膜16bが形成された第2のゲート電極形成部14Bを覆うように形成される。そして、絶縁膜27は、第1の外側サイドウォール20aが除去された断面形状がL字状の第1の内側サイドウォール19a、及び第2の外側サイドウォール20bが除去された断面形状がL字状の第2の内側サイドウォール19bの上に接して形成される。

【0085】

その後、例えばCVD法により、絶縁膜27上に、シリコン酸化膜からなる第1の層間絶縁膜28を堆積した後、例えばCMP(Chemical Mechanical Polishing)法により、第1の層間絶縁膜28の表面の平坦化を行いながら、第1の保護膜16a及び第2の保護膜16bの上に形成されている絶縁膜27の上面が露出するまで、第1の層間絶縁膜28を研磨除去する。

【0086】

次に、図4(a) に示すように、第1,第2のシリコン膜(ポリシリコン膜)15a,15bと選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14A、及び第2のゲート電極形成部14Bの上に形成されている第1,第2の保護膜(シリコン酸化膜)16a,16b及び絶縁膜(シリコン窒化膜)27を除去して、第1のゲート電極形成部14Aにおける第1のシリコン膜15a、及び第2のゲート電極形成部14Bにおける第2のシリコン膜15bの上面を露出する。このとき、第1のゲート電極形成部14A及び第2のゲート電極形成部14Bの側方に形成されている第1,第2のオフセットスペーサ17a,17b、第1,第2の内側サイドウォール19a,19b、絶縁膜27、及び第1の層間絶縁膜28は、その上面高さが、第1,第2のシリコン膜15a,15bの上面高さと同じ又は同程度になるまで同時に除去される。

【0087】

このように、絶縁膜27は、第1,第2のゲート電極形成部14A,14Bの側面上から第1,第2の活性領域10a,10bにおける第1,第2のゲート電極形成部14A,14Bの側方に位置する領域の上面上に跨って形成される一方、第1,第2のゲート電極形成部14A,14Bの上面上には形成されない。

【0088】

次に、図4(b) に示すように、第1,第2の金属膜(TiN膜)14a,14b、第1,第2のオフセットスペーサ17a,17b、第1,第2の内側サイドウォール19a,19b、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のシリコン膜15a、及び第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去する。

【0089】

次に、図4(c) に示すように、半導体基板10上に、n型MIS形成領域を開口しp型MIS形成領域を覆うレジストマスク29を形成した後、第1のゲート絶縁膜13a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1の金属膜14aを除去する。

【0090】

このように図4(b) 〜(c) に示す工程を順次経ることにより、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して、第1の活性領域10a上に、第1のオフセットスペーサ17a及び第1の内側サイドウォール19aを順次介して絶縁膜27に囲まれ、第1のゲート絶縁膜13aが底面に露出する第1の凹部Caを形成する。それと共に、図4(b) に示す工程を経ることにより、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して、第2の活性領域10b上に、第2のオフセットスペーサ17b及び第2の内側サイドウォール19bを順次介して絶縁膜27に囲まれ、第1の金属膜14bが底面に露出する第2の凹部Cbを形成する。

【0091】

次に、図5(a) に示すように、レジストマスク29を除去した後、半導体基板10上に、例えばCVD法、ALD法、又はスパッタ法等により、第1の凹部Ca及び第2の凹部Cb内を埋め込むように、例えば窒化タンタル(TaN)からなる第2の金属膜30を堆積する。ここで、第2の金属膜30としては、n型MISトランジスタ用に最適化された金属材料又は金属化合物材料(以下、「nMIS用金属材料」と称す)からなり、4.05eV以上で4.6eV以下の仕事関数を有することが望ましい。そして、第2の金属膜30の具体例としては、例えばTaNの他に、タンタル(Ta)若しくはハフニウム(Hf)等の金属、又はTa及びHfのうち少なくとも1種を含む窒化物、炭素窒化物若しくは珪素窒化物等が挙げられる。

【0092】

次に、図5(b) に示すように、例えばCMP法、又はエッチバック法により、絶縁膜27の上面が露出するまで、第2の金属膜30を除去する。これにより、第1の凹部Ca内における第1のゲート絶縁膜13a上に第2の金属膜30aを形成すると共に、第2の凹部Cb内における第1の金属膜14b上に第2の金属膜30bを形成する。

【0093】

このようにして、第1の活性領域10a上に、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2の活性領域10b上に、第2のゲート絶縁膜13bを介して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30Bを形成する。

【0094】

次に、図5(c) に示すように、例えばCVD法により、第1の層間絶縁膜28上に、第1,第2のゲート電極30A,30Bを覆うように、第2の層間絶縁膜31を堆積した後、例えばCMP法により、第2の層間絶縁膜31の表面の平坦化を行う。

【0095】

その後、通常のMISトランジスタを有する半導体装置の製造方法と同様に、第2の層間絶縁膜31上に、レジスト(図示せず)を形成した後、レジストをマスクにして、ドライエッチング法により、絶縁膜27、第1の層間絶縁膜28及び第2の層間絶縁膜31中に、第1,第2の金属シリサイド膜26a,26bの上面に到達する第1,第2のコンタクトホール32a,32bを形成する。このとき、絶縁膜27が露出したところで一度エッチングを止める2ステップのエッチング法を用いることにより、第1,第2の金属シリサイド膜26a,26bのオーバーエッチング量を減らすことができる。

【0096】

その後、スパッタ法又はCVD法により、第1,第2のコンタクトホール32a,32bの底部及び側壁部に、チタンと窒化チタンとが順次堆積されてなるバリアメタル膜を形成する。その後、CVD法により、第2の層間絶縁膜31上に、第1,第2のコンタクトホール32a,32b内を埋め込むように、タングステン膜を堆積した後、CMP法により、第1,第2のコンタクトホール32a,32b外に形成されているタングステン膜を除去する。このようにして、第1,第2のコンタクトホール32a,32b内に、バリアメタル膜を介してタングステン膜が埋め込まれてなる第1,第2のコンタクトプラグ33a,33bを形成する。その後、第2の層間絶縁膜31上に、第1,第2のコンタクトプラグ33a,33bと電気的に接続する金属配線(図示せず)を形成する。

【0097】

以上のようにして、本実施形態に係る半導体装置、すなわち、第2の金属膜30aからなる第1のゲート電極30Aを有するn型MISトランジスタNTrと、第1の金属膜14b及び第2の金属膜(導電膜)30bからなる第2のゲート電極30Bを有するp型MISトランジスタPTrとを備えた半導体装置を製造することができる。

【0098】

以下に、本発明の第1の実施形態に係る半導体装置の構成について、図6(a) 及び(b) を参照しながら説明する。図6(a) 及び(b) は、本発明の第1の実施形態に係る半導体装置の構成について示す図であり、具体的には、図6(a) は平面図であり、図6(b) は図6(a) に示すVIb-VIb線におけるゲート幅方向の断面図である。なお、図6(a) に示すVl-Vl線は、図5(c) 中の左図における断面線に相当する一方、図6(a) に示すVr-Vr線は、図5(c) 中の右図における断面線に相当する。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0099】

図6(a) に示すように、n型MIS形成領域には、素子分離領域に囲まれた第1の活性領域10aが形成され、p型MIS形成領域には、素子分離領域に囲まれた第2の活性領域10bが形成されている。第1の活性領域10a上には、第1のゲート絶縁膜を介して、第1のゲート電極30Aが形成されていると共に、第2の活性領域10b上には、第2のゲート絶縁膜を介して、第2のゲート電極30Bが形成されている。第1,第2のゲート電極30A,30Bの側面上には、第1,第2のオフセットスペーサ17a,17b及び第1,第2の内側サイドウォール19a,19bを順次介して、絶縁膜27が形成されている。なお、図6(a) においては、第1の層間絶縁膜(図5(c):28参照)、及び第2の層間絶縁膜(図5(c):31参照)の図示を省略しているが、第1の層間絶縁膜は、絶縁膜27上に形成されている。また、第2の層間絶縁膜は、第1,第2のゲート電極30A,30Bを覆うように、第1の層間絶縁膜上に形成されている。

【0100】

図6(b) に示すように、半導体基板10の上部には、n型MIS形成領域とp型MIS形成領域とを区画するように、トレンチ内に絶縁膜が埋め込まれた素子分離領域11が形成されている。半導体基板10におけるn型MIS形成領域には、p型ウェル領域12aが形成されている一方、半導体基板10におけるp型MIS形成領域には、n型ウェル領域12bが形成されている。第1の活性領域10a上には、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aが形成されている一方、第2の活性領域10b上には、第2のゲート絶縁膜13bを介して、第1の金属膜14bと第1の金属膜14b上に形成された第2の金属膜(導電膜)30bとからなる第2のゲート電極30Bが形成されている。半導体基板10上には、第1,第2のゲート電極30A,30Bを覆うように第2の層間絶縁膜31が形成されている。

【0101】

ここで、n型MISトランジスタ及びp型MISトランジスタの構成について、図5(c) を参照しながら詳細に説明する。

【0102】

n型MISトランジスタNTrは、図5(c) に示すように、半導体基板10における素子分離領域11に囲まれた第1の活性領域10aと、第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極30Aの側面上に第1のオフセットスペーサ17aを介して形成され断面形状がL字状の第1の内側サイドウォール19aと、第1の活性領域10aにおける第1のゲート電極30Aの側方下に形成された浅いn型ソースドレイン領域18aと、第1の活性領域10aにおける第1の内側サイドウォール19aの外側方下に形成された深いn型ソースドレイン領域25aと、第1のゲート電極30Aの側面上から第1の活性領域10aにおける第1のゲート電極30Aの側方に位置する領域の上面上に跨って形成された絶縁膜27と、深いn型ソースドレイン領域25aの上部に形成された第1の金属シリサイド膜26aとを備えている。

【0103】

p型MISトランジスタPTrは、図5(c) に示すように、半導体基板10における素子分離領域11に囲まれた第2の活性領域10bと、第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され第1の金属膜14b及び第2の金属膜(導電膜)30bからなる第2のゲート電極30Bと、第2のゲート電極30Bの側面上に第2のオフセットスペーサ17bを介して形成され断面形状がL字状の第2の内側サイドウォール19bと、第2の活性領域10bにおける第1のゲート電極30Bの側方下に形成された浅いp型ソースドレイン領域18bと、第2の活性領域10bにおける第2の内側サイドウォール19bの外側方下に形成されシリコン混晶層24を含む深いp型ソースドレイン領域25bと、第2のゲート電極30Bの側面上から第2の活性領域10bにおける第2のゲート電極30Bの側方に位置する領域の上面上に跨って形成された絶縁膜27と、深いp型ソースドレイン領域25bの上部に形成された第2の金属シリサイド膜26bとを備えている。

【0104】

第1のゲート電極30Aを構成する第2の金属膜30aは、4.05eV以上で4.6eV以下の仕事関数を有する金属材料(又は金属化合物材料)からなる一方、第2のゲート電極30Bを構成する第1の金属膜14bは、4.6eV以上で5.15eV以下の仕事関数を有する金属材料(又は金属化合物材料)からなる。このように、第2の金属膜30aと第1の金属膜14bとは、互いに異なる仕事関数を有し、互いに異なる金属材料(又は金属化合物材料)からなる。

【0105】

また、第1のゲート電極30Aと第2のゲート電極30Bとは、その上面高さが互いに同じであり、第1のゲート電極30Aは、第2の金属膜30aからなる一方、第2のゲート電極30Bは、第1の金属膜14b及び第2の金属膜30bからなる。そのため、第2の金属膜30aの膜厚は、第1の金属膜14bの膜厚及び第2の金属膜(導電膜)30bの膜厚に比べて厚い。

【0106】

絶縁膜27は、第1,第2のゲート電極30A,30Bの側面上から第1,第2の活性領域10a,10bにおける第1,第2のゲート電極30A,30Bの側方に位置する領域の上面上に跨って形成されている一方、第1,第2のゲート電極30A,30Bの上面上には形成されていない。そして、絶縁膜27の膜厚は、第1,第2のゲート電極30A,30Bの膜厚に比べて薄い。

【0107】

第1のゲート絶縁膜13aと第2のゲート絶縁膜13bとは、互いに同一の工程において形成され、互いに同じ絶縁材料からなる。

【0108】

本実施形態によると、互いに同一の工程において、第1,第2のゲート電極形成部14A,14B(図1(c) 参照)を形成した後、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して形成された第1の凹部Ca(図4(c) 参照)内に、第2の金属膜30aを形成して、第2の金属膜30aからなる第1のゲート電極30A(図5(b) 参照)を形成する。一方、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して形成された第2の凹部Cb(図4(b) 参照)内に、第2の金属膜30bを形成して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30B(図5(b) 参照)を形成する。そのため、第1のゲート電極形成部14Aにおける第1の金属膜14aの除去の際には、図4(c) に示すように、n型MIS形成領域及びp型MIS形成領域の一方を開口し他方を覆うレジストマスク29を形成するため、素子分離領域11に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部14A,14Bの形成の際には、素子分離領域11に合わせマージンは必要とされない。従って、素子分離領域11に合わせマージンが必要とされる工程(以下、「合わせマージン必要工程」と称す)数を1回に抑えることができるので、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域11のゲート幅方向の幅(図6(b):Wnp参照)を縮小化することができるので、半導体装置の微細化を図ることができる。

【0109】

これに対し、第2の従来の半導体装置の製造方法では、図14(a) に示す工程において、レジストマスク206の形成の際に素子分離領域201に合わせマージンが必要とされると共に、図14(b) に示す工程において、レジストマスク210の形成の際に素子分離領域201に合わせマージンが必要とされるため、2回の合わせマージン必要工程があるので、既述の通り、素子分離領域201のゲート幅方向の幅を縮小化することができない。

【0110】

加えて、図1(c) に示すように、互いに同一の工程において、互いに同一のシリコン膜15、同一の第1の金属膜14、及び同一のゲート絶縁膜形成膜13が順次パターニングされて、第1,第2のゲート電極形成部14A,14Bが形成されるため、第1,第2のゲート電極形成部14A,14Bを容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部14Aにおける第1の金属膜14a及び第1のシリコン膜15aを、第2の金属膜30aと置換して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、精度良く形成された第2のゲート電極形成部14Bにおける第2のシリコン膜15bを、第2の金属膜30bと置換して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30Bを形成することができるため、精度良く形成された第1,第2のゲート電極30A,30Bを実現することができる。

【0111】

これに対し、第1の従来の半導体装置の製造方法では、図13に示すように、第1のパターニング部107Aと第2のパターニング部107Bとが、互いに構成が異なるにも拘わらず、互いに同一の工程において、パターニングされるため、既述の通り、第1,第2のゲート電極の双方を精度良く形成することができない。一方、第2の従来の半導体装置の製造方法においても、図14(d) に示すように、第1のパターニング部と第2のパターニング部とが、互いに構成が異なるにも拘わらず、互いに同一の工程において、パターニングされるため、既述の通り、第1,第2のゲート電極の双方を精度良く形成することができない。

【0112】

さらに、深いp型ソースドレイン領域25bが、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を生じさせるシリコン混晶層24を含むことにより、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を印加することができるので、p型MISトランジスタの駆動能力を向上させることができる。

【0113】

なお、第1の実施形態では、p型MISトランジスタの駆動能力を向上させることを目的に、第1,第2のサイドウォール20A,20Bの形成(図2(a) 参照)後で、深いn型,p型ソースドレイン領域25a,25bの形成(図3(b) 参照)前に、図2(b) 〜図3(a) に示す工程を順次行い、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に形成されたトレンチ23内に、例えばp型SiGe層からなるシリコン混晶層24を形成する場合を具体例に挙げて説明したが、本発明はこれに限定されるものではない。

【0114】

例えば、図2(a) に示すように、第1,第2のサイドウォール20A,20Bを形成した後、図2(b) 〜図3(a) に示す工程を順次行うことなく、すなわち、シリコン混晶層24を形成することなく、図3(b) に示すように、深いn型,p型ソースドレイン領域25a,25bを形成してもよい。

【0115】

また例えば、第1,第2のサイドウォール20A,20Bの形成(図2(a) 参照)後で、深いn型,p型ソースドレイン領域25a,25bの形成(図3(b) 参照)前に、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に形成されたトレンチ内に、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を生じさせるシリコン混晶層(例えばn型SiC層)を形成してもよい。この場合、p型MISトランジスタではなく、n型MISトランジスタの駆動能力を向上させることができる。

【0116】

(第2の実施形態)

本発明の第2の実施形態に係る半導体装置及びその製造方法について図面を参照しながら説明する。なお、第2の実施形態に係る半導体装置及びその製造方法について、前述の第1の実施形態に係る半導体装置及びその製造方法と相違する点を中心に説明し、共通する点については適宜省略して説明する。

【0117】

以下に、本発明の第2の実施形態に係る半導体装置の製造方法について、図7(a) 〜(c) 及び図8(a) 〜(c) を参照しながら説明する。図7(a) 〜図8(c) は、本発明の第2の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図7(a) 〜図8(c) において、前述の第1の実施形態における構成要素と同一の構成要素には、第1の実施形態における図1(a) 〜図5(c) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0118】

まず、第1の実施形態における図1(a) 〜図4(a) に示す工程を順次行い、図7(a) に示す構成(すなわち、図4(a) に示す構成と同一の構成)を得る。

【0119】

次に、図7(b) に示すように、半導体基板10上に、n型MIS形成領域を開口しp型MIS形成領域を覆うレジストマスク29を形成した後、第1の金属膜14a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のシリコン膜15aを除去する。その後、第1のゲート絶縁膜13a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1の金属膜14aを除去する。

【0120】

このようにして、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して、第1の活性領域10a上に、第1のオフセットスペーサ17a及び第1の内側サイドウォール19aを順次介して絶縁膜27に囲まれ、第1のゲート絶縁膜13aが底面に露出する第1の凹部Caを形成する。

【0121】

次に、図7(c) に示すように、レジストマスク29を除去した後、半導体基板10上に、例えばCVD法、ALD法、又はスパッタ法等により、第1の凹部Ca内を埋め込むように、例えばTaNからなる第2の金属膜30を堆積する。

【0122】

次に、図8(a) に示すように、例えばCMP法、又はエッチバック法により、絶縁膜27の上面が露出するまで、第2の金属膜30を除去する。これにより、第1の凹部Ca内における第1のゲート絶縁膜13a上に第2の金属膜30aを形成する。

【0123】

このようにして、第1の活性領域10a上に、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2の活性領域10b上に、第2のゲート絶縁膜13bを介して、第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。

【0124】

次に、図8(b) に示すように、第2のシリコン膜15bの表面に形成されている自然酸化膜(図示せず)を除去した後、例えばスパッタ法により、半導体基板10上の全面に、例えば膜厚が10nmのニッケルからなる金属膜(図示せず)を堆積する。その後、例えば窒素雰囲気中、320℃の下、1回目のRTA処理により、第2のシリコン膜15bのSiと金属膜のNiとを反応させて、第2のシリコン膜15bの上部に、ニッケルシリサイドからなる金属シリサイド膜34を形成する。

【0125】

その後、硫酸と過酸化水素水との混合液からなるエッチング液中に半導体基板10を浸漬することにより、第1の層間絶縁膜28、絶縁膜27、第1,第2の内側サイドウォール19a,19b、及び第1,第2のオフセットスペーサ17a,17b等の上に残存する未反応の金属膜を除去した後、1回目のRTA処理での温度よりも高い温度(例えば550℃)の下、2回目のRTA処理により、金属シリサイド膜34のシリサイド組成比を安定化させる。

【0126】

次に、図8(c) に示すように、例えばCVD法により、第1の層間絶縁膜28上に、第1,第2のゲート電極30A,30Bを覆うように、第2の層間絶縁膜31を堆積した後、例えばCMP法により、第2の層間絶縁膜31の表面の平坦化を行う。その後、通常のMISトランジスタを有する半導体装置の製造方法と同様に、絶縁膜27、第1の層間絶縁膜28、及び第2の層間絶縁膜31中の第1,第2のコンタクトホール32a,32b内に形成され、第1,第2の金属シリサイド膜26a,26bと接続する第1,第2のコンタクトプラグ33a,33bを形成する。その後、第2の層間絶縁膜31上に、第1,第2のコンタクトプラグ33a,33bと電気的に接続する金属配線(図示せず)を形成する。

【0127】

以上のようにして、本実施形態に係る半導体装置、すなわち、第2の金属膜30aからなる第1のゲート電極30Aを有するn型MISトランジスタNTrと、第1の金属膜14b及び第2のシリコン膜(導電膜)15bからなる第2のゲート電極30Bを有するp型MISトランジスタPTrとを備えた半導体装置を製造することができる。

【0128】

ここで、本実施形態と第1の実施形態との製造方法上の相違点は、以下に示す点である。

【0129】

第1の実施形態では、図4(b) に示すように、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して形成された第2の凹部Cb内に、第2の金属膜30bを形成して、第2のゲート電極形成部14Bにおける第1の金属膜14b、及び第2の金属膜30bからなる第2のゲート電極30Bを形成する。

【0130】

これに対し、本実施形態では、第1の実施形態における図4(b) に示すように第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去せずに、第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。そして、第2のゲート電極30Bの形成後に、図8(b) に示すように、第2のゲート電極30Bにおける第2のシリコン膜15b上に金属シリサイド膜34を形成する。

【0131】

以下に、本発明の第2の実施形態に係る半導体装置の構成について、図9を参照しながら説明する。図9は、本発明の第2の実施形態に係る半導体装置の構成について示すゲート幅方向の断面図である。なお、図9において、第1の実施形態における構成要素と同一の構成要素には、第1の実施形態における図6(b) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0132】

図9に示すように、第1の活性領域10a上には、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aが形成されている一方、第2の活性領域10b上には、第2のゲート絶縁膜13bを介して、第1の金属膜14bと第1の金属膜14b上に形成された第2のシリコン膜(導電膜)15bとからなる第2のゲート電極30Bが形成されている。第2のシリコン膜15b上には、金属シリサイド膜34が形成されている。

【0133】

ここで、本実施形態と第1の実施形態との構造上の相違点は、以下に示す点である。

【0134】

本実施形態では、第2のゲート電極30Bは、第1の金属膜14bと第2のシリコン膜15bとからなる。そして、第2のシリコン膜15b上には、金属シリサイド膜34が形成されている。これに対し、第1の実施形態では、第2のゲート電極30Bは、第1の金属膜14bと第2の金属膜30bとからなる。

【0135】

このように、第2のゲート電極30Bにおける第1の金属膜14b上に形成された導電膜が、本実施形態では第2のシリコン膜15bであるのに対し、第1の実施形態では第2の金属膜30bである。

【0136】

本実施形態によると、互いに同一の工程において、第1,第2のゲート電極形成部14A,14B(図1(c) 参照)を形成した後、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して形成された第1の凹部Ca(図7(b) 参照)内に、第2の金属膜30aを形成して、第2の金属膜30aからなる第1のゲート電極30A(図8(a) 参照)を形成する。一方、第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。そのため、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aの除去の際には、図7(b) に示すように、n型MIS形成領域及びp型MIS形成領域の一方を開口し他方を覆うレジストマスク29を形成するため、素子分離領域11に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部14A,14Bの形成の際には、素子分離領域11に合わせマージンは必要とされない。従って、合わせマージン必要工程数を1回に抑えることができるため、素子分離領域11のゲート幅方向の幅(図9:Wnp参照)を縮小化することができるので、半導体装置の微細化を図ることができる。

【0137】

加えて、図1(c) に示すように、互いに同一の工程において、互いに同一のシリコン膜15、同一の第1の金属膜14、及び同一のゲート絶縁膜形成膜13が順次パターニングされて、第1,第2のゲート電極形成部14A,14Bが形成されるため、第1,第2のゲート電極形成部14A,14Bを容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部14Aにおける第1の金属膜14a及び第1のシリコン膜15aを、第2の金属膜30aと置換して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、精度良く形成された第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成することができるため、精度良く形成された第1,第2のゲート電極30A,30Bを実現することができる。

【0138】

さらに、第1の実施形態と同様に、深いp型ソースドレイン領域25bがシリコン混晶層24を含むことにより、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を印加することができるので、p型MISトランジスタの駆動能力を向上させることができる。

【0139】

(第2の実施形態の変形例)

以下に、本発明の第2の実施形態の変形例に係る半導体装置及びその製造方法について図面を参照しながら説明する。なお、第2の実施形態の変形例に係る半導体装置及びその製造方法について、前述の第2の実施形態に係る半導体装置及びその製造方法と相違する点を中心に説明し、共通する点については適宜省略して説明する。

【0140】

以下に、本発明の第2の実施形態の変形例に係る半導体装置の製造方法について、図10(a) 〜(c) 及び図11(a) 〜(c) を参照しながら説明する。図10(a) 〜図11(c) は、本発明の第2の実施形態の変形例に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図10(a) 〜図11(c) において、前述の第2の実施形態における構成要素と同一の構成要素には、第2の実施形態における図7(a) 〜図8(c) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0141】

まず、第1の実施形態における図1(a) 〜図4(a) に示す工程を順次行い、第2の実施形態と同様に、図7(a) に示す構成を得る。但し、本変形例におけるゲート絶縁膜形成膜13としては、p型MISトランジスタ用に最適化された膜厚を有し、p型MISトランジスタ用に最適化された絶縁材料からなることが望ましい。

【0142】

次に、図10(a) に示すように、半導体基板10上に、n型MIS形成領域を開口しp型MIS形成領域を覆うレジストマスク29を形成した後、第1の金属膜14a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のシリコン膜15aを除去する。その後、第1のゲート絶縁膜13a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1の金属膜14aを除去する。このように、第2の実施形態における図7(b) に示す工程と同様の工程を行う。

【0143】

その後、半導体基板と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のゲート絶縁膜13aを除去する。

【0144】

このようにして、第1のゲート電極形成部14Aにおける第1のシリコン膜15a、第1の金属膜14a、及び第1のゲート絶縁膜13aを順次除去して、第1の活性領域10a上に、第1のオフセットスペーサ17a及び第1の内側サイドウォール19aを順次介して絶縁膜27に囲まれ、第1の活性領域10aが底面に露出する第1の凹部Caを形成する。

【0145】

次に、図10(b) に示すように、レジストマスク29を除去した後、例えばHPM(Hydrochloric Acid/Hydrogen Peroxide/Water Mixture)処理により、半導体基板10の表面にケミカル酸化膜(図示せず)を形成した後、例えばMOCVD法により、半導体基板10上に、第1の凹部Ca内を覆うように、例えば膜厚が2nmの高誘電率膜からなるゲート絶縁膜形成膜35を堆積する。ここで、ゲート絶縁膜形成膜35としては、比誘電率が10以上の金属酸化物からなる高誘電率膜を含むことが望ましい。さらに、ゲート絶縁膜形成膜35としては、n型MISトランジスタ用に最適化された膜厚を有し、n型MISトランジスタ用に最適化された絶縁材料からなることが望ましい。

【0146】

その後、半導体基板10上に、例えばCVD法、ALD法、又はスパッタ法等により、ゲート絶縁膜形成膜35を介して第1の凹部Ca内を埋め込むように、例えばTaNからなる第2の金属膜30を堆積する。

【0147】

次に、図10(c) に示すように、例えばCMP法、又はエッチバック法により、絶縁膜27の上面が露出するまで、第2の金属膜30及びゲート絶縁膜形成膜35を除去する。これにより、第1の凹部Ca内に第3のゲート絶縁膜35aを形成すると共に、第3のゲート絶縁膜35a上に第2の金属膜30aを形成する。ここで、第3のゲート絶縁膜35aは、第1の凹部Ca内における第1の活性領域10a上から第2の金属膜30aの側面上に亘って形成される。そのため、図10(c) に示す図は、ゲート長方向の断面図であるため図示されないが、第3のゲート絶縁膜35aは、ゲート幅方向に沿って互いに隣り合う第2の金属膜30aと第1の金属膜14b及び第2のシリコン膜15bとの間に介在するように形成される。

【0148】

次に、図11(a) に示すように、第2の金属膜30aと選択比のあるエッチング法、又は例えば希釈フッ酸処理により、第3のゲート絶縁膜35aの上部を除去して、第3のゲート絶縁膜35aの上端高さを、第2の金属膜30aの上面高さよりも低くして、溝Rを形成する。ここで、溝Rは、第2の金属膜30aの周縁に沿って、第2の金属膜30aの側面を露出するように形成される。そのため、図11(a) に示す図は、ゲート長方向の断面図であるため図示されないが、溝Rは、ゲート幅方向に沿って互いに隣り合う第2の金属膜30aと第2のシリコン膜15bとの間に形成され、溝R内に、第2の金属膜30aのゲート幅方向の側面と、第2のシリコン膜15bのゲート幅方向の側面とが露出される。

【0149】

このように図10(b) 〜図11(a) に示す工程を順次経ることにより、第1の凹部Ca内に第3のゲート絶縁膜35aを形成すると共に、第3のゲート絶縁膜35a上に、溝R内に側面が露出する第2の金属膜30aを形成する。

【0150】

このようにして、第1の活性領域10a上に、第3のゲート絶縁膜35aを介して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2の活性領域10b上に、第2のゲート絶縁膜13bを介して、第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。

【0151】

次に、図11(b) に示すように、第2のシリコン膜15bの表面に形成されている自然酸化膜(図示せず)を除去した後、例えばスパッタ法により、半導体基板10上の全面に、例えば膜厚が10nmのニッケルからなる金属膜(図示せず)を堆積する。その後、例えば窒素雰囲気中、320℃の下、1回目のRTA処理により、第2のシリコン膜15bのSiと金属膜のNiとを反応させて、第2のシリコン膜15bの上部に、ニッケルシリサイドからなる金属シリサイド膜34を形成する。このとき、本変形例における金属シリサイド膜34は、その体積膨張により、第2の金属膜30aと第2のシリコン膜15bとの間に形成された溝R内にも形成される。すなわち、溝R内に露出する第2の金属膜30aのゲート幅方向の側面及び第2のシリコン膜15bのゲート幅方向の側面の上に接して形成される(後述の図12:34参照)。そのため、金属シリサイド膜34により、第2の金属膜30aと第2のシリコン膜15bとを電気的に接続することができる。

【0152】

その後、硫酸と過酸化水素水との混合液からなるエッチング液中に半導体基板10を浸漬することにより、第1の層間絶縁膜28、絶縁膜27、第1,第2の内側サイドウォール19a,19b、及び第1,第2のオフセットスペーサ17a,17b等の上に残存する未反応の金属膜を除去した後、1回目のRTA処理での温度よりも高い温度(例えば550℃)の下、2回目のRTA処理により、金属シリサイド膜34のシリサイド組成比を安定化させる。

【0153】

次に、図11(c) に示すように、例えばCVD法により、第1の層間絶縁膜28上に、第1,第2のゲート電極30A,30Bを覆うように、第2の層間絶縁膜31を堆積した後、例えばCMP法により、第2の層間絶縁膜31の表面の平坦化を行う。その後、通常のMISトランジスタを有する半導体装置の製造方法と同様に、絶縁膜27、第1の層間絶縁膜28、及び第2の層間絶縁膜31中の第1,第2のコンタクトホール32a,32b内に形成され、第1,第2の金属シリサイド膜26a,26bと接続する第1,第2のコンタクトプラグ33a,33bを形成する。その後、第2の層間絶縁膜31上に、第1,第2のコンタクトプラグ33a,33bと電気的に接続する金属配線(図示せず)を形成する。このように、第2の実施形態における図8(c) に示す工程と同様の工程を行う。

【0154】

以上のようにして、本実施形態に係る半導体装置、すなわち、第2の金属膜30aからなる第1のゲート電極30Aを有するn型MISトランジスタNTrと、第1の金属膜14b及び第2のシリコン膜(導電膜)15bからなる第2のゲート電極30Bを有するp型MISトランジスタPTrとを備えた半導体装置を製造することができる。

【0155】

ここで、本変形例と第2の実施形態との製造方法上の相違点は、以下に示す点である。

【0156】

第2の実施形態では、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを除去して形成された第1の凹部Ca(図7(b) 参照)内における第1のゲート絶縁膜13a上に、第2の金属膜30aを形成する。

【0157】

これに対し、本変形例では、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aに加えて第1のゲート絶縁膜13aを除去して形成された第1の凹部Ca(図10(a) 参照)内に第3のゲート絶縁膜35aを形成すると共に、第3のゲート絶縁膜35a上に第2の金属膜30aを形成する。

【0158】

そして、本変形例では、第1のゲート電極形成部14Aにおける第1のゲート絶縁膜13aを、第3のゲート絶縁膜35aと置換したことに伴い、ゲート幅方向に沿って互いに隣り合う第1のゲート電極30Aと第2のゲート電極30Bとの間に、第3のゲート絶縁膜35aが介在する。そのため、本変形例では、金属シリサイド膜34(図11(b) 参照)の形成の際に、第1のゲート電極30Aと第2のゲート電極30Bとの電気的接続を図ることを目的に、図11(a) に示すように、第3のゲート絶縁膜35aの上部を除去し溝Rを形成して、溝R内に、第2の金属膜30aのゲート幅方向の側面及び第2のシリコン膜15bのゲート幅方向の側面を露出させる。これにより、図11(b) に示す図は、ゲート長方向の断面図であるため図示されないが、金属シリサイド膜34を、後述の図12に示すように、溝R内に露出する第2の金属膜30aのゲート幅方向の側面及び第2のシリコン膜15bのゲート幅方向の側面の上に接して形成することができるので、第2の金属膜30aと第2のシリコン膜15bとを電気的に接続させて、第1のゲート電極30Aと第2のゲート電極30Bとの電気的接続を図ることができる。

【0159】

以下に、本発明の第2の実施形態の変形例に係る半導体装置の構成について、図12を参照しながら説明する。図12は、本発明の第2の実施形態の変形例に係る半導体装置の構成について示すゲート幅方向の断面図である。なお、図12において、第2の実施形態における構成要素と同一の構成要素には、第2の実施形態における図9に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0160】

図12に示すように、第1の活性領域10a上には、第3のゲート絶縁膜35aを介して、第2の金属膜30aからなる第1のゲート電極30Aが形成されている一方、第2の活性領域10b上には、第2のゲート絶縁膜13bを介して、第1の金属膜14bと第1の金属膜14b上に形成された第2のシリコン膜(導電膜)15bとからなる第2のゲート電極30Bが形成されている。第2のシリコン膜15b上には、金属シリサイド膜34が形成されている。

【0161】

ここで、本変形例と第2の実施形態との構造上の相違点は、以下に示す点である。

【0162】

本変形例では、第3のゲート絶縁膜35aは、第2のゲート絶縁膜13bと異なる絶縁材料からなる。そして、第3のゲート絶縁膜35aは、図12に示すように、第1の活性領域10a上から第2の金属膜30aのゲート幅方向の側面上に亘って形成され、第1のゲート電極30Aの下部領域と第2のゲート電極30Bの下部領域との間に介在している(なお、第3のゲート絶縁膜35aは、図11(c) に示すように、第2の金属膜30aのゲート幅方向の側面上だけでなくゲート長方向の側面上にも形成されている)。また、金属シリサイド膜34は、溝R内に露出する第2の金属膜30aのゲート幅方向の側面及び第2のシリコン膜15bのゲート幅方向の側面の上に接して形成されている。そして、金属シリサイド膜34により、第1のゲート電極30Aと第2のゲート電極30Bとが電気的に接続している。

【0163】

これに対し、第2の実施形態では、第1のゲート絶縁膜13aは、第2のゲート絶縁膜13bと同じ絶縁材料からなる。そして、第1のゲート絶縁膜13aは、第1のゲート電極30Aと第2のゲート電極30Bとの間に介在していない。

【0164】

このように、n型MIS形成領域のゲート絶縁膜とp型MIS形成領域のゲート絶縁膜とが、本変形例では互いに異なる絶縁材料からなるのに対し、第2の実施形態では互いに同じ絶縁材料からなる。

【0165】

本変形例によると、第2の実施形態と同様の効果を得ることができる。

【0166】

加えて、第3のゲート絶縁膜35aは、n型MISトランジスタ用に最適化された膜厚を有し、n型MISトランジスタ用に最適化された絶縁材料(以下、「nMIS用絶縁材料」と称す)からなると共に、第2のゲート絶縁膜13bは、p型MISトランジスタ用に最適化された膜厚を有し、p型MISトランジスタ用に最適化された絶縁材料(以下、「pMIS用絶縁材料」と称す)からなるため、トランジスタ設計の自由度が増し、所望のトランジスタ特性を実現することができる。

【0167】

なお、第1,第2の実施形態では、第1の金属膜14としてpMIS用金属材料からなるpMIS用金属膜を用いると共に第2の金属膜30としてnMIS用金属材料からなるnMIS用金属膜を用いて、第1のゲート電極形成部14Aにおける第1の金属膜(pMIS用金属膜)14a及び第1のシリコン膜15aを、第2の金属膜(nMIS用金属膜)30aと置換して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2のゲート電極形成部14Bにおける第1の金属膜(pMIS用金属膜)14bを含む第2のゲート電極30Bを形成する場合を具体例に挙げて説明したが、本発明はこれに限定されるものではない。

【0168】

その反対に、第1の金属膜14としてnMIS用金属膜を用いると共に第2の金属膜30としてpMIS用金属膜を用いてもよい。但し、この場合、第2のゲート電極形成部における第1の金属膜(nMIS用金属膜)及び第2のシリコン膜を、第2の金属膜(pMIS用金属膜)と置換して、第2の金属膜からなる第2のゲート電極を形成する一方、第1のゲート電極形成部における第1の金属膜(nMIS用金属膜)を含む第1のゲート電極を形成する。

【0169】

また、第2の実施形態の変形例においても、第1の金属膜14としてnMIS用金属膜を用いると共に第2の金属膜30としてpMIS用金属膜を用いてもよい。但し、この場合、ゲート絶縁膜形成膜13としてnMIS用絶縁材料からなるnMIS用絶縁膜を用いると共に、ゲート絶縁膜形成膜35としてpMIS用絶縁材料からなるpMIS用絶縁膜を用いる。

【0170】

なお、第1, 第2の実施形態及びその変形例では、図3(c) に示すように、第1,第2の外側サイドウォール20a,20bの除去後、図3(d) に示すように、絶縁膜27として、例えばプラズマCVD法により、シリコン窒化膜からなる下地絶縁膜を形成する場合を具体例に挙げて説明したが、本発明はこれに限定されるものではない。例えば、第1,第2の外側サイドウォール20a,20bの除去後、絶縁膜27として、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を生じさせる応力絶縁膜を形成してもよい。ここで、応力絶縁膜の形成方法の具体例としては、例えばプラズマCVD法により、水素を多量に含むシリコン窒化膜を堆積した後、紫外線照射により、シリコン窒化膜に含まれる水素を飛ばして、シリコン窒化膜からなる応力絶縁膜を形成する方法が挙げられる。

【0171】

このようにすると、応力絶縁膜により、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を印加して、n型MISトランジスタの駆動能力を向上させることができる。そのため、第1,第2の実施形態及びその変形例のようにシリコン混晶層24によりp型MISトランジスタの駆動能力を向上させるのに加えて、応力絶縁膜によりn型MISトランジスタの駆動能力を向上させることができる。

【0172】

加えて、第1,第2の外側サイドウォール20a,20bの除去後に応力絶縁膜が形成されるため、第1,第2の外側サイドウォール20a,20bの除去分だけ、応力絶縁膜を厚く形成することができるため、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を効果的に印加することができる。

【0173】

さらに、第1,第2の外側サイドウォール20a,20bの除去分だけ、応力絶縁膜を、第1の活性領域10aにおけるチャネル領域に近付けて形成することができるので、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力をより一層効果的に印加することができる。

【0174】

このように、絶縁膜27として、下地絶縁膜ではなく応力絶縁膜を用いた場合、応力絶縁膜の形成前に、第1,第2の外側サイドウォール20a,20bを予め除去することにより、応力絶縁膜による引っ張り応力を、第1の活性領域10aにおけるチャネル領域のゲート長方向に効果的に印加することができる。

【0175】

一方、絶縁膜27として、第1,第2の実施形態及びその変形例のように下地絶縁膜を用いた場合、絶縁膜27の形成前に、図3(c) に示すように、第1,第2の外側サイドウォール20a,20bを除去する必要は必ずしもない。

【0176】

なお、第1,第2の実施形態及びその変形例では、シリコン混晶層24により、p型MISトランジスタの駆動能力を向上させる場合を具体例に挙げて説明したが、本発明はこれに限定されるものではなく、n型MISトランジスタの駆動能力及びp型MISトランジスタの駆動能力の双方を向上させてもよい。第1に例えば、第1,第2の実施形態及びその変形例のようにシリコン混晶層24を設ける一方、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に形成されたトレンチ内に、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を生じさせるシリコン混晶層を設けてもよい。第2に例えば、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に形成されたトレンチ内に、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を生じさせるシリコン混晶層を設ける一方、絶縁膜27として、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を生じさせる応力絶縁膜を設けてもよい。

【0177】

なお、第1,第2の実施形態におけるゲート絶縁膜形成膜13、又は、第2の実施形態の変形例におけるゲート絶縁膜形成膜13及びゲート絶縁膜形成膜35の具体例としては、例えば酸化ハフニウム(HfO2)、ハフニウムシリケート(HfSiO)、及び窒化ハフニウムシリケート(HfSiON)等のハフニウム系酸化物、並びにタンタル(Ta)、ジルコニウム(Zr)、チタン(Ti)、アルミニウム(Al)、スカンジウム(Sc)、イットリウム(Y)、又はランタン(La)等を含む酸化物が挙げられる。第1,第2の実施形態におけるゲート絶縁膜形成膜13として、これらの絶縁材料の中からn型MISトランジスタ及びp型MISトランジスタの双方に適した絶縁材料を使用する。また、第2の実施形態の変形例におけるゲート絶縁膜形成膜13及びゲート絶縁膜形成膜35として、p型MISトランジスタに最適化した絶縁材料及びn型MISトランジスタに最適化した絶縁材料をそれぞれ使用する。このとき、n型MISトランジスタ用のゲート絶縁膜形成膜35とp型MISトランジスタ用のゲート絶縁膜形成膜13とで、異なる絶縁材料を使用しても良いし、同じ絶縁材料でもそれぞれの膜厚又は組成(濃度)を変えて最適化して使用しても良い。

【0178】

また、第1, 第2の実施形態及びその変形例では、シリコン膜15として、ポリシリコン膜を用いたが、これに代えて、例えばアモルファスシリコン膜又はシリコン膜等を含む他の半導体材料からなるシリコン膜を用いてもよい。

【0179】

また、第1, 第2の実施形態及びその変形例では、第1,第2の金属シリサイド膜26a,26bの形成の際に、深いn型,p型ソースドレイン領域25a,25bの上部と反応させる金属膜として、ニッケルからなる金属膜を用いたが、これに代えて、例えば白金、コバルト、チタン、及びタングステン等のシリサイド化用金属からなる金属膜を用いてもよい。

【産業上の利用可能性】

【0180】

本発明は、精度良く形成されたn型,p型MISトランジスタのゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現することができるので、デュアルメタルゲート構造の半導体装置及びその製造方法に有用である。

【図面の簡単な説明】

【0181】

【図1】(a) 〜(d) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図2】(a) 〜(d) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図3】(a) 〜(d) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図4】(a) 〜(c) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図5】(a) 〜(c) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図6】(a) 及び(b) は、本発明の第1の実施形態に係る半導体装置の構成について示す図である。

【図7】(a) 〜(c) は、本発明の第2の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図8】(a) 〜(c) は、本発明の第2の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図9】本発明の第2の実施形態に係る半導体装置の構成について示すゲート幅方向の断面図である。

【図10】(a) 〜(c) は、本発明の第2の実施形態の変形例に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図11】(a) 〜(c) は、本発明の第2の実施形態の変形例に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。

【図12】本発明の第2の実施形態の変形例に係る半導体装置の構成について示すゲート幅方向の断面図である。

【図13】第1の従来の半導体装置の製造方法を示すゲート幅方向の要部工程断面図である。

【図14】(a) 〜(e) は、第2の従来の半導体装置の製造方法を工程順に示すゲート幅方向の要部工程断面図である。

【図15】第2の従来の半導体装置の製造方法における問題点について示す平面図である。

【図16】第2の従来の半導体装置の製造方法における問題点について示すゲート幅方向の断面図である。

【符号の説明】

【0182】

10 半導体基板

10a 第1の活性領域

10b 第2の活性領域

11 素子分離領域

12a p型ウェル領域

12b n型ウェル領域

13 ゲート絶縁膜形成膜

13a 第1のゲート絶縁膜

13b 第2のゲート絶縁膜

14,14a,14b 第1の金属膜

15 シリコン膜

15a 第1のシリコン膜

15b 第2のシリコン膜

16 保護膜

16a 第1の保護膜

16b 第2の保護膜

17a 第1のオフセットスペーサ

17b 第2のオフセットスペーサ

18a 浅いn型ソースドレイン領域

18b 浅いp型ソースドレイン領域

19a 第1の内側サイドウォール

19b 第2の内側サイドウォール

20a 第1の外側サイドウォール

20b 第2の外側サイドウォール

20A 第1のサイドウォール

20B 第2のサイドウォール

21,21a 表面保護膜

22 レジストマスク

23 トレンチ

24 シリコン混晶層

25a 深いn型ソースドレイン領域

25b 深いp型ソースドレイン領域

26a 第1の金属シリサイド膜

26b 第2の金属シリサイド膜

27 絶縁膜

28 第1の層間絶縁膜

29 レジストマスク

30,30a,30b 第2の金属膜

30A 第1のゲート電極

30B 第2のゲート電極

31 第2の層間絶縁膜

32a 第1のコンタクトホール

32b 第2のコンタクトホール

33a 第1のコンタクトプラグ

33b 第2のコンタクトプラグ

34 金属シリサイド膜

35 ゲート絶縁膜形成膜

35a 第3のゲート絶縁膜

Wnp 素子分離領域のゲート幅方向の幅

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に金属材料からなるゲート電極を有するMISFET(Metal Insulator Semiconductor Field Effect Transistor)を備えた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体集積回路装置の高集積化及び高速化に伴い、MISFETの微細化が進められている。MISFETの微細化によるゲート絶縁膜の極薄膜化に伴い、ポリシリコンゲート電極の空乏容量の顕在化及びボロンのチャネル領域への突き抜けという問題がある。この問題の解決策として、n型MISFET(以下、「n型MISトランジスタ」と称す)のゲート電極として金属材料からなるメタルゲート電極を用いると共に、p型MISFET(以下、「p型MISトランジスタ」と称す)のゲート電極として金属材料からなるメタルゲート電極を用いたデュアルメタルゲート構造の半導体装置が検討されている。

【0003】

デュアルメタルゲート構造の半導体装置の場合、n型MISトランジスタのゲート電極と、p型MISトランジスタのゲート電極とが互いに異なる金属材料からなることが必要とされる。例えば、n型MISトランジスタのゲート電極は、4.05eV以上で4.6eV以下の仕事関数を有する金属材料からなる一方、p型MISトランジスタのゲート電極は、4.6eV以上で5.15eV以下の仕事関数を有する金属材料からなることが必要とされる。

【0004】

デュアルメタルゲート構造の半導体装置の製造方法としては、例えば、第1の従来の半導体装置の製造方法(例えば非特許文献1参照)、及び第2の従来の半導体装置の製造方法(例えば非特許文献2参照)が提案されている。

【非特許文献1】Z.B.Zhang et al., “Integration of Dual Metal Gate CMOS withTaSiN(NMOS) and Ru(PMOS) Gate Electrodes on HfO2 Gate Dielectric”, VLSI2005

【非特許文献2】S.C.Song et al., “Highly Manufacturable 45nm LSTP CMOSFETs Using Novel Dual High-k and Dual Metal Gate CMOS Integration”, VLSI2006

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、第1,第2の従来の半導体装置の製造方法では、以下に示す問題がある。

【0006】

以下に、第1の従来の半導体装置の製造方法及びその問題点について順に説明する。第1の従来の半導体装置の製造方法について、図13を参照しながら説明する。図13は、第1の従来の半導体装置の製造方法を示すゲート幅方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0007】

まず、半導体基板100の上部に素子分離領域101を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域101に囲まれた第1の活性領域100aが形成され、p型MIS形成領域には、素子分離領域101に囲まれた第2の活性領域100bが形成される。その後、半導体基板100におけるn型MIS形成領域にp型ウェル領域102aを形成する一方、半導体基板100におけるp型MIS形成領域にn型ウェル領域102bを形成する。

【0008】

次に、半導体基板100上に、ゲート絶縁膜形成膜、n型MISトランジスタ用のゲート電極材料(以下、「nMIS用金属材料」と称す)からなる第1の金属膜、p型MISトランジスタ用のゲート電極材料(以下、「pMIS用金属材料」と称す)からなる第2の金属膜、及びシリコン膜を順次形成する。

【0009】

このようにして、図13に示すように、第1の活性領域100a上に、ゲート絶縁膜形成膜103a、第1の金属膜104a、第2の金属膜105a、及びシリコン膜106aが順次形成された第1のパターニング部107Aを形成すると共に、第2の活性領域100b上に、ゲート絶縁膜形成膜103b、第2の金属膜105b、及びシリコン膜106bが順次形成された第2のパターニング部107Bを形成する。

【0010】

その後、図示しないが、シリコン膜106a,106b上に形成されたゲートパターン形状を有するレジストをマスクにして、ドライエッチング法により、第1のパターニング部107Aをパターニングして、ゲート絶縁膜形成膜103aからなる第1のゲート絶縁膜、並びに第1の金属膜104a、第2の金属膜105a、及びシリコン膜106aからなる第1のゲート電極を形成すると共に、第2のパターニング部107Bをパターニングして、ゲート絶縁膜形成膜103bからなる第2のゲート絶縁膜、並びに第2の金属膜105b及びシリコン膜106bからなる第2のゲート電極を形成する。

【0011】

ここで、第1の従来の半導体装置の製造方法における問題点について説明する。第1の従来の半導体装置の製造方法では、図13に示すように、第1のパターニング部107Aと第2のパターニング部107Bとは、互いに構成が異なるにも拘わらず(詳細には、第1のパターニング部107Aの構成は4層構成であるのに対し、第2のパターニング部107Bの構成は3層構成である)、互いに同一の工程において、すなわち、互いに同一のエッチング条件の下、パターニングされるため、第1のゲート電極及び第2のゲート電極の双方を精度良く形成することができないという問題がある。例えば、エッチング条件を、第2のゲート電極が精度良く形成されるエッチング条件にした場合、第1のパターニング部107Aにおける第1の金属膜104a及びゲート絶縁膜形成膜103aがエッチングされずに残存するため、第1のゲート電極を精度良く形成することができない。一方、例えば、エッチング条件を、第1のゲート電極が精度良く形成されるエッチング条件にした場合、p型MIS形成領域の半導体基板100及び素子分離領域101中にエッチング削れが発生するので、第2のゲート電極を精度良く形成することができない。

【0012】

以下に、第2の従来の半導体装置の製造方法及びその問題点について順に説明する。第2の従来の半導体装置の製造方法について、図14(a) 〜(e) を参照しながら説明する。図14(a) 〜(e) は、第2の従来の半導体装置の製造方法を工程順に示すゲート幅方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0013】

まず、半導体基板200の上部に素子分離領域201を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域201に囲まれた第1の活性領域200aが形成され、p型MIS形成領域には、素子分離領域201に囲まれた第2の活性領域200bが形成される。その後、半導体基板200におけるn型MIS形成領域にp型ウェル領域202aを形成する一方、半導体基板200におけるp型MIS形成領域にn型ウェル領域202bを形成する。

【0014】

次に、半導体基板200上に、n型MISトランジスタ用のゲート絶縁膜材料(以下、「nMIS用絶縁材料」と称す)からなる第1のゲート絶縁膜形成膜、nMIS用金属材料からなる第1の金属膜、及び第1のマスク膜を順次形成する。その後、図14(a) に示すように、フォトリソグラフィ法により、第1のマスク膜上にn型MIS形成領域を覆うレジストマスク206を形成する。

【0015】

次に、レジストマスク206をマスクにして、第1のマスク膜をエッチングして、第1のマスク膜205aを形成した後、レジストマスク206を除去する。その後、第1のマスク膜205aをマスクにして、第1の金属膜204、及び第1のゲート絶縁膜形成膜203を順次エッチングする。

【0016】

次に、図14(b) に示すように、半導体基板200上に、p型MISトランジスタ用のゲート絶縁膜材料(以下、「pMIS用絶縁材料」と称す)からなる第2のゲート絶縁膜形成膜207、pMIS用金属材料からなる第2の金属膜208、及び第2のマスク膜209を順次形成する。その後、フォトリソグラフィ法により、第2のマスク膜209上にp型MIS形成領域を覆うレジストマスク210を形成する。

【0017】

次に、図14(c) に示すように、レジストマスク210をマスクにして、第2のマスク膜209をエッチングして、第2のマスク膜209bを形成した後、レジストマスク210を除去する。その後、第2のマスク膜209bをマスクにして、第2の金属膜208、及び第2のゲート絶縁膜形成膜207を順次エッチングする。

【0018】

次に、図14(d) に示すように、第1,第2のマスク膜205a,209bを除去した後、第1の金属膜204及び第2の金属膜208上に、シリコン膜211を形成する。

【0019】

このようにして、図14(d) に示すように、第1の活性領域200a上に、第1のゲート絶縁膜形成膜203、第1の金属膜204、及びシリコン膜211が順次形成された第1のパターニング部を形成すると共に、第2の活性領域200b上に、第2のゲート絶縁膜形成膜207、第2の金属膜208、及びシリコン膜211が順次形成された第2のパターニング部を形成する。

【0020】

次に、図14(e) に示すように、フォトリソグラフィ法により、シリコン膜211上にゲートパターン形状を有するレジスト(図示せず)を形成した後、レジストをマスクにして、エッチング法により、第1のパターニング部をパターニングして、第1のゲート絶縁膜203a、並びに第1の金属膜204a及び第1のシリコン膜211aからなる第1のゲート電極212Aを形成すると共に、第2のパターニング部をパターニングして、第2のゲート絶縁膜207b、並びに第2の金属膜208b及び第2のシリコン膜211bからなる第2のゲート電極212Bを形成する。

【0021】

ここで、第2の従来の半導体装置の製造方法における問題点について、図15を参照しながら説明する。図15は、第2の従来の半導体装置の製造方法における問題点について示す平面図である。なお、図15に示すXIVe-XIVe線は、図14(e) に示す断面図の断面線に相当する。

【0022】

p型MIS形成領域を覆うレジストマスク210が、ゲート幅方向にずれて形成されて、図14(b) に示すように、レジストマスク210のゲート幅方向の端部が、n型MIS形成領域側に位置すると、図14(d) に示すように、素子分離領域201上に、第1のマスク膜205aの残部205c、第2のゲート絶縁膜形成膜207の残部207c、及び第2の金属膜208の残部208cからなる残部rが突出して形成される。

【0023】

この残部rが形成された状態でパターニングを行うと、図15に示すように、素子分離領域201上に、ゲート長方向に伸びるように、パターニングされた残部rp(なお、パターニングされた残部rpは、図14(e) に示すように、パターニングされた残部205cpと、パターニングされた残部207cpと、パターニングされた残部208cpとからなる)が残存する。加えて、パターニングされた残部rpのゲート幅方向の側面上に、シリコン膜211からなる側壁絶縁膜211cが形成される。

【0024】

パターニングされた残部rp(又は側壁絶縁膜211c)により、第1,第2のゲート電極212A,212Bが、第1,第2のゲート電極212A,212Bとゲート長方向に沿って隣り合う他の第1,第2のゲート電極(図示せず)と電気的に接続するため、第1,第2のゲート電極212A,212Bはゲート電極としての機能を果たさない。このように、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極212A,212Bを形成することができないという問題がある。

【0025】

なお、この問題の要因として、p型MIS形成領域を覆うレジストマスク210がn型MIS形成領域側にずれて形成される場合を具体例に挙げて説明したが、仮にレジストマスク210がn型MIS形成領域側にずれて形成されることがなくとも、n型MIS形成領域を覆うレジストマスク206がp型MIS形成領域側にずれて形成されることにより、上記と同様の問題が生じる。すなわち、図14(a) に示す工程において、レジストマスク206が、p型MIS形成領域側にずれて形成された場合、図16に示すように、素子分離領域201上に残部rが突出して形成される。

【0026】

ここで、上記の問題は、素子分離領域201のゲート幅方向の幅を拡げることで回避することが可能である。すなわち、素子分離領域201に予め合わせマージン(余裕領域)を設けて、素子分離領域201のゲート幅方向の幅を拡げることで、図14(a) に示す工程において、レジストマスク206の形成の際に、レジストマスク206がゲート幅方向にずれて形成されることがあっても、レジストマスク206のゲート幅方向の端部を、p型MIS形成領域側に位置させずに、n型MIS形成領域側に位置させることができる。それと共に、図14(b) に示す工程において、レジストマスク210の形成の際に、レジストマスク210がゲート幅方向にずれて形成されることがあっても、レジストマスク210のゲート幅方向の端部を、n型MIS形成領域側に位置させずに、p型MIS形成領域側に位置させることができる。しかしながら、この場合、次に示す問題がある。すなわち、レジストマスク206の形成、及びレジストマスク210の形成の際に、素子分離領域201に合わせマージンが必要とされるため、素子分離領域201のゲート幅方向の幅を縮小化することができないという問題がある。

【0027】

さらに、第2の従来の半導体装置の製造方法では、図14(d) に示すように、第1のパターニング部と第2のパターニング部とは、互いに構成が異なるにも拘わらず(詳細には、第1,第2のパターニング部は、互いに同一のシリコン膜211を有するものの、互いに異なる第1,第2のゲート絶縁膜形成膜203,207及び第1,第2の金属膜204,208を有する)、言い換えれば、互いにエッチング特性が異なるにも拘わらず、互いに同一のエッチング条件の下、パターニングされるため、第1,第2のゲート電極の双方を精度良く形成することができないという問題もある。

【0028】

このように、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極を形成することは可能なものの、第1,第2のゲート電極の双方を精度良く形成することはできず、さらに、素子分離領域201のゲート幅方向の幅を縮小化することができないという問題がある。

【0029】

以上のように、第1の従来の半導体装置の製造方法では、第1,第2のゲート電極の双方を精度良く形成することができないという問題がある。一方、第2の従来の半導体装置の製造方法では、第1,第2のゲート電極の双方を精度良く形成することができないだけでなく、さらに、素子分離領域のゲート幅方向の幅を縮小化することができないという問題がある。

【0030】

前記に鑑み、本発明の目的は、互いに異なる金属材料からなるゲート電極を有するn型,p型MISトランジスタを備えた半導体装置において、精度良く形成されたn型,p型MISトランジスタのゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現することである。

【課題を解決するための手段】

【0031】

前記の目的を達成するために、本発明に係る半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板における第1の活性領域上に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第2の金属膜からなる第1のゲート電極と、第1のゲート電極の側面上から第1の活性領域における第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜とを備え、第2のMISトランジスタは、半導体基板における第2の活性領域上に形成された第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成され第1の金属膜と第1の金属膜上に形成された導電膜とからなる第2のゲート電極と、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1のゲート電極及び第2のゲート電極の各上面上には、絶縁膜が形成されていないことを特徴とする。

【0032】

本発明に係る半導体装置によると、精度良く形成された第1,第2のゲート電極を実現することができる。加えて、ゲート幅方向の幅が縮小化された素子分離領域を実現することができるので、半導体装置の微細化を図ることができる。

【0033】

本発明に係る半導体装置において、第1の金属膜は、第2の金属膜に比べて膜厚が薄いことが好ましい。

【0034】

本発明に係る半導体装置において、第1の金属膜と第2の金属膜とは、互いに仕事関数が異なっていることが好ましい。

【0035】

本発明に係る半導体装置において、絶縁膜の膜厚は、第1のゲート電極の膜厚に比べて薄いことが好ましい。

【0036】

本発明に係る半導体装置において、導電膜は、第2の金属膜からなることが好ましい。

【0037】

本発明に係る半導体装置において、導電膜は、シリコン膜からなり、シリコン膜上に形成された金属シリサイド膜をさらに備えていることが好ましい。

【0038】

本発明に係る半導体装置において、第1のゲート絶縁膜は、第2のゲート絶縁膜と同じ絶縁材料からなることが好ましい。

【0039】

本発明に係る半導体装置において、第1のゲート絶縁膜は、第2のゲート絶縁膜と異なる絶縁材料からなることが好ましい。

【0040】

本発明に係る半導体装置において、第1のゲート電極の側面上に形成された断面形状がL字状の第1の内側サイドウォールと、第2のゲート電極の側面上に形成された断面形状がL字状の第2の内側サイドウォールとをさらに備え、絶縁膜は、第1の内側サイドウォール及び第2の内側サイドウォールの上に接して形成されていることが好ましい。

【0041】

本発明に係る半導体装置において、絶縁膜は、第1の活性領域におけるチャネル領域のゲート長方向に第1の応力を生じさせる応力絶縁膜であることが好ましい。

【0042】

このようにすると、応力絶縁膜により、第1の活性領域におけるチャネル領域のゲート長方向に第1の応力を印加して、第1のMISトランジスタの駆動能力を向上させることができる。

【0043】

本発明に係る半導体装置において、第1のMISトランジスタは、n型MISトランジスタであり、絶縁膜は、シリコン窒化膜からなり、第1の応力は、引っ張り応力であることが好ましい。

【0044】

本発明に係る半導体装置において、第2の活性領域における第2のゲート電極の外側方下に形成されたソースドレイン領域をさらに備え、ソースドレイン領域は、第2の活性領域に設けられたトレンチ内に形成され、第2の活性領域におけるチャネル領域のゲート長方向に第2の応力を生じさせるシリコン混晶層を含むことが好ましい。

【0045】

このようにすると、シリコン混晶層により、第2の活性領域におけるチャネル領域のゲート長方向に第2の応力を印加して、第2のMISトランジスタの駆動能力を向上させることができる。

【0046】

本発明に係る半導体装置において、第2のMISトランジスタは、p型MISトランジスタであり、シリコン混晶層は、SiGe層からなり、第2の応力は、圧縮応力であることが好ましい。

【0047】

本発明に係る半導体装置において、第1のゲート絶縁膜及び第2のゲート絶縁膜は、比誘電率が10以上の金属酸化物からなる高誘電率膜を含むことが好ましい。

【0048】

前記の目的を達成するために、本発明に係る半導体装置の製造方法は、半導体基板における第1の活性領域上に形成された第1のMISトランジスタと、半導体基板における第2の活性領域上に形成された第2のMISトランジスタとを有する半導体装置の製造方法であって、第1の活性領域上に第1のゲート絶縁膜、第1の金属膜及び第1のシリコン膜を有する第1のゲート電極形成部を形成すると共に、第2の活性領域上に第2のゲート絶縁膜、第1の金属膜及び第2のシリコン膜を有する第2のゲート電極形成部を形成する工程(a)と、工程(a)の後に、半導体基板上に第1のゲート電極形成部及び第2のゲート電極形成部を覆う絶縁膜を形成する工程(b)と、第1のゲート電極形成部及び第2のゲート電極形成部の上に形成されている絶縁膜を除去して、第1のゲート電極形成部における第1のシリコン膜及び第2のゲート電極形成部における第2のシリコン膜の各上面を露出する工程(c)と、工程(c)の後に、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して、第1の活性領域上に絶縁膜に囲まれた第1の凹部を形成する工程(d)と、第1の凹部内に第2の金属膜を形成する工程(e)とを備え、第1のMISトランジスタの第1のゲート電極は、第2の金属膜からなり、第2のMISトランジスタの第2のゲート電極は、第2のゲート電極形成部における第1の金属膜を含むことを特徴とする。

【0049】

本発明に係る半導体装置の製造方法によると、互いに同一の工程において、第1,第2のゲート電極形成部を形成した後、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して形成された第1の凹部内に、第2の金属膜を形成して、第2の金属膜からなる第1のゲート電極を形成する。一方、第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成する。そのため、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を、第2の金属膜に置換するに当たっては、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の際には、素子分離領域に合わせマージンは必要とされない。従って、素子分離領域に合わせマージンが必要とされる工程数を削減することができるため、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域のゲート幅方向の幅を縮小化することができるので、半導体装置の微細化を図ることができる。

【0050】

加えて、互いに同一の工程において、互いに同一の構成の第1,第2のゲート電極形成部(言い換えれば、互いに同一のエッチング特性の第1,第2のゲート電極形成部)を形成するため、第1,第2のゲート電極形成部を容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部における第1の金属膜及び第1のシリコン膜を、第2の金属膜と置換して、第2の金属膜からなる第1のゲート電極を形成することができる。一方、精度良く形成された第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成することができるため、精度良く形成された第1,第2のゲート電極を実現することができる。

【0051】

本発明に係る半導体装置の製造方法において、工程(d)は、第1の活性領域上に第1のゲート絶縁膜が底面に露出する第1の凹部を形成すると共に、第2のゲート電極形成部における第2のシリコン膜を除去して、第2の活性領域上に絶縁膜に囲まれ、第1の金属膜が底面に露出する第2の凹部を形成する工程を含み、工程(e)は、第1の凹部内における第1のゲート絶縁膜上に第2の金属膜を形成すると共に、第2の凹部内における第1の金属膜上に第2の金属膜を形成する工程を含み、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜と、第1の金属膜上に形成された第2の金属膜とからなることが好ましい。

【0052】

このようにすると、第1のゲート電極形成部における第1の金属膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0053】

本発明に係る半導体装置の製造方法において、工程(d)は、第1の活性領域上に第1のゲート絶縁膜が底面に露出する第1の凹部を形成する工程を含み、工程(e)は、第1の凹部内における第1のゲート絶縁膜上に第2の金属膜を形成する工程を含み、工程(e)の後に、第2のシリコン膜上に金属シリサイド膜を形成する工程(f)をさらに備え、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜及び第2のシリコン膜からなることが好ましい。

【0054】

このようにすると、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0055】

本発明に係る半導体装置の製造方法において、工程(d)は、第1のゲート電極形成部における第1のシリコン膜、第1の金属膜及び第1のゲート絶縁膜を順次除去して、第1の活性領域上に第1の活性領域が底面に露出する第1の凹部を形成する工程を含み、工程(e)は、第1の凹部内に第3のゲート絶縁膜を形成すると共に、第3のゲート絶縁膜上に第2の金属膜を形成する工程を含み、工程(e)の後に、第2のシリコン膜上に金属シリサイド膜を形成する工程(f)をさらに備え、第2のゲート電極は、第2のゲート電極形成部における第1の金属膜及び第2のシリコン膜からなることが好ましい。

【0056】

このようにすると、第1のゲート電極形成部における第1のシリコン膜、第1の金属膜及び第1のゲート絶縁膜の除去の際には、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の形成の際には、素子分離領域に合わせマージンは必要とされないため、素子分離領域に合わせマージンが必要とされる工程数を1回に抑えることができる。

【0057】

本発明に係る半導体装置の製造方法において、工程(a)の後で、工程(b)の前に、第1のゲート電極形成部の側面上に断面形状がL字状の第1の内側サイドウォールを形成すると共に、第2のゲート電極形成部の側面上に断面形状がL字状の第2の内側サイドウォールを形成する工程(g)をさらに備え、工程(b)において、絶縁膜を、第1の内側サイドウォール及び第2の内側サイドウォールの上に接して形成することが好ましい。

【0058】

本発明に係る半導体装置の製造方法において、工程(a)の後で、工程(b)の前に、第2の活性領域における第2のゲート電極形成部の外側方下にトレンチを形成する工程(h)と、トレンチ内に、第2の活性領域におけるチャネル領域のゲート長方向に応力を生じさせるシリコン混晶層を形成する工程(i)とをさらに備えていることが好ましい。

【発明の効果】

【0059】

本発明に係る半導体装置及びその製造方法によると、互いに同一の工程において、第1,第2のゲート電極形成部を形成した後、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を順次除去して形成された第1の凹部内に、第2の金属膜を形成して、第2の金属膜からなる第1のゲート電極を形成する。一方、第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成する。そのため、第1のゲート電極形成部における第1のシリコン膜及び第1の金属膜を、第2の金属膜に置換するに当たっては、素子分離領域に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部の際には、素子分離領域に合わせマージンは必要とされない。従って、素子分離領域に合わせマージンが必要とされる工程数を削減することができるため、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域のゲート幅方向の幅を縮小化することができるので、半導体装置の微細化を図ることができる。

【0060】

加えて、互いに同一の工程において、互いに同一の構成の第1,第2のゲート電極形成部を形成するため、第1,第2のゲート電極形成部を容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部における第1の金属膜及び第1のシリコン膜を、第2の金属膜と置換して、第2の金属膜からなる第1のゲート電極を形成することができる。一方、精度良く形成された第2のゲート電極形成部における第1の金属膜を含む第2のゲート電極を形成することができるため、精度良く形成された第1,第2のゲート電極を実現することができる。

【発明を実施するための最良の形態】

【0061】

以下に、本発明の各実施形態について、図面を参照しながら説明する。

【0062】

(第1の実施形態)

本発明の第1の実施形態に係る半導体装置及びその製造方法について図面を参照しながら説明する。

【0063】

以下に、本発明の第1の実施形態に係る半導体装置の製造方法について、図1(a) 〜(d) 、図2(a) 〜(d) 、図3(a) 〜(d) 、図4(a) 〜(c) 及び図5(a) 〜(c) を参照しながら説明する。図1(a) 〜図5(c) は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0064】

まず、図1(a) に示すように、例えば埋め込み素子分離(Shallow Trench Isolation:STI)法により、例えばp型シリコンからなる半導体基板10の上部に、トレンチ内に絶縁膜が埋め込まれた素子分離領域11を選択的に形成する。これにより、n型MIS形成領域には、素子分離領域11に囲まれた半導体基板10からなる第1の活性領域10aが形成され、p型MIS形成領域には、素子分離領域11に囲まれた半導体基板10からなる第2の活性領域10bが形成される。その後、リソグラフィ法及びイオン注入法により、半導体基板10におけるn型MIS形成領域に、例えばB(ホウ素)等のp型不純物を注入する一方、半導体基板10におけるp型MIS形成領域に、例えばP(リン)等のn型不純物を注入した後、半導体基板10に対して例えば850℃,30秒間の熱処理を施すことにより、半導体基板10におけるn型MIS形成領域に、p型ウェル領域12aを形成する一方、半導体基板10におけるp型MIS形成領域に、n型ウェル領域12bを形成する。

【0065】

次に、図1(b) に示すように、例えば希釈フッ酸処理により、半導体基板10の表面を洗浄した後、例えばISSG(In-Situ Steam Generation)酸化法により、第1の活性領域10a及び第2の活性領域10b上に、例えば膜厚が0.8〜1nm程度のシリコン酸化膜からなる下地膜(図示せず)を形成する。その後、例えば有機金属気相堆積(Metal Organic Chemical Vapor Deposition:MOCVD)法により、下地膜上に、例えば膜厚が2nmの高誘電率膜からなるゲート絶縁膜形成膜13を堆積する。ここで、ゲート絶縁膜形成膜13としては、比誘電率が10以上の金属酸化物からなる高誘電率膜を含むことが望ましい。

【0066】

その後、例えばCVD(Chemical Vapor Deposition)法、ALD(Atomic Layer Deposition)法、又はスパッタ法等により、例えば窒化チタン(TiN)からなる第1の金属膜14を堆積する。ここで、第1の金属膜14としては、p型MISトランジスタ用に最適化された金属材料又は金属化合物材料(以下、「pMIS用金属材料」と称す)からなり、4.6eV以上で5.15eV以下の仕事関数を有することが望ましい。そして、第1の金属膜14の具体例としては、TiN膜の他に、例えば、チタン(Ti)、ルテニウム(Ru)、白金(Pt)若しくはタングステン(W)等の金属、又はTi、Ru、Pt及びWのうち少なくとも1種以上の金属を含む窒化物、炭素窒化物若しくは珪素窒化物等が挙げられる。その後、例えばCVD法により、第1の金属膜14上に、例えば膜厚が100nmのポリシリコン膜からなるシリコン膜15を堆積した後、例えばCVD法により、シリコン膜15上に、例えば膜厚が30nmのシリコン酸化膜からなる保護膜16を堆積する。

【0067】

次に、図1(c) に示すように、フォトリソグラフィ法により、保護膜16上に、ゲートパターン形状を有するレジスト(図示せず)を形成する。その後、レジストをマスクにして、ドライエッチング法により、保護膜16、シリコン膜15、第1の金属膜14及びゲート絶縁膜形成膜13を順次パターニングする。これにより、第1の活性領域10a上に、第1のゲート絶縁膜13a、第1の金属膜14a、第1のシリコン膜15a及び第1の保護膜16aを順次形成すると共に、第2の活性領域10b上に、第2のゲート絶縁膜13b、第1の金属膜14b、第2のシリコン膜15b及び第2の保護膜16bを順次形成する。

【0068】

このようにして、第1の活性領域10a上に第1のゲート絶縁膜13a、第1の金属膜14a及び第1のシリコン膜15aを有する第1のゲート電極形成部14Aを形成すると共に、第2の活性領域10b上に第2のゲート絶縁膜13b、第1の金属膜14b及び第2のシリコン膜15bを有する第2のゲート電極形成部14Bを形成する。

【0069】

次に、図1(d) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなるオフセットスペーサ用絶縁膜を堆積した後、オフセットスペーサ用絶縁膜に対して異方性エッチングを行う。これにより、第1のゲート電極形成部14Aの側面上に第1のオフセットスペーサ17aを形成すると共に、第2のゲート電極形成部14Bの側面上に第2のオフセットスペーサ17bを形成する。

【0070】

その後、半導体基板10上にn型MIS形成領域を開口しp型MIS形成領域を覆うレジスト(図示せず)を形成した後、第1の活性領域10aに、第1のゲート電極形成部14Aをマスクにして、例えばAs(ヒ素)等のn型不純物を注入することにより、第1の活性領域10aにおける第1のゲート電極形成部14Aの側方下に接合深さが比較的浅いn型ソースドレイン領域(LDD領域又はエクステンション領域)18aを自己整合的に形成する。一方、半導体基板10上にn型MIS形成領域を覆いp型MIS形成領域を開口するレジスト(図示せず)を形成した後、第2の活性領域10bに、第2のゲート電極形成部14Bをマスクにして、例えばBF2等のp型不純物を注入することにより、第2の活性領域10bにおける第2のゲート電極形成部14Bの側方下に接合深さが比較的浅いp型ソースドレイン領域(LDD領域又はエクステンション領域)18bを自己整合的に形成する。

【0071】

次に、図2(a) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなる第1の絶縁膜、及び膜厚が30nmのシリコン窒化膜からなる第2の絶縁膜を順次堆積した後、第1の絶縁膜及び第2の絶縁膜に対して異方性エッチングを行う。これにより、第1のゲート電極形成部14Aの側面上に、第1のオフセットスペーサ17aを介して、断面形状がL字状の第1の絶縁膜からなる第1の内側サイドウォール19aと第1の内側サイドウォール19a上に形成された第2の絶縁膜からなる第1の外側サイドウォール20aとで構成された第1のサイドウォール20Aを形成すると共に、第2のゲート電極形成部14Bの側面上に、第2のオフセットスペーサ17bを介して、断面形状がL字状の第1の絶縁膜からなる第2の内側サイドウォール19bと第2の内側サイドウォール19b上に形成された第2の絶縁膜からなる第2の外側サイドウォール20bとで構成された第2のサイドウォール20Bを形成する。

【0072】

次に、図2(b) に示すように、例えばCVD法により、半導体基板10上の全面に、例えば膜厚が10nmのシリコン酸化膜からなる表面保護膜21を堆積する。

【0073】

次に、図2(c) に示すように、表面保護膜21上に、n型MIS形成領域を覆いp型MIS形成領域を開口するレジストマスク22を形成した後、第2の外側サイドウォール20b(シリコン窒化膜)と選択比のある異方性ドライエッチング法を用いて、p型MIS形成領域に形成されている表面保護膜21を除去して、n型MIS形成領域に表面保護膜21aを残存させる。これにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下の領域、すなわち、ソースドレイン形成領域の表面を露出させる。

【0074】

次に、図2(d) に示すように、レジストマスク22を除去した後、表面保護膜21a(シリコン酸化膜)、第2の保護膜16b(シリコン酸化膜)、第2のオフセットスペーサ17b(シリコン酸化膜)、第2の内側サイドウォール19b(シリコン酸化膜)及び第2の外側サイドウォール20b(シリコン窒化膜)と選択比のあるドライエッチング法を用いる、又はこれらの膜と選択比のあるドライエッチング法及びウェットエッチング法を順次組み合わせて用いて、表面に露出されている第2の活性領域10bをエッチングする。これにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下の領域(すなわちソースドレイン形成領域)に、例えば深さが60nmのトレンチ23を形成する。このとき、第1の活性領域10aの表面は表面保護膜21aで覆われているため、第1の活性領域10aはエッチングされない。また、第1のシリコン膜15aの上面は第1の保護膜16a及び表面保護膜21aで順次覆われている一方、第2のシリコン膜15bの上面は第2の保護膜16bで覆われているため、第1,第2のシリコン膜15a,15bはエッチングされない。

【0075】

次に、図3(a) に示すように、例えばフッ酸処理により、トレンチ23内のエッチング残渣及び自然酸化膜等を除去した後、例えばCVD法により、例えばシランガス(SiH4)及びゲルマンガス(GeH4)を、例えばジボランガス(B2H6)等のp型ドーパントガスと共に例えば650〜700℃の温度で供給することにより、トレンチ23内を充填するようにp型SiGe層からなるシリコン混晶層24をエピタキシャル成長させる。このとき、第1の活性領域10aの表面は表面保護膜21aで覆われているため、第1の活性領域10a上にSiGe層はエピタキシャル成長されない。また、第1のシリコン膜15aの上面は第1の保護膜16a及び表面保護膜21aで順次覆われている一方、第2のシリコン膜15bの上面は第2の保護膜16bで覆われているため、第1,第2のシリコン膜15a,15b上にSiGe層はエピタキシャル成長されない。

【0076】

その後、半導体基板10及び第1の外側サイドウォール20a(シリコン窒化膜)と選択比のあるドライエッチング法を用いる、又はこれらの膜と選択比のあるドライエッチング法及びウェットエッチング法を順次組み合わせて用いて、n型MIS形成領域に形成されている表面保護膜21aを除去して、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下の領域、すなわち、ソースドレイン形成領域の表面を露出させる。

【0077】

このように図2(b) 〜図3(a) に示す工程を順次経ることにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に形成されたトレンチ23内に、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を生じさせるシリコン混晶層24を形成する。

【0078】

次に、図3(b) に示すように、リソグラフィ法及びイオン注入法により、第1の活性領域10aに、第1のゲート電極形成部14A、第1のオフセットスペーサ17a及び第1のサイドウォール20Aをマスクにして、例えばAs(ヒ素)等のn型不純物を注入することにより、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に、浅いn型ソースドレイン領域18aよりも深い接合深さを有し、接合深さが比較的深いn型ソースドレイン領域25aを自己整合的に形成する。一方、第2の活性領域10bに、第2のゲート電極形成部14B、第2のオフセットスペーサ17b及び第2のサイドウォール20Bをマスクにして、例えばB(ボロン)等のp型不純物を注入することにより、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に、浅いp型ソースドレイン領域18bよりも深い接合深さを有し、接合深さが比較的深いp型ソースドレイン領域25bを自己整合的に形成する。その後、熱処理により、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bに含まれる不純物を活性化させる。

【0079】

このように、深いp型ソースドレイン領域25bは、第2の活性領域10bに設けられたトレンチ23内に形成されたシリコン混晶層24を含むように形成される。

【0080】

次に、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bの表面に形成されている自然酸化膜(図示せず)を除去した後、例えばスパッタ法により、半導体基板10上の全面に、例えば膜厚が10nmのニッケルからなる金属膜(図示せず)を堆積する。その後、例えば窒素雰囲気中、320℃の下、1回目のRTA(Rapid Thermal Annealing)処理により、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bのSiと金属膜のNiとを反応させて、深いn型ソースドレイン領域25a及び深いp型ソースドレイン領域25bの上部に、ニッケルシリサイドからなる第1,第2の金属シリサイド膜26a,26bを形成する。

【0081】

その後、硫酸と過酸化水素水との混合液からなるエッチング液中に半導体基板10を浸漬することにより、素子分離領域11、第1,第2のオフセットスペーサ17a,17b及び第1,第2のサイドウォール20A,20B等の上に残存する未反応の金属膜を除去した後、1回目のRTA処理での温度よりも高い温度(例えば550℃)の下、2回目のRTA処理により、第1,第2の金属シリサイド膜26a,26bのシリサイド組成比を安定化させる。

【0082】

次に、図3(c) に示すように、例えば、第1,第2の内側サイドウォール19a,19b(シリコン酸化膜)と選択比のあるドライエッチング法を用いて、第1の外側サイドウォール20a(シリコン窒化膜)及び第2の外側サイドウォール20b(シリコン窒化膜)を除去する。

【0083】

次に、図3(d) に示すように、例えばプラズマCVD法により、半導体基板10上の全面に、例えば膜厚50nmのシリコン窒化膜からなる絶縁膜27を堆積する。

【0084】

このように、絶縁膜27は、表面に第1の保護膜16aが形成された第1のゲート電極形成部14A、及び表面に第2の保護膜16bが形成された第2のゲート電極形成部14Bを覆うように形成される。そして、絶縁膜27は、第1の外側サイドウォール20aが除去された断面形状がL字状の第1の内側サイドウォール19a、及び第2の外側サイドウォール20bが除去された断面形状がL字状の第2の内側サイドウォール19bの上に接して形成される。

【0085】

その後、例えばCVD法により、絶縁膜27上に、シリコン酸化膜からなる第1の層間絶縁膜28を堆積した後、例えばCMP(Chemical Mechanical Polishing)法により、第1の層間絶縁膜28の表面の平坦化を行いながら、第1の保護膜16a及び第2の保護膜16bの上に形成されている絶縁膜27の上面が露出するまで、第1の層間絶縁膜28を研磨除去する。

【0086】

次に、図4(a) に示すように、第1,第2のシリコン膜(ポリシリコン膜)15a,15bと選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14A、及び第2のゲート電極形成部14Bの上に形成されている第1,第2の保護膜(シリコン酸化膜)16a,16b及び絶縁膜(シリコン窒化膜)27を除去して、第1のゲート電極形成部14Aにおける第1のシリコン膜15a、及び第2のゲート電極形成部14Bにおける第2のシリコン膜15bの上面を露出する。このとき、第1のゲート電極形成部14A及び第2のゲート電極形成部14Bの側方に形成されている第1,第2のオフセットスペーサ17a,17b、第1,第2の内側サイドウォール19a,19b、絶縁膜27、及び第1の層間絶縁膜28は、その上面高さが、第1,第2のシリコン膜15a,15bの上面高さと同じ又は同程度になるまで同時に除去される。

【0087】

このように、絶縁膜27は、第1,第2のゲート電極形成部14A,14Bの側面上から第1,第2の活性領域10a,10bにおける第1,第2のゲート電極形成部14A,14Bの側方に位置する領域の上面上に跨って形成される一方、第1,第2のゲート電極形成部14A,14Bの上面上には形成されない。

【0088】

次に、図4(b) に示すように、第1,第2の金属膜(TiN膜)14a,14b、第1,第2のオフセットスペーサ17a,17b、第1,第2の内側サイドウォール19a,19b、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のシリコン膜15a、及び第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去する。

【0089】

次に、図4(c) に示すように、半導体基板10上に、n型MIS形成領域を開口しp型MIS形成領域を覆うレジストマスク29を形成した後、第1のゲート絶縁膜13a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1の金属膜14aを除去する。

【0090】

このように図4(b) 〜(c) に示す工程を順次経ることにより、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して、第1の活性領域10a上に、第1のオフセットスペーサ17a及び第1の内側サイドウォール19aを順次介して絶縁膜27に囲まれ、第1のゲート絶縁膜13aが底面に露出する第1の凹部Caを形成する。それと共に、図4(b) に示す工程を経ることにより、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して、第2の活性領域10b上に、第2のオフセットスペーサ17b及び第2の内側サイドウォール19bを順次介して絶縁膜27に囲まれ、第1の金属膜14bが底面に露出する第2の凹部Cbを形成する。

【0091】

次に、図5(a) に示すように、レジストマスク29を除去した後、半導体基板10上に、例えばCVD法、ALD法、又はスパッタ法等により、第1の凹部Ca及び第2の凹部Cb内を埋め込むように、例えば窒化タンタル(TaN)からなる第2の金属膜30を堆積する。ここで、第2の金属膜30としては、n型MISトランジスタ用に最適化された金属材料又は金属化合物材料(以下、「nMIS用金属材料」と称す)からなり、4.05eV以上で4.6eV以下の仕事関数を有することが望ましい。そして、第2の金属膜30の具体例としては、例えばTaNの他に、タンタル(Ta)若しくはハフニウム(Hf)等の金属、又はTa及びHfのうち少なくとも1種を含む窒化物、炭素窒化物若しくは珪素窒化物等が挙げられる。

【0092】

次に、図5(b) に示すように、例えばCMP法、又はエッチバック法により、絶縁膜27の上面が露出するまで、第2の金属膜30を除去する。これにより、第1の凹部Ca内における第1のゲート絶縁膜13a上に第2の金属膜30aを形成すると共に、第2の凹部Cb内における第1の金属膜14b上に第2の金属膜30bを形成する。

【0093】

このようにして、第1の活性領域10a上に、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2の活性領域10b上に、第2のゲート絶縁膜13bを介して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30Bを形成する。

【0094】

次に、図5(c) に示すように、例えばCVD法により、第1の層間絶縁膜28上に、第1,第2のゲート電極30A,30Bを覆うように、第2の層間絶縁膜31を堆積した後、例えばCMP法により、第2の層間絶縁膜31の表面の平坦化を行う。

【0095】

その後、通常のMISトランジスタを有する半導体装置の製造方法と同様に、第2の層間絶縁膜31上に、レジスト(図示せず)を形成した後、レジストをマスクにして、ドライエッチング法により、絶縁膜27、第1の層間絶縁膜28及び第2の層間絶縁膜31中に、第1,第2の金属シリサイド膜26a,26bの上面に到達する第1,第2のコンタクトホール32a,32bを形成する。このとき、絶縁膜27が露出したところで一度エッチングを止める2ステップのエッチング法を用いることにより、第1,第2の金属シリサイド膜26a,26bのオーバーエッチング量を減らすことができる。

【0096】

その後、スパッタ法又はCVD法により、第1,第2のコンタクトホール32a,32bの底部及び側壁部に、チタンと窒化チタンとが順次堆積されてなるバリアメタル膜を形成する。その後、CVD法により、第2の層間絶縁膜31上に、第1,第2のコンタクトホール32a,32b内を埋め込むように、タングステン膜を堆積した後、CMP法により、第1,第2のコンタクトホール32a,32b外に形成されているタングステン膜を除去する。このようにして、第1,第2のコンタクトホール32a,32b内に、バリアメタル膜を介してタングステン膜が埋め込まれてなる第1,第2のコンタクトプラグ33a,33bを形成する。その後、第2の層間絶縁膜31上に、第1,第2のコンタクトプラグ33a,33bと電気的に接続する金属配線(図示せず)を形成する。

【0097】

以上のようにして、本実施形態に係る半導体装置、すなわち、第2の金属膜30aからなる第1のゲート電極30Aを有するn型MISトランジスタNTrと、第1の金属膜14b及び第2の金属膜(導電膜)30bからなる第2のゲート電極30Bを有するp型MISトランジスタPTrとを備えた半導体装置を製造することができる。

【0098】

以下に、本発明の第1の実施形態に係る半導体装置の構成について、図6(a) 及び(b) を参照しながら説明する。図6(a) 及び(b) は、本発明の第1の実施形態に係る半導体装置の構成について示す図であり、具体的には、図6(a) は平面図であり、図6(b) は図6(a) に示すVIb-VIb線におけるゲート幅方向の断面図である。なお、図6(a) に示すVl-Vl線は、図5(c) 中の左図における断面線に相当する一方、図6(a) に示すVr-Vr線は、図5(c) 中の右図における断面線に相当する。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0099】

図6(a) に示すように、n型MIS形成領域には、素子分離領域に囲まれた第1の活性領域10aが形成され、p型MIS形成領域には、素子分離領域に囲まれた第2の活性領域10bが形成されている。第1の活性領域10a上には、第1のゲート絶縁膜を介して、第1のゲート電極30Aが形成されていると共に、第2の活性領域10b上には、第2のゲート絶縁膜を介して、第2のゲート電極30Bが形成されている。第1,第2のゲート電極30A,30Bの側面上には、第1,第2のオフセットスペーサ17a,17b及び第1,第2の内側サイドウォール19a,19bを順次介して、絶縁膜27が形成されている。なお、図6(a) においては、第1の層間絶縁膜(図5(c):28参照)、及び第2の層間絶縁膜(図5(c):31参照)の図示を省略しているが、第1の層間絶縁膜は、絶縁膜27上に形成されている。また、第2の層間絶縁膜は、第1,第2のゲート電極30A,30Bを覆うように、第1の層間絶縁膜上に形成されている。

【0100】

図6(b) に示すように、半導体基板10の上部には、n型MIS形成領域とp型MIS形成領域とを区画するように、トレンチ内に絶縁膜が埋め込まれた素子分離領域11が形成されている。半導体基板10におけるn型MIS形成領域には、p型ウェル領域12aが形成されている一方、半導体基板10におけるp型MIS形成領域には、n型ウェル領域12bが形成されている。第1の活性領域10a上には、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aが形成されている一方、第2の活性領域10b上には、第2のゲート絶縁膜13bを介して、第1の金属膜14bと第1の金属膜14b上に形成された第2の金属膜(導電膜)30bとからなる第2のゲート電極30Bが形成されている。半導体基板10上には、第1,第2のゲート電極30A,30Bを覆うように第2の層間絶縁膜31が形成されている。

【0101】

ここで、n型MISトランジスタ及びp型MISトランジスタの構成について、図5(c) を参照しながら詳細に説明する。

【0102】

n型MISトランジスタNTrは、図5(c) に示すように、半導体基板10における素子分離領域11に囲まれた第1の活性領域10aと、第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極30Aの側面上に第1のオフセットスペーサ17aを介して形成され断面形状がL字状の第1の内側サイドウォール19aと、第1の活性領域10aにおける第1のゲート電極30Aの側方下に形成された浅いn型ソースドレイン領域18aと、第1の活性領域10aにおける第1の内側サイドウォール19aの外側方下に形成された深いn型ソースドレイン領域25aと、第1のゲート電極30Aの側面上から第1の活性領域10aにおける第1のゲート電極30Aの側方に位置する領域の上面上に跨って形成された絶縁膜27と、深いn型ソースドレイン領域25aの上部に形成された第1の金属シリサイド膜26aとを備えている。

【0103】

p型MISトランジスタPTrは、図5(c) に示すように、半導体基板10における素子分離領域11に囲まれた第2の活性領域10bと、第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され第1の金属膜14b及び第2の金属膜(導電膜)30bからなる第2のゲート電極30Bと、第2のゲート電極30Bの側面上に第2のオフセットスペーサ17bを介して形成され断面形状がL字状の第2の内側サイドウォール19bと、第2の活性領域10bにおける第1のゲート電極30Bの側方下に形成された浅いp型ソースドレイン領域18bと、第2の活性領域10bにおける第2の内側サイドウォール19bの外側方下に形成されシリコン混晶層24を含む深いp型ソースドレイン領域25bと、第2のゲート電極30Bの側面上から第2の活性領域10bにおける第2のゲート電極30Bの側方に位置する領域の上面上に跨って形成された絶縁膜27と、深いp型ソースドレイン領域25bの上部に形成された第2の金属シリサイド膜26bとを備えている。

【0104】

第1のゲート電極30Aを構成する第2の金属膜30aは、4.05eV以上で4.6eV以下の仕事関数を有する金属材料(又は金属化合物材料)からなる一方、第2のゲート電極30Bを構成する第1の金属膜14bは、4.6eV以上で5.15eV以下の仕事関数を有する金属材料(又は金属化合物材料)からなる。このように、第2の金属膜30aと第1の金属膜14bとは、互いに異なる仕事関数を有し、互いに異なる金属材料(又は金属化合物材料)からなる。

【0105】

また、第1のゲート電極30Aと第2のゲート電極30Bとは、その上面高さが互いに同じであり、第1のゲート電極30Aは、第2の金属膜30aからなる一方、第2のゲート電極30Bは、第1の金属膜14b及び第2の金属膜30bからなる。そのため、第2の金属膜30aの膜厚は、第1の金属膜14bの膜厚及び第2の金属膜(導電膜)30bの膜厚に比べて厚い。

【0106】

絶縁膜27は、第1,第2のゲート電極30A,30Bの側面上から第1,第2の活性領域10a,10bにおける第1,第2のゲート電極30A,30Bの側方に位置する領域の上面上に跨って形成されている一方、第1,第2のゲート電極30A,30Bの上面上には形成されていない。そして、絶縁膜27の膜厚は、第1,第2のゲート電極30A,30Bの膜厚に比べて薄い。

【0107】

第1のゲート絶縁膜13aと第2のゲート絶縁膜13bとは、互いに同一の工程において形成され、互いに同じ絶縁材料からなる。

【0108】

本実施形態によると、互いに同一の工程において、第1,第2のゲート電極形成部14A,14B(図1(c) 参照)を形成した後、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して形成された第1の凹部Ca(図4(c) 参照)内に、第2の金属膜30aを形成して、第2の金属膜30aからなる第1のゲート電極30A(図5(b) 参照)を形成する。一方、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して形成された第2の凹部Cb(図4(b) 参照)内に、第2の金属膜30bを形成して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30B(図5(b) 参照)を形成する。そのため、第1のゲート電極形成部14Aにおける第1の金属膜14aの除去の際には、図4(c) に示すように、n型MIS形成領域及びp型MIS形成領域の一方を開口し他方を覆うレジストマスク29を形成するため、素子分離領域11に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部14A,14Bの形成の際には、素子分離領域11に合わせマージンは必要とされない。従って、素子分離領域11に合わせマージンが必要とされる工程(以下、「合わせマージン必要工程」と称す)数を1回に抑えることができるので、合わせマージンのゲート幅方向の幅を狭くして、素子分離領域11のゲート幅方向の幅(図6(b):Wnp参照)を縮小化することができるので、半導体装置の微細化を図ることができる。

【0109】

これに対し、第2の従来の半導体装置の製造方法では、図14(a) に示す工程において、レジストマスク206の形成の際に素子分離領域201に合わせマージンが必要とされると共に、図14(b) に示す工程において、レジストマスク210の形成の際に素子分離領域201に合わせマージンが必要とされるため、2回の合わせマージン必要工程があるので、既述の通り、素子分離領域201のゲート幅方向の幅を縮小化することができない。

【0110】

加えて、図1(c) に示すように、互いに同一の工程において、互いに同一のシリコン膜15、同一の第1の金属膜14、及び同一のゲート絶縁膜形成膜13が順次パターニングされて、第1,第2のゲート電極形成部14A,14Bが形成されるため、第1,第2のゲート電極形成部14A,14Bを容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部14Aにおける第1の金属膜14a及び第1のシリコン膜15aを、第2の金属膜30aと置換して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、精度良く形成された第2のゲート電極形成部14Bにおける第2のシリコン膜15bを、第2の金属膜30bと置換して、第1の金属膜14b及び第2の金属膜30bからなる第2のゲート電極30Bを形成することができるため、精度良く形成された第1,第2のゲート電極30A,30Bを実現することができる。

【0111】

これに対し、第1の従来の半導体装置の製造方法では、図13に示すように、第1のパターニング部107Aと第2のパターニング部107Bとが、互いに構成が異なるにも拘わらず、互いに同一の工程において、パターニングされるため、既述の通り、第1,第2のゲート電極の双方を精度良く形成することができない。一方、第2の従来の半導体装置の製造方法においても、図14(d) に示すように、第1のパターニング部と第2のパターニング部とが、互いに構成が異なるにも拘わらず、互いに同一の工程において、パターニングされるため、既述の通り、第1,第2のゲート電極の双方を精度良く形成することができない。

【0112】

さらに、深いp型ソースドレイン領域25bが、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を生じさせるシリコン混晶層24を含むことにより、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を印加することができるので、p型MISトランジスタの駆動能力を向上させることができる。

【0113】

なお、第1の実施形態では、p型MISトランジスタの駆動能力を向上させることを目的に、第1,第2のサイドウォール20A,20Bの形成(図2(a) 参照)後で、深いn型,p型ソースドレイン領域25a,25bの形成(図3(b) 参照)前に、図2(b) 〜図3(a) に示す工程を順次行い、第2の活性領域10bにおける第2のサイドウォール20Bの外側方下に形成されたトレンチ23内に、例えばp型SiGe層からなるシリコン混晶層24を形成する場合を具体例に挙げて説明したが、本発明はこれに限定されるものではない。

【0114】

例えば、図2(a) に示すように、第1,第2のサイドウォール20A,20Bを形成した後、図2(b) 〜図3(a) に示す工程を順次行うことなく、すなわち、シリコン混晶層24を形成することなく、図3(b) に示すように、深いn型,p型ソースドレイン領域25a,25bを形成してもよい。

【0115】

また例えば、第1,第2のサイドウォール20A,20Bの形成(図2(a) 参照)後で、深いn型,p型ソースドレイン領域25a,25bの形成(図3(b) 参照)前に、第1の活性領域10aにおける第1のサイドウォール20Aの外側方下に形成されたトレンチ内に、第1の活性領域10aにおけるチャネル領域のゲート長方向に引っ張り応力を生じさせるシリコン混晶層(例えばn型SiC層)を形成してもよい。この場合、p型MISトランジスタではなく、n型MISトランジスタの駆動能力を向上させることができる。

【0116】

(第2の実施形態)

本発明の第2の実施形態に係る半導体装置及びその製造方法について図面を参照しながら説明する。なお、第2の実施形態に係る半導体装置及びその製造方法について、前述の第1の実施形態に係る半導体装置及びその製造方法と相違する点を中心に説明し、共通する点については適宜省略して説明する。

【0117】

以下に、本発明の第2の実施形態に係る半導体装置の製造方法について、図7(a) 〜(c) 及び図8(a) 〜(c) を参照しながら説明する。図7(a) 〜図8(c) は、本発明の第2の実施形態に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図7(a) 〜図8(c) において、前述の第1の実施形態における構成要素と同一の構成要素には、第1の実施形態における図1(a) 〜図5(c) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0118】

まず、第1の実施形態における図1(a) 〜図4(a) に示す工程を順次行い、図7(a) に示す構成(すなわち、図4(a) に示す構成と同一の構成)を得る。

【0119】

次に、図7(b) に示すように、半導体基板10上に、n型MIS形成領域を開口しp型MIS形成領域を覆うレジストマスク29を形成した後、第1の金属膜14a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるドライエッチング法又はウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1のシリコン膜15aを除去する。その後、第1のゲート絶縁膜13a、第1のオフセットスペーサ17a、第1の内側サイドウォール19a、絶縁膜27、及び第1の層間絶縁膜28と選択比のあるウェットエッチング法を用いて、第1のゲート電極形成部14Aにおける第1の金属膜14aを除去する。

【0120】

このようにして、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して、第1の活性領域10a上に、第1のオフセットスペーサ17a及び第1の内側サイドウォール19aを順次介して絶縁膜27に囲まれ、第1のゲート絶縁膜13aが底面に露出する第1の凹部Caを形成する。

【0121】

次に、図7(c) に示すように、レジストマスク29を除去した後、半導体基板10上に、例えばCVD法、ALD法、又はスパッタ法等により、第1の凹部Ca内を埋め込むように、例えばTaNからなる第2の金属膜30を堆積する。

【0122】

次に、図8(a) に示すように、例えばCMP法、又はエッチバック法により、絶縁膜27の上面が露出するまで、第2の金属膜30を除去する。これにより、第1の凹部Ca内における第1のゲート絶縁膜13a上に第2の金属膜30aを形成する。

【0123】

このようにして、第1の活性領域10a上に、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、第2の活性領域10b上に、第2のゲート絶縁膜13bを介して、第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。

【0124】

次に、図8(b) に示すように、第2のシリコン膜15bの表面に形成されている自然酸化膜(図示せず)を除去した後、例えばスパッタ法により、半導体基板10上の全面に、例えば膜厚が10nmのニッケルからなる金属膜(図示せず)を堆積する。その後、例えば窒素雰囲気中、320℃の下、1回目のRTA処理により、第2のシリコン膜15bのSiと金属膜のNiとを反応させて、第2のシリコン膜15bの上部に、ニッケルシリサイドからなる金属シリサイド膜34を形成する。

【0125】

その後、硫酸と過酸化水素水との混合液からなるエッチング液中に半導体基板10を浸漬することにより、第1の層間絶縁膜28、絶縁膜27、第1,第2の内側サイドウォール19a,19b、及び第1,第2のオフセットスペーサ17a,17b等の上に残存する未反応の金属膜を除去した後、1回目のRTA処理での温度よりも高い温度(例えば550℃)の下、2回目のRTA処理により、金属シリサイド膜34のシリサイド組成比を安定化させる。

【0126】

次に、図8(c) に示すように、例えばCVD法により、第1の層間絶縁膜28上に、第1,第2のゲート電極30A,30Bを覆うように、第2の層間絶縁膜31を堆積した後、例えばCMP法により、第2の層間絶縁膜31の表面の平坦化を行う。その後、通常のMISトランジスタを有する半導体装置の製造方法と同様に、絶縁膜27、第1の層間絶縁膜28、及び第2の層間絶縁膜31中の第1,第2のコンタクトホール32a,32b内に形成され、第1,第2の金属シリサイド膜26a,26bと接続する第1,第2のコンタクトプラグ33a,33bを形成する。その後、第2の層間絶縁膜31上に、第1,第2のコンタクトプラグ33a,33bと電気的に接続する金属配線(図示せず)を形成する。

【0127】

以上のようにして、本実施形態に係る半導体装置、すなわち、第2の金属膜30aからなる第1のゲート電極30Aを有するn型MISトランジスタNTrと、第1の金属膜14b及び第2のシリコン膜(導電膜)15bからなる第2のゲート電極30Bを有するp型MISトランジスタPTrとを備えた半導体装置を製造することができる。

【0128】

ここで、本実施形態と第1の実施形態との製造方法上の相違点は、以下に示す点である。

【0129】

第1の実施形態では、図4(b) に示すように、第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去して形成された第2の凹部Cb内に、第2の金属膜30bを形成して、第2のゲート電極形成部14Bにおける第1の金属膜14b、及び第2の金属膜30bからなる第2のゲート電極30Bを形成する。

【0130】

これに対し、本実施形態では、第1の実施形態における図4(b) に示すように第2のゲート電極形成部14Bにおける第2のシリコン膜15bを除去せずに、第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。そして、第2のゲート電極30Bの形成後に、図8(b) に示すように、第2のゲート電極30Bにおける第2のシリコン膜15b上に金属シリサイド膜34を形成する。

【0131】

以下に、本発明の第2の実施形態に係る半導体装置の構成について、図9を参照しながら説明する。図9は、本発明の第2の実施形態に係る半導体装置の構成について示すゲート幅方向の断面図である。なお、図9において、第1の実施形態における構成要素と同一の構成要素には、第1の実施形態における図6(b) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0132】

図9に示すように、第1の活性領域10a上には、第1のゲート絶縁膜13aを介して、第2の金属膜30aからなる第1のゲート電極30Aが形成されている一方、第2の活性領域10b上には、第2のゲート絶縁膜13bを介して、第1の金属膜14bと第1の金属膜14b上に形成された第2のシリコン膜(導電膜)15bとからなる第2のゲート電極30Bが形成されている。第2のシリコン膜15b上には、金属シリサイド膜34が形成されている。

【0133】

ここで、本実施形態と第1の実施形態との構造上の相違点は、以下に示す点である。

【0134】

本実施形態では、第2のゲート電極30Bは、第1の金属膜14bと第2のシリコン膜15bとからなる。そして、第2のシリコン膜15b上には、金属シリサイド膜34が形成されている。これに対し、第1の実施形態では、第2のゲート電極30Bは、第1の金属膜14bと第2の金属膜30bとからなる。

【0135】

このように、第2のゲート電極30Bにおける第1の金属膜14b上に形成された導電膜が、本実施形態では第2のシリコン膜15bであるのに対し、第1の実施形態では第2の金属膜30bである。

【0136】

本実施形態によると、互いに同一の工程において、第1,第2のゲート電極形成部14A,14B(図1(c) 参照)を形成した後、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aを順次除去して形成された第1の凹部Ca(図7(b) 参照)内に、第2の金属膜30aを形成して、第2の金属膜30aからなる第1のゲート電極30A(図8(a) 参照)を形成する。一方、第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成する。そのため、第1のゲート電極形成部14Aにおける第1のシリコン膜15a及び第1の金属膜14aの除去の際には、図7(b) に示すように、n型MIS形成領域及びp型MIS形成領域の一方を開口し他方を覆うレジストマスク29を形成するため、素子分離領域11に合わせマージンが必要とされるものの、第1,第2のゲート電極形成部14A,14Bの形成の際には、素子分離領域11に合わせマージンは必要とされない。従って、合わせマージン必要工程数を1回に抑えることができるため、素子分離領域11のゲート幅方向の幅(図9:Wnp参照)を縮小化することができるので、半導体装置の微細化を図ることができる。

【0137】

加えて、図1(c) に示すように、互いに同一の工程において、互いに同一のシリコン膜15、同一の第1の金属膜14、及び同一のゲート絶縁膜形成膜13が順次パターニングされて、第1,第2のゲート電極形成部14A,14Bが形成されるため、第1,第2のゲート電極形成部14A,14Bを容易に且つ精度良く形成することができる。これにより、精度良く形成された第1のゲート電極形成部14Aにおける第1の金属膜14a及び第1のシリコン膜15aを、第2の金属膜30aと置換して、第2の金属膜30aからなる第1のゲート電極30Aを形成する一方、精度良く形成された第2のゲート電極形成部14Bにおける第1の金属膜14b及び第2のシリコン膜15bからなる第2のゲート電極30Bを形成することができるため、精度良く形成された第1,第2のゲート電極30A,30Bを実現することができる。

【0138】

さらに、第1の実施形態と同様に、深いp型ソースドレイン領域25bがシリコン混晶層24を含むことにより、第2の活性領域10bにおけるチャネル領域のゲート長方向に圧縮応力を印加することができるので、p型MISトランジスタの駆動能力を向上させることができる。

【0139】

(第2の実施形態の変形例)

以下に、本発明の第2の実施形態の変形例に係る半導体装置及びその製造方法について図面を参照しながら説明する。なお、第2の実施形態の変形例に係る半導体装置及びその製造方法について、前述の第2の実施形態に係る半導体装置及びその製造方法と相違する点を中心に説明し、共通する点については適宜省略して説明する。

【0140】

以下に、本発明の第2の実施形態の変形例に係る半導体装置の製造方法について、図10(a) 〜(c) 及び図11(a) 〜(c) を参照しながら説明する。図10(a) 〜図11(c) は、本発明の第2の実施形態の変形例に係る半導体装置の製造方法を工程順に示すゲート長方向の要部工程断面図である。なお、図10(a) 〜図11(c) において、前述の第2の実施形態における構成要素と同一の構成要素には、第2の実施形態における図7(a) 〜図8(c) に示す符号と同一の符号を付している。また、図中において、左側に示す「nMIS」とはn型MISトランジスタが形成されるn型MIS形成領域を示し、右側に示す「pMIS」とはp型MISトランジスタが形成されるp型MIS形成領域を示している。

【0141】

まず、第1の実施形態における図1(a) 〜図4(a) に示す工程を順次行い、第2の実施形態と同様に、図7(a) に示す構成を得る。但し、本変形例におけるゲート絶縁膜形成膜13としては、p型MISトランジスタ用に最適化された膜厚を有し、p型MISトランジスタ用に最適化された絶縁材料からなることが望ましい。

【0142】