半導体装置及びその製造方法

【課題】MIPS構造のデュアル・メタルゲートを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できる半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極122aは、第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタのゲート電極122bは、第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第3の金属含有導電膜113は、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されている。

【解決手段】NMISトランジスタのゲート電極122aは、第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタのゲート電極122bは、第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第3の金属含有導電膜113は、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特にMIPS(Metal inserted Poly-Si Stack)構造のDMG(Dual Metal Gate )プロセスにおいて、ゲート電極等の配線の配線幅を太くする等により高集積化を妨げることなく、金属シリサイド膜のPN境界における断線等に起因する配線の高抵抗化を抑制することを目的とした有効な半導体製造技術に関するものである。

【背景技術】

【0002】

近年、半導体装置の高集積化、微細化に伴い、トランジスタにおいても微細化が急速に進められている。これに伴って、トランジスタのゲート絶縁膜においては、薄膜化が進んでいる。ところが、従来のSiO2 やSiONからなるゲート絶縁膜を薄膜化すると、ゲートリーク電流の値が無視できないほど増大してしまう。そこで、ゲート絶縁膜として、高誘電率膜(以下、High-k膜と称する)を用いることが検討されている。比誘電率の高いHigh-k膜をゲート絶縁膜として用いる場合、実際の物理膜厚を厚く確保してトンネル電流を抑えつつ、EOT(等価酸化膜厚)を薄くしてトランジスタの高駆動力化、低消費電力化を実現することができる。

【0003】

一方、ゲート電極においては、トランジスタの微細化に伴い、電極の空乏化に起因する容量の低下が問題となる。ゲート電極材料として、従来のようにポリシリコンを用いた場合、この容量の低下は、シリコン酸化膜の膜厚に換算して約0.4nmの増大に相当する。この値は、薄膜化が求められているゲート絶縁膜の膜厚と比較すると、無視できない大きさである。そこで、ゲート電極においては、従来のポリシリコンに代えて、メタルを用いることが考えられている。メタルゲート電極を用いる場合、前述のようなゲート空乏化の問題を抑えることができる。しかしながら、High-kゲート絶縁膜にメタルゲート電極を適用するためには、N型MIS(metal-insulator-semiconductor )トランジスタ(以下「NMISトランジスタ」又は「NMIS」と称する)及びP型MISトランジスタ(以下「PMISトランジスタ」又は「PMIS」と称する)のそれぞれについて適切なメタル材料を選定する必要がある。

【0004】

メタルゲートプロセスは、ゲートファーストプロセス及びゲートラストプロセスの2種類に大きく分けることができる。ゲートファーストプロセスにおいては、ゲート電極を形成した後に、イオン注入や熱処理等を含むトランジスタ形成工程を行う。これに対して、ゲートラストプロセスにおいては、ダミーゲートを用いてトランジスタを形成した後に、ダミーゲートを除去してゲート電極を形成するため、ゲートファーストプロセスと比較して、より難易度が高いプロセスとなる。このため、現在、ゲートファーストプロセスを用いたメタルゲート電極形成の検討が行われている。尚、ゲートファーストプロセスにおいては、ゲート加工性やCMOS(complementary-metal-oxide-semiconductor )プロセスとの整合性等を考慮して、一般的にMIPS構造が用いられている。

【0005】

以上のように、次世代のプロセスとして、High-kゲート絶縁膜とMIPS構造のDMGとを適用することが検討されている(例えば非特許文献1参照)。

【0006】

図17は、非特許文献1に開示されているMIPS構造のDMGを備えた半導体装置の断面図、具体的には、ゲート幅方向(W方向)のトランジスタの断面図を示す。図17に示すように、半導体基板1における素子分離形成領域RC には、NMIS形成領域RA の半導体基板1からなる第1の活性領域1AとPMIS形成領域RB の半導体基板1からなる第2の活性領域1Bとを区画するSTI(shallow trench isolation)からなる素子分離領域2が形成されている。素子分離領域2に囲まれたNMIS形成領域RA の第1の活性領域1AにはPウェル領域1aが形成されていると共に、素子分離領域2に囲まれたPMIS形成領域RB の第2の活性領域1BにはNウェル領域1bが形成されている。第1の活性領域1A上にはゲート絶縁膜3aを介してメタルゲート電極4aが形成されている。第2の活性領域1B上にはゲート絶縁膜3bを介してメタルゲート電極4bが形成されている。メタルゲート電極4a及び4bの上並びに当該両電極の間に位置する素子分離領域2の上にはポリシリコン膜6が連続的に形成されている。尚、ポリシリコン膜6は、メタルゲート電極4a及び4bを電気的に接続する配線部分を含むゲート電極形状に加工されている。また、ポリシリコン膜6の表面はシリサイド化されており、それによってシリサイド層7が形成されている。また、図示していないが、イオン注入工程や熱処理工程等によって各MIS形成領域RA 及びRB にはソース・ドレイン領域等の不純物領域が形成されており、それによってトランジスタ構造が構成されている。

【非特許文献1】S.C.Song他、Highly Manufacturable 45nm LSTP CMOSFETs Using Novel Dual High-k and Dual Metal Gate CMOS Integration、VLSI Techonology、2006年8月6日、P.16

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、前述の非特許文献1に開示されているMIPS構造のDMGによると、PMISトランジスタのゲート電極とNMISトランジスタのゲート電極とを電気的に接続する配線、つまりPN境界部配線において金属を含まない領域が存在するため、高抵抗化したり、断線したりする等の問題が生じる。具体的には、NMIS形成領域においてはNMIS用のメタルゲート電極(メタルゲート電極4a)が存在し、PMIS形成領域にはPMIS用のメタルゲート電極(メタルゲート電極4b)が存在している一方、当該両MIS形成領域の境界においてはNMIS用のメタルもPMIS用のメタルもそれぞれのパターニング工程によって除去されている。その結果、図17に示すように、電流8は相対的に抵抗の低い箇所を流れるため、PN境界部配線(金属を含まない領域)においては、ポリシリコン膜6の最表面のシリサイド層7に電流が集中して流れるので、シリサイド層7が断線したり、それに起因して配線の高抵抗化が生じたりする。

【0008】

尚、前述のような問題を防止するために、従来、PN境界部配線の配線幅を太くする等の対策が取られているが、これは高集積化の妨げとなる。

【0009】

前記に鑑み、本発明は、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するために、本願発明者らは、種々の検討を重ねた結果、MIPS構造のDMGを有する半導体装置において、NMIS用のメタルゲート電極及びPMIS用のメタルゲート電極のそれぞれの直上に、ポリシリコンよりも抵抗が低い材料からなる導電層を連続的に形成するという発明を想到した。

【0011】

具体的には、本発明に係る半導体装置は、半導体基板における第1の活性領域上に形成され且つ第1の金属含有導電膜を有する第1のゲート電極と、前記半導体基板における第2の活性領域上に形成され且つ第2の金属含有導電膜を有する第2のゲート電極と、前記第1の活性領域と前記第2の活性領域とを区画するように前記半導体基板に形成された素子分離領域とを備え、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されており、前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜が連続的に形成されており、前記第3の金属含有導電膜は、前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接している。

【0012】

本発明に係る半導体装置によると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、各ゲート電極の一部となる第3の金属含有導電膜、つまりポリシリコンよりも抵抗が低い材料からなる導電層が素子分離領域を横断するように連続的に形成されている。このため、第1のゲート電極と第2のゲート電極とを電気的に接続する配線、つまり素子分離領域上のPN境界部配線が金属(第3の金属含有導電膜)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0013】

本発明に係る半導体装置において、前記第3の金属含有導電膜は前記素子分離領域と接していてもよい。このようにすると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、第3の金属含有導電膜を素子分離領域と接するように形成することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記第3の金属含有導電膜は、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成されていてもよい。

【0014】

本発明に係る半導体装置において、前記第3の金属含有導電膜と前記素子分離領域との間にはシリコン領域が介在していてもよい。すなわち、MIPS構造におけるシリコンのうち素子分離領域の直上の部分はシリサイド化されていなくてもよい。

【0015】

本発明に係る半導体装置において、前記第3の金属含有導電膜はシリサイドから構成されていてもよい。このようにすると、MIPS構造におけるシリコンをシリサイド化することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記シリサイドはTi、Ni、Co又はPtを含んでいてもよい。

【0016】

本発明に係る半導体装置において、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜がさらに形成されていてもよい。すなわち、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本発明に係る半導体装置の構造を実現してもよい。尚、前記シリコン膜の表面はシリサイド化されていてもよい。

【0017】

本発明に係る半導体装置において、前記第1の活性領域と前記第1のゲート電極との間に形成された第1の高誘電率ゲート絶縁膜と、前記第2の活性領域と前記第2のゲート電極との間に形成された第2の高誘電率ゲート絶縁膜とをさらに備えていてもよい。尚、本願において、高誘電率ゲート絶縁膜とは、誘電率がSiONよりも高いゲート絶縁膜、例えばHf系やZr系の元素を含むゲート絶縁膜を意味する。

【0018】

本発明に係る半導体装置において、前記第1のゲート電極がN型MISトランジスタのゲート電極である場合には、前記第1の金属含有導電膜は、仕事関数が4.55eV以下の材料、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなることが好ましい。

【0019】

本発明に係る半導体装置において、前記第2のゲート電極がP型MISトランジスタのゲート電極である場合には、前記第2の金属含有導電膜は、仕事関数が4.65eV以上の材料、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなることが好ましい。

【0020】

本発明に係る半導体装置の製造方法は、半導体基板における第1の活性領域と第2の活性領域とを区画するように、前記半導体基板に素子分離領域を形成する工程(a)と、前記第1の活性領域上に、第1のゲート電極の一部となる第1の金属含有導電膜を形成する工程(b)と、前記第2の活性領域上に、第2のゲート電極の一部となる第2の金属含有導電膜を形成する工程(c)と、前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜を前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接するように連続的に形成する工程(d)とを備え、前記工程(d)において、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されている。

【0021】

本発明に係る半導体装置の製造方法によると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、各ゲート電極の一部となる第3の金属含有導電膜、つまりポリシリコンよりも抵抗が低い材料からなる導電層を素子分離領域を横断するように連続的に形成する。このため、第1のゲート電極と第2のゲート電極とを電気的に接続する配線、つまり素子分離領域上のPN境界部配線が金属(第3の金属含有導電膜)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0022】

本発明に係る半導体装置の製造方法において、前記工程(b)は、前記半導体基板上に前記第1の金属含有導電膜を形成した後、前記第2の活性領域上の前記第1の金属含有導電膜を選択的に除去する工程を含み、前記工程(c)は、前記半導体基板上に前記第2の金属含有導電膜を形成した後、前記第1の活性領域上の前記第2の金属含有導電膜を選択的に除去する工程を含んでいてもよい。このようにすると、金属含有導電膜のパターニング時におけるゲート絶縁膜の劣化を防止することができる。

【0023】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記第3の金属含有導電膜を前記素子分離領域と接するように形成する工程を含んでいてもよい。このようにすると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、第3の金属含有導電膜を素子分離領域と接するように形成することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記工程(d)は、前記第3の金属含有導電膜を、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成する工程を含んでいてもよい。

【0024】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記第1の金属含有導電膜、前記素子分離領域及び前記第2の金属含有導電膜のそれぞれの上にシリコン膜を形成した後、前記第1の金属含有導電膜、前記第2の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜をシリサイド化して前記第3の金属含有導電膜を形成する工程を含んでいてもよい。このようにすると、MIPS構造におけるシリコンをシリサイド化することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記工程(d)は、前記第3の金属含有導電膜と前記素子分離領域との間に前記シリコン領域の一部を残存させる工程を含んでいてもよい。言い換えると、MIPS構造におけるシリコンのうち素子分離領域の直上の部分をシリサイド化しなくてもよい。

【0025】

本発明に係る半導体装置の製造方法において、前記工程(d)よりも後に、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜を形成する工程(e)をさらに備えていてもよい。すなわち、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本発明に係る半導体装置の構造を実現してもよい。尚、前記工程(e)よりも後に、前記第1の金属含有導電膜、前記第2の金属含有導電膜、前記第3の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜の表面をシリサイド化する工程をさらに備えていてもよい。

【発明の効果】

【0026】

本発明によると、第1のゲート電極と第2のゲート電極とを電気的に接続するPN境界部配線が金属を含むため、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。従って、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、PN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【発明を実施するための最良の形態】

【0027】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0028】

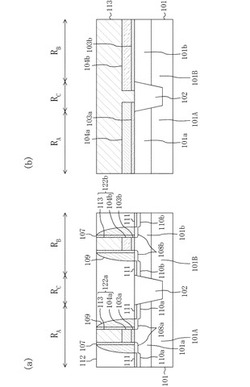

図1(a)及び(b)は、本発明の第1の実施形態に係る半導体装置の断面構成を示しており、図1(a)はゲート長方向(L方向)の断面図であり、図1(b)はゲート幅方向(W方向)の断面図である。尚、図中において、左側に示す「RA 」はNMISトランジスタが形成されるNMIS形成領域を示し、右側に示す「RB 」はPMISトランジスタが形成されるPMIS形成領域を示し、中央に示す「RC 」は素子分離領域が形成される素子分離形成領域を示している。

【0029】

図1(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC には、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102が形成されている。素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにはPウェル領域101aが形成されていると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにはNウェル領域101bが形成されている。第1の活性領域101A上には第1のゲート絶縁膜103aを介して第1のゲート電極122aが形成されていると共に、第2の活性領域101B上には第2のゲート絶縁膜103bを介して第2のゲート電極122bが形成されている。ゲート絶縁膜103a及び103bは、例えばHigh-k膜であるHfSiO膜からなる。NMISトランジスタの第1のゲート電極122aは、第1のゲート絶縁膜103a上に形成された第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタの第2のゲート電極122bは、第2のゲート絶縁膜103b上に形成された第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第1の金属含有導電膜104aは、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなり、第2の金属含有導電膜104bは、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなり、第3の金属含有導電膜113は、例えば、Ti、Ni、Co又はPtを含むシリサイドからなる。

【0030】

また、図1(a)及び(b)に示すように、ゲート電極122a及び122bのそれぞれの側面には絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109が形成されている。第1の活性領域101Aの表面部における絶縁性サイドウォールスペーサー109の下側にはN型エクステンション領域(浅いN型ソース・ドレイン領域)108aが形成されており、その外側にはN型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110aが形成されている。第2の活性領域101Bの表面部における絶縁性サイドウォールスペーサー109の下側にはP型エクステンション領域(浅いP型ソース・ドレイン領域)108bが形成されており、その外側にはP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bが形成されている。ソース・ドレイン領域110a及び110bの表面部にはシリサイド層111が形成されている。半導体基板101上の全面に、ゲート電極122a及び122bがそれぞれの上面を除いて埋まるように、層間絶縁膜112が形成されている。

【0031】

尚、図1(a)に示す本実施形態では、ゲート電極122a及び122bの上面高さは層間絶縁膜112の上面高さと同じであるが、両者は必ずしも同じ高さである必要はない。例えば、ゲート電極122a及び122bの上面高さは層間絶縁膜112の上面高さよりも高くても良い。

【0032】

本実施形態の特徴は、ゲート電極122a及び122bのそれぞれの一部となる第3の金属含有導電膜113が、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されていることである。

【0033】

尚、本実施形態において、図1(b)に示すように、W方向において、第1のゲート電極122aを構成する第1の金属含有導電膜104aは、第1の活性領域101A上及びそれに隣接する素子分離領域102の端部上に形成されており、第2のゲート電極122bを構成する第2の金属含有導電膜104bは、第2の活性領域101B上及びそれに隣接する素子分離領域102の端部上に形成されている。すなわち、W方向において、第1の活性領域101Aと第2の活性領域101Bとの間に位置する素子分離領域102上で、第1の金属含有導電膜104aと第2の金属含有導電膜104bとは分断されている。また、本実施形態において、第3の金属含有導電膜113は、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるように、言い換えると、素子分離領域102と接するように形成されている。

【0034】

以下、図1(a)及び(b)に示す本実施形態の半導体装置を製造するための方法について説明する。図2(a)〜(d)、図3(a)〜(d)、図4(a)〜(d)、図5(a)〜(d)、図6(a)〜(d)、図7(a)〜(d)、図8(a)〜(d)、図9(a)、(b)及び図10(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図2(a)、(c)、図3(a)、(c)、図4(a)、(c)、図5(a)、(c)、図6(a)、(c)、図7(a)、(c)、図8(a)、(c)、図9(a)及び図10(a)はL方向の断面図であり、図2(b)、(d)、図3(b)、(d)、図4(b)、(d)、図5(b)、(d)、図6(b)、(d)、図7(b)、(d)、図8(b)、(d)、図9(b)及び図10(b)はW方向の断面図である。

【0035】

まず、図2(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC に、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102を形成する。次に、素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにPウェル領域101aを形成すると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにNウェル領域101bを形成する。次に、半導体基板101の全面に、NMISトランジスタ用の第1のゲート絶縁膜103aとして、例えばHigh-k膜であるHfSiO膜をCVD(chemical vapor deposition )法により成膜する。

【0036】

次に、図2(c)及び(d)に示すように、第1のゲート絶縁膜103a上に、NMISトランジスタ用のメタルゲート電極として、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなる厚さ20nm程度の第1の金属含有導電膜104aを成膜する。

【0037】

次に、図3(a)及び(b)に示すように、PMIS形成領域RB に堆積されたNMISトランジスタ用の第1のゲート絶縁膜103a及び第1の金属含有導電膜104aを除去するために、第1の金属含有導電膜104a上に、第1の活性領域101A及びそれに隣接する素子分離領域102の端部を覆い且つPMIS形成領域RB が開口された厚さ40nm程度のハードマスク105aを形成する。ハードマスク105aの材料としては、金属材料を酸化させないような材料、例えばSi系の材料が好ましい。

【0038】

次に、図3(c)及び(d)に示すように、ハードマスク105aを用いて、PMIS形成領域RB の第1のゲート絶縁膜103a及び第1の金属含有導電膜104aをウェットエッチング又はドライエッチングによって除去する。このとき、第1のゲート絶縁膜103a及び第1の金属含有導電膜104aが、第1の活性領域101a上のみならず、それに隣接する素子分離領域102の端部上にも残存するように、エッチングを行う。尚、ドライエッチングを用いる場合、同一チャンバー内においてエッチャント等のエッチング条件を変えることによって第1のゲート絶縁膜103a及び第1の金属含有導電膜104aに対して連続的にエッチングを行ってもよい。

【0039】

次に、図4(a)及び(b)に示すように、半導体基板101の全面に、PMISトランジスタ用の第2のゲート絶縁膜103bとして、例えばHigh-k膜であるHfSiO膜をCVD法により成膜する。

【0040】

次に、図4(c)及び(d)に示すように、第2のゲート絶縁膜103b上に、PMISトランジスタ用のメタルゲート電極として、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなる厚さ20nm程度の第2の金属含有導電膜104bを成膜する。

【0041】

次に、図5(a)及び(b)に示すように、NMIS形成領域RA に堆積されたPMISトランジスタ用の第2のゲート絶縁膜103b及び第2の金属含有導電膜104bを除去するために、第2の金属含有導電膜104b上に、第2の活性領域101B及びそれに隣接する素子分離領域102の端部を覆い且つNMIS形成領域RA が開口された厚さ40nm程度のハードマスク105bを形成する。ハードマスク105bの材料としては、金属材料を酸化させないような材料、例えばSi系の材料が好ましい。

【0042】

次に、図5(c)及び(d)に示すように、ハードマスク105bを用いて、NMIS形成領域RA の第2のゲート絶縁膜103b及び第2の金属含有導電膜104bをウェットエッチング又はドライエッチングによって除去する。このとき、NMIS形成領域RA においてはハードマスク105aがエッチングストッパーとして機能する。また、このとき、第2のゲート絶縁膜103b及び第2の金属含有導電膜104bが、第2の活性領域101B上のみならず、それに隣接する素子分離領域102の端部上にも残存するように、エッチングを行う。これにより、第1の活性領域101Aと第2の活性領域101Bとの間に位置する素子分離領域102上において、第1の金属含有導電膜104aと第2の金属含有導電膜104bとは少なくとも所定の距離(第2のゲート絶縁膜103b及び第2の金属含有導電膜104bの合計厚さ)以上離間して形成される。尚、ドライエッチングを用いる場合、同一チャンバー内においてエッチャント等のエッチング条件を変えることによって第2のゲート絶縁膜103b及び第2の金属含有導電膜104bに対して連続的にエッチングを行ってもよい。

【0043】

尚、図3(c)及び(d)に示す工程で、PMIS形成領域RB の第1のゲート絶縁膜103aを除去せずに、これをPMISトランジスタ用のゲート絶縁膜として用いることも可能ではあるが、その場合、図4(c)及び(d)に示す工程で第2の金属含有導電膜104bを成膜した際に、PMIS形成領域RB に残存する第1のゲート絶縁膜103aの劣化は不可避である。従って、本実施形態では、各トランジスタ用にメタルゲート電極のみならずゲート絶縁膜も作り分けている。

【0044】

次に、図6(a)及び(b)に示すように、ハードマスク105a及び105bを除去した後、図6(c)及び(d)に示すように、半導体基板101上の全面に、例えば厚さ100nm程度のポリシリコン膜106を成膜する。

【0045】

次に、図7(a)及び(b)に示すように、NMIS形成領域RA のポリシリコン膜106及び第1の金属含有導電膜104a、並びにPMIS形成領域RB のポリシリコン膜106及び第2の金属含有導電膜104bをそれぞれドライエッチングによりパターニングする。これにより、第1の活性領域101A上に第1のゲート絶縁膜103aを介して、第1の金属含有導電膜104a及びポリシリコン膜106からなる第1のゲート部121aを形成すると共に、第2の活性領域101B上に第2のゲート絶縁膜103bを介して、第2の金属含有導電膜104b及びポリシリコン膜106からなる第2のゲート部121bを形成する。このとき、図7(b)に示すように、第1のゲート部121aのポリシリコン膜106と、第2のゲート部121bのポリシリコン膜106とは、素子分離領域102上に形成されたポリシリコン膜106を介して一体的に形成されている。さらに、図7(a)及び(b)に示す工程において、第1のゲート部121aの外側の第1のゲート絶縁膜103a、及び第2のゲート部121bの外側の第2のゲート絶縁膜103bがそれぞれ除去される。尚、本実施形態においては、金属含有導電膜104a及び104bの材料並びにエッチング条件を適切に選択することにより、同一チャンバー内においてポリシリコン膜106並びに金属含有導電膜104a及び104bに対して連続的にエッチングを行い、それによってゲート部121a及び121bのパターニング形成を同時に行う。

【0046】

次に、図7(c)及び(d)に示すように、ゲート部121a及び121bのそれぞれの側面上に絶縁性オフセットスペーサー107を形成した後、ゲート部121a及び121b並びに絶縁性オフセットスペーサー107をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型エクステンション領域(浅いN型ソース・ドレイン領域)108a及びP型エクステンション領域(浅いP型ソース・ドレイン領域)108bを形成する。

【0047】

次に、図8(a)及び(b)に示すように、ゲート部121a及び121bのそれぞれの側面に絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109を形成した後、ゲート部121a及び121b並びに絶縁性オフセットスペーサー107及び絶縁性サイドウォールスペーサー109をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110a及びP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bを形成する。

【0048】

次に、図8(c)及び(d)に示すように、ゲート部121a及び121bを構成するポリシリコン膜106の表面部、及びソース・ドレイン領域110a及び110bの表面部をシリサイド化してシリサイド層111を形成する。これにより、ソース・ドレイン領域110a及び110bを低抵抗化することができる。尚、本実施形態において、ゲート部121a及び121bを構成するポリシリコン膜106の表面部には、必ずしもシリサイド層111を形成する必要はない。

【0049】

次に、図9(a)及び(b)に示すように、半導体基板101上の全面に、ゲート部121a及び121bを覆うことができる厚さ(例えば200nm以上)を持つ層間絶縁膜112を成膜する。その後、図10(a)及び(b)に示すように、例えばCMP(chemical mechanical polishing )法により、ゲート部121a及び121bの表面部に設けられているシリサイド層111が露出するまで層間絶縁膜112を研磨する。このとき、ゲート部121a及び121bの表面のシリサイド層111については必ずしも残存させる必要はなく、ゲート部121a及び121bを構成するポリシリコン膜106の表面が露出するまで層間絶縁膜112を研磨してもよい。また、層間絶縁膜112を研磨する際に、CMP法に代えてドライエッチング法を用いてもよい。

【0050】

次に、ゲート部121a及び121bの上に、例えばTi、Ni、Co又はPt等からなる金属膜(図示省略)を例えば100nm程度の厚さ(ポリシリコン膜106を十分にシリサイド化することができる厚さ)で堆積した後、熱処理を行うことにより、ゲート部121a及び121bを構成するポリシリコン膜106と前記金属膜とを反応させ、その後、未反応の前記金属膜を除去した後、再度熱処理を行うことにより、シリサイドからなる第3の金属含有導電膜113を形成する。これにより、図1(a)及び(b)に示す本実施形態の半導体装置、つまり、第1の金属含有導電膜104a及び第3の金属含有導電膜113からなる第1のゲート電極122aを有するNMISトランジスタと、第2の金属含有導電膜104b及び第3の金属含有導電膜113からなる第2のゲート電極122bを有するPMISトランジスタとを備えた半導体装置が得られる。

【0051】

尚、本実施形態においては、ポリシリコン膜106を完全にシリサイド化することにより、第1の金属含有導電膜104a及び第2の金属含有導電膜104b並びに素子分離領域102のそれぞれと接するように第3の金属含有導電膜113を形成する。また、本実施形態においては、工程を簡単化するため、ゲート部121a及び121bの表面にシリサイド層111を残存させたまま、ポリシリコン膜106のシリサイド化を行うが、これによる弊害は特にない。

【0052】

最後に、図示は省略しているが、公知の技術を用いて、ゲート電極122a及び122b並びにソース・ドレイン領域110a及び110bと電気的に接続するコンタクトや配線を形成する。

【0053】

以上に説明したように、第1の実施形態によると、第1のゲート電極122aを構成する第1の金属含有導電膜104a、及び第2のゲート電極122bを構成する第2の金属含有導電膜104bのそれぞれの直上に、各ゲート電極122a及び122bの一部となる第3の金属含有導電膜113、つまりポリシリコンよりも抵抗が低い材料(シリサイド)からなる導電層が素子分離領域102を横断するように連続的に形成されている。このため、第1のゲート電極122aと第2のゲート電極122bとを電気的に接続する配線、つまり素子分離領域102上のPN境界部配線が金属(第3の金属含有導電膜113)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0054】

また、第1の実施形態によると、第3の金属含有導電膜113がシリサイドから構成されているため、MIPS構造におけるシリコンをシリサイド化することによって、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0055】

また、第1の実施形態によると、各MIS形成領域RA 及びRB においてメタルゲート電極となる金属含有導電膜104a及び104bのみならずゲート絶縁膜103a及び103bをも作り分けているので、金属含有導電膜104a及び104bのパターニング時におけるゲート絶縁膜103a及び103bの劣化を防止することができる。

【0056】

尚、第1の実施形態において、NMISトランジスタの第1のゲート電極122aを構成する第1の金属含有導電膜104aの材料として、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.55eV以下の材料を用いてよい。

【0057】

また、第1の実施形態において、PMISトランジスタの第2のゲート電極122bを構成する第2の金属含有導電膜104bの材料として、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.65eV以上の材料を用いてよい。

【0058】

また、第1の実施形態において、ゲート部121a及び121bの表面にシリサイド層111を残存させたまま、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成したが、これに代えて、CMPやエッチング等によってゲート部121a及び121bの表面のシリサイド層111を削り取ってポリシリコン膜106の表面を露出させてから、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。

【0059】

また、第1の実施形態において、ゲート部121a及び121bの表面にシリサイド層111を形成しなくてもよい。具体的には、図6(c)及び(d)に示す工程でポリシリコン膜106上にハードマスクを形成し、図7(a)及び(b)に示す工程で当該ハードマスクをポリシリコン膜106等と共にパターニングし、図8(c)及び(d)に示す工程で当該ハードマスクによってポリシリコン膜106の表面のシリサイド化を防止し、その後、当該ハードマスクを除去してから、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。

【0060】

また、第1の実施形態において、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるように、言い換えると、素子分離領域102と接するように、シリサイドからなる第3の金属含有導電膜113を形成した。しかし、これに代えて、図11(本実施形態の半導体装置におけるW方向の断面構成のバリエーション)に示すように、素子分離領域102と第3の金属含有導電膜113との間にポリシリコン膜106の一部が残存するように、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。すなわち、第3の金属含有導電膜113は、第1の金属含有導電膜104aの直上から第2の金属含有導電膜104bの直上まで連続的に形成されていれば、素子分離領域102と接していなくてもよい。言い換えると、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるポリシリコン膜106はシリサイド化されていなくてもよい。

【0061】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0062】

図12(a)及び(b)は、本発明の第2の実施形態に係る半導体装置の断面構成を示しており、図12(a)はゲート長方向(L方向)の断面図であり、図12(b)はゲート幅方向(W方向)の断面図である。

【0063】

図12(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC には、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102が形成されている。素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにはPウェル領域101aが形成されていると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにはNウェル領域101bが形成されている。第1の活性領域101A上には第1のゲート絶縁膜103aを介して第1のゲート電極132aが形成されていると共に、第2の活性領域101B上には第2のゲート絶縁膜103bを介して第2のゲート電極132bが形成されている。ゲート絶縁膜103a及び103bは、例えばHigh-k膜であるHfSiO膜からなる。NMISトランジスタの第1のゲート電極132aは、第1のゲート絶縁膜103a上に形成された第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜104cと、第3の金属含有導電膜104c上に形成されたポリシリコン膜106と、ポリシリコン膜106の表面部に形成されたシリサイド層111とから構成されている。PMISトランジスタの第2のゲート電極132bは、第2のゲート絶縁膜103b上に形成された第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜104cと、第3の金属含有導電膜104c上に形成されたポリシリコン膜106と、ポリシリコン膜106の表面部に形成されたシリサイド層111とから構成されている。第1の金属含有導電膜104aは、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなり、第2の金属含有導電膜104bは、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなる。第3の金属含有導電膜104cの材料は、ポリシリコンよりも抵抗が低い材料であれば、特に限定されないが、例えば、第1の金属含有導電膜104a又は第2の金属含有導電膜104bと同様の高融点金属含有材料を用いることができる。

【0064】

また、図12(a)及び(b)に示すように、ゲート電極132a及び132bのそれぞれの側面には絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109が形成されている。第1の活性領域101Aの表面部における絶縁性サイドウォールスペーサー109の下側にはN型エクステンション領域(浅いN型ソース・ドレイン領域)108aが形成されており、その外側にはN型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110aが形成されている。第2の活性領域101Bの表面部における絶縁性サイドウォールスペーサー109の下側にはP型エクステンション領域(浅いソP型ース・ドレイン領域)108bが形成されており、その外側にはP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bが形成されている。ソース・ドレイン領域110a及び110bの表面部にはシリサイド層111が形成されている。半導体基板101上の全面に、ゲート電極132a及び132bが埋まるように、層間絶縁膜112が形成されている。

【0065】

本実施形態の特徴は、ゲート電極132a及び132bのそれぞれの一部となる第3の金属含有導電膜104cが、第1の金属含有導電膜104a、第2の金属含有導電膜104b及び素子分離領域102のそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されていることである。

【0066】

尚、本実施形態において、図12(b)に示すように、W方向において、第1のゲート電極132aを構成する第1の金属含有導電膜104aは、第1の活性領域101A上及びそれに隣接する素子分離領域102の端部上に形成されており、第2のゲート電極132bを構成する第2の金属含有導電膜104bは、第2の活性領域101B上及びそれに隣接する素子分離領域102の端部上に形成されている。すなわち、W方向においては、素子分離領域102上で第1の金属含有導電膜104aと第2の金属含有導電膜104bとは分断されている。また、本実施形態においては、第3の金属含有導電膜104cは、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペース内に凹部が残るように形成されており、当該凹部を埋めるようにポリシリコン膜106がさらに形成されている。

【0067】

以下、図12(a)及び(b)に示す本実施形態の半導体装置を製造するための方法について説明する。図13(a)〜(d)、図14(a)〜(d)及び図15(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図13(a)、(c)、図14(a)、(c)及び図15(a)、(c)はL方向の断面図であり、図13(b)、(d)、図14(b)、(d)及び図15(b)、(d)はW方向の断面図である。

【0068】

まず、本実施形態においては、図2(a)〜(d)、図3(a)〜(d)、図4(a)〜(d)及び図5(a)〜(d)に示す第1の実施形態に係る半導体装置の製造方法の各工程を実施した後、図13(a)及び(b)に示すように、ハードマスク105a及び105bを除去する。これにより、NMIS形成領域RA の第1の活性領域101A上に第1のゲート絶縁膜103aを介して第1の金属含有導電膜104aが形成されると共に、PMIS形成領域RB の第2の活性領域101B上に第2のゲート絶縁膜103bを介して第2の金属含有導電膜104bが形成される。

【0069】

次に、図13(c)及び(d)に示すように、半導体基板101上の全面に、例えば金属含有導電膜104a又は104bと同様の高融点金属含有材料からなる厚さ10nm程度の第3の金属含有導電膜104cを成膜した後、第3の金属含有導電膜104c上に例えば厚さ100nm程度のポリシリコン膜106を成膜する。

【0070】

次に、図14(a)及び(b)に示すように、NMIS形成領域RA のポリシリコン膜106、第3の金属含有導電膜104c及び第1の金属含有導電膜104a、並びにPMIS形成領域RB のポリシリコン膜106、第3の金属含有導電膜104c及び第2の金属含有導電膜104bをそれぞれドライエッチングによりパターニングする。これにより、第1の活性領域101A上に第1のゲート絶縁膜103aを介して、第1の金属含有導電膜104a、第3の金属含有誘電膜104c及びポリシリコン膜106からなる第1のゲート部131aを形成すると共に、第2の活性領域101B上に第2のゲート絶縁膜103bを介して、第2の金属含有導電膜104b、第3の金属含有誘電膜104c及びポリシリコン膜106からなる第2のゲート部131bを形成する。このとき、図14(b)に示すように、第1のゲート部121aを構成する第3の金属含有誘電膜104c及びポリシリコン膜106と、第2のゲート部121bを構成する第3の金属含有誘電膜104c及びポリシリコン膜106とは、素子分離領域102上に形成された第3の金属含有誘電膜104c及びポリシリコン膜106を介して一体的に形成されている。さらに、図14(a)及び(b)に示す工程において、第1のゲート部131aの外側の第1のゲート絶縁膜103a、及び第2のゲート部131bの外側の第2のゲート絶縁膜103bがそれぞれ除去される。尚、本実施形態においては、金属含有導電膜104a及び104bの材料並びにエッチング条件を適切に選択することにより、同一チャンバー内においてポリシリコン膜106、第3の金属含有導電膜104c並びに第1及び第2の金属含有導電膜104a及び104bに対して連続的にエッチングを行い、それによってゲート部131a及び131bのパターニング形成を同時に行う。

【0071】

次に、図14(c)及び(d)に示すように、ゲート部131a及び131bのそれぞれの側面上に絶縁性オフセットスペーサー107を形成した後、第1のゲート部131a及び131b並びに絶縁性オフセットスペーサー107をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型エクステンション領域(浅いN型ソース・ドレイン領域)108a及びP型エクステンション領域(浅いP型ソース・ドレイン領域)108bを形成する。

【0072】

次に、図15(a)及び(b)に示すように、ゲート部131a及び131bのそれぞれの側面上に絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109を形成した後、ゲート部131a及び131b並びに絶縁性オフセットスペーサー107及び絶縁性サイドウォールスペーサー109をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110a及びP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bを形成する。

【0073】

次に、図15(c)及び(d)に示すように、ゲート部131a及び131bを構成するポリシリコン膜106の表面部、及びソース・ドレイン領域110a及び110bの表面部をシリサイド化してシリサイド層111を形成する。これによって、ポリシリコン膜106上にシリサイド層111が形成された第1のゲート電極132a及び第2のゲート電極132bが形成されると共に、ゲート電極132a及び132b並びにソース・ドレイン領域110a及び110bを低抵抗化することができる。

【0074】

次に、半導体基板101上の全面に、ゲート電極132a及び132bを覆うことができる厚さ(例えば200nm以上の厚さ)を持つ層間絶縁膜112を成膜する。これにより、図12(a)及び(b)に示す本実施形態の半導体装置、つまり、第1の金属含有導電膜104a、第3の金属含有導電膜104c、ポリシリコン膜106及びシリサイド層111からなる第1のゲート電極132aを有するNMISトランジスタと、第2の金属含有導電膜104b、第3の金属含有導電膜104c、ポリシリコン膜106及びシリサイド層111からなる第2のゲート電極132bを有するPMISトランジスタとを備えた半導体装置が得られる。

【0075】

最後に、図示は省略しているが、公知の技術を用いて、ゲート電極132a及び132b並びにソース・ドレイン領域110a及び110bと電気的に接続するコンタクトや配線を形成する。

【0076】

以上に説明したように、第2の実施形態によると、第1のゲート電極132aを構成する第1の金属含有導電膜104a、及び第2のゲート電極132bを構成する第2の金属含有導電膜104bのそれぞれの直上に、各ゲート電極132a及び132bの一部となる第3の金属含有導電膜104c、つまりポリシリコンよりも抵抗が低い材料からなる導電層が素子分離領域102を横断するように連続的に形成されている。このため、第1のゲート電極132aと第2のゲート電極132bとを電気的に接続する配線、つまり素子分離領域102上のPN境界部配線が金属(第3の金属含有導電膜104c)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0077】

また、第2の実施形態によると、第1のゲート電極132aを構成する第1の金属含有導電膜104a、及び第2のゲート電極132bを構成する第2の金属含有導電膜104bのそれぞれの直上に、第3の金属含有導電膜104cを素子分離領域102と接するように形成することによって、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0078】

また、第2の実施形態によると、第3の金属含有導電膜104c上に、第1のゲート電極132a及び第2のゲート電極132bのそれぞれの一部となるポリシリコン膜106がさらに形成されているため、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0079】

また、第2の実施形態によると、各MIS形成領域RA 及びRB においてメタルゲート電極となる金属含有導電膜104a及び104bのみならずゲート絶縁膜103a及び103bをも作り分けているので、金属含有導電膜104a及び104bのパターニング時におけるゲート絶縁膜103a及び103bの劣化を防止することができる。

【0080】

尚、第2の実施形態において、NMISトランジスタの第1のゲート電極132aを構成する第1の金属含有導電膜104aの材料として、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.55eV以下の材料を用いてよい。

【0081】

また、第2の実施形態において、PMISトランジスタの第2のゲート電極132bを構成する第2の金属含有導電膜104bの材料として、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.65eV以上の材料を用いてよい。

【0082】

また、第2の実施形態において、PN境界部配線を含むゲート電極132a及び132b中に第3の金属含有導電膜104cを連続的に形成しているため、ゲート電極132a及び132bを構成するポリシリコン膜106の表面部のみをシリサイド化してシリサイド層111を形成した。しかし、これに代えて、ポリシリコン膜106を完全にシリサイド化してもよい。

【0083】

また、第2の実施形態において、第3の金属含有導電膜104cを、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペース内に凹部が残るように、比較的薄く形成した。しかし、これに代えて、図16(本実施形態の半導体装置におけるW方向の断面構成のバリエーション)に示すように、第3の金属含有導電膜104cを、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースが埋まるように、比較的厚く形成してもよい。但し、第3の金属含有導電膜104cを薄く形成した方が、図14(a)及び(b)に示すゲート部131a及び131bのパターニング形成工程で第3の金属含有導電膜104cの加工が容易になるというメリットが得られる。

【産業上の利用可能性】

【0084】

以上に説明したように、半導体装置及びその製造方法に関し、特にMIPS構造のDMGプロセスに適用した場合には、PN境界部配線の高抵抗化に起因する断線等の問題を防止することができ、非常に有用である。

【図面の簡単な説明】

【0085】

【図1】図1(a)及び(b)は、本発明の第1の実施形態に係る半導体装置の断面構成を示しており、図1(a)はゲート長方向(L方向)の断面図であり、図1(b)はゲート幅方向(W方向)の断面図である。

【図2】図2(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図2(a)、(c)はL方向の断面図であり、図2(b)、(d)はW方向の断面図である。

【図3】図3(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図3(a)、(c)はL方向の断面図であり、図3(b)、(d)はW方向の断面図である。

【図4】図4(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図4(a)、(c)はL方向の断面図であり、図4(b)、(d)はW方向の断面図である。

【図5】図5(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図5(a)、(c)はL方向の断面図であり、図5(b)、(d)はW方向の断面図である。

【図6】図6(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図6(a)、(c)はL方向の断面図であり、図6(b)、(d)はW方向の断面図である。

【図7】図7(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図7(a)、(c)はL方向の断面図であり、図7(b)、(d)はW方向の断面図である。

【図8】図8(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図8(a)、(c)はL方向の断面図であり、図8(b)、(d)はW方向の断面図である。

【図9】図9(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図9(a)はL方向の断面図であり、図9(b)はW方向の断面図である。

【図10】図10(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図10(a)はL方向の断面図であり、図10(b)はW方向の断面図である。

【図11】図11は、本発明の第1の実施形態に係る半導体装置におけるW方向の断面構成のバリエーションを示す図である。

【図12】図12(a)及び(b)は、本発明の第2の実施形態に係る半導体装置の断面構成を示しており、図12(a)はL方向の断面図であり、図12(b)はW方向の断面図である。

【図13】図13(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図13(a)、(c)はL方向の断面図であり、図13(b)、(d)はW方向の断面図である。

【図14】図14(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図14(a)、(c)はL方向の断面図であり、図14(b)、(d)はW方向の断面図である。

【図15】図15(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図15(a)、(c)はL方向の断面図であり、図15(b)、(d)はW方向の断面図である。

【図16】図16は、本発明の第2の実施形態に係る半導体装置におけるW方向の断面構成のバリエーションを示す図である。

【図17】非特許文献1に開示されているMIPS構造のDMGを備えた半導体装置の断面図である。

【符号の説明】

【0086】

101 半導体基板

101A 第1の活性領域

101B 第2の活性領域

101a Pウェル領域

101b Nウェル領域

102 素子分離領域

103a 第1のゲート絶縁膜

103b 第2のゲート絶縁膜

104a 第1の金属含有導電膜

104b 第2の金属含有導電膜

104c 第3の金属含有導電膜

105a、105b ハードマスク

106 ポリシリコン膜

107 絶縁性オフセットスペーサー

108a N型エクステンション領域

108b P型エクステンション領域

109 絶縁性サイドウォールスペーサー

110a N型ソース・ドレイン領域

110b P型ソース・ドレイン領域

111 シリサイド層

112 層間絶縁膜

113 第3の金属含有導電膜

121a 第1のゲート部

121b 第2のゲート部

122a 第1のゲート電極

122b 第2のゲート電極

131a 第1のゲート部

131b 第2のゲート部

132a 第1のゲート電極

132b 第2のゲート電極

RA NMIS形成領域

RB PMIS形成領域

RC 素子分離形成領域

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特にMIPS(Metal inserted Poly-Si Stack)構造のDMG(Dual Metal Gate )プロセスにおいて、ゲート電極等の配線の配線幅を太くする等により高集積化を妨げることなく、金属シリサイド膜のPN境界における断線等に起因する配線の高抵抗化を抑制することを目的とした有効な半導体製造技術に関するものである。

【背景技術】

【0002】

近年、半導体装置の高集積化、微細化に伴い、トランジスタにおいても微細化が急速に進められている。これに伴って、トランジスタのゲート絶縁膜においては、薄膜化が進んでいる。ところが、従来のSiO2 やSiONからなるゲート絶縁膜を薄膜化すると、ゲートリーク電流の値が無視できないほど増大してしまう。そこで、ゲート絶縁膜として、高誘電率膜(以下、High-k膜と称する)を用いることが検討されている。比誘電率の高いHigh-k膜をゲート絶縁膜として用いる場合、実際の物理膜厚を厚く確保してトンネル電流を抑えつつ、EOT(等価酸化膜厚)を薄くしてトランジスタの高駆動力化、低消費電力化を実現することができる。

【0003】

一方、ゲート電極においては、トランジスタの微細化に伴い、電極の空乏化に起因する容量の低下が問題となる。ゲート電極材料として、従来のようにポリシリコンを用いた場合、この容量の低下は、シリコン酸化膜の膜厚に換算して約0.4nmの増大に相当する。この値は、薄膜化が求められているゲート絶縁膜の膜厚と比較すると、無視できない大きさである。そこで、ゲート電極においては、従来のポリシリコンに代えて、メタルを用いることが考えられている。メタルゲート電極を用いる場合、前述のようなゲート空乏化の問題を抑えることができる。しかしながら、High-kゲート絶縁膜にメタルゲート電極を適用するためには、N型MIS(metal-insulator-semiconductor )トランジスタ(以下「NMISトランジスタ」又は「NMIS」と称する)及びP型MISトランジスタ(以下「PMISトランジスタ」又は「PMIS」と称する)のそれぞれについて適切なメタル材料を選定する必要がある。

【0004】

メタルゲートプロセスは、ゲートファーストプロセス及びゲートラストプロセスの2種類に大きく分けることができる。ゲートファーストプロセスにおいては、ゲート電極を形成した後に、イオン注入や熱処理等を含むトランジスタ形成工程を行う。これに対して、ゲートラストプロセスにおいては、ダミーゲートを用いてトランジスタを形成した後に、ダミーゲートを除去してゲート電極を形成するため、ゲートファーストプロセスと比較して、より難易度が高いプロセスとなる。このため、現在、ゲートファーストプロセスを用いたメタルゲート電極形成の検討が行われている。尚、ゲートファーストプロセスにおいては、ゲート加工性やCMOS(complementary-metal-oxide-semiconductor )プロセスとの整合性等を考慮して、一般的にMIPS構造が用いられている。

【0005】

以上のように、次世代のプロセスとして、High-kゲート絶縁膜とMIPS構造のDMGとを適用することが検討されている(例えば非特許文献1参照)。

【0006】

図17は、非特許文献1に開示されているMIPS構造のDMGを備えた半導体装置の断面図、具体的には、ゲート幅方向(W方向)のトランジスタの断面図を示す。図17に示すように、半導体基板1における素子分離形成領域RC には、NMIS形成領域RA の半導体基板1からなる第1の活性領域1AとPMIS形成領域RB の半導体基板1からなる第2の活性領域1Bとを区画するSTI(shallow trench isolation)からなる素子分離領域2が形成されている。素子分離領域2に囲まれたNMIS形成領域RA の第1の活性領域1AにはPウェル領域1aが形成されていると共に、素子分離領域2に囲まれたPMIS形成領域RB の第2の活性領域1BにはNウェル領域1bが形成されている。第1の活性領域1A上にはゲート絶縁膜3aを介してメタルゲート電極4aが形成されている。第2の活性領域1B上にはゲート絶縁膜3bを介してメタルゲート電極4bが形成されている。メタルゲート電極4a及び4bの上並びに当該両電極の間に位置する素子分離領域2の上にはポリシリコン膜6が連続的に形成されている。尚、ポリシリコン膜6は、メタルゲート電極4a及び4bを電気的に接続する配線部分を含むゲート電極形状に加工されている。また、ポリシリコン膜6の表面はシリサイド化されており、それによってシリサイド層7が形成されている。また、図示していないが、イオン注入工程や熱処理工程等によって各MIS形成領域RA 及びRB にはソース・ドレイン領域等の不純物領域が形成されており、それによってトランジスタ構造が構成されている。

【非特許文献1】S.C.Song他、Highly Manufacturable 45nm LSTP CMOSFETs Using Novel Dual High-k and Dual Metal Gate CMOS Integration、VLSI Techonology、2006年8月6日、P.16

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、前述の非特許文献1に開示されているMIPS構造のDMGによると、PMISトランジスタのゲート電極とNMISトランジスタのゲート電極とを電気的に接続する配線、つまりPN境界部配線において金属を含まない領域が存在するため、高抵抗化したり、断線したりする等の問題が生じる。具体的には、NMIS形成領域においてはNMIS用のメタルゲート電極(メタルゲート電極4a)が存在し、PMIS形成領域にはPMIS用のメタルゲート電極(メタルゲート電極4b)が存在している一方、当該両MIS形成領域の境界においてはNMIS用のメタルもPMIS用のメタルもそれぞれのパターニング工程によって除去されている。その結果、図17に示すように、電流8は相対的に抵抗の低い箇所を流れるため、PN境界部配線(金属を含まない領域)においては、ポリシリコン膜6の最表面のシリサイド層7に電流が集中して流れるので、シリサイド層7が断線したり、それに起因して配線の高抵抗化が生じたりする。

【0008】

尚、前述のような問題を防止するために、従来、PN境界部配線の配線幅を太くする等の対策が取られているが、これは高集積化の妨げとなる。

【0009】

前記に鑑み、本発明は、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するために、本願発明者らは、種々の検討を重ねた結果、MIPS構造のDMGを有する半導体装置において、NMIS用のメタルゲート電極及びPMIS用のメタルゲート電極のそれぞれの直上に、ポリシリコンよりも抵抗が低い材料からなる導電層を連続的に形成するという発明を想到した。

【0011】

具体的には、本発明に係る半導体装置は、半導体基板における第1の活性領域上に形成され且つ第1の金属含有導電膜を有する第1のゲート電極と、前記半導体基板における第2の活性領域上に形成され且つ第2の金属含有導電膜を有する第2のゲート電極と、前記第1の活性領域と前記第2の活性領域とを区画するように前記半導体基板に形成された素子分離領域とを備え、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されており、前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜が連続的に形成されており、前記第3の金属含有導電膜は、前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接している。

【0012】

本発明に係る半導体装置によると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、各ゲート電極の一部となる第3の金属含有導電膜、つまりポリシリコンよりも抵抗が低い材料からなる導電層が素子分離領域を横断するように連続的に形成されている。このため、第1のゲート電極と第2のゲート電極とを電気的に接続する配線、つまり素子分離領域上のPN境界部配線が金属(第3の金属含有導電膜)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0013】

本発明に係る半導体装置において、前記第3の金属含有導電膜は前記素子分離領域と接していてもよい。このようにすると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、第3の金属含有導電膜を素子分離領域と接するように形成することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記第3の金属含有導電膜は、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成されていてもよい。

【0014】

本発明に係る半導体装置において、前記第3の金属含有導電膜と前記素子分離領域との間にはシリコン領域が介在していてもよい。すなわち、MIPS構造におけるシリコンのうち素子分離領域の直上の部分はシリサイド化されていなくてもよい。

【0015】

本発明に係る半導体装置において、前記第3の金属含有導電膜はシリサイドから構成されていてもよい。このようにすると、MIPS構造におけるシリコンをシリサイド化することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記シリサイドはTi、Ni、Co又はPtを含んでいてもよい。

【0016】

本発明に係る半導体装置において、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜がさらに形成されていてもよい。すなわち、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本発明に係る半導体装置の構造を実現してもよい。尚、前記シリコン膜の表面はシリサイド化されていてもよい。

【0017】

本発明に係る半導体装置において、前記第1の活性領域と前記第1のゲート電極との間に形成された第1の高誘電率ゲート絶縁膜と、前記第2の活性領域と前記第2のゲート電極との間に形成された第2の高誘電率ゲート絶縁膜とをさらに備えていてもよい。尚、本願において、高誘電率ゲート絶縁膜とは、誘電率がSiONよりも高いゲート絶縁膜、例えばHf系やZr系の元素を含むゲート絶縁膜を意味する。

【0018】

本発明に係る半導体装置において、前記第1のゲート電極がN型MISトランジスタのゲート電極である場合には、前記第1の金属含有導電膜は、仕事関数が4.55eV以下の材料、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなることが好ましい。

【0019】

本発明に係る半導体装置において、前記第2のゲート電極がP型MISトランジスタのゲート電極である場合には、前記第2の金属含有導電膜は、仕事関数が4.65eV以上の材料、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなることが好ましい。

【0020】

本発明に係る半導体装置の製造方法は、半導体基板における第1の活性領域と第2の活性領域とを区画するように、前記半導体基板に素子分離領域を形成する工程(a)と、前記第1の活性領域上に、第1のゲート電極の一部となる第1の金属含有導電膜を形成する工程(b)と、前記第2の活性領域上に、第2のゲート電極の一部となる第2の金属含有導電膜を形成する工程(c)と、前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜を前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接するように連続的に形成する工程(d)とを備え、前記工程(d)において、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されている。

【0021】

本発明に係る半導体装置の製造方法によると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、各ゲート電極の一部となる第3の金属含有導電膜、つまりポリシリコンよりも抵抗が低い材料からなる導電層を素子分離領域を横断するように連続的に形成する。このため、第1のゲート電極と第2のゲート電極とを電気的に接続する配線、つまり素子分離領域上のPN境界部配線が金属(第3の金属含有導電膜)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0022】

本発明に係る半導体装置の製造方法において、前記工程(b)は、前記半導体基板上に前記第1の金属含有導電膜を形成した後、前記第2の活性領域上の前記第1の金属含有導電膜を選択的に除去する工程を含み、前記工程(c)は、前記半導体基板上に前記第2の金属含有導電膜を形成した後、前記第1の活性領域上の前記第2の金属含有導電膜を選択的に除去する工程を含んでいてもよい。このようにすると、金属含有導電膜のパターニング時におけるゲート絶縁膜の劣化を防止することができる。

【0023】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記第3の金属含有導電膜を前記素子分離領域と接するように形成する工程を含んでいてもよい。このようにすると、第1のゲート電極を構成する第1の金属含有導電膜、及び第2のゲート電極を構成する第2の金属含有導電膜のそれぞれの直上に、第3の金属含有導電膜を素子分離領域と接するように形成することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記工程(d)は、前記第3の金属含有導電膜を、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成する工程を含んでいてもよい。

【0024】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記第1の金属含有導電膜、前記素子分離領域及び前記第2の金属含有導電膜のそれぞれの上にシリコン膜を形成した後、前記第1の金属含有導電膜、前記第2の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜をシリサイド化して前記第3の金属含有導電膜を形成する工程を含んでいてもよい。このようにすると、MIPS構造におけるシリコンをシリサイド化することによって、本発明に係る半導体装置の構造を簡単に得ることができる。この場合、前記工程(d)は、前記第3の金属含有導電膜と前記素子分離領域との間に前記シリコン領域の一部を残存させる工程を含んでいてもよい。言い換えると、MIPS構造におけるシリコンのうち素子分離領域の直上の部分をシリサイド化しなくてもよい。

【0025】

本発明に係る半導体装置の製造方法において、前記工程(d)よりも後に、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜を形成する工程(e)をさらに備えていてもよい。すなわち、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本発明に係る半導体装置の構造を実現してもよい。尚、前記工程(e)よりも後に、前記第1の金属含有導電膜、前記第2の金属含有導電膜、前記第3の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜の表面をシリサイド化する工程をさらに備えていてもよい。

【発明の効果】

【0026】

本発明によると、第1のゲート電極と第2のゲート電極とを電気的に接続するPN境界部配線が金属を含むため、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。従って、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、PN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【発明を実施するための最良の形態】

【0027】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0028】

図1(a)及び(b)は、本発明の第1の実施形態に係る半導体装置の断面構成を示しており、図1(a)はゲート長方向(L方向)の断面図であり、図1(b)はゲート幅方向(W方向)の断面図である。尚、図中において、左側に示す「RA 」はNMISトランジスタが形成されるNMIS形成領域を示し、右側に示す「RB 」はPMISトランジスタが形成されるPMIS形成領域を示し、中央に示す「RC 」は素子分離領域が形成される素子分離形成領域を示している。

【0029】

図1(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC には、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102が形成されている。素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにはPウェル領域101aが形成されていると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにはNウェル領域101bが形成されている。第1の活性領域101A上には第1のゲート絶縁膜103aを介して第1のゲート電極122aが形成されていると共に、第2の活性領域101B上には第2のゲート絶縁膜103bを介して第2のゲート電極122bが形成されている。ゲート絶縁膜103a及び103bは、例えばHigh-k膜であるHfSiO膜からなる。NMISトランジスタの第1のゲート電極122aは、第1のゲート絶縁膜103a上に形成された第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタの第2のゲート電極122bは、第2のゲート絶縁膜103b上に形成された第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第1の金属含有導電膜104aは、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなり、第2の金属含有導電膜104bは、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなり、第3の金属含有導電膜113は、例えば、Ti、Ni、Co又はPtを含むシリサイドからなる。

【0030】

また、図1(a)及び(b)に示すように、ゲート電極122a及び122bのそれぞれの側面には絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109が形成されている。第1の活性領域101Aの表面部における絶縁性サイドウォールスペーサー109の下側にはN型エクステンション領域(浅いN型ソース・ドレイン領域)108aが形成されており、その外側にはN型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110aが形成されている。第2の活性領域101Bの表面部における絶縁性サイドウォールスペーサー109の下側にはP型エクステンション領域(浅いP型ソース・ドレイン領域)108bが形成されており、その外側にはP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bが形成されている。ソース・ドレイン領域110a及び110bの表面部にはシリサイド層111が形成されている。半導体基板101上の全面に、ゲート電極122a及び122bがそれぞれの上面を除いて埋まるように、層間絶縁膜112が形成されている。

【0031】

尚、図1(a)に示す本実施形態では、ゲート電極122a及び122bの上面高さは層間絶縁膜112の上面高さと同じであるが、両者は必ずしも同じ高さである必要はない。例えば、ゲート電極122a及び122bの上面高さは層間絶縁膜112の上面高さよりも高くても良い。

【0032】

本実施形態の特徴は、ゲート電極122a及び122bのそれぞれの一部となる第3の金属含有導電膜113が、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されていることである。

【0033】

尚、本実施形態において、図1(b)に示すように、W方向において、第1のゲート電極122aを構成する第1の金属含有導電膜104aは、第1の活性領域101A上及びそれに隣接する素子分離領域102の端部上に形成されており、第2のゲート電極122bを構成する第2の金属含有導電膜104bは、第2の活性領域101B上及びそれに隣接する素子分離領域102の端部上に形成されている。すなわち、W方向において、第1の活性領域101Aと第2の活性領域101Bとの間に位置する素子分離領域102上で、第1の金属含有導電膜104aと第2の金属含有導電膜104bとは分断されている。また、本実施形態において、第3の金属含有導電膜113は、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるように、言い換えると、素子分離領域102と接するように形成されている。

【0034】

以下、図1(a)及び(b)に示す本実施形態の半導体装置を製造するための方法について説明する。図2(a)〜(d)、図3(a)〜(d)、図4(a)〜(d)、図5(a)〜(d)、図6(a)〜(d)、図7(a)〜(d)、図8(a)〜(d)、図9(a)、(b)及び図10(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図2(a)、(c)、図3(a)、(c)、図4(a)、(c)、図5(a)、(c)、図6(a)、(c)、図7(a)、(c)、図8(a)、(c)、図9(a)及び図10(a)はL方向の断面図であり、図2(b)、(d)、図3(b)、(d)、図4(b)、(d)、図5(b)、(d)、図6(b)、(d)、図7(b)、(d)、図8(b)、(d)、図9(b)及び図10(b)はW方向の断面図である。

【0035】

まず、図2(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC に、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102を形成する。次に、素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにPウェル領域101aを形成すると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにNウェル領域101bを形成する。次に、半導体基板101の全面に、NMISトランジスタ用の第1のゲート絶縁膜103aとして、例えばHigh-k膜であるHfSiO膜をCVD(chemical vapor deposition )法により成膜する。

【0036】

次に、図2(c)及び(d)に示すように、第1のゲート絶縁膜103a上に、NMISトランジスタ用のメタルゲート電極として、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなる厚さ20nm程度の第1の金属含有導電膜104aを成膜する。

【0037】

次に、図3(a)及び(b)に示すように、PMIS形成領域RB に堆積されたNMISトランジスタ用の第1のゲート絶縁膜103a及び第1の金属含有導電膜104aを除去するために、第1の金属含有導電膜104a上に、第1の活性領域101A及びそれに隣接する素子分離領域102の端部を覆い且つPMIS形成領域RB が開口された厚さ40nm程度のハードマスク105aを形成する。ハードマスク105aの材料としては、金属材料を酸化させないような材料、例えばSi系の材料が好ましい。

【0038】

次に、図3(c)及び(d)に示すように、ハードマスク105aを用いて、PMIS形成領域RB の第1のゲート絶縁膜103a及び第1の金属含有導電膜104aをウェットエッチング又はドライエッチングによって除去する。このとき、第1のゲート絶縁膜103a及び第1の金属含有導電膜104aが、第1の活性領域101a上のみならず、それに隣接する素子分離領域102の端部上にも残存するように、エッチングを行う。尚、ドライエッチングを用いる場合、同一チャンバー内においてエッチャント等のエッチング条件を変えることによって第1のゲート絶縁膜103a及び第1の金属含有導電膜104aに対して連続的にエッチングを行ってもよい。

【0039】

次に、図4(a)及び(b)に示すように、半導体基板101の全面に、PMISトランジスタ用の第2のゲート絶縁膜103bとして、例えばHigh-k膜であるHfSiO膜をCVD法により成膜する。

【0040】

次に、図4(c)及び(d)に示すように、第2のゲート絶縁膜103b上に、PMISトランジスタ用のメタルゲート電極として、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなる厚さ20nm程度の第2の金属含有導電膜104bを成膜する。

【0041】

次に、図5(a)及び(b)に示すように、NMIS形成領域RA に堆積されたPMISトランジスタ用の第2のゲート絶縁膜103b及び第2の金属含有導電膜104bを除去するために、第2の金属含有導電膜104b上に、第2の活性領域101B及びそれに隣接する素子分離領域102の端部を覆い且つNMIS形成領域RA が開口された厚さ40nm程度のハードマスク105bを形成する。ハードマスク105bの材料としては、金属材料を酸化させないような材料、例えばSi系の材料が好ましい。

【0042】

次に、図5(c)及び(d)に示すように、ハードマスク105bを用いて、NMIS形成領域RA の第2のゲート絶縁膜103b及び第2の金属含有導電膜104bをウェットエッチング又はドライエッチングによって除去する。このとき、NMIS形成領域RA においてはハードマスク105aがエッチングストッパーとして機能する。また、このとき、第2のゲート絶縁膜103b及び第2の金属含有導電膜104bが、第2の活性領域101B上のみならず、それに隣接する素子分離領域102の端部上にも残存するように、エッチングを行う。これにより、第1の活性領域101Aと第2の活性領域101Bとの間に位置する素子分離領域102上において、第1の金属含有導電膜104aと第2の金属含有導電膜104bとは少なくとも所定の距離(第2のゲート絶縁膜103b及び第2の金属含有導電膜104bの合計厚さ)以上離間して形成される。尚、ドライエッチングを用いる場合、同一チャンバー内においてエッチャント等のエッチング条件を変えることによって第2のゲート絶縁膜103b及び第2の金属含有導電膜104bに対して連続的にエッチングを行ってもよい。

【0043】

尚、図3(c)及び(d)に示す工程で、PMIS形成領域RB の第1のゲート絶縁膜103aを除去せずに、これをPMISトランジスタ用のゲート絶縁膜として用いることも可能ではあるが、その場合、図4(c)及び(d)に示す工程で第2の金属含有導電膜104bを成膜した際に、PMIS形成領域RB に残存する第1のゲート絶縁膜103aの劣化は不可避である。従って、本実施形態では、各トランジスタ用にメタルゲート電極のみならずゲート絶縁膜も作り分けている。

【0044】

次に、図6(a)及び(b)に示すように、ハードマスク105a及び105bを除去した後、図6(c)及び(d)に示すように、半導体基板101上の全面に、例えば厚さ100nm程度のポリシリコン膜106を成膜する。

【0045】

次に、図7(a)及び(b)に示すように、NMIS形成領域RA のポリシリコン膜106及び第1の金属含有導電膜104a、並びにPMIS形成領域RB のポリシリコン膜106及び第2の金属含有導電膜104bをそれぞれドライエッチングによりパターニングする。これにより、第1の活性領域101A上に第1のゲート絶縁膜103aを介して、第1の金属含有導電膜104a及びポリシリコン膜106からなる第1のゲート部121aを形成すると共に、第2の活性領域101B上に第2のゲート絶縁膜103bを介して、第2の金属含有導電膜104b及びポリシリコン膜106からなる第2のゲート部121bを形成する。このとき、図7(b)に示すように、第1のゲート部121aのポリシリコン膜106と、第2のゲート部121bのポリシリコン膜106とは、素子分離領域102上に形成されたポリシリコン膜106を介して一体的に形成されている。さらに、図7(a)及び(b)に示す工程において、第1のゲート部121aの外側の第1のゲート絶縁膜103a、及び第2のゲート部121bの外側の第2のゲート絶縁膜103bがそれぞれ除去される。尚、本実施形態においては、金属含有導電膜104a及び104bの材料並びにエッチング条件を適切に選択することにより、同一チャンバー内においてポリシリコン膜106並びに金属含有導電膜104a及び104bに対して連続的にエッチングを行い、それによってゲート部121a及び121bのパターニング形成を同時に行う。

【0046】

次に、図7(c)及び(d)に示すように、ゲート部121a及び121bのそれぞれの側面上に絶縁性オフセットスペーサー107を形成した後、ゲート部121a及び121b並びに絶縁性オフセットスペーサー107をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型エクステンション領域(浅いN型ソース・ドレイン領域)108a及びP型エクステンション領域(浅いP型ソース・ドレイン領域)108bを形成する。

【0047】

次に、図8(a)及び(b)に示すように、ゲート部121a及び121bのそれぞれの側面に絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109を形成した後、ゲート部121a及び121b並びに絶縁性オフセットスペーサー107及び絶縁性サイドウォールスペーサー109をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110a及びP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bを形成する。

【0048】

次に、図8(c)及び(d)に示すように、ゲート部121a及び121bを構成するポリシリコン膜106の表面部、及びソース・ドレイン領域110a及び110bの表面部をシリサイド化してシリサイド層111を形成する。これにより、ソース・ドレイン領域110a及び110bを低抵抗化することができる。尚、本実施形態において、ゲート部121a及び121bを構成するポリシリコン膜106の表面部には、必ずしもシリサイド層111を形成する必要はない。

【0049】

次に、図9(a)及び(b)に示すように、半導体基板101上の全面に、ゲート部121a及び121bを覆うことができる厚さ(例えば200nm以上)を持つ層間絶縁膜112を成膜する。その後、図10(a)及び(b)に示すように、例えばCMP(chemical mechanical polishing )法により、ゲート部121a及び121bの表面部に設けられているシリサイド層111が露出するまで層間絶縁膜112を研磨する。このとき、ゲート部121a及び121bの表面のシリサイド層111については必ずしも残存させる必要はなく、ゲート部121a及び121bを構成するポリシリコン膜106の表面が露出するまで層間絶縁膜112を研磨してもよい。また、層間絶縁膜112を研磨する際に、CMP法に代えてドライエッチング法を用いてもよい。

【0050】

次に、ゲート部121a及び121bの上に、例えばTi、Ni、Co又はPt等からなる金属膜(図示省略)を例えば100nm程度の厚さ(ポリシリコン膜106を十分にシリサイド化することができる厚さ)で堆積した後、熱処理を行うことにより、ゲート部121a及び121bを構成するポリシリコン膜106と前記金属膜とを反応させ、その後、未反応の前記金属膜を除去した後、再度熱処理を行うことにより、シリサイドからなる第3の金属含有導電膜113を形成する。これにより、図1(a)及び(b)に示す本実施形態の半導体装置、つまり、第1の金属含有導電膜104a及び第3の金属含有導電膜113からなる第1のゲート電極122aを有するNMISトランジスタと、第2の金属含有導電膜104b及び第3の金属含有導電膜113からなる第2のゲート電極122bを有するPMISトランジスタとを備えた半導体装置が得られる。

【0051】

尚、本実施形態においては、ポリシリコン膜106を完全にシリサイド化することにより、第1の金属含有導電膜104a及び第2の金属含有導電膜104b並びに素子分離領域102のそれぞれと接するように第3の金属含有導電膜113を形成する。また、本実施形態においては、工程を簡単化するため、ゲート部121a及び121bの表面にシリサイド層111を残存させたまま、ポリシリコン膜106のシリサイド化を行うが、これによる弊害は特にない。

【0052】

最後に、図示は省略しているが、公知の技術を用いて、ゲート電極122a及び122b並びにソース・ドレイン領域110a及び110bと電気的に接続するコンタクトや配線を形成する。

【0053】

以上に説明したように、第1の実施形態によると、第1のゲート電極122aを構成する第1の金属含有導電膜104a、及び第2のゲート電極122bを構成する第2の金属含有導電膜104bのそれぞれの直上に、各ゲート電極122a及び122bの一部となる第3の金属含有導電膜113、つまりポリシリコンよりも抵抗が低い材料(シリサイド)からなる導電層が素子分離領域102を横断するように連続的に形成されている。このため、第1のゲート電極122aと第2のゲート電極122bとを電気的に接続する配線、つまり素子分離領域102上のPN境界部配線が金属(第3の金属含有導電膜113)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0054】

また、第1の実施形態によると、第3の金属含有導電膜113がシリサイドから構成されているため、MIPS構造におけるシリコンをシリサイド化することによって、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0055】

また、第1の実施形態によると、各MIS形成領域RA 及びRB においてメタルゲート電極となる金属含有導電膜104a及び104bのみならずゲート絶縁膜103a及び103bをも作り分けているので、金属含有導電膜104a及び104bのパターニング時におけるゲート絶縁膜103a及び103bの劣化を防止することができる。

【0056】

尚、第1の実施形態において、NMISトランジスタの第1のゲート電極122aを構成する第1の金属含有導電膜104aの材料として、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.55eV以下の材料を用いてよい。

【0057】

また、第1の実施形態において、PMISトランジスタの第2のゲート電極122bを構成する第2の金属含有導電膜104bの材料として、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.65eV以上の材料を用いてよい。

【0058】

また、第1の実施形態において、ゲート部121a及び121bの表面にシリサイド層111を残存させたまま、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成したが、これに代えて、CMPやエッチング等によってゲート部121a及び121bの表面のシリサイド層111を削り取ってポリシリコン膜106の表面を露出させてから、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。

【0059】

また、第1の実施形態において、ゲート部121a及び121bの表面にシリサイド層111を形成しなくてもよい。具体的には、図6(c)及び(d)に示す工程でポリシリコン膜106上にハードマスクを形成し、図7(a)及び(b)に示す工程で当該ハードマスクをポリシリコン膜106等と共にパターニングし、図8(c)及び(d)に示す工程で当該ハードマスクによってポリシリコン膜106の表面のシリサイド化を防止し、その後、当該ハードマスクを除去してから、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。

【0060】

また、第1の実施形態において、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるように、言い換えると、素子分離領域102と接するように、シリサイドからなる第3の金属含有導電膜113を形成した。しかし、これに代えて、図11(本実施形態の半導体装置におけるW方向の断面構成のバリエーション)に示すように、素子分離領域102と第3の金属含有導電膜113との間にポリシリコン膜106の一部が残存するように、ポリシリコン膜106のシリサイド化を行って第3の金属含有導電膜113を形成してもよい。すなわち、第3の金属含有導電膜113は、第1の金属含有導電膜104aの直上から第2の金属含有導電膜104bの直上まで連続的に形成されていれば、素子分離領域102と接していなくてもよい。言い換えると、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースを埋めるポリシリコン膜106はシリサイド化されていなくてもよい。

【0061】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0062】

図12(a)及び(b)は、本発明の第2の実施形態に係る半導体装置の断面構成を示しており、図12(a)はゲート長方向(L方向)の断面図であり、図12(b)はゲート幅方向(W方向)の断面図である。

【0063】

図12(a)及び(b)に示すように、半導体基板101における素子分離形成領域RC には、NMIS形成領域RA の半導体基板101からなる第1の活性領域101AとPMIS形成領域RB の半導体基板101からなる第2の活性領域101Bとを区画するSTIからなる素子分離領域102が形成されている。素子分離領域102に囲まれたNMIS形成領域RA の第1の活性領域101AにはPウェル領域101aが形成されていると共に、素子分離領域102に囲まれたPMIS形成領域RB の第2の活性領域101BにはNウェル領域101bが形成されている。第1の活性領域101A上には第1のゲート絶縁膜103aを介して第1のゲート電極132aが形成されていると共に、第2の活性領域101B上には第2のゲート絶縁膜103bを介して第2のゲート電極132bが形成されている。ゲート絶縁膜103a及び103bは、例えばHigh-k膜であるHfSiO膜からなる。NMISトランジスタの第1のゲート電極132aは、第1のゲート絶縁膜103a上に形成された第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜104cと、第3の金属含有導電膜104c上に形成されたポリシリコン膜106と、ポリシリコン膜106の表面部に形成されたシリサイド層111とから構成されている。PMISトランジスタの第2のゲート電極132bは、第2のゲート絶縁膜103b上に形成された第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜104cと、第3の金属含有導電膜104c上に形成されたポリシリコン膜106と、ポリシリコン膜106の表面部に形成されたシリサイド層111とから構成されている。第1の金属含有導電膜104aは、例えば、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなり、第2の金属含有導電膜104bは、例えば、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなる。第3の金属含有導電膜104cの材料は、ポリシリコンよりも抵抗が低い材料であれば、特に限定されないが、例えば、第1の金属含有導電膜104a又は第2の金属含有導電膜104bと同様の高融点金属含有材料を用いることができる。

【0064】

また、図12(a)及び(b)に示すように、ゲート電極132a及び132bのそれぞれの側面には絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109が形成されている。第1の活性領域101Aの表面部における絶縁性サイドウォールスペーサー109の下側にはN型エクステンション領域(浅いN型ソース・ドレイン領域)108aが形成されており、その外側にはN型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110aが形成されている。第2の活性領域101Bの表面部における絶縁性サイドウォールスペーサー109の下側にはP型エクステンション領域(浅いソP型ース・ドレイン領域)108bが形成されており、その外側にはP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bが形成されている。ソース・ドレイン領域110a及び110bの表面部にはシリサイド層111が形成されている。半導体基板101上の全面に、ゲート電極132a及び132bが埋まるように、層間絶縁膜112が形成されている。

【0065】

本実施形態の特徴は、ゲート電極132a及び132bのそれぞれの一部となる第3の金属含有導電膜104cが、第1の金属含有導電膜104a、第2の金属含有導電膜104b及び素子分離領域102のそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されていることである。

【0066】

尚、本実施形態において、図12(b)に示すように、W方向において、第1のゲート電極132aを構成する第1の金属含有導電膜104aは、第1の活性領域101A上及びそれに隣接する素子分離領域102の端部上に形成されており、第2のゲート電極132bを構成する第2の金属含有導電膜104bは、第2の活性領域101B上及びそれに隣接する素子分離領域102の端部上に形成されている。すなわち、W方向においては、素子分離領域102上で第1の金属含有導電膜104aと第2の金属含有導電膜104bとは分断されている。また、本実施形態においては、第3の金属含有導電膜104cは、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペース内に凹部が残るように形成されており、当該凹部を埋めるようにポリシリコン膜106がさらに形成されている。

【0067】

以下、図12(a)及び(b)に示す本実施形態の半導体装置を製造するための方法について説明する。図13(a)〜(d)、図14(a)〜(d)及び図15(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図13(a)、(c)、図14(a)、(c)及び図15(a)、(c)はL方向の断面図であり、図13(b)、(d)、図14(b)、(d)及び図15(b)、(d)はW方向の断面図である。

【0068】

まず、本実施形態においては、図2(a)〜(d)、図3(a)〜(d)、図4(a)〜(d)及び図5(a)〜(d)に示す第1の実施形態に係る半導体装置の製造方法の各工程を実施した後、図13(a)及び(b)に示すように、ハードマスク105a及び105bを除去する。これにより、NMIS形成領域RA の第1の活性領域101A上に第1のゲート絶縁膜103aを介して第1の金属含有導電膜104aが形成されると共に、PMIS形成領域RB の第2の活性領域101B上に第2のゲート絶縁膜103bを介して第2の金属含有導電膜104bが形成される。

【0069】

次に、図13(c)及び(d)に示すように、半導体基板101上の全面に、例えば金属含有導電膜104a又は104bと同様の高融点金属含有材料からなる厚さ10nm程度の第3の金属含有導電膜104cを成膜した後、第3の金属含有導電膜104c上に例えば厚さ100nm程度のポリシリコン膜106を成膜する。

【0070】

次に、図14(a)及び(b)に示すように、NMIS形成領域RA のポリシリコン膜106、第3の金属含有導電膜104c及び第1の金属含有導電膜104a、並びにPMIS形成領域RB のポリシリコン膜106、第3の金属含有導電膜104c及び第2の金属含有導電膜104bをそれぞれドライエッチングによりパターニングする。これにより、第1の活性領域101A上に第1のゲート絶縁膜103aを介して、第1の金属含有導電膜104a、第3の金属含有誘電膜104c及びポリシリコン膜106からなる第1のゲート部131aを形成すると共に、第2の活性領域101B上に第2のゲート絶縁膜103bを介して、第2の金属含有導電膜104b、第3の金属含有誘電膜104c及びポリシリコン膜106からなる第2のゲート部131bを形成する。このとき、図14(b)に示すように、第1のゲート部121aを構成する第3の金属含有誘電膜104c及びポリシリコン膜106と、第2のゲート部121bを構成する第3の金属含有誘電膜104c及びポリシリコン膜106とは、素子分離領域102上に形成された第3の金属含有誘電膜104c及びポリシリコン膜106を介して一体的に形成されている。さらに、図14(a)及び(b)に示す工程において、第1のゲート部131aの外側の第1のゲート絶縁膜103a、及び第2のゲート部131bの外側の第2のゲート絶縁膜103bがそれぞれ除去される。尚、本実施形態においては、金属含有導電膜104a及び104bの材料並びにエッチング条件を適切に選択することにより、同一チャンバー内においてポリシリコン膜106、第3の金属含有導電膜104c並びに第1及び第2の金属含有導電膜104a及び104bに対して連続的にエッチングを行い、それによってゲート部131a及び131bのパターニング形成を同時に行う。

【0071】

次に、図14(c)及び(d)に示すように、ゲート部131a及び131bのそれぞれの側面上に絶縁性オフセットスペーサー107を形成した後、第1のゲート部131a及び131b並びに絶縁性オフセットスペーサー107をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型エクステンション領域(浅いN型ソース・ドレイン領域)108a及びP型エクステンション領域(浅いP型ソース・ドレイン領域)108bを形成する。

【0072】

次に、図15(a)及び(b)に示すように、ゲート部131a及び131bのそれぞれの側面上に絶縁性オフセットスペーサー107を介して絶縁性サイドウォールスペーサー109を形成した後、ゲート部131a及び131b並びに絶縁性オフセットスペーサー107及び絶縁性サイドウォールスペーサー109をマスクとして、第1の活性領域101A及び第2の活性領域101Bのそれぞれに対してイオン注入を行うことにより、N型ソース・ドレイン領域(深いN型ソース・ドレイン領域)110a及びP型ソース・ドレイン領域(深いP型ソース・ドレイン領域)110bを形成する。

【0073】

次に、図15(c)及び(d)に示すように、ゲート部131a及び131bを構成するポリシリコン膜106の表面部、及びソース・ドレイン領域110a及び110bの表面部をシリサイド化してシリサイド層111を形成する。これによって、ポリシリコン膜106上にシリサイド層111が形成された第1のゲート電極132a及び第2のゲート電極132bが形成されると共に、ゲート電極132a及び132b並びにソース・ドレイン領域110a及び110bを低抵抗化することができる。

【0074】

次に、半導体基板101上の全面に、ゲート電極132a及び132bを覆うことができる厚さ(例えば200nm以上の厚さ)を持つ層間絶縁膜112を成膜する。これにより、図12(a)及び(b)に示す本実施形態の半導体装置、つまり、第1の金属含有導電膜104a、第3の金属含有導電膜104c、ポリシリコン膜106及びシリサイド層111からなる第1のゲート電極132aを有するNMISトランジスタと、第2の金属含有導電膜104b、第3の金属含有導電膜104c、ポリシリコン膜106及びシリサイド層111からなる第2のゲート電極132bを有するPMISトランジスタとを備えた半導体装置が得られる。

【0075】

最後に、図示は省略しているが、公知の技術を用いて、ゲート電極132a及び132b並びにソース・ドレイン領域110a及び110bと電気的に接続するコンタクトや配線を形成する。

【0076】

以上に説明したように、第2の実施形態によると、第1のゲート電極132aを構成する第1の金属含有導電膜104a、及び第2のゲート電極132bを構成する第2の金属含有導電膜104bのそれぞれの直上に、各ゲート電極132a及び132bの一部となる第3の金属含有導電膜104c、つまりポリシリコンよりも抵抗が低い材料からなる導電層が素子分離領域102を横断するように連続的に形成されている。このため、第1のゲート電極132aと第2のゲート電極132bとを電気的に接続する配線、つまり素子分離領域102上のPN境界部配線が金属(第3の金属含有導電膜104c)を含むので、PN境界部配線の配線幅を太くする等の対策を講じることなく、PN境界部配線を低抵抗化することができる。これによって、MIPS構造のDMGを有する半導体装置において高集積化を進展させつつ、従来のMIPS構造におけるポリシリコン表面のシリサイドへの電流の集中に起因する当該シリサイドの断線等の問題、つまりPN境界部配線の高抵抗化に起因する断線等の問題を防止することができる。

【0077】

また、第2の実施形態によると、第1のゲート電極132aを構成する第1の金属含有導電膜104a、及び第2のゲート電極132bを構成する第2の金属含有導電膜104bのそれぞれの直上に、第3の金属含有導電膜104cを素子分離領域102と接するように形成することによって、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0078】

また、第2の実施形態によると、第3の金属含有導電膜104c上に、第1のゲート電極132a及び第2のゲート電極132bのそれぞれの一部となるポリシリコン膜106がさらに形成されているため、MIPS構造においてメタルとシリコンとの間にさらに他のメタルを挿入することにより、本実施形態に係る半導体装置の構造を簡単に得ることができる。

【0079】

また、第2の実施形態によると、各MIS形成領域RA 及びRB においてメタルゲート電極となる金属含有導電膜104a及び104bのみならずゲート絶縁膜103a及び103bをも作り分けているので、金属含有導電膜104a及び104bのパターニング時におけるゲート絶縁膜103a及び103bの劣化を防止することができる。

【0080】

尚、第2の実施形態において、NMISトランジスタの第1のゲート電極132aを構成する第1の金属含有導電膜104aの材料として、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.55eV以下の材料を用いてよい。

【0081】

また、第2の実施形態において、PMISトランジスタの第2のゲート電極132bを構成する第2の金属含有導電膜104bの材料として、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料を用いたが、これに限らず、仕事関数が4.65eV以上の材料を用いてよい。

【0082】

また、第2の実施形態において、PN境界部配線を含むゲート電極132a及び132b中に第3の金属含有導電膜104cを連続的に形成しているため、ゲート電極132a及び132bを構成するポリシリコン膜106の表面部のみをシリサイド化してシリサイド層111を形成した。しかし、これに代えて、ポリシリコン膜106を完全にシリサイド化してもよい。

【0083】

また、第2の実施形態において、第3の金属含有導電膜104cを、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペース内に凹部が残るように、比較的薄く形成した。しかし、これに代えて、図16(本実施形態の半導体装置におけるW方向の断面構成のバリエーション)に示すように、第3の金属含有導電膜104cを、素子分離領域102上における第1の金属含有導電膜104aと第2の金属含有導電膜104bとに挟まれたスペースが埋まるように、比較的厚く形成してもよい。但し、第3の金属含有導電膜104cを薄く形成した方が、図14(a)及び(b)に示すゲート部131a及び131bのパターニング形成工程で第3の金属含有導電膜104cの加工が容易になるというメリットが得られる。

【産業上の利用可能性】

【0084】

以上に説明したように、半導体装置及びその製造方法に関し、特にMIPS構造のDMGプロセスに適用した場合には、PN境界部配線の高抵抗化に起因する断線等の問題を防止することができ、非常に有用である。

【図面の簡単な説明】

【0085】

【図1】図1(a)及び(b)は、本発明の第1の実施形態に係る半導体装置の断面構成を示しており、図1(a)はゲート長方向(L方向)の断面図であり、図1(b)はゲート幅方向(W方向)の断面図である。

【図2】図2(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図2(a)、(c)はL方向の断面図であり、図2(b)、(d)はW方向の断面図である。

【図3】図3(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図3(a)、(c)はL方向の断面図であり、図3(b)、(d)はW方向の断面図である。

【図4】図4(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図4(a)、(c)はL方向の断面図であり、図4(b)、(d)はW方向の断面図である。

【図5】図5(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図5(a)、(c)はL方向の断面図であり、図5(b)、(d)はW方向の断面図である。

【図6】図6(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図6(a)、(c)はL方向の断面図であり、図6(b)、(d)はW方向の断面図である。

【図7】図7(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図7(a)、(c)はL方向の断面図であり、図7(b)、(d)はW方向の断面図である。

【図8】図8(a)〜(d)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図8(a)、(c)はL方向の断面図であり、図8(b)、(d)はW方向の断面図である。

【図9】図9(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図9(a)はL方向の断面図であり、図9(b)はW方向の断面図である。

【図10】図10(a)、(b)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図10(a)はL方向の断面図であり、図10(b)はW方向の断面図である。

【図11】図11は、本発明の第1の実施形態に係る半導体装置におけるW方向の断面構成のバリエーションを示す図である。

【図12】図12(a)及び(b)は、本発明の第2の実施形態に係る半導体装置の断面構成を示しており、図12(a)はL方向の断面図であり、図12(b)はW方向の断面図である。

【図13】図13(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図13(a)、(c)はL方向の断面図であり、図13(b)、(d)はW方向の断面図である。

【図14】図14(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図14(a)、(c)はL方向の断面図であり、図14(b)、(d)はW方向の断面図である。

【図15】図15(a)〜(d)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図であり、図15(a)、(c)はL方向の断面図であり、図15(b)、(d)はW方向の断面図である。

【図16】図16は、本発明の第2の実施形態に係る半導体装置におけるW方向の断面構成のバリエーションを示す図である。

【図17】非特許文献1に開示されているMIPS構造のDMGを備えた半導体装置の断面図である。

【符号の説明】

【0086】

101 半導体基板

101A 第1の活性領域

101B 第2の活性領域

101a Pウェル領域

101b Nウェル領域

102 素子分離領域

103a 第1のゲート絶縁膜

103b 第2のゲート絶縁膜

104a 第1の金属含有導電膜

104b 第2の金属含有導電膜

104c 第3の金属含有導電膜

105a、105b ハードマスク

106 ポリシリコン膜

107 絶縁性オフセットスペーサー

108a N型エクステンション領域

108b P型エクステンション領域

109 絶縁性サイドウォールスペーサー

110a N型ソース・ドレイン領域

110b P型ソース・ドレイン領域

111 シリサイド層

112 層間絶縁膜

113 第3の金属含有導電膜

121a 第1のゲート部

121b 第2のゲート部

122a 第1のゲート電極

122b 第2のゲート電極

131a 第1のゲート部

131b 第2のゲート部

132a 第1のゲート電極

132b 第2のゲート電極

RA NMIS形成領域

RB PMIS形成領域

RC 素子分離形成領域

【特許請求の範囲】

【請求項1】

半導体基板における第1の活性領域上に形成され、第1の金属含有導電膜を有する第1のゲート電極と、

前記半導体基板における第2の活性領域上に形成され、第2の金属含有導電膜を有する第2のゲート電極と、

前記第1の活性領域と前記第2の活性領域とを区画するように前記半導体基板に形成された素子分離領域とを備え、

前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されており、

前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜が連続的に形成されており、

前記第3の金属含有導電膜は、前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接していることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第3の金属含有導電膜は前記素子分離領域と接していることを特徴とする半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第3の金属含有導電膜は、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成されていることを特徴とする半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記第3の金属含有導電膜と前記素子分離領域との間にはシリコン領域が介在することを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記第3の金属含有導電膜はシリサイドからなることを特徴とする半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

前記シリサイドはTi、Ni、Co又はPtを含むことを特徴とする半導体装置。

【請求項7】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜がさらに形成されていることを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記シリコン膜の表面はシリサイド化されていることを特徴とする半導体装置。

【請求項9】

請求項1〜8のいずれか1項に記載の半導体装置において、

前記第1の活性領域と前記第1のゲート電極との間に形成された第1の高誘電率ゲート絶縁膜と、

前記第2の活性領域と前記第2のゲート電極との間に形成された第2の高誘電率ゲート絶縁膜とをさらに備えていることを特徴とする半導体装置。

【請求項10】

請求項1〜9のいずれか1項に記載の半導体装置において、

前記第1のゲート電極はN型MISトランジスタのゲート電極であり、

前記第1の金属含有導電膜は、仕事関数が4.55eV以下の材料からなることを特徴とする半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1の金属含有導電膜は、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなることを特徴とする半導体装置。

【請求項12】

請求項1〜11のいずれか1項に記載の半導体装置において、

前記第2のゲート電極はP型MISトランジスタのゲート電極であり、

前記第2の金属含有導電膜は、仕事関数が4.65eV以上の材料からなることを特徴とする半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第2の金属含有導電膜は、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなることを特徴とする半導体装置。

【請求項14】

半導体基板における第1の活性領域と第2の活性領域とを区画するように、前記半導体基板に素子分離領域を形成する工程(a)と、

前記第1の活性領域上に、第1のゲート電極の一部となる第1の金属含有導電膜を形成する工程(b)と、

前記第2の活性領域上に、第2のゲート電極の一部となる第2の金属含有導電膜を形成する工程(c)と、

前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜を前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接するように連続的に形成する工程(d)とを備え、

前記工程(d)において、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されていることを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法において、

前記工程(b)は、前記半導体基板上に前記第1の金属含有導電膜を形成した後、前記第2の活性領域上の前記第1の金属含有導電膜を選択的に除去する工程を含み、

前記工程(c)は、前記半導体基板上に前記第2の金属含有導電膜を形成した後、前記第1の活性領域上の前記第2の金属含有導電膜を選択的に除去する工程を含むことを特徴とする半導体装置の製造方法。

【請求項16】

請求項14又は15に記載の半導体装置の製造方法において、

前記工程(d)は、前記第3の金属含有導電膜を前記素子分離領域と接するように形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)は、前記第3の金属含有導電膜を、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項18】

請求項14〜17のいずれか1項に記載の半導体装置の製造方法において、

前記工程(d)は、前記第1の金属含有導電膜、前記素子分離領域及び前記第2の金属含有導電膜のそれぞれの上にシリコン膜を形成した後、前記第1の金属含有導電膜、前記第2の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜をシリサイド化して前記第3の金属含有導電膜を形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項19】

請求項14〜17のいずれか1項に記載の半導体装置の製造方法において、

前記工程(d)よりも後に、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜を形成する工程(e)をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項20】

請求項19に記載の半導体装置の製造方法において、

前記工程(e)よりも後に、前記第1の金属含有導電膜、前記第2の金属含有導電膜、前記第3の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜の表面をシリサイド化する工程をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板における第1の活性領域上に形成され、第1の金属含有導電膜を有する第1のゲート電極と、

前記半導体基板における第2の活性領域上に形成され、第2の金属含有導電膜を有する第2のゲート電極と、

前記第1の活性領域と前記第2の活性領域とを区画するように前記半導体基板に形成された素子分離領域とを備え、

前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されており、

前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜が連続的に形成されており、

前記第3の金属含有導電膜は、前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接していることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第3の金属含有導電膜は前記素子分離領域と接していることを特徴とする半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第3の金属含有導電膜は、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成されていることを特徴とする半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記第3の金属含有導電膜と前記素子分離領域との間にはシリコン領域が介在することを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記第3の金属含有導電膜はシリサイドからなることを特徴とする半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

前記シリサイドはTi、Ni、Co又はPtを含むことを特徴とする半導体装置。

【請求項7】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜がさらに形成されていることを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記シリコン膜の表面はシリサイド化されていることを特徴とする半導体装置。

【請求項9】

請求項1〜8のいずれか1項に記載の半導体装置において、

前記第1の活性領域と前記第1のゲート電極との間に形成された第1の高誘電率ゲート絶縁膜と、

前記第2の活性領域と前記第2のゲート電極との間に形成された第2の高誘電率ゲート絶縁膜とをさらに備えていることを特徴とする半導体装置。

【請求項10】

請求項1〜9のいずれか1項に記載の半導体装置において、

前記第1のゲート電極はN型MISトランジスタのゲート電極であり、

前記第1の金属含有導電膜は、仕事関数が4.55eV以下の材料からなることを特徴とする半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1の金属含有導電膜は、Ta化合物及びHf化合物のうちの少なくとも1つを含む材料からなることを特徴とする半導体装置。

【請求項12】

請求項1〜11のいずれか1項に記載の半導体装置において、

前記第2のゲート電極はP型MISトランジスタのゲート電極であり、

前記第2の金属含有導電膜は、仕事関数が4.65eV以上の材料からなることを特徴とする半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第2の金属含有導電膜は、Ti化合物及びRu化合物のうちの少なくとも1つを含む材料からなることを特徴とする半導体装置。

【請求項14】

半導体基板における第1の活性領域と第2の活性領域とを区画するように、前記半導体基板に素子分離領域を形成する工程(a)と、

前記第1の活性領域上に、第1のゲート電極の一部となる第1の金属含有導電膜を形成する工程(b)と、

前記第2の活性領域上に、第2のゲート電極の一部となる第2の金属含有導電膜を形成する工程(c)と、

前記第1の金属含有導電膜上から前記素子分離領域上を経て前記第2の金属含有導電膜の上まで、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となる第3の金属含有導電膜を前記第1の金属含有導電膜及び前記第2の金属含有導電膜のそれぞれと接するように連続的に形成する工程(d)とを備え、

前記工程(d)において、前記第1の金属含有導電膜及び前記第2の金属含有導電膜はそれぞれ前記素子分離領域上に互いに離間して形成されていることを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法において、

前記工程(b)は、前記半導体基板上に前記第1の金属含有導電膜を形成した後、前記第2の活性領域上の前記第1の金属含有導電膜を選択的に除去する工程を含み、

前記工程(c)は、前記半導体基板上に前記第2の金属含有導電膜を形成した後、前記第1の活性領域上の前記第2の金属含有導電膜を選択的に除去する工程を含むことを特徴とする半導体装置の製造方法。

【請求項16】

請求項14又は15に記載の半導体装置の製造方法において、

前記工程(d)は、前記第3の金属含有導電膜を前記素子分離領域と接するように形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)は、前記第3の金属含有導電膜を、前記素子分離領域上における前記第1の金属含有導電膜と前記第2の金属含有導電膜とに挟まれたスペースを埋めるように形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項18】

請求項14〜17のいずれか1項に記載の半導体装置の製造方法において、

前記工程(d)は、前記第1の金属含有導電膜、前記素子分離領域及び前記第2の金属含有導電膜のそれぞれの上にシリコン膜を形成した後、前記第1の金属含有導電膜、前記第2の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜をシリサイド化して前記第3の金属含有導電膜を形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項19】

請求項14〜17のいずれか1項に記載の半導体装置の製造方法において、

前記工程(d)よりも後に、前記第3の金属含有導電膜上に、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの一部となるシリコン膜を形成する工程(e)をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項20】

請求項19に記載の半導体装置の製造方法において、

前記工程(e)よりも後に、前記第1の金属含有導電膜、前記第2の金属含有導電膜、前記第3の金属含有導電膜及び前記シリコン膜を前記第1のゲート電極及び前記第2のゲート電極のそれぞれの形状にパターニングし、その後、パターニングされた前記シリコン膜の表面をシリサイド化する工程をさらに備えていることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2009−224509(P2009−224509A)

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願番号】特願2008−66543(P2008−66543)

【出願日】平成20年3月14日(2008.3.14)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願日】平成20年3月14日(2008.3.14)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]