半導体装置及びその製造方法

【課題】積層配置される半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを抑制するとともに、半導体装置として大形化を招くことのない支持部材を有する、半導体装置及びその製造方法を提供することを目的とする。

【解決手段】上記の課題を解決するため、本発明によって提供される半導体装置は、電極端子が配設された支持基体と、支持基体上に搭載された中間部材と、一部が中間部材により支持されて、支持基体上に配設された半導体素子と、半導体素子の電極端子に対応して、支持基体上あるいは前記中間部材上に配設された凸状部材とを具備し、半導体素子の電極端子と前記支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする。

【解決手段】上記の課題を解決するため、本発明によって提供される半導体装置は、電極端子が配設された支持基体と、支持基体上に搭載された中間部材と、一部が中間部材により支持されて、支持基体上に配設された半導体素子と、半導体素子の電極端子に対応して、支持基体上あるいは前記中間部材上に配設された凸状部材とを具備し、半導体素子の電極端子と前記支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に支持基体上に複数の半導体素子が積層配置される半導体装置及びその製造方法に関する。

【背景技術】

【0002】

電子機器の高機能化ならびに小型化に伴い、当該電子機器に搭載される半導体集積回路装置などの半導体装置に対しても、より高機能化、高速動作化と共に、更なる小形化、軽量化が求められている。

【0003】

この為、当該半導体装置にあっては、回路基板などの支持基体(支持基板)上に、複数個の半導体素子を積層して搭載することがなされている。

【0004】

この様に、複数個の半導体素子を積層配置する構成は、例えば、マイクロプロセッサなどの論理機能素子と、不揮発性メモリなどの半導体記憶素子とを組み合わせて所望の機能を発揮させる場合などに生ずる。

【0005】

かかる場合、論理機能素子ならびに半導体記憶素子は、その回路機能・回路規模を全く異にすることから、外形寸法が異なることが一般的である。

【0006】

また、当該半導体素子は通常、矩形状の平面形状を有する。

【0007】

従って、積層された状態に於いて、上方に位置する半導体素子の少なくとも一端が、下方(支持基体側)に位置する半導体素子の外方に庇状に延出(突出)する状態が生じてしまう場合がある。

【0008】

また、前記支持基体に於けるところの、半導体素子の電極端子が接続される接続端子の配置構成、あるいは当該支持基体の電子機器への接続用端子の配置構成などによって、これら複数の半導体素子から導出されるボンディングワイヤの導出方向及び/あるいは導出箇所などが制限される場合がある。

【0009】

かかる場合、積層される半導体素子は、その中心線が交差する如く異なる方向とされて(回転配置されて)積層され、当該半導体素子の電極端子からのボンディングワイヤなどの導出の自由度が高められる。

【0010】

このとき、上方に位置する半導体素子の両端、あるいは少なくとも一端が、下方(支持基体側)に位置する半導体素子の電極端子配設部(配設辺)とは異なる方向に庇状に延出(突出)する状態となる場合がある。

【0011】

尚、前記支持基体上への半導体素子の搭載形態としては、当該支持基体上に所謂フリップチップ(フェイスダウン)形態をもって搭載される形態、あるいは当該支持基体上にフェイスアップ状態をもって搭載されその電極端子パッドがワイヤボンディング法により支持基体上の電極端子に接続される形態がある。

【0012】

これらの搭載形態は適宜選択され、組み合わされて、支持基体上に、複数の半導体素子が積層されて搭載されるが、前述の如く、上方に位置する半導体素子の一部が下方(支持基体側)に位置する半導体素子の外方に、当該下方に位置する半導体素子の縁部を越えて庇状に延出(突出)する状態は、当該半導体素子相互間の寸法関係、及び/あるいは搭載する方向により発生する。

【0013】

更に、複数の半導体素子を積層して配設する際、半導体素子相互間に所謂スペーサ(間隔保持体)を配設し、当該半導体素子間に空間を設けることが行われる場合がある。

【0014】

このとき、上方に位置する半導体素子の少なくとも一端が、支持基体であるスペーサの外方に庇状に延出(突出)する状態が生じる場合がある。

【0015】

また、前記半導体装置にあっては、前述の如き半導体素子の積層構造を含むものであっても、その厚さ(高さ)をより減少させることが要求されている。

【0016】

一方、積層される半導体素子の組み合わせについても、種々の要求がなされつつある。

【0017】

この為、前記半導体素子も、その厚さをより減じることが必要とされている。

【0018】

この様に厚さが減じられた半導体素子が、前記積層構造体を構成する際に適用され、当該半導体素子が上方に位置する場合には、前述の如く、当該上方に位置する半導体素子に於ける電極端子部が、前記延出部に位置してしまう状態が生ずる。

【0019】

かかる場合、当該上方に位置する半導体素子の電極端子にワイヤボンディングを行おうとすると、当該半導体素子の延出部が撓み(下方、支持基体側に湾曲し)、十分な加圧がなされないことから正常なワイヤボンディングが行われない。

【0020】

また、より大きな圧力を加えれば、当該上方に位置する半導体素子の延出部に損傷を生じてしまう場合もある。

【0021】

この様に、半導体素子の積層構造を採用してなる半導体装置に於いて、上方に位置する半導体素子の電極端子へワイヤボンディングを行う際、当該半導体素子の延出部の変形を防止する為に、従来種々の提案がなされている。

【0022】

一つに、基板上に、第1の半導体チップと、当該第1の半導体チップよりも大であって当該第1の半導体チップ上に積層配置された第2の半導体チップとが配置され、当該第2の半導体チップと基板との間に、台部材を配設してなる構成が提案されている。(例えば、特許文献1参照)

また、基板上に、第1の半導体チップと、当該第1の半導体チップよりも大であって当該第1の半導体チップ上に積層配置された第2の半導体チップとが配置され、当該第2の半導体チップと基板との間に、複数の柱状の支持部を配設してなる構成が提案されている。(例えば、特許文献2参照)

【特許文献1】特開2001−320014号公報

【特許文献2】特開2005−197491号公報

【発明の開示】

【発明が解決しようとする課題】

【0023】

しかしながら、前記半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを防止しようとすると、突出部の大きさに対応した専用の支持部材が必要となり、多種類の支持材を用意する必要が生じる。

【0024】

また、当該支持材が大形化されると、当該支持材を避けて他の半導体素子あるいは受動部品を配置する必要が生じ、半導体装置の大型化を招来してしまう。

【0025】

本発明は、このような問題に鑑みてなされたものであり、積層配置される半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを抑制するとともに、半導体装置として大形化を招くことのない支持部材を有する、半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0026】

上記の課題を達成するため、本発明の第1の側面によれば、電極端子が配設された支持基体と、支持基体上に搭載された中間部材と、一部が前記中間部材により支持されて、支持基体上に配設された半導体素子と、半導体素子の電極端子に対応して、支持基体上あるいは中間部材上に配設された凸状部材とを具備し、半導体素子の電極端子と支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置を提供する。

【0027】

また、本発明の第2の側面によれば、電極端子が配設された支持基体上に、中間部材を搭載する工程と、支持基体上に、凸状部材を配設する工程と、中間部材上に、半導体素子をフェイスアップ状態をもって搭載する工程と、半導体素子の電極端子と支持基体の電極端子とをワイヤボンディング法により接続する工程とを含むことを特徴とする半導体装置の製造方法を提供する。

【発明の効果】

【0028】

本発明によれば、支持基体上に、複数個の半導体素子が積層状態をもって配設される半導体装置にあって、上方に位置する半導体素子(支持基体から遠い位置にある半導体素子)が、下方に位置する半導体素子の縁部を越えて延出(突出)する状態を有する半導体装置において、前記上方に位置する半導体素子の電極へのボンディングワイヤの接続が確実になされる。

【0029】

また、所定の外形寸法を有するスペーサ上に、当該スペーサよりも大なる外形寸法を有する半導体素子が配設される場合にあっても、当該半導体素子の電極へのボンディングワイヤの接続が確実になされる。

【0030】

これにより、異なる外形寸法を有する半導体素子を積層してなる半導体装置、あるいは複数の半導体素子がその中心線が交差する如く異なる方向をもって積層される半導体装置を、高い接続信頼性をもって、容易に実現することができる。

【0031】

また、本発明によれば、上記の半導体装置を容易に製造することができる。

【発明を実施するための最良の形態】

【0032】

以下、本発明による半導体装置の実施形態について、その製造方法と共に詳細に説明する。本発明による半導体装置は、以下に記すように、複数の実施形態を含む。

(実施形態1)

本発明による半導体装置の実施形態その1について、図1乃至図9を用いて説明する。

【0033】

本実施形態に於ける半導体装置は、支持基体である配線基板上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により当該配線基板上の電極端子に接続される第1の半導体素子と、当該第1の半導体素子上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により前記配線基板上の電極端子に接続される第2の半導体素子とを具備する。

【0034】

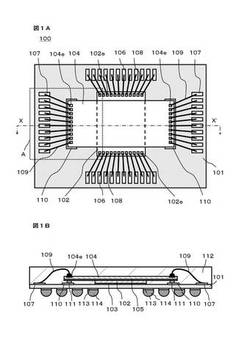

本発明の、実施形態その1にかかる半導体装置100を、図1に示す。

【0035】

図1Aは、当該半導体装置100の平面を示し、また図1Bは、図1Aに於けるX−X’断面を示す。尚、図1Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0036】

当該半導体装置100にあっては、支持基体である配線基板101の一方の主面上に、二つの半導体素子が積層配置されている。

【0037】

即ち、当該配線基板101上には、第1の半導体素子102が接着剤層103を介して、所謂フェイスアップ状態をもって搭載されており、更に当該第1の半導体素子102上には、第2の半導体素子104が、接着剤層105を介してフェイスアップ状態をもって搭載されている。

【0038】

ここで、第2の半導体素子104は長方形状を有し、第1の半導体素子102上に於いて、当該第1の半導体素子102の幅を越えて庇状(片持ち梁状)に延出(突出)して搭載されている。この為、第1の半導体素子102の側部に於いて、第2の半導体素子104の延出(突出)部と前記支持基板101との間は離間している。

【0039】

そして、第1の半導体素子102は、配線基板101と第2の半導体素子104との間に位置して中間部材をなしている。

【0040】

かかる構成に於いて、前記第1の半導体素子102の外部接続用電極端子102eは、前記第2の半導体素子104が延出する2辺とは異なる2辺に沿って、その縁部近傍にそれぞれ複数個配設されている。

【0041】

また、第2の半導体素子104の外部接続用電極端子104eは、当該第2の半導体素子104の長手方向の両端の2辺に沿って、その縁部近傍にそれぞれ複数個配設されている。

【0042】

一方、前記配線基板101の主面上には、第1の半導体素子102の外部接続用電極端子102eに対応して電極端子106が複数個配設され、また第2の半導体素子104の外部接続用電極端子104eに対応して電極端子107が複数個配設されている。

【0043】

そして、第1の半導体素子102の外部接続用電極端子102eと配線基板101上の電極端子106との間は、ボンディングワイヤ108により接続され、一方、第2の半導体素子104の外部接続用電極端子104eと配線基板101上の電極端子107との間は、ボンディングワイヤ109により接続されている。

【0044】

本実施形態に於ける特徴的構成として、前記第2の半導体素子104に於ける延出部の両端部近傍に於ける配線基板101上に、当該第2の半導体素子104の縁部(辺)に沿って、且つ当該半導体素子104の辺の長さと同等の長さを有する長尺状の導電性パッド110が配設され、当該導電性パッド110上に、前記第2の半導体素子104に於ける複数個の外部接続用電極端子104eそれぞれの略直下に位置して、バンプ111からなる凸状部材が配設されている。

【0045】

一方、配線基板1の一方の主面に於いては、半導体素子102、半導体素子104ならびにボンディングワイヤ108、109などを覆って、封止用樹脂112が被覆されている。

【0046】

更に、当該配線基板101の他方の主面には、格子状に配設された複数個の電極端子113上に、それぞれ外部接続用端子114が配設されている。

【0047】

かかる構成に於いて、前記配線基板101は、例えば、ガラス−エポキシ、ガラス−BT(ビスマレイミドトリアジン)、ポリイミド等の有機絶縁性樹脂、あるいはセラミック、ガラス、シリコン等の無機材料から形成される。そして、当該配線基板1の表面及び/あるいは内部には、所謂多層配線技術が適用されて、銅(Cu)などからなる配線ならびに電極端子が配設される。当該銅配線あるいは電極端子の表面には、必要に応じてニッケル(Ni)及び金(Au)からなる被覆層が配設されてもよい。

【0048】

当該配線基板101は、支持基板、回路基板あるいはインターポーザとも称される。

【0049】

また、前記半導体素子102、半導体素子104は、シリコン(Si)あるいはガリウム砒素(GaAs)などの半導体基板の一方の主面に、所謂ウエファープロセスが適用されて、トランジスタなどの能動素子、容量素子などの受動素子ならびにこれらの機能素子を相互に接続する配線層をもって電子回路が形成されており、当該配線層は当該半導体素子の外部接続用電極端子に接続されている。

【0050】

半導体素子102、半導体素子104は、配線基板101に対し、前記電子回路が形成された主面を上面(表出面)として搭載・配置されている。かかる状態をフェイスアップ状態と称する。

【0051】

また、当該半導体素子に於ける外部接続用電極端子と、配線基板1上に配設された電極端子との間を接続するボンディングワイヤ108、ボンディングワイヤ109は、金(Au)、銅(Cu)またはアルミニウム(Al)等の金属を主成分とする細線が適用される。

【0052】

そして、当該半導体素子の他方の主面に配設される接着剤層103、105は、ポリイミド系樹脂あるいはエポキシ系樹脂を主とする材料から構成される。当該接着剤は、銀(Ag)、金(Au)、パラジウム(Pd)、銅(Cu)等の導電性材料からなる微粒子を含有していてもよい。

【0053】

また、配線基板1上に配設される長尺状の導電性パッド110は、当該配線基板101に形成される配線、電極端子と同様に、銅(Cu)から形成される。当該導電性パッド110の表面には、必要に応じてニッケル(Ni)及び金(Au)からなる被覆層が配設されてもよい。

【0054】

そして、凸状部材として、当該導電性パッド110上に配設されるバンプ111は、所謂ボールボンディング法により形成された金属バンプからなる。

【0055】

尚、前記導電性パッド110は、後述する如く、長尺状の形状に換えて、バンプ111の配設位置に対応して個別化されて、即ち独立して配設されても良く、また複数のバンプ111毎に分割されて配設されても良い。

【0056】

また、前記樹脂封止部112を形成する樹脂部材としては、エポキシ樹脂を主体とする樹脂が適用される。

【0057】

更に、前記配線基板101の他方の主面に於いて、外部接続用端子113に配設される外部接続用端子114は、はんだボール(はんだバンプ)をもって形成される。

【0058】

この様に、本実施形態に於ける半導体装置100は、所謂BGA(Ball Grid Array)型半導体装置をなしている。

【0059】

従って、前記外部接続用端子113にはんだボールを配設せず、所謂LGA(Land Grid Array)型半導体装置とすることは、必要に応じて行うことができる。

【0060】

かかる半導体装置100にあっては、第1の半導体素子102上に搭載された第2の半導体素子104に於ける配線基板101からの離間部分、即ち第1の半導体素子102からの延出部に位置する外部接続用電極端子104eに対するボンディングワイヤ109の接続の際、当該第2の半導体素子104の被ワイヤボンディング部は、前記バンプ111によって機械的に支持される。

【0061】

これにより、当該ワイヤボンディング処理の際、第2の半導体素子104の湾曲が抑制され、第2の半導体素子104の破損が防止される。

【0062】

また、ボンディングキャピラリからの押圧力が有効に印加されて、ボンディングワイヤ109は、第2の半導体素子104の外部接続用電極端子104eに確実に接続される。

【0063】

次に、前記半導体装置100の製造方法について、図2及び図3を用いて説明する。

【0064】

尚、図2及び図3は、前記図1Bに示した断面に相当し、図1に示した構成要素と同一の構成要素には、同一の符号を付している。

【0065】

表面に電極端子106、107、113ならびに長尺状の導電性パッド110などが配設された配線基板101を、ダイボンダのボンディングステージ(図示せず)上に載置する。(図2A参照)

そして、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0066】

次いで、吸着コレット151によって上面(電子回路形成面)が吸着・保持された第1の半導体素子102を配線基板101上に載置し、当該吸着コレット151による押圧を伴って、当該第1の半導体素子102の裏面あるいは予め配線基板101の上面に選択的に配設された接着剤層103により、当該第1の半導体素子102を配線基板101上に固着する。(図2B参照)

当該接着剤層103は、塗布または貼付け等により予め配設される。

【0067】

なお、当該接着剤として、熱硬化性樹脂を適用しても良い。かかる場合には、第1の半導体素子102を配線基板101上に搭載した後、恒温槽またはホットプレート等により、例えば120℃〜240℃に加熱して、接着剤を半硬化または硬化せしめる。

【0068】

次いで、前記配線基板101をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0069】

そして、ワイヤボンディングツールに於けるボンディングキャピラリ161を用いての所謂ボールボンディング法を適用し、配線基板101に於ける長尺状の導電性パッド110の表面に、バンプ111を複数個形成する。(図2C参照)

かかる導電性パッド110の表面へのバンプ111の配設は、第2の半導体素子104に於ける外部接続用電極端子104eが配設された位置に対応するように行われる。

【0070】

そして、当該バンプ111の高さは、前記第1の半導体素子102の上面と略同等の高さとされる。(図2D参照)

即ち、当該バンプ111の高さは、第1の半導体素子102と接着剤層103との厚さからもたらされる高さと略一致する高さとされる。

【0071】

尚、当該導電性パッド110上ヘのバンプ111の配設工程と、前記第1の半導体素子102の配線基板101上への固着工程は、その順番を入れ換えてもよい。

【0072】

次いで、配線基板101を、ダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0073】

そして、吸着コレット152により上面(電子回路形成面)が吸着された第2の半導体素子104を、前記第1の半導体素子102上に載置し、当該吸着コレット152による押圧を伴って、当該第2の半導体素子104の裏面あるいは予め第1の半導体素子102の上面に選択的に配設された接着剤層105より、当該第2の半導体素子104を第1の半導体素子102上に固着する。(図2E参照)

この結果、前記バンプ111は、第2の半導体素子104に於ける外部接続用電極端子104eそれぞれの略直下に位置する。

【0074】

なお、前記接着剤層105を前記第2の半導体素子104の裏面全面に配設する場合には、前記バンプ111と前記第2の半導体素子104の裏面とを、前記接着剤層105を介して固着してもよい。

【0075】

しかる後、配線基板101をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0076】

そして、通常のボールボンディング法により、半導体素子の外部接続用電極端子と、これに対応する配線基板上の電極端子とを、ボンディングワイヤにより接続する。

【0077】

即ち、ボンディングキャピラリ162を用いて、前記第2の半導体素子104の外部接続用電極端子104eに、ボンディングワイヤ109の始端、即ちボール部を接続する。(図3A参照)

かかるボンディングワイヤ109の接続の際、第2の半導体素子104の外部接続用電極端子104eの被ワイヤボンディング部は、前記バンプ111により機械的に支持され、当該第2の半導体素子104の湾曲が抑制されて、その破損が防止される。

【0078】

また、超音波振動の吸収も防止され、押圧力が有効に印加されて、ボンディングワイヤ109は第2の半導体素子104の外部接続用電極端子104eに確実に接続される。

【0079】

即ち、配線基板101上にあって、バンプ111は、第2の半導体素子104の外部接続用電極端子104eの略直下に位置しており、当該第2の半導体素子104の外部接続用電極端子104eに対するボンディングワイヤ109の接続の際の押圧に対抗する。

【0080】

かかるワイヤボンディングの後、ボンディングワイヤ109の他端(終端)を、配線基板101上の電極端子107対しステッィチボンディング法により接続する。(図3B参照)

この時、当該ボンディングワイヤ109に、所望のルーピング形状を付与する。

【0081】

尚、当該第2の半導体素子104の外部接続電極端子104eと配線基板101上の電極端子107との間のワイヤボンディング処理の前あるいは終了後に、前記第1の半導体素子102の外部接続用電極端子102eと配線基板101上の電極端子105との間も、ボンディングワイヤ108を用いて接続する。(図示せず)

この様にして、半導体素子の外部接続電極端子と配線基板上の電極端子との間をワイヤボンディング法により接続した後、 配線基板101の主面上に形成された半導体素子の積層構造体を、ボンディングワイヤ108、109などと共に、封止用樹脂112より被覆する。(図3C参照)

封止用樹脂112の被覆方法としては、周知のトランスファーモールド法、コンプレッションモールド法、あるいはポッティング法を適用することができる。

【0082】

尚、かかる樹脂封止の際にも、第2の半導体素子104の延出部はバンプ111によって支持される。

【0083】

従って、トランスファーモールド法などに於ける、封止用樹脂112の流入圧力によって、当該第2の半導体素子104が変形あるいは破損することが防止される。

【0084】

しかる後、前記配線基板101の他方の主面に於ける電極端子113に対し、リフローソルダリング法等を用いて、はんだボール電極からなる外部接続用端子114を配設し、半導体装置100を形成する。(図3D参照)

尚、前記配線基板101が大判であって、当該配線基板101の一方の主面に、半導体素子の積層構造体が複数個形成される工程をとる場合(図示せず)には、前記外部接続用端子114の形成後、前記樹脂封止部112及び配線基板101をその積層方向(厚さ方向)に切断することにより、個片化された半導体装置100を得る。

【0085】

ここで、配線基板101上の導電性パッド110上に、バンプ111を、所謂ボールボンディング法により形成する工程について、図4を用いて説明する。

【0086】

ワイヤボンディングツールのボンディングキャピラリ161の先端から導出された金(Au)を主体とする金属からなるボンディングワイヤ171と、トーチ181との間に於いて放電を生じさせ、ボンディングワイヤ171の先端部にボール172を形成する。(図4A参照)

次いで、当該ボール172を、ボンディングキャピラリ161により荷重と超音波振動を付与しつつ、被接続部材、即ち配線基板101の表面に配設された導電性パッド110上に押圧し、当該導電性パッド110に接続する。(図4B参照)

かかる接続処理により、前記ボール172は変形し、導電性パッド110表面に対し、平板状部をもって接続される。

【0087】

尚、この時、ボンディングキャピラリ161により印加される荷重は、ボンディングワイヤ171の直径が15μmである場合には4gf乃至7gf程度とされ、当該ワイヤ172の径が20μmの場合には10gf乃至20gf程度とされる。

【0088】

また、かかるボンディング工程に於いて、前記配線基板101を保持するボンディングステージを100℃〜200℃に加熱してもよい。

【0089】

次いで、前記ボンディングキャピラリ161に於けるクランパ(図示せず)によりボンディングワイヤ171を保持した状態に於いて、当該ボンディングキャピラリ161を上昇せしめ、ボンディングワイヤ171を切断する(引きちぎる)。(図4C参照)

これにより、前記導電性パッド110上には、平版状基部111aとその上面に突出した突出部111bを有するバンプ111が形成される。

【0090】

当該バンプ111は、その適用箇所(配置箇所)に対応して、種々の変形が与えられる。

【0091】

即ち、一つには、当該バンプ111の突出部111bの形状が、適用箇所(配置箇所)に対応して変形される。また、当該バンプ111が、積層構造体とされる場合もある。

【0092】

かかるバンプ111の変形例を、図5を用いて説明する。

【0093】

例えば、前記半導体装置100に於いて、第2の半導体素子104の延出部の長さが長い、即ち下に位置する第1の半導体素子102の縁部からの延出長が長い場合には、当該第2の半導体素子104の外部接続用電極端子104eへのワイヤボンディングの際、当該第2の半導体素子104に於ける湾曲が大きくなる。

【0094】

かかる場合、第2の半導体素子104に於ける湾曲に対し、面接触状態をもって接する様、バンプ111の突出部111b上面を、当該第2の半導体素子104に於いて生ずる湾曲面に対応する傾斜面とする。(図5A参照)

即ち、バンプ111の突出部111b上面を、前記第1の半導体素子102側から第2の半導体素子104の延出方向に沿って降下する傾斜面とする。

【0095】

かかる傾斜面の形成は、前記図4に示す工程に於いて、ボール172のボンディング後、ボンディングワイヤ171を引きちぎる前に、ボンディングキャピラリ162を一旦上昇させ、更に水平方向に移動せしめた後、当該ボンディングキャピラリ162の先端部の傾斜した平面部分をボンディングワイヤ171の頭頂部に押し付けることにより行われる。

【0096】

その後、ボンディングワイヤ171を引きちぎり、上面に傾斜面を有する突出部111bを具備したバンプ111を形成する。

【0097】

一方、前記第2の半導体素子4の延出部の長さが短い場合などには、上面が平坦面とされた突出部を具備したバンプが配設される。(図5B参照)

かかる平坦面の形成は、前記図4に示す工程の後、バンプ111の頂部に、前記配線基板101と並行な平坦部を有するスタンピングツール又は平板状部材等を押し付けることにより行われる。

【0098】

なお、当該スタンピングツールまたは平板状部材等による押し付けは、個々のバンプ111単位で行っても、複数個のバンプ111に対して一括して行ってもよい。

【0099】

また、前記半導体装置100に於いて、第2の半導体素子104の延出部と、配線基板101の上面との間の離間距離が大きい場合、即ち前記第1の半導体素子102と接着剤層103とからなる積層構造体の厚さが大である場合などには、バンプ111を複数のバンプの積層構造体して構成する。(図5C参照)

かかる積層構造体は、前記図4に示した方法を繰り返すことにより形成することができる。当該多段(多層)積層バンプの配設により、第2の半導体素子4の延出部の支持を確実に行うことができる。

【0100】

尚、当該バンプ111の形成方法としては、前述のボールボンディング法の他、所謂選択めっき法を適用することもできる。

【0101】

従って、当該バンプ111の外形形状も、前記多段形状に限られず、柱状をなす場合もある。

【0102】

そして、当該バンプ111は、その配設位置及び/あるいは配設個数を、必要に応じて選択することができる。

【0103】

当該バンプ111の配設位置及び/あるいは配設個数の変形例について、図6を用いて説明する。

【0104】

尚、当該図6は、前記図1Aに於いて、破線Aにより囲繞された矩形領域を表示している。また、当該図6にあっては、第1の半導体素子104上に搭載される第2の半導体素子104、ボンディングワイヤ109、樹脂封止部112の表示を省略し、第2の半導体素子104の外形を破線で示している。

【0105】

前述の如く、半導体装置100にあっては、導電性パッド110の表面へのバンプ111の配設は、第2の半導体素子4に於ける外部接続用電極端子の配設された位置に対応するよう行われている。(図6A参照)

即ち、当該バンプ111は、第2の半導体素子104に於ける複数の外部接続用電極端子104eそれぞれの略直下に位置して配設されている。(図示される状態では10個)

この様な形態であれば、第2の半導体素子104に於ける複数の外部接続用電極端子104eに対するワイヤボンディングの際、個々の被ボンディング電極端子に印加される押圧に対してその直下に位置するバンプ111が対応して、良好なワイヤボンディングがなされる。

【0106】

かかる構成にあっては、第2の半導体素子104に於ける外部接続用電極端子104eの数に対応するバンプ111の配設が必要とされる。

【0107】

しかしながら、この様なバンプの配設構成では、第2の半導体素子104として、より多数の外部接続用端子を具備する半導体素子が適用された場合には、バンプ111の配設に要する時間の増加を招いてしまう。

【0108】

一方、第2の半導体素子104として、比較的小形あるいは細幅の長尺状の半導体素子が適用された場合には、当該半導体素子に於ける外部接続用電極端子に対応する数のバンプ111の配設を必要としない場合がある。

【0109】

かかる場合には、例えば、次の様なバンプ配設構成をとることができる。

【0110】

一つには、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部両隅部にのみ配設(計2個)する。(図6B参照)

又は、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部の辺の略中央部にのみ配設(1個)する。(図6C参照)

あるいは、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部両隅部、及び当該端部の辺の略中央部に配設(計3個)する。(図6D参照)

また、前記バンプ111は、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の外部接続用電極端子配列の線上に位置することに限られず、当該外部接続用電極端子配列の線上から内側あるいは外側に偏寄して配置してもよい。(図示せず)

これらのバンプ配設構造に於いては、前記導電性パッド110は、長尺状である必要はなく、バンプ111が配設される箇所に対応して、選択的に配設されることを可とする。

【0111】

この様なバンプ111の選択的配設構成によれば、当該バンプ111の配設個数を低減することができ、配設工程の低コスト化、効率化を図ることができる。

【0112】

前記半導体装置100にあっては、更に種々の変形が可能である。

【0113】

一つには、前記第2の半導体素子104に於ける外部接続用電極端子104eと配線基板101上の電極端子107との間を接続するボンディングワイヤ109の接続法として、所謂リバースボンディング法を適用することができる。

【0114】

かかるリバースボンディング法が適用された形態を半導体装置130として、図7に示す。同図に於いて、前記図1に示す構成と対応する部位には同一の符号を付している。

【0115】

図7に示される様に、半導体装置130にあっては、ボンディングワイヤ109の始端であるボール部が配線基板101上の電極端子107に接続され、当該ボンディングワイヤ109の他端(終端)が第2の半導体素子104に於ける外部接続用電極端子104e上に配設されたバンプ115に接続されている。

【0116】

かかるリバースボンディング法を適用した場合であっても、ボンディングワイヤ109の他端(終端)を第2の半導体素子104に於ける外部接続用電極端子104eに接続する際、当該第2の半導体素子104に対してボンディングツールの押圧力が印加される。

【0117】

また、当該接続に先立つ、第2の半導体素子104の外部接続用電極端子104e上へのバンプ115の配設は、前記図4を用いて説明した方法と同様に、所謂ボールボンディング法が用いられて行なわれる。

【0118】

従って、このバンプ115の配設の際にも、第2の半導体素子104に対し、ボンディングツールの押圧力が印加される。

【0119】

かかるボンディングツールの押圧力に対し、前記バンプ111は対抗して、第2の半導体素子104を支持し、当該第2の半導体素子104の変形、破損を防止する。

【0120】

この様なリバースボンディング法を適用することにより、前記半導体装置100に於ける通常のワイヤボンディング法に比較して、ボンディングワイヤ109に於けるワイヤループの高さを低くすることができる。

【0121】

これにより、当該半導体装置130にあっては、樹脂封止部の高さ(厚さ)の増加を招来せず、より高さの低い(厚さの薄い)半導体装置を形成することができる。

【0122】

また、前記半導体装置100にあっては、第2の半導体素子104は、第1の半導体素子102上に於いて、当該第1の半導体素子102の対向する2辺から双方向に庇状に延出して搭載されている。

【0123】

しかしながら、第1の半導体素子102の形態によっては、当該第1の半導体素子102上に於ける第2の半導体素子104の搭載位置、ならびにその延出方向が特定あるいは制限される場合がある。

【0124】

即ち、例えば半導体記憶素子の様に、外部接続用電極端子が当該半導体素子のほぼ中央部に位置し、且つ当該半導体記憶素子の長手方向に列状に配設される形態がある。

【0125】

この様な半導体素子を第1の半導体素子102として配線基板1上にフェイスアップ状態をもって搭載し、当該第1の半導体素子102上に第2の半導体素子104を搭載する場合には、当該第1の半導体素子102の外部接続用電極端子に対するボンディングワイヤ108の接続を可能とする為に、当該第1の半導体素子102に於ける外部接続用電極端子の配列に沿う2辺の一方が開放され、第2の半導体素子104は当該辺に於いて庇状(片持ち梁状)に延出して搭載される必要がある。

【0126】

かかる半導体素子の搭載形態を含む半導体装置構造を、半導体装置140として図8に示す。

【0127】

図8Aは、当該半導体装置140の平面を示し、また図8Bは、図8Aに於けるX−X’断面を示す。なお、図8Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0128】

当該半導体装置140にあっては、支持基板である配線基板101の一方の主面上に、二つの半導体素子が積層配置されている。

【0129】

即ち、当該配線基板101上には、第1の半導体素子102が接着剤層103を介して、所謂フェイスアップ状態をもって搭載されており、また当該第1の半導体素子102上には、第2の半導体素子104が、接着剤層105を介してフェイスアップ状態をもって搭載されている。

【0130】

そして、第1の半導体素子102にあっては、その表面のほぼ中央部に、複数個の外部接続用電極端子102eが列状に配設されている。

【0131】

また、第2の半導体素子104は、当該第1の半導体素子102上に於いて、当該第1の半導体素子102に於ける外部接続用電極端子102eの配設部を避け、且つ当該第1の半導体素子102の外部接続用電極端子102eの配列と並行な辺の一方から、庇状(片持ち梁状)に延出(突出)して搭載されている。

【0132】

この為、第1の半導体素子102の側部に於いて、第2の半導体素子104の延出(突出)部と支持基板101との間は離間している。

【0133】

当該第1の半導体素子102は、配線基板101と第2の半導体素子104との間に位置して中間部材をなしている。

【0134】

かかる配設構成にあっては、第2の半導体素子104の延出部の長さ(突出量)は、第2の半導体素子104の延出方向に並行な辺の長さの1/2よりも大きい。

【0135】

すなわち、第2の半導体素子104の延出部の面積は、当該第2の半導体素子104が第1の半導体素子102上に固着される面積よりも大きい。

【0136】

そして、第2の半導体素子104の外部接続用電極端子104eは、当該第2の半導体素子104の対向する2辺に沿ってそれぞれ複数個配設されており、その一方の配列は前記第1の半導体素子102に於ける外部接続用電極端子102eの配列に近接し、略並行している。また、他方の配列は、延出(突出)部に於いて、第1の半導体素子102からより遠い領域に位置している。

【0137】

一方、前記配線基板101の主面上には、前記第1の半導体素子102の外部接続用電極端子102eに対応して電極端子106が複数個配設され、また前記第2の半導体素子104の外部接続用電極端子104eに対応して電極端子107が複数個配設されている。

【0138】

当該電極端子107の一部は、前記電極端子106の配列の外側に位置し、且つ略並行して配設されている。

【0139】

そして、当該第1の半導体素子102の外部接続用電極端子102eと、前記配線基板101上の電極端子106との間はボンディングワイヤ108より接続され、第2の半導体素子104の外部接続用電極端子104eと、前記配線基板101上の電極端子107との間はボンディングワイヤ109より接続されている。

【0140】

ここでは、前記第1の半導体素子102の外部接続用電極端子102eに対するボンディングワイヤ108の接続法として、ならびに第2の半導体素子104の当該第1の半導体素子102上に位置する外部接続用電極端子104eに対するボンディングワイヤ109の接続法として、リバースボンディング法が適用されている。

【0141】

即ち、第1の半導体素子102の外部接続用電極端子102e上に配設されたバンプ121にボンディングワイヤ108の終端が接続され、一方、第2の半導体素子104の第1の半導体素子102上に位置する外部接続用電極端子104e上に配設されたバンプ122にボンディングワイヤ109の終端が接続されている。

【0142】

これらのボンディングワイヤ108、ボンディングワイヤ109は、その延在する方向がほぼ同一であることから、互いの接触を防止しつつワイヤループの高さを抑制するうえで、当該リバースボンディング法は有効である。

【0143】

かかる半導体装置140に於ける特徴的構成として、第2の半導体素子104の延出(突出)部に於ける配線基板101上に、当該第2の半導体素子104の縁部(辺)に沿って、且つ当該第2の半導体素子104の辺の長さと同等の長さを有する長尺状の導電性パッド110が配設されている。当該導電性パッド110上には、第2の半導体素子104に於ける複数個の外部接続用電極端子104eそれぞれの略直下に位置して、バンプ111が配設されている。

【0144】

そして、前記第2の半導体素子104の延出(突出)部に於ける外部接続用電極端子104eに対しては、通常のワイヤボンディング法により、ボンディングワイヤ109sが接続されている。

【0145】

また、当該配線基板101の一方の主面に於いて、前記半導体素子102、半導体素子104ならびにボンディングワイヤ108、ボンディングワイヤ109などを覆って、封止用樹脂112が配設されている。

【0146】

更に、当該配線基板101の他方の主面には、格子状に配設された電極端子113上にはんだボール(はんだバンプ)からなる外部接続用端子114が配設されている。

【0147】

かかる半導体装置140にあっては、第2の半導体素子104の延出(突出)部の長さ(延出長)が比較的大きくなることから、前記バンプ111の配設の有効性は高い。

【0148】

すなわち,第2の半導体素子104に於ける外部接続用電極端子104eにボンディングワイヤ109sの始端を接続する際、当該第2の半導体素子104の被ワイヤボンディング部はバンプ111により機械的に支持される。従って、当該第2の半導体素子104の湾曲が抑制され、当該第2の半導体素子104の破損が防止される。

【0149】

更に、第2の半導体素子104を第1の半導体素子102上に搭載する際に、当該バンプ111によって支持しながら搭載することが可能であるため、第2の半導体素子104を第1の半導体素子102上に傾斜することなく、精度良く積層配設することができる。

【0150】

これにより、半導体装置に於ける第1の半導体素子102と第2の半導体素子104との配置構成の設計自由度が向上する。

(実施形態2)

本発明による半導体装置の実施形態その2について、図9乃至図13用いて説明する。

【0151】

本実施形態に於ける半導体装置は、支持基体である配線基板上にフェイスダウン(フリップチップ)状態をもって搭載され、その外部接続用バンプ電極が当該配線基板上の電極端子に接続される第1の半導体素子と、当該第1の半導体素子上にフェイスアップ状態をもって搭載され、その電極端子パッドがワイヤボンディング法により前記配線基板上の電極端子に接続される第2の半導体素子とを含む。

【0152】

実施形態その2にかかる半導体装置200を、図9に示す。

【0153】

図9Aは、当該半導体装置200の平面を示し、また図9Bは、図9Aに於けるX−X’断面を示す。なお、図9Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0154】

当該半導体装置200にあっては、支持基体である配線基板201の一方の主面上に、二つの半導体素子が積層配置されている。

【0155】

即ち、当該配線基板201上には、第1の半導体素子202が、所謂フェイスダウン(フリップチップ)状態をもって搭載され、その電極端子(図示せず)上に配設された外部接続用突起(バンプ)電極202eにより、配線基板201上の電極端子203に接続されている。

【0156】

そして、当該第1の半導体素子202上に、第2の半導体素子204が、接着剤層205を介してフェイスアップ状態をもって搭載されている。

【0157】

ここで、前記第1の半導体素子202は比較的小さな平面形状を有しており、長方形を有する第2の半導体素子204は、当該第1の半導体素子202上に於いて、当該第1の半導体素子202の幅を越えて庇状(片持ち梁状)に延出(突出)して搭載されている。

【0158】

この為、第1の半導体素子202の側部に於いて、第2の半導体素子204の延出(突出)部と配線基板201との間は離間している。

【0159】

当該第1の半導体素子202は、配線基板201と第2の半導体素子204との間に位置して中間部材をなしている。

【0160】

そして、第1の半導体素子202と配線基板201との間には、所謂アンダーフィル材206が充填されている。

【0161】

当該アンダーフィル材206は、配線基板201の、第1の半導体素子202と対向する領域よりも外方に裾状に拡がって配設され、前記第1の半導体素子202の外部接続用突起(バンプ)電極202eと配線基板201上の電極端子203との間の接続を保護するとともに、第1の半導体素子202と配線基板201とを固着する。

【0162】

尚、前記第1の半導体素子202の外部接続用突起電極202eは、当該半導体素子202の主表面(電子回路形成面)に於いて、4つの縁部に沿ってそれぞれ複数個配設されている。

【0163】

また、前記第2の半導体素子204の外部接続用電極端子204eは、当該第2の半導体素子204の長手方向の両端の縁部に沿ってそれぞれ複数個配設されている。

【0164】

一方、前記配線基板201の主面上には、前述の如く、第1の半導体素子202の外部接続用突起電極202eに対応して電極端子203が複数個配設され、また前記第2の半導体素子204の外部接続用電極端子204eに対応して電極端子207が複数個配設されている。

【0165】

そして、第1の半導体素子202の外部接続用突起電極202eと、前記配線基板201上の電極端子201eとの間は圧接接続され、一方、第2の半導体素子204の外部接続用電極端子204eと、前記配線基板201上の電極端子207との間はボンディングワイヤ208により接続されている。

【0166】

尚、第1の半導体素子202の外部接続用突起電極202eは、例えば金(Au)、銅(Cu)、あるいはニッケル(Ni)等を主成分とする合金材料、錫(Sn)−銀(Ag)、錫(Sn)−銀(Ag)−銅(Cu)を主成分とする半田材料、あるいは銀(Ag)等の金属粒子を含有する導電性樹脂材料から形成されている。

【0167】

また、前記アンダーフィル材206は、熱硬化性あるいは熱可塑性の絶縁性樹脂を主体として形成され、例えばエポキシ系、ポリイミド系、アクリル系、あるいはシリコン系樹脂が適用される。

【0168】

尚、当該アンダーフィル材206は、その適用量が比較的少であることから、封止用部材と同一の物性を有するか否かは問われない。

【0169】

本実施形態に於ける特徴的構成として、前記第2の半導体素子204の長手方向の両端部近傍に於ける配線基板201上に、当該第2の半導体素子204の縁に沿って、且つ当該半導体素子204の縁の長さと同等の長さを有する長尺状の導電性パッド209が配設されている。

【0170】

当該導電性パッド209上には、前記第2の半導体素子204に於ける複数個の電極端子204eそれぞれの略直下に位置して、凸状部材であるバンプ210が配設されている。

【0171】

そして、配線基板201の一方の主面に於いて、前記半導体素子202、半導体素子204ならびにボンディングワイヤ208などを覆って、封止用樹脂211が被覆されている。

【0172】

更に、当該配線基板201の他方の主面には、格子状に配設された電極端子212上に、はんだボール(はんだバンプ)からなる外部接続用端子213が配設されている。

【0173】

かかる構成によれば、第1の半導体素子202がフリップチップ方式により搭載されることから、当該半導体素子202からのボンディングワイヤの導出、ならびに当該半導体素子202周囲の配線基板201上への電極端子の配設を必要とせず、半導体装置として大形化を招来しない。

【0174】

尚、外部接続用突起電極202eの適用により、第1の半導体素子202の背面の高さ、即ち当該第1の半導体素子202上に搭載される第2の半導体素子204と配線基板201の表面との離間距離(間隔)は大きなものとなる。しかしながら、第2の半導体素子204の厚さならびにバンプ210の高さを選択して、ワイヤボンディング時に於ける当該第2の半導体素子204の撓み量を制限することにより、当該第2の半導体素子204の破損は防止される。

【0175】

当該実施形態その2にかかる半導体装置200の製造方法について、図10乃至図12を用いて説明する。

【0176】

先ず、主面に電極端子204、207ならびに電極端子212などが配設された配線基板201を準備し、その一方の主面(半導体素子搭載面)に於ける、第1の半導体素子202の搭載予定部にアンダーフィル材206を被着する。(図10A参照)

当該配線基板201は、必要に応じて多層配線構造がとられる。またアンダーフィル材206は、ノズル251を介して当該配線基板201上に選択的に滴下される。

【0177】

次いで、配線基板201を、フリップチップボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜150℃に加熱する。

【0178】

そして、予め所定温度、例えば150℃〜300℃に加熱したボンディングツール261によりその背面(電子回路非形成面)が吸着・保持された第1の半導体素子202を、前記配線基板201上に位置せしめる。(図10B参照)

当該ボンディングツール261による押圧および加熱を伴って、当該第1の半導体素子202の外部接続用突起電極202eを、配線基板201上の電極端子203に接続する。(図10C参照)

即ち、当該第1の半導体素子202は、フェイスダウン形態をもって搭載される。

【0179】

この結果、前記アンダーフィル材206は、当該第1の半導体素子202と配線基板201との間の空間を埋めると共に、当該第1の半導体素子202の周囲に於いて裾拡がり状に拡がり、硬化する。(図10D参照)

かかるアンダーフィル材206の配設により、配線基板201の電極端子201eへの

第1の半導体素子202の外部接続用突起電極202eの接続が強化されると共に、当該第1の半導体素子202と配線基板201との間の空間への水分などの侵入が防止される。

【0180】

次いで、配線基板201をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0181】

そして、ボンディングキャピラリ271を用いての所謂ボールボンディング法を適用して、当該配線基板201に於ける長尺状の導電性パッド209の表面に、バンプ210を複数個形成する。(図11A参照)

かかる導電性パッド209の表面へのバンプ210の配設は、第2の半導体素子204に於ける外部接続用電極端子の配設された位置に対応するよう行われる。そして、当該バンプ210の高さは、前記第1の半導体素子202の背面の位置する高さと略同等の高さあるいはこれより若干低い高さとされる。(図11B参照)

即ち、当該バンプ210の高さは、外部接続用突起電極202eを含む第1の半導体素子202の厚さからもたらされる高さと略一致するかあるいはこれより若干低い高さとされる。当該バンプ210の高さが、外部接続用突起電極202eを含む第1の半導体素子202の厚さからもたらされる高さよりも若干低い高さとされる場合には、その高さは、後の工程で配設され、ワイヤボンディングがなされる第2の半導体素子204に於ける撓み量が、許容値を越えることのない高さとされる。

【0182】

次いで、前記配線基板201を、ダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0183】

そして、吸着コレット262によりその上面(電子回路形成面)が吸着された第2の半導体素子204を第1の半導体素子202上に載置し、当該吸着コレット262による押圧を伴って、当該第2の半導体素子204の裏面あるいは予め第1の半導体素子202の上面に選択的に配設された接着剤層205より、当該第2の半導体素子204を第1の半導体素子202上に固着する。(図11C参照)

この結果、前記バンプ210は、第2の半導体素子204に於ける外部接続用電極端子204eそれぞれの略直下に位置することとなる。

【0184】

しかる後、配線基板201をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0185】

そして、ボンディングキャピラリ272を用いてのボールボンディング法により、前記第2の半導体素子204の外部接続用電極端子204eに、ボンディングワイヤ208の始端を接続する。(図12A参照)

かかるボンディングワイヤ208の接続の際、前記バンプ210によって、第2の半導体素子204の被ワイヤボンディング部は機械的に支持され、当該第2の半導体素子204の湾曲が抑制され、その破損が防止される。

【0186】

また、超音波振動の吸収も防止され、押圧力が有効に印加されて、ボンディングワイヤ208は第2の半導体素子204の外部接続用電極端子204eに確実に接続される。

【0187】

即ち、配線基板201上にあって、バンプ210は、第2の半導体素子204の外部接続用電極端子204eの略直下に位置しており、当該第2の半導体素子204の外部接続用電極端子204eに対するボンディングワイヤ208の接続の際の押圧に対抗する。

【0188】

かかるワイヤボンディングの後、前記ボンディングワイヤ208の他端(終端)を、配線基板201上の電極端子207にステッィチボンディング法により接続する。(図12B参照)

この時、当該ボンディングワイヤ208には、所望のルーピング形状を付与する。

【0189】

次いで、前記配線基板201の主面上に形成された半導体素子の積層構造体は、ボンディングワイヤと共に封止用樹脂211により被覆される。(図12C参照)

樹脂被覆方法としては、前述の如くトランスファーモールド法、コンプレッションモールド法、あるいはポッティング法を適用することができる。

【0190】

尚、かかる樹脂封止の際にも、第2の半導体素子204の延出部はバンプ210によって支持される。従って、トランスファーモールド法などに於ける、封止用樹脂211の流入圧力による第2の半導体素子204の湾曲が抑制され、その破損が防止される。

【0191】

しかる後、前記配線基板201の他方の主面に於ける電極端子212に、リフローソルダリング法等を用いて、はんだボール電極からなる外部接続用端子213を配設し、半導体装置200を形成する。(図12D参照)

尚、前記配線基板201が大判であって、当該配線基板201の一方の主面に、半導体素子の積層構造体が複数個形成される工程をとる場合(図示せず)には、前記外部接続用端子213の形成後、前記樹脂封止部211及び配線基板201をその積層方向(厚さ方向)に切断することにより、個片化された半導体装置200を得る。

【0192】

また、前記第2の半導体素子204に於ける第1の半導体素子202からの延出量(長)が大である場合には、前記バンプ210の突出部上面形状として、前記図5Aをもって説明したところの、「第1の半導体素子202側から第2の半導体素子204の延出方向に向かって降下する傾斜面」を適用することもできる。(図13A参照)

かかる構成により、第2の半導体素子204に於ける外部接続用電極端子204eへのワイヤボンディングの際、当該バンプ210は、当該半導体素子204に生ずる湾曲に対し面接触状態をもって接する。(図13B参照)

これにより、当該半導体素子204はその湾曲が抑制され、破損が防止される。

(実施形態3)

本発明による半導体装置の実施形態その3について、図14乃至図22を用いて説明する。

【0193】

本実施形態その3に於ける半導体装置は、支持基体である配線基板上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により当該配線基板上の電極端子に接続される第1の半導体素子と、当該第1の半導体素子上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により前記配線基板上の電極端子に接続される第2の半導体素子、ならびに当該第2の半導体素子上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により前記配線基板上の電極端子に接続される第3の半導体素子を具備する。

【0194】

かかる実施形態その3に於ける半導体装置300を、図14に示す。

【0195】

図14Aは、当該半導体装置300の平面を示し、また図14Bは、図14Aに於けるX−X’断面を示す。尚、図14Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0196】

当該半導体装置300にあっては、支持基体である配線基板301の一方の主面上に、3個の半導体素子が積層されて搭載されている。

【0197】

即ち、当該配線基板301上には、第1の半導体素子302が接着剤層303を介して、所謂フェイスアップ状態をもって搭載されており、当該第1の半導体素子302上には、第2の半導体素子304が、接着剤層305を介してフェイスアップ状態をもって搭載され、更に当該第2の半導体素子304上には、第3の半導体素子306が、接着剤層307を介してフェイスアップ状態をもって搭載されている。

【0198】

ここで、第1の半導体素子302は長方形状を有し、配線基板301上に於いて、一方向(X方向)に搭載されている。

【0199】

また第2の半導体素子304も長方形状を有し、第1の半導体素子302上に於いて、当該第1の半導体素子302の幅をY方向に越えて庇状(片持ち梁状)に延出(突出)して搭載されている。この為、第1の半導体素子302の側部に於いて、第2の半導体素子304の延出(突出)部と支持基板301との間は離間している。

【0200】

更に、第3の半導体素子306も長方形状を有し、第2の半導体素子304上に、前記第1の半導体素子302と同一の方向(X方向)に搭載され、当該第1の半導体素子302の略直上に位置して搭載されている。

【0201】

即ち、第1乃至第3の半導体素子は、互いにその上あるいは下に位置する半導体素子と、略直交して交差した状態をもって積層配置されている。

【0202】

そして、第2の半導体素子304は、第1の半導体素子302と第3の半導体素子306との間に位置し、中間部材をなしている。

【0203】

かかる構成に於いて、前記第1の半導体素子302の外部接続用電極端子302eは、前記第2の半導体素子304が延出する2辺とは異なる2辺に沿ってそれぞれ複数個配設されている。

【0204】

また、第2の半導体素子304の外部接続用電極端子304eは当該第2の半導体素子304の長手方向の両端の2辺に沿ってそれぞれ複数個配設されている。

【0205】

更に、前記第3の半導体素子306の外部接続用電極端子306eは、前記第2の半導体素子304が延出する2辺とは異なる2辺に沿ってそれぞれ複数個配設され、前記第1の半導体素子302の外部接続用電極端子302eの略直上に位置している。

【0206】

一方、前記配線基板301の主面上には、前記第1の半導体素子302の外部接続用電極端子302eに対応して電極端子308が配設され、また前記第2の半導体素子304の外部接続用電極端子304e対応して電極端子309が配設されている。

【0207】

更に、第3の半導体素子306の外部接続用電極端子306e対応して電極端子310が、前記第1の半導体素子302に対応する電極端子308の配列に並行して複数個配設されている。

【0208】

そして、当該第1の半導体素子302の外部接続用電極端子302eと前記配線基板301上の電極端子308との間は、リバースボンディング法によって、ボンディングワイヤ311より接続されている。

【0209】

一方、第2の半導体素子304の外部接続用電極端子304eと前記配線基板301上の電極端子309との間は、順ボンディング法によってボンディングワイヤ312により接続されている。また、第3の半導体素子306の外部接続用電極端子306eと、前記配線基板301上の電極端子310との間も、順ボンディング法によってボンディングワイヤ313より接続されている。

【0210】

本実施形態に於ける特徴的構成として、前記第1の半導体素子302の外部接続用電極端子302eに於いて、当該外部接続用電極端子302eに接続されたボンディングワイヤ311の終端上に、凸状部材であるバンプが配設されている。

【0211】

即ち、第1の半導体素子302の外部接続用電極端子302e上には、バンプ314aが配設され、当該バンプ314a上にはボンディングワイヤ311の終端が接続され、更に当該ボンディングワイヤ311の終端部上に第2のバンプ314bが配設されている。そして、当該積層構造を有するバンプ314は、第3の半導体素子306の外部接続用電極端子306eの略直下に位置している。

【0212】

尚、前記第2の半導体素子304は、第1の半導体素子302からの延出量(長)が少である。

【0213】

従って、配線基板301上に於ける、当該第2の半導体素子304の辺に沿っての長尺状の導電性パッドの配設、並びに当該導電性パッド上への第2の半導体素子304に於ける外部接続用電極端子304eに対応するバンプの配設は行っていない。

【0214】

当該第2の半導体素子304の、第1の半導体素子302からの延出量(長)が多い場合などには、当該バンプの配設が必要に応じてなされる。

【0215】

そして、当該配線基板301の一方の主面に於いて、前記半導体素子302、半導体素子304、半導体素子306ならびにボンディングワイヤ311、312、313などを覆って封止用樹脂315が被覆されている。

【0216】

更に、当該配線基板301の他方の主面には、格子状に配設された電極端子316上に、はんだボール(はんだバンプ)からなる外部接続用端子317が配設されている。

【0217】

かかる半導体装置300にあっては、前記第2の半導体素子304上に搭載された第3の半導体素子306に於ける第1の半導体素子302からの離間部分、即ち第2の半導体素子304からの延出部に位置する外部接続用電極端子306eに対するボンディングワイヤの接続の際、第1の半導体素子302の外部接続用電極端子302e上に配設されたバンプ314によって、当該第3の半導体素子306の被ワイヤボンディング部は機械的に支持され、当該第3の半導体素子306の湾曲が抑制され、その破損が防止される。

【0218】

また、ボンディングキャピラリからの押圧力が有効に印加されて、ボンディングワイヤ313は、第3の半導体素子306の外部接続用電極端子306eに確実に接続される。

【0219】

この時、第1の半導体素子302は、配線基板301に比べて反りあるいはうねりが小さい。従って、当該第1の半導体素子302の外部接続用電極端子302e上にバンプ314を複数個配設する際、これらのバンプはその上面の高さがより均一に形成される。

【0220】

従って、第3の半導体素子306の外部接続用電極端子306eに対するワイヤボンディング処理の際、当該第3の半導体素子306をより確実に支持することができる。

【0221】

また、外部接続用電極端子302e上のバンプ314aに接続されたボンディングワイヤ311上に、更にバンプ314bを配設することにより、ボンディングワイヤ311と外部接続用電極端子302eとの接続が強化され、半導体装置300の信頼性を向上することができる。

【0222】

次に、かかる構成を有する半導体装置300の製造方法について、図15乃至図17を用いて説明する。

【0223】

先ず、表面に電極端子308、309、310ならびに316などが配設された配線基板301を、ダイボンダのボンディングステージ(図示せず)上に載置する。(図15A参照)

そして、当該ボンディングステージに配設されたヒーターにより、当該配線基板301を所定温度、例えば50℃〜200℃に加熱する。

【0224】

次いで、吸着コレット351によりその上面(電子回路形成面)が吸着・保持された第1の半導体素子302を前記配線基板301上に載置し、当該吸着コレット351による押圧を伴って、当該第1の半導体素子302の裏面あるいは配線基板301の上面に予め選択的に配設された接着剤層303により、当該第1の半導体素子302を配線基板301上に固着する。(図15B参照)

次いで、吸着コレット352によりその上面(電子回路形成面)が吸着された第2の半導体素子304を第1の半導体素子302上に載置し、当該吸着コレット352による押圧を伴って、当該第2の半導体素子304の裏面あるいは第1の半導体素子302の上面に予め選択的に配設された接着剤層305より、当該第2の半導体素子304を第1の半導体素子302上に固着する。(図15C参照)

前記接着剤層305は、塗布または貼付け等により予め配設される。

【0225】

なお、当該接着剤として、熱硬化性樹脂を適用しても良い。かかる場合には、第1の半導体素子302を配線基板301上に搭載した後、恒温槽またはホットプレート等により、例えば120℃〜240℃に加熱して、接着剤を半硬化せしめる。

【0226】

次いで、前記配線基板301をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0227】

そして、ボンディングキャピラリ361を用いての所謂ボールボンディング法を適用して、前記第1の半導体素子302に於ける外部接続用電極端子302eそれぞれの表面に、バンプ314aを形成する。(図15D、図15E参照)

次いで、ボンディングキャピラリ371を用い、リバースボンディング法を適用して、ボンディングワイヤ311の始端であるボール部を配線基板301上の電極端子308に接続する。

【0228】

そして、当該ボンディングワイヤ311の他端(終端)を、第1の半導体素子304の外部接続用電極端子304e上に配設されているバンプ314aへ接続する。(図16A、図16B参照)

この時、当該ボンディングワイヤ311には、所望のルーピング形状を付与する。

【0229】

しかる後、再びボンディングキャピラリ361を用いての所謂ボールボンディング法を適用して、前記バンプ314aに接続されたボンディングワイヤ311の終端部上に、第2のバンプ314bを形成する。(図16C、図16D参照)

即ち、バンプ314aならびにバンプ314bは、積層構造をもってバンプ314を構成する。

【0230】

次いで、配線基板301をダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターによって所定温度、例えば50℃〜200℃に加熱する。

【0231】

そして、吸着コレット353によりその上面(電子回路形成面)が吸着された第3の半導体素子306を第2の半導体素子304上に載置し、当該吸着コレット353による押圧を伴って、当該第3の半導体素子306の裏面あるいは予め第2の半導体素子304の上面に選択的に配設された接着剤層307より、当該第3の半導体素子306を第2の半導体素子304上に固着する。(図16E参照)

この時、当該第3の半導体素子306に於ける外部接続用電極端子306eは、第1の半導体素子302の外部接続用電極端子302eの上に配設されたバンプ314の略直上に位置する。

【0232】

なお、前記接着剤層307を前記第3半導体素子306裏面全面に配設する場合には、前記バンプ314と前記第3半導体素子306の裏面とを、当該接着剤層307を介して固着してもよい。

【0233】

次いで、前記配線基板301をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0234】

そして、ボンディングキャピラリ371を用いて、前記第3の半導体素子306の外部接続用電極端子306eに、ボンディングワイヤ313の始端を接続する。(図17A参照)

かかるボンディングワイヤ313の接続の際、第3の半導体素子306の被ワイヤボンディング部は、バンプ314によって機械的に支持され、当該第3の半導体素子306の湾曲が抑制され、その破損が防止される。

【0235】

また、超音波振動の吸収も防止され、押圧力が有効に印加されて、ボンディングワイヤ313は第3の半導体素子306の外部接続用電極端子306eに確実に接続される。

【0236】

即ち、配線基板301上にあって、バンプ314は、第3の半導体素子306の外部接続用電極端子306eの略直下に位置しており、当該第3の半導体素子306の外部接続用電極端子306eに対するボンディングワイヤの接続の際の押圧に対抗する。

【0237】

そして、当該ボンディングワイヤ313の他端(終端)を、配線基板301上の電極端子310に対し、ステッィチボンディング法により接続する。(図17B参照)

この時、当該ボンディングワイヤ313には、所望のルーピング形状を付与する。

【0238】

尚、かかる第3の半導体素子306の外部接続用電極端子306eと配線基板301上の電極端子310との間のワイヤボンディング処理の前あるいは終了後に、前記第2の半導体素子304の外部接続用電極端子304eと配線基板301上の電極端子309との間も、ボンディングワイヤ312を用いてのワイヤボンディング法により接続する。(図示せず)

次いで、前記配線基板301の主面上に形成された半導体素子の積層構造体は、ボンディングワイヤと共に封止用樹脂315により被覆される。(図17C参照)

当該樹脂被覆を施す方法としては、周知のトランスファーモールド法、コンプレッションモールド法、あるいはポッティング法を適用することができる。

【0239】

尚、かかる樹脂封止の際にも、第3の半導体素子306の延出部はバンプ314によって支持される。従って、トランスファーモールド法などに於ける封止用樹脂315の流入圧力による第3の半導体素子306の湾曲が抑制され、変形あるいは破損が防止される。

【0240】

しかる後、前記配線基板301の他方の主面に於ける電極端子316に、リフローソルダリング法等を用いて、はんだボール電極からなる外部接続用端子317を配設し、半導体装置300を形成する。(図17D参照)

尚、前記配線基板301が大判であって、当該配線基板301の一方の主面に、半導体素子の積層構造体が複数個形成される工程をとる場合(図示せず)には、前記外部接続用端子316の形成後、前記樹脂封止部315及び配線基板301をその積層方向(厚さ方向)に切断することにより、個片化された半導体装置300を得る。

【0241】

また、前記第1の半導体素子302に於ける外部接続用電極端子302eそれぞれの表面に配設されたバンプ314は、その配設位置及び/あるいは配設形体を、必要に応じて選択することができる。

【0242】

当該バンプ314の配設位置及び/あるいは配設形体の変形例について、図18を用いて説明する。尚、当該図18は、前記図14Aに於いて、破線Aにより囲繞された矩形領域を表示している。

【0243】

当該図18にあっては、第2の半導体素子304上に搭載される第3の半導体素子306、ボンディングワイヤ313、並びに樹脂封止部315の表示を省略している。

【0244】

前述の如く、半導体装置300にあっては、第1の半導体素子302の外部接続用電極端子302e上へのバンプ314の配設は、当該第1の半導体素子302に於ける外部接続用電極端子302eの全て(図示される状態では10個)に対して行われている。(図18A参照)

かかる構成により、第3の半導体素子306に於ける複数の外部接続用電極端子306eに対するワイヤボンディングの際、個々の被ボンディング電極端子に印加される押圧に対しその直下に位置するバンプ314が対応して、良好なワイヤボンディングがなされる。

【0245】

しかしながら、かかる場合には、少なくとも第3の半導体素子306に於ける外部接続用電極端子306eに対応する数のバンプの配設が必要とされる。

【0246】

そして、当該バンプ314は、第1の半導体素子302の外部接続用電極端子302e上のバンプ314aの配設、当該バンプ314a上へのボンディングワイヤ311の終端の接続、更に当該ボンディングワイヤ311の終端接続部へのバンプ314bの配設との工程がとられる。

【0247】

この様な多段構成を有するバンプ314の適用は、前記第3の半導体素子306として、より大形の半導体素子あるいは多機能を有して多数の外部接続用電極端子306eを具備する半導体素子が適用された場合には、当該バンプ314の配設工程に要する時間の増加を招いてしまう。

【0248】

一方、当該第3の半導体素子306として、比較的小形あるいは長尺状の半導体素子が適用された場合には、当該半導体素子に於ける外部接続用電極端子に対応する数のバンプ314の配設を必要としない場合がある。

【0249】

この様な場合、例えば次の様なバンプ配設構成をとることができる。

【0250】

一つには、前記バンプ314bを、第1の半導体素子302に於ける外部接続用電極端子302e配列に於いて、両端部に位置する外部接続用端子に於けるバンプ314a上へのボンディングワイヤ311の終端部上のみに配設(計2個)する。(図18B参照)

あるいは、当該バンプ314bを、第1の半導体素子302に於ける外部接続用電極端子302e配列の内、選択された複数個(ここでは計4個)の外部接続用端子に於けるバンプ314a上のボンディングワイヤ311の終端部に対し配設する。(図18C参照)

すなわち、前記ボンディングワイヤ311の終端が接続されたバンプ314aの全てに 対してバンプ314bを配設することは行わず、その配設箇所を適宜選択する。

【0251】

この様に、バンプ314bの配設箇所を選択すること、すなわち積層バンプ314の配設形体を選択することにより、当該バンプ314の配設工程の効率化を図ることができる。

【0252】

また、当該第1の半導体素子302に於ける外部接続用電極端子302e上へのバンプ314の配設構成は、次の様な形態をとることもできる。

【0253】

一つに、第1の半導体素子302に於ける外部接続用電極端子302eの平面形状を長尺状のものとし、その一方の端部側を被ワイヤボンディング領域とし、他方の端部近傍をバンプ314の配設部とする。(図19A参照)

尚、当該図19Aも、前記図14Aに於いて、破線Aにより囲繞された矩形領域を表示している。

【0254】

そして、当該図19Aにあっても、第3の半導体素子306、当該第3の半導体素子306の外部接続用電極端子306eから導出され電極端子310へ接続されるボンディングワイヤ313、ならびに樹脂封止部315については、図示することを省略している。

【0255】

即ち、かかる構成にあっては、第1の半導体素子302の外部接続用電極端子302eに於いて、ボンディングワイヤ311の被ワイヤボンディング部と、バンプ314の配設部とを重畳しない。

【0256】

かかる電極端子構成を採用することにより、当該第1の半導体素子302の外部接続用電極端子302eに対するワイヤボンディング方法として、ボンディングワイヤの始端であるボールを接続する通常のワイヤボンディング法を適用する(図19B参照)こと、あるいはボンディングワイヤの終端を接続するリバースボンディング法を適用する(図19C参照)ことの、何れをも選択して適用することができる。

【0257】

尚、リバースボンディング法を適用する際には、外部接続用電極端子302eの被ワイヤボンディング部には予めバンプ321が配設される。

【0258】

この様な被ワイヤボンディング部とバンプ配設部の分離により、第3の半導体素子306の外部接続用電極端子306eへのワイヤボンディングの際、当該第3の半導体素子306の外部接続用電極端子306eの被ワイヤボンディング部直下にバンプは存在していないが、当該第3の半導体素子306の撓み部は有効に支持される。

【0259】

また、当該第1の半導体素子302の外部接続用電極端子302e上に、バンブ314a及びバンプ314bを積層して配設する際、両バンプ間にボンディングワイヤが介在されない為、当該バンプ間の接続がより強固になされ、また積層されたバンプの高さの決定が容易となる。従って、積層されるバンプの高さを、第2の半導体素子304の上面と略同等の高さとし、当該バンプの上面が第3の半導体素子306の底面に接することを可能とすることも容易である。

【0260】

一方、第1の半導体素子302に於いて、その外部接続用電極端子302eとバンプの配設部とを分離しても良い。

【0261】

即ち、外部接続用電極端子302eの配列の近傍であって、且つ当該外部接続用電極端子302eの配列とは異なる位置に、バンプ配設部325を配置する。(図20A参照)

当該バンプ配設部325は、前記外部接続用電極端子302eと同様の材料から形成された端子パッド部と、その上に形成された少なくとも一つのバンプを含む。当該バンプは必要に応じて複数個積層される。

【0262】

尚、当該図20Aも、前記図14Aに於いて、破線Aにより囲繞された矩形領域を表示している。

【0263】

そして、当該図20Aにあっても、第3の半導体素子306、当該第3の半導体素子306の外部接続用電極端子306eから導出され電極端子310へ接続されるボンディングワイヤ313、ならびに樹脂封止部315については、図示することを省略している。

【0264】

この様な、バンプ配設部325の分離・孤立配設により、第3の半導体素子306の外部接続用電極端子306eへのワイヤボンディングの際、当該第3の半導体素子306の外部接続用電極端子306eの直下にバンプは存在していないが、当該第3の半導体素子306の撓み部は有効に支持される。

【0265】

そして、かかる電極端子構成を採用することによっても、当該第1の半導体素子302の外部接続用電極端子302eに対するワイヤボンディング方法として、ボンディングワイヤの始端であるボールを接続する通常のワイヤボンディング法を適用する(図20B参照)こと、あるいはボンディングワイヤ311の終端を、バンプ321を介して接続するリバースボンディング法を適用する(図20C参照)ことの、何れをも選択して適用することができる。

【0266】

また、当該第1の半導体素子302のバンプ配設部325に於いて、バンブを積層して配設する際には、バンプ間にボンディングワイヤが介在されない為、バンプ間の接続がより強固になされ、また積層されるバンプの高さの決定が容易となる。

【0267】

更に、他の手段として、第1の半導体素子302に於ける外部接続用電極端子302eとバンプの配設部とを分離しても良い。

【0268】

即ち、当該外部接続用電極端子302e配列の両端部近傍に、当該外部接続用電極端子302eから離間して、バンプ配設部325を配置する。(図21A参照)

尚、当該図21Aも、前記図14Aに於いて、破線Aにより囲繞された矩形領域を表示している。

【0269】

そして、当該図21Aにあっても、第3の半導体素子306、当該第3の半導体素子306の外部接続用電極端子306eから導出され電極端子310へ接続されるボンディングワイヤ313、ならびに樹脂封止部315については、図示することを省略している。

【0270】

この様にバンプ配設部325が分離されて孤立した配置構成にあっては、第3の半導体素子306の外部接続用電極端子306eへのワイヤボンディングの際、当該第3の半導体素子306の外部接続用電極端子306eの直下にバンプは存在していない。しかしながら、2個のバンプによって当該第3の半導体素子306は有効に支持される。

【0271】

そして、かかる電極端子構成を採用する場合であっても、当該第1の半導体素子302の外部接続用電極端子302eに対するワイヤボンディング方法として、ボンディングワイヤの始端であるボールを接続する通常のワイヤボンディング法を適用する(図21B参照)こと、あるいはボンディングワイヤの終端を接続するリバースボンディング法を適用する(図21C参照)ことの何れをも選択して適用することができる。

【0272】

かかる形体にあっても、第1の半導体素子302の外部接続用電極端子302eにバンブを積層して配設する際には、バンプ間にボンディングワイヤが介在されない為、当該バンプ間の接続がより強固になされ、また積層されたバンプの高さの決定が容易となる。

【0273】

ところで、前記実施態様その3にあっては、第1の半導体素子302と第3の半導体素子306が同一方向に、且つ重畳して配置され、両者の間に配置された第2の半導体素子304がこれらの半導体素子とは異なる方向に、即ち第1の半導体素子302と第3の半導体素子306とは交差する如く配設されている。

【0274】

しかしながら、半導体装置として求められる機能を満たす為に、上記形態とは異なる積層配置構造が採られる場合がある。

【0275】

即ち、例えば図22に示される半導体装置330の如く、配線基板301上に、第1の半導体素子302が接着剤層303を介して、所謂フェイスアップ状態をもって搭載され、当該第1の半導体素子302上に、第2の半導体素子304が、接着剤層305を介してフェイスアップ状態をもって且つ前記第1の半導体素子301と同一方向(Y方向)に搭載され、一方、当該第2の半導体素子304上には、第3の半導体素子306が、接着剤層307を介してフェイスアップ状態をもって且つ当該第2の半導体素子304とは異なる方向(X方向)に搭載される場合がある。

【0276】

ここで、第1の半導体素子302は長方形状を有し、配線基板301上に於いて、一方向(Y方向)に搭載されている。

【0277】

また、第2の半導体素子304も長方形状を有し、第1の半導体素子302上に、当該第1の半導体素子302と同一方向(Y方向)に搭載されている。但しその外形寸法は第1の半導体素子302よりも小であって、それぞれの外部接続端子は重畳する位置関係にはない。

【0278】

そして、第3の半導体素子306は長方形状を有し、前記第2の半導体素子304上に、当該第2の半導体素子304の幅をX方向に越えて庇状(片持ち梁上)に延出(突出)して搭載されている。この為、第2の半導体素子304の側部に於いて、当該第3の半導体素子306の延出(突出)部と支持基板301との間は離間している。

【0279】

即ち、第3の半導体素子306は、第1及び第2の半導体素子の積層構造体とは、互いに直交して交差した状態をもって積層配置されている。

【0280】

当該第1の半導体素子302並びに第2の半導体素子304は、配線基板301と第3の半導体素子306との間に位置して中間部材をなしている。

【0281】

かかる構成に於いて、前記第1の半導体素子302の外部接続用電極端子302eは、前記第3の半導体素子306が延出する2辺とは異なる2辺に沿ってそれぞれ複数個配設されている。

【0282】

また、第2の半導体素子304の外部接続用電極端子304eも、前記第3の半導体素子306が延出する2辺とは異なる2辺に沿ってそれぞれ複数個配設されている。

【0283】

即ち、第1の半導体素子302の外部接続用電極端子配列と、第2の半導体素子304の外部接続用電極端子配列は、互いに並行して位置する。

【0284】

一方、第3の半導体素子306の外部接続用電極端子306eは、第2の半導体素子304からの延出部の端部の辺に沿って複数個配設されている。

【0285】

そして、前記配線基板301の主面上には、前記第1の半導体素子302の外部接続用電極端子302eに対応する電極端子308が複数個列状に配設され、また前記第2の半導体素子304の外部接続用電極端子304eに対応する電極端子309が、前記第301の半導体素子302に対応する電極端子308の配列に並行して複数個列状に配設されている。

【0286】

更に、第3の半導体素子306の外部接続用電極端子306eに対応して電極端子310が複数個列状に配設されている。

【0287】

そして、第1の半導体素子302の外部接続用電極端子302eと、前記配線基板301上の電極端子308との間はボンディングワイヤ311により接続され、第2の半導体素子304の外部接続用電極端子304eと、前記配線基板301上の電極端子309との間はボンディングワイヤ312により接続されている。

【0288】

また、第3の半導体素子306の外部接続用電極端子306eと、前記配線基板301上の電極端子310との間もボンディングワイヤ313により接続されている。

【0289】

かかる実施形態に於ける特徴的構成として、第2の半導体素子304の幅をX方向に越えて庇状(片持ち梁上)に延出(突出)している第3の半導体素子306の電極端子306eの直下に位置する配線基板301の表面には、当該第3の半導体素子306の短辺に沿って、長尺状導電パターン331が配設され、当該導電パターン331上に、前記第3の半導体素子306の電極端子306eの略直下に位置して、バンプ332が複数個配設されている。

【0290】

ここでは、当該バンプ332は、二つのバンプの積層構造を有している。

【0291】

かかる半導体装置にあっては、第2の半導体素子304上に搭載された第3の半導体素子306に於ける配線基板301からの離間部分、即ち当該第2の半導体素子304からの延出部に位置する外部接続用電極端子306eに対するボンディングワイヤ313の接続の際、前記配線基板301上の導電パターン331上に配設されたバンプ332によって、当該第3の半導体素子306の被ワイヤボンディング部は機械的に支持される。

【0292】

従って、当該第3の半導体素子306の湾曲が抑制されて、その破損が防止される。

【0293】

また、ボンディングキャピラリからの押圧力が有効に印加されて、ボンディングワイヤ313は、当該第3の半導体素子306の外部接続用電極端子306eに確実に接続される。

(実施形態4)

前述の如く、配線基板上に複数個の半導体素子を積層して搭載・配設する際に、当該半導体素子間に、所謂スペーサ部材を配設して積層構造を形成する場合がある。

【0294】

かかるスペーサ部材を適用してなる半導体素子の搭載形態を含む半導体装置構造を、本発明による半導体装置の実施形態その4として、図23に示す。

【0295】

図23Aは、当該実施形態その4にかかる半導体装置400の平面を示し、また図23Bは、図23Aに於けるX−X’断面を示す。尚、図23Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0296】

即ち、当該半導体装置400にあっては、支持基体である配線基板401上に、第1の半導体素子402が、接着剤層403を介して、所謂フェイスアップ状態をもって搭載されており、当該第1の半導体素子402上に、スペーサ404が、接着剤層405を介して搭載されている。

【0297】

そして、当該スペーサ404上に、第2の半導体素子406が、接着剤層407を介して、フェイスアップ状態をもって搭載されている。

【0298】

ここで、第1の半導体素子402は長方形状を有し、配線基板401上に於いて、一方向(X方向)に搭載されている。

【0299】

また、第2の半導体素子406も長方形状を有し、スペーサ404上に於いて、前記第1の半導体素子402と同じ一方向(X方向)に搭載され、当該第1の半導体素子402の直上に位置している。

【0300】

当該スペーサ404は、第1の半導体素子402と第2の半導体素子406との間に位置して中間部材をなしている。

【0301】

そして、当該スペーサ404は、その上に配置される第2の半導体素子406よりも小なる平面形状・面積を有している。

【0302】

当該スペーサ404としては、半導体素子と同様の熱膨張係数を有する材料、例えば板状のシリコン(Si)片が適用される。

【0303】

また、第2の半導体素子406の外部接続用電極端子406eは、第1の半導体素子402の外部接続用電極端子402eの略直上に位置している。

【0304】

一方、前記配線基板401の主面上には、前記第1の半導体素子402の外部接続用電極端子402eに対応して電極端子408が複数個配設され、また第2の半導体素子406の外部接続用電極端子406eに対応して電極端子409が、前記第1の半導体素子402に対応する電気端子408の配列に並行して、複数個配設されている。

【0305】

そして、前記第1の半導体素子402の外部接続用電極端子402eと、配線基板401上の電極端子408との間はボンディングワイヤ410により接続され、また第2の半導体素子406の外部接続用電極端子406eと、前記配線基板401上の電極端子409との間はボンディングワイヤ411により接続されている。

【0306】

本実施形態に於ける特徴的構成として、前記第1の半導体素子402の外部接続用電極端子402e上にはバンプ412aが配設され、リバースボンディング法により当該バンプ412aに接続されたボンディングワイヤ410の終端上に、バンプ412bが配設されている。

【0307】

この様に、凸状部材であるバンプ412は積層構造体(多段バンプ)であって、前記第2の半導体素子406の外部接続用電極端子406eの略直下に位置している。

【0308】

当該第1の半導体素子402の外部接続用電極端子402e上に配設されるバンプ構造を形成する方法としては、例えば前記図15D乃至図16Dに示される方法を適用することができる。

【0309】

そして、当該配線基板401の一方の主面に於いて、前記半導体素子402、半導体素子406ならびにボンディングワイヤ410、411などを覆って、封止用樹脂413が被覆されている。

【0310】

更に、当該配線基板401の他方の主面には、格子状に配設された電極端子414に、はんだボール(はんだバンプ)からなる外部接続用端子415が配設されている。

【0311】

かかる半導体装置400にあっては、前記スペーサ404上に搭載された第2の半導体素子406に於ける第1の半導体素子402からの離間部分、即ちスペーサ404からの延出部に位置する外部接続用電極端子406eに対するボンディングワイヤ411の接続の際、前記第1の半導体素子402の外部接続用電極端子402e上に配設されたバンプ412によって、当該第2の半導体素子406の被ワイヤボンディング部は機械的に支持されて、当該第2の半導体素子406の湾曲が抑制され、その破損が防止される。

【0312】

また、ボンディングキャピラリからの押圧力が有効に印加されて、ボンディングワイヤ411は、第2の半導体素子406の外部接続用電極端子406eに確実に接続される。

【0313】

この様に、スペーサ404を適用してなる半導体素子積層構造に於いては、配線基板401上に搭載される第1の半導体素子402が、当該第1の半導体素子402上にスペーサ404を介して搭載される第2の半導体素子406よりも小面積である場合、あるいは第2の半導体素子406が第1の半導体素子402上から何れかの方向に延出する状態をもって搭載される。

【0314】

かかる場合、第1の半導体素子402の外部接続用電極端子402eがボンディングワイヤ410を介して接続される配線基板401上の電極端子408の配設構成、ならびに第2の半導体素子406の外部接続用電極端子406eの略直下に位置して配設されるバンプ412の配設構成を選択することができる。

【0315】

即ち、スペーサ404介しての第1の半導体素子402及び第2の半導体素子406の積層構造に於いて、当該第2の半導体素子406に於ける前記第1の半導体素子402の縁部からの延出量(長)が比較的少(短)である場合、当該第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410が接続される配線基板401上の電極端子408に於いて、積層して配設されたバンプ412下に当該ボンディングワイヤ410の終端が配設された構造とすることができる。

【0316】

かかる構成を、図24に示す。尚、図24Bは、図24AのX−X’断面を示す。

【0317】

この時、当該バンプ412の積層数は、必要とされる高さに応じて選択される。

【0318】

かかる構造によれば、第2の半導体素子406の外部接続用電極端子406eに対するボンディングワイヤ411の接続の際、バンプ412の存在により、当該第2の半導体素子406の破損が防止されると共に、当該第2の半導体素子406の外部接続用電極端子406eに対して高い信頼性をもってワイヤボンディングがなされる。

【0319】

一方、前記第2の半導体素子406に於ける第1の半導体素子402の縁部からの延出量(長)が比較的大(長)である場合には、当該第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410が接続される配線基板401上の電極端子408の形成構造を、以下の様に変更する必要がある。

【0320】

即ち、ボンディングワイヤ410の長さの増大を抑え、インダクタンスの増加を防止することが必要とされる。

【0321】

この為、一つには、前記第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410が接続される配線基板上の電極端子408の形状を長尺状のものとし、その一方の端部、即ち第1の半導体素子側402の近傍端部を被ワイヤボンディング領域とし、他方の端部をバンプ412の配設部とする。

【0322】

かかる構成を図25に示す。尚、図25Bは、図25AのX−X’断面を示す。

【0323】

この様な配線基板401上の電極端子構成によれば、第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410の実効長の増加を招くことはなく、当該ボンディングワイヤ410のインダクタンスの増加を招来しない。

【0324】

また、かかる手段に代えて、前記第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410が接続される配線基板上の電極端子408と、多段バンプ412が配設される導電パターン421を分離してもよい。

【0325】

かかる構成を図26に示す。尚、図26Bは、図26AのX−X’断面を示す。

【0326】

当該導電パターン421は、当該配線基板401上の電極端子配列に沿う長尺状を有し、その表面に、第2の半導体素子406の外部接続用電極端子406eに対応してバンプ412が配設される。

【0327】

この様な配線基板401上の電極端子、導電層の配置構成によっても、第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410の実効長の増加を招くことがなく、当該ボンディングワイヤ410のインダクタンスの増加を招来しない。

【0328】

一方、前記第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410に於けるインダクタンスの抑制を必要とせず、バンプの配設工程の簡略化が必要とされる場合には、前記第1の半導体素子402の外部接続用電極端子402eから導出されるボンディングワイヤ410が接続される電極端子配列を、第2の半導体素子406の延出端部よりも外側に配置し、当該第2の半導体素子406の延出部の隅部に対応してバンプ412の配設部422を配置してもよい。

【0329】

かかる構成を図27に示す。尚、図27Bは、図27AのX−X’断面を示す。

【0330】

かかる配線基板401上の電極端子構成によれば、バンプ412の配設工程が簡略化され、当該半導体装置400の製造コストを低減することができる。

(実施形態5)

本発明による半導体装置の実施形態その5について、図28乃至図31を用いて説明する。

【0331】

本実施形態その5に於ける半導体装置は、所謂リードフレームが用いられて形成される樹脂封止型半導体装置である。

【0332】

そして、当該リードフレーム構造体から形成されたダイステージ上に、フェイスアップ状態をもって搭載され、その電極端子パッドがワイヤボンディング法によりインナーリードに接続される第1の半導体素子と、当該第1の半導体素子上に配設されたスペーサ、ならびに当該スペーサ上にフェイスアップ状態をもって搭載され、その電極端子パッドがワイヤボンディング法により前記インナーリードに接続される第2の半導体素子を具備する。

【0333】

かかる構成に於いて、前記第1の半導体素子ならびに第2の半導体素子は、半導体記憶素子(半導体メモリー)などの同一機能を有する半導体素子であって、共通の信号端子あるいは電源端子に接続される電極端子が、同一のインナーリードに接続される。

【0334】

また、前記スペーサは、第2の半導体素子よりも小なる平面形状・面積を有する。

【0335】

本実施形態にかかる半導体装置500を、図28に示す。

【0336】

図28Aは、当該半導体装置500の平面を示し、また図28Bは、図28Aに於けるX−X’断面を示す。尚、図28Aにあっては、樹脂封止部の表示を省略し、その外形を破線で示している。

【0337】

当該半導体装置500は、所謂TSOP(Thin Small Outline Package)型の半導体装置である。

【0338】

即ち、所謂リードフレーム構造体から形成されたダイステージ501aと、当該ダイステージ501aの周囲に配設された複数のリード501bを具備する。

【0339】

ここでは、当該リード501bは、略矩形状を有するダイステージ501aの、対向する2辺に沿って配設されている。

【0340】

そして、前記ダイステージ501aには、第1の半導体素子502が、接着剤層503をもって搭載・固着されている。

【0341】

当該第1の半導体素子502の外部接続用電極端子502eと、前記リード501bのインナーリード部501b1との間は、ボンディングワイヤ504により接続されている。

【0342】

ここでは、当該ボンディングワイヤ504の始端がリード501bのインナーリード部501b1に接続され、その終端が第1の半導体素子502の外部接続用電極端子502e上に配設されたバンプ505に接続されている。

【0343】

当該バンプ505は、後述する如く、外部接続用電極端子502e上に配設されてボンディングワイヤ504の終端が接続されるバンプ505aと、当該バンプ505a上に配設されたバンプ505bとの積層(縦積み)構造を有する。

【0344】

また、当該第1の半導体素子502の上面(電子回路形成面)のほぼ中央部には、当該半導体素子と同様の熱膨張係数を有する材料、例えばチップ状シリコン片からなるスペーサ506が接着剤層507をもって固着されている。

【0345】

そして、当該スペーサ506上には、第2の半導体素子508が接着剤層509をもって搭載・固着されている。

【0346】

前記スペーサ506は、第1の半導体素子502と第2の半導体素子508との間に位置して中間部材をなしている。

【0347】

かかる構成に於いて、第2の半導体素子508は、スペーサ506よりも大なる平面形状を有し、当該スペーサ506の周囲に於いて、第1の半導体素子502との間が離間している。

【0348】

そして、当該第2の半導体素子508の外部接続用電極端子508eと、前記リード501bのインナーリード部501b1との間は、ボンディングワイヤ510により接続されている。

【0349】

ここでは、当該ボンディングワイヤ510の始端がリード501bのインナーリード部501b1に接続され、その終端が第2の半導体素子508の外部接続用電極端子508e上に配設されたバンプ511に接続されたリバースボンディング法が適用されている。

【0350】

尚、前記第1の半導体素子502、第2の半導体素子508が、同一の端子構成を有する半導体記憶素子である場合には、第1の半導体素子502の特定の電極端子(例えばアドレスA1)と、これに対応する第2の半導体素子508の特定の電極端子(例えばアドレスA1)は、それぞれボンディングワイヤを介して、一つのインナーリード部501b1に共通に接続される。

【0351】

他のアドレス端子、データ端子も同様に、対応する端子毎に、共通に対応するリード501bに接続される。

【0352】

但し、第1の半導体素子502並びに第2の半導体素子508に於けるチップセレクト端子は、リード501bの、それぞれ異なるインナーリード部501b11、501b12に接続される。

【0353】

かかる構成に於いて、前記第1の半導体素子502の外部接続用電極端子502eには、前述の如く、バンプ505aが配設され、当該バンプ505aに対して、ボンディングワイヤ504の終端が接続されている。そして、当該ボンディングワイヤ504の終端接続部上には、更にバンプ505bが配設されて、積層(縦積み)構造を有するバンプ505とされている。

【0354】

この様に、積層(縦積み)構造を有する凸状部材であるバンプ505の上面の高さは、前記スペーサ506の上面の高さとほぼ同等の位置とされている。

【0355】

そして、これらの第1の半導体素子502、第2の半導体素子508の積層構造体、ボンディングワイヤ504、510、ならびにリードフレーム構造体501の一部を被覆して、封止用樹脂512が配設されている。

【0356】

当該半導体装置500にあっては、半導体素子の支持部材あるいは外部接続端子としてリードフレーム構造体が適用される為、前記実施形態1乃至4に於ける半導体装置の如く、配線基板、はんだボール電極などを用いる半導体装置と比較して、製造コストを低下せしめることができる。

【0357】

かかる本発明の実施形態その5にかかる半導体装置500の製造方法について、図29乃至図31を用いて説明する。

【0358】

先ず、リードフレーム構造体501に於けるダイステージ501a上に、エポキシ系樹脂あるいはポリイミド系樹脂を主とする材料からなる接着剤503が、ノズル551を介して被着される。(図29A参照)

当該接着剤503は、銀(Ag)、金(Au)、パラジウム(Pd)、銅(Cu)等の導電性材料からなる微粒子を含有していてもよい。

【0359】

次いで、吸着コレット561により、その上面(電子回路形成面)が吸着・保持された第1の半導体素子502が、前記接着剤503上に押圧される。

【0360】

かかる押圧により、前記接着剤503は第1の半導体素子502とダイステージ501aとの間に拡がり、当該第1の半導体素子503は、ダイステージ501a上に搭載される。(図29B参照)

次いで、オーブン、ヒーターブロック等により例えば、150℃〜200℃に加熱して、前記接着剤503を硬化せしめ、第1の半導体素子502をダイステージ501a上に固着する。(図29C参照)

次いで、前記リードフレーム構造体501を、ダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0361】

そして、吸着コレット562に吸着・保持されたスペーサ506を、前記第1の半導体素子502の上面(電子回路形成面)のほぼ中央部に配設・固着する。(図29D参照)

当該スペーサ506は、シリコン(Si)片からなり、その被固着面には予め接着剤層507が被覆されている。

【0362】

次いで、前記リードフレーム構造体501をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば150℃〜300℃に加熱する。

【0363】

そして、前記第1の半導体素子502の外部接続用電極端子502eのそれぞれに、バンプ505aを配設する。(図29E参照)

当該バンプ505aは、ボンディングキャピラリ571を用いての所謂ボールボンディング法によって形成することができる。

【0364】

次いで、前記第1の半導体素子502の外部接続用電極端子502eとこれに対応するリードフレーム構造体501に於けるリード501bとの間を、ボンディングキャピラリ581を用いて、ボンディングワイヤ504により接続する。(図30A参照)

ここで、当該ボンディングワイヤ504は、その始端がリード501bのインナーリード部501b1に接続され、その終端は第1の半導体素子502の外部接続用電極端子502eに配設されているバンプ505a上に接続される。

【0365】

次いで、前記ボンディングワイヤ504の終端が接続されたバンプ505a上に、ボンディングキャピラリ571を用いてバンプ505bを配設する。(図30B参照)

即ち、第1の半導体素子502の外部接続用電極端子502e上には、バンプ505a及びバンプ505bが積層(縦積み)状態をもって配設される。

【0366】

当該積層(縦積み)状態のバンプ505の上面の高さは、前記スペーサ506の上面の高さとほぼ同等とされる。

【0367】

しかる後、リードフレーム構造体501を、ダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0368】

そして、吸着コレット563により、その上面(電子回路形成面)が吸着・保持された第2の半導体素子508を、前記スペーサ506上に配置し、押圧する。

【0369】

当該第2の半導体素子508の裏面には、予め接着剤509が被着されていることにより、当該第2の半導体素子508は、スペーサ506上に固着される。(図30C参照)

この時、当該第2の半導体素子508は、その外部接続用電極端子508eが、積層(縦積み)構造体とされているバンプ505の略直上に位置して固着される。

【0370】

尚、接着剤層509を前記第2の半導体素子508の裏面全面に配設する場合には、前記バンプ505と前記第2の半導体素子508の裏面とを、当該接着剤層509を介して固着してもよい。

【0371】

次いで、ボンディングキャピラリ571を用いての所謂ボールボンディング法により、第2の半導体素子508の外部接続用電極端子508eのそれぞれに、バンプ511を配設する。(図30D参照)

かかるバンプ511の配設の際、第2の半導体素子508の被ボンディング部は、前記バンプ505によって機械的に支持され、当該第2の半導体素子508の湾曲が抑制され、その破損が防止される。

【0372】

また、押圧力が有効に印加されて、バンプ511は第2の半導体素子508の外部接続用電極端子508eに確実に接続・配設される。

【0373】

即ち、第1の半導体素子502の外部接続用電極端子502e上に位置するバンプ505は、第2の半導体素子508の外部接続用電極端子508eの略直下に位置していることから、当該第2の半導体素子508の外部接続用電極端子508eに対するバンプ511の配設の際の押圧に対抗する。

【0374】

次いで、前記第2の半導体素子508の外部接続用電極端子508eと、これに対応するリードフレーム構造体501に於けるリード501bとの間を、ボンディングキャピラリ581を用いて、ボンディングワイヤ510により接続する。(図30E参照)

ここで、当該ボンディングワイヤ510の始端がリード501bのインナーリード部501b1に接続され、またその終端は第2の半導体素子508の外部接続用電極端子508e上に配設されているバンプ511に接続される。

【0375】

かかるボンディングワイヤ510の終端の接続の際、第2の半導体素子508の被ボンディング部は、前記バンプ505によって機械的に支持され、当該第2の半導体素子508の破損が防止される。

【0376】

また、押圧力が有効に印加されて、ボンディングワイヤ510の終端は第2の半導体素子508の外部接続用電極端子508eに確実に接続される。

【0377】

即ち、第1の半導体素子502の外部接続用電極端子502e上に位置するバンプ505は、第2の半導体素子508の外部接続用電極端子508eの略直下に位置していることから、当該第2の半導体素子508の外部接続用電極端子508eに対するボンディングワイヤ510の終端の接続の際の押圧に対抗する。

【0378】

次いで、前記半導体素子の積層構造体は、ボンディングワイヤ、リードフレーム構造体501と共に封止用樹脂512により被覆される。(図31A参照)

当該樹脂被覆は、周知のトランスファーモールド法を適用して行うことができる。

【0379】

この時、前記リード501bのアウターリード部501b2は、封止用樹脂512により被覆されず、露出される。

【0380】

次いで、前記アウターリード部501b2に対する半田めっき処理を施した後、リードフレーム構造体501の切断・分離、ならびに曲げ加工を行い、個別の半導体装置500を形成する。(図31B参照)

本発明は、本実施形態5に於けるTSOP型半導体装置の他、J型の外部接続端子を有する所謂SOJ(Small Out−line J−leaded Package)型半導体装置、あるいは外部接続端子を4方向に配置した所謂QFP(Quad Flat Package)型半導体装置にも適用することができる。

【0381】

そして、本発明は前記実施形態に示した構成に限定されるものではなく、本発明思想を逸脱しない範囲に於いて、種々変形することができる。

以下に本発明の特徴を付記する。

(付記1)

電極端子が配設された支持基体と、

前記支持基体上に搭載された中間部材と、

一部が前記中間部材により支持されて、前記支持基体上に配設された半導体素子と、

前記半導体素子の電極端子に対応して、前記支持基体上あるいは前記中間部材上に配設された凸状部材と

を具備し、

前記半導体素子の電極端子と前記支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置。

(付記2)

前記中間部材は、他の半導体素子あるいはスペーサ部材であることを特徴とする付記1記載の半導体装置。

(付記3)

電極端子が配設された支持基板と、

前記支持基板上に搭載された第1の半導体素子と、

一部が前記第1の半導体素子により支持されて、前記支持基板上に配設された第2の半導体素子と、

前記第2の半導体素子の電極端子に対応して、前記支持基板上に配設された凸状部材と

を具備し、

前記第2の半導体素子の電極端子と前記支持基板上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置。

(付記4)

電極端子が配設された支持基板と、

前記支持基板上に搭載されたスペーサ部材と、

一部が前記スペーサ部材により支持されて、前記支持基板上に配設された半導体素子と、

前記半導体素子の電極端子に対応して、前記支持基板上に配設された凸状部材と

を具備し、

前記半導体素子の電極端子と前記支持基板上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置。

(付記5)

電極端子が配設された支持基板と、

前記支持基板上に搭載された第1の半導体素子と、

前記第1の半導体素子上に搭載されたスペーサ部材と、

一部が前記スペーサ部材により支持されて、前記支持基板上に配設された第2の半導体素子と、

前記第2の半導体素子の電極端子に対応して、前記第1の半導体素子上に配設された凸状部材と

を具備し、

前記第2の半導体素子の電極端子と前記支持基板上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置。

(付記6)

ダイステージと、

前記ダイステージの周囲に配設された複数のリードと、

前記ダイステージ上に搭載された第1の半導体素子と、

前記第1の半導体素子上に配置されたスペーサと、

一部が前記スペーサに支持されて前記第1の半導体素子上に配設された第2の半導体素子と、

前記第2の半導体素子の電極端子に対応して、前記第1の半導体素子上に配設された凸状部材と

を有し、

前記第2の半導体素子の電極端子と前記リードが、ボンディングワイヤにより接続されてなることを特徴とする半導体装置。

(付記7)

前記凸状部材は、金属バンプであることを特徴とする付記1乃至6の何れか1項に記載の半導体装置。

(付記8)

前記第2の半導体素子は、前記第1の半導体素子から前記支持基板上に片持ち梁状に延出してなることを特徴とする付記3記載の半導体装置。

(付記9)

電極端子が配設された支持基体上に、中間部材を搭載する工程と、

前記支持基体上に、凸状部材を配設する工程と、

前記中間部材上に、半導体素子をフェイスアップ状態をもって搭載する工程と、

前記半導体素子の電極端子と前記支持基体の電極端子とをワイヤボンディング法により接続する工程と

を含むことを特徴とする半導体装置の製造方法。

(付記10)

電極端子が配設された支持基板上に、第1の半導体素子を搭載する工程と、

前記支持基板上に、凸状部材を配設する工程と、

前記第1の半導体素子上に、第2の半導体素子をフェイスアップ状態をもって搭載する工程と、

前記第2の半導体素子の電極端子と前記支持基板の電極端子とをワイヤボンディング法により接続する工程と

を含むことを特徴とする半導体装置の製造方法。

(付記11)

前記凸状部材は、金属バンプでありボールボンディング法により形成されることを特徴とする付記8又は9記載の半導体装置の製造方法。

(付記12)

前記第1の半導体素子上に前記第2の半導体素子を搭載する工程に於いて、

前記第1の半導体素子上に、第2の半導体素子を片持ち梁状に延出せしめて搭載することを特徴とする付記10記載の半導体装置の製造方法。

(付記13)

前記第1の半導体素子上に前記第2の半導体素子を搭載する工程に於いて、

前記第1の半導体素子上にスペーサ部材を搭載してから、第2の半導体素子を配設する

ことを特徴とする付記10記載の半導体装置の製造方法。

【図面の簡単な説明】

【0382】

【図1】本発明の第1の実施形態にかかる半導体装置の構造を示す図であって、図1Aは当該半導体装置の平面を示し、図1Bは図1Aに於けるX−X’断面を示す。

【図2】本発明の第1の実施形態にかかる半導体装置の製造工程を示す断面図である。

【図3】本発明の第1の実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図2に示す製造工程に続く製造工程を示す。

【図4】バンプを形成する工程を示す図である。

【図5】バンプの変形例を示す図である。

【図6】本発明の第1の実施形態にかかる半導体装置に於ける、バンプの配置形態を示す平面図である。

【図7】本発明の第1の実施形態にかかる半導体装置に於ける、ボンディングワイヤの接続変形例を示す断面図である。

【図8】本発明の第1の実施形態にかかる半導体装置の変形例の構造を示す図であって、図8Aは当該半導体装置の平面を示し、図8Bは図8Aに於けるX−X’断面を示す。

【図9】本発明の第2の実施形態にかかる半導体装置の構造を示す図であって、図9Aは当該半導体装置の平面を示し、図9Bは図9Aに於けるX−X’断面を示す。

【図10】本発明の第2の実施形態にかかる半導体装置の製造工程を示す断面図である。

【図11】本発明の第2の実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図10に示す製造工程に続く製造工程を示す。

【図12】本発明の第2の実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図11に示す製造工程に続く製造工程を示す。

【図13】本発明の第2の実施形態にかかる半導体装置に於けるバンプの配設形態とボンディングワイヤの接続形態を示す図である。

【図14】本発明の第3の実施形態に本発明の半導体装置の構造を示す図であって、図14Aは当該半導体装置の平面を示し、図14Bは図14Aに於けるX−X’断面を示す。

【図15】本発明の第3の実施形態にかかる半導体装置の製造工程を示す断面図である。

【図16】本発明の第3の実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図15に示す製造工程に続く製造工程を示す。

【図17】本発明の第3の実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図16に示す製造工程に続く製造工程を示す。

【図18】本発明の第3の実施形態にかかる半導体装置に於けるバンプの配置形態その1を示す平面図である。

【図19】本発明の第3の実施形態にかかる半導体装置に於けるバンプの配置形態その2を示す図であり、図19B並びに図19Cは図19Aに於けるX−X’断面を示す。

【図20】本発明の第3の実施形態にかかる半導体装置に於けるバンプの配置形態その3を示す図であり、図20B並びに図20Cは図20Aに於けるX−X’断面を示す。

【図21】本発明の第3の実施形態にかかる半導体装置に於けるバンプの配置形態その4を示す図であり、図21B並びに図21Cは図21Aに於けるX−X’断面を示す。

【図22】本発明の第3の実施形態にかかる半導体装置の変形例の構造を示す図であって、図22Aは当該半導体装置の平面を示し、図22Bは図22Aに於けるX−X’断面を示す。

【図23】本発明の第4の実施形態にかかる半導体装置の構造を示す図であって、図23Aは当該半導体装置の平面を示し、図23Bは図23Aに於けるX−X’断面を示す。

【図24】本発明の第4の実施形態にかかる半導体装置に於けるバンプの配置形態その1を示す図であり、図24Aは当該半導体装置の平面を示し、図24Bは図24Aに於けるX−X’断面を示す。

【図25】本発明の第4の実施形態にかかる半導体装置に於けるバンプの配置形態その2を示す図であり、図25Aは当該半導体装置の平面を示し、図25Bは図25Aに於けるX−X’断面を示す。

【図26】本発明の第4の実施形態にかかる半導体装置に於けるバンプの配置形態その3を示す図であり、図26Aは当該半導体装置の平面を示し、図26Bは図26Aに於けるX−X’断面を示す。

【図27】本発明の第4の実施形態にかかる半導体装置に於けるバンプの配置形態その4を示す図であり、図27Aは当該半導体装置の平面を示し、図27Bは断面を示す。

【図28】本発明の第5の実施形態にかかる半導体装置の構造を示す図であって、図25Aは当該半導体装置の平面を示し、図25Bは断面を示す。

【図29】本発明の第5の実施形態にかかる半導体装置の製造工程を示す断面図である。

【図30】本発明の第5実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図29に示す製造工程に続く製造工程を示す。

【図31】本発明の第5実施形態にかかる半導体装置の製造工程を示す断面図であって、前記図30に示す製造工程に続く製造工程を示す。

【符号の説明】

【0383】

100、130、140、200、300、330、400、500:半導体装置

101、201、301、401:配線基板

102、202、302、402、502:第1の半導体素子

104、204、304、406、508:第2の半導体素子

306:第3の半導体素子

404、506:スペーサ

111、210、314、412、505:凸状部材(バンプ)

108、109、208、311、312、313、410、411、504、510:ボンディングワイヤ

112、211、315、413、512:封止用樹脂

114、213、317、415、501b2:外部接続用端子

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に支持基体上に複数の半導体素子が積層配置される半導体装置及びその製造方法に関する。

【背景技術】

【0002】

電子機器の高機能化ならびに小型化に伴い、当該電子機器に搭載される半導体集積回路装置などの半導体装置に対しても、より高機能化、高速動作化と共に、更なる小形化、軽量化が求められている。

【0003】

この為、当該半導体装置にあっては、回路基板などの支持基体(支持基板)上に、複数個の半導体素子を積層して搭載することがなされている。

【0004】

この様に、複数個の半導体素子を積層配置する構成は、例えば、マイクロプロセッサなどの論理機能素子と、不揮発性メモリなどの半導体記憶素子とを組み合わせて所望の機能を発揮させる場合などに生ずる。

【0005】

かかる場合、論理機能素子ならびに半導体記憶素子は、その回路機能・回路規模を全く異にすることから、外形寸法が異なることが一般的である。

【0006】

また、当該半導体素子は通常、矩形状の平面形状を有する。

【0007】

従って、積層された状態に於いて、上方に位置する半導体素子の少なくとも一端が、下方(支持基体側)に位置する半導体素子の外方に庇状に延出(突出)する状態が生じてしまう場合がある。

【0008】

また、前記支持基体に於けるところの、半導体素子の電極端子が接続される接続端子の配置構成、あるいは当該支持基体の電子機器への接続用端子の配置構成などによって、これら複数の半導体素子から導出されるボンディングワイヤの導出方向及び/あるいは導出箇所などが制限される場合がある。

【0009】

かかる場合、積層される半導体素子は、その中心線が交差する如く異なる方向とされて(回転配置されて)積層され、当該半導体素子の電極端子からのボンディングワイヤなどの導出の自由度が高められる。

【0010】

このとき、上方に位置する半導体素子の両端、あるいは少なくとも一端が、下方(支持基体側)に位置する半導体素子の電極端子配設部(配設辺)とは異なる方向に庇状に延出(突出)する状態となる場合がある。

【0011】

尚、前記支持基体上への半導体素子の搭載形態としては、当該支持基体上に所謂フリップチップ(フェイスダウン)形態をもって搭載される形態、あるいは当該支持基体上にフェイスアップ状態をもって搭載されその電極端子パッドがワイヤボンディング法により支持基体上の電極端子に接続される形態がある。

【0012】

これらの搭載形態は適宜選択され、組み合わされて、支持基体上に、複数の半導体素子が積層されて搭載されるが、前述の如く、上方に位置する半導体素子の一部が下方(支持基体側)に位置する半導体素子の外方に、当該下方に位置する半導体素子の縁部を越えて庇状に延出(突出)する状態は、当該半導体素子相互間の寸法関係、及び/あるいは搭載する方向により発生する。

【0013】

更に、複数の半導体素子を積層して配設する際、半導体素子相互間に所謂スペーサ(間隔保持体)を配設し、当該半導体素子間に空間を設けることが行われる場合がある。

【0014】

このとき、上方に位置する半導体素子の少なくとも一端が、支持基体であるスペーサの外方に庇状に延出(突出)する状態が生じる場合がある。

【0015】

また、前記半導体装置にあっては、前述の如き半導体素子の積層構造を含むものであっても、その厚さ(高さ)をより減少させることが要求されている。

【0016】

一方、積層される半導体素子の組み合わせについても、種々の要求がなされつつある。

【0017】

この為、前記半導体素子も、その厚さをより減じることが必要とされている。

【0018】

この様に厚さが減じられた半導体素子が、前記積層構造体を構成する際に適用され、当該半導体素子が上方に位置する場合には、前述の如く、当該上方に位置する半導体素子に於ける電極端子部が、前記延出部に位置してしまう状態が生ずる。

【0019】

かかる場合、当該上方に位置する半導体素子の電極端子にワイヤボンディングを行おうとすると、当該半導体素子の延出部が撓み(下方、支持基体側に湾曲し)、十分な加圧がなされないことから正常なワイヤボンディングが行われない。

【0020】

また、より大きな圧力を加えれば、当該上方に位置する半導体素子の延出部に損傷を生じてしまう場合もある。

【0021】

この様に、半導体素子の積層構造を採用してなる半導体装置に於いて、上方に位置する半導体素子の電極端子へワイヤボンディングを行う際、当該半導体素子の延出部の変形を防止する為に、従来種々の提案がなされている。

【0022】

一つに、基板上に、第1の半導体チップと、当該第1の半導体チップよりも大であって当該第1の半導体チップ上に積層配置された第2の半導体チップとが配置され、当該第2の半導体チップと基板との間に、台部材を配設してなる構成が提案されている。(例えば、特許文献1参照)

また、基板上に、第1の半導体チップと、当該第1の半導体チップよりも大であって当該第1の半導体チップ上に積層配置された第2の半導体チップとが配置され、当該第2の半導体チップと基板との間に、複数の柱状の支持部を配設してなる構成が提案されている。(例えば、特許文献2参照)

【特許文献1】特開2001−320014号公報

【特許文献2】特開2005−197491号公報

【発明の開示】

【発明が解決しようとする課題】

【0023】

しかしながら、前記半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを防止しようとすると、突出部の大きさに対応した専用の支持部材が必要となり、多種類の支持材を用意する必要が生じる。

【0024】

また、当該支持材が大形化されると、当該支持材を避けて他の半導体素子あるいは受動部品を配置する必要が生じ、半導体装置の大型化を招来してしまう。

【0025】

本発明は、このような問題に鑑みてなされたものであり、積層配置される半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを抑制するとともに、半導体装置として大形化を招くことのない支持部材を有する、半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0026】

上記の課題を達成するため、本発明の第1の側面によれば、電極端子が配設された支持基体と、支持基体上に搭載された中間部材と、一部が前記中間部材により支持されて、支持基体上に配設された半導体素子と、半導体素子の電極端子に対応して、支持基体上あるいは中間部材上に配設された凸状部材とを具備し、半導体素子の電極端子と支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする半導体装置を提供する。

【0027】

また、本発明の第2の側面によれば、電極端子が配設された支持基体上に、中間部材を搭載する工程と、支持基体上に、凸状部材を配設する工程と、中間部材上に、半導体素子をフェイスアップ状態をもって搭載する工程と、半導体素子の電極端子と支持基体の電極端子とをワイヤボンディング法により接続する工程とを含むことを特徴とする半導体装置の製造方法を提供する。

【発明の効果】

【0028】

本発明によれば、支持基体上に、複数個の半導体素子が積層状態をもって配設される半導体装置にあって、上方に位置する半導体素子(支持基体から遠い位置にある半導体素子)が、下方に位置する半導体素子の縁部を越えて延出(突出)する状態を有する半導体装置において、前記上方に位置する半導体素子の電極へのボンディングワイヤの接続が確実になされる。

【0029】

また、所定の外形寸法を有するスペーサ上に、当該スペーサよりも大なる外形寸法を有する半導体素子が配設される場合にあっても、当該半導体素子の電極へのボンディングワイヤの接続が確実になされる。

【0030】

これにより、異なる外形寸法を有する半導体素子を積層してなる半導体装置、あるいは複数の半導体素子がその中心線が交差する如く異なる方向をもって積層される半導体装置を、高い接続信頼性をもって、容易に実現することができる。

【0031】

また、本発明によれば、上記の半導体装置を容易に製造することができる。

【発明を実施するための最良の形態】

【0032】

以下、本発明による半導体装置の実施形態について、その製造方法と共に詳細に説明する。本発明による半導体装置は、以下に記すように、複数の実施形態を含む。

(実施形態1)

本発明による半導体装置の実施形態その1について、図1乃至図9を用いて説明する。

【0033】

本実施形態に於ける半導体装置は、支持基体である配線基板上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により当該配線基板上の電極端子に接続される第1の半導体素子と、当該第1の半導体素子上にフェイスアップ状態をもって搭載され、その外部接続用電極端子がワイヤボンディング法により前記配線基板上の電極端子に接続される第2の半導体素子とを具備する。

【0034】

本発明の、実施形態その1にかかる半導体装置100を、図1に示す。

【0035】

図1Aは、当該半導体装置100の平面を示し、また図1Bは、図1Aに於けるX−X’断面を示す。尚、図1Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0036】

当該半導体装置100にあっては、支持基体である配線基板101の一方の主面上に、二つの半導体素子が積層配置されている。

【0037】

即ち、当該配線基板101上には、第1の半導体素子102が接着剤層103を介して、所謂フェイスアップ状態をもって搭載されており、更に当該第1の半導体素子102上には、第2の半導体素子104が、接着剤層105を介してフェイスアップ状態をもって搭載されている。

【0038】

ここで、第2の半導体素子104は長方形状を有し、第1の半導体素子102上に於いて、当該第1の半導体素子102の幅を越えて庇状(片持ち梁状)に延出(突出)して搭載されている。この為、第1の半導体素子102の側部に於いて、第2の半導体素子104の延出(突出)部と前記支持基板101との間は離間している。

【0039】

そして、第1の半導体素子102は、配線基板101と第2の半導体素子104との間に位置して中間部材をなしている。

【0040】

かかる構成に於いて、前記第1の半導体素子102の外部接続用電極端子102eは、前記第2の半導体素子104が延出する2辺とは異なる2辺に沿って、その縁部近傍にそれぞれ複数個配設されている。

【0041】

また、第2の半導体素子104の外部接続用電極端子104eは、当該第2の半導体素子104の長手方向の両端の2辺に沿って、その縁部近傍にそれぞれ複数個配設されている。

【0042】

一方、前記配線基板101の主面上には、第1の半導体素子102の外部接続用電極端子102eに対応して電極端子106が複数個配設され、また第2の半導体素子104の外部接続用電極端子104eに対応して電極端子107が複数個配設されている。

【0043】

そして、第1の半導体素子102の外部接続用電極端子102eと配線基板101上の電極端子106との間は、ボンディングワイヤ108により接続され、一方、第2の半導体素子104の外部接続用電極端子104eと配線基板101上の電極端子107との間は、ボンディングワイヤ109により接続されている。

【0044】

本実施形態に於ける特徴的構成として、前記第2の半導体素子104に於ける延出部の両端部近傍に於ける配線基板101上に、当該第2の半導体素子104の縁部(辺)に沿って、且つ当該半導体素子104の辺の長さと同等の長さを有する長尺状の導電性パッド110が配設され、当該導電性パッド110上に、前記第2の半導体素子104に於ける複数個の外部接続用電極端子104eそれぞれの略直下に位置して、バンプ111からなる凸状部材が配設されている。

【0045】

一方、配線基板1の一方の主面に於いては、半導体素子102、半導体素子104ならびにボンディングワイヤ108、109などを覆って、封止用樹脂112が被覆されている。

【0046】

更に、当該配線基板101の他方の主面には、格子状に配設された複数個の電極端子113上に、それぞれ外部接続用端子114が配設されている。

【0047】

かかる構成に於いて、前記配線基板101は、例えば、ガラス−エポキシ、ガラス−BT(ビスマレイミドトリアジン)、ポリイミド等の有機絶縁性樹脂、あるいはセラミック、ガラス、シリコン等の無機材料から形成される。そして、当該配線基板1の表面及び/あるいは内部には、所謂多層配線技術が適用されて、銅(Cu)などからなる配線ならびに電極端子が配設される。当該銅配線あるいは電極端子の表面には、必要に応じてニッケル(Ni)及び金(Au)からなる被覆層が配設されてもよい。

【0048】

当該配線基板101は、支持基板、回路基板あるいはインターポーザとも称される。

【0049】

また、前記半導体素子102、半導体素子104は、シリコン(Si)あるいはガリウム砒素(GaAs)などの半導体基板の一方の主面に、所謂ウエファープロセスが適用されて、トランジスタなどの能動素子、容量素子などの受動素子ならびにこれらの機能素子を相互に接続する配線層をもって電子回路が形成されており、当該配線層は当該半導体素子の外部接続用電極端子に接続されている。

【0050】

半導体素子102、半導体素子104は、配線基板101に対し、前記電子回路が形成された主面を上面(表出面)として搭載・配置されている。かかる状態をフェイスアップ状態と称する。

【0051】

また、当該半導体素子に於ける外部接続用電極端子と、配線基板1上に配設された電極端子との間を接続するボンディングワイヤ108、ボンディングワイヤ109は、金(Au)、銅(Cu)またはアルミニウム(Al)等の金属を主成分とする細線が適用される。

【0052】

そして、当該半導体素子の他方の主面に配設される接着剤層103、105は、ポリイミド系樹脂あるいはエポキシ系樹脂を主とする材料から構成される。当該接着剤は、銀(Ag)、金(Au)、パラジウム(Pd)、銅(Cu)等の導電性材料からなる微粒子を含有していてもよい。

【0053】

また、配線基板1上に配設される長尺状の導電性パッド110は、当該配線基板101に形成される配線、電極端子と同様に、銅(Cu)から形成される。当該導電性パッド110の表面には、必要に応じてニッケル(Ni)及び金(Au)からなる被覆層が配設されてもよい。

【0054】

そして、凸状部材として、当該導電性パッド110上に配設されるバンプ111は、所謂ボールボンディング法により形成された金属バンプからなる。

【0055】

尚、前記導電性パッド110は、後述する如く、長尺状の形状に換えて、バンプ111の配設位置に対応して個別化されて、即ち独立して配設されても良く、また複数のバンプ111毎に分割されて配設されても良い。

【0056】

また、前記樹脂封止部112を形成する樹脂部材としては、エポキシ樹脂を主体とする樹脂が適用される。

【0057】

更に、前記配線基板101の他方の主面に於いて、外部接続用端子113に配設される外部接続用端子114は、はんだボール(はんだバンプ)をもって形成される。

【0058】

この様に、本実施形態に於ける半導体装置100は、所謂BGA(Ball Grid Array)型半導体装置をなしている。

【0059】

従って、前記外部接続用端子113にはんだボールを配設せず、所謂LGA(Land Grid Array)型半導体装置とすることは、必要に応じて行うことができる。

【0060】

かかる半導体装置100にあっては、第1の半導体素子102上に搭載された第2の半導体素子104に於ける配線基板101からの離間部分、即ち第1の半導体素子102からの延出部に位置する外部接続用電極端子104eに対するボンディングワイヤ109の接続の際、当該第2の半導体素子104の被ワイヤボンディング部は、前記バンプ111によって機械的に支持される。

【0061】

これにより、当該ワイヤボンディング処理の際、第2の半導体素子104の湾曲が抑制され、第2の半導体素子104の破損が防止される。

【0062】

また、ボンディングキャピラリからの押圧力が有効に印加されて、ボンディングワイヤ109は、第2の半導体素子104の外部接続用電極端子104eに確実に接続される。

【0063】

次に、前記半導体装置100の製造方法について、図2及び図3を用いて説明する。

【0064】

尚、図2及び図3は、前記図1Bに示した断面に相当し、図1に示した構成要素と同一の構成要素には、同一の符号を付している。

【0065】

表面に電極端子106、107、113ならびに長尺状の導電性パッド110などが配設された配線基板101を、ダイボンダのボンディングステージ(図示せず)上に載置する。(図2A参照)

そして、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0066】

次いで、吸着コレット151によって上面(電子回路形成面)が吸着・保持された第1の半導体素子102を配線基板101上に載置し、当該吸着コレット151による押圧を伴って、当該第1の半導体素子102の裏面あるいは予め配線基板101の上面に選択的に配設された接着剤層103により、当該第1の半導体素子102を配線基板101上に固着する。(図2B参照)

当該接着剤層103は、塗布または貼付け等により予め配設される。

【0067】

なお、当該接着剤として、熱硬化性樹脂を適用しても良い。かかる場合には、第1の半導体素子102を配線基板101上に搭載した後、恒温槽またはホットプレート等により、例えば120℃〜240℃に加熱して、接着剤を半硬化または硬化せしめる。

【0068】

次いで、前記配線基板101をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0069】

そして、ワイヤボンディングツールに於けるボンディングキャピラリ161を用いての所謂ボールボンディング法を適用し、配線基板101に於ける長尺状の導電性パッド110の表面に、バンプ111を複数個形成する。(図2C参照)

かかる導電性パッド110の表面へのバンプ111の配設は、第2の半導体素子104に於ける外部接続用電極端子104eが配設された位置に対応するように行われる。

【0070】

そして、当該バンプ111の高さは、前記第1の半導体素子102の上面と略同等の高さとされる。(図2D参照)

即ち、当該バンプ111の高さは、第1の半導体素子102と接着剤層103との厚さからもたらされる高さと略一致する高さとされる。

【0071】

尚、当該導電性パッド110上ヘのバンプ111の配設工程と、前記第1の半導体素子102の配線基板101上への固着工程は、その順番を入れ換えてもよい。

【0072】

次いで、配線基板101を、ダイボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば50℃〜200℃に加熱する。

【0073】

そして、吸着コレット152により上面(電子回路形成面)が吸着された第2の半導体素子104を、前記第1の半導体素子102上に載置し、当該吸着コレット152による押圧を伴って、当該第2の半導体素子104の裏面あるいは予め第1の半導体素子102の上面に選択的に配設された接着剤層105より、当該第2の半導体素子104を第1の半導体素子102上に固着する。(図2E参照)

この結果、前記バンプ111は、第2の半導体素子104に於ける外部接続用電極端子104eそれぞれの略直下に位置する。

【0074】

なお、前記接着剤層105を前記第2の半導体素子104の裏面全面に配設する場合には、前記バンプ111と前記第2の半導体素子104の裏面とを、前記接着剤層105を介して固着してもよい。

【0075】

しかる後、配線基板101をワイヤボンダのボンディングステージ(図示せず)上に載置し、当該ボンディングステージに配設されたヒーターにより所定温度、例えば100℃〜200℃に加熱する。

【0076】

そして、通常のボールボンディング法により、半導体素子の外部接続用電極端子と、これに対応する配線基板上の電極端子とを、ボンディングワイヤにより接続する。

【0077】

即ち、ボンディングキャピラリ162を用いて、前記第2の半導体素子104の外部接続用電極端子104eに、ボンディングワイヤ109の始端、即ちボール部を接続する。(図3A参照)

かかるボンディングワイヤ109の接続の際、第2の半導体素子104の外部接続用電極端子104eの被ワイヤボンディング部は、前記バンプ111により機械的に支持され、当該第2の半導体素子104の湾曲が抑制されて、その破損が防止される。

【0078】

また、超音波振動の吸収も防止され、押圧力が有効に印加されて、ボンディングワイヤ109は第2の半導体素子104の外部接続用電極端子104eに確実に接続される。

【0079】

即ち、配線基板101上にあって、バンプ111は、第2の半導体素子104の外部接続用電極端子104eの略直下に位置しており、当該第2の半導体素子104の外部接続用電極端子104eに対するボンディングワイヤ109の接続の際の押圧に対抗する。

【0080】

かかるワイヤボンディングの後、ボンディングワイヤ109の他端(終端)を、配線基板101上の電極端子107対しステッィチボンディング法により接続する。(図3B参照)

この時、当該ボンディングワイヤ109に、所望のルーピング形状を付与する。

【0081】

尚、当該第2の半導体素子104の外部接続電極端子104eと配線基板101上の電極端子107との間のワイヤボンディング処理の前あるいは終了後に、前記第1の半導体素子102の外部接続用電極端子102eと配線基板101上の電極端子105との間も、ボンディングワイヤ108を用いて接続する。(図示せず)

この様にして、半導体素子の外部接続電極端子と配線基板上の電極端子との間をワイヤボンディング法により接続した後、 配線基板101の主面上に形成された半導体素子の積層構造体を、ボンディングワイヤ108、109などと共に、封止用樹脂112より被覆する。(図3C参照)

封止用樹脂112の被覆方法としては、周知のトランスファーモールド法、コンプレッションモールド法、あるいはポッティング法を適用することができる。

【0082】

尚、かかる樹脂封止の際にも、第2の半導体素子104の延出部はバンプ111によって支持される。

【0083】

従って、トランスファーモールド法などに於ける、封止用樹脂112の流入圧力によって、当該第2の半導体素子104が変形あるいは破損することが防止される。

【0084】

しかる後、前記配線基板101の他方の主面に於ける電極端子113に対し、リフローソルダリング法等を用いて、はんだボール電極からなる外部接続用端子114を配設し、半導体装置100を形成する。(図3D参照)

尚、前記配線基板101が大判であって、当該配線基板101の一方の主面に、半導体素子の積層構造体が複数個形成される工程をとる場合(図示せず)には、前記外部接続用端子114の形成後、前記樹脂封止部112及び配線基板101をその積層方向(厚さ方向)に切断することにより、個片化された半導体装置100を得る。

【0085】

ここで、配線基板101上の導電性パッド110上に、バンプ111を、所謂ボールボンディング法により形成する工程について、図4を用いて説明する。

【0086】

ワイヤボンディングツールのボンディングキャピラリ161の先端から導出された金(Au)を主体とする金属からなるボンディングワイヤ171と、トーチ181との間に於いて放電を生じさせ、ボンディングワイヤ171の先端部にボール172を形成する。(図4A参照)

次いで、当該ボール172を、ボンディングキャピラリ161により荷重と超音波振動を付与しつつ、被接続部材、即ち配線基板101の表面に配設された導電性パッド110上に押圧し、当該導電性パッド110に接続する。(図4B参照)

かかる接続処理により、前記ボール172は変形し、導電性パッド110表面に対し、平板状部をもって接続される。

【0087】

尚、この時、ボンディングキャピラリ161により印加される荷重は、ボンディングワイヤ171の直径が15μmである場合には4gf乃至7gf程度とされ、当該ワイヤ172の径が20μmの場合には10gf乃至20gf程度とされる。

【0088】

また、かかるボンディング工程に於いて、前記配線基板101を保持するボンディングステージを100℃〜200℃に加熱してもよい。

【0089】

次いで、前記ボンディングキャピラリ161に於けるクランパ(図示せず)によりボンディングワイヤ171を保持した状態に於いて、当該ボンディングキャピラリ161を上昇せしめ、ボンディングワイヤ171を切断する(引きちぎる)。(図4C参照)

これにより、前記導電性パッド110上には、平版状基部111aとその上面に突出した突出部111bを有するバンプ111が形成される。

【0090】

当該バンプ111は、その適用箇所(配置箇所)に対応して、種々の変形が与えられる。

【0091】

即ち、一つには、当該バンプ111の突出部111bの形状が、適用箇所(配置箇所)に対応して変形される。また、当該バンプ111が、積層構造体とされる場合もある。

【0092】

かかるバンプ111の変形例を、図5を用いて説明する。

【0093】

例えば、前記半導体装置100に於いて、第2の半導体素子104の延出部の長さが長い、即ち下に位置する第1の半導体素子102の縁部からの延出長が長い場合には、当該第2の半導体素子104の外部接続用電極端子104eへのワイヤボンディングの際、当該第2の半導体素子104に於ける湾曲が大きくなる。

【0094】

かかる場合、第2の半導体素子104に於ける湾曲に対し、面接触状態をもって接する様、バンプ111の突出部111b上面を、当該第2の半導体素子104に於いて生ずる湾曲面に対応する傾斜面とする。(図5A参照)

即ち、バンプ111の突出部111b上面を、前記第1の半導体素子102側から第2の半導体素子104の延出方向に沿って降下する傾斜面とする。

【0095】

かかる傾斜面の形成は、前記図4に示す工程に於いて、ボール172のボンディング後、ボンディングワイヤ171を引きちぎる前に、ボンディングキャピラリ162を一旦上昇させ、更に水平方向に移動せしめた後、当該ボンディングキャピラリ162の先端部の傾斜した平面部分をボンディングワイヤ171の頭頂部に押し付けることにより行われる。

【0096】

その後、ボンディングワイヤ171を引きちぎり、上面に傾斜面を有する突出部111bを具備したバンプ111を形成する。

【0097】

一方、前記第2の半導体素子4の延出部の長さが短い場合などには、上面が平坦面とされた突出部を具備したバンプが配設される。(図5B参照)

かかる平坦面の形成は、前記図4に示す工程の後、バンプ111の頂部に、前記配線基板101と並行な平坦部を有するスタンピングツール又は平板状部材等を押し付けることにより行われる。

【0098】

なお、当該スタンピングツールまたは平板状部材等による押し付けは、個々のバンプ111単位で行っても、複数個のバンプ111に対して一括して行ってもよい。

【0099】

また、前記半導体装置100に於いて、第2の半導体素子104の延出部と、配線基板101の上面との間の離間距離が大きい場合、即ち前記第1の半導体素子102と接着剤層103とからなる積層構造体の厚さが大である場合などには、バンプ111を複数のバンプの積層構造体して構成する。(図5C参照)

かかる積層構造体は、前記図4に示した方法を繰り返すことにより形成することができる。当該多段(多層)積層バンプの配設により、第2の半導体素子4の延出部の支持を確実に行うことができる。

【0100】

尚、当該バンプ111の形成方法としては、前述のボールボンディング法の他、所謂選択めっき法を適用することもできる。

【0101】

従って、当該バンプ111の外形形状も、前記多段形状に限られず、柱状をなす場合もある。

【0102】

そして、当該バンプ111は、その配設位置及び/あるいは配設個数を、必要に応じて選択することができる。

【0103】

当該バンプ111の配設位置及び/あるいは配設個数の変形例について、図6を用いて説明する。

【0104】

尚、当該図6は、前記図1Aに於いて、破線Aにより囲繞された矩形領域を表示している。また、当該図6にあっては、第1の半導体素子104上に搭載される第2の半導体素子104、ボンディングワイヤ109、樹脂封止部112の表示を省略し、第2の半導体素子104の外形を破線で示している。

【0105】

前述の如く、半導体装置100にあっては、導電性パッド110の表面へのバンプ111の配設は、第2の半導体素子4に於ける外部接続用電極端子の配設された位置に対応するよう行われている。(図6A参照)

即ち、当該バンプ111は、第2の半導体素子104に於ける複数の外部接続用電極端子104eそれぞれの略直下に位置して配設されている。(図示される状態では10個)

この様な形態であれば、第2の半導体素子104に於ける複数の外部接続用電極端子104eに対するワイヤボンディングの際、個々の被ボンディング電極端子に印加される押圧に対してその直下に位置するバンプ111が対応して、良好なワイヤボンディングがなされる。

【0106】

かかる構成にあっては、第2の半導体素子104に於ける外部接続用電極端子104eの数に対応するバンプ111の配設が必要とされる。

【0107】

しかしながら、この様なバンプの配設構成では、第2の半導体素子104として、より多数の外部接続用端子を具備する半導体素子が適用された場合には、バンプ111の配設に要する時間の増加を招いてしまう。

【0108】

一方、第2の半導体素子104として、比較的小形あるいは細幅の長尺状の半導体素子が適用された場合には、当該半導体素子に於ける外部接続用電極端子に対応する数のバンプ111の配設を必要としない場合がある。

【0109】

かかる場合には、例えば、次の様なバンプ配設構成をとることができる。

【0110】

一つには、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部両隅部にのみ配設(計2個)する。(図6B参照)

又は、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部の辺の略中央部にのみ配設(1個)する。(図6C参照)

あるいは、当該バンプ111を、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の長手方向の端部両隅部、及び当該端部の辺の略中央部に配設(計3個)する。(図6D参照)

また、前記バンプ111は、半導体素子(前記半導体装置100に於ける第2の半導体素子104)の外部接続用電極端子配列の線上に位置することに限られず、当該外部接続用電極端子配列の線上から内側あるいは外側に偏寄して配置してもよい。(図示せず)

これらのバンプ配設構造に於いては、前記導電性パッド110は、長尺状である必要はなく、バンプ111が配設される箇所に対応して、選択的に配設されることを可とする。

【0111】

この様なバンプ111の選択的配設構成によれば、当該バンプ111の配設個数を低減することができ、配設工程の低コスト化、効率化を図ることができる。

【0112】

前記半導体装置100にあっては、更に種々の変形が可能である。

【0113】

一つには、前記第2の半導体素子104に於ける外部接続用電極端子104eと配線基板101上の電極端子107との間を接続するボンディングワイヤ109の接続法として、所謂リバースボンディング法を適用することができる。

【0114】

かかるリバースボンディング法が適用された形態を半導体装置130として、図7に示す。同図に於いて、前記図1に示す構成と対応する部位には同一の符号を付している。

【0115】

図7に示される様に、半導体装置130にあっては、ボンディングワイヤ109の始端であるボール部が配線基板101上の電極端子107に接続され、当該ボンディングワイヤ109の他端(終端)が第2の半導体素子104に於ける外部接続用電極端子104e上に配設されたバンプ115に接続されている。

【0116】

かかるリバースボンディング法を適用した場合であっても、ボンディングワイヤ109の他端(終端)を第2の半導体素子104に於ける外部接続用電極端子104eに接続する際、当該第2の半導体素子104に対してボンディングツールの押圧力が印加される。

【0117】

また、当該接続に先立つ、第2の半導体素子104の外部接続用電極端子104e上へのバンプ115の配設は、前記図4を用いて説明した方法と同様に、所謂ボールボンディング法が用いられて行なわれる。

【0118】

従って、このバンプ115の配設の際にも、第2の半導体素子104に対し、ボンディングツールの押圧力が印加される。

【0119】

かかるボンディングツールの押圧力に対し、前記バンプ111は対抗して、第2の半導体素子104を支持し、当該第2の半導体素子104の変形、破損を防止する。

【0120】

この様なリバースボンディング法を適用することにより、前記半導体装置100に於ける通常のワイヤボンディング法に比較して、ボンディングワイヤ109に於けるワイヤループの高さを低くすることができる。

【0121】

これにより、当該半導体装置130にあっては、樹脂封止部の高さ(厚さ)の増加を招来せず、より高さの低い(厚さの薄い)半導体装置を形成することができる。

【0122】

また、前記半導体装置100にあっては、第2の半導体素子104は、第1の半導体素子102上に於いて、当該第1の半導体素子102の対向する2辺から双方向に庇状に延出して搭載されている。

【0123】

しかしながら、第1の半導体素子102の形態によっては、当該第1の半導体素子102上に於ける第2の半導体素子104の搭載位置、ならびにその延出方向が特定あるいは制限される場合がある。

【0124】

即ち、例えば半導体記憶素子の様に、外部接続用電極端子が当該半導体素子のほぼ中央部に位置し、且つ当該半導体記憶素子の長手方向に列状に配設される形態がある。

【0125】

この様な半導体素子を第1の半導体素子102として配線基板1上にフェイスアップ状態をもって搭載し、当該第1の半導体素子102上に第2の半導体素子104を搭載する場合には、当該第1の半導体素子102の外部接続用電極端子に対するボンディングワイヤ108の接続を可能とする為に、当該第1の半導体素子102に於ける外部接続用電極端子の配列に沿う2辺の一方が開放され、第2の半導体素子104は当該辺に於いて庇状(片持ち梁状)に延出して搭載される必要がある。

【0126】

かかる半導体素子の搭載形態を含む半導体装置構造を、半導体装置140として図8に示す。

【0127】

図8Aは、当該半導体装置140の平面を示し、また図8Bは、図8Aに於けるX−X’断面を示す。なお、図8Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0128】

当該半導体装置140にあっては、支持基板である配線基板101の一方の主面上に、二つの半導体素子が積層配置されている。

【0129】

即ち、当該配線基板101上には、第1の半導体素子102が接着剤層103を介して、所謂フェイスアップ状態をもって搭載されており、また当該第1の半導体素子102上には、第2の半導体素子104が、接着剤層105を介してフェイスアップ状態をもって搭載されている。

【0130】

そして、第1の半導体素子102にあっては、その表面のほぼ中央部に、複数個の外部接続用電極端子102eが列状に配設されている。

【0131】

また、第2の半導体素子104は、当該第1の半導体素子102上に於いて、当該第1の半導体素子102に於ける外部接続用電極端子102eの配設部を避け、且つ当該第1の半導体素子102の外部接続用電極端子102eの配列と並行な辺の一方から、庇状(片持ち梁状)に延出(突出)して搭載されている。

【0132】

この為、第1の半導体素子102の側部に於いて、第2の半導体素子104の延出(突出)部と支持基板101との間は離間している。

【0133】

当該第1の半導体素子102は、配線基板101と第2の半導体素子104との間に位置して中間部材をなしている。

【0134】

かかる配設構成にあっては、第2の半導体素子104の延出部の長さ(突出量)は、第2の半導体素子104の延出方向に並行な辺の長さの1/2よりも大きい。

【0135】

すなわち、第2の半導体素子104の延出部の面積は、当該第2の半導体素子104が第1の半導体素子102上に固着される面積よりも大きい。

【0136】

そして、第2の半導体素子104の外部接続用電極端子104eは、当該第2の半導体素子104の対向する2辺に沿ってそれぞれ複数個配設されており、その一方の配列は前記第1の半導体素子102に於ける外部接続用電極端子102eの配列に近接し、略並行している。また、他方の配列は、延出(突出)部に於いて、第1の半導体素子102からより遠い領域に位置している。

【0137】

一方、前記配線基板101の主面上には、前記第1の半導体素子102の外部接続用電極端子102eに対応して電極端子106が複数個配設され、また前記第2の半導体素子104の外部接続用電極端子104eに対応して電極端子107が複数個配設されている。

【0138】

当該電極端子107の一部は、前記電極端子106の配列の外側に位置し、且つ略並行して配設されている。

【0139】

そして、当該第1の半導体素子102の外部接続用電極端子102eと、前記配線基板101上の電極端子106との間はボンディングワイヤ108より接続され、第2の半導体素子104の外部接続用電極端子104eと、前記配線基板101上の電極端子107との間はボンディングワイヤ109より接続されている。

【0140】

ここでは、前記第1の半導体素子102の外部接続用電極端子102eに対するボンディングワイヤ108の接続法として、ならびに第2の半導体素子104の当該第1の半導体素子102上に位置する外部接続用電極端子104eに対するボンディングワイヤ109の接続法として、リバースボンディング法が適用されている。

【0141】

即ち、第1の半導体素子102の外部接続用電極端子102e上に配設されたバンプ121にボンディングワイヤ108の終端が接続され、一方、第2の半導体素子104の第1の半導体素子102上に位置する外部接続用電極端子104e上に配設されたバンプ122にボンディングワイヤ109の終端が接続されている。

【0142】

これらのボンディングワイヤ108、ボンディングワイヤ109は、その延在する方向がほぼ同一であることから、互いの接触を防止しつつワイヤループの高さを抑制するうえで、当該リバースボンディング法は有効である。

【0143】

かかる半導体装置140に於ける特徴的構成として、第2の半導体素子104の延出(突出)部に於ける配線基板101上に、当該第2の半導体素子104の縁部(辺)に沿って、且つ当該第2の半導体素子104の辺の長さと同等の長さを有する長尺状の導電性パッド110が配設されている。当該導電性パッド110上には、第2の半導体素子104に於ける複数個の外部接続用電極端子104eそれぞれの略直下に位置して、バンプ111が配設されている。

【0144】

そして、前記第2の半導体素子104の延出(突出)部に於ける外部接続用電極端子104eに対しては、通常のワイヤボンディング法により、ボンディングワイヤ109sが接続されている。

【0145】

また、当該配線基板101の一方の主面に於いて、前記半導体素子102、半導体素子104ならびにボンディングワイヤ108、ボンディングワイヤ109などを覆って、封止用樹脂112が配設されている。

【0146】

更に、当該配線基板101の他方の主面には、格子状に配設された電極端子113上にはんだボール(はんだバンプ)からなる外部接続用端子114が配設されている。

【0147】

かかる半導体装置140にあっては、第2の半導体素子104の延出(突出)部の長さ(延出長)が比較的大きくなることから、前記バンプ111の配設の有効性は高い。

【0148】

すなわち,第2の半導体素子104に於ける外部接続用電極端子104eにボンディングワイヤ109sの始端を接続する際、当該第2の半導体素子104の被ワイヤボンディング部はバンプ111により機械的に支持される。従って、当該第2の半導体素子104の湾曲が抑制され、当該第2の半導体素子104の破損が防止される。

【0149】

更に、第2の半導体素子104を第1の半導体素子102上に搭載する際に、当該バンプ111によって支持しながら搭載することが可能であるため、第2の半導体素子104を第1の半導体素子102上に傾斜することなく、精度良く積層配設することができる。

【0150】

これにより、半導体装置に於ける第1の半導体素子102と第2の半導体素子104との配置構成の設計自由度が向上する。

(実施形態2)

本発明による半導体装置の実施形態その2について、図9乃至図13用いて説明する。

【0151】

本実施形態に於ける半導体装置は、支持基体である配線基板上にフェイスダウン(フリップチップ)状態をもって搭載され、その外部接続用バンプ電極が当該配線基板上の電極端子に接続される第1の半導体素子と、当該第1の半導体素子上にフェイスアップ状態をもって搭載され、その電極端子パッドがワイヤボンディング法により前記配線基板上の電極端子に接続される第2の半導体素子とを含む。

【0152】

実施形態その2にかかる半導体装置200を、図9に示す。

【0153】

図9Aは、当該半導体装置200の平面を示し、また図9Bは、図9Aに於けるX−X’断面を示す。なお、図9Aにあっては、樹脂封止部の表示を省略し、その外形を実線で示している。

【0154】

当該半導体装置200にあっては、支持基体である配線基板201の一方の主面上に、二つの半導体素子が積層配置されている。

【0155】

即ち、当該配線基板201上には、第1の半導体素子202が、所謂フェイスダウン(フリップチップ)状態をもって搭載され、その電極端子(図示せず)上に配設された外部接続用突起(バンプ)電極202eにより、配線基板201上の電極端子203に接続されている。

【0156】

そして、当該第1の半導体素子202上に、第2の半導体素子204が、接着剤層205を介してフェイスアップ状態をもって搭載されている。

【0157】

ここで、前記第1の半導体素子202は比較的小さな平面形状を有しており、長方形を有する第2の半導体素子204は、当該第1の半導体素子202上に於いて、当該第1の半導体素子202の幅を越えて庇状(片持ち梁状)に延出(突出)して搭載されている。

【0158】

この為、第1の半導体素子202の側部に於いて、第2の半導体素子204の延出(突出)部と配線基板201との間は離間している。

【0159】

当該第1の半導体素子202は、配線基板201と第2の半導体素子204との間に位置して中間部材をなしている。

【0160】

そして、第1の半導体素子202と配線基板201との間には、所謂アンダーフィル材206が充填されている。

【0161】

当該アンダーフィル材206は、配線基板201の、第1の半導体素子202と対向する領域よりも外方に裾状に拡がって配設され、前記第1の半導体素子202の外部接続用突起(バンプ)電極202eと配線基板201上の電極端子203との間の接続を保護するとともに、第1の半導体素子202と配線基板201とを固着する。

【0162】

尚、前記第1の半導体素子202の外部接続用突起電極202eは、当該半導体素子202の主表面(電子回路形成面)に於いて、4つの縁部に沿ってそれぞれ複数個配設されている。

【0163】

また、前記第2の半導体素子204の外部接続用電極端子204eは、当該第2の半導体素子204の長手方向の両端の縁部に沿ってそれぞれ複数個配設されている。

【0164】

一方、前記配線基板201の主面上には、前述の如く、第1の半導体素子202の外部接続用突起電極202eに対応して電極端子203が複数個配設され、また前記第2の半導体素子204の外部接続用電極端子204eに対応して電極端子207が複数個配設されている。

【0165】

そして、第1の半導体素子202の外部接続用突起電極202eと、前記配線基板201上の電極端子201eとの間は圧接接続され、一方、第2の半導体素子204の外部接続用電極端子204eと、前記配線基板201上の電極端子207との間はボンディングワイヤ208により接続されている。

【0166】

尚、第1の半導体素子202の外部接続用突起電極202eは、例えば金(Au)、銅(Cu)、あるいはニッケル(Ni)等を主成分とする合金材料、錫(Sn)−銀(Ag)、錫(Sn)−銀(Ag)−銅(Cu)を主成分とする半田材料、あるいは銀(Ag)等の金属粒子を含有する導電性樹脂材料から形成されている。

【0167】

また、前記アンダーフィル材206は、熱硬化性あるいは熱可塑性の絶縁性樹脂を主体として形成され、例えばエポキシ系、ポリイミド系、アクリル系、あるいはシリコン系樹脂が適用される。

【0168】

尚、当該アンダーフィル材206は、その適用量が比較的少であることから、封止用部材と同一の物性を有するか否かは問われない。

【0169】

本実施形態に於ける特徴的構成として、前記第2の半導体素子204の長手方向の両端部近傍に於ける配線基板201上に、当該第2の半導体素子204の縁に沿って、且つ当該半導体素子204の縁の長さと同等の長さを有する長尺状の導電性パッド209が配設されている。

【0170】

当該導電性パッド209上には、前記第2の半導体素子204に於ける複数個の電極端子204eそれぞれの略直下に位置して、凸状部材であるバンプ210が配設されている。

【0171】

そして、配線基板201の一方の主面に於いて、前記半導体素子202、半導体素子204ならびにボンディングワイヤ208などを覆って、封止用樹脂211が被覆されている。

【0172】

更に、当該配線基板201の他方の主面には、格子状に配設された電極端子212上に、はんだボール(はんだバンプ)からなる外部接続用端子213が配設されている。

【0173】

かかる構成によれば、第1の半導体素子202がフリップチップ方式により搭載されることから、当該半導体素子202からのボンディングワイヤの導出、ならびに当該半導体素子202周囲の配線基板201上への電極端子の配設を必要とせず、半導体装置として大形化を招来しない。

【0174】