半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年の半導体デバイスは多数の露光用マスクを用いて製造されている。各マスクパターンを転写したパターン同士を重ね合わせる際には、パターン間に位置合わせずれが発生するが、この位置合わせずれについては一定の範囲内に制御する必要がある。特に、微細化の進行に伴い、位置合わせの精度が非常に重要になる。言い換えると、位置合わせずれに強い加工方法や構造が求められることになる。

【0003】

そのような位置合わせずれに強い加工方法の1つであるセルフアラインコンタクト(SAC)技術は、ソース・ドレイン領域となる不純物層上にコンタクトホールを自己整合的に形成する技術であり、多くの半導体装置の製造方法において使用されるようになってきている。

【0004】

さらに、コンタクトホールパターンを転写する際に位置合わせずれが発生した場合の対策として、例えば特許文献1に開示されているような方法が提案されている。

【0005】

特許文献1に開示されている方法は、コンタクトホールパターンを転写する際に位置合わせずれが発生した場合にもリーク電流の小さい半導体素子構造を実現するものであって、その具体的内容は以下の通りである。

【0006】

図4(a)〜(f)は、特許文献1に開示されている従来の半導体装置の製造方法の各工程を示す断面図である。

【0007】

まず、図4(a)に示すように、半導体基板500に素子分離用のトレンチ501を形成した後、トレンチ501内に素子分離用絶縁膜502をその表面が半導体基板500の表面と面一になるように埋め込む。続いて、素子分離用絶縁膜502と隣接する領域に位置する半導体基板500の表面部に不純物をイオン注入して不純物層503を形成する。その後、図4(b)に示すように、素子分離用絶縁膜502の上部をエッチングにより除去してトレンチ501の壁面の一部を露出させる。

【0008】

次に、図4(c)に示すように、素子分離用絶縁膜502上を含む半導体基板500上の全面に金属膜504及びキャップ膜505を順次形成した後、熱処理を行って、金属膜504と不純物層503の表面部とを反応させる。これにより、図4(d)に示すように、不純物層503の上面上及びトレンチ501の壁面の一部の上に金属シリサイド膜506が形成される。続いて、図4(e)に示すように、キャップ膜505及び未反応の金属膜504を除去した後、図4(f)に示すように、半導体基板500上の全面に絶縁膜507を形成し、その後、絶縁膜507に、金属シリサイド膜506に達するコンタクトホール508を形成した後、コンタクトホール508に導電膜を埋め込んでコンタクト509を形成する。

【0009】

このように形成された従来の半導体装置は、素子分離用のトレンチ501の壁面の一部が金属シリサイド膜506によって被覆されていることを特徴としている。

【0010】

この特徴により、コンタクトホールを形成時に位置合わせずれが発生しても、トレンチ501の壁面を覆う金属シリサイド膜506によって、コンタクトホールを形成するためのエッチング時に過剰なオーバーエッチングが発生する事態を阻止することができるので、リーク電流の小さい半導体素子構造を形成することが可能になる。

【特許文献1】特開2004−134586号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

近年、デバイスの微細化に伴い、ショートチャネル効果と呼ばれる、ゲート長が小さくなったときに生じるしきい値電圧や飽和電流の変動を抑制するために、ソース・ドレイン領域となる不純物層はますます浅くなってきている。一般的には、Pチャネル型トランジスタにおいてはN型ウェル領域にソース・ドレイン領域となるP型不純物層が形成されており、Nチャネル型トランジスタにおいてはP型ウェル領域にN型不純物層が形成されている。

【0012】

しかしながら、特許文献1に開示されている方法のように、素子分離用絶縁膜502の上部をエッチングにより除去してトレンチ501の壁面の一部を露出させ、当該壁面の一部の上に金属シリサイド膜506を形成した場合には、次のような問題が生じる。

【0013】

まず、図5(a)に示すように、ソース・ドレイン領域となる不純物層503が浅く形成されると、トレンチ501の壁面を覆う金属シリサイド膜506の最下部とPN接合との間隔が小さくなるので、接合リーク電流が生じやすくなり、回路の誤動作や消費電力の増大等の問題が起こる。

【0014】

また、図5(b)に示すように、コンタクトホール508の形成時に位置合わせずれが生じると、不純物層503上の金属シリサイド膜506とコンタクト509との接触面積が小さくなり、コンタクト抵抗が上昇するので、信号遅延や回路の誤動作等の問題が起こる。

【0015】

本発明は、以上の課題に鑑みてなされたものであり、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすること、及び、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにすることを目的とする。

【課題を解決するための手段】

【0016】

前記の目的を達成するために、本発明に係る半導体装置は、基板上に形成された素子分離領域と、前記素子分離領域と隣接するように前記基板上に形成された不純物層と、前記不純物層上に形成されたシリサイド層と、前記シリサイド層と接続するように前記シリサイド層上に形成されたコンタクトとを備え、前記不純物層と前記シリサイド層との界面は、前記素子分離領域の上面よりも低く、前記シリサイド層は前記素子分離領域の上部コーナーを覆っている。

【0017】

本発明に係る半導体装置によると、不純物層とシリサイド層との界面が素子分離領域の上面よりも低くなるようにシリサイド層が形成されているため、シリサイド層の最下部が不純物層上面よりも下側に位置することはない。従って、不純物層が浅く形成された場合にも、シリサイド層とPN接合(不純物層の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層は素子分離領域の上部コーナーを覆っているため、言い換えると、不純物層近傍の素子分離領域の上面がシリサイド層により覆われているため、コンタクトホール形成時に位置合わせずれが生じた場合にも、具体的には、素子分離領域とオーバーラップするようにコンタクトホールが形成された場合にも、シリサイド層とコンタクトとの接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層近傍の素子分離領域の上面がシリサイド層により覆われているため、コンタクトホール形成のためのエッチング時に、素子分離領域を構成する絶縁膜がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0018】

本発明に係る半導体装置において、前記素子分離領域はトレンチ構造を有していてもよい。

【0019】

本発明に係る半導体装置において、前記素子分離領域は前記不純物層よりも深く形成されていてもよい。

【0020】

本発明に係る半導体装置において、前記素子分離領域の幅が100nm以下であると、前述の本発明の効果が顕著に発揮される。すなわち、本発明は、デザインルールが32nm以下の場合に好適である。

【0021】

本発明に係る半導体装置において、前記シリサイド層と前記素子分離領域の上面とのオーバーラップ幅が1nm以上で且つ20nm以下であると、素子分離領域上での素子同士の意図せぬ導通を防止しながら、前述の本発明の効果を得ることができる。

【0022】

本発明に係る半導体装置において、前記シリサイド層は、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム及びパラジウムのうちの少なくとも1つの金属を含んでいてもよい。

【0023】

本発明に係る第1の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜及びキャップ膜を順次形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記工程(c)において、前記素子分離領域と前記不純物層との境界上に位置する部分の前記キャップ膜にクラックを発生させ、前記工程(d)において、前記クラックに沿ってシリサイド反応を進展させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0024】

本発明に係る第1の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0025】

本発明に係る第1の半導体装置の製造方法において、前記キャップ膜は、金属、金属酸化物又は金属窒化物から構成されていてもよい。

【0026】

本発明に係る第1の半導体装置の製造方法において、前記工程(c)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、前記工程(c)において、前記キャップ膜の厚さを前記段差の高さの3倍以上に設定すると、前記工程(c)において、素子分離領域と不純物層との境界上に位置する部分のキャップ膜に確実にクラックを発生させることができる。

【0027】

本発明に係る第2の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記工程(b)と前記工程(c)との間に、イオン注入又は逆スパッタを用いて、前記不純物層の一部分を除去すると共に当該一部分の構成物質を、前記不純物層近傍の前記素子分離領域上に付着させる工程(e)をさらに備え、前記工程(d)において、前記素子分離領域上の前記構成物質と前記金属膜とを反応させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0028】

本発明に係る第2の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0029】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)で、前記不純物層を構成する元素よりも重い元素を用いてイオン注入を行うと、前記工程(e)において、不純物層の一部分を除去して当該一部分の構成物質を、不純物層近傍の素子分離領域上に確実に付着させることができる。

【0030】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)で、Arを用いて逆スパッタを行ってもよい。

【0031】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、前記工程(e)において、前記段差の上部に位置する前記不純物層を除去すると、前記工程(e)において、当該除去部分の構成物質を、不純物層近傍の素子分離領域上に確実に付着させることができる。

【0032】

本発明に係る第3の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記金属膜は、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含み、前記工程(d)において、前記不純物層近傍の前記素子分離領域上に位置する部分の前記金属膜中にシリコンを拡散させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0033】

本発明に係る第3の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0034】

本発明に係る第3の半導体装置の製造方法において、前記第1の金属は、ニッケル、モリブデン、タングステン又は鉄であり、前記第2の金属は、白金、コバルト又はチタンであってもよい。

【0035】

本発明に係る第3の半導体装置の製造方法において、前記工程(c)で、前記素子分離領域の上面と前記不純物層の上面とは面一であってもよい。言い換えると、本発明に係る第3の半導体装置の製造方法においては、前記工程(c)よりも前に、素子分離領域の上面が不純物層の上面よりも低くなるように段差を形成しなくてもよい。

【発明の効果】

【0036】

本発明によれば、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、不純物層が浅く形成された場合にも接合リーク電流の増大を抑制することができると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制することができる。すなわち、信頼性の高い半導体装置を提供することが可能となる。

【発明を実施するための最良の形態】

【0037】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0038】

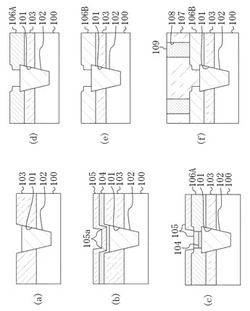

図1(a)〜(f)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0039】

まず、図1(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板100に素子分離用のトレンチ101を形成した後、例えばCVD(chemical vapor deposition )法や塗布法などを用いて、トレンチ101内に素子分離用絶縁膜102を埋め込む。トレンチ101の幅は例えば60〜80nm程度であり、トレンチ101の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜102の上面が半導体基板100の上面と面一になるように素子分離用絶縁膜102の上面を平坦化する。続いて、素子分離用絶縁膜102と隣接する領域に位置する半導体基板100の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層103を形成する。尚、トレンチ101内に埋め込まれた素子分離用絶縁膜102(つまり素子分離領域)は不純物層103よりも深く形成されている。

【0040】

その後、図1(a)に示すように、例えばドライエッチングやウェットエッチングを用いて、トレンチ101内に埋め込まれた素子分離用絶縁膜102の上部をエッチングにより除去する。具体的には、素子分離用絶縁膜102の上面が半導体基板100の上面よりも5nm程度低くなるように素子分離用絶縁膜102を掘り下げる。

【0041】

次に、図1(b)に示すように、素子分離用絶縁膜102上を含む半導体基板100上の全面に、シリサイド形成用の金属膜104及びキャップ膜105を順次形成する。キャップ膜105は、例えば、金属膜、金属酸化膜又は金属窒化膜等からなり、具体的には、キャップ膜105の材料として、チタン、窒化チタン、タンタル、窒化タンタル、タングステン又は窒化タングステン等を用いてもよい。また、キャップ膜105は、例えばCVD法、蒸着法又はスパッタ法などを用いて成膜されるが、本実施形態においては、キャップ膜105の膜厚を、素子分離用絶縁膜102の上面と半導体基板100の上面との間に形成した段差の高さの3倍程度以上(つまり15nm程度以上)に設定する。これにより、図1(b)に示すように、当該段差上に位置する部分のキャップ膜105、つまり素子分離用絶縁膜102(素子分離領域)と不純物層103との境界上に位置する部分のキャップ膜105に応力が集中して、当該部分にクラック(膜割れ)105aが発生する。

【0042】

次に、金属膜104に対して1回目のシリサイド化熱処理を行うことにより、図1(c)に示すように、不純物層103の表面部と金属膜104とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層106Aを形成する。例えば、金属膜104としてニッケルを用いた場合、300℃程度の温度で30秒間のアニールを行い、シリサイド層106AとしてNi2 Siを形成する。

【0043】

ところで、金属とシリコンとの化合物であるシリサイドが形成される場合には体積膨張が起きるが、本実施形態では、素子分離用絶縁膜102と不純物層103との境界上に位置する部分のキャップ膜105にクラック105aが生じているため、クラック105aに沿ってシリサイド反応が進展する。その結果、図1(c)に示すように、素子分離用絶縁膜102(素子分離領域)の上部コーナーを覆うようにシリサイド層106Aが形成される。すなわち、本実施形態では、シリサイド層106Aの下面が素子分離用絶縁膜102の上面よりも低くなり、且つシリサイド層106Aの側端部が素子分離用絶縁膜102の上面と重なるように、シリサイド層106Aを形成する。尚、シリサイド層106Aの形成後の時点で、不純物層103の厚さは例えば30nm程度であり、不純物層103上のシリサイド層106Aの厚さは例えば20〜30nm程度である。

【0044】

次に、図1(d)に示すように、未反応の金属膜104とキャップ膜105とを除去する。例えば、金属膜104としてニッケル膜、キャップ膜105として窒化チタン膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜104及びキャップ膜105の除去が可能である。

【0045】

次に、シリサイド層106Aに対して2回目のシリサイド化熱処理を行うことにより、図1(e)に示すように、所望の低抵抗値を持つシリサイド層106Bを形成する。例えば、金属膜104としてニッケルを用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層106Bを形成する。

【0046】

次に、図1(f)に示すように、シリサイド層106B上及び素子分離用絶縁膜102上を含む半導体基板100上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜107を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜107にシリサイド層106Bに達するコンタクトホール108を形成する。コンタクトホール108の口径は例えば50〜60nm程度である。その後、コンタクトホール108に導電膜を埋め込むことにより、シリサイド層106Bを通じて不純物層103と電気的に接続するコンタクト109を形成する。

【0047】

以上に説明した第1の実施形態によると、不純物層103とシリサイド層106Bとの界面が素子分離用絶縁膜102(素子分離領域)の上面よりも低くなるようにシリサイド層106Bが形成されているため、シリサイド層106Bの最下部が不純物層103の上面よりも下側に位置することはない。従って、不純物層103が浅く形成された場合にも、シリサイド層106BとPN接合(不純物層103の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層106Bは素子分離用絶縁膜102の上部コーナーを覆っているため、言い換えると、不純物層103近傍の素子分離用絶縁膜102の上面がシリサイド層106Bにより覆われているため、コンタクトホール108の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜102とオーバーラップするようにコンタクトホール108が形成された場合にも、シリサイド層106Bとコンタクト109との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層103近傍の素子分離用絶縁膜102の上面がシリサイド層106Bにより覆われているため、コンタクトホール108を形成するためのエッチング時に、素子分離用絶縁膜102がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0048】

また、第1の実施形態によると、シリサイド形成用の金属膜104を覆うキャップ膜105を形成する際に、素子分離用絶縁膜102と不純物層103との境界上(素子分離用絶縁膜102の上面と不純物層103の上面との間の段差上)に位置する部分のキャップ膜105にクラック105aを発生させている。このため、金属膜104に対してシリサイド化熱処理を行う際に、クラック105aに沿ってシリサイド反応を進展させることができるので、素子分離用絶縁膜102(素子分離領域)の上部コーナーを覆うようにシリサイド層106Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0049】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0050】

また、本実施形態において、シリサイド層106Bと素子分離用絶縁膜102(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜102上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【0051】

また、本実施形態において、金属膜104の材料、つまりシリサイド層106Bの構成金属は特に限定されるものではないが、例えば、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム又はパラジウム等を用いることができる。

【0052】

また、本実施形態において、金属膜104を覆うキャップ膜105を形成する時点で、素子分離用絶縁膜102の上面と不純物層103の上面との間の段差高さが5nm程度以上あり、且つキャップ膜105の厚さが15nm程度以上であること、つまり、キャップ膜105の厚さを前記段差高さの3倍以上に設定することが好ましい。このようにすると、素子分離用絶縁膜102と不純物層103との境界上に位置する部分のキャップ膜105にクラック105aを確実に発生させることができる。

【0053】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0054】

図2(a)〜(g)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0055】

まず、図2(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板200に素子分離用のトレンチ201を形成した後、例えばCVD法や塗布法などを用いて、トレンチ201内に素子分離用絶縁膜202を埋め込む。トレンチ201の幅は例えば60〜80nm程度であり、トレンチ201の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜202の上面が半導体基板200の上面と面一になるように素子分離用絶縁膜202の上面を平坦化する。続いて、素子分離用絶縁膜202と隣接する領域に位置する半導体基板200の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層203を形成する。尚、トレンチ201内に埋め込まれた素子分離用絶縁膜202(つまり素子分離領域)は不純物層203よりも深く形成されている。

【0056】

その後、図2(a)に示すように、例えばドライエッチングやウェットエッチングを用いて、トレンチ201内に埋め込まれた素子分離用絶縁膜202の上部をエッチングにより除去する。具体的には、素子分離用絶縁膜202の上面が半導体基板200の上面よりも5nm程度低くなるように素子分離用絶縁膜202を掘り下げる。

【0057】

次に、図2(b)に示すように、イオン注入法により、Geイオン204を、注入エネルギーが20keV、ドーズ量が1×1014atom/cm2 の条件で半導体基板200の全面に注入する。これにより、トレンチ201内の素子分離用絶縁膜202の上面よりも高い部分の半導体基板200がGeイオン204によってスパッタされることになり、半導体基板200(つまり不純物層203)の一部分が除去されると共に当該一部分の構成物質が半導体基板200上に再付着する。特に、素子分離用絶縁膜202との間の段差の上部に位置する不純物層203においてこの現象が顕著に発生するため、当該部分の不純物層203がGeイオン204によってスパッタされ、その結果、当該部分の構成物質(主としてSi)205が、不純物層203近傍の素子分離用絶縁膜202上に再付着する。

【0058】

次に、図2(c)に示すように、素子分離用絶縁膜202上を含む半導体基板200上の全面に、シリサイド形成用の金属膜206を形成する。このとき、金属膜206を覆うようにキャップ膜を形成してもよい。

【0059】

次に、金属膜206に対して1回目のシリサイド化熱処理を行うことにより、図2(d)に示すように、不純物層203の表面部と金属膜206とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層207Aを形成する。例えば、金属膜206としてニッケルを用いた場合、300℃程度の温度で30秒間のアニールを行い、シリサイド層207AとしてNi2 Siを形成する。このとき、図2(b)に示す工程で素子分離用絶縁膜202上に再付着した構成物質(不純物層203つまり基板200を構成するSi)205と金属膜206との間でもシリサイド反応が生じる結果、素子分離用絶縁膜202(素子分離領域)の上部コーナーを覆うようにシリサイド層207Aが形成される。すなわち、本実施形態では、シリサイド層207Aの下面が素子分離用絶縁膜202の上面よりも低くなり、且つシリサイド層207Aの側端部が素子分離用絶縁膜202の上面と重なるように、シリサイド層207Aを形成する。尚、シリサイド層207Aの形成後の時点で、不純物層203の厚さは例えば30nm程度であり、不純物層203上のシリサイド層207Aの厚さは例えば20〜30nm程度である。

【0060】

次に、図2(e)に示すように、未反応の金属膜206を除去する。例えば、金属膜206としてニッケル膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜206の除去が可能である。

【0061】

次に、シリサイド層207Aに対して2回目のシリサイド化熱処理を行うことにより、図2(f)に示すように、所望の低抵抗値を持つシリサイド層207Bを形成する。例えば、金属膜206としてニッケルを用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層207Bを形成する。

【0062】

次に、図2(g)に示すように、シリサイド層207B上及び素子分離用絶縁膜202上を含む半導体基板200上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜208を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜208にシリサイド層207Bに達するコンタクトホール209を形成する。コンタクトホール209の口径は例えば50〜60nm程度である。その後、コンタクトホール209に導電膜を埋め込むことにより、シリサイド層207Bを通じて不純物層203と電気的に接続するコンタクト210を形成する。

【0063】

以上に説明した第2の実施形態によると、不純物層203とシリサイド層207Bとの界面が素子分離用絶縁膜202(素子分離領域)の上面よりも低くなるようにシリサイド層207Bが形成されているため、シリサイド層207Bの最下部が不純物層203の上面よりも下側に位置することはない。従って、不純物層203が浅く形成された場合にも、シリサイド層207BとPN接合(不純物層203の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層207Bは素子分離用絶縁膜202の上部コーナーを覆っているため、言い換えると、不純物層203近傍の素子分離用絶縁膜202の上面がシリサイド層207Bにより覆われているため、コンタクトホール209の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜202とオーバーラップするようにコンタクトホール209が形成された場合にも、シリサイド層207Bとコンタクト210との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層203近傍の素子分離用絶縁膜202の上面がシリサイド層207Bにより覆われているため、コンタクトホール209を形成するためのエッチング時に、素子分離用絶縁膜202がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0064】

また、第2の実施形態によると、シリサイド形成用の金属膜206を形成する前に、イオン注入を用いて、不純物層203の一部分を除去すると共に当該一部分の構成物質205を、不純物層203近傍の素子分離用絶縁膜202上に付着させている。このため、金属膜206に対してシリサイド化熱処理を行う際に、当該構成物質205と金属膜206との間でもシリサイド反応が生じる結果、素子分離用絶縁膜202(素子分離領域)の上部コーナーを覆うようにシリサイド層207Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0065】

また、第2の実施形態によると、図2(b)に示すイオン注入工程よりも前に、図2(a)に示す工程で、素子分離用絶縁膜202の上面が不純物層203の上面よりも低くなるように段差を形成している。このため、図2(b)に示す工程で、素子分離用絶縁膜202との間の段差の上部に位置する不純物層203をイオンによってスパッタ除去し、それにより、当該除去部分の構成物質(主としてSi)205を、不純物層203近傍の素子分離用絶縁膜202上に確実に再付着させることができる。

【0066】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0067】

また、本実施形態において、シリサイド層207Bと素子分離用絶縁膜202(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜202上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【0068】

また、本実施形態において、金属膜206の材料、つまりシリサイド層207Bの構成金属は特に限定されるものではないが、例えば、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム又はパラジウム等を用いることができる。

【0069】

また、本実施形態において、図2(b)に示すイオン注入工程で用いるイオンとしては、基板特性(不純物層203の特性)を変えないイオン、例えば窒素イオンや、基板構成元素と同族の元素のイオン(Si基板であればIV族元素イオン)を用いることができ、その中でも特に、基板構成元素よりも重い元素のイオン(Si基板であればIV族元素イオンのうちのGeイオン)を用いることが好ましい。このようにすると、半導体基板200(つまり不純物層203)の一部分を除去し、当該一部分の構成物質を半導体基板200上に確実に再付着させることができる。

【0070】

また、本実施形態において、図2(b)に示す工程で、イオン注入に代えて、例えばArを用いて逆スパッタを行ってもよい。この場合にも、本実施形態と同様の効果を得ることができる。

【0071】

また、本実施形態において、図2(b)に示すイオン注入工程よりも前に、図2(a)に示す工程で、素子分離用絶縁膜202の上面が不純物層203の上面よりも低くなるように段差を形成したが、当該段差形成工程を省略しても良い。

【0072】

(第3の実施形態)

以下、本発明の第3の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0073】

図3(a)〜(f)は、第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0074】

まず、図3(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板300に素子分離用のトレンチ301を形成した後、例えばCVD法や塗布法などを用いて、トレンチ301内に素子分離用絶縁膜302を埋め込む。トレンチ301の幅は例えば60〜80nm程度であり、トレンチ301の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜302の上面が半導体基板300の上面と面一になるように素子分離用絶縁膜302の上面を平坦化する。続いて、素子分離用絶縁膜302と隣接する領域に位置する半導体基板300の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層303を形成する。尚、トレンチ301内に埋め込まれた素子分離用絶縁膜302(つまり素子分離領域)は不純物層303よりも深く形成されている。

【0075】

次に、図3(b)に示すように、素子分離用絶縁膜302上を含む半導体基板300上の全面に、シリサイド形成用の金属膜304を形成する。このとき、金属膜304を覆うようにキャップ膜を形成してもよい。また、本実施形態の特徴として、金属膜304は、シリサイド反応時にシリコンよりも拡散しやすい(つまり金属拡散が支配的になる)第1の金属(例えばニッケル、モリブデン、タングステン又は鉄)と、シリサイド反応時にシリコンよりも拡散しにくい(つまりシリコン拡散が支配的になる)第2の金属(例えば白金、コバルト又はチタン)とを含んでいる。

【0076】

次に、金属膜304に対して1回目のシリサイド化熱処理を行うことにより、図3(c)に示すように、不純物層303の表面部と金属膜304とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層305Aを形成する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合、450℃程度の温度で30秒間のアニールを行い、シリサイド層305AとしてNiCoSiを形成する。このとき、コバルトのシリサイド化反応においてはシリコンの拡散が支配的であるため、金属膜304中にシリコンが拡散する結果、素子分離用絶縁膜302(素子分離領域)の上部コーナーを覆うようにシリサイド層305Aが形成される。すなわち、シリサイド層305Aの側端部が素子分離用絶縁膜302の上面と重なるようにシリサイド層305Aが形成される。また、ニッケルのシリサイド化反応においてはニッケルの拡散が支配的であるため、不純物層303中にニッケルが拡散する結果、シリサイド層305Aの下面は素子分離用絶縁膜302の上面よりも低くなる。尚、シリサイド層305Aの形成後の時点で、不純物層303の厚さは例えば30nm程度であり、不純物層303上のシリサイド層305Aの厚さは例えば20〜30nm程度である。

【0077】

次に、図3(d)に示すように、未反応の金属膜304を除去する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜304の除去が可能である。

【0078】

次に、シリサイド層305Aに対して2回目のシリサイド化熱処理を行うことにより、図3(e)に示すように、所望の低抵抗値を持つシリサイド層305Bを形成する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層305Bを形成する。

【0079】

次に、図3(f)に示すように、シリサイド層305B上及び素子分離用絶縁膜302上を含む半導体基板300上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜306を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜306にシリサイド層305Bに達するコンタクトホール307を形成する。コンタクトホール307の口径は例えば50〜60nm程度である。その後、コンタクトホール307に導電膜を埋め込むことにより、シリサイド層305Bを通じて不純物層303と電気的に接続するコンタクト308を形成する。

【0080】

以上に説明した第3の実施形態によると、不純物層303とシリサイド層305Bとの界面が素子分離用絶縁膜302(素子分離領域)の上面よりも低くなるようにシリサイド層305Bが形成されているため、シリサイド層305Bの最下部が不純物層303の上面よりも下側に位置することはない。従って、不純物層303が浅く形成された場合にも、シリサイド層305BとPN接合(不純物層303の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層305Bは素子分離用絶縁膜302の上部コーナーを覆っているため、言い換えると、不純物層303近傍の素子分離用絶縁膜302の上面がシリサイド層305Bにより覆われているため、コンタクトホール307の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜302とオーバーラップするようにコンタクトホール307が形成された場合にも、シリサイド層305Bとコンタクト308との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層303近傍の素子分離用絶縁膜302の上面がシリサイド層305Bにより覆われているため、コンタクトホール307を形成するためのエッチング時に、素子分離用絶縁膜302がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0081】

また、第3の実施形態によると、シリサイド形成用の金属膜304が、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含んでいる。このため、金属膜304に対してシリサイド化熱処理を行った際に、第2の金属のシリサイド化反応においてはシリコンの拡散が支配的であるため、金属膜304中にシリコンが拡散する結果、素子分離用絶縁膜302(素子分離領域)の上部コーナーを覆うようにシリサイド層305Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0082】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0083】

また、本実施形態において、シリサイド層305Bと素子分離用絶縁膜302(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜302上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【産業上の利用可能性】

【0084】

本発明は、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、接合リーク電流の増大及びコンタクト抵抗の上昇を抑制することにより、信頼性の高い半導体装置を提供するものであり、非常に有用である。

【図面の簡単な説明】

【0085】

【図1】図1(a)〜(f)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図2】図2(a)〜(g)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図3】図3(a)〜(f)は、本発明の第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図4】図4(a)〜(f)は、従来の半導体装置の製造方法の各工程を示す断面図である。

【図5】図5(a)及び(b)は、従来の半導体装置の製造方法により生じる問題点を説明する図である。

【符号の説明】

【0086】

100 半導体基板

101 トレンチ

102 素子分離用絶縁膜

103 不純物層

104 金属膜

105 キャップ膜

105a キャップ膜のクラック

106A、106B シリサイド層

107 絶縁膜

108 コンタクトホール

109 コンタクト

200 半導体基板

201 トレンチ

202 素子分離用絶縁膜

203 不純物層

204 Geイオン

205 半導体基板(不純物層)の構成物質

206 金属膜

207A、207B シリサイド層

208 絶縁膜

209 コンタクトホール

210 コンタクト

300 半導体基板

301 トレンチ

302 素子分離用絶縁膜

303 不純物層

304 金属膜

305A、305B シリサイド層

306 絶縁膜

307 コンタクトホール

308 コンタクト

【技術分野】

【0001】

本発明は、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年の半導体デバイスは多数の露光用マスクを用いて製造されている。各マスクパターンを転写したパターン同士を重ね合わせる際には、パターン間に位置合わせずれが発生するが、この位置合わせずれについては一定の範囲内に制御する必要がある。特に、微細化の進行に伴い、位置合わせの精度が非常に重要になる。言い換えると、位置合わせずれに強い加工方法や構造が求められることになる。

【0003】

そのような位置合わせずれに強い加工方法の1つであるセルフアラインコンタクト(SAC)技術は、ソース・ドレイン領域となる不純物層上にコンタクトホールを自己整合的に形成する技術であり、多くの半導体装置の製造方法において使用されるようになってきている。

【0004】

さらに、コンタクトホールパターンを転写する際に位置合わせずれが発生した場合の対策として、例えば特許文献1に開示されているような方法が提案されている。

【0005】

特許文献1に開示されている方法は、コンタクトホールパターンを転写する際に位置合わせずれが発生した場合にもリーク電流の小さい半導体素子構造を実現するものであって、その具体的内容は以下の通りである。

【0006】

図4(a)〜(f)は、特許文献1に開示されている従来の半導体装置の製造方法の各工程を示す断面図である。

【0007】

まず、図4(a)に示すように、半導体基板500に素子分離用のトレンチ501を形成した後、トレンチ501内に素子分離用絶縁膜502をその表面が半導体基板500の表面と面一になるように埋め込む。続いて、素子分離用絶縁膜502と隣接する領域に位置する半導体基板500の表面部に不純物をイオン注入して不純物層503を形成する。その後、図4(b)に示すように、素子分離用絶縁膜502の上部をエッチングにより除去してトレンチ501の壁面の一部を露出させる。

【0008】

次に、図4(c)に示すように、素子分離用絶縁膜502上を含む半導体基板500上の全面に金属膜504及びキャップ膜505を順次形成した後、熱処理を行って、金属膜504と不純物層503の表面部とを反応させる。これにより、図4(d)に示すように、不純物層503の上面上及びトレンチ501の壁面の一部の上に金属シリサイド膜506が形成される。続いて、図4(e)に示すように、キャップ膜505及び未反応の金属膜504を除去した後、図4(f)に示すように、半導体基板500上の全面に絶縁膜507を形成し、その後、絶縁膜507に、金属シリサイド膜506に達するコンタクトホール508を形成した後、コンタクトホール508に導電膜を埋め込んでコンタクト509を形成する。

【0009】

このように形成された従来の半導体装置は、素子分離用のトレンチ501の壁面の一部が金属シリサイド膜506によって被覆されていることを特徴としている。

【0010】

この特徴により、コンタクトホールを形成時に位置合わせずれが発生しても、トレンチ501の壁面を覆う金属シリサイド膜506によって、コンタクトホールを形成するためのエッチング時に過剰なオーバーエッチングが発生する事態を阻止することができるので、リーク電流の小さい半導体素子構造を形成することが可能になる。

【特許文献1】特開2004−134586号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

近年、デバイスの微細化に伴い、ショートチャネル効果と呼ばれる、ゲート長が小さくなったときに生じるしきい値電圧や飽和電流の変動を抑制するために、ソース・ドレイン領域となる不純物層はますます浅くなってきている。一般的には、Pチャネル型トランジスタにおいてはN型ウェル領域にソース・ドレイン領域となるP型不純物層が形成されており、Nチャネル型トランジスタにおいてはP型ウェル領域にN型不純物層が形成されている。

【0012】

しかしながら、特許文献1に開示されている方法のように、素子分離用絶縁膜502の上部をエッチングにより除去してトレンチ501の壁面の一部を露出させ、当該壁面の一部の上に金属シリサイド膜506を形成した場合には、次のような問題が生じる。

【0013】

まず、図5(a)に示すように、ソース・ドレイン領域となる不純物層503が浅く形成されると、トレンチ501の壁面を覆う金属シリサイド膜506の最下部とPN接合との間隔が小さくなるので、接合リーク電流が生じやすくなり、回路の誤動作や消費電力の増大等の問題が起こる。

【0014】

また、図5(b)に示すように、コンタクトホール508の形成時に位置合わせずれが生じると、不純物層503上の金属シリサイド膜506とコンタクト509との接触面積が小さくなり、コンタクト抵抗が上昇するので、信号遅延や回路の誤動作等の問題が起こる。

【0015】

本発明は、以上の課題に鑑みてなされたものであり、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすること、及び、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにすることを目的とする。

【課題を解決するための手段】

【0016】

前記の目的を達成するために、本発明に係る半導体装置は、基板上に形成された素子分離領域と、前記素子分離領域と隣接するように前記基板上に形成された不純物層と、前記不純物層上に形成されたシリサイド層と、前記シリサイド層と接続するように前記シリサイド層上に形成されたコンタクトとを備え、前記不純物層と前記シリサイド層との界面は、前記素子分離領域の上面よりも低く、前記シリサイド層は前記素子分離領域の上部コーナーを覆っている。

【0017】

本発明に係る半導体装置によると、不純物層とシリサイド層との界面が素子分離領域の上面よりも低くなるようにシリサイド層が形成されているため、シリサイド層の最下部が不純物層上面よりも下側に位置することはない。従って、不純物層が浅く形成された場合にも、シリサイド層とPN接合(不純物層の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層は素子分離領域の上部コーナーを覆っているため、言い換えると、不純物層近傍の素子分離領域の上面がシリサイド層により覆われているため、コンタクトホール形成時に位置合わせずれが生じた場合にも、具体的には、素子分離領域とオーバーラップするようにコンタクトホールが形成された場合にも、シリサイド層とコンタクトとの接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層近傍の素子分離領域の上面がシリサイド層により覆われているため、コンタクトホール形成のためのエッチング時に、素子分離領域を構成する絶縁膜がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0018】

本発明に係る半導体装置において、前記素子分離領域はトレンチ構造を有していてもよい。

【0019】

本発明に係る半導体装置において、前記素子分離領域は前記不純物層よりも深く形成されていてもよい。

【0020】

本発明に係る半導体装置において、前記素子分離領域の幅が100nm以下であると、前述の本発明の効果が顕著に発揮される。すなわち、本発明は、デザインルールが32nm以下の場合に好適である。

【0021】

本発明に係る半導体装置において、前記シリサイド層と前記素子分離領域の上面とのオーバーラップ幅が1nm以上で且つ20nm以下であると、素子分離領域上での素子同士の意図せぬ導通を防止しながら、前述の本発明の効果を得ることができる。

【0022】

本発明に係る半導体装置において、前記シリサイド層は、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム及びパラジウムのうちの少なくとも1つの金属を含んでいてもよい。

【0023】

本発明に係る第1の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜及びキャップ膜を順次形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記工程(c)において、前記素子分離領域と前記不純物層との境界上に位置する部分の前記キャップ膜にクラックを発生させ、前記工程(d)において、前記クラックに沿ってシリサイド反応を進展させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0024】

本発明に係る第1の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0025】

本発明に係る第1の半導体装置の製造方法において、前記キャップ膜は、金属、金属酸化物又は金属窒化物から構成されていてもよい。

【0026】

本発明に係る第1の半導体装置の製造方法において、前記工程(c)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、前記工程(c)において、前記キャップ膜の厚さを前記段差の高さの3倍以上に設定すると、前記工程(c)において、素子分離領域と不純物層との境界上に位置する部分のキャップ膜に確実にクラックを発生させることができる。

【0027】

本発明に係る第2の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記工程(b)と前記工程(c)との間に、イオン注入又は逆スパッタを用いて、前記不純物層の一部分を除去すると共に当該一部分の構成物質を、前記不純物層近傍の前記素子分離領域上に付着させる工程(e)をさらに備え、前記工程(d)において、前記素子分離領域上の前記構成物質と前記金属膜とを反応させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0028】

本発明に係る第2の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0029】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)で、前記不純物層を構成する元素よりも重い元素を用いてイオン注入を行うと、前記工程(e)において、不純物層の一部分を除去して当該一部分の構成物質を、不純物層近傍の素子分離領域上に確実に付着させることができる。

【0030】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)で、Arを用いて逆スパッタを行ってもよい。

【0031】

本発明に係る第2の半導体装置の製造方法において、前記工程(e)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、前記工程(e)において、前記段差の上部に位置する前記不純物層を除去すると、前記工程(e)において、当該除去部分の構成物質を、不純物層近傍の素子分離領域上に確実に付着させることができる。

【0032】

本発明に係る第3の半導体装置の製造方法は、基板上に素子分離領域を形成する工程(a)と、前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、前記金属膜は、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含み、前記工程(d)において、前記不純物層近傍の前記素子分離領域上に位置する部分の前記金属膜中にシリコンを拡散させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成する。

【0033】

本発明に係る第3の半導体装置の製造方法によると、前述の本発明に係る半導体装置を確実に製造することができる。

【0034】

本発明に係る第3の半導体装置の製造方法において、前記第1の金属は、ニッケル、モリブデン、タングステン又は鉄であり、前記第2の金属は、白金、コバルト又はチタンであってもよい。

【0035】

本発明に係る第3の半導体装置の製造方法において、前記工程(c)で、前記素子分離領域の上面と前記不純物層の上面とは面一であってもよい。言い換えると、本発明に係る第3の半導体装置の製造方法においては、前記工程(c)よりも前に、素子分離領域の上面が不純物層の上面よりも低くなるように段差を形成しなくてもよい。

【発明の効果】

【0036】

本発明によれば、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、不純物層が浅く形成された場合にも接合リーク電流の増大を抑制することができると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制することができる。すなわち、信頼性の高い半導体装置を提供することが可能となる。

【発明を実施するための最良の形態】

【0037】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0038】

図1(a)〜(f)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0039】

まず、図1(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板100に素子分離用のトレンチ101を形成した後、例えばCVD(chemical vapor deposition )法や塗布法などを用いて、トレンチ101内に素子分離用絶縁膜102を埋め込む。トレンチ101の幅は例えば60〜80nm程度であり、トレンチ101の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜102の上面が半導体基板100の上面と面一になるように素子分離用絶縁膜102の上面を平坦化する。続いて、素子分離用絶縁膜102と隣接する領域に位置する半導体基板100の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層103を形成する。尚、トレンチ101内に埋め込まれた素子分離用絶縁膜102(つまり素子分離領域)は不純物層103よりも深く形成されている。

【0040】

その後、図1(a)に示すように、例えばドライエッチングやウェットエッチングを用いて、トレンチ101内に埋め込まれた素子分離用絶縁膜102の上部をエッチングにより除去する。具体的には、素子分離用絶縁膜102の上面が半導体基板100の上面よりも5nm程度低くなるように素子分離用絶縁膜102を掘り下げる。

【0041】

次に、図1(b)に示すように、素子分離用絶縁膜102上を含む半導体基板100上の全面に、シリサイド形成用の金属膜104及びキャップ膜105を順次形成する。キャップ膜105は、例えば、金属膜、金属酸化膜又は金属窒化膜等からなり、具体的には、キャップ膜105の材料として、チタン、窒化チタン、タンタル、窒化タンタル、タングステン又は窒化タングステン等を用いてもよい。また、キャップ膜105は、例えばCVD法、蒸着法又はスパッタ法などを用いて成膜されるが、本実施形態においては、キャップ膜105の膜厚を、素子分離用絶縁膜102の上面と半導体基板100の上面との間に形成した段差の高さの3倍程度以上(つまり15nm程度以上)に設定する。これにより、図1(b)に示すように、当該段差上に位置する部分のキャップ膜105、つまり素子分離用絶縁膜102(素子分離領域)と不純物層103との境界上に位置する部分のキャップ膜105に応力が集中して、当該部分にクラック(膜割れ)105aが発生する。

【0042】

次に、金属膜104に対して1回目のシリサイド化熱処理を行うことにより、図1(c)に示すように、不純物層103の表面部と金属膜104とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層106Aを形成する。例えば、金属膜104としてニッケルを用いた場合、300℃程度の温度で30秒間のアニールを行い、シリサイド層106AとしてNi2 Siを形成する。

【0043】

ところで、金属とシリコンとの化合物であるシリサイドが形成される場合には体積膨張が起きるが、本実施形態では、素子分離用絶縁膜102と不純物層103との境界上に位置する部分のキャップ膜105にクラック105aが生じているため、クラック105aに沿ってシリサイド反応が進展する。その結果、図1(c)に示すように、素子分離用絶縁膜102(素子分離領域)の上部コーナーを覆うようにシリサイド層106Aが形成される。すなわち、本実施形態では、シリサイド層106Aの下面が素子分離用絶縁膜102の上面よりも低くなり、且つシリサイド層106Aの側端部が素子分離用絶縁膜102の上面と重なるように、シリサイド層106Aを形成する。尚、シリサイド層106Aの形成後の時点で、不純物層103の厚さは例えば30nm程度であり、不純物層103上のシリサイド層106Aの厚さは例えば20〜30nm程度である。

【0044】

次に、図1(d)に示すように、未反応の金属膜104とキャップ膜105とを除去する。例えば、金属膜104としてニッケル膜、キャップ膜105として窒化チタン膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜104及びキャップ膜105の除去が可能である。

【0045】

次に、シリサイド層106Aに対して2回目のシリサイド化熱処理を行うことにより、図1(e)に示すように、所望の低抵抗値を持つシリサイド層106Bを形成する。例えば、金属膜104としてニッケルを用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層106Bを形成する。

【0046】

次に、図1(f)に示すように、シリサイド層106B上及び素子分離用絶縁膜102上を含む半導体基板100上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜107を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜107にシリサイド層106Bに達するコンタクトホール108を形成する。コンタクトホール108の口径は例えば50〜60nm程度である。その後、コンタクトホール108に導電膜を埋め込むことにより、シリサイド層106Bを通じて不純物層103と電気的に接続するコンタクト109を形成する。

【0047】

以上に説明した第1の実施形態によると、不純物層103とシリサイド層106Bとの界面が素子分離用絶縁膜102(素子分離領域)の上面よりも低くなるようにシリサイド層106Bが形成されているため、シリサイド層106Bの最下部が不純物層103の上面よりも下側に位置することはない。従って、不純物層103が浅く形成された場合にも、シリサイド層106BとPN接合(不純物層103の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層106Bは素子分離用絶縁膜102の上部コーナーを覆っているため、言い換えると、不純物層103近傍の素子分離用絶縁膜102の上面がシリサイド層106Bにより覆われているため、コンタクトホール108の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜102とオーバーラップするようにコンタクトホール108が形成された場合にも、シリサイド層106Bとコンタクト109との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層103近傍の素子分離用絶縁膜102の上面がシリサイド層106Bにより覆われているため、コンタクトホール108を形成するためのエッチング時に、素子分離用絶縁膜102がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0048】

また、第1の実施形態によると、シリサイド形成用の金属膜104を覆うキャップ膜105を形成する際に、素子分離用絶縁膜102と不純物層103との境界上(素子分離用絶縁膜102の上面と不純物層103の上面との間の段差上)に位置する部分のキャップ膜105にクラック105aを発生させている。このため、金属膜104に対してシリサイド化熱処理を行う際に、クラック105aに沿ってシリサイド反応を進展させることができるので、素子分離用絶縁膜102(素子分離領域)の上部コーナーを覆うようにシリサイド層106Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0049】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0050】

また、本実施形態において、シリサイド層106Bと素子分離用絶縁膜102(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜102上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【0051】

また、本実施形態において、金属膜104の材料、つまりシリサイド層106Bの構成金属は特に限定されるものではないが、例えば、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム又はパラジウム等を用いることができる。

【0052】

また、本実施形態において、金属膜104を覆うキャップ膜105を形成する時点で、素子分離用絶縁膜102の上面と不純物層103の上面との間の段差高さが5nm程度以上あり、且つキャップ膜105の厚さが15nm程度以上であること、つまり、キャップ膜105の厚さを前記段差高さの3倍以上に設定することが好ましい。このようにすると、素子分離用絶縁膜102と不純物層103との境界上に位置する部分のキャップ膜105にクラック105aを確実に発生させることができる。

【0053】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0054】

図2(a)〜(g)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0055】

まず、図2(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板200に素子分離用のトレンチ201を形成した後、例えばCVD法や塗布法などを用いて、トレンチ201内に素子分離用絶縁膜202を埋め込む。トレンチ201の幅は例えば60〜80nm程度であり、トレンチ201の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜202の上面が半導体基板200の上面と面一になるように素子分離用絶縁膜202の上面を平坦化する。続いて、素子分離用絶縁膜202と隣接する領域に位置する半導体基板200の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層203を形成する。尚、トレンチ201内に埋め込まれた素子分離用絶縁膜202(つまり素子分離領域)は不純物層203よりも深く形成されている。

【0056】

その後、図2(a)に示すように、例えばドライエッチングやウェットエッチングを用いて、トレンチ201内に埋め込まれた素子分離用絶縁膜202の上部をエッチングにより除去する。具体的には、素子分離用絶縁膜202の上面が半導体基板200の上面よりも5nm程度低くなるように素子分離用絶縁膜202を掘り下げる。

【0057】

次に、図2(b)に示すように、イオン注入法により、Geイオン204を、注入エネルギーが20keV、ドーズ量が1×1014atom/cm2 の条件で半導体基板200の全面に注入する。これにより、トレンチ201内の素子分離用絶縁膜202の上面よりも高い部分の半導体基板200がGeイオン204によってスパッタされることになり、半導体基板200(つまり不純物層203)の一部分が除去されると共に当該一部分の構成物質が半導体基板200上に再付着する。特に、素子分離用絶縁膜202との間の段差の上部に位置する不純物層203においてこの現象が顕著に発生するため、当該部分の不純物層203がGeイオン204によってスパッタされ、その結果、当該部分の構成物質(主としてSi)205が、不純物層203近傍の素子分離用絶縁膜202上に再付着する。

【0058】

次に、図2(c)に示すように、素子分離用絶縁膜202上を含む半導体基板200上の全面に、シリサイド形成用の金属膜206を形成する。このとき、金属膜206を覆うようにキャップ膜を形成してもよい。

【0059】

次に、金属膜206に対して1回目のシリサイド化熱処理を行うことにより、図2(d)に示すように、不純物層203の表面部と金属膜206とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層207Aを形成する。例えば、金属膜206としてニッケルを用いた場合、300℃程度の温度で30秒間のアニールを行い、シリサイド層207AとしてNi2 Siを形成する。このとき、図2(b)に示す工程で素子分離用絶縁膜202上に再付着した構成物質(不純物層203つまり基板200を構成するSi)205と金属膜206との間でもシリサイド反応が生じる結果、素子分離用絶縁膜202(素子分離領域)の上部コーナーを覆うようにシリサイド層207Aが形成される。すなわち、本実施形態では、シリサイド層207Aの下面が素子分離用絶縁膜202の上面よりも低くなり、且つシリサイド層207Aの側端部が素子分離用絶縁膜202の上面と重なるように、シリサイド層207Aを形成する。尚、シリサイド層207Aの形成後の時点で、不純物層203の厚さは例えば30nm程度であり、不純物層203上のシリサイド層207Aの厚さは例えば20〜30nm程度である。

【0060】

次に、図2(e)に示すように、未反応の金属膜206を除去する。例えば、金属膜206としてニッケル膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜206の除去が可能である。

【0061】

次に、シリサイド層207Aに対して2回目のシリサイド化熱処理を行うことにより、図2(f)に示すように、所望の低抵抗値を持つシリサイド層207Bを形成する。例えば、金属膜206としてニッケルを用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層207Bを形成する。

【0062】

次に、図2(g)に示すように、シリサイド層207B上及び素子分離用絶縁膜202上を含む半導体基板200上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜208を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜208にシリサイド層207Bに達するコンタクトホール209を形成する。コンタクトホール209の口径は例えば50〜60nm程度である。その後、コンタクトホール209に導電膜を埋め込むことにより、シリサイド層207Bを通じて不純物層203と電気的に接続するコンタクト210を形成する。

【0063】

以上に説明した第2の実施形態によると、不純物層203とシリサイド層207Bとの界面が素子分離用絶縁膜202(素子分離領域)の上面よりも低くなるようにシリサイド層207Bが形成されているため、シリサイド層207Bの最下部が不純物層203の上面よりも下側に位置することはない。従って、不純物層203が浅く形成された場合にも、シリサイド層207BとPN接合(不純物層203の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層207Bは素子分離用絶縁膜202の上部コーナーを覆っているため、言い換えると、不純物層203近傍の素子分離用絶縁膜202の上面がシリサイド層207Bにより覆われているため、コンタクトホール209の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜202とオーバーラップするようにコンタクトホール209が形成された場合にも、シリサイド層207Bとコンタクト210との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層203近傍の素子分離用絶縁膜202の上面がシリサイド層207Bにより覆われているため、コンタクトホール209を形成するためのエッチング時に、素子分離用絶縁膜202がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0064】

また、第2の実施形態によると、シリサイド形成用の金属膜206を形成する前に、イオン注入を用いて、不純物層203の一部分を除去すると共に当該一部分の構成物質205を、不純物層203近傍の素子分離用絶縁膜202上に付着させている。このため、金属膜206に対してシリサイド化熱処理を行う際に、当該構成物質205と金属膜206との間でもシリサイド反応が生じる結果、素子分離用絶縁膜202(素子分離領域)の上部コーナーを覆うようにシリサイド層207Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0065】

また、第2の実施形態によると、図2(b)に示すイオン注入工程よりも前に、図2(a)に示す工程で、素子分離用絶縁膜202の上面が不純物層203の上面よりも低くなるように段差を形成している。このため、図2(b)に示す工程で、素子分離用絶縁膜202との間の段差の上部に位置する不純物層203をイオンによってスパッタ除去し、それにより、当該除去部分の構成物質(主としてSi)205を、不純物層203近傍の素子分離用絶縁膜202上に確実に再付着させることができる。

【0066】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0067】

また、本実施形態において、シリサイド層207Bと素子分離用絶縁膜202(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜202上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【0068】

また、本実施形態において、金属膜206の材料、つまりシリサイド層207Bの構成金属は特に限定されるものではないが、例えば、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム又はパラジウム等を用いることができる。

【0069】

また、本実施形態において、図2(b)に示すイオン注入工程で用いるイオンとしては、基板特性(不純物層203の特性)を変えないイオン、例えば窒素イオンや、基板構成元素と同族の元素のイオン(Si基板であればIV族元素イオン)を用いることができ、その中でも特に、基板構成元素よりも重い元素のイオン(Si基板であればIV族元素イオンのうちのGeイオン)を用いることが好ましい。このようにすると、半導体基板200(つまり不純物層203)の一部分を除去し、当該一部分の構成物質を半導体基板200上に確実に再付着させることができる。

【0070】

また、本実施形態において、図2(b)に示す工程で、イオン注入に代えて、例えばArを用いて逆スパッタを行ってもよい。この場合にも、本実施形態と同様の効果を得ることができる。

【0071】

また、本実施形態において、図2(b)に示すイオン注入工程よりも前に、図2(a)に示す工程で、素子分離用絶縁膜202の上面が不純物層203の上面よりも低くなるように段差を形成したが、当該段差形成工程を省略しても良い。

【0072】

(第3の実施形態)

以下、本発明の第3の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

【0073】

図3(a)〜(f)は、第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0074】

まず、図3(a)に示すように、公知のフォトレジスト工程及び異方性ドライエッチングを用いて、例えばシリコンからなる半導体基板300に素子分離用のトレンチ301を形成した後、例えばCVD法や塗布法などを用いて、トレンチ301内に素子分離用絶縁膜302を埋め込む。トレンチ301の幅は例えば60〜80nm程度であり、トレンチ301の深さは例えば200〜300nm程度である。その後、例えば化学機械研磨法などを用いて、素子分離用絶縁膜302の上面が半導体基板300の上面と面一になるように素子分離用絶縁膜302の上面を平坦化する。続いて、素子分離用絶縁膜302と隣接する領域に位置する半導体基板300の表面部に不純物をイオン注入して、例えばトランジスタのソース・ドレイン領域となる不純物層303を形成する。尚、トレンチ301内に埋め込まれた素子分離用絶縁膜302(つまり素子分離領域)は不純物層303よりも深く形成されている。

【0075】

次に、図3(b)に示すように、素子分離用絶縁膜302上を含む半導体基板300上の全面に、シリサイド形成用の金属膜304を形成する。このとき、金属膜304を覆うようにキャップ膜を形成してもよい。また、本実施形態の特徴として、金属膜304は、シリサイド反応時にシリコンよりも拡散しやすい(つまり金属拡散が支配的になる)第1の金属(例えばニッケル、モリブデン、タングステン又は鉄)と、シリサイド反応時にシリコンよりも拡散しにくい(つまりシリコン拡散が支配的になる)第2の金属(例えば白金、コバルト又はチタン)とを含んでいる。

【0076】

次に、金属膜304に対して1回目のシリサイド化熱処理を行うことにより、図3(c)に示すように、不純物層303の表面部と金属膜304とを反応させてシリサイド(ダイ金属シリサイド:M2 Si(Mは金属))層305Aを形成する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合、450℃程度の温度で30秒間のアニールを行い、シリサイド層305AとしてNiCoSiを形成する。このとき、コバルトのシリサイド化反応においてはシリコンの拡散が支配的であるため、金属膜304中にシリコンが拡散する結果、素子分離用絶縁膜302(素子分離領域)の上部コーナーを覆うようにシリサイド層305Aが形成される。すなわち、シリサイド層305Aの側端部が素子分離用絶縁膜302の上面と重なるようにシリサイド層305Aが形成される。また、ニッケルのシリサイド化反応においてはニッケルの拡散が支配的であるため、不純物層303中にニッケルが拡散する結果、シリサイド層305Aの下面は素子分離用絶縁膜302の上面よりも低くなる。尚、シリサイド層305Aの形成後の時点で、不純物層303の厚さは例えば30nm程度であり、不純物層303上のシリサイド層305Aの厚さは例えば20〜30nm程度である。

【0077】

次に、図3(d)に示すように、未反応の金属膜304を除去する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合には、硫酸と過酸化水素との混合液を用いることにより、残存する金属膜304の除去が可能である。

【0078】

次に、シリサイド層305Aに対して2回目のシリサイド化熱処理を行うことにより、図3(e)に示すように、所望の低抵抗値を持つシリサイド層305Bを形成する。例えば、金属膜304として、ニッケル及びコバルトを含む合金膜を用いた場合、500℃程度の温度で30秒間のアニールを行い、シリサイド層305Bを形成する。

【0079】

次に、図3(f)に示すように、シリサイド層305B上及び素子分離用絶縁膜302上を含む半導体基板300上の全面に公知の方法を用いて、例えば厚さ200〜300nm程度の絶縁膜306を形成した後、リソグラフィー法及び異方性ドライエッチング法を用いて、絶縁膜306にシリサイド層305Bに達するコンタクトホール307を形成する。コンタクトホール307の口径は例えば50〜60nm程度である。その後、コンタクトホール307に導電膜を埋め込むことにより、シリサイド層305Bを通じて不純物層303と電気的に接続するコンタクト308を形成する。

【0080】

以上に説明した第3の実施形態によると、不純物層303とシリサイド層305Bとの界面が素子分離用絶縁膜302(素子分離領域)の上面よりも低くなるようにシリサイド層305Bが形成されているため、シリサイド層305Bの最下部が不純物層303の上面よりも下側に位置することはない。従って、不純物層303が浅く形成された場合にも、シリサイド層305BとPN接合(不純物層303の下面)との間隔が小さくなることがないので、接合リーク電流の増大を抑制することができる。また、シリサイド層305Bは素子分離用絶縁膜302の上部コーナーを覆っているため、言い換えると、不純物層303近傍の素子分離用絶縁膜302の上面がシリサイド層305Bにより覆われているため、コンタクトホール307の形成時に位置合わせずれが生じた場合にも、具体的には、素子分離用絶縁膜302とオーバーラップするようにコンタクトホール307が形成された場合にも、シリサイド層305Bとコンタクト308との接触面積を確保することができる。従って、コンタクト抵抗の上昇を抑制することができる。また、この場合、不純物層303近傍の素子分離用絶縁膜302の上面がシリサイド層305Bにより覆われているため、コンタクトホール307を形成するためのエッチング時に、素子分離用絶縁膜302がエッチングされる量を低減できるので、接合リーク電流をさらに抑制することができる。

【0081】

また、第3の実施形態によると、シリサイド形成用の金属膜304が、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含んでいる。このため、金属膜304に対してシリサイド化熱処理を行った際に、第2の金属のシリサイド化反応においてはシリコンの拡散が支配的であるため、金属膜304中にシリコンが拡散する結果、素子分離用絶縁膜302(素子分離領域)の上部コーナーを覆うようにシリサイド層305Aを形成することができ、前述の本実施形態の特徴的構造を実現することができる。

【0082】

尚、以上に述べた本実施形態の効果は、デザインルールが32nm以下の世代において特に顕著に発揮されるものである。すなわち、本発明は素子分離領域幅が100nm以下の場合に特に好適である。

【0083】

また、本実施形態において、シリサイド層305Bと素子分離用絶縁膜302(素子分離領域)の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることが好ましい。このようにすると、素子分離用絶縁膜302上での素子同士の意図せぬ導通を防止しながら、前述の本実施形態の効果を得ることができる。

【産業上の利用可能性】

【0084】

本発明は、不純物層上に形成されたシリサイド層と、不純物層と電気的に接続するコンタクトとを具備する半導体装置において、接合リーク電流の増大及びコンタクト抵抗の上昇を抑制することにより、信頼性の高い半導体装置を提供するものであり、非常に有用である。

【図面の簡単な説明】

【0085】

【図1】図1(a)〜(f)は、本発明の第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図2】図2(a)〜(g)は、本発明の第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図3】図3(a)〜(f)は、本発明の第3の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図4】図4(a)〜(f)は、従来の半導体装置の製造方法の各工程を示す断面図である。

【図5】図5(a)及び(b)は、従来の半導体装置の製造方法により生じる問題点を説明する図である。

【符号の説明】

【0086】

100 半導体基板

101 トレンチ

102 素子分離用絶縁膜

103 不純物層

104 金属膜

105 キャップ膜

105a キャップ膜のクラック

106A、106B シリサイド層

107 絶縁膜

108 コンタクトホール

109 コンタクト

200 半導体基板

201 トレンチ

202 素子分離用絶縁膜

203 不純物層

204 Geイオン

205 半導体基板(不純物層)の構成物質

206 金属膜

207A、207B シリサイド層

208 絶縁膜

209 コンタクトホール

210 コンタクト

300 半導体基板

301 トレンチ

302 素子分離用絶縁膜

303 不純物層

304 金属膜

305A、305B シリサイド層

306 絶縁膜

307 コンタクトホール

308 コンタクト

【特許請求の範囲】

【請求項1】

基板上に形成された素子分離領域と、

前記素子分離領域と隣接するように前記基板上に形成された不純物層と、

前記不純物層上に形成されたシリサイド層と、

前記シリサイド層と接続するように前記シリサイド層上に形成されたコンタクトとを備え、

前記不純物層と前記シリサイド層との界面は、前記素子分離領域の上面よりも低く、

前記シリサイド層は前記素子分離領域の上部コーナーを覆っていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記素子分離領域はトレンチ構造を有することを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記素子分離領域は前記不純物層よりも深く形成されていることを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記素子分離領域の幅は100nm以下であることを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記シリサイド層と前記素子分離領域の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記シリサイド層は、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム及びパラジウムのうちの少なくとも1つの金属を含むことを特徴とする半導体装置。

【請求項7】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜及びキャップ膜を順次形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記工程(c)において、前記素子分離領域と前記不純物層との境界上に位置する部分の前記キャップ膜にクラックを発生させ、

前記工程(d)において、前記クラックに沿ってシリサイド反応を進展させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7に記載の半導体装置の製造方法において、

前記キャップ膜は、金属、金属酸化物又は金属窒化物からなることを特徴とする半導体装置の製造方法。

【請求項9】

請求項7又は8に記載の半導体装置の製造方法において、

前記工程(c)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、

前記工程(c)において、前記キャップ膜の厚さを前記段差の高さの3倍以上に設定することを特徴とする半導体装置の製造方法。

【請求項10】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記工程(b)と前記工程(c)との間に、イオン注入又は逆スパッタを用いて、前記不純物層の一部分を除去すると共に当該一部分の構成物質を、前記不純物層近傍の前記素子分離領域上に付着させる工程(e)をさらに備え、

前記工程(d)において、前記素子分離領域上の前記構成物質と前記金属膜とを反応させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法において、

前記工程(e)において、前記不純物層を構成する元素よりも重い元素を用いてイオン注入を行うことを特徴とする半導体装置の製造方法。

【請求項12】

請求項10に記載の半導体装置の製造方法において、

前記工程(e)において、Arを用いて逆スパッタを行うことを特徴とする半導体装置の製造方法。

【請求項13】

請求項10〜12のいずれか1項に記載の半導体装置の製造方法において、

前記工程(e)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、

前記工程(e)において、前記段差の上部に位置する前記不純物層を除去することを特徴とする半導体装置の製造方法。

【請求項14】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記金属膜は、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含み、

前記工程(d)において、前記不純物層近傍の前記素子分離領域上に位置する部分の前記金属膜中にシリコンを拡散させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法において、

前記第1の金属は、ニッケル、モリブデン、タングステン又は鉄であり、

前記第2の金属は、白金、コバルト又はチタンであることを特徴とする半導体装置の製造方法。

【請求項16】

請求項14又は15に記載の半導体装置の製造方法において、

前記工程(c)において、前記素子分離領域の上面と前記不純物層の上面とは面一であることを特徴とする半導体装置の製造方法。

【請求項1】

基板上に形成された素子分離領域と、

前記素子分離領域と隣接するように前記基板上に形成された不純物層と、

前記不純物層上に形成されたシリサイド層と、

前記シリサイド層と接続するように前記シリサイド層上に形成されたコンタクトとを備え、

前記不純物層と前記シリサイド層との界面は、前記素子分離領域の上面よりも低く、

前記シリサイド層は前記素子分離領域の上部コーナーを覆っていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記素子分離領域はトレンチ構造を有することを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記素子分離領域は前記不純物層よりも深く形成されていることを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記素子分離領域の幅は100nm以下であることを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記シリサイド層と前記素子分離領域の上面とのオーバーラップ幅は1nm以上で且つ20nm以下であることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記シリサイド層は、ニッケル、白金、コバルト、チタン、ジルコニウム、ハフニウム、タンタル、モリブデン、タングステン、鉄、イリジウム及びパラジウムのうちの少なくとも1つの金属を含むことを特徴とする半導体装置。

【請求項7】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜及びキャップ膜を順次形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記工程(c)において、前記素子分離領域と前記不純物層との境界上に位置する部分の前記キャップ膜にクラックを発生させ、

前記工程(d)において、前記クラックに沿ってシリサイド反応を進展させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7に記載の半導体装置の製造方法において、

前記キャップ膜は、金属、金属酸化物又は金属窒化物からなることを特徴とする半導体装置の製造方法。

【請求項9】

請求項7又は8に記載の半導体装置の製造方法において、

前記工程(c)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、

前記工程(c)において、前記キャップ膜の厚さを前記段差の高さの3倍以上に設定することを特徴とする半導体装置の製造方法。

【請求項10】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記工程(b)と前記工程(c)との間に、イオン注入又は逆スパッタを用いて、前記不純物層の一部分を除去すると共に当該一部分の構成物質を、前記不純物層近傍の前記素子分離領域上に付着させる工程(e)をさらに備え、

前記工程(d)において、前記素子分離領域上の前記構成物質と前記金属膜とを反応させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法において、

前記工程(e)において、前記不純物層を構成する元素よりも重い元素を用いてイオン注入を行うことを特徴とする半導体装置の製造方法。

【請求項12】

請求項10に記載の半導体装置の製造方法において、

前記工程(e)において、Arを用いて逆スパッタを行うことを特徴とする半導体装置の製造方法。

【請求項13】

請求項10〜12のいずれか1項に記載の半導体装置の製造方法において、

前記工程(e)よりも前に、前記素子分離領域の上面が前記不純物層の上面よりも低くなるように段差を形成する工程をさらに備え、

前記工程(e)において、前記段差の上部に位置する前記不純物層を除去することを特徴とする半導体装置の製造方法。

【請求項14】

基板上に素子分離領域を形成する工程(a)と、

前記素子分離領域と隣接するように前記基板上に不純物層を形成する工程(b)と、

前記不純物層上及び前記素子分離領域上に金属膜を形成する工程(c)と、

熱処理を行うことにより、前記不純物層の表面部と前記金属膜とを反応させてシリサイド層を形成する工程(d)とを備え、

前記金属膜は、シリサイド反応時にシリコンよりも拡散しやすい第1の金属と、シリサイド反応時にシリコンよりも拡散しにくい第2の金属とを含み、

前記工程(d)において、前記不純物層近傍の前記素子分離領域上に位置する部分の前記金属膜中にシリコンを拡散させることにより、前記素子分離領域の上部コーナーを覆うように前記シリサイド層を形成することを特徴とする半導体装置の製造方法。

【請求項15】

請求項14に記載の半導体装置の製造方法において、

前記第1の金属は、ニッケル、モリブデン、タングステン又は鉄であり、

前記第2の金属は、白金、コバルト又はチタンであることを特徴とする半導体装置の製造方法。

【請求項16】

請求項14又は15に記載の半導体装置の製造方法において、

前記工程(c)において、前記素子分離領域の上面と前記不純物層の上面とは面一であることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−182962(P2010−182962A)

【公開日】平成22年8月19日(2010.8.19)

【国際特許分類】

【出願番号】特願2009−26588(P2009−26588)

【出願日】平成21年2月6日(2009.2.6)

【出願人】(000005821)パナソニック株式会社 (73,050)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年8月19日(2010.8.19)

【国際特許分類】

【出願日】平成21年2月6日(2009.2.6)

【出願人】(000005821)パナソニック株式会社 (73,050)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]