半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、例えば、DRAM(Dynamic Random Access Memory)素子等の半導体装置の分野においては、半導体装置が使用される機器の高機能化等により、さらなる高集積化が進められている。

また、このような、半導体装置に備えられるトランジスタの微細化に伴い、ショートチャネル効果によるトランジスタ特性の悪化や、コンタクトホール径の縮小によるコンタクト抵抗の増加が問題となっている。

【0003】

これらの問題を解決し、さらに微細化を進めるため、埋め込みゲート型のトランジスタが提案されている。このような埋め込みゲート型トランジスタは、高集積化に適しているため、例えば、DRAMのセルトランジスタとしての利用も検討されている(例えば、特許文献1、非特許文献1を参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−180150号公報

【非特許文献】

【0005】

【非特許文献1】T. Schloesser,et.al,「インターナショナル・エレクトロン・デバイス・ミーティング(International Electron Devices Meeting)」,P809〜812,2008.,

【発明の概要】

【発明が解決しようとする課題】

【0006】

以下、従来の構成の埋め込みゲート型のセルトランジスタを備えるDRAM(半導体装置)について、図41〜図46を参照しながら説明する。

図41に示す例のように、DRAMに備えられる埋め込みゲート型のセルトランジスタは、n型のトランジスタとして構成され、ライン状にパターニングされた活性領域201と、同様にライン状の埋め込みゲート電極パターン202が形成されている。隣接するトランジスタとの素子分離は、STI(Shallow Trench Isolation)構造を用いるのが一般的であるが、図41に示す半導体装置では、縦方向の素子間はSTI領域204によって分離され、横方向に隣接する素子間は埋め込みゲート電極によって分離される。ここで、トランジスタの埋め込みゲート電極パターン202と素子分離用の埋め込みゲート電極パターン203は、同時形成が可能であることから公知のダブルパターニング技術が適用でき、さらなる微細化に好適な構造であることが知られている。

【0007】

図42に、図41に示すA−Aの位置に対応したトランジスタの断面図を示す。図42に示すように、TiN/W積層膜で構成されるゲート電極253、254、及び、隣接セルトランジスタとの分離用ゲート電極255は、p型シリコン基板の表面よりも深い位置に埋め込まれた構造とされている。また、詳細な図示を省略するが、容量コンタクトプラグ258は、DRAMの容量(キャパシタ)に、ビット線側コンタクトプラグ259はビット線に接続されている。

【0008】

上述のように、高集積化が求められるDRAMのセルトランジスタではあるが、高集積化と同時に、セル容量への電荷の書き込み・読み出しに十分な電流駆動能力を確保することも必要となる。さらに、セル容量に書き込まれた電荷を保持するために、接合リーク電流を低く抑えることも必要となる.

【0009】

図43に、セル容量に電荷を保持している状態のトランジスタの模式図を示す。図43に示すように、トランジスタはセル容量に電荷を蓄えているため、容量側のpn接合は、容量側空乏層端265から基板側空乏層端269までの範囲で空乏化する。ここで、トランジスタのリーク電流は、容量側pn接合の空乏層中における生成電流が主な成分であり、これは、接合電界によって生じるTAT(Trap Assisted Tunneling)によって大きく加速される。このため、DRAMセルトランジスタにおいては、容量側の接合電界を低く抑えることが重要となり、容量側のn型拡散層の濃度は薄く設計されている。従って、容量側とビット線側では、ソース・ドレイン拡散層のpn接合の深さが異なった構造とされている。

【0010】

図44(a)、(b)を用いて、セル容量に電荷が保持されている状態におけるトランジスタ中の電界分布を模式的に説明する。ここで、ゲート電極の埋め込みが深い構造における電界分布を図44(a)に、ゲート電極の埋め込みが浅い構造における電界分布を図44(b)に示す。図44(a)、(b)の各々の不純物濃度プロファイルは同じであるが、図44(b)に示すようにゲート電極の埋め込みが浅くなると、容量側pn接合の空乏層中に発生する電界が強くなり、その勾配も急峻になることが判る。このため、ゲート電極の埋め込みが浅くなると接合リークが増加し、DRAMのリフレッシュ特性が低下する。従って、埋め込みゲート型トランジスタをDRAMのセルトランジスタに適用する場合には、ゲート電極の埋め込みを、接合電界が十分緩和できる深さに設計する必要がある。

【0011】

しかしながら、ゲート電極の埋め込みを深くした場合、容量側n型拡散層とゲート電極の距離が大きくなり過ぎ、濃度が薄く設計されている容量側n型拡散層の抵抗が増加する。このため、図45のグラフに示すように、ゲート電極の埋め込みが浅い場合(図44(b))に対して、ゲートの埋め込みが深い場合(図44(a))は、電流駆動能力が大きく減少してしまう。特に、図41に示すように、活性領域パターン201の方向に隣接するDRAMセルとの素子分離をトランジスタで行う構造においては、素子分離用トランジスタのゲート電位の影響により、さらにソース・ドレイン拡散層の抵抗が増加して電流が低下する。

【0012】

図46(a)、(b)の断面模式図に、トランジスタがオン状態の電流密度分布を示す。図46(a)は、素子分離用ゲート電極に0Vの電圧が印加された状態を示し、図46(b)は、−0.5Vの電圧が印加された状態を示している。通常、素子分離用トランジスタのゲート電極には、トランジスタをオフするため、図46(b)に示すような負電位が印加される。この際、図46(a)に示すような正電位の場合と比較して、図46(b)に示すような負電位が印加された場合には、素子分離用ゲート電極近傍の電子密度が低下し、これによって電流密度も低下してしまう。

【0013】

上述のように、従来の半導体装置においては、埋め込みゲート型トランジスタをDRAMのセルトランジスタとして使用する場合、接合リークを低減するためにゲート電極の埋め込みを深くすると、電流駆動能力も低下してしまうという問題があった。

【課題を解決するための手段】

【0014】

本発明の半導体装置は、半導体基板に形成された複数の埋め込みゲート型トランジスタを有する半導体装置であり、前記半導体基板には、STI(Shallow Trench Isolation)構造を有する素子分離領域と、該素子分離領域に囲まれた活性領域とが形成されており、前記半導体基板に形成されるゲートトレンチと、前記ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、前記活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極と、前記半導体基板の上面側に設けられ、前記活性領域内において、前記埋め込みゲート電極を挟むように前記ゲートトレンチの両側に位置するソース・ドレイン拡散層と、が備えられており、前記埋め込みゲート電極が、それぞれ仕事関数が異なるゲート材料からなる上部電極と下部電極とが積層された構造とされており、且つ、前記半導体基板の上面側の前記ソース・ドレイン拡散層側に配置される前記上部電極が、前記下部電極に比べて、仕事関数の低いゲート材料から構成されることを特徴とする。

【0015】

係る構成の半導体装置によれば、半導体基板のゲートトレンチ内に設けられる埋め込みゲート電極を上部電極と下部電極とから構成し、ソース・ドレイン拡散層側に配置される上部電極を、下部電極をなすゲート材料よりも仕事関数が低いゲート材料から構成することにより、埋め込みゲート電極を深い位置に形成した場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができる。

【0016】

本発明の半導体装置の製造方法は、上記構成の半導体装置を製造する方法であり、半導体基板に、STI(Shallow Trench Isolation)構造を有する素子分離領域を形成することにより、該素子分離領域に囲まれた活性領域を形成する工程と、前記半導体基板の表面をエッチングすることによってゲートトレンチを形成する工程と、前記ゲートトレンチの底部にゲート材料を堆積させることによって下部電極を形成した後、さらに、前記下部電極の上にゲート材料を堆積させることによって上部電極を形成し、且つ、前記下部電極と前記上部電極を、それぞれ仕事関数が異なるゲート材料から形成するとともに、前記上部電極を、前記下部電極に比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が前記活性領域を複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極を形成する工程と、前記半導体基板の上面側からイオン注入を行った後、熱処理することにより、前記活性領域内において、前記埋め込みゲート電極を挟んで前記ゲートトレンチの両側に位置するようにソース・ドレイン拡散層を形成する工程と、を備えることを特徴とする。

【0017】

係る構成の半導体装置の製造方法によれば、上記した構成を有し、接合リーク電流を抑制しながら、電極近傍の電流密度を確保できる半導体装置を製造することが可能となる。

【発明の効果】

【0018】

本発明の半導体装置によれば、上記構成を採用することにより、接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力が確保されたものとなるので、素子特性に優れた半導体装置が得られる。

また、本発明の半導体装置の製造方法によれば、上記した方法を採用することにより、接合リーク電流が低減されるとともに、高い電流駆動能力を備える半導体装置を製造することが可能となる。

【図面の簡単な説明】

【0019】

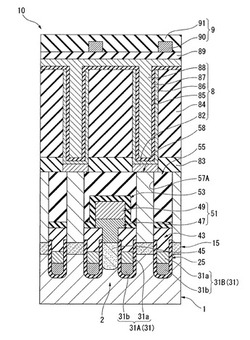

【図1】本発明を適用した一実施形態である半導体装置を示す模式断面図である。

【図2】本発明を適用した一実施形態である半導体装置を示す模式平面図である。

【図3】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図4】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図5】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図6】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図7】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図8】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図9】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図10】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図11】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図12】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図13】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図14】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図15】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図16】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図17】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図18】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図19】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図20】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図21】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図22】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図23】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図24】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図25】本発明を適用した一実施形態である半導体装置を説明するための模式図であり、図2中に示すA−A’線に沿った断面図で、(a)トランジスタの電荷保持状態の電解分布を示す図、(b)トランジスタがオン状態の電流密度分布を示す図である。

【図26】本発明を適用した一実施形態である半導体装置を説明するための模式図であり、(a)接合電界のゲート埋め込み深さ依存性を示すグラフ、(b)オン電流のゲート埋め込み深さ依存性を示すグラフである。

【図27】本発明を適用した他の例である半導体装置を説明するための模式平面図である。

【図28】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図29】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図30】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図31】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図32】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図33】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図34】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図35】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図36】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図37】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図38】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図39】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図40】本発明を適用した他の例である半導体装置を説明するための模式図であり、トランジスタのドレイン電流のゲート電圧依存性を示すグラフである。

【図41】従来の半導体装置を説明するための模式平面図である。

【図42】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図である。

【図43】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図である。

【図44】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図で、(a)ゲート電極の埋め込みが深い場合の電界分布を示す図、(b)ゲート電極の埋め込みが浅い場合の電界分布を示す図である。

【図45】従来の半導体装置の製造方法を説明するための模式図であり、ゲート電極の埋め込みが深い場合と浅い場合の電流駆動能力の差を示すグラフである。

【図46】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図で、(a)素子分離用のゲート電極に0Vの電圧を印加した際の電流密度分布を示す図、(b)、素子分離用のゲート電極に−0.5Vの電圧を印加した際の電流密度分布を示す図である。

【発明を実施するための形態】

【0020】

以下に、本発明を適用した一実施形態である半導体装置及びその製造方法について、図面を適宜参照しながら説明する。本実施形態においては、半導体装置の一例として、n型MOS−FET構造で構成されるメモリセルトランジスタを備えたDRAM(Dynamic Random Access Memory)に、本発明を適用した場合を例に挙げて説明する。なお、以下の説明において参照する図面は、本実施形態の半導体装置の製造方法を説明する図面であって、図示される各部の大きさや厚さや寸法等は、実際の半導体装置等の寸法関係とは異なっていることがある。また、以下の説明において例示する材料や寸法等は一例であり、本発明はそれらに必ずしも限定されるものではなく、その要旨を変更しない範囲で適宜変更して実施することが可能である。

【0021】

[半導体装置]

まず、本発明を適用した一実施形態である半導体装置を適用して得られるDRAM(半導体装置)の構成について説明する。

図1は本発明を適用した半導体装置の一実施形態であるDRAM10のメモリセル領域の一部を示す模式断面図であり、図2は模式平面図である。以下の説明においては、図2中に示す、活性領域1aのパターンに平行な埋め込みゲート型MOSトランジスタ(埋め込みゲート型トランジスタ:図1中の符号2を参照)のB−B’線(又はA−A’線)に沿った断面図を適宜参照しながら説明を行う。

【0022】

図2に示すように、DRAM10のメモリセル領域には、素子分離溝からなる素子分離領域4に囲まれて区画された活性領域1aが、所定方向に所定間隔で複数形成されている。また、活性領域1aを縦断するように、ワード線となる埋め込みゲート電極31A(31)及び素子分離用の埋め込みゲート電極31B(31)が、所定方向(図2中における縦長方向)に所定の間隔で埋め込み形成されている。さらに、図2中においては図示を省略するが、埋め込みゲート電極31A、31Bと直交する方向(図2中における横幅方向)に、図1中に示すビット線51が所定の間隔で複数配置されている。そして、埋め込みゲート電極31Aと活性領域1aとが交差する領域にそれぞれメモリセルが形成されている。

【0023】

本実施形態で説明するDRAM10は、より具体的には、半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には、STI構造を有する素子分離領域4と、素子分離領域4に囲まれた活性領域1aとが形成されており、半導体基板1に形成されるゲートトレンチ13と、該ゲートトレンチ13の内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域1aを複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31(31A、31B)と、半導体基板1の上面側に設けられ、活性領域1a内において、埋め込みゲート電極31A、31Bを挟むようにゲートトレンチ13の両側に位置するソース・ドレイン拡散層15、45と、が備えられている。そして、DRAM10は、埋め込みゲート電極31A、31Bが、それぞれ仕事関数が異なるゲート材料からなる上部電極31aと下部電極31bとが積層された構造とされており、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる構成を採用している。

【0024】

ここで、埋め込みゲート電極(ワード線)31A及び埋め込みゲート電極(素子分離)31Bは、同一の構造を有しているが、機能が異なっている。ここで、埋め込みゲート電極31Aがメモリセルのゲート電極として用いられるのに対して、素子分離用の埋め込みゲート電極31Bは、所定の電位をかけて隣接するトランジスタ間を分離するために設けられている。すなわち、同一の活性領域1a上で隣接するトランジスタ間は、素子分離用の埋め込みゲート電極31Bを所定の電位に維持することで、寄生トランジスタをオフ状態として分離する。

【0025】

また、メモリセル領域全体には、複数のメモリセルが形成されており、個々のメモリセルには、それぞれキャパシタ素子(図1を参照)が設けられている。また、それらキャパシタが接続される容量コンタクトパッド82は、図1に示すように、それぞれが重ならないように、メモリセル領域内に所定の間隔で配置されている。

なお、本実施形態で説明するDRAM10は、図1に示すように、6F2セル配置(Fは最小加工寸法)とされている。

【0026】

次に、DRAM10を構成するメモリセルについて詳しく説明する。

図1に示すように、DRAM10を構成するメモリセルは、ワード線が半導体基板内に完全に埋め込まれた埋め込みゲート型トランジスタ、キャパシタ、配線層が形成された積層構造体である。

【0027】

埋め込みゲート型MOSトランジスタ2は、上記したように、表層がシリコンからなる半導体基板1と、半導体基板1に形成された埋め込み絶縁膜からなる素子分離膜(素子分離領域4)と、素子分離領域4によって区画形成された活性領域1aと、ゲートトレンチ13の内部にゲート絶縁膜25を介して埋め込み形成され、上部電極31a及び下部電極31bからなる積層構造とされた埋め込みゲート電極31A、31Bと、半導体基板1の表面を覆うとともに、ゲートトレンチ13の内部で埋め込みゲート電極31A、31Bの上面を保護する第1層間絶縁膜43と、該第1層間絶縁膜43を介して上方に形成されるビット線51と、から概略構成されている。

また、上記構成の埋め込みゲート型MOSトランジスタ2は、半導体基板1における、埋め込みゲート電極31A、31Bの幅方向両側の活性領域1aにイオンを注入することによって形成される、ソース・ドレイン拡散層15、45を備えている。そして、ソース・ドレイン拡散層15が容量コンタクトプラグ58を介してキャパシタ構造8に接続されているとともに、ソース・ドレイン拡散層45とビット線51とが接続されている。

【0028】

また、上記したように、埋め込みゲート電極31A、31Bは、ともに、上部電極31a及び下部電極31bからなる積層構造とされており、上部電極31a及び下部電極31bは、それぞれ仕事関数が異なるゲート材料から構成されている。さらに、埋め込みゲート電極31A、31Bは、上部電極31aが、下部電極31bに比べて仕事関数の低いゲート材料から構成されている。

【0029】

本発明においては、埋め込みゲート電極31A、31Bを構成する上部電極31a及び下部電極31bの各々の仕事関数を上記関係に規定することにより、ゲート電極の埋め込みを深くした場合であっても、特に、素子分離用の埋め込みゲート電極31Bの近傍における電流密度が低下することなく、十分な電流駆動能力を確保することが可能となる。これは、半導体基板1の上面側に配されるソース・ドレイン拡散層15、45の近傍に、仕事関数が低いゲート材料からなる上部電極31aを配置することにより、n型不純物濃度が薄く設計されている容量側のソース・ドレイン拡散層15の抵抗が抑制され、埋め込みゲート電極31A、31B近傍の電流密度が確保されるためである。

【0030】

ここで、素子分離として設けられる埋め込みゲート電極31Bは、通常、トランジスタをオフにするための負電位が印加されるが、従来の構成のゲート電極を用いた場合には、電極近傍の電子密度が低下することで電流密度も低下し、十分な電流駆動能力が得られ難いという問題がある。本発明では、埋め込みゲート電極31B(31A)を上記構成の積層構造とすることにより、埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができ、十分な電流駆動能力が得られるという効果が得られる。

【0031】

埋め込みゲート電極31A、31Bは、上部電極31aが、仕事関数が4.1〜4.4eVの範囲であるゲート材料からなり、また、下部電極31bが、仕事関数が4.4eV超5.3eV以下の範囲であるゲート材料からなることが好ましい。上部電極31a及び下部電極31bの仕事関数を、上記範囲の関係とすることにより、上記効果がより顕著に得られる。

【0032】

また、本実施形態では、上部電極31aと下部電極31bの仕事関数の関係を上記範囲とするにあたり、そのゲート材料は特に限定されない。しかしながら、本実施形態においては、例えば、上部電極31aに、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかを用いたうえで、下部電極31bに、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかをゲート材料として用いることができる。また、本実施形態では、これらのゲート材料を用いたうえで、上部電極31aを構成するゲート材料が、下部電極31bを構成するゲート材料よりも仕事関数が低い組み合わせで構成することで、上記効果がより顕著に得られる。

より具体的には、上部電極31a/下部電極31bの組み合わせを、例えば、N+ポリシリコン/メタル(TiNとWの積層膜)、Al/メタル(TiNとWの積層膜)、導電性カーボン/N+ポリシリコン、導電性カーボン/(TiNとWの積層膜)等の組み合わせとすることができる。

【0033】

なお、本発明においては、素子分離として設けられる埋め込みゲート電極31Bのみならず、ワード線として設けられる埋め込みゲート電極31Aについても、上記した積層構造として構成しているが、これには限定されない。本実施形態では、工程上、埋め込みゲート電極31A、31Bを同時に形成することが可能であることから、これら各ゲート電極を同じ構成としているが、本発明においては、少なくとも素子分離用の埋め込みゲート電極31Bが上記条件の積層構造とされていれば、上記効果が十分に得られる。

例えば、詳細を後述する埋め込みゲート電極を形成する工程において、埋め込みゲート電極31Aと埋め込みゲート電極31Bを別工程として形成する場合には、素子分離用の埋め込みゲート電極31Bのみを上記構成とし、ワード線として設けられる埋め込みゲート電極を従来の構成とすることも可能である。

【0034】

また、本実施形態で説明する埋め込みゲート型MOSトランジスタ2は、詳細な図示を省略するが、素子分離として設けられる埋め込みゲート電極31Bの底面の一部が、当該埋め込みゲート電極31Bの長手方向に配置された隣接する素子分離膜の間に埋め込む構成となっている。これにより、素子分離膜と、埋め込みゲート電極31Bの埋め込まれた底面の一部の側面部分との間には、半導体基板1の一部である、図示略の薄膜状シリコン部がサイドウォール形状に設けられる。

【0035】

ここで、埋め込みゲート電極(ワード線)31A及び埋め込みゲート電極(素子分離)31Bは同じ構造を有していることから、埋め込みゲート電極31Aの底面の一部においても同様の薄膜状シリコン部が設けられる。この薄膜状シリコン部は、ソース領域とドレイン領域との電位差が閾値を超えた際に、チャネルとして機能させることができる。このように、本実施形態の埋め込みゲート型MOSトランジスタ2は、薄膜状シリコン部のようなチャネル領域を有するリセスチャネル型トランジスタとして構成される。

【0036】

埋め込みゲート型MOSトランジスタ2の上方には、層間絶縁膜55等を介してキャパシタ構造8が設けられている。具体的には、層間絶縁膜55上には、埋め込みゲート型MOSトランジスタ2のソース・ドレイン拡散層15と容量コンタクトプラグ58を介して接続される容量コンタクトパッド82が設けられている。そして、この容量コンタクトパッド82上に、ストッパー膜83及び第3層間絶縁膜84を貫通するように設けられた第1電極86、容量絶縁膜87及び第2電極88から構成されるキャパシタ構造8が形成されている。

【0037】

なお、本実施形態のキャパシタ構造8は、下部側の第1電極86の内壁のみを電極として利用するシリンダー型を一例として記載しているが、これに限定されるものではない。例えば、第1電極の内壁及び外壁を電極として利用するクラウン型キャパシタに変更することも可能である。

【0038】

配線層は、上記構成のキャパシタ構造8上に第4層間絶縁膜89を介して設けられており、上部金属配線90及び保護膜91から構成されている。本実施形態では、配線層が1層配線構造の場合を一例として記載しているが、これに限定されるものではない。例えば、複数の配線層及び層間絶縁膜から構成される多層配線構造に変更することも可能である。

【0039】

上述したような本発明に係る半導体素子であるDRAM10によれば、半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には、STI構造を有する素子分離領域4と、素子分離領域4に囲まれた活性領域1aとが形成されており、半導体基板1に形成されるゲートトレンチ13と、該ゲートトレンチ13の内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域1aを複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、半導体基板1の上面側に設けられ、活性領域1a内において、埋め込みゲート電極31を挟むようにゲートトレンチ13の両側に位置するソース・ドレイン拡散層15、45と、埋め込みゲート電極31A、31Bが、それぞれ仕事関数が異なるゲート材料からなる上部電極31aと下部電極31bとが積層された構造とされている。そして、DRAM10によれば、さらに、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる構成を採用している。即ち、DRAM10は、上述のような積層構造とされた埋め込みゲート電極31A、31Bを備えた構成なので、接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力が確保されたものとなり、優れた素子特性が得られる。

【0040】

[半導体装置の製造方法]

続いて、上記構成を有するDRAM(半導体装置)10の製造方法について、図3〜図24を参照しながら説明する。ここで、図3〜図24は、本実施形態のDRAMの製造方法を説明するための図であり、各図における断面は、それぞれ、図2中に示すA−A’線に沿った断面か、あるいは、B−B’線に沿った断面をそれぞれ示している。

【0041】

本実施形態のDRAM(半導体装置)10の製造方法は、半導体基板1に、STI構造を有する素子分離領域4を形成することにより、素子分離領域4に囲まれた活性領域1aを形成する工程と、半導体基板1の表面をエッチングすることによってゲートトレンチ13を形成する工程と、ゲートトレンチ13の底部にゲート材料を堆積させることによって下部電極31bを形成した後、さらに、下部電極31bの上にゲート材料を堆積させることによって上部電極31aを形成し、且つ、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が活性領域1aを複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極31A、31Bを形成する工程と、半導体基板1の上面側からイオン注入を行った後、熱処理することにより、活性領域1a内において、埋め込みゲート電極31A、31Bを挟んでゲートトレンチ13の両側に位置するようにソース・ドレイン拡散層15、45を形成する工程と、を具備して概略構成されている。

以下に、各工程について、詳細に説明する。

【0042】

まず、シリコンからなる半導体基板1の表面に、通常の方法で、活性領域1aを分離するための素子分離領域4(図2を参照)を形成する。素子分離領域4の形成は、詳細な図示を省略するが、まず、例えばP型のシリコン基板(半導体基板1)上に、シリコン酸化膜(SiO2)とマスク用のシリコン窒化膜(Si3N4)とを順次堆積する。次に、フォトリソグラフィ技術およびドライエッチング技術を用いて、これらシリコン窒化膜、シリコン窒化膜、及び、半導体基板1のパターニングを順次行ない、半導体基板1に活性領域1aを区画するための素子分離溝(トレンチ)を形成する。また、半導体基板1の活性領域1aとなるシリコン表面は、マスク用のシリコン窒化膜で覆われている。この際、STI構造に埋め込まれる絶縁膜としては、例えば、HDP−CVDによる酸化膜、又は、SOD(Spin On Dielectric)等の塗布材料を用いることができる。そして、例えば、ウェットエッチング等の方法によって、マスク用のシリコン窒化膜およびシリコン酸化膜を除去する。このようにして、素子分離領域を構成するSTI(Shallow Trench Isolation)素子分離膜を形成することで素子分離領域4を形成することにより、半導体基板1に活性領域1aを区画形成する。

【0043】

次に、図3に示すように、素子分離溝内に露出する半導体基板1の表面にシリコン酸化膜12を形成する。

具体的には、素子分離溝内の半導体基板1の表面とともに、半導体基板1の活性領域1aを被覆する図示略のシリコン窒化膜及びシリコン窒化膜の表面に、通常の熱酸化により、シリコン酸化膜12を、例えば、10nm程度の膜厚で形成する。

【0044】

次に、半導体基板1の表面に不純物を拡散させることにより、容量側のソース・ドレイン拡散層15を形成する。

具体的には、まず、図4に示すように、シリコン酸化膜12をマスクとして、半導体基板1の活性領域1aに、例えば、リン等のn型不純物を、1.0×1013/cm2程度の濃度で、20keVの加速エネルギーでイオン注入する。そして、窒素雰囲気中で980℃・10秒の熱処理を行うことにより、n型不純物が拡散されたソース・ドレイン拡散層40を形成する.このソース・ドレイン拡散層15は、埋め込みゲート型MOSトランジスタ2のソース・ドレイン領域の一部として機能する。

【0045】

次に、図5に示すように、LP−CVDを用いて窒化シリコン材料を堆積させることにより、シリコン窒化膜17を、例えば150nm程度の膜厚で形成する。

次に、図6に示すように、通常の液浸露光技術及び材料を用い、幅40nmのレジストパターン21を、90nmピッチで形成する。

【0046】

次に、図7に示すように、周知のドライエッチング技術を用いて、シリコン窒化膜17を異方性エッチングした後、レジストパターン21を除去し、異方性エッチングによってシリコン酸化膜12を除去する。

【0047】

次に、図7に示すように、CF4とArの混合ガスにH2を添加したガスを用いる異方性ドライエッチングにより、半導体基板1のシリコン酸化膜12及びシリコン窒化膜15から露出する位置をエッチングすることにより、ゲートトレンチ13を形成する。この際、ゲートトレンチ13の深さとしては、例えば、140nm程度とする。このゲートトレンチ13は、活性領域1aと交差する所定の方向(例えば、図1中の縦長方向)に延在するライン状のパターンとして形成される。

【0048】

また、詳細な図示を省略するが、ゲートトレンチ13を形成する際に、素子分離膜の表面の高さが、半導体基板1の表面の高さよりも低くなるように、素子分離膜の部分を深くエッチングする。また、ゲートトレンチ13の深さは、素子分離膜と同等か、もしくは、素子分離膜の方が深い構造となるようにする。

【0049】

次に、図8に示すように、ゲートトレンチ13の内面を覆うように、ゲート酸化膜25を、例えば、4nm程度の膜厚で形成する。この際、ゲート酸化膜25としては、例えば、ゲートトレンチ13の内面表層を、ISSG(in−situ steam generation)によって熱酸化することによって形成することができる。

【0050】

次に、ゲートトレンチ13の内部のゲート酸化膜25上にゲート材料を順次堆積させることにより、これらの材料をゲートトレンチ13内に埋め込み、上部電極31a及び下部電極31bからなる埋め込みゲート電極31A、31Bを形成する。

具体的には、図9に示すように、まず、ゲートトレンチ13の内部に、例えば、窒化チタン(TiN)を下層側とて堆積させ、その上にタングステン(W)を堆積させることにより、TiN/Wの積層膜を形成する。この際、各積層膜の膜厚としては、例えば、TiNを5nm程度、Wを80nm程度とすることができる。なお、図9に示す例では、詳細な図示を省略するが、上層側として堆積させるWを、半導体基板1の表面を覆うまで堆積させている。

【0051】

次いで、図10に示すように、TiN/Wの積層膜の一部を、通常のドライエッチング等の方法でエッチバックして除去することにより、下部電極31bを、ゲートトレンチ13の底部に残存した状態で形成する。この際、シリコン窒化膜17をマスクとして、例えば、TiN/Wの積層膜を、半導体基板1の表面、即ち、ゲートトレンチ13の入口から、90nm程度の位置までエッチバックする。

【0052】

次いで、図11に示すように、ゲートトレンチ13の底部に形成した下部電極31bの上に、リンを1×1020/cm3〜1×1022/cm3の濃度、より好ましくは1×1020/cm3でドープしたポリシリコン材料を、例えば、80nmの膜厚で堆積させる。この際、ゲートトレンチ13内に先に埋め込まれた、下部電極31bの上層側のW膜とポリシリコンとの界面がシリサイド化されるが、過度のシリサイド化を抑制するため、ポリシリコン材料の堆積前に、バリア膜及び低抵抗シリサイド膜を形成する構成とすることも可能である。また、ポリシリコン材料を、520℃程度の成膜温度でアモルファス状態として堆積させ、後の熱処理によって結晶化することでシリコン結晶粒を大きくする条件とした場合には、低抵抗化の効果が得られる。

【0053】

そして、シリコン窒化膜17をマスクとして、通常のドライエッチング技術を用いて、ポリシリコンを半導体基板1の表面から、例えば、70nmの位置までエッチバックすることにより、下部電極31bの上に、n型ポリシリコンからなる上部電極31aを形成する。

以上のような手順により、ゲートトレンチ13の内部に、上部電極31a及び下部電極31bの積層構造からなる、埋め込みゲート電極31A、31Bを形成する。

【0054】

本発明においては、埋め込みゲート電極31A、31Bを形成するにあたり、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成する。これにより、上述したように、電極の埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができ、十分な電流駆動能力が得られるという効果が得られる。特に、素子分離として設けられる埋め込みゲート電極31Bを上記方法で形成することにより、電極近傍の電流密度が低下すること無く、十分な電流駆動能力が得られるものとなる。

【0055】

また、上述したように、埋め込みゲート電極31A、31Bを形成する工程においては、上部電極31aとして、仕事関数が4.1〜4.4eVの範囲であるゲート材料を用いるとともに、下部電極31bとして、仕事関数が4.4eV超5.3eV以下の範囲であるゲート材料を用いることが、上記効果が顕著に得られる点からより好ましい。

【0056】

また、上述のような仕事関数の条件を満足できるゲート材料としては、例えば、下部電極31bを、窒化チタン(TiN)/タングステン(W)積層膜、導電性カーボンの何れかを用いて形成したうえで、上部電極31aを、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかを用いて形成することができる。また、これらのゲート材料を用いたうえで、上部電極31aの形成に用いるゲート材料を、下部電極31bの形成に用いるゲート材料よりも仕事関数が低い組み合わせとすることにより、上記効果がより顕著に得られる。

【0057】

次に、図12に示すように、埋め込みゲート電極31A、31Bの上、即ち、上部電極31aの表面に、プラズマ酸化膜を、例えば、140nm程度の膜厚で堆積させた後、シリコン窒化膜17をマスクとして、CMPによってプラズマ酸化膜を研磨除去する。このような手順により、埋め込みゲート電極31A、31Bの上に、第1層間絶縁膜43を形成する。

【0058】

次に、図13に示すように、従来公知のリソグラフィ及びドライエッチング技術を用いてシリコン窒化膜17を選択的に除去することにより、ビット線と接続するためのコンタクトホール46を形成する。

ここで、コンタクトホール46は、例えば、図2に示すように、ワード線として設けられる埋め込みゲート電極31Aと同一の方向(図2中における縦長方向)に延在するライン状の開口パターンとして形成する。また、コンタクトホール46の開口パターンと活性領域1aとが交差する部分では、コンタクトホール46から半導体基板1のシリコン表面が露出する。

【0059】

次に、図14に示すように、半導体基板1の表面にリン等のn型の不純物を注入することにより、ビット線側のソース・ドレイン拡散層45を形成する。

具体的には、コンタクトホール46から露出した半導体基板1の表面に、2.0×1015/cm2の濃度のリンを、5keVの加速エネルギーでイオン注入した後、950℃で10秒の熱処理を行うことにより、ビット線側のソース・ドレイン拡散層45を形成する。この際、第1層間絶縁膜43をマスクとして、コンタクトホール46から露出する半導体基板1の表面に不純物(リン)をイオン注入することで、ソース・ドレイン拡散層45を形成する。このソース・ドレイン拡散層は、トランジスタのソース・ドレイン領域の一方として機能する、ビット線側のソース・ドレイン拡散層45となる。

【0060】

次に、図15に示すように、ビット線51を形成する。この際、まず、半導体基板1の表面及び第1層間絶縁膜43の表面を覆うように、例えば、N型の不純物であるリンを1×1020/cm3程度の濃度でドープした膜厚が80nm程度のポリシリコン47を形成する。この際、コンタクトホール46内に、ポリシリコン47を確実に埋め込むように形成する。

次いで、このポリシリコン47の上に、例えば、膜厚が5nm程度の窒化タングステン(WN)と、膜厚70nm程度のタングステン(W)膜とを順次堆積させることにより、W/WN膜49を形成する。

【0061】

次いで、図15に示すように、従来公知のリソグラフィ及びドライエッチング技術を用い、W/WN膜49およびポリシリコン47からなる積層膜をライン形状にパターニングすることにより、ビット線51を形成する(図1も参照)。

【0062】

このビット線51は、コンタクトホール46内において、ビット線側のソース・ドレイン拡散層45と接続される。即ち、ビット線51を構成するポリシリコン47と、コンタクトホール46から露出している半導体基板1の表面部分に形成されたソース・ドレイン拡散層45とが接続される。このように、本実施形態のビット線51は、埋め込みゲート型MOSトランジスタ2のソース・ドレイン領域の一方であるとともに、素子分離として設けられるソース・ドレイン拡散層45と接続するコンタクトプラグの機能を兼ねるものである。本実施形態の製造方法では、このようなコンタクトプラグの機能を兼ねるビット線51を、上記工程により、一回のリソグラフィ工程で形成(一括形成)することが可能である。

【0063】

また、ビット線51は、埋め込みゲート電極31A、31Bと交差する方向(図2中における横幅方向)に延在するパターンとして形成される。なお、ビット線51は、埋め込みゲート電極31A、31Bと直交する直線形状とすることができるが、これに限定されるものではなく、例えば、一部を湾曲させた形状として配置してもよい。

【0064】

次に、図16に示すように、例えば、LP−CVD法を用いて、半導体基板1の表面及び第1層間絶縁膜43の表面、並びに、ビット線51を覆うように窒化シリコン(Si3N4)を堆積させることにより、膜厚が10nm程度のシリコン窒化膜53を形成する。

【0065】

次に、容量コンタクトプラグ58を形成する。容量コンタクトプラグ58の形成にあたっては、まず、先ず、図17に示すように、後工程で形成する配線層との間に配される第2層間絶縁膜55を形成する。

具体的には、例えば、CVD法を用いて、シリコン窒化膜53上を覆うように、B(ボロン)及びP(リン)を含有するSiO2膜、即ち、BPSG(Boron Phosphor Silicate Glass)膜を400nm程度の膜厚で堆積させる。そして、750℃で30分程度のリフロー処理を行うことにより、第2層間絶縁膜55を形成する。

【0066】

次に、図18に示すように、従来公知のリソグラフィ技術を用いて、容量側コンタクトホールパターン57を形成し、これをマスクとして、通常の異方性ドライエッチングによって第2層間絶縁膜55をエッチングすることにより、容量コンタクトホール57Aを形成する。

【0067】

具体的には、まず、第2層間絶縁膜55上に、例えば、埋め込みゲート電極31A、31Bと同一の方向(図2中における縦長方向)に延在するライン状の開口パターンを有するように、容量側コンタクトホールパターン57を形成する。

次に、この容量側コンタクトホールパターン57から露出する第2層間絶縁膜55、シリコン窒化膜53及びシリコン窒化膜17を順次エッチングして除去することにより、容量コンタクトホール57Aを形成する。

ここで、図18に示すように、容量コンタクトホール57Aと活性領域1a(図2を参照)とが重なる部分では、容量コンタクトホール57Aから半導体基板1のシリコン表面が露出する。

【0068】

次に、第2層間絶縁膜55上に、容量コンタクトホール57A内を埋め込むように、LP−CVD法を用いて、リンを1×1020/cm3の濃度でドープしたポリシリコンを、厚さ80nm程度で堆積させる。次いで、図19に示すように、CMP法によってポリシリコンを研磨除去することにより、容量コンタクトホール57A内を充填するように、容量コンタクトプラグ58を形成する。

【0069】

以上のような手順で形成した埋め込みゲート型MOSトランジスタ2は、従来のような、埋め込みゲート電極がTiN/W積層膜のみのトランジスタと同様、チャネルポテンシャルの制御をTiN/W積層膜のゲートで行うため、従来と同等のサブスレッショルド特性としきい値電圧を得ることが可能となる

【0070】

ここで、本実施形態で説明する方法によって製造されたトランジスタ(埋め込みゲート型MOSトランジスタ2)の電荷保持状態の電界分布を、図25(a)の模式図に示す。図25(a)中に示すように、N+ポリシリコンの仕事関数は、Ti/W積層膜よりも低いことから、容量側のソース・ドレイン拡散層からシリコンの半導体基板に向かうポテンシャル変化が従来に比べて緩やかになり、容量側の接合電界が大きく緩和される。これにより、従来の構成とされたトランジスタに比べ、接合リーク電流を低く抑えることが可能となる。

【0071】

また、図25(b)の模式図に、本実施形態で説明する方法によって製造されたトランジスタがオン状態である場合の電流密度分布を示す。図25(b)中に示すように、N+ポリシリコンの仕事関数は、Ti/W積層膜よりも低いことから、N+ポリシリコンをソース・ドレイン拡散層側に配置することにより、低濃度に設計された容量側ソース・ドレイン拡散層中の電子密度の低下が、従来に比べて抑制されている。従って、容量側ソース・ドレイン拡散層中の電流密度も増加し、効果的にオン電流を増加させることが可能となる。

【0072】

本実施形態においては、オン電流を確保しながら接合電界を緩和するため、埋め込みゲート電極31Bの上面が、容量側のソース・ドレイン拡散層15の接合位置61と同じ深さになるように制御している。また、埋め込みゲート電極31Bの上面と容量側のソース・ドレイン拡散層15の接合位置61との関係は、同じ深さに限定するものではなく、例えば、10nm程度のオーバーラップ、又は、10nm程度のオフセットを有する範囲であれば良い。

【0073】

ここで、図26(a)、(b)のグラフに、接合電界及びオン電流のゲート埋め込み深さ依存性を、各々示す。図26(a)、(b)において、グラフの横軸は、シリコンの半導体基板表面から埋め込みゲート電極上端までの距離である。本実施形態で説明する例では、容量側のソース・ドレイン拡散層の接合位置61が70nmに制御されていることから、埋め込みゲート電極の上端の距離が70nmよりも浅ければ、容量側のソース・ドレイン拡散層とオーバーラップした構造となり、埋め込みゲート電極の上端の距離が70nmよりも深ければ、容量側のソース・ドレイン拡散層とオフセットした構造となる。図26(a)、(b)におけるグラフの縦軸は、一般的なDRAM製品の規格を満たす数値で規格化されている。即ち、図26(a)、(b)のグラフにおいては、電界は1.0以下、オン電流は1.0以上で製品規格を満足する。従来の方法で得られる、従来の構成のトランジスタの場合、ゲートの埋め込み深さを72nmから76nmの範囲で管理する必要があるが、本発明により、ゲートの埋め込み深さを60nmから84nmの範囲とした場合でも製品動作が可能となる。

【0074】

なお、本発明においては、埋め込みゲート電極の埋め込み深さは、製品が動作する範囲内で任意の値を採用することが可能である。例えば、埋め込みゲート電極の埋め込み深さを60nmとすれば、従来と同等の接合電界を維持しながら、オン電流が増加する。従って、従来と同等のリフレッシュ特性を維持しながら、高速動作が可能となる。

同様に、ゲートの埋め込み深さを84nmとすれば、従来と同等のオン電流を維持しながら、接合電界を緩和できる。従って、従来と同等の動作速度を維持しながら、リフレッシュ周期を長くすることで、消費電力を低下させることが可能となる。

【0075】

そして、本発明においては、上記構成の埋め込みゲート型MOSトランジスタ2上に、さらに、キャパシタ構造8並びに配線層を形成することにより、DRAM構造を有する半導体装置(DRAM10)を製造することができる。

【0076】

まず、キャパシタ構造8を形成する。キャパシタ構造8の形成にあたっては、まず、容量コンタクトプラグ58を形成した後の基板の表面に、窒化タングステン(WN)及びタングステン(W)を順次堆積して積層膜を形成する。次に、この積層膜をパターニングして、図20に示すような容量コンタクトパッド82を形成する。ここで、メモリセル領域においては、容量コンタクトパッド82を均等な間隔で形成する必要がある。このため、図20に示すように、容量コンタクトパッド82は、容量コンタクトプラグ58の直上からずらした位置に形成されるが、容量コンタクトパッド82の底面と容量コンタクトプラグ58の上面とが重なる部分で容量コンタクトパッド82が接続される。

【0077】

次に、図21に示すように、基板上に、容量コンタクトパッド82を覆うように、例えば、シリコン窒化膜等を用いてストッパー膜83を形成する。次に、このストッパー膜83の上に、例えばシリコン酸化膜等を用いて第3層間絶縁膜84を形成する。

【0078】

次に、図22に示すように、第3層間絶縁膜84と容量コンタクトパッド82上のストッパー膜83とを貫通するコンタクトホール85を形成して、容量コンタクトパッド82の上面の一部を露出させる。次に、コンタクトホール85の内壁面と、露出する容量コンタクトパッド82の上面とを覆うようにして、例えば、窒化チタン等を用いてキャパシタ構造8の第1電極86を形成する。これにより、第1電極86の底面は、容量コンタクトパッド82の上面と接続される。

【0079】

次に、図23に示すように、第3層間絶縁膜84の上に、第1電極86の表面を覆うようにして容量絶縁膜87を形成する。容量絶縁膜87としては、例えば、酸化ジルコニウム(ZrO2)、酸化アルミニウム(Al2O3)、酸化ハフニウム(HfO2)及びこれらの積層膜を用いることができる。次に、容量絶縁膜87の表面を覆うように、例えば、窒化チタン等を用いてキャパシタ構造8の第2電極88を形成する。このようにして、キャパシタ構造8を形成する。

【0080】

次に、キャパシタ構造8を介して、半導体基板1上に配線層9を形成する。配線層9の形成にあたっては、まず、図24に示すように、第2電極88の上に、この第2電極88を覆うようにして、例えば、シリコン酸化膜等からなる第4層間絶縁膜89を形成する。次に、第4層間絶縁膜89の上に、例えばアルミニウム(Al)や銅(Cu)等で上部金属配線90を形成する。その後、上部金属配線90を覆うように保護膜91を形成することにより、DRAMのメモリセルが完成する。

上記各工程により、本実施形態のDRAM10を製造することができる。

【0081】

以上説明したように、本発明に係る半導体素子であるDRAM10の製造方法によれば、半導体基板1に、STI構造を有する素子分離領域4を形成することにより、素子分離領域4に囲まれた活性領域1aを形成する工程と、半導体基板1の表面をエッチングすることによってゲートトレンチ13を形成する工程と、ゲートトレンチ13の底部にゲート材料を堆積させることによって下部電極31bを形成した後、さらに、下部電極31bの上にゲート材料を堆積させることによって上部電極31aを形成し、且つ、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が活性領域1aを複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極31A、31Bを形成する工程と、半導体基板1の上面側からイオン注入を行った後、熱処理することにより、活性領域1a内において、埋め込みゲート電極31A、31Bを挟んでゲートトレンチ13の両側に位置するようにソース・ドレイン拡散層15、45を形成する工程と、を具備し方法を採用している。このような方法及び条件によって埋め込みゲート電極31A、31Bを形成することにより、電極の埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができる。従って、セル容量への書き込み・読み出しに十分な電流駆動能力が確保され、素子特性に優れたDRAM(半導体装置)10を製造することが可能となる。

【0082】

[その他の半導体装置及びその製造方法の例]

本発明の技術範囲は上記実施の形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。例えば、上述した実施形態においては、本発明をDRAMに適用した例について説明したが、本発明はこれに限定されるものではなく、種々の半導体装置に適用することができる。

【0083】

具体的には、図40に示すような、ロジックICで使用されるMOSFETを製造するにあたって本発明を適用することも可能であり、以下、このような場合の例について、主に図27〜図41を参照しながら説明する。なお、以下の説明において、上記実施形態の半導体装置であるDRAMと同一の構成部分については、その詳細な説明を省略する。

【0084】

図27は、本発明を適用して製造可能な半導体装置であるロジックICのN型MOS領域を示す平面図である。以下の説明においては、図27中に示すような、埋め込みゲート電極パターン102に垂直なトランジスタの断面を、D−D’線で表して説明する。

【0085】

まず、従来公知の方法でSTIによる素子分離を行い、活性領域101を形成する。

次に、図28に示すように、通常のウェットエッチング法により、p型のシリコンからなる半導体基板111の表面を露出した状態とし、熱酸化によって、膜厚が10nm程度の酸化膜112を成長させる。次いで、5.0×1015/cm2のヒ素を10keVでイオン注入し,続いて、1.0×1013/cm2の濃度のリンを30keVでイオン注入した後、不活性ガス雰囲気中で950℃10秒の熱処理を行い、LDD(Lightly Doped Drain)拡散層115と高濃度ソース・ドレイン拡散層117を形成する。

【0086】

次に、図29に示すように、通常のウェットエッチングにより、酸化膜112を除去する。

次に、スパッタ法を用いてコバルトを15nmの膜厚で堆積させた後、不活性ガス雰囲気中において、650℃で30秒の熱処理を行うことにより、基板表面にコバルトシリサイドを形成する。次いで、図29に示すように、塩酸と過酸化水素水の混合液によって未反応のコバルトを除去し、コバルトシリサイド層119を形成する。

【0087】

次に、図30に示すように、プラズマCVD法を用いて、膜厚が150nm程度のシリコン窒化膜121を堆積した後、通常のリソグラフィ技術を用いて、トレンチゲート形成のためのフォトレジストパターン123を形成する。

次に、図31に示すように、フォトレジストパターン123をマスクとして、通常の異方性ドライエッチングによってシリコン窒化膜121とシリサイド層119をエッチングし、フォトレジストパターン123を除去する。

次に、図31に示すように、LP−CVD法を用いて、膜厚が10nmのシリコン窒化膜を堆積した後、エッチバックを行うことにより、シリコン窒化膜サイドウォール125を形成する。

【0088】

次に、図32に示すように、異方性ドライエッチングにより、ゲート電極を埋め込むためのトレンチ125を形成する。

次に、図33に示すように、通常の熱酸化により、トレンチ125内に厚さ1.5nm程度のゲート酸化膜131を形成する。

次に、図34に示すように、CVD法を用いて、膜厚が3.0nm程度のハフニウムシリケート膜133を堆積させる。

【0089】

次に、図35に示すように、5nmのTiNと80nmのWの、TiN/Wの積層膜からなるゲート電極材料135を堆積した後、シリコン基板表面から90nmの位置までエッチバックする。

次に、図36に示すように、リフロースパッタ法を用いて、膜厚が100nm程度のアルミニウム137を堆積させる。

次に、図37に示すように、通常のドライエッチングにより、アルミニウム137をシリコン基板表面から70nmの位置までエッチバックすることで、埋め込みゲート電極138を形成する。

【0090】

次に、図38に示すように、HDP(High Density Plasma)−CVD法を用いて、膜厚が400nm程度の酸化膜を堆積させ、CMP(Chemical Mechanical Polish)法を用いて研磨することにより、層間絶縁膜141を形成する。

次に、図39に示すように、通常のリソグラフィ及びドライエッチング技術を用いてコンタクトホールを形成した後、CVD法によってコンタクトホールにタングステンを埋め込むことにより、コンタクトプラグ143を形成する。

上記手順により、ロジックICを構成するMOSFET120を製造することができる。

【0091】

なお、上記手順で製造したMOSFET120の上に、上記した実施形態のDRAM10と同様に、さらに、ロジックICを構成する各層を形成することにより、本発明が適用され、素子特性に優れたロジックICを得ることが可能である。

【0092】

上記手順及び条件によって製造されたトランジスタ(MOSFET120)と、従来の構成とされたトランジスタの、ドレイン電流のゲート電圧依存性について、図40のグラフに示す。ここで、本例で述べる従来のトランジスタとは、ゲート長が上述した実施形態のDRAMに備えられる埋め込みゲート電極の幅と同じ長さで製造された、通常のプレーナ型のn型MOSトランジスタである。

【0093】

本例の手順及び条件によって製造されたトランジスタのゲート電極は、アルミニウム(仕事関数(4.1eV)と、TiN/W(仕事関数4.6〜4.7eV)とからなる積層構造とされている。さらに,ロジックICとして使用される半導体装置は、リーク電流よりも電流駆動能力がより重要な特性となるため、本例においては、埋め込みゲート電極138の上面が、ソース・ドレイン拡散層115とp型シリコンの接合よりも30nmほど高い位置まで突き出るように制御している。また、埋め込みゲート電極138の上面の突き出る高さは、30nmに限るものではなく、例えば、10nm〜50nmの範囲であれば良い。

【0094】

通常、ゲート電圧が負の側に大きくなると高い電界が発生し、バンド間トンネリングによるリーク電流が発生するが、図40のグラフに示すように、本発明を適用することにより、リーク電流が抑制されることがわかる。また、トレンチゲート型のデバイスであることから、実効チャネル長が従来よりも長くなり、DIBL(Drain Induced Barrier Lowering)によるSCE(Short Channel Effect)も抑制され、サブスレッショルド係数が改善されていることが明らかである。

【0095】

また、通常の高誘電率ゲート絶縁膜を用いたメタルゲートデバイスの製造プロセスにおいては、メタルゲートをソース・ドレイン活性化のための高温熱処理から避ける場合には、所謂ゲートラストプロセスが用いられる。しかしながら、ゲートラストプロセスは、一旦、ポリシリコン等で仮のゲート電極を形成した後、ソース・ドレイン拡散層の形成後に仮のゲート電極を除去し、メタルゲート電極を形成する方法であるため、工程増となる。

これに対し、本発明を半導体装置に適用した場合には、ソース・ドレイン拡散層の形成をメタルゲートの形成以前に行うことができるため、仮のゲートを形成するプロセスを省略することが可能となり、製造効率が向上しし、また、製造コストの低減が可能となる。

【0096】

なお、上述した実施形態に記載された構成を、本例に記載された好ましい範囲の構成とすることにより、本発明をロジック用半導体装置に適用することが可能である。また、これとは逆に、本例に記載された構成を、上述した実施形態に記載された好ましい範囲の構成とすることにより、DRAM用半導体装置に適用することが可能である。

【符号の説明】

【0097】

1…シリコン基板(半導体基板)、

1a…活性領域、

4…素子分離領域、

2…埋め込みゲート型MOSトランジスタ(埋め込みゲート型トランジスタ)

120…MOSFET(埋め込みゲート型トランジスタ)、

13、125…ゲートトレンチ、

15…ソース・ドレイン拡散層(ビット線側)

45…ソース・ドレイン拡散層(容量側)

31A…埋め込みゲート電極(ワード線)、

31B、138…埋め込みゲート電極(素子分離)、

31a…上部電極、

31b…下部電極、

51…ビット線、

58…容量コンタクトプラグ、

8…キャパシタ構造、

86…第1電極、

87…容量絶縁膜、

88…第2電極、

9…配線層、

90…上部金属配線(配線層)、

91…保護膜(配線層)、

10…DRAM(半導体装置)

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、例えば、DRAM(Dynamic Random Access Memory)素子等の半導体装置の分野においては、半導体装置が使用される機器の高機能化等により、さらなる高集積化が進められている。

また、このような、半導体装置に備えられるトランジスタの微細化に伴い、ショートチャネル効果によるトランジスタ特性の悪化や、コンタクトホール径の縮小によるコンタクト抵抗の増加が問題となっている。

【0003】

これらの問題を解決し、さらに微細化を進めるため、埋め込みゲート型のトランジスタが提案されている。このような埋め込みゲート型トランジスタは、高集積化に適しているため、例えば、DRAMのセルトランジスタとしての利用も検討されている(例えば、特許文献1、非特許文献1を参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−180150号公報

【非特許文献】

【0005】

【非特許文献1】T. Schloesser,et.al,「インターナショナル・エレクトロン・デバイス・ミーティング(International Electron Devices Meeting)」,P809〜812,2008.,

【発明の概要】

【発明が解決しようとする課題】

【0006】

以下、従来の構成の埋め込みゲート型のセルトランジスタを備えるDRAM(半導体装置)について、図41〜図46を参照しながら説明する。

図41に示す例のように、DRAMに備えられる埋め込みゲート型のセルトランジスタは、n型のトランジスタとして構成され、ライン状にパターニングされた活性領域201と、同様にライン状の埋め込みゲート電極パターン202が形成されている。隣接するトランジスタとの素子分離は、STI(Shallow Trench Isolation)構造を用いるのが一般的であるが、図41に示す半導体装置では、縦方向の素子間はSTI領域204によって分離され、横方向に隣接する素子間は埋め込みゲート電極によって分離される。ここで、トランジスタの埋め込みゲート電極パターン202と素子分離用の埋め込みゲート電極パターン203は、同時形成が可能であることから公知のダブルパターニング技術が適用でき、さらなる微細化に好適な構造であることが知られている。

【0007】

図42に、図41に示すA−Aの位置に対応したトランジスタの断面図を示す。図42に示すように、TiN/W積層膜で構成されるゲート電極253、254、及び、隣接セルトランジスタとの分離用ゲート電極255は、p型シリコン基板の表面よりも深い位置に埋め込まれた構造とされている。また、詳細な図示を省略するが、容量コンタクトプラグ258は、DRAMの容量(キャパシタ)に、ビット線側コンタクトプラグ259はビット線に接続されている。

【0008】

上述のように、高集積化が求められるDRAMのセルトランジスタではあるが、高集積化と同時に、セル容量への電荷の書き込み・読み出しに十分な電流駆動能力を確保することも必要となる。さらに、セル容量に書き込まれた電荷を保持するために、接合リーク電流を低く抑えることも必要となる.

【0009】

図43に、セル容量に電荷を保持している状態のトランジスタの模式図を示す。図43に示すように、トランジスタはセル容量に電荷を蓄えているため、容量側のpn接合は、容量側空乏層端265から基板側空乏層端269までの範囲で空乏化する。ここで、トランジスタのリーク電流は、容量側pn接合の空乏層中における生成電流が主な成分であり、これは、接合電界によって生じるTAT(Trap Assisted Tunneling)によって大きく加速される。このため、DRAMセルトランジスタにおいては、容量側の接合電界を低く抑えることが重要となり、容量側のn型拡散層の濃度は薄く設計されている。従って、容量側とビット線側では、ソース・ドレイン拡散層のpn接合の深さが異なった構造とされている。

【0010】

図44(a)、(b)を用いて、セル容量に電荷が保持されている状態におけるトランジスタ中の電界分布を模式的に説明する。ここで、ゲート電極の埋め込みが深い構造における電界分布を図44(a)に、ゲート電極の埋め込みが浅い構造における電界分布を図44(b)に示す。図44(a)、(b)の各々の不純物濃度プロファイルは同じであるが、図44(b)に示すようにゲート電極の埋め込みが浅くなると、容量側pn接合の空乏層中に発生する電界が強くなり、その勾配も急峻になることが判る。このため、ゲート電極の埋め込みが浅くなると接合リークが増加し、DRAMのリフレッシュ特性が低下する。従って、埋め込みゲート型トランジスタをDRAMのセルトランジスタに適用する場合には、ゲート電極の埋め込みを、接合電界が十分緩和できる深さに設計する必要がある。

【0011】

しかしながら、ゲート電極の埋め込みを深くした場合、容量側n型拡散層とゲート電極の距離が大きくなり過ぎ、濃度が薄く設計されている容量側n型拡散層の抵抗が増加する。このため、図45のグラフに示すように、ゲート電極の埋め込みが浅い場合(図44(b))に対して、ゲートの埋め込みが深い場合(図44(a))は、電流駆動能力が大きく減少してしまう。特に、図41に示すように、活性領域パターン201の方向に隣接するDRAMセルとの素子分離をトランジスタで行う構造においては、素子分離用トランジスタのゲート電位の影響により、さらにソース・ドレイン拡散層の抵抗が増加して電流が低下する。

【0012】

図46(a)、(b)の断面模式図に、トランジスタがオン状態の電流密度分布を示す。図46(a)は、素子分離用ゲート電極に0Vの電圧が印加された状態を示し、図46(b)は、−0.5Vの電圧が印加された状態を示している。通常、素子分離用トランジスタのゲート電極には、トランジスタをオフするため、図46(b)に示すような負電位が印加される。この際、図46(a)に示すような正電位の場合と比較して、図46(b)に示すような負電位が印加された場合には、素子分離用ゲート電極近傍の電子密度が低下し、これによって電流密度も低下してしまう。

【0013】

上述のように、従来の半導体装置においては、埋め込みゲート型トランジスタをDRAMのセルトランジスタとして使用する場合、接合リークを低減するためにゲート電極の埋め込みを深くすると、電流駆動能力も低下してしまうという問題があった。

【課題を解決するための手段】

【0014】

本発明の半導体装置は、半導体基板に形成された複数の埋め込みゲート型トランジスタを有する半導体装置であり、前記半導体基板には、STI(Shallow Trench Isolation)構造を有する素子分離領域と、該素子分離領域に囲まれた活性領域とが形成されており、前記半導体基板に形成されるゲートトレンチと、前記ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、前記活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極と、前記半導体基板の上面側に設けられ、前記活性領域内において、前記埋め込みゲート電極を挟むように前記ゲートトレンチの両側に位置するソース・ドレイン拡散層と、が備えられており、前記埋め込みゲート電極が、それぞれ仕事関数が異なるゲート材料からなる上部電極と下部電極とが積層された構造とされており、且つ、前記半導体基板の上面側の前記ソース・ドレイン拡散層側に配置される前記上部電極が、前記下部電極に比べて、仕事関数の低いゲート材料から構成されることを特徴とする。

【0015】

係る構成の半導体装置によれば、半導体基板のゲートトレンチ内に設けられる埋め込みゲート電極を上部電極と下部電極とから構成し、ソース・ドレイン拡散層側に配置される上部電極を、下部電極をなすゲート材料よりも仕事関数が低いゲート材料から構成することにより、埋め込みゲート電極を深い位置に形成した場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができる。

【0016】

本発明の半導体装置の製造方法は、上記構成の半導体装置を製造する方法であり、半導体基板に、STI(Shallow Trench Isolation)構造を有する素子分離領域を形成することにより、該素子分離領域に囲まれた活性領域を形成する工程と、前記半導体基板の表面をエッチングすることによってゲートトレンチを形成する工程と、前記ゲートトレンチの底部にゲート材料を堆積させることによって下部電極を形成した後、さらに、前記下部電極の上にゲート材料を堆積させることによって上部電極を形成し、且つ、前記下部電極と前記上部電極を、それぞれ仕事関数が異なるゲート材料から形成するとともに、前記上部電極を、前記下部電極に比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が前記活性領域を複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極を形成する工程と、前記半導体基板の上面側からイオン注入を行った後、熱処理することにより、前記活性領域内において、前記埋め込みゲート電極を挟んで前記ゲートトレンチの両側に位置するようにソース・ドレイン拡散層を形成する工程と、を備えることを特徴とする。

【0017】

係る構成の半導体装置の製造方法によれば、上記した構成を有し、接合リーク電流を抑制しながら、電極近傍の電流密度を確保できる半導体装置を製造することが可能となる。

【発明の効果】

【0018】

本発明の半導体装置によれば、上記構成を採用することにより、接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力が確保されたものとなるので、素子特性に優れた半導体装置が得られる。

また、本発明の半導体装置の製造方法によれば、上記した方法を採用することにより、接合リーク電流が低減されるとともに、高い電流駆動能力を備える半導体装置を製造することが可能となる。

【図面の簡単な説明】

【0019】

【図1】本発明を適用した一実施形態である半導体装置を示す模式断面図である。

【図2】本発明を適用した一実施形態である半導体装置を示す模式平面図である。

【図3】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図4】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図5】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図6】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図7】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図8】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図9】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図10】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図11】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図12】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図13】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図14】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図15】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図16】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図17】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図18】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図19】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図20】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図21】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図22】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図23】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図24】本発明を適用した一実施形態である半導体装置の製造方法を説明するための模式工程図であり、図2中に示すB−B’線に沿った断面図である。

【図25】本発明を適用した一実施形態である半導体装置を説明するための模式図であり、図2中に示すA−A’線に沿った断面図で、(a)トランジスタの電荷保持状態の電解分布を示す図、(b)トランジスタがオン状態の電流密度分布を示す図である。

【図26】本発明を適用した一実施形態である半導体装置を説明するための模式図であり、(a)接合電界のゲート埋め込み深さ依存性を示すグラフ、(b)オン電流のゲート埋め込み深さ依存性を示すグラフである。

【図27】本発明を適用した他の例である半導体装置を説明するための模式平面図である。

【図28】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図29】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図30】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図31】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図32】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図33】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図34】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図35】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図36】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図37】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図38】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図39】本発明を適用した他の例である半導体装置の製造方法を説明するための模式工程図であり、図27中に示すC−C’線に沿った断面図である。

【図40】本発明を適用した他の例である半導体装置を説明するための模式図であり、トランジスタのドレイン電流のゲート電圧依存性を示すグラフである。

【図41】従来の半導体装置を説明するための模式平面図である。

【図42】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図である。

【図43】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図である。

【図44】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図で、(a)ゲート電極の埋め込みが深い場合の電界分布を示す図、(b)ゲート電極の埋め込みが浅い場合の電界分布を示す図である。

【図45】従来の半導体装置の製造方法を説明するための模式図であり、ゲート電極の埋め込みが深い場合と浅い場合の電流駆動能力の差を示すグラフである。

【図46】従来の半導体装置の製造方法を説明するための模式図であり、図42中に示すD−D’線に沿った断面図で、(a)素子分離用のゲート電極に0Vの電圧を印加した際の電流密度分布を示す図、(b)、素子分離用のゲート電極に−0.5Vの電圧を印加した際の電流密度分布を示す図である。

【発明を実施するための形態】

【0020】

以下に、本発明を適用した一実施形態である半導体装置及びその製造方法について、図面を適宜参照しながら説明する。本実施形態においては、半導体装置の一例として、n型MOS−FET構造で構成されるメモリセルトランジスタを備えたDRAM(Dynamic Random Access Memory)に、本発明を適用した場合を例に挙げて説明する。なお、以下の説明において参照する図面は、本実施形態の半導体装置の製造方法を説明する図面であって、図示される各部の大きさや厚さや寸法等は、実際の半導体装置等の寸法関係とは異なっていることがある。また、以下の説明において例示する材料や寸法等は一例であり、本発明はそれらに必ずしも限定されるものではなく、その要旨を変更しない範囲で適宜変更して実施することが可能である。

【0021】

[半導体装置]

まず、本発明を適用した一実施形態である半導体装置を適用して得られるDRAM(半導体装置)の構成について説明する。

図1は本発明を適用した半導体装置の一実施形態であるDRAM10のメモリセル領域の一部を示す模式断面図であり、図2は模式平面図である。以下の説明においては、図2中に示す、活性領域1aのパターンに平行な埋め込みゲート型MOSトランジスタ(埋め込みゲート型トランジスタ:図1中の符号2を参照)のB−B’線(又はA−A’線)に沿った断面図を適宜参照しながら説明を行う。

【0022】

図2に示すように、DRAM10のメモリセル領域には、素子分離溝からなる素子分離領域4に囲まれて区画された活性領域1aが、所定方向に所定間隔で複数形成されている。また、活性領域1aを縦断するように、ワード線となる埋め込みゲート電極31A(31)及び素子分離用の埋め込みゲート電極31B(31)が、所定方向(図2中における縦長方向)に所定の間隔で埋め込み形成されている。さらに、図2中においては図示を省略するが、埋め込みゲート電極31A、31Bと直交する方向(図2中における横幅方向)に、図1中に示すビット線51が所定の間隔で複数配置されている。そして、埋め込みゲート電極31Aと活性領域1aとが交差する領域にそれぞれメモリセルが形成されている。

【0023】

本実施形態で説明するDRAM10は、より具体的には、半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には、STI構造を有する素子分離領域4と、素子分離領域4に囲まれた活性領域1aとが形成されており、半導体基板1に形成されるゲートトレンチ13と、該ゲートトレンチ13の内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域1aを複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31(31A、31B)と、半導体基板1の上面側に設けられ、活性領域1a内において、埋め込みゲート電極31A、31Bを挟むようにゲートトレンチ13の両側に位置するソース・ドレイン拡散層15、45と、が備えられている。そして、DRAM10は、埋め込みゲート電極31A、31Bが、それぞれ仕事関数が異なるゲート材料からなる上部電極31aと下部電極31bとが積層された構造とされており、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる構成を採用している。

【0024】

ここで、埋め込みゲート電極(ワード線)31A及び埋め込みゲート電極(素子分離)31Bは、同一の構造を有しているが、機能が異なっている。ここで、埋め込みゲート電極31Aがメモリセルのゲート電極として用いられるのに対して、素子分離用の埋め込みゲート電極31Bは、所定の電位をかけて隣接するトランジスタ間を分離するために設けられている。すなわち、同一の活性領域1a上で隣接するトランジスタ間は、素子分離用の埋め込みゲート電極31Bを所定の電位に維持することで、寄生トランジスタをオフ状態として分離する。

【0025】

また、メモリセル領域全体には、複数のメモリセルが形成されており、個々のメモリセルには、それぞれキャパシタ素子(図1を参照)が設けられている。また、それらキャパシタが接続される容量コンタクトパッド82は、図1に示すように、それぞれが重ならないように、メモリセル領域内に所定の間隔で配置されている。

なお、本実施形態で説明するDRAM10は、図1に示すように、6F2セル配置(Fは最小加工寸法)とされている。

【0026】

次に、DRAM10を構成するメモリセルについて詳しく説明する。

図1に示すように、DRAM10を構成するメモリセルは、ワード線が半導体基板内に完全に埋め込まれた埋め込みゲート型トランジスタ、キャパシタ、配線層が形成された積層構造体である。

【0027】

埋め込みゲート型MOSトランジスタ2は、上記したように、表層がシリコンからなる半導体基板1と、半導体基板1に形成された埋め込み絶縁膜からなる素子分離膜(素子分離領域4)と、素子分離領域4によって区画形成された活性領域1aと、ゲートトレンチ13の内部にゲート絶縁膜25を介して埋め込み形成され、上部電極31a及び下部電極31bからなる積層構造とされた埋め込みゲート電極31A、31Bと、半導体基板1の表面を覆うとともに、ゲートトレンチ13の内部で埋め込みゲート電極31A、31Bの上面を保護する第1層間絶縁膜43と、該第1層間絶縁膜43を介して上方に形成されるビット線51と、から概略構成されている。

また、上記構成の埋め込みゲート型MOSトランジスタ2は、半導体基板1における、埋め込みゲート電極31A、31Bの幅方向両側の活性領域1aにイオンを注入することによって形成される、ソース・ドレイン拡散層15、45を備えている。そして、ソース・ドレイン拡散層15が容量コンタクトプラグ58を介してキャパシタ構造8に接続されているとともに、ソース・ドレイン拡散層45とビット線51とが接続されている。

【0028】

また、上記したように、埋め込みゲート電極31A、31Bは、ともに、上部電極31a及び下部電極31bからなる積層構造とされており、上部電極31a及び下部電極31bは、それぞれ仕事関数が異なるゲート材料から構成されている。さらに、埋め込みゲート電極31A、31Bは、上部電極31aが、下部電極31bに比べて仕事関数の低いゲート材料から構成されている。

【0029】

本発明においては、埋め込みゲート電極31A、31Bを構成する上部電極31a及び下部電極31bの各々の仕事関数を上記関係に規定することにより、ゲート電極の埋め込みを深くした場合であっても、特に、素子分離用の埋め込みゲート電極31Bの近傍における電流密度が低下することなく、十分な電流駆動能力を確保することが可能となる。これは、半導体基板1の上面側に配されるソース・ドレイン拡散層15、45の近傍に、仕事関数が低いゲート材料からなる上部電極31aを配置することにより、n型不純物濃度が薄く設計されている容量側のソース・ドレイン拡散層15の抵抗が抑制され、埋め込みゲート電極31A、31B近傍の電流密度が確保されるためである。

【0030】

ここで、素子分離として設けられる埋め込みゲート電極31Bは、通常、トランジスタをオフにするための負電位が印加されるが、従来の構成のゲート電極を用いた場合には、電極近傍の電子密度が低下することで電流密度も低下し、十分な電流駆動能力が得られ難いという問題がある。本発明では、埋め込みゲート電極31B(31A)を上記構成の積層構造とすることにより、埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができ、十分な電流駆動能力が得られるという効果が得られる。

【0031】

埋め込みゲート電極31A、31Bは、上部電極31aが、仕事関数が4.1〜4.4eVの範囲であるゲート材料からなり、また、下部電極31bが、仕事関数が4.4eV超5.3eV以下の範囲であるゲート材料からなることが好ましい。上部電極31a及び下部電極31bの仕事関数を、上記範囲の関係とすることにより、上記効果がより顕著に得られる。

【0032】

また、本実施形態では、上部電極31aと下部電極31bの仕事関数の関係を上記範囲とするにあたり、そのゲート材料は特に限定されない。しかしながら、本実施形態においては、例えば、上部電極31aに、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかを用いたうえで、下部電極31bに、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかをゲート材料として用いることができる。また、本実施形態では、これらのゲート材料を用いたうえで、上部電極31aを構成するゲート材料が、下部電極31bを構成するゲート材料よりも仕事関数が低い組み合わせで構成することで、上記効果がより顕著に得られる。

より具体的には、上部電極31a/下部電極31bの組み合わせを、例えば、N+ポリシリコン/メタル(TiNとWの積層膜)、Al/メタル(TiNとWの積層膜)、導電性カーボン/N+ポリシリコン、導電性カーボン/(TiNとWの積層膜)等の組み合わせとすることができる。

【0033】

なお、本発明においては、素子分離として設けられる埋め込みゲート電極31Bのみならず、ワード線として設けられる埋め込みゲート電極31Aについても、上記した積層構造として構成しているが、これには限定されない。本実施形態では、工程上、埋め込みゲート電極31A、31Bを同時に形成することが可能であることから、これら各ゲート電極を同じ構成としているが、本発明においては、少なくとも素子分離用の埋め込みゲート電極31Bが上記条件の積層構造とされていれば、上記効果が十分に得られる。

例えば、詳細を後述する埋め込みゲート電極を形成する工程において、埋め込みゲート電極31Aと埋め込みゲート電極31Bを別工程として形成する場合には、素子分離用の埋め込みゲート電極31Bのみを上記構成とし、ワード線として設けられる埋め込みゲート電極を従来の構成とすることも可能である。

【0034】

また、本実施形態で説明する埋め込みゲート型MOSトランジスタ2は、詳細な図示を省略するが、素子分離として設けられる埋め込みゲート電極31Bの底面の一部が、当該埋め込みゲート電極31Bの長手方向に配置された隣接する素子分離膜の間に埋め込む構成となっている。これにより、素子分離膜と、埋め込みゲート電極31Bの埋め込まれた底面の一部の側面部分との間には、半導体基板1の一部である、図示略の薄膜状シリコン部がサイドウォール形状に設けられる。

【0035】

ここで、埋め込みゲート電極(ワード線)31A及び埋め込みゲート電極(素子分離)31Bは同じ構造を有していることから、埋め込みゲート電極31Aの底面の一部においても同様の薄膜状シリコン部が設けられる。この薄膜状シリコン部は、ソース領域とドレイン領域との電位差が閾値を超えた際に、チャネルとして機能させることができる。このように、本実施形態の埋め込みゲート型MOSトランジスタ2は、薄膜状シリコン部のようなチャネル領域を有するリセスチャネル型トランジスタとして構成される。

【0036】

埋め込みゲート型MOSトランジスタ2の上方には、層間絶縁膜55等を介してキャパシタ構造8が設けられている。具体的には、層間絶縁膜55上には、埋め込みゲート型MOSトランジスタ2のソース・ドレイン拡散層15と容量コンタクトプラグ58を介して接続される容量コンタクトパッド82が設けられている。そして、この容量コンタクトパッド82上に、ストッパー膜83及び第3層間絶縁膜84を貫通するように設けられた第1電極86、容量絶縁膜87及び第2電極88から構成されるキャパシタ構造8が形成されている。

【0037】

なお、本実施形態のキャパシタ構造8は、下部側の第1電極86の内壁のみを電極として利用するシリンダー型を一例として記載しているが、これに限定されるものではない。例えば、第1電極の内壁及び外壁を電極として利用するクラウン型キャパシタに変更することも可能である。

【0038】

配線層は、上記構成のキャパシタ構造8上に第4層間絶縁膜89を介して設けられており、上部金属配線90及び保護膜91から構成されている。本実施形態では、配線層が1層配線構造の場合を一例として記載しているが、これに限定されるものではない。例えば、複数の配線層及び層間絶縁膜から構成される多層配線構造に変更することも可能である。

【0039】

上述したような本発明に係る半導体素子であるDRAM10によれば、半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には、STI構造を有する素子分離領域4と、素子分離領域4に囲まれた活性領域1aとが形成されており、半導体基板1に形成されるゲートトレンチ13と、該ゲートトレンチ13の内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域1aを複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、半導体基板1の上面側に設けられ、活性領域1a内において、埋め込みゲート電極31を挟むようにゲートトレンチ13の両側に位置するソース・ドレイン拡散層15、45と、埋め込みゲート電極31A、31Bが、それぞれ仕事関数が異なるゲート材料からなる上部電極31aと下部電極31bとが積層された構造とされている。そして、DRAM10によれば、さらに、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる構成を採用している。即ち、DRAM10は、上述のような積層構造とされた埋め込みゲート電極31A、31Bを備えた構成なので、接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力が確保されたものとなり、優れた素子特性が得られる。

【0040】

[半導体装置の製造方法]

続いて、上記構成を有するDRAM(半導体装置)10の製造方法について、図3〜図24を参照しながら説明する。ここで、図3〜図24は、本実施形態のDRAMの製造方法を説明するための図であり、各図における断面は、それぞれ、図2中に示すA−A’線に沿った断面か、あるいは、B−B’線に沿った断面をそれぞれ示している。

【0041】

本実施形態のDRAM(半導体装置)10の製造方法は、半導体基板1に、STI構造を有する素子分離領域4を形成することにより、素子分離領域4に囲まれた活性領域1aを形成する工程と、半導体基板1の表面をエッチングすることによってゲートトレンチ13を形成する工程と、ゲートトレンチ13の底部にゲート材料を堆積させることによって下部電極31bを形成した後、さらに、下部電極31bの上にゲート材料を堆積させることによって上部電極31aを形成し、且つ、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が活性領域1aを複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極31A、31Bを形成する工程と、半導体基板1の上面側からイオン注入を行った後、熱処理することにより、活性領域1a内において、埋め込みゲート電極31A、31Bを挟んでゲートトレンチ13の両側に位置するようにソース・ドレイン拡散層15、45を形成する工程と、を具備して概略構成されている。

以下に、各工程について、詳細に説明する。

【0042】

まず、シリコンからなる半導体基板1の表面に、通常の方法で、活性領域1aを分離するための素子分離領域4(図2を参照)を形成する。素子分離領域4の形成は、詳細な図示を省略するが、まず、例えばP型のシリコン基板(半導体基板1)上に、シリコン酸化膜(SiO2)とマスク用のシリコン窒化膜(Si3N4)とを順次堆積する。次に、フォトリソグラフィ技術およびドライエッチング技術を用いて、これらシリコン窒化膜、シリコン窒化膜、及び、半導体基板1のパターニングを順次行ない、半導体基板1に活性領域1aを区画するための素子分離溝(トレンチ)を形成する。また、半導体基板1の活性領域1aとなるシリコン表面は、マスク用のシリコン窒化膜で覆われている。この際、STI構造に埋め込まれる絶縁膜としては、例えば、HDP−CVDによる酸化膜、又は、SOD(Spin On Dielectric)等の塗布材料を用いることができる。そして、例えば、ウェットエッチング等の方法によって、マスク用のシリコン窒化膜およびシリコン酸化膜を除去する。このようにして、素子分離領域を構成するSTI(Shallow Trench Isolation)素子分離膜を形成することで素子分離領域4を形成することにより、半導体基板1に活性領域1aを区画形成する。

【0043】

次に、図3に示すように、素子分離溝内に露出する半導体基板1の表面にシリコン酸化膜12を形成する。

具体的には、素子分離溝内の半導体基板1の表面とともに、半導体基板1の活性領域1aを被覆する図示略のシリコン窒化膜及びシリコン窒化膜の表面に、通常の熱酸化により、シリコン酸化膜12を、例えば、10nm程度の膜厚で形成する。

【0044】

次に、半導体基板1の表面に不純物を拡散させることにより、容量側のソース・ドレイン拡散層15を形成する。

具体的には、まず、図4に示すように、シリコン酸化膜12をマスクとして、半導体基板1の活性領域1aに、例えば、リン等のn型不純物を、1.0×1013/cm2程度の濃度で、20keVの加速エネルギーでイオン注入する。そして、窒素雰囲気中で980℃・10秒の熱処理を行うことにより、n型不純物が拡散されたソース・ドレイン拡散層40を形成する.このソース・ドレイン拡散層15は、埋め込みゲート型MOSトランジスタ2のソース・ドレイン領域の一部として機能する。

【0045】

次に、図5に示すように、LP−CVDを用いて窒化シリコン材料を堆積させることにより、シリコン窒化膜17を、例えば150nm程度の膜厚で形成する。

次に、図6に示すように、通常の液浸露光技術及び材料を用い、幅40nmのレジストパターン21を、90nmピッチで形成する。

【0046】

次に、図7に示すように、周知のドライエッチング技術を用いて、シリコン窒化膜17を異方性エッチングした後、レジストパターン21を除去し、異方性エッチングによってシリコン酸化膜12を除去する。

【0047】

次に、図7に示すように、CF4とArの混合ガスにH2を添加したガスを用いる異方性ドライエッチングにより、半導体基板1のシリコン酸化膜12及びシリコン窒化膜15から露出する位置をエッチングすることにより、ゲートトレンチ13を形成する。この際、ゲートトレンチ13の深さとしては、例えば、140nm程度とする。このゲートトレンチ13は、活性領域1aと交差する所定の方向(例えば、図1中の縦長方向)に延在するライン状のパターンとして形成される。

【0048】

また、詳細な図示を省略するが、ゲートトレンチ13を形成する際に、素子分離膜の表面の高さが、半導体基板1の表面の高さよりも低くなるように、素子分離膜の部分を深くエッチングする。また、ゲートトレンチ13の深さは、素子分離膜と同等か、もしくは、素子分離膜の方が深い構造となるようにする。

【0049】

次に、図8に示すように、ゲートトレンチ13の内面を覆うように、ゲート酸化膜25を、例えば、4nm程度の膜厚で形成する。この際、ゲート酸化膜25としては、例えば、ゲートトレンチ13の内面表層を、ISSG(in−situ steam generation)によって熱酸化することによって形成することができる。

【0050】

次に、ゲートトレンチ13の内部のゲート酸化膜25上にゲート材料を順次堆積させることにより、これらの材料をゲートトレンチ13内に埋め込み、上部電極31a及び下部電極31bからなる埋め込みゲート電極31A、31Bを形成する。

具体的には、図9に示すように、まず、ゲートトレンチ13の内部に、例えば、窒化チタン(TiN)を下層側とて堆積させ、その上にタングステン(W)を堆積させることにより、TiN/Wの積層膜を形成する。この際、各積層膜の膜厚としては、例えば、TiNを5nm程度、Wを80nm程度とすることができる。なお、図9に示す例では、詳細な図示を省略するが、上層側として堆積させるWを、半導体基板1の表面を覆うまで堆積させている。

【0051】

次いで、図10に示すように、TiN/Wの積層膜の一部を、通常のドライエッチング等の方法でエッチバックして除去することにより、下部電極31bを、ゲートトレンチ13の底部に残存した状態で形成する。この際、シリコン窒化膜17をマスクとして、例えば、TiN/Wの積層膜を、半導体基板1の表面、即ち、ゲートトレンチ13の入口から、90nm程度の位置までエッチバックする。

【0052】

次いで、図11に示すように、ゲートトレンチ13の底部に形成した下部電極31bの上に、リンを1×1020/cm3〜1×1022/cm3の濃度、より好ましくは1×1020/cm3でドープしたポリシリコン材料を、例えば、80nmの膜厚で堆積させる。この際、ゲートトレンチ13内に先に埋め込まれた、下部電極31bの上層側のW膜とポリシリコンとの界面がシリサイド化されるが、過度のシリサイド化を抑制するため、ポリシリコン材料の堆積前に、バリア膜及び低抵抗シリサイド膜を形成する構成とすることも可能である。また、ポリシリコン材料を、520℃程度の成膜温度でアモルファス状態として堆積させ、後の熱処理によって結晶化することでシリコン結晶粒を大きくする条件とした場合には、低抵抗化の効果が得られる。

【0053】

そして、シリコン窒化膜17をマスクとして、通常のドライエッチング技術を用いて、ポリシリコンを半導体基板1の表面から、例えば、70nmの位置までエッチバックすることにより、下部電極31bの上に、n型ポリシリコンからなる上部電極31aを形成する。

以上のような手順により、ゲートトレンチ13の内部に、上部電極31a及び下部電極31bの積層構造からなる、埋め込みゲート電極31A、31Bを形成する。

【0054】

本発明においては、埋め込みゲート電極31A、31Bを形成するにあたり、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成する。これにより、上述したように、電極の埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができ、十分な電流駆動能力が得られるという効果が得られる。特に、素子分離として設けられる埋め込みゲート電極31Bを上記方法で形成することにより、電極近傍の電流密度が低下すること無く、十分な電流駆動能力が得られるものとなる。

【0055】

また、上述したように、埋め込みゲート電極31A、31Bを形成する工程においては、上部電極31aとして、仕事関数が4.1〜4.4eVの範囲であるゲート材料を用いるとともに、下部電極31bとして、仕事関数が4.4eV超5.3eV以下の範囲であるゲート材料を用いることが、上記効果が顕著に得られる点からより好ましい。

【0056】

また、上述のような仕事関数の条件を満足できるゲート材料としては、例えば、下部電極31bを、窒化チタン(TiN)/タングステン(W)積層膜、導電性カーボンの何れかを用いて形成したうえで、上部電極31aを、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかを用いて形成することができる。また、これらのゲート材料を用いたうえで、上部電極31aの形成に用いるゲート材料を、下部電極31bの形成に用いるゲート材料よりも仕事関数が低い組み合わせとすることにより、上記効果がより顕著に得られる。

【0057】

次に、図12に示すように、埋め込みゲート電極31A、31Bの上、即ち、上部電極31aの表面に、プラズマ酸化膜を、例えば、140nm程度の膜厚で堆積させた後、シリコン窒化膜17をマスクとして、CMPによってプラズマ酸化膜を研磨除去する。このような手順により、埋め込みゲート電極31A、31Bの上に、第1層間絶縁膜43を形成する。

【0058】

次に、図13に示すように、従来公知のリソグラフィ及びドライエッチング技術を用いてシリコン窒化膜17を選択的に除去することにより、ビット線と接続するためのコンタクトホール46を形成する。

ここで、コンタクトホール46は、例えば、図2に示すように、ワード線として設けられる埋め込みゲート電極31Aと同一の方向(図2中における縦長方向)に延在するライン状の開口パターンとして形成する。また、コンタクトホール46の開口パターンと活性領域1aとが交差する部分では、コンタクトホール46から半導体基板1のシリコン表面が露出する。

【0059】

次に、図14に示すように、半導体基板1の表面にリン等のn型の不純物を注入することにより、ビット線側のソース・ドレイン拡散層45を形成する。

具体的には、コンタクトホール46から露出した半導体基板1の表面に、2.0×1015/cm2の濃度のリンを、5keVの加速エネルギーでイオン注入した後、950℃で10秒の熱処理を行うことにより、ビット線側のソース・ドレイン拡散層45を形成する。この際、第1層間絶縁膜43をマスクとして、コンタクトホール46から露出する半導体基板1の表面に不純物(リン)をイオン注入することで、ソース・ドレイン拡散層45を形成する。このソース・ドレイン拡散層は、トランジスタのソース・ドレイン領域の一方として機能する、ビット線側のソース・ドレイン拡散層45となる。

【0060】

次に、図15に示すように、ビット線51を形成する。この際、まず、半導体基板1の表面及び第1層間絶縁膜43の表面を覆うように、例えば、N型の不純物であるリンを1×1020/cm3程度の濃度でドープした膜厚が80nm程度のポリシリコン47を形成する。この際、コンタクトホール46内に、ポリシリコン47を確実に埋め込むように形成する。

次いで、このポリシリコン47の上に、例えば、膜厚が5nm程度の窒化タングステン(WN)と、膜厚70nm程度のタングステン(W)膜とを順次堆積させることにより、W/WN膜49を形成する。

【0061】

次いで、図15に示すように、従来公知のリソグラフィ及びドライエッチング技術を用い、W/WN膜49およびポリシリコン47からなる積層膜をライン形状にパターニングすることにより、ビット線51を形成する(図1も参照)。

【0062】

このビット線51は、コンタクトホール46内において、ビット線側のソース・ドレイン拡散層45と接続される。即ち、ビット線51を構成するポリシリコン47と、コンタクトホール46から露出している半導体基板1の表面部分に形成されたソース・ドレイン拡散層45とが接続される。このように、本実施形態のビット線51は、埋め込みゲート型MOSトランジスタ2のソース・ドレイン領域の一方であるとともに、素子分離として設けられるソース・ドレイン拡散層45と接続するコンタクトプラグの機能を兼ねるものである。本実施形態の製造方法では、このようなコンタクトプラグの機能を兼ねるビット線51を、上記工程により、一回のリソグラフィ工程で形成(一括形成)することが可能である。

【0063】

また、ビット線51は、埋め込みゲート電極31A、31Bと交差する方向(図2中における横幅方向)に延在するパターンとして形成される。なお、ビット線51は、埋め込みゲート電極31A、31Bと直交する直線形状とすることができるが、これに限定されるものではなく、例えば、一部を湾曲させた形状として配置してもよい。

【0064】

次に、図16に示すように、例えば、LP−CVD法を用いて、半導体基板1の表面及び第1層間絶縁膜43の表面、並びに、ビット線51を覆うように窒化シリコン(Si3N4)を堆積させることにより、膜厚が10nm程度のシリコン窒化膜53を形成する。

【0065】

次に、容量コンタクトプラグ58を形成する。容量コンタクトプラグ58の形成にあたっては、まず、先ず、図17に示すように、後工程で形成する配線層との間に配される第2層間絶縁膜55を形成する。

具体的には、例えば、CVD法を用いて、シリコン窒化膜53上を覆うように、B(ボロン)及びP(リン)を含有するSiO2膜、即ち、BPSG(Boron Phosphor Silicate Glass)膜を400nm程度の膜厚で堆積させる。そして、750℃で30分程度のリフロー処理を行うことにより、第2層間絶縁膜55を形成する。

【0066】

次に、図18に示すように、従来公知のリソグラフィ技術を用いて、容量側コンタクトホールパターン57を形成し、これをマスクとして、通常の異方性ドライエッチングによって第2層間絶縁膜55をエッチングすることにより、容量コンタクトホール57Aを形成する。

【0067】

具体的には、まず、第2層間絶縁膜55上に、例えば、埋め込みゲート電極31A、31Bと同一の方向(図2中における縦長方向)に延在するライン状の開口パターンを有するように、容量側コンタクトホールパターン57を形成する。

次に、この容量側コンタクトホールパターン57から露出する第2層間絶縁膜55、シリコン窒化膜53及びシリコン窒化膜17を順次エッチングして除去することにより、容量コンタクトホール57Aを形成する。

ここで、図18に示すように、容量コンタクトホール57Aと活性領域1a(図2を参照)とが重なる部分では、容量コンタクトホール57Aから半導体基板1のシリコン表面が露出する。

【0068】

次に、第2層間絶縁膜55上に、容量コンタクトホール57A内を埋め込むように、LP−CVD法を用いて、リンを1×1020/cm3の濃度でドープしたポリシリコンを、厚さ80nm程度で堆積させる。次いで、図19に示すように、CMP法によってポリシリコンを研磨除去することにより、容量コンタクトホール57A内を充填するように、容量コンタクトプラグ58を形成する。

【0069】

以上のような手順で形成した埋め込みゲート型MOSトランジスタ2は、従来のような、埋め込みゲート電極がTiN/W積層膜のみのトランジスタと同様、チャネルポテンシャルの制御をTiN/W積層膜のゲートで行うため、従来と同等のサブスレッショルド特性としきい値電圧を得ることが可能となる

【0070】

ここで、本実施形態で説明する方法によって製造されたトランジスタ(埋め込みゲート型MOSトランジスタ2)の電荷保持状態の電界分布を、図25(a)の模式図に示す。図25(a)中に示すように、N+ポリシリコンの仕事関数は、Ti/W積層膜よりも低いことから、容量側のソース・ドレイン拡散層からシリコンの半導体基板に向かうポテンシャル変化が従来に比べて緩やかになり、容量側の接合電界が大きく緩和される。これにより、従来の構成とされたトランジスタに比べ、接合リーク電流を低く抑えることが可能となる。

【0071】

また、図25(b)の模式図に、本実施形態で説明する方法によって製造されたトランジスタがオン状態である場合の電流密度分布を示す。図25(b)中に示すように、N+ポリシリコンの仕事関数は、Ti/W積層膜よりも低いことから、N+ポリシリコンをソース・ドレイン拡散層側に配置することにより、低濃度に設計された容量側ソース・ドレイン拡散層中の電子密度の低下が、従来に比べて抑制されている。従って、容量側ソース・ドレイン拡散層中の電流密度も増加し、効果的にオン電流を増加させることが可能となる。

【0072】

本実施形態においては、オン電流を確保しながら接合電界を緩和するため、埋め込みゲート電極31Bの上面が、容量側のソース・ドレイン拡散層15の接合位置61と同じ深さになるように制御している。また、埋め込みゲート電極31Bの上面と容量側のソース・ドレイン拡散層15の接合位置61との関係は、同じ深さに限定するものではなく、例えば、10nm程度のオーバーラップ、又は、10nm程度のオフセットを有する範囲であれば良い。

【0073】

ここで、図26(a)、(b)のグラフに、接合電界及びオン電流のゲート埋め込み深さ依存性を、各々示す。図26(a)、(b)において、グラフの横軸は、シリコンの半導体基板表面から埋め込みゲート電極上端までの距離である。本実施形態で説明する例では、容量側のソース・ドレイン拡散層の接合位置61が70nmに制御されていることから、埋め込みゲート電極の上端の距離が70nmよりも浅ければ、容量側のソース・ドレイン拡散層とオーバーラップした構造となり、埋め込みゲート電極の上端の距離が70nmよりも深ければ、容量側のソース・ドレイン拡散層とオフセットした構造となる。図26(a)、(b)におけるグラフの縦軸は、一般的なDRAM製品の規格を満たす数値で規格化されている。即ち、図26(a)、(b)のグラフにおいては、電界は1.0以下、オン電流は1.0以上で製品規格を満足する。従来の方法で得られる、従来の構成のトランジスタの場合、ゲートの埋め込み深さを72nmから76nmの範囲で管理する必要があるが、本発明により、ゲートの埋め込み深さを60nmから84nmの範囲とした場合でも製品動作が可能となる。

【0074】

なお、本発明においては、埋め込みゲート電極の埋め込み深さは、製品が動作する範囲内で任意の値を採用することが可能である。例えば、埋め込みゲート電極の埋め込み深さを60nmとすれば、従来と同等の接合電界を維持しながら、オン電流が増加する。従って、従来と同等のリフレッシュ特性を維持しながら、高速動作が可能となる。

同様に、ゲートの埋め込み深さを84nmとすれば、従来と同等のオン電流を維持しながら、接合電界を緩和できる。従って、従来と同等の動作速度を維持しながら、リフレッシュ周期を長くすることで、消費電力を低下させることが可能となる。

【0075】

そして、本発明においては、上記構成の埋め込みゲート型MOSトランジスタ2上に、さらに、キャパシタ構造8並びに配線層を形成することにより、DRAM構造を有する半導体装置(DRAM10)を製造することができる。

【0076】

まず、キャパシタ構造8を形成する。キャパシタ構造8の形成にあたっては、まず、容量コンタクトプラグ58を形成した後の基板の表面に、窒化タングステン(WN)及びタングステン(W)を順次堆積して積層膜を形成する。次に、この積層膜をパターニングして、図20に示すような容量コンタクトパッド82を形成する。ここで、メモリセル領域においては、容量コンタクトパッド82を均等な間隔で形成する必要がある。このため、図20に示すように、容量コンタクトパッド82は、容量コンタクトプラグ58の直上からずらした位置に形成されるが、容量コンタクトパッド82の底面と容量コンタクトプラグ58の上面とが重なる部分で容量コンタクトパッド82が接続される。

【0077】

次に、図21に示すように、基板上に、容量コンタクトパッド82を覆うように、例えば、シリコン窒化膜等を用いてストッパー膜83を形成する。次に、このストッパー膜83の上に、例えばシリコン酸化膜等を用いて第3層間絶縁膜84を形成する。

【0078】

次に、図22に示すように、第3層間絶縁膜84と容量コンタクトパッド82上のストッパー膜83とを貫通するコンタクトホール85を形成して、容量コンタクトパッド82の上面の一部を露出させる。次に、コンタクトホール85の内壁面と、露出する容量コンタクトパッド82の上面とを覆うようにして、例えば、窒化チタン等を用いてキャパシタ構造8の第1電極86を形成する。これにより、第1電極86の底面は、容量コンタクトパッド82の上面と接続される。

【0079】

次に、図23に示すように、第3層間絶縁膜84の上に、第1電極86の表面を覆うようにして容量絶縁膜87を形成する。容量絶縁膜87としては、例えば、酸化ジルコニウム(ZrO2)、酸化アルミニウム(Al2O3)、酸化ハフニウム(HfO2)及びこれらの積層膜を用いることができる。次に、容量絶縁膜87の表面を覆うように、例えば、窒化チタン等を用いてキャパシタ構造8の第2電極88を形成する。このようにして、キャパシタ構造8を形成する。

【0080】

次に、キャパシタ構造8を介して、半導体基板1上に配線層9を形成する。配線層9の形成にあたっては、まず、図24に示すように、第2電極88の上に、この第2電極88を覆うようにして、例えば、シリコン酸化膜等からなる第4層間絶縁膜89を形成する。次に、第4層間絶縁膜89の上に、例えばアルミニウム(Al)や銅(Cu)等で上部金属配線90を形成する。その後、上部金属配線90を覆うように保護膜91を形成することにより、DRAMのメモリセルが完成する。

上記各工程により、本実施形態のDRAM10を製造することができる。

【0081】

以上説明したように、本発明に係る半導体素子であるDRAM10の製造方法によれば、半導体基板1に、STI構造を有する素子分離領域4を形成することにより、素子分離領域4に囲まれた活性領域1aを形成する工程と、半導体基板1の表面をエッチングすることによってゲートトレンチ13を形成する工程と、ゲートトレンチ13の底部にゲート材料を堆積させることによって下部電極31bを形成した後、さらに、下部電極31bの上にゲート材料を堆積させることによって上部電極31aを形成し、且つ、下部電極31bと上部電極31aを、それぞれ仕事関数が異なるゲート材料から形成するとともに、上部電極31aを、下部電極31bに比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部が活性領域1aを複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極31A、31Bを形成する工程と、半導体基板1の上面側からイオン注入を行った後、熱処理することにより、活性領域1a内において、埋め込みゲート電極31A、31Bを挟んでゲートトレンチ13の両側に位置するようにソース・ドレイン拡散層15、45を形成する工程と、を具備し方法を採用している。このような方法及び条件によって埋め込みゲート電極31A、31Bを形成することにより、電極の埋め込みを深くした場合であっても、接合リーク電流を抑制しながら、電極近傍の電流密度を確保することができる。従って、セル容量への書き込み・読み出しに十分な電流駆動能力が確保され、素子特性に優れたDRAM(半導体装置)10を製造することが可能となる。

【0082】

[その他の半導体装置及びその製造方法の例]

本発明の技術範囲は上記実施の形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。例えば、上述した実施形態においては、本発明をDRAMに適用した例について説明したが、本発明はこれに限定されるものではなく、種々の半導体装置に適用することができる。

【0083】

具体的には、図40に示すような、ロジックICで使用されるMOSFETを製造するにあたって本発明を適用することも可能であり、以下、このような場合の例について、主に図27〜図41を参照しながら説明する。なお、以下の説明において、上記実施形態の半導体装置であるDRAMと同一の構成部分については、その詳細な説明を省略する。

【0084】

図27は、本発明を適用して製造可能な半導体装置であるロジックICのN型MOS領域を示す平面図である。以下の説明においては、図27中に示すような、埋め込みゲート電極パターン102に垂直なトランジスタの断面を、D−D’線で表して説明する。

【0085】

まず、従来公知の方法でSTIによる素子分離を行い、活性領域101を形成する。

次に、図28に示すように、通常のウェットエッチング法により、p型のシリコンからなる半導体基板111の表面を露出した状態とし、熱酸化によって、膜厚が10nm程度の酸化膜112を成長させる。次いで、5.0×1015/cm2のヒ素を10keVでイオン注入し,続いて、1.0×1013/cm2の濃度のリンを30keVでイオン注入した後、不活性ガス雰囲気中で950℃10秒の熱処理を行い、LDD(Lightly Doped Drain)拡散層115と高濃度ソース・ドレイン拡散層117を形成する。

【0086】

次に、図29に示すように、通常のウェットエッチングにより、酸化膜112を除去する。

次に、スパッタ法を用いてコバルトを15nmの膜厚で堆積させた後、不活性ガス雰囲気中において、650℃で30秒の熱処理を行うことにより、基板表面にコバルトシリサイドを形成する。次いで、図29に示すように、塩酸と過酸化水素水の混合液によって未反応のコバルトを除去し、コバルトシリサイド層119を形成する。

【0087】

次に、図30に示すように、プラズマCVD法を用いて、膜厚が150nm程度のシリコン窒化膜121を堆積した後、通常のリソグラフィ技術を用いて、トレンチゲート形成のためのフォトレジストパターン123を形成する。

次に、図31に示すように、フォトレジストパターン123をマスクとして、通常の異方性ドライエッチングによってシリコン窒化膜121とシリサイド層119をエッチングし、フォトレジストパターン123を除去する。

次に、図31に示すように、LP−CVD法を用いて、膜厚が10nmのシリコン窒化膜を堆積した後、エッチバックを行うことにより、シリコン窒化膜サイドウォール125を形成する。

【0088】

次に、図32に示すように、異方性ドライエッチングにより、ゲート電極を埋め込むためのトレンチ125を形成する。

次に、図33に示すように、通常の熱酸化により、トレンチ125内に厚さ1.5nm程度のゲート酸化膜131を形成する。

次に、図34に示すように、CVD法を用いて、膜厚が3.0nm程度のハフニウムシリケート膜133を堆積させる。

【0089】

次に、図35に示すように、5nmのTiNと80nmのWの、TiN/Wの積層膜からなるゲート電極材料135を堆積した後、シリコン基板表面から90nmの位置までエッチバックする。

次に、図36に示すように、リフロースパッタ法を用いて、膜厚が100nm程度のアルミニウム137を堆積させる。

次に、図37に示すように、通常のドライエッチングにより、アルミニウム137をシリコン基板表面から70nmの位置までエッチバックすることで、埋め込みゲート電極138を形成する。

【0090】

次に、図38に示すように、HDP(High Density Plasma)−CVD法を用いて、膜厚が400nm程度の酸化膜を堆積させ、CMP(Chemical Mechanical Polish)法を用いて研磨することにより、層間絶縁膜141を形成する。

次に、図39に示すように、通常のリソグラフィ及びドライエッチング技術を用いてコンタクトホールを形成した後、CVD法によってコンタクトホールにタングステンを埋め込むことにより、コンタクトプラグ143を形成する。

上記手順により、ロジックICを構成するMOSFET120を製造することができる。

【0091】

なお、上記手順で製造したMOSFET120の上に、上記した実施形態のDRAM10と同様に、さらに、ロジックICを構成する各層を形成することにより、本発明が適用され、素子特性に優れたロジックICを得ることが可能である。

【0092】

上記手順及び条件によって製造されたトランジスタ(MOSFET120)と、従来の構成とされたトランジスタの、ドレイン電流のゲート電圧依存性について、図40のグラフに示す。ここで、本例で述べる従来のトランジスタとは、ゲート長が上述した実施形態のDRAMに備えられる埋め込みゲート電極の幅と同じ長さで製造された、通常のプレーナ型のn型MOSトランジスタである。

【0093】

本例の手順及び条件によって製造されたトランジスタのゲート電極は、アルミニウム(仕事関数(4.1eV)と、TiN/W(仕事関数4.6〜4.7eV)とからなる積層構造とされている。さらに,ロジックICとして使用される半導体装置は、リーク電流よりも電流駆動能力がより重要な特性となるため、本例においては、埋め込みゲート電極138の上面が、ソース・ドレイン拡散層115とp型シリコンの接合よりも30nmほど高い位置まで突き出るように制御している。また、埋め込みゲート電極138の上面の突き出る高さは、30nmに限るものではなく、例えば、10nm〜50nmの範囲であれば良い。

【0094】

通常、ゲート電圧が負の側に大きくなると高い電界が発生し、バンド間トンネリングによるリーク電流が発生するが、図40のグラフに示すように、本発明を適用することにより、リーク電流が抑制されることがわかる。また、トレンチゲート型のデバイスであることから、実効チャネル長が従来よりも長くなり、DIBL(Drain Induced Barrier Lowering)によるSCE(Short Channel Effect)も抑制され、サブスレッショルド係数が改善されていることが明らかである。

【0095】

また、通常の高誘電率ゲート絶縁膜を用いたメタルゲートデバイスの製造プロセスにおいては、メタルゲートをソース・ドレイン活性化のための高温熱処理から避ける場合には、所謂ゲートラストプロセスが用いられる。しかしながら、ゲートラストプロセスは、一旦、ポリシリコン等で仮のゲート電極を形成した後、ソース・ドレイン拡散層の形成後に仮のゲート電極を除去し、メタルゲート電極を形成する方法であるため、工程増となる。

これに対し、本発明を半導体装置に適用した場合には、ソース・ドレイン拡散層の形成をメタルゲートの形成以前に行うことができるため、仮のゲートを形成するプロセスを省略することが可能となり、製造効率が向上しし、また、製造コストの低減が可能となる。

【0096】

なお、上述した実施形態に記載された構成を、本例に記載された好ましい範囲の構成とすることにより、本発明をロジック用半導体装置に適用することが可能である。また、これとは逆に、本例に記載された構成を、上述した実施形態に記載された好ましい範囲の構成とすることにより、DRAM用半導体装置に適用することが可能である。

【符号の説明】

【0097】

1…シリコン基板(半導体基板)、

1a…活性領域、

4…素子分離領域、

2…埋め込みゲート型MOSトランジスタ(埋め込みゲート型トランジスタ)

120…MOSFET(埋め込みゲート型トランジスタ)、

13、125…ゲートトレンチ、

15…ソース・ドレイン拡散層(ビット線側)

45…ソース・ドレイン拡散層(容量側)

31A…埋め込みゲート電極(ワード線)、

31B、138…埋め込みゲート電極(素子分離)、

31a…上部電極、

31b…下部電極、

51…ビット線、

58…容量コンタクトプラグ、

8…キャパシタ構造、

86…第1電極、

87…容量絶縁膜、

88…第2電極、

9…配線層、

90…上部金属配線(配線層)、

91…保護膜(配線層)、

10…DRAM(半導体装置)

【特許請求の範囲】

【請求項1】

半導体基板に形成された複数の埋め込みゲート型トランジスタを有する半導体装置であって、

前記半導体基板には、STI(Shallow Trench Isolation)構造を有する素子分離領域と、該素子分離領域に囲まれた活性領域とが形成されており、

前記半導体基板に形成されるゲートトレンチと、

前記ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、前記活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極と、

前記半導体基板の上面側に設けられ、前記活性領域内において、前記埋め込みゲート電極を挟むように前記ゲートトレンチの両側に位置するソース・ドレイン拡散層と、が備えられており、

前記埋め込みゲート電極が、それぞれ仕事関数が異なるゲート材料からなる上部電極と下部電極とが積層された構造とされており、且つ、前記半導体基板の上面側の前記ソース・ドレイン拡散層側に配置される前記上部電極が、前記下部電極に比べて、仕事関数の低いゲート材料から構成されることを特徴とする半導体装置。

【請求項2】

前記埋め込みゲート電極は、前記上部電極の仕事関数が4.1〜4.4eVの範囲であり、前記下部電極の仕事関数が4.4eV超5.3eV以下の範囲であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記埋め込みゲート電極は、前記上部電極をなすゲート材料が、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかであり、前記下部電極をなすゲート材料が、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかであり、且つ、前記上部電極を構成するゲート材料が、前記下部電極を構成するゲート材料よりも仕事関数が低い組み合わせで構成されることを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

さらに、前記ソース・ドレイン拡散層に、容量コンタクトプラグを介してキャパシタ構造が接続されているとともに、前記ソース・ドレイン拡散層にビット線が接続されていることを特徴とする請求項1〜請求項3の何れか1項に記載の半導体装置。

【請求項5】

請求項1〜請求項4の何れかに記載の半導体装置を製造する方法であって、

半導体基板に、STI(Shallow Trench Isolation)構造を有する素子分離領域を形成することにより、該素子分離領域に囲まれた活性領域を形成する工程と、

前記半導体基板の表面をエッチングすることによってゲートトレンチを形成する工程と、

前記ゲートトレンチの底部にゲート材料を堆積させることによって下部電極を形成した後、さらに、前記下部電極の上にゲート材料を堆積させることによって上部電極を形成し、且つ、前記下部電極と前記上部電極を、それぞれ仕事関数が異なるゲート材料から形成するとともに、前記上部電極を、前記下部電極に比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部前記活性領域を複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極を形成する工程と、

前記半導体基板の上面側からイオン注入を行った後、熱処理することにより、前記活性領域内において、前記埋め込みゲート電極を挟んで前記ゲートトレンチの両側に位置するようにソース・ドレイン拡散層を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項6】

前記埋め込みゲート電極を形成する工程は、前記上部電極として、仕事関数が4.1〜4.2eVの範囲であるゲート材料を用いるとともに、前記下部電極として、仕事関数が4.5〜4.6eVの範囲であるゲート材料を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記埋め込みゲート電極を形成する工程は、前記上部電極を、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかのゲート材料を用いて形成し、前記下部電極を、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかのゲート材料を用いて形成し、且つ、前記上部電極の形成に用いるゲート材料を、前記下部電極の形成に用いるゲート材料よりも仕事関数が低い材料で組み合わせることを特徴とする請求項5又は請求項6に記載の半導体装置の製造方法。

【請求項8】

さらに、前記ソース・ドレイン拡散層に、容量コンタクトプラグを介して接続するキャパシタ構造を形成する工程と、

前記ソース・ドレイン拡散層に接続するビット線を形成する工程を備えることを特徴とする請求項5〜請求項7の何れか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板に形成された複数の埋め込みゲート型トランジスタを有する半導体装置であって、

前記半導体基板には、STI(Shallow Trench Isolation)構造を有する素子分離領域と、該素子分離領域に囲まれた活性領域とが形成されており、

前記半導体基板に形成されるゲートトレンチと、

前記ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、前記活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極と、

前記半導体基板の上面側に設けられ、前記活性領域内において、前記埋め込みゲート電極を挟むように前記ゲートトレンチの両側に位置するソース・ドレイン拡散層と、が備えられており、

前記埋め込みゲート電極が、それぞれ仕事関数が異なるゲート材料からなる上部電極と下部電極とが積層された構造とされており、且つ、前記半導体基板の上面側の前記ソース・ドレイン拡散層側に配置される前記上部電極が、前記下部電極に比べて、仕事関数の低いゲート材料から構成されることを特徴とする半導体装置。

【請求項2】

前記埋め込みゲート電極は、前記上部電極の仕事関数が4.1〜4.4eVの範囲であり、前記下部電極の仕事関数が4.4eV超5.3eV以下の範囲であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記埋め込みゲート電極は、前記上部電極をなすゲート材料が、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかであり、前記下部電極をなすゲート材料が、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかであり、且つ、前記上部電極を構成するゲート材料が、前記下部電極を構成するゲート材料よりも仕事関数が低い組み合わせで構成されることを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

さらに、前記ソース・ドレイン拡散層に、容量コンタクトプラグを介してキャパシタ構造が接続されているとともに、前記ソース・ドレイン拡散層にビット線が接続されていることを特徴とする請求項1〜請求項3の何れか1項に記載の半導体装置。

【請求項5】

請求項1〜請求項4の何れかに記載の半導体装置を製造する方法であって、

半導体基板に、STI(Shallow Trench Isolation)構造を有する素子分離領域を形成することにより、該素子分離領域に囲まれた活性領域を形成する工程と、

前記半導体基板の表面をエッチングすることによってゲートトレンチを形成する工程と、

前記ゲートトレンチの底部にゲート材料を堆積させることによって下部電極を形成した後、さらに、前記下部電極の上にゲート材料を堆積させることによって上部電極を形成し、且つ、前記下部電極と前記上部電極を、それぞれ仕事関数が異なるゲート材料から形成するとともに、前記上部電極を、前記下部電極に比べて仕事関数の低いゲート材料を用いて形成することにより、少なくとも一部がワード線として設けられるとともに、その他の残部前記活性領域を複数の素子領域に分離する素子分離として設けられる、積層構造の埋め込みゲート電極を形成する工程と、

前記半導体基板の上面側からイオン注入を行った後、熱処理することにより、前記活性領域内において、前記埋め込みゲート電極を挟んで前記ゲートトレンチの両側に位置するようにソース・ドレイン拡散層を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項6】

前記埋め込みゲート電極を形成する工程は、前記上部電極として、仕事関数が4.1〜4.2eVの範囲であるゲート材料を用いるとともに、前記下部電極として、仕事関数が4.5〜4.6eVの範囲であるゲート材料を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記埋め込みゲート電極を形成する工程は、前記上部電極を、N+ポリシリコン(Si)、アルミニウム(Al)、導電性カーボンの何れかのゲート材料を用いて形成し、前記下部電極を、窒化チタン(TiN)/タングステン(W)積層膜、N+ポリシリコンの何れかのゲート材料を用いて形成し、且つ、前記上部電極の形成に用いるゲート材料を、前記下部電極の形成に用いるゲート材料よりも仕事関数が低い材料で組み合わせることを特徴とする請求項5又は請求項6に記載の半導体装置の製造方法。

【請求項8】

さらに、前記ソース・ドレイン拡散層に、容量コンタクトプラグを介して接続するキャパシタ構造を形成する工程と、

前記ソース・ドレイン拡散層に接続するビット線を形成する工程を備えることを特徴とする請求項5〜請求項7の何れか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【公開番号】特開2011−192800(P2011−192800A)

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願番号】特願2010−57812(P2010−57812)

【出願日】平成22年3月15日(2010.3.15)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願日】平成22年3月15日(2010.3.15)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]