半導体装置及びその製造方法

【課題】半導体装置におけるワイヤ接続不良の抑制化を図る。

【解決手段】主面3aの外周部に並んで配置された複数のボンディングリード3hを有するパッケージ基板3と、パッケージ基板3の主面3aのボンディングリード列の内側に搭載された半導体チップ1と、半導体チップ1のパッド1cと基板のボンディングリード3hとを接続するワイヤ4と、半導体チップ1及び複数のワイヤ4を樹脂封止する封止体と、パッケージ基板3の裏面に設けられた複数の半田バンプとを有している。さらに、ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置されていることにより、ボンディングリード3hと半導体チップ1のパッド1cとの接続においてワイヤ長を長くすることができ、その結果、ワイヤ4のループ形状の安定化を図ってワイヤ接続不良の抑制化を図る。

【解決手段】主面3aの外周部に並んで配置された複数のボンディングリード3hを有するパッケージ基板3と、パッケージ基板3の主面3aのボンディングリード列の内側に搭載された半導体チップ1と、半導体チップ1のパッド1cと基板のボンディングリード3hとを接続するワイヤ4と、半導体チップ1及び複数のワイヤ4を樹脂封止する封止体と、パッケージ基板3の裏面に設けられた複数の半田バンプとを有している。さらに、ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置されていることにより、ボンディングリード3hと半導体チップ1のパッド1cとの接続においてワイヤ長を長くすることができ、その結果、ワイヤ4のループ形状の安定化を図ってワイヤ接続不良の抑制化を図る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体製造技術に関し、特に、ワイヤボンディングにおける接続不良の抑制化に適用して有効な技術に関する。

【背景技術】

【0002】

第1ボンディング点にネック部分を形成後、第1所定量の長さのワイヤを繰り出しながらキャピラリを上昇させ、第2ボンディング点に向かう方向に移動させて第1癖付け部分を形成する。キャピラリを下降させ、第2ボンディング点と反対側に向かう方向に移動させて第2癖付け部分を形成する。キャピラリを上昇させて第1癖付け部分がキャピラリ先端に位置するまでワイヤを繰り出し、その状態でキャピラリを第2ボンディング点まで移動させワイヤループを形成する技術がある(例えば、特許文献1参照)。

【0003】

第1ボンディング点にワイヤを接続する工程と、キャピラリを少し上昇させ、第1のリバース動作を行う工程と、キャピラリを上昇させ、第2のリバース動作を行う工程と、キャピラリを上昇させ、第3のリバース動作を行う工程とを行う。さらに、クランパが閉じ、キャピラリを第2ボンディング点の反対の方向に水平移動させる工程と、クランパが開き、キャピラリを第2ボンディング点の方向に水平移動させる工程と、キャピラリを第1ボンディング点の上方まで上昇させてワイヤを繰り出し、第2ボンディング点に接続する工程とを行う技術がある(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−87747号公報(図2)

【特許文献2】特開2004−319921号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0005】

小型化の要求に応えた半導体装置の一例として、チップサイズと半導体パッケージ(配線基板)のサイズがほぼ同じであるCSP(Chip Size Package)と呼ばれる半導体装置が知られている。

【0006】

前記CSPは、半導体チップの端部(端辺)と配線基板の端部(端辺)との距離が約0.2〜0.3mmと狭い(短い)ため、配線基板の主面に形成されたワイヤ接続するためのボンディングリード(端子)と半導体チップの端部(端辺)との距離も約0.1mmと非常に狭い(短い)。そのため、ワイヤボンディング工程において、半導体チップの電極と接続する点を1st側、配線基板の主面に形成されたボンディングリードと接続する点を2nd側とする所謂正ボンディング方式によりワイヤ接続を行うと、ワイヤがキャピラリとチップ端の間に入らないという現象が起こる。

【0007】

これを詳細に説明すると、図27の比較例に示すように、1st側から2nd側に打ち下ろしたワイヤ4にキャピラリ18の一部が接触する。そこで、キャピラリ18の根元から先端まで補足加工した部分(L)を長くすれば、ワイヤ4との干渉は抑制できるが、ワイヤボンディング工程では超音波を併用したネイルヘッドボンディング方式により行うため、細いL寸法分が長すぎると、細い部分でキャピラリ18が撓むため、超音波がキャピラリ18の先端に伝わり難くなる。

【0008】

また、正ボンディングの場合、2nd側のワイヤ4を圧着する際、ワイヤ4が2nd側よりも高い位置から引き出されているために、図27に示すようにA部において、キャピラリ18の一部とワイヤ4との間で摩擦が生じ易く、キャピラリ18の一部が磨耗し易い。

【0009】

そこで、前記特許文献1(特開2004−87747号公報)や前記特許文献2(特開2004−319921号公報)に記載されているように、配線基板の主面に形成されたボンディングリードと接続する点を1st(第1ボンド)側、半導体チップの電極と接続する点を2nd(第2ボンド)側とする所謂逆ボンディング方式によりワイヤ接続を行えば、ワイヤ断線不良を抑制することができる。すなわち、ワイヤは低い位置にある1st側から高い位置にある2nd側へとほぼ同じ高さまで垂直方向に引き上げられ、その後、水平方向にキャピラリを移動させて高い位置にある2nd側に接続するため、1st側におけるワイヤの根元が折れ曲がることはなく、その結果、ワイヤ断線不良を抑制することができる。

【0010】

しかしながら、上記したように半導体装置の小型化に伴い、配線基板の主面に形成されたボンディングリードと半導体チップの端部(端辺)との距離も約0.1mmと非常に狭いため、逆ボンディング方式によりワイヤ接続を行うと、最終的にワイヤを2nd側に倒したときに、ワイヤの引き回しのマージンが足りないため、図28の比較例の小型パッケージ30に示すように、ワイヤ4がチップ端部に接触するという現象が起こる。

【0011】

言い換えると、スプールからのワイヤ送り速度とキャピラリ18の動く速度が対応しておらず、ワイヤ4の送り速度よりもキャピラリ18の動きの方が速いため、ワイヤ供給力が少なくなり、形成されたワイヤ4が短く安定しないことから、チップ端部にショートしてワイヤ接続不良を引き起こすという問題が発生する。特に、半導体チップ1の主面1aの端部にテストパターンが形成されている場合があり、この場合、テストパターンとワイヤ4とがショートすることも問題となる。

【0012】

本発明の目的は、ワイヤ接続不良の抑制化を図ることができる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0015】

すなわち、本発明は、主面の周縁部に沿って配置された複数の端子を有する配線基板と、配線基板の主面の端子列の内側に搭載された半導体チップと、半導体チップの電極と配線基板の端子とを接続し、配線基板側の端子が第1ボンドとして接続され、半導体チップの電極が第2ボンドとして接続された複数のワイヤとを有し、前記ワイヤの一部が、前記端子におけるワイヤ接続部より前記周縁部側に配置されているものである。

【0016】

また、本発明は、配線基板に半導体チップを接続した後、ワイヤの先端部を配線基板の端子に接続し、その後キャピラリを半導体チップから離れる方向に移動させてワイヤを前記端子から引き出し、さらにキャピラリを半導体チップの電極上に配置した後、前記ワイヤの一部を半導体チップの電極に接続する工程を有し、ワイヤの一部が、配線基板の端子におけるワイヤ接続部より周縁部側に配置されるようにワイヤを接続するものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0018】

ワイヤの一部が、配線基板の端子における第1ボンドのワイヤ接続部より外側に配置されていることにより、ワイヤが外側に遠回りして引き回されるため、配線基板の端子と半導体チップの電極との接続においてワイヤ長を長くすることができる。これにより、ワイヤの引き回しのマージンが増えてキャピラリの動く速度にワイヤ送り速度が追従することが可能になり、ワイヤのループ形状の安定化を図ることができる。その結果、チップ端部とワイヤのショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図2】図1に示す半導体装置の構造の一例を示す断面図である。

【図3】図2に示すA部の構造を示す拡大部分断面図である。

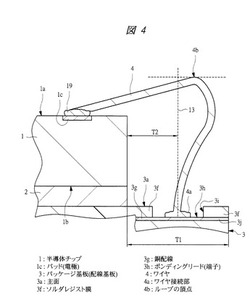

【図4】図3に示すワイヤ接合部の構造の一例を示す拡大部分断面図である。

【図5】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図6】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図7】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図8】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図9】図1に示す半導体装置に組み込まれる配線基板の主面側の配線パターンの一例を示す平面図である。

【図10】図9に示す配線基板の裏面側の配線パターンの一例を示す裏面図である。

【図11】図9に示す配線基板の構造の一例を示す断面図である。

【図12】図11に示すA部の構造を示す拡大部分断面図である。

【図13】図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図である。

【図14】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図である。

【図15】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【図16】本発明の実施の形態1の変形例の配線基板の主面側の配線パターンを示す平面図である。

【図17】図16に示す配線基板の裏面側の配線パターンを示す裏面図である。

【図18】図16に示す配線基板の構造を示す断面図である。

【図19】図18に示すA部の構造を示す拡大部分断面図である。

【図20】本発明の実施の形態1の他の変形例の配線基板の主面側の配線パターンを示す平面図である。

【図21】図20に示す配線基板の構造を示す断面図である。

【図22】図21に示すA部の構造を示す拡大部分断面図である。

【図23】本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図24】図23に示す半導体装置の構造の一例を示す断面図である。

【図25】図24に示すA部の構造を示す拡大部分断面図である。

【図26】図24に示すB部の構造を示す拡大部分断面図である。

【図27】比較例のワイヤボンディング時のキャピラリ押し付け状態の一例を示す拡大部分断面図である。

【図28】比較例のワイヤボンディング後の接続不良の状態を示す断面図である。

【発明を実施するための形態】

【0020】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

【0022】

また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0023】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0024】

(実施の形態1)

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1に示す半導体装置の構造の一例を示す断面図、図3は図2に示すA部の構造を示す拡大部分断面図、図4は図3に示すワイヤ接合部の構造の一例を示す拡大部分断面図、図5〜図8は図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。また、図9は図1に示す半導体装置に組み込まれる配線基板の主面側の配線パターンの一例を示す平面図、図10は図9に示す配線基板の裏面側の配線パターンの一例を示す裏面図、図11は図9に示す配線基板の構造の一例を示す断面図、図12は図11に示すA部の構造を示す拡大部分断面図である。さらに、図13は図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図、図14は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図、図15は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【0025】

また、図16は本発明の実施の形態1の変形例の配線基板の主面側の配線パターンを示す平面図、図17は図16に示す配線基板の裏面側の配線パターンを示す裏面図、図18は図16に示す配線基板の構造を示す断面図、図19は図18に示すA部の構造を示す拡大部分断面図である。さらに、図20は本発明の実施の形態1の他の変形例の配線基板の主面側の配線パターンを示す平面図、図21は図20に示す配線基板の構造を示す断面図、図22は図21に示すA部の構造を示す拡大部分断面図である。

【0026】

本実施の形態1の半導体装置は、配線基板上に半導体チップ1が搭載された樹脂封止型の小型の半導体パッケージであり、本実施の形態1ではその一例として、図1〜図3に示すようなCSP7を取り上げて説明する。

【0027】

なお、CSP7は、配線基板の裏面3bに複数の外部端子である半田バンプ8が格子状に配置されて取り付けられており、したがって、CSP7はBGA(Ball Grid Array)型の半導体パッケージである。

【0028】

図1〜図3を用いてCSP7の構造について説明すると、主面3aと、主面3aに対向する裏面3bと、主面3aの外周部に並んで配置された複数のボンディングリード(端子)3hとを有する配線基板であるパッケージ基板3と、パッケージ基板3の主面3aのボンディングリード列の内側(複数のボンディングリード3hの内側の領域)に搭載され、かつ集積回路を有する半導体チップ1とを備えている。また、半導体チップ1の電極であるパッド1cとパッケージ基板3のボンディングリード3hとを電気的に接続する導電性のワイヤ4と、パッケージ基板3の主面3aと半導体チップ1との間に配置された(予め半導体チップ1の裏面側に貼り付けられた)ダイボンド材であるダイボンド用フィルム2と、パッケージ基板3の裏面3bの複数のランド3dに設けられた複数の外部端子(外部接続用端子)である半田バンプ8とを備えている。さらに、半導体チップ1及び複数のワイヤ4を樹脂封止する封止体6を備えており、パッケージ基板3の主面3aの保護膜であるソルダレジスト膜3f上に、半導体チップ1がダイボンド用フィルム2を介して固定されている。

【0029】

なお、CSP7は、小型の半導体パッケージであるが、半導体チップ1の大きさとパッケージ基板3の大きさがほぼ同じであり、パッケージ基板3の方が僅かに大きい程度である。例えば、図4に示すように、半導体チップ1の端部からパッケージ基板3の端部までの距離(T1)は、約0.2〜0.3mmと非常に狭い(短い)。

【0030】

したがって、パッケージ基板3の主面3aの外周部(周縁部)に形成されたワイヤ接続するためのボンディングリード3hと半導体チップ1の端部(端辺)との距離(T2)も約0.1mm程度と非常に狭い(短い)。

【0031】

そこで、CSP7では、図1及び図3に示すように、パッケージ基板3においてチップ外側の領域で、かつ基板の外周部に複数のボンディングリード3hが並んで配置されており、半導体チップ1の主面1aに設けられた電極であるパッド1cと、これに対応するパッケージ基板3のボンディングリード3hとが金線等の導電性のワイヤ4によって電気的に接続されている。

【0032】

その際、本実施の形態1のCSP7では、図1に示すように、複数のワイヤ4それぞれが、半導体チップ1のパッド1cと、これに対応するパッケージ基板3のボンディングリード3hとを電気的に接続するとともに、基板側のボンディングリード3hが第1ボンドとして接続され、一方、チップ側のパッド1cが第2ボンドとして接続されたものである。

【0033】

ここで、前記第1ボンドは、電気トーチによりワイヤ先端に形成されたボールをキャピラリ18で端子に押し付けて接続するものであり、一方、前記第2ボンドは、第1ボンド後、ワイヤ4を前記端子から引き出してキャピラリ18を他方の端子上に配置し、その後、ワイヤ4の一部を前記他方の端子に対してキャピラリ18で押し潰してこの他方の端子に接続するものである。

【0034】

本実施の形態1のCSP7では、前記第1ボンドがパッケージ基板3のボンディングリード3hに対して行われ、前記第2ボンドが半導体チップ1のパッド1cに対して行われたものである。すなわち、CSP7は、半導体チップ1のパッド1cとパッケージ基板3のボンディングリード3hとの接続において、逆ボンディングによるワイヤボンディングが行われて組み立てられたものである。

【0035】

これは、CSP7は、半導体チップ1とパッケージ基板3の大きさがほぼ同じ小型の半導体パッケージであり、チップの端部から基板の端部までの距離が、約0.2〜0.3mmと非常に狭い構造となっており、さらにボンディングリード3hとチップの端部との距離も約0.1mm程度と非常に狭いため、基板上の半導体チップ1の外側の領域において第2ボンドとしてキャピラリ18を滑らしながら配置することが困難なためである。

【0036】

すなわち、ワイヤ接続時にキャピラリ18をボンディングリード3hから上方に移動させることでワイヤボンディング用に狭い領域しか確保できない基板側を第1ボンドとし、チップ側を第2ボンドとするものである。

【0037】

さらに、本実施の形態1のCSP7では、図1に示すように、パッケージ基板3の主面3a上において、逆ボンディングによって接続されたそれぞれのワイヤ4の一部が、ボンディングリード3hにおける第1ボンドのワイヤ接続部4aより外側に(パッケージ基板3の外周部に向かって)配置(形成)されている。

【0038】

具体的には、図4に示すように、ワイヤ4の一部であるループの頂点4bが第1ボンドのワイヤ接続部4aより外側に配置されている。すなわち、各ワイヤ4のループの最上位地点(ここでは4b)がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側(半導体チップ1から離れる方向)に配置されているものである。

【0039】

ここで、図5〜図8を用いて、図4に示すワイヤ4のループ形状の形成方法について説明すると、まず、パッケージ基板3のボンディングリード3hに第1ボンドを行う。すなわち、ワイヤ4のボール状に形成された先端部を、図4、図5に示すように、キャピラリ18でパッケージ基板3の図4に示すボンディングリード3hに押し付けて接続する。

【0040】

その後、図6に示すように、キャピラリ18を半導体チップ1から離れる方向に移動させてワイヤ4を前記ボンディングリード3hから引き出す。すなわち、キャピラリ18を半導体チップ1から離れる方向で(パッケージ基板3の外周部に向かって)、かつ斜め上方に移動させてワイヤ4を前記ボンディングリード3hから斜め上方に引き出す。

【0041】

その後、キャピラリ18の移動を所定箇所で一旦停止し、続いて図7に示すように、キャピラリ18を真上(垂直上)に移動させてワイヤ4を上方に引き出す。

【0042】

その後、ワイヤ4がチップ高さを超えたところでキャピラリ18の上方への移動を停止し、その後、図8に示すように、キャピラリ18を半導体チップ1のパッド1c上にほぼ水平に移動させて、半導体チップ1のパッド1c上にワイヤ4を配置する。

【0043】

その後、パッド1cにおいてキャピラリ18によりワイヤ4の一部を押し潰して半導体チップ1のパッド1cにワイヤ4を接続する。これにより、ワイヤ4と半導体チップ1のパッド1cとの接続である第2ボンドを完了するとともに、各ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置された状態となる。

【0044】

なお、半導体チップ1のパッド1c上には、予め金バンプ(スタッドバンプ)19が形成されており、第2ボンドの際には、ワイヤ4をパッド1c上の金バンプ19に接続する。これは、ワイヤボンディング工程において、第2ボンドの際には、キャピラリ18を擦り付ける様にワイヤ4をパッド1c(又は、ボンディングリード3h)に圧着するため、キャピラリ18を滑走させる距離だけパッド1cの形状を相対的に大きく形成しておく必要がある。しかしながら、本実施の形態1のように、逆ボンディング方式の場合、半導体チップ1の主面上に形成されたパッド1cを相対的に大きく形成しようとすると、その分半導体チップ1を小型化することが困難となる。更には、半導体チップ1の主面上において上記圧着動作を行うと、圧着圧力により、半導体チップ1に応力が伝わり、特に半導体チップ1の厚さが薄ければチップの抗折強度も低いため、チップクラックを起こす原因となる。そこで、第2ボンドする前に、金バンプ19を形成しておく。金バンプ19はパッド1cに比べ硬度が低いため、微小な圧着圧力でもワイヤ4の一部を容易に圧着することが可能である。更には、第1ボンドする前に金バンプ19を形成しておくことで、第2ボンドする際のボンディングポイントを事前に認識しておくことが可能であるため、ワイヤボンディングの座標が変わらず、安定したワイヤボンディング工程が可能となる。ただし、半導体チップ1の面積が相対的に大きく、半導体チップ1の厚さも厚ければチップの抗折強度も高いため、パッド1c上に金バンプ19は形成されていなくてもよく、その場合は、ワイヤ4を直接パッド1cに接続する。

【0045】

次に、図9〜図12に示すCSP7に組み込まれるパッケージ基板3の構造について説明する。

【0046】

パッケージ基板3は、コア材3cと、その主面3a及び裏面3bに形成された複数の導体部と、主面3aと裏面3bの前記導体部を接続するスルーホール3eと、前記導体部の少なくとも一部を覆うソルダレジスト膜3fとを有している。パッケージ基板3の表面である主面3aには、図9に示すように基板の外周部(周縁部)に複数のボンディングリード3hが各辺に沿って一列に並んで設けられている。

【0047】

なお、ボンディングリード3hは、それぞれスルーホール3eと銅配線3gを介して電気的に接続されている。また、各ボンディングリード3hにはそれぞれの外側に向かって給電線3jが接続されている。

【0048】

一方、パッケージ基板3の裏面3bには、図10に示すように、複数のランド3dが格子状に配置されて設けられており、これらランド3dには外部端子である半田バンプ8(図3参照)が接続される。また、複数のランド3dは、それぞれスルーホール3eと接続されている。

【0049】

このようにパッケージ基板3の主面3a及び裏面3bには、ボンディングリード3h、銅配線3g、給電線3j、ランド3d及びスルーホール3e等の導体部が形成されており、これらの導体部は、例えば、銅合金(Cu)によって形成されている。また、複数のランド3d及びボンディングリード3hには、導電性のワイヤ4との接続強度を向上するために、銅合金の上にNi/Au、あるいはNi/Pd/Auなどの表面処理を施している。

【0050】

また、パッケージ基板3の主面3a及び裏面3bには、図12に示すように絶縁膜であるソルダレジスト膜3fが形成されている。なお、主面3aにおいては、ソルダレジスト膜3fの細長い開口部3i(図9参照)に複数のボンディングリード3hが並んだ状態で露出している。一方、裏面3bにおいては、ランド3dのみが露出している。すなわち、ソルダレジスト膜3fは、ボンディングリード3hやランド3d以外の導体部である銅配線3g、給電線3j及びスルーホール3e等を覆っている。

【0051】

次に、CSP7に組み込まれている種々の構成部材の材質等について説明すると、半導体チップ1は、例えば、シリコンなどによって形成され、その主面1aには集積回路が形成されている。さらに、図1に示すように半導体チップ1の主面1aの周縁部には複数の電極であるパッド1cが形成されている。また、このパッド1cと、パッケージ基板3の主面3aの外周部(周縁部)に配置されたボンディングリード3hとを電気的に接続する導電性のワイヤ4は、例えば、金線などである。

【0052】

また、半導体チップ1は、図2、図3に示すように、その裏面1bが、ダイボンド用フィルム2を介してパッケージ基板3に固着され、主面1aを上方に向けた状態でパッケージ基板3に搭載されている。

【0053】

さらに、半導体チップ1や複数の導電性のワイヤ4を樹脂封止する封止体6は、例えば、熱硬化性のエポキシ樹脂などによって形成されている。

【0054】

次に、本実施の形態1のCSP7の製造方法を、図13及び図14に示す製造プロセスフロー図を用いて説明する。

【0055】

まず、図13のステップS1に示す基板準備を行う。ここでは、複数のパッケージ基板3を形成する領域が区画配置された多数個取り基板9を準備する。なお、パッケージ基板3を形成する領域には、各領域の外周部(周縁部)に複数のボンディングリード3hが並んで配置された基板を準備する。

【0056】

その後、ステップS2に示すダイボンディングを行って多数個取り基板9上に図3に示すダイボンド用フィルム2を介して半導体チップ1を固着する。その際、ダイボンド用フィルム2は、例えば、半導体ウエハをダイシングによって個片化する際に用いるダイシング用のテープ部材の接着層をウエハ裏面に残留させたものである。

【0057】

なお、パッケージ基板3に対応した各領域には、各領域の外周部に複数のボンディングリード3hが並んで配置されており、したがって、半導体チップ1は、外周部のボンディングリード列の内側に搭載する。

【0058】

その後、ステップS3に示すワイヤボンディングを行う。ここでは、図3及び図4に示すように、半導体チップ1の主面1aのパッド1cと、これに対応する多数個取り基板9のパッケージ基板3のボンディングリード3hとを金線等の導電性のワイヤ4によって電気的に接続する。

【0059】

その際、本実施の形態1では、逆ボンディング方式によって基板のボンディングリード3hと半導体チップ1のパッド1cとをワイヤ4で接続する。また、各ワイヤ4において、ワイヤ4の一部であるループの頂点4bが第1ボンドのワイヤ接続部4aより外側に配置されるようにワイヤボンディングする。すなわち、各ワイヤ4のループの最上位地点がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側(パッケージ基板3の外周部側)に配置されるようにワイヤボンディングする。

【0060】

ワイヤボンディング工程では、まず、多数個取り基板9のパッケージ基板3の領域のボンディングリード3hに第1ボンドを行う。すなわち、図5に示すように、ワイヤ4のボール状に形成された先端部をキャピラリ18で基板の図4に示すボンディングリード3hに押し付けて接続する。

【0061】

その後、図6に示すように、キャピラリ18を半導体チップ1から離れる方向に移動させてワイヤ4を前記ボンディングリード3hから引き出す。すなわち、キャピラリ18を半導体チップ1から離れる方向で、かつ斜め上方に移動させてワイヤ4を前記ボンディングリード3hから斜め上方に引き出す。

【0062】

その後、キャピラリ18の移動を所定箇所で一旦停止し、続いて図7に示すように、キャピラリ18を真上(垂直上)に移動させてワイヤ4を上方に引き出す。

【0063】

その後、ワイヤ4がチップ高さを超えたところでキャピラリ18の上方への移動を停止し、その後、図8に示すように、キャピラリ18を半導体チップ1のパッド1c上にほぼ水平に移動させて、半導体チップ1のパッド1c上にワイヤ4を配置する。

【0064】

その後、パッド1cにおいてキャピラリ18によりワイヤ4の一部を押し潰して半導体チップ1のパッド1cにワイヤ4を接続する。これにより、ワイヤ4と半導体チップ1のパッド1cとの接続である第2ボンドを完了するとともに、各ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置された状態となる。

【0065】

なお、半導体チップ1のパッド1c上には、予め金バンプ19が形成されており、第2ボンドの際には、ワイヤ4をパッド1c上の金バンプ19に接続する。ただし、パッド1c上に金バンプ19は形成されていなくてもよく、その場合は、ワイヤ4を直接パッド1cに接続する。

【0066】

その後、ステップS4に示す樹脂モールドを行う。ここでは、多数個取り基板9上において、樹脂成形金型20の1つのキャビティ20aで多数個取り基板9上の複数の領域(複数のパッケージ基板3の領域)を一括して覆った状態で樹脂封止を行い、これにより、一括封止体5を形成する。なお、一括封止体5を形成する封止用樹脂は、例えば、熱硬化性のエポキシ樹脂などである。

【0067】

その後、図14のステップS5に示すボールマウントを行って図3に示すように各ランド3dに半田バンプ8を接続する。

【0068】

その後、ステップS6に示すマークを行う。ここではレーザマーキング法などでマーキング10を行って一括封止体5にマークを付す。なお、マーキング10は、例えば、インクマーキング法などで行ってもよい。

【0069】

その後、ステップS7に示す個片化を行う。ここでは、一括封止体5の表面にダイシングテープ12を貼り、ダイシングテープ12で固定した状態でダイシングブレード11によって切断して各CSP7に個片化する。

【0070】

これにより、ステップS8に示すようにCSP7の組み立てを完了して製品完成となる。

【0071】

なお、図15は一括封止による樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図であり、この変形例の製造プロセスは、マークを行った後にボールマウントを行うものである。

【0072】

ボールマウントの工程は、パッケージ基板3のランド3dに半田を塗布した後、リフロー処理により半田バンプ8を形成する。このため、ボールマウントの工程においても、このリフロー処理によりパッケージ基板3が更に反る問題が生じる。マークの工程では、レーザマーキング法などでマーキングを行うが、パッケージ基板3が反った状態では、一括封止体5の表面に垂直にレーザを照射することが困難となるため、一括封止体5の表面にマークが付されないというマーキング不良が発生する。

【0073】

そこで、図15に示す変形例では、パッケージ基板3が反る要因の一つである半田バンプ8形成時のリフロー処理を行う前に、先にマークの工程を行う。これにより、マーキング不良を抑制することができる。

【0074】

本実施の形態1の半導体装置及びその製造方法によれば、逆ボンディングによって接続された各ワイヤの一部であるループの頂点4bが、パッケージ基板3のボンディングリード3hにおける第1ボンドのワイヤ接続部4aより外側(パッケージ基板3の外周部側)に配置されていることにより、ワイヤ4が外側に遠回りして引き回されるため、パッケージ基板3のボンディングリード3hと半導体チップ1のパッド1cとの接続においてワイヤ長を長くすることができる。

【0075】

これにより、ワイヤ4の引き回しのマージンが増えてキャピラリ18の動く速度にワイヤ送り速度が追従することが可能になり、ワイヤ4のループ形状の安定化を図ることができる。

【0076】

その結果、チップ端部とワイヤ4のショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【0077】

これにより、半導体チップ1の主面1aの端部にテストパターンが形成されている場合であっても、テストパターンとワイヤ4とがショートすることを低減できる。

【0078】

また、ワイヤ4を外側に遠回りさせることにより、パッケージ端部からパッケージ基板3の端子(ボンディングリード3h)までの距離を長くしてリークパスを長くできるため、吸湿不良のマージンを確保することが可能になる。

【0079】

また、ワイヤ4を遠回りさせる方法としては、ループの頂点4bを高くしてもワイヤ長を長く形成することは可能であるが、その場合、ワイヤ4の一部が封止体6の表面側から露出しないように、封止体6を厚く形成する必要がある。そのため、半導体装置の薄型化が困難となる。しかしながら、本実施の形態1では、ワイヤ4を外側(半導体チップ1とは反対側の方向)に遠回りさせて横方向に膨らませているため、ワイヤ4の一部が封止体6の表面側から露出することを防止できる。すなわち、低ループを形成しつつワイヤ長を長くすることができるため、CSP7の更なる薄型化にも対応することができる。

【0080】

さらに、低ループによってワイヤ長を長くできるため、半導体装置の薄型化の要求が低ければ、ワイヤ4を低ループで形成したことにより、ワイヤ4のループの頂点4bから封止体6の表面までの厚さを十分確保できる。これにより、封止体6の表面にレーザマーキングを施したとしても、レーザマーキングにより形成される溝からワイヤ4が露出する恐れや、レーザによりワイヤ4の一部を溶断する恐れを低減することができる。

【0081】

また、ワイヤボンディングにおいて、逆ボンディング方式を採用することにより、第2ボンド時にキャピラリ18を極端に低い側に打ち降ろすことを避けることができる。これにより、ワイヤ4がキャピラリ18と半導体チップ1の端部の間に入らない問題や、1st側から2nd側に打ち下ろしたワイヤ4にキャピラリ18の一部が接触する問題、更にはキャピラリ18の先端のワイヤ4との摩耗を低減することができ、キャピラリ18の長寿命化を図ることができる。

【0082】

次に、本実施の形態1の変形例のパッケージ基板3について説明する。

【0083】

図16〜図19に示す変形例のパッケージ基板3は、導体部のめっきが、無電解めっき処理によって形成されたものであり、図9に示すパッケージ基板3のようなボンディングリード3hの外側の給電線3jが形成されていない構造となっている。したがって、主面3aに形成されたソルダレジスト膜3fがボンディングリード3h上のワイヤ接続部4aより内側に配置されている。

【0084】

また、図20〜22に示す変形例のパッケージ基板3は、各ボンディングリード3hの外側に給電線3jが形成されており、一方、給電線3jを覆うソルダレジスト膜3fは形成されずにボンディングリード3hとともに給電線3jが露出している構造のものである。

【0085】

これは、CSP7では、半導体チップ1の端部からパッケージ基板3の端部までの距離が約0.2〜0.3mmと非常に狭く、かつソルダレジスト膜3fの位置精度は、±0.05mmと非常に大きいため、給電線3j上にソルダレジスト膜3fを形成した場合の位置ずれを考慮して、ソルダレジスト膜3fを形成せずに給電線3jを露出させるものである。

【0086】

ただし、給電線3jを露出させた場合、ソルダレジスト膜3fの位置ずれの問題は回避されるものの、吸湿の影響が出る可能性があり、したがって、各ボンディングリード3hの外側に給電線3jが形成されている場合、給電線3jを覆うソルダレジスト膜3fは形成されていても、形成されていなくてもどちらでもよいが、チップ端部から基板端部までの距離との兼ね合いで形成可能であれば形成した方が好ましい。

【0087】

(実施の形態2)

図23は本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図、図24は図23に示す半導体装置の構造の一例を示す断面図、図25は図24に示すA部の構造を示す拡大部分断面図、図26は図24に示すB部の構造を示す拡大部分断面図である。

【0088】

図23〜図26に示す本実施の形態2の半導体装置は、半導体チップ1の上に他の半導体チップである第2の半導体チップ17がダイボンド用フィルム2を介して固定されているものであり、実施の形態1のCSP7と同様に樹脂封止型で、かつ小型のチップスタック構造のCSP14である。

【0089】

すなわち、図25及び図26に示すように、パッケージ基板3の主面3aのソルダレジスト膜3f上に、ダイボンド用フィルム2を介して1段目(下段側)の半導体チップ1がその主面1aを上方に向けてフェイスアップ実装されており、さらにこの上に2段目(上段側)の第2の半導体チップ17がその主面17aを上方に向けてフェイスアップ実装されている。その際、第2の半導体チップ17もその裏面17bがダイボンド用フィルム2を介して半導体チップ1の主面1a上に固定されている。

【0090】

また、CSP14は、実施の形態1のCSP7と同様に小型の半導体パッケージである。すなわち、半導体チップ1の大きさとパッケージ基板3の大きさがほぼ同じであり、パッケージ基板3の方が僅かに大きい程度である。例えば、半導体チップ1の端部からパッケージ基板3の端部までの距離は、CSP7と同様に約0.2〜0.3mmと非常に狭い。

【0091】

したがって、図25及び図26に示すように、上下段両方のチップとも逆ボンディングによってワイヤボンディングが行われて組み立てられたものである。

【0092】

なお、1段目の半導体チップ1のワイヤボンディングについては、基板側のボンディングリード3hへのワイヤ接続が第1ボンドとなっており、半導体チップ1のパッド1cへのワイヤ接続が第2ボンドとなっている。その際、実施の形態1のCSP7と同様に、それぞれのワイヤ4の一部であるループの頂点4bがワイヤ接続部4aより外側に配置されている。すなわち、各ワイヤ4のループの最上位地点(ここでは4b)がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側に配置されている。

【0093】

さらに、2段目の第2の半導体チップ17のワイヤ接続のうち、図26に示すように、1段目の半導体チップ1のパッド1cと上段(2段目)の第2の半導体チップ17のパッド17cとを接続する第2ワイヤ(他のワイヤ)15については、パッド1cとパッド17cの距離が短いため、ワイヤ4と同様に、それぞれの第2ワイヤ15の一部であるループの頂点15bがワイヤ接続部15aより外側に配置されている。つまり、各第2ワイヤ15のループの最上位地点(ここでは15b)がワイヤ接続部15aのワイヤ引き出し方向の中心線13より外側に配置されている。

【0094】

なお、2段目の第2の半導体チップ17のワイヤ接続のうち、図25に示すように、パッケージ基板3のボンディングリード3hと上段(2段目)の第2の半導体チップ17のパッド17cとを接続する第3ワイヤ16については、通常の逆ボンディングが行われている。すなわち、パッケージ基板3のボンディングリード3hと上段の第2の半導体チップ17のパッド17cとのワイヤ接続においては、ボンディングリード3hとパッド17cの距離が長く、ワイヤ長を長く形成することが可能なため、ワイヤループの形状の安定化を図ることができる。

【0095】

したがって、2段目の第2の半導体チップ17のワイヤ接続では、1段目の半導体チップ1のパッド1cと2段目の第2の半導体チップ17のパッド17cとを接続するワイヤボンディングのみに、第2ワイヤ15のループの頂点15bがワイヤ接続部15aより外側に配置されるようなワイヤ接続を行う。

【0096】

本実施の形態2のCSP14においても、各ワイヤの一部であるループの頂点4b,15bが、それぞれの第1ボンドのワイヤ接続部4a,15aより外側に配置されていることにより、ワイヤ4及び第2ワイヤ15が外側に遠回りして引き回されるため、ワイヤ長を長くすることができる。

【0097】

これにより、ワイヤ4及び第2ワイヤ15の引き回しのマージンが増えてキャピラリ18の動く速度にワイヤ送り速度が追従することが可能になり、ワイヤ4及び第2ワイヤ15それぞれのループ形状の安定化を図ることができる。

【0098】

その結果、チップ端部とワイヤ4や第2ワイヤ15とのショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【0099】

本実施の形態2のCSP14のその他の構造及びその他の効果については、実施の形態1のCSP7と同様であるため、その重複説明は省略する。

【0100】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0101】

例えば、前記実施の形態1及び2では、半導体装置の一例として、BGA型の小型の半導体パッケージ(CSP7,14)の場合について説明したが、前記半導体装置は、LGA(Land Grid Array)型やQFN(Quad Flat Non-leaded Package)型のものであってもよい。

【0102】

また、半導体チップ1や第2の半導体チップ17の固定については、ダイボンド用フィルム2に限らず、例えば、ペースト状の接着材等を用いて固定してもよい。

【0103】

また、ボールマウントの工程については、パッケージ基板3のランド3dに半田を塗布した後、リフロー処理により半田バンプ8を形成する方法に限らず、例えば、予めボール形状に形成しておき、ランド3dに転写する方法や、マスクを介して半田を印刷する方法を用いてもよい。

【産業上の利用可能性】

【0104】

本発明は、配線基板を有した電子装置およびその製造技術に好適である。

【符号の説明】

【0105】

1 半導体チップ

1a 主面

1b 裏面

1c パッド(電極)

2 ダイボンド用フィルム

3 パッケージ基板(配線基板)

3a 主面

3b 裏面

3c コア材

3d ランド

3e スルーホール

3f ソルダレジスト膜

3g 銅配線

3h ボンディングリード(端子)

3i 開口部

3j 給電線

4 ワイヤ

4a ワイヤ接続部

4b ループの頂点

5 一括封止体

6 封止体

7 CSP(半導体装置)

8 半田バンプ(外部端子)

9 多数個取り基板

10 マーキング

11 ダイシングブレード

12 ダイシングテープ

13 中心線

14 CSP(半導体装置)

15 第2ワイヤ(他のワイヤ)

15a ワイヤ接続部

15b ループの頂点

16 第3ワイヤ

17 第2の半導体チップ(他の半導体チップ)

17a 主面

17b 裏面

17c パッド(電極)

18 キャピラリ

19 金バンプ

20 樹脂成形金型

20a キャビティ

30 小型パッケージ

【技術分野】

【0001】

本発明は、半導体製造技術に関し、特に、ワイヤボンディングにおける接続不良の抑制化に適用して有効な技術に関する。

【背景技術】

【0002】

第1ボンディング点にネック部分を形成後、第1所定量の長さのワイヤを繰り出しながらキャピラリを上昇させ、第2ボンディング点に向かう方向に移動させて第1癖付け部分を形成する。キャピラリを下降させ、第2ボンディング点と反対側に向かう方向に移動させて第2癖付け部分を形成する。キャピラリを上昇させて第1癖付け部分がキャピラリ先端に位置するまでワイヤを繰り出し、その状態でキャピラリを第2ボンディング点まで移動させワイヤループを形成する技術がある(例えば、特許文献1参照)。

【0003】

第1ボンディング点にワイヤを接続する工程と、キャピラリを少し上昇させ、第1のリバース動作を行う工程と、キャピラリを上昇させ、第2のリバース動作を行う工程と、キャピラリを上昇させ、第3のリバース動作を行う工程とを行う。さらに、クランパが閉じ、キャピラリを第2ボンディング点の反対の方向に水平移動させる工程と、クランパが開き、キャピラリを第2ボンディング点の方向に水平移動させる工程と、キャピラリを第1ボンディング点の上方まで上昇させてワイヤを繰り出し、第2ボンディング点に接続する工程とを行う技術がある(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−87747号公報(図2)

【特許文献2】特開2004−319921号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0005】

小型化の要求に応えた半導体装置の一例として、チップサイズと半導体パッケージ(配線基板)のサイズがほぼ同じであるCSP(Chip Size Package)と呼ばれる半導体装置が知られている。

【0006】

前記CSPは、半導体チップの端部(端辺)と配線基板の端部(端辺)との距離が約0.2〜0.3mmと狭い(短い)ため、配線基板の主面に形成されたワイヤ接続するためのボンディングリード(端子)と半導体チップの端部(端辺)との距離も約0.1mmと非常に狭い(短い)。そのため、ワイヤボンディング工程において、半導体チップの電極と接続する点を1st側、配線基板の主面に形成されたボンディングリードと接続する点を2nd側とする所謂正ボンディング方式によりワイヤ接続を行うと、ワイヤがキャピラリとチップ端の間に入らないという現象が起こる。

【0007】

これを詳細に説明すると、図27の比較例に示すように、1st側から2nd側に打ち下ろしたワイヤ4にキャピラリ18の一部が接触する。そこで、キャピラリ18の根元から先端まで補足加工した部分(L)を長くすれば、ワイヤ4との干渉は抑制できるが、ワイヤボンディング工程では超音波を併用したネイルヘッドボンディング方式により行うため、細いL寸法分が長すぎると、細い部分でキャピラリ18が撓むため、超音波がキャピラリ18の先端に伝わり難くなる。

【0008】

また、正ボンディングの場合、2nd側のワイヤ4を圧着する際、ワイヤ4が2nd側よりも高い位置から引き出されているために、図27に示すようにA部において、キャピラリ18の一部とワイヤ4との間で摩擦が生じ易く、キャピラリ18の一部が磨耗し易い。

【0009】

そこで、前記特許文献1(特開2004−87747号公報)や前記特許文献2(特開2004−319921号公報)に記載されているように、配線基板の主面に形成されたボンディングリードと接続する点を1st(第1ボンド)側、半導体チップの電極と接続する点を2nd(第2ボンド)側とする所謂逆ボンディング方式によりワイヤ接続を行えば、ワイヤ断線不良を抑制することができる。すなわち、ワイヤは低い位置にある1st側から高い位置にある2nd側へとほぼ同じ高さまで垂直方向に引き上げられ、その後、水平方向にキャピラリを移動させて高い位置にある2nd側に接続するため、1st側におけるワイヤの根元が折れ曲がることはなく、その結果、ワイヤ断線不良を抑制することができる。

【0010】

しかしながら、上記したように半導体装置の小型化に伴い、配線基板の主面に形成されたボンディングリードと半導体チップの端部(端辺)との距離も約0.1mmと非常に狭いため、逆ボンディング方式によりワイヤ接続を行うと、最終的にワイヤを2nd側に倒したときに、ワイヤの引き回しのマージンが足りないため、図28の比較例の小型パッケージ30に示すように、ワイヤ4がチップ端部に接触するという現象が起こる。

【0011】

言い換えると、スプールからのワイヤ送り速度とキャピラリ18の動く速度が対応しておらず、ワイヤ4の送り速度よりもキャピラリ18の動きの方が速いため、ワイヤ供給力が少なくなり、形成されたワイヤ4が短く安定しないことから、チップ端部にショートしてワイヤ接続不良を引き起こすという問題が発生する。特に、半導体チップ1の主面1aの端部にテストパターンが形成されている場合があり、この場合、テストパターンとワイヤ4とがショートすることも問題となる。

【0012】

本発明の目的は、ワイヤ接続不良の抑制化を図ることができる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0015】

すなわち、本発明は、主面の周縁部に沿って配置された複数の端子を有する配線基板と、配線基板の主面の端子列の内側に搭載された半導体チップと、半導体チップの電極と配線基板の端子とを接続し、配線基板側の端子が第1ボンドとして接続され、半導体チップの電極が第2ボンドとして接続された複数のワイヤとを有し、前記ワイヤの一部が、前記端子におけるワイヤ接続部より前記周縁部側に配置されているものである。

【0016】

また、本発明は、配線基板に半導体チップを接続した後、ワイヤの先端部を配線基板の端子に接続し、その後キャピラリを半導体チップから離れる方向に移動させてワイヤを前記端子から引き出し、さらにキャピラリを半導体チップの電極上に配置した後、前記ワイヤの一部を半導体チップの電極に接続する工程を有し、ワイヤの一部が、配線基板の端子におけるワイヤ接続部より周縁部側に配置されるようにワイヤを接続するものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0018】

ワイヤの一部が、配線基板の端子における第1ボンドのワイヤ接続部より外側に配置されていることにより、ワイヤが外側に遠回りして引き回されるため、配線基板の端子と半導体チップの電極との接続においてワイヤ長を長くすることができる。これにより、ワイヤの引き回しのマージンが増えてキャピラリの動く速度にワイヤ送り速度が追従することが可能になり、ワイヤのループ形状の安定化を図ることができる。その結果、チップ端部とワイヤのショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図2】図1に示す半導体装置の構造の一例を示す断面図である。

【図3】図2に示すA部の構造を示す拡大部分断面図である。

【図4】図3に示すワイヤ接合部の構造の一例を示す拡大部分断面図である。

【図5】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図6】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図7】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図8】図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。

【図9】図1に示す半導体装置に組み込まれる配線基板の主面側の配線パターンの一例を示す平面図である。

【図10】図9に示す配線基板の裏面側の配線パターンの一例を示す裏面図である。

【図11】図9に示す配線基板の構造の一例を示す断面図である。

【図12】図11に示すA部の構造を示す拡大部分断面図である。

【図13】図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図である。

【図14】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図である。

【図15】図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【図16】本発明の実施の形態1の変形例の配線基板の主面側の配線パターンを示す平面図である。

【図17】図16に示す配線基板の裏面側の配線パターンを示す裏面図である。

【図18】図16に示す配線基板の構造を示す断面図である。

【図19】図18に示すA部の構造を示す拡大部分断面図である。

【図20】本発明の実施の形態1の他の変形例の配線基板の主面側の配線パターンを示す平面図である。

【図21】図20に示す配線基板の構造を示す断面図である。

【図22】図21に示すA部の構造を示す拡大部分断面図である。

【図23】本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図である。

【図24】図23に示す半導体装置の構造の一例を示す断面図である。

【図25】図24に示すA部の構造を示す拡大部分断面図である。

【図26】図24に示すB部の構造を示す拡大部分断面図である。

【図27】比較例のワイヤボンディング時のキャピラリ押し付け状態の一例を示す拡大部分断面図である。

【図28】比較例のワイヤボンディング後の接続不良の状態を示す断面図である。

【発明を実施するための形態】

【0020】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

【0022】

また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0023】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0024】

(実施の形態1)

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1に示す半導体装置の構造の一例を示す断面図、図3は図2に示すA部の構造を示す拡大部分断面図、図4は図3に示すワイヤ接合部の構造の一例を示す拡大部分断面図、図5〜図8は図4に示すワイヤリング時のキャピラリの移動軌跡の一例を示す断面図である。また、図9は図1に示す半導体装置に組み込まれる配線基板の主面側の配線パターンの一例を示す平面図、図10は図9に示す配線基板の裏面側の配線パターンの一例を示す裏面図、図11は図9に示す配線基板の構造の一例を示す断面図、図12は図11に示すA部の構造を示す拡大部分断面図である。さらに、図13は図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図、図14は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図、図15は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

【0025】

また、図16は本発明の実施の形態1の変形例の配線基板の主面側の配線パターンを示す平面図、図17は図16に示す配線基板の裏面側の配線パターンを示す裏面図、図18は図16に示す配線基板の構造を示す断面図、図19は図18に示すA部の構造を示す拡大部分断面図である。さらに、図20は本発明の実施の形態1の他の変形例の配線基板の主面側の配線パターンを示す平面図、図21は図20に示す配線基板の構造を示す断面図、図22は図21に示すA部の構造を示す拡大部分断面図である。

【0026】

本実施の形態1の半導体装置は、配線基板上に半導体チップ1が搭載された樹脂封止型の小型の半導体パッケージであり、本実施の形態1ではその一例として、図1〜図3に示すようなCSP7を取り上げて説明する。

【0027】

なお、CSP7は、配線基板の裏面3bに複数の外部端子である半田バンプ8が格子状に配置されて取り付けられており、したがって、CSP7はBGA(Ball Grid Array)型の半導体パッケージである。

【0028】

図1〜図3を用いてCSP7の構造について説明すると、主面3aと、主面3aに対向する裏面3bと、主面3aの外周部に並んで配置された複数のボンディングリード(端子)3hとを有する配線基板であるパッケージ基板3と、パッケージ基板3の主面3aのボンディングリード列の内側(複数のボンディングリード3hの内側の領域)に搭載され、かつ集積回路を有する半導体チップ1とを備えている。また、半導体チップ1の電極であるパッド1cとパッケージ基板3のボンディングリード3hとを電気的に接続する導電性のワイヤ4と、パッケージ基板3の主面3aと半導体チップ1との間に配置された(予め半導体チップ1の裏面側に貼り付けられた)ダイボンド材であるダイボンド用フィルム2と、パッケージ基板3の裏面3bの複数のランド3dに設けられた複数の外部端子(外部接続用端子)である半田バンプ8とを備えている。さらに、半導体チップ1及び複数のワイヤ4を樹脂封止する封止体6を備えており、パッケージ基板3の主面3aの保護膜であるソルダレジスト膜3f上に、半導体チップ1がダイボンド用フィルム2を介して固定されている。

【0029】

なお、CSP7は、小型の半導体パッケージであるが、半導体チップ1の大きさとパッケージ基板3の大きさがほぼ同じであり、パッケージ基板3の方が僅かに大きい程度である。例えば、図4に示すように、半導体チップ1の端部からパッケージ基板3の端部までの距離(T1)は、約0.2〜0.3mmと非常に狭い(短い)。

【0030】

したがって、パッケージ基板3の主面3aの外周部(周縁部)に形成されたワイヤ接続するためのボンディングリード3hと半導体チップ1の端部(端辺)との距離(T2)も約0.1mm程度と非常に狭い(短い)。

【0031】

そこで、CSP7では、図1及び図3に示すように、パッケージ基板3においてチップ外側の領域で、かつ基板の外周部に複数のボンディングリード3hが並んで配置されており、半導体チップ1の主面1aに設けられた電極であるパッド1cと、これに対応するパッケージ基板3のボンディングリード3hとが金線等の導電性のワイヤ4によって電気的に接続されている。

【0032】

その際、本実施の形態1のCSP7では、図1に示すように、複数のワイヤ4それぞれが、半導体チップ1のパッド1cと、これに対応するパッケージ基板3のボンディングリード3hとを電気的に接続するとともに、基板側のボンディングリード3hが第1ボンドとして接続され、一方、チップ側のパッド1cが第2ボンドとして接続されたものである。

【0033】

ここで、前記第1ボンドは、電気トーチによりワイヤ先端に形成されたボールをキャピラリ18で端子に押し付けて接続するものであり、一方、前記第2ボンドは、第1ボンド後、ワイヤ4を前記端子から引き出してキャピラリ18を他方の端子上に配置し、その後、ワイヤ4の一部を前記他方の端子に対してキャピラリ18で押し潰してこの他方の端子に接続するものである。

【0034】

本実施の形態1のCSP7では、前記第1ボンドがパッケージ基板3のボンディングリード3hに対して行われ、前記第2ボンドが半導体チップ1のパッド1cに対して行われたものである。すなわち、CSP7は、半導体チップ1のパッド1cとパッケージ基板3のボンディングリード3hとの接続において、逆ボンディングによるワイヤボンディングが行われて組み立てられたものである。

【0035】

これは、CSP7は、半導体チップ1とパッケージ基板3の大きさがほぼ同じ小型の半導体パッケージであり、チップの端部から基板の端部までの距離が、約0.2〜0.3mmと非常に狭い構造となっており、さらにボンディングリード3hとチップの端部との距離も約0.1mm程度と非常に狭いため、基板上の半導体チップ1の外側の領域において第2ボンドとしてキャピラリ18を滑らしながら配置することが困難なためである。

【0036】

すなわち、ワイヤ接続時にキャピラリ18をボンディングリード3hから上方に移動させることでワイヤボンディング用に狭い領域しか確保できない基板側を第1ボンドとし、チップ側を第2ボンドとするものである。

【0037】

さらに、本実施の形態1のCSP7では、図1に示すように、パッケージ基板3の主面3a上において、逆ボンディングによって接続されたそれぞれのワイヤ4の一部が、ボンディングリード3hにおける第1ボンドのワイヤ接続部4aより外側に(パッケージ基板3の外周部に向かって)配置(形成)されている。

【0038】

具体的には、図4に示すように、ワイヤ4の一部であるループの頂点4bが第1ボンドのワイヤ接続部4aより外側に配置されている。すなわち、各ワイヤ4のループの最上位地点(ここでは4b)がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側(半導体チップ1から離れる方向)に配置されているものである。

【0039】

ここで、図5〜図8を用いて、図4に示すワイヤ4のループ形状の形成方法について説明すると、まず、パッケージ基板3のボンディングリード3hに第1ボンドを行う。すなわち、ワイヤ4のボール状に形成された先端部を、図4、図5に示すように、キャピラリ18でパッケージ基板3の図4に示すボンディングリード3hに押し付けて接続する。

【0040】

その後、図6に示すように、キャピラリ18を半導体チップ1から離れる方向に移動させてワイヤ4を前記ボンディングリード3hから引き出す。すなわち、キャピラリ18を半導体チップ1から離れる方向で(パッケージ基板3の外周部に向かって)、かつ斜め上方に移動させてワイヤ4を前記ボンディングリード3hから斜め上方に引き出す。

【0041】

その後、キャピラリ18の移動を所定箇所で一旦停止し、続いて図7に示すように、キャピラリ18を真上(垂直上)に移動させてワイヤ4を上方に引き出す。

【0042】

その後、ワイヤ4がチップ高さを超えたところでキャピラリ18の上方への移動を停止し、その後、図8に示すように、キャピラリ18を半導体チップ1のパッド1c上にほぼ水平に移動させて、半導体チップ1のパッド1c上にワイヤ4を配置する。

【0043】

その後、パッド1cにおいてキャピラリ18によりワイヤ4の一部を押し潰して半導体チップ1のパッド1cにワイヤ4を接続する。これにより、ワイヤ4と半導体チップ1のパッド1cとの接続である第2ボンドを完了するとともに、各ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置された状態となる。

【0044】

なお、半導体チップ1のパッド1c上には、予め金バンプ(スタッドバンプ)19が形成されており、第2ボンドの際には、ワイヤ4をパッド1c上の金バンプ19に接続する。これは、ワイヤボンディング工程において、第2ボンドの際には、キャピラリ18を擦り付ける様にワイヤ4をパッド1c(又は、ボンディングリード3h)に圧着するため、キャピラリ18を滑走させる距離だけパッド1cの形状を相対的に大きく形成しておく必要がある。しかしながら、本実施の形態1のように、逆ボンディング方式の場合、半導体チップ1の主面上に形成されたパッド1cを相対的に大きく形成しようとすると、その分半導体チップ1を小型化することが困難となる。更には、半導体チップ1の主面上において上記圧着動作を行うと、圧着圧力により、半導体チップ1に応力が伝わり、特に半導体チップ1の厚さが薄ければチップの抗折強度も低いため、チップクラックを起こす原因となる。そこで、第2ボンドする前に、金バンプ19を形成しておく。金バンプ19はパッド1cに比べ硬度が低いため、微小な圧着圧力でもワイヤ4の一部を容易に圧着することが可能である。更には、第1ボンドする前に金バンプ19を形成しておくことで、第2ボンドする際のボンディングポイントを事前に認識しておくことが可能であるため、ワイヤボンディングの座標が変わらず、安定したワイヤボンディング工程が可能となる。ただし、半導体チップ1の面積が相対的に大きく、半導体チップ1の厚さも厚ければチップの抗折強度も高いため、パッド1c上に金バンプ19は形成されていなくてもよく、その場合は、ワイヤ4を直接パッド1cに接続する。

【0045】

次に、図9〜図12に示すCSP7に組み込まれるパッケージ基板3の構造について説明する。

【0046】

パッケージ基板3は、コア材3cと、その主面3a及び裏面3bに形成された複数の導体部と、主面3aと裏面3bの前記導体部を接続するスルーホール3eと、前記導体部の少なくとも一部を覆うソルダレジスト膜3fとを有している。パッケージ基板3の表面である主面3aには、図9に示すように基板の外周部(周縁部)に複数のボンディングリード3hが各辺に沿って一列に並んで設けられている。

【0047】

なお、ボンディングリード3hは、それぞれスルーホール3eと銅配線3gを介して電気的に接続されている。また、各ボンディングリード3hにはそれぞれの外側に向かって給電線3jが接続されている。

【0048】

一方、パッケージ基板3の裏面3bには、図10に示すように、複数のランド3dが格子状に配置されて設けられており、これらランド3dには外部端子である半田バンプ8(図3参照)が接続される。また、複数のランド3dは、それぞれスルーホール3eと接続されている。

【0049】

このようにパッケージ基板3の主面3a及び裏面3bには、ボンディングリード3h、銅配線3g、給電線3j、ランド3d及びスルーホール3e等の導体部が形成されており、これらの導体部は、例えば、銅合金(Cu)によって形成されている。また、複数のランド3d及びボンディングリード3hには、導電性のワイヤ4との接続強度を向上するために、銅合金の上にNi/Au、あるいはNi/Pd/Auなどの表面処理を施している。

【0050】

また、パッケージ基板3の主面3a及び裏面3bには、図12に示すように絶縁膜であるソルダレジスト膜3fが形成されている。なお、主面3aにおいては、ソルダレジスト膜3fの細長い開口部3i(図9参照)に複数のボンディングリード3hが並んだ状態で露出している。一方、裏面3bにおいては、ランド3dのみが露出している。すなわち、ソルダレジスト膜3fは、ボンディングリード3hやランド3d以外の導体部である銅配線3g、給電線3j及びスルーホール3e等を覆っている。

【0051】

次に、CSP7に組み込まれている種々の構成部材の材質等について説明すると、半導体チップ1は、例えば、シリコンなどによって形成され、その主面1aには集積回路が形成されている。さらに、図1に示すように半導体チップ1の主面1aの周縁部には複数の電極であるパッド1cが形成されている。また、このパッド1cと、パッケージ基板3の主面3aの外周部(周縁部)に配置されたボンディングリード3hとを電気的に接続する導電性のワイヤ4は、例えば、金線などである。

【0052】

また、半導体チップ1は、図2、図3に示すように、その裏面1bが、ダイボンド用フィルム2を介してパッケージ基板3に固着され、主面1aを上方に向けた状態でパッケージ基板3に搭載されている。

【0053】

さらに、半導体チップ1や複数の導電性のワイヤ4を樹脂封止する封止体6は、例えば、熱硬化性のエポキシ樹脂などによって形成されている。

【0054】

次に、本実施の形態1のCSP7の製造方法を、図13及び図14に示す製造プロセスフロー図を用いて説明する。

【0055】

まず、図13のステップS1に示す基板準備を行う。ここでは、複数のパッケージ基板3を形成する領域が区画配置された多数個取り基板9を準備する。なお、パッケージ基板3を形成する領域には、各領域の外周部(周縁部)に複数のボンディングリード3hが並んで配置された基板を準備する。

【0056】

その後、ステップS2に示すダイボンディングを行って多数個取り基板9上に図3に示すダイボンド用フィルム2を介して半導体チップ1を固着する。その際、ダイボンド用フィルム2は、例えば、半導体ウエハをダイシングによって個片化する際に用いるダイシング用のテープ部材の接着層をウエハ裏面に残留させたものである。

【0057】

なお、パッケージ基板3に対応した各領域には、各領域の外周部に複数のボンディングリード3hが並んで配置されており、したがって、半導体チップ1は、外周部のボンディングリード列の内側に搭載する。

【0058】

その後、ステップS3に示すワイヤボンディングを行う。ここでは、図3及び図4に示すように、半導体チップ1の主面1aのパッド1cと、これに対応する多数個取り基板9のパッケージ基板3のボンディングリード3hとを金線等の導電性のワイヤ4によって電気的に接続する。

【0059】

その際、本実施の形態1では、逆ボンディング方式によって基板のボンディングリード3hと半導体チップ1のパッド1cとをワイヤ4で接続する。また、各ワイヤ4において、ワイヤ4の一部であるループの頂点4bが第1ボンドのワイヤ接続部4aより外側に配置されるようにワイヤボンディングする。すなわち、各ワイヤ4のループの最上位地点がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側(パッケージ基板3の外周部側)に配置されるようにワイヤボンディングする。

【0060】

ワイヤボンディング工程では、まず、多数個取り基板9のパッケージ基板3の領域のボンディングリード3hに第1ボンドを行う。すなわち、図5に示すように、ワイヤ4のボール状に形成された先端部をキャピラリ18で基板の図4に示すボンディングリード3hに押し付けて接続する。

【0061】

その後、図6に示すように、キャピラリ18を半導体チップ1から離れる方向に移動させてワイヤ4を前記ボンディングリード3hから引き出す。すなわち、キャピラリ18を半導体チップ1から離れる方向で、かつ斜め上方に移動させてワイヤ4を前記ボンディングリード3hから斜め上方に引き出す。

【0062】

その後、キャピラリ18の移動を所定箇所で一旦停止し、続いて図7に示すように、キャピラリ18を真上(垂直上)に移動させてワイヤ4を上方に引き出す。

【0063】

その後、ワイヤ4がチップ高さを超えたところでキャピラリ18の上方への移動を停止し、その後、図8に示すように、キャピラリ18を半導体チップ1のパッド1c上にほぼ水平に移動させて、半導体チップ1のパッド1c上にワイヤ4を配置する。

【0064】

その後、パッド1cにおいてキャピラリ18によりワイヤ4の一部を押し潰して半導体チップ1のパッド1cにワイヤ4を接続する。これにより、ワイヤ4と半導体チップ1のパッド1cとの接続である第2ボンドを完了するとともに、各ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置された状態となる。

【0065】

なお、半導体チップ1のパッド1c上には、予め金バンプ19が形成されており、第2ボンドの際には、ワイヤ4をパッド1c上の金バンプ19に接続する。ただし、パッド1c上に金バンプ19は形成されていなくてもよく、その場合は、ワイヤ4を直接パッド1cに接続する。

【0066】

その後、ステップS4に示す樹脂モールドを行う。ここでは、多数個取り基板9上において、樹脂成形金型20の1つのキャビティ20aで多数個取り基板9上の複数の領域(複数のパッケージ基板3の領域)を一括して覆った状態で樹脂封止を行い、これにより、一括封止体5を形成する。なお、一括封止体5を形成する封止用樹脂は、例えば、熱硬化性のエポキシ樹脂などである。

【0067】

その後、図14のステップS5に示すボールマウントを行って図3に示すように各ランド3dに半田バンプ8を接続する。

【0068】

その後、ステップS6に示すマークを行う。ここではレーザマーキング法などでマーキング10を行って一括封止体5にマークを付す。なお、マーキング10は、例えば、インクマーキング法などで行ってもよい。

【0069】

その後、ステップS7に示す個片化を行う。ここでは、一括封止体5の表面にダイシングテープ12を貼り、ダイシングテープ12で固定した状態でダイシングブレード11によって切断して各CSP7に個片化する。

【0070】

これにより、ステップS8に示すようにCSP7の組み立てを完了して製品完成となる。

【0071】

なお、図15は一括封止による樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図であり、この変形例の製造プロセスは、マークを行った後にボールマウントを行うものである。

【0072】

ボールマウントの工程は、パッケージ基板3のランド3dに半田を塗布した後、リフロー処理により半田バンプ8を形成する。このため、ボールマウントの工程においても、このリフロー処理によりパッケージ基板3が更に反る問題が生じる。マークの工程では、レーザマーキング法などでマーキングを行うが、パッケージ基板3が反った状態では、一括封止体5の表面に垂直にレーザを照射することが困難となるため、一括封止体5の表面にマークが付されないというマーキング不良が発生する。

【0073】

そこで、図15に示す変形例では、パッケージ基板3が反る要因の一つである半田バンプ8形成時のリフロー処理を行う前に、先にマークの工程を行う。これにより、マーキング不良を抑制することができる。

【0074】

本実施の形態1の半導体装置及びその製造方法によれば、逆ボンディングによって接続された各ワイヤの一部であるループの頂点4bが、パッケージ基板3のボンディングリード3hにおける第1ボンドのワイヤ接続部4aより外側(パッケージ基板3の外周部側)に配置されていることにより、ワイヤ4が外側に遠回りして引き回されるため、パッケージ基板3のボンディングリード3hと半導体チップ1のパッド1cとの接続においてワイヤ長を長くすることができる。

【0075】

これにより、ワイヤ4の引き回しのマージンが増えてキャピラリ18の動く速度にワイヤ送り速度が追従することが可能になり、ワイヤ4のループ形状の安定化を図ることができる。

【0076】

その結果、チップ端部とワイヤ4のショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【0077】

これにより、半導体チップ1の主面1aの端部にテストパターンが形成されている場合であっても、テストパターンとワイヤ4とがショートすることを低減できる。

【0078】

また、ワイヤ4を外側に遠回りさせることにより、パッケージ端部からパッケージ基板3の端子(ボンディングリード3h)までの距離を長くしてリークパスを長くできるため、吸湿不良のマージンを確保することが可能になる。

【0079】

また、ワイヤ4を遠回りさせる方法としては、ループの頂点4bを高くしてもワイヤ長を長く形成することは可能であるが、その場合、ワイヤ4の一部が封止体6の表面側から露出しないように、封止体6を厚く形成する必要がある。そのため、半導体装置の薄型化が困難となる。しかしながら、本実施の形態1では、ワイヤ4を外側(半導体チップ1とは反対側の方向)に遠回りさせて横方向に膨らませているため、ワイヤ4の一部が封止体6の表面側から露出することを防止できる。すなわち、低ループを形成しつつワイヤ長を長くすることができるため、CSP7の更なる薄型化にも対応することができる。

【0080】

さらに、低ループによってワイヤ長を長くできるため、半導体装置の薄型化の要求が低ければ、ワイヤ4を低ループで形成したことにより、ワイヤ4のループの頂点4bから封止体6の表面までの厚さを十分確保できる。これにより、封止体6の表面にレーザマーキングを施したとしても、レーザマーキングにより形成される溝からワイヤ4が露出する恐れや、レーザによりワイヤ4の一部を溶断する恐れを低減することができる。

【0081】

また、ワイヤボンディングにおいて、逆ボンディング方式を採用することにより、第2ボンド時にキャピラリ18を極端に低い側に打ち降ろすことを避けることができる。これにより、ワイヤ4がキャピラリ18と半導体チップ1の端部の間に入らない問題や、1st側から2nd側に打ち下ろしたワイヤ4にキャピラリ18の一部が接触する問題、更にはキャピラリ18の先端のワイヤ4との摩耗を低減することができ、キャピラリ18の長寿命化を図ることができる。

【0082】

次に、本実施の形態1の変形例のパッケージ基板3について説明する。

【0083】

図16〜図19に示す変形例のパッケージ基板3は、導体部のめっきが、無電解めっき処理によって形成されたものであり、図9に示すパッケージ基板3のようなボンディングリード3hの外側の給電線3jが形成されていない構造となっている。したがって、主面3aに形成されたソルダレジスト膜3fがボンディングリード3h上のワイヤ接続部4aより内側に配置されている。

【0084】

また、図20〜22に示す変形例のパッケージ基板3は、各ボンディングリード3hの外側に給電線3jが形成されており、一方、給電線3jを覆うソルダレジスト膜3fは形成されずにボンディングリード3hとともに給電線3jが露出している構造のものである。

【0085】

これは、CSP7では、半導体チップ1の端部からパッケージ基板3の端部までの距離が約0.2〜0.3mmと非常に狭く、かつソルダレジスト膜3fの位置精度は、±0.05mmと非常に大きいため、給電線3j上にソルダレジスト膜3fを形成した場合の位置ずれを考慮して、ソルダレジスト膜3fを形成せずに給電線3jを露出させるものである。

【0086】

ただし、給電線3jを露出させた場合、ソルダレジスト膜3fの位置ずれの問題は回避されるものの、吸湿の影響が出る可能性があり、したがって、各ボンディングリード3hの外側に給電線3jが形成されている場合、給電線3jを覆うソルダレジスト膜3fは形成されていても、形成されていなくてもどちらでもよいが、チップ端部から基板端部までの距離との兼ね合いで形成可能であれば形成した方が好ましい。

【0087】

(実施の形態2)

図23は本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図、図24は図23に示す半導体装置の構造の一例を示す断面図、図25は図24に示すA部の構造を示す拡大部分断面図、図26は図24に示すB部の構造を示す拡大部分断面図である。

【0088】

図23〜図26に示す本実施の形態2の半導体装置は、半導体チップ1の上に他の半導体チップである第2の半導体チップ17がダイボンド用フィルム2を介して固定されているものであり、実施の形態1のCSP7と同様に樹脂封止型で、かつ小型のチップスタック構造のCSP14である。

【0089】

すなわち、図25及び図26に示すように、パッケージ基板3の主面3aのソルダレジスト膜3f上に、ダイボンド用フィルム2を介して1段目(下段側)の半導体チップ1がその主面1aを上方に向けてフェイスアップ実装されており、さらにこの上に2段目(上段側)の第2の半導体チップ17がその主面17aを上方に向けてフェイスアップ実装されている。その際、第2の半導体チップ17もその裏面17bがダイボンド用フィルム2を介して半導体チップ1の主面1a上に固定されている。

【0090】

また、CSP14は、実施の形態1のCSP7と同様に小型の半導体パッケージである。すなわち、半導体チップ1の大きさとパッケージ基板3の大きさがほぼ同じであり、パッケージ基板3の方が僅かに大きい程度である。例えば、半導体チップ1の端部からパッケージ基板3の端部までの距離は、CSP7と同様に約0.2〜0.3mmと非常に狭い。

【0091】

したがって、図25及び図26に示すように、上下段両方のチップとも逆ボンディングによってワイヤボンディングが行われて組み立てられたものである。

【0092】

なお、1段目の半導体チップ1のワイヤボンディングについては、基板側のボンディングリード3hへのワイヤ接続が第1ボンドとなっており、半導体チップ1のパッド1cへのワイヤ接続が第2ボンドとなっている。その際、実施の形態1のCSP7と同様に、それぞれのワイヤ4の一部であるループの頂点4bがワイヤ接続部4aより外側に配置されている。すなわち、各ワイヤ4のループの最上位地点(ここでは4b)がワイヤ接続部4aのワイヤ引き出し方向の中心線13より外側に配置されている。

【0093】

さらに、2段目の第2の半導体チップ17のワイヤ接続のうち、図26に示すように、1段目の半導体チップ1のパッド1cと上段(2段目)の第2の半導体チップ17のパッド17cとを接続する第2ワイヤ(他のワイヤ)15については、パッド1cとパッド17cの距離が短いため、ワイヤ4と同様に、それぞれの第2ワイヤ15の一部であるループの頂点15bがワイヤ接続部15aより外側に配置されている。つまり、各第2ワイヤ15のループの最上位地点(ここでは15b)がワイヤ接続部15aのワイヤ引き出し方向の中心線13より外側に配置されている。

【0094】

なお、2段目の第2の半導体チップ17のワイヤ接続のうち、図25に示すように、パッケージ基板3のボンディングリード3hと上段(2段目)の第2の半導体チップ17のパッド17cとを接続する第3ワイヤ16については、通常の逆ボンディングが行われている。すなわち、パッケージ基板3のボンディングリード3hと上段の第2の半導体チップ17のパッド17cとのワイヤ接続においては、ボンディングリード3hとパッド17cの距離が長く、ワイヤ長を長く形成することが可能なため、ワイヤループの形状の安定化を図ることができる。

【0095】

したがって、2段目の第2の半導体チップ17のワイヤ接続では、1段目の半導体チップ1のパッド1cと2段目の第2の半導体チップ17のパッド17cとを接続するワイヤボンディングのみに、第2ワイヤ15のループの頂点15bがワイヤ接続部15aより外側に配置されるようなワイヤ接続を行う。

【0096】

本実施の形態2のCSP14においても、各ワイヤの一部であるループの頂点4b,15bが、それぞれの第1ボンドのワイヤ接続部4a,15aより外側に配置されていることにより、ワイヤ4及び第2ワイヤ15が外側に遠回りして引き回されるため、ワイヤ長を長くすることができる。

【0097】

これにより、ワイヤ4及び第2ワイヤ15の引き回しのマージンが増えてキャピラリ18の動く速度にワイヤ送り速度が追従することが可能になり、ワイヤ4及び第2ワイヤ15それぞれのループ形状の安定化を図ることができる。

【0098】

その結果、チップ端部とワイヤ4や第2ワイヤ15とのショートを低減してワイヤ接続不良の発生を低減することができ、ワイヤ接続不良の抑制化を図ることができる。

【0099】

本実施の形態2のCSP14のその他の構造及びその他の効果については、実施の形態1のCSP7と同様であるため、その重複説明は省略する。

【0100】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0101】

例えば、前記実施の形態1及び2では、半導体装置の一例として、BGA型の小型の半導体パッケージ(CSP7,14)の場合について説明したが、前記半導体装置は、LGA(Land Grid Array)型やQFN(Quad Flat Non-leaded Package)型のものであってもよい。

【0102】

また、半導体チップ1や第2の半導体チップ17の固定については、ダイボンド用フィルム2に限らず、例えば、ペースト状の接着材等を用いて固定してもよい。

【0103】

また、ボールマウントの工程については、パッケージ基板3のランド3dに半田を塗布した後、リフロー処理により半田バンプ8を形成する方法に限らず、例えば、予めボール形状に形成しておき、ランド3dに転写する方法や、マスクを介して半田を印刷する方法を用いてもよい。

【産業上の利用可能性】

【0104】

本発明は、配線基板を有した電子装置およびその製造技術に好適である。

【符号の説明】

【0105】

1 半導体チップ

1a 主面

1b 裏面

1c パッド(電極)

2 ダイボンド用フィルム

3 パッケージ基板(配線基板)

3a 主面

3b 裏面

3c コア材

3d ランド

3e スルーホール

3f ソルダレジスト膜

3g 銅配線

3h ボンディングリード(端子)

3i 開口部

3j 給電線

4 ワイヤ

4a ワイヤ接続部

4b ループの頂点

5 一括封止体

6 封止体

7 CSP(半導体装置)

8 半田バンプ(外部端子)

9 多数個取り基板

10 マーキング

11 ダイシングブレード

12 ダイシングテープ

13 中心線

14 CSP(半導体装置)

15 第2ワイヤ(他のワイヤ)

15a ワイヤ接続部

15b ループの頂点

16 第3ワイヤ

17 第2の半導体チップ(他の半導体チップ)

17a 主面

17b 裏面

17c パッド(電極)

18 キャピラリ

19 金バンプ

20 樹脂成形金型

20a キャビティ

30 小型パッケージ

【特許請求の範囲】

【請求項1】

以下の工程を含むことを特徴とする半導体装置の製造方法:

(a)平面形状が矩形状から成る上面、前記上面とは反対側の下面、及び前記上面の上

面辺に沿うように、前記上面に配置された複数の端子を有する配線基板を準備する工程;

(b)平面形状が矩形状から成る第1主面、前記第1主面とは反対側の第1裏面、及び前記第1主面の第1主面辺に沿うように、前記第1主面に配置された複数の第1パッドを有する第1半導体チップを、前記複数の端子から成る端子列よりも前記配線基板の内側に位置し、かつ前記第1裏面が前記配線基板の前記上面と対向するように、前記配線基板の前記上面に搭載する工程;

(c)平面形状が矩形状から成る第2主面、前記第2主面とは反対側の第2裏面、及び前記第2主面の第2主面辺に沿うように、前記第2主面に配置された複数の第2パッドを有する第2半導体チップを、前記複数の第1パッドから成る端子列よりも前記第1半導体チップの内側に位置し、かつ前記第2裏面が前記第1半導体チップの前記第1主面と対向するように、前記第1半導体チップの前記第1主面に積層する工程;

(d)前記第2半導体チップの前記複数の第2パッドと前記第1半導体チップの前記複数の第1パッドとを複数の第1ワイヤを介して、前記第2半導体チップの前記複数の第2パッドと前記配線基板の前記複数の端子とを複数の第2ワイヤを介して、それぞれ電気的に接続する工程;

(e)前記第1半導体チップ、前記第2半導体チップ、前記複数の第1ワイヤ及び前記複数の第2ワイヤを樹脂で封止することで、前記第2半導体チップの前記第2主面側に位置する表面を有する封止体を形成する工程;

ここで、

前記複数の第1ワイヤのそれぞれは、前記第1ワイヤの第1部分を前記第1半導体チップの前記第1パッドと接続してから、前記第1ワイヤの前記第1部分とは異なる第2部分を前記第2半導体チップの前記第2パッドと接続することで、形成され、

前記複数の第1ワイヤのそれぞれは、前記複数の第1ワイヤのそれぞれの一部が、前記第1ワイヤの前記第1部分より前記第1半導体チップの前記第1主面における前記第1主面辺側に位置するように、形成され、

前記複数の第2ワイヤのそれぞれは、前記複数の第2ワイヤのそれぞれが、前記第2ワイヤのうちの前記配線基板の前記端子と接続される部分より前記配線基板の前記上面における前記上面辺側に配置される部分を有さないように、形成される。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記(d)工程では、超音波を併用したキャピラリを用いて行うことを特徴とする半導体装置の製造方法。

【請求項3】

平面形状が矩形状から成る上面、前記上面とは反対側の下面、及び前記上面の上面辺に沿うように、前記上面に配置された複数の端子を有する配線基板と、

平面形状が矩形状から成る第1主面、前記第1主面とは反対側の第1裏面、及び前記第1主面の第1主面辺に沿うように、前記第1主面に配置された複数の第1パッドを有し、前記複数の端子から成る端子列よりも前記配線基板の内側に位置し、かつ前記第1裏面が前記配線基板の前記上面と対向するように、前記配線基板の前記上面に搭載された第1半導体チップと、

平面形状が矩形状から成る第2主面、前記第2主面とは反対側の第2裏面、及び前記第2主面の第2主面辺に沿うように、前記第2主面に配置された複数の第2パッドを有し、前記複数の第1パッドから成る端子列よりも前記第1半導体チップの内側に位置し、かつ前記第2裏面が前記第1半導体チップの前記第1主面と対向するように、前記第1半導体チップの前記第1主面に積層された第2半導体チップと、

前記第2半導体チップの前記複数の第2パッドと前記第1半導体チップの前記複数の第1パッドとをそれぞれ電気的に接続する複数の第1ワイヤと、

前記第2半導体チップの前記複数の第2パッドと前記配線基板の前記複数の端子とをそれぞれ電気的に接続する複数の第2ワイヤと、

前記第2半導体チップの前記第2主面側に位置する表面を有し、前記第1半導体チップ、前記第2半導体チップ、前記複数の第1ワイヤ及び前記複数の第2ワイヤを封止する封止体と、

を含み、

前記複数の第1ワイヤのそれぞれは、前記第1半導体チップの前記複数の第1パッドのそれぞれと接続される第1ワイヤ接続部を有し、

前記複数の第1ワイヤのそれぞれの一部は、前記第1ワイヤ接続部より前記第1半導体チップの前記第1主面における前記第1主面辺側に配置されており、

前記複数の第2ワイヤのそれぞれは、前記配線基板の前記複数の端子のそれぞれと接続される第2ワイヤ接続部を有し、

前記複数の第2ワイヤのそれぞれは、前記第2ワイヤ接続部より前記配線基板の前記上面における前記上面辺側に配置される部分を有していないことを特徴とする半導体装置。

【請求項1】

以下の工程を含むことを特徴とする半導体装置の製造方法:

(a)平面形状が矩形状から成る上面、前記上面とは反対側の下面、及び前記上面の上

面辺に沿うように、前記上面に配置された複数の端子を有する配線基板を準備する工程;

(b)平面形状が矩形状から成る第1主面、前記第1主面とは反対側の第1裏面、及び前記第1主面の第1主面辺に沿うように、前記第1主面に配置された複数の第1パッドを有する第1半導体チップを、前記複数の端子から成る端子列よりも前記配線基板の内側に位置し、かつ前記第1裏面が前記配線基板の前記上面と対向するように、前記配線基板の前記上面に搭載する工程;

(c)平面形状が矩形状から成る第2主面、前記第2主面とは反対側の第2裏面、及び前記第2主面の第2主面辺に沿うように、前記第2主面に配置された複数の第2パッドを有する第2半導体チップを、前記複数の第1パッドから成る端子列よりも前記第1半導体チップの内側に位置し、かつ前記第2裏面が前記第1半導体チップの前記第1主面と対向するように、前記第1半導体チップの前記第1主面に積層する工程;

(d)前記第2半導体チップの前記複数の第2パッドと前記第1半導体チップの前記複数の第1パッドとを複数の第1ワイヤを介して、前記第2半導体チップの前記複数の第2パッドと前記配線基板の前記複数の端子とを複数の第2ワイヤを介して、それぞれ電気的に接続する工程;

(e)前記第1半導体チップ、前記第2半導体チップ、前記複数の第1ワイヤ及び前記複数の第2ワイヤを樹脂で封止することで、前記第2半導体チップの前記第2主面側に位置する表面を有する封止体を形成する工程;

ここで、

前記複数の第1ワイヤのそれぞれは、前記第1ワイヤの第1部分を前記第1半導体チップの前記第1パッドと接続してから、前記第1ワイヤの前記第1部分とは異なる第2部分を前記第2半導体チップの前記第2パッドと接続することで、形成され、

前記複数の第1ワイヤのそれぞれは、前記複数の第1ワイヤのそれぞれの一部が、前記第1ワイヤの前記第1部分より前記第1半導体チップの前記第1主面における前記第1主面辺側に位置するように、形成され、

前記複数の第2ワイヤのそれぞれは、前記複数の第2ワイヤのそれぞれが、前記第2ワイヤのうちの前記配線基板の前記端子と接続される部分より前記配線基板の前記上面における前記上面辺側に配置される部分を有さないように、形成される。

【請求項2】

請求項1記載の半導体装置の製造方法において、

前記(d)工程では、超音波を併用したキャピラリを用いて行うことを特徴とする半導体装置の製造方法。

【請求項3】

平面形状が矩形状から成る上面、前記上面とは反対側の下面、及び前記上面の上面辺に沿うように、前記上面に配置された複数の端子を有する配線基板と、

平面形状が矩形状から成る第1主面、前記第1主面とは反対側の第1裏面、及び前記第1主面の第1主面辺に沿うように、前記第1主面に配置された複数の第1パッドを有し、前記複数の端子から成る端子列よりも前記配線基板の内側に位置し、かつ前記第1裏面が前記配線基板の前記上面と対向するように、前記配線基板の前記上面に搭載された第1半導体チップと、

平面形状が矩形状から成る第2主面、前記第2主面とは反対側の第2裏面、及び前記第2主面の第2主面辺に沿うように、前記第2主面に配置された複数の第2パッドを有し、前記複数の第1パッドから成る端子列よりも前記第1半導体チップの内側に位置し、かつ前記第2裏面が前記第1半導体チップの前記第1主面と対向するように、前記第1半導体チップの前記第1主面に積層された第2半導体チップと、

前記第2半導体チップの前記複数の第2パッドと前記第1半導体チップの前記複数の第1パッドとをそれぞれ電気的に接続する複数の第1ワイヤと、

前記第2半導体チップの前記複数の第2パッドと前記配線基板の前記複数の端子とをそれぞれ電気的に接続する複数の第2ワイヤと、

前記第2半導体チップの前記第2主面側に位置する表面を有し、前記第1半導体チップ、前記第2半導体チップ、前記複数の第1ワイヤ及び前記複数の第2ワイヤを封止する封止体と、

を含み、

前記複数の第1ワイヤのそれぞれは、前記第1半導体チップの前記複数の第1パッドのそれぞれと接続される第1ワイヤ接続部を有し、

前記複数の第1ワイヤのそれぞれの一部は、前記第1ワイヤ接続部より前記第1半導体チップの前記第1主面における前記第1主面辺側に配置されており、

前記複数の第2ワイヤのそれぞれは、前記配線基板の前記複数の端子のそれぞれと接続される第2ワイヤ接続部を有し、

前記複数の第2ワイヤのそれぞれは、前記第2ワイヤ接続部より前記配線基板の前記上面における前記上面辺側に配置される部分を有していないことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【公開番号】特開2011−249838(P2011−249838A)

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願番号】特願2011−170871(P2011−170871)

【出願日】平成23年8月4日(2011.8.4)

【分割の表示】特願2006−1027(P2006−1027)の分割

【原出願日】平成18年1月6日(2006.1.6)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【分割の表示】特願2006−1027(P2006−1027)の分割

【原出願日】平成18年1月6日(2006.1.6)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]