半導体装置及びその製造方法

【課題】絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において接続信頼性を向上させる。

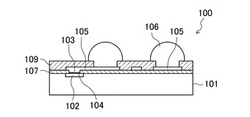

【解決手段】半導体素子101の一面上に電極部102が配置されている。電極部102を除いて半導体素子101の一面を覆うように絶縁層107が形成されている。電極部102と電気的に接続する導電性突起体103を有する配線105が絶縁層107上に形成されている。導電性突起体103と電極部102との間に、錫及び銅を含む合金層104が介在している。

【解決手段】半導体素子101の一面上に電極部102が配置されている。電極部102を除いて半導体素子101の一面を覆うように絶縁層107が形成されている。電極部102と電気的に接続する導電性突起体103を有する配線105が絶縁層107上に形成されている。導電性突起体103と電極部102との間に、錫及び銅を含む合金層104が介在している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

近年、情報通信機器や事務用電子機器の小型化及び高機能化に伴い、これらの機器に使用される半導体装置に対しては、小型化、薄型化、高密度化及び多端子化が要求されている。そのため、小型軽量多端子パッケージとして各種のCSP(Chip Scale Package:チップスケールパッケージ)が開発されている。

【0003】

特に、WL−CSP(ウエハレベルCSP)は、半導体素子の電極部と外部電極端子とを接続する金属配線をウエハ上に形成し、半導体装置の製造工程における最終段階でウエハを個々のパッケージごとに分離する技術であり、ベアチップと同等なサイズの極めて小型の半導体装置を実現する技術として注目されている。

【0004】

従来のWL−CSPは、別工程で銅箔上に作成した導電性突起体を、絶縁樹脂層中を貫通させて直接に半導体素子と積層させ、導電性突起体と半導体素子の電極部とを圧接接合することにより両者の電気的接続を行ったものである。ここで、銅箔と、絶縁性基体と、絶縁性基体を貫通して形成された複数の導電性突起体とを用いた構成であるB2 it法(ビー・スクェア・イット法:登録商標Buried−Bump−Interconnection Technology(株式会社東芝))が用いられている。

【0005】

以下、従来技術について図面を参照して説明する。

【0006】

図7は従来例に係る半導体装置の構成を示す断面図である。また、図8(a)〜(e)は、従来例に係る半導体装置の製造方法の各工程を示す断面図であり、図8(a)は、導電性突起体を有する金属箔を準備する工程を説明する断面図であり、図8(b)は、導電性突起体が絶縁樹脂層を貫通するように金属箔と絶縁樹脂層とを一体化する工程を説明する断面図であり、図8(c)は、絶縁樹脂層と一体化した導電性突起体と、半導体素子の素子電極とを対向させて絶縁樹脂層と半導体素子とを貼り合わせる工程を説明する断面図であり、図8(d)は、金属箔を所定のパターンの金属ランドに加工する工程を説明する断面図であり、図8(e)は、金属ランド上にはんだボールを形成する工程を説明する断面図である。

【0007】

図7に示すように、従来のWL−CSP9は、接続端子となる複数の素子電極2が表面に形成された半導体素子1と、各素子電極2を除いて半導体素子1を覆う絶縁樹脂層7と、半導体素子1上の各素子電極2と接続する複数の導電性突起体3と、各導電性突起体3の直上の金属ランドを覆って形成されたはんだボ−ル6とを備えている。ここで、WL−CSP9が設けられるウエハには半導体素子1が複数設けられている。また、導電性突起体3及び絶縁樹脂層7は前述のB2 it法によって形成されたものである。

【0008】

WL−CSP9の具体的な製造方法は次の通りである。

【0009】

まず、図8(a)に示すように、銅箔等の導電性金属箔5の一面上に、銀粒子等の導電性粉末、エポキシ樹脂等の樹脂及び溶剤を成分とする導電性ペーストを塗布した後に乾燥させることにより、円錐形状の導電性突起体3を形成する。

【0010】

次に、図8(b)に示すように、導電性突起体3が半硬化状の絶縁樹脂層7を貫通して導電性突起体3の頂部が絶縁樹脂層7から突出するように、導電性金属箔5と絶縁樹脂層7とを一体化する。その後、図8(c)に示すように、素子電極2を設けた半導体素子1を有するウエハと、導電性突起体3を設けた絶縁樹脂層7とを位置合わせし、積層プレスすることにより、導電性突起体3の頂部と、ウエハ上の接続端子である素子電極2とを直接圧接接合させる。この圧接接合により、絶縁樹脂層7から突出した導電性突起体3の頂部がつぶれ、導電性突起体3は円錐台形状となる。

【0011】

次に、図8(d)に示すように、導電性金属箔5をパターニングして、導電性突起体3と接続する金属ランド8を形成した後、図8(e)に示すように、金属ランド8を覆うようにはんだボ−ル6を形成する。

【0012】

尚、絶縁樹脂層7の厚さは任意に設定できるが、導電性突起体3が貫通できるようにすると共に絶縁性を確保するために、0.06〜0.1mmの厚さに設定する。また、端子ピッチは120μm以上に設定する。また、導電性突起体3の高さについては、絶縁樹脂層7を貫通する必要があることから、少なくとも使用する絶縁樹脂層7の厚さよりも大きく且つ素子電極2と圧接接合するのに必要十分な高さに設定する。さらに、導電性突起体3を形成する銅箔等の導電性金属箔5の厚さも任意に設定できるが、一般的な銅箔等の厚さである18μmに設定しても問題無い。

【0013】

以上に説明した半導体装置としては、例えば特許文献1に開示されている半導体装置が知られている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2004−193297号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

しかしながら、特許文献1に開示された構成に代表されるような従来の半導体装置には、次のような2つの問題点があると考えられる。

【0016】

第1の問題点は、導電性突起体3と素子電極2との接続信頼性の低下である。具体的には、導電性突起体3と素子電極2とを接続する圧接接合技術においては、接合材料や絶縁樹脂層材料が持つ物性により接合状態が変わり、中でも特に材料間の熱膨張係数の差は接合状態に大きい影響を及ぼすため、繰り返し熱応力を受けることによって接合界面に断線が生じるという不具合が起こる場合があることが報告されている。また、プリント基板への2次実装が完了した実装体において、熱的及び機械的な外力を受けた際のプリント基板の変形により半導体装置内部の接合界面にオープン不良が生じることも報告されている。

【0017】

第2の問題点は、素子電極の破壊ダメージである。具体的には、絶縁樹脂層7への貫通性を向上させるために、特許文献1に開示された構成においては導電性突起体3の先端を尖らせているので、導電性突起体3の頂部を半導体素子1の素子電極2に圧着させた際に、半導体素子1の素子電極2に圧力が集中し、素子電極2がダメージを受けて破壊されるおそれがある。特に、近年の配線ルールの縮小化やチップサイズのシュリンク化に伴って、配線層の薄化や配線層間絶縁膜の脆弱化が進んできているため、素子電極2の取り扱いが難しくなってきているので、実装が困難になってきている。

【0018】

本発明は、以上のような従来技術における問題点を解決するためになされたものであって、その目的は、高い接続信頼性を有し且つ実装しやすい半導体装置を提供することにある。

【課題を解決するための手段】

【0019】

前記の目的を達成するために、本発明に係る第1の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層が介在している。

【0020】

本発明に係る第1の半導体装置によると、半導体素子の電極部と、電極部上に設けられる導電性突起体との間に、錫及び銅を含む合金層が介在しているため、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫及び銅を含む合金層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0021】

本発明に係る第2の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体における少なくとも前記電極部と対向する表面部には銅含有層が形成されており、前記電極部における前記導電性突起体と対向する面上には錫含有層が形成されている。

【0022】

本発明に係る第2の半導体装置によると、半導体素子の電極部における導電性突起体と対向する面上には錫含有層が形成されていると共に、導電性突起体における電極部と対向する表面部には銅含有層が形成されているため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫含有層及び銅含有層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0023】

本発明に係る第3の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体における少なくとも前記電極部と対向する表面部には錫含有層が形成されており、前記電極部における前記導電性突起体と対向する面上には銅含有層が形成されている。

【0024】

本発明に係る第3の半導体装置によると、半導体素子の電極部における導電性突起体と対向する面上には銅含有層が形成されていると共に、導電性突起体における電極部と対向する表面部には錫含有層が形成されているため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、銅含有層及び錫含有層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0025】

本発明に係る第1の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記ウエハにおける前記電極部の配置面側に、前記電極部と対向するように導電性突起体を準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備え、前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層を形成する工程をさらに備えている。

【0026】

本発明に係る第1の半導体装置の製造方法によると、半導体素子の電極部と、電極上に設けられる導電性突起体との間に、錫及び銅を含む合金層を形成するため、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0027】

本発明に係る第1の半導体装置の製造方法において、前記合金層を形成するための加熱を、前記外部端子を形成する際のリフロー加熱工程で実施してもよい。このようにすると、半導体素子の電極部への局地的な圧接によるストレスが解放されるため、内部応力に起因する電極部へのダメージを緩和できると共に半導体素子の反りも緩和できる。

【0028】

本発明に係る第1の半導体装置の製造方法において、前記ウエハが分割されてなる半導体装置をプリント基板上に実装する工程をさらに備え、前記合金層を形成するための加熱を、前記半導体装置を前記プリント基板上に実装する際のリフロー加熱工程で実施してもよい。このようにすると、半導体素子の電極部への局地的な圧接によるストレスが解放されるため、内部応力に起因する電極部へのダメージを緩和できると共に半導体素子の反りも緩和できる。

【0029】

本発明に係る第2の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記電極部の表面上に錫含有層を形成する工程と、前記ウエハにおける前記電極部の配置面側に、銅含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備えている。

【0030】

本発明に係る第2の半導体装置の製造方法によると、銅含有層を表面部に有する導電性突起体と対向する半導体素子の電極部上に錫含有層を形成するため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫含有層及び銅含有層が介在するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0031】

本発明に係る第3の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記電極部の表面上に銅含有層を形成する工程と、前記ウエハにおける前記電極部の配置面側に、錫含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備えている。

【0032】

本発明に係る第3の半導体装置の製造方法によると、錫含有層を表面部に有する導電性突起体と対向する半導体素子の電極部上に銅含有層を形成するため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、銅含有層及び錫含有層が介在するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0033】

本発明に係る第2又は第3の半導体装置の製造方法において、前記錫含有層は、めっき法により形成されてもよいし、又は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されてもよい。

【0034】

本発明に係る第2又は第3の半導体装置の製造方法において、前記銅含有層は、めっき法により形成されてもよいし、又は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されてもよい。

【発明の効果】

【0035】

本発明によれば、絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において、接続信頼性を向上させることができると共に、電極部へのダメージを緩和して実装を簡単化することができる。

【図面の簡単な説明】

【0036】

【図1】図1は本発明の一実施形態に係る半導体装置の構成を示す断面図である。

【図2】図2は本発明の一実施形態に係る半導体装置の構成を示す斜視図である。

【図3】図3(a)〜(d)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図3(a)は、素子電極が形成されたウエハを準備する工程を説明する断面図であり、図3(b)は、半導体素子の裏面を研磨する工程を説明する断面図であり、図3(c)は、半導体素子の表面上に絶縁樹脂層を形成する工程を説明する断面図であり、図3(d)は、素子電極上にSn含有層を形成する工程を説明する断面図である。

【図4】図4(a)及び(b)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図4(a)は、導電性突起体を有する金属層及び絶縁樹脂層を準備する工程を説明する断面図であり、図4(b)は、導電性突起体が絶縁樹脂層を貫通するように金属層と絶縁樹脂層とを一体化する工程を説明する断面図である。

【図5】図5(a)〜(d)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図5(a)は、絶縁樹脂層と一体化した導電性突起体と、別の絶縁樹脂層と一体化した半導体素子とを対向させる工程を説明する断面図であり、図5(b)は、開口部を通じて導電性突起体と素子電極とを接触させると共に金属層を金属配線に加工する工程を説明する断面図であり、図5(c)は、金属配線のうちはんだボール形成領域を除く領域を絶縁樹脂層によって覆う工程を説明する断面図であり、図5(d)は、絶縁樹脂層が開口されている金属配線上にはんだボールを形成する工程を説明する断面図である。

【図6】図6は、本発明の一実施形態に係る半導体装置が複数設けられたウエハをダイシングブレードを用いて各半導体装置ごとに分割する工程を説明する斜視図である。

【図7】図7は従来例に係る半導体装置の構成を示す断面図である。

【図8】図8(a)〜(e)は、従来例に係る半導体装置の製造方法の各工程を示す図であり、図8(a)は、導電性突起体を有する金属箔を準備する工程を説明する断面図であり、図8(b)は、導電性突起体が絶縁樹脂層を貫通するように金属箔と絶縁樹脂層とを一体化する工程を説明する断面図であり、図8(c)は、絶縁樹脂層と一体化した導電性突起体と、半導体素子の素子電極とを対向させて絶縁樹脂層と半導体素子とを貼り合わせる工程を説明する断面図であり、図8(d)は、金属箔を所定のパターンの金属ランドに加工する工程を説明する断面図であり、図8(e)は、金属ランド上にはんだボールを形成する工程を説明する断面図である。

【発明を実施するための形態】

【0037】

(実施形態)

以下、本発明の一実施形態に係る半導体装置及びその製造方法について、WL−CSP(ウェハレベルCSP)を例として、図面を参照しながら説明する。尚、各図において、同等の構成要素については同じ符号を用いることにより、重複する説明を省略する場合がある。

【0038】

図1及び図2はそれぞれ、本実施形態に係る半導体装置の構成を示す断面図及び斜視図である。ここで、図1は、図2のA−A’線における断面図である。また、図2では、半導体装置を構成する絶縁樹脂層等の一部を切り欠くことによって装置内部を部分的に露出させた状態を示している。

【0039】

図1及び図2に示すように、本実施形態の半導体装置100は、例えば直方体形状をした半導体素子101を有している。半導体素子101の表面上には複数の素子電極102が配置されている。また、半導体素子101の表面は保護膜(図示省略)によって覆われている。当該保護膜には半導体素子101の周縁に沿って複数の開口が形成されており、各開口から各素子電極102が露出している。

【0040】

また、図1及び図2に示すように、本実施形態の半導体装置100においては、半導体素子101上に設けられた素子電極102と、素子電極102に対向する位置に設けられた導電性突起体103とは、SnCu合金層104により接続されている。ここで、半導体素子101は、例えば集積回路などの半導体チップであり、その表面は、例えばポリイミド層からなる図示しない保護層によって覆われている。また、導電性突起体103は金属配線105の一部として形成されている。また、金属配線105上には、プリント基板実装をするための外部電極端子として、いわゆるはんだボール106が形成されている。金属配線105と半導体素子101との間には絶縁樹脂層107が設けられており、絶縁樹脂層107の一方の面は金属配線105と圧着しており、絶縁樹脂層107の他方の面は半導体素子101と圧着している。具体的には、半導体素子101は、素子電極102が設けられた電極面を絶縁樹脂層側に向けて絶縁樹脂層107に圧着されている。また、絶縁樹脂層107は素子電極102上に開口を有している。尚、絶縁樹脂層107の材料として、例えばエポキシ系熱硬化型樹脂等を用いてもよい。また、絶縁樹脂層107上及び金属配線105上には、外部電極端子(はんだボール106)形成領域が開口された絶縁樹脂層109が形成されている。

【0041】

次に、本実施形態の半導体装置の製造方法について、図面を参照しながら説明する。図3(a)〜(d)、図4(a)、(b)及び図5(a)〜(d)は、本実施形態の半導体装置の製造方法の各工程を示す、図2に示す半導体装置100のA−A’線に沿った断面図である。詳しくは、図3(a)は、素子電極が形成されたウエハを準備する工程を説明する断面図であり、図3(b)は、半導体素子の裏面を研磨する工程を説明する断面図であり、図3(c)は、半導体素子の表面上に絶縁樹脂層を形成する工程を説明する断面図であり、図3(d)は、素子電極上にSn含有層を形成する工程を説明する断面図である。また、図4(a)は、導電性突起体を有する金属層及び絶縁樹脂層を準備する工程を説明する断面図であり、図4(b)は、導電性突起体が絶縁樹脂層を貫通するように金属層と絶縁樹脂層とを一体化する工程を説明する断面図である。また、図5(a)は、絶縁樹脂層と一体化した導電性突起体と、別の絶縁樹脂層と一体化した半導体素子とを対向させる工程を説明する断面図であり、図5(b)は、開口部を通じて導電性突起体と素子電極とを接触させると共に金属層を金属配線に加工する工程を説明する断面図であり、図5(c)は、金属配線のうちはんだボール形成領域を除く領域を絶縁樹脂層によって覆う工程を説明する断面図であり、図5(d)は、絶縁樹脂層が開口されている金属配線上にはんだボールを形成する工程を説明する断面図である。

【0042】

まず、図3(a)に示すように、複数の半導体素子101を有するウエハを準備する。ここで、各半導体素子101の表面には、外部と電気的接続を行うための複数の素子電極102が配置されている。

【0043】

次に、図3(b)に示すとおり、各半導体素子101の裏面を研磨することにより、各半導体素子101の厚さを所定の厚さにする。各半導体素子101の厚さは、通常の場合、例えば350μm〜500μm程度であり、薄型化する場合、例えば100μm〜350μm程度とすることが好ましい。図示は省略しているが、各半導体素子101の裏面に、例えば電解めっき法又はスパッタリング法などにより、例えば銅や銀を主成分とする厚さ数μm程度から数十μm程度までの金属膜を形成してもよい。

【0044】

次に、図3(c)に示すように、各半導体素子101の表面(素子電極102の配置面:以下同じ)上に、例えば感光性の絶縁性樹脂を塗布して絶縁樹脂層107Aを形成した後、フォトリソグラフィ法を用いてパターン露光及び現像を順次行うことにより、各素子電極102が露出するように絶縁樹脂層107Aに複数の開口部110を形成する。ここで、絶縁樹脂層107Aの材料として、例えばポリイミドを用いてもよい。また、絶縁樹脂層107Aの厚さについては、フォトリソグラフィ法による露光性及び現像性を向上させる観点から例えば5μm〜50μm程度とすることが好ましく、約10μm程度とすることがより好ましい。

【0045】

尚、本実施形態において、コスト削減や工程数削減を目的として、絶縁樹脂層107Aの形成を省いてもよい。その場合、後述する絶縁樹脂層107Bにより同等の絶縁効果を得ることができる。

【0046】

次に、図3(d)に示すとおり、各素子電極102の上に、例えばめっき法などにより、Sn含有金属層111を形成する。Sn含有金属層111はSnのみから構成されていてもよいし、又はSnを主成分とする合金から構成されていてもよい。尚、Sn含有金属層111の形成方法として、めっき法に代えて、例えば、Snを主体とするペーストを印刷法などにより素子電極102上に塗布した後にリフロー加熱を行うことによって厚いSn含有層を形成できるプリコーティング法を用いてもよい。

【0047】

次に、図4(a)に示すように、導電性突起体103を有する金属層105A、及び絶縁樹脂層107Bを準備した後、図4(b)に示すように、導電性突起体103が絶縁樹脂層107Bを貫通するように、金属層105Aと絶縁樹脂層107Bとを一体化する。具体的には、絶縁樹脂層107Bを貫通した導電性突起体103の頂部は絶縁樹脂層107Bから突出して露出している。ここで、導電性突起体103の全体的な形状は、先端(頂部)に近づくにつれて細くなっている。これにより、絶縁樹脂層107Bに対する導電性突起体103の貫通性が向上する。また、導電性突起体103は、例えば導電性材料又は圧延金属などから構成されており、その表面には、例えば電解めっき法又は無電解めっき法により、銅層又は銅を主体とする合金層が設けられている。尚、導電性突起体103自体がCuから構成されている場合には、前述のめっき処理は省略可能であり、導電性突起体103の表面に防錆処理を施しておけばよい。また、導電性突起体103の高さは、絶縁樹脂層107Bの厚さと比べて同等又は高くなっている。これにより、後述する素子電極102への導電性突起体103の接合を確実に行うことが可能となる。

【0048】

次に、図5(a)に示すように、絶縁樹脂層107Bと一体化した導電性突起体103と、絶縁樹脂層107Aと一体化した半導体素子101上の素子電極102とを対向させた後、図5(b)に示すように、絶縁樹脂層107Aと絶縁樹脂層107Bとを貼り合わせる。ここで、絶縁樹脂層107Aの開口部110を通じて導電性突起体103と素子電極102とが電気的に接続される。

【0049】

本実施形態では、素子電極102と導電性突起体103との接続に際して、素子電極102上に比較的柔らかいSn含有金属層111が形成されているため、仮に導電性突起体103の先端が鋭利な形状であったとしても、導電性突起体103の素子電極102への接触時のダメージを軽減することができる。また、導電性突起体103に高さバラツキがあったとしても、素子電極102の一部が局地的に大きなダメージを受ける事態をSn含有金属層111によって回避することができる。

【0050】

尚、以下の説明では、絶縁樹脂層107A及び絶縁樹脂層107Bの積層体を単に絶縁樹脂層107と称するが、前述のように、絶縁樹脂層107A及び絶縁樹脂層107Bのいずれか一方を、コストや製造工程数の削減のために省略してもよい。

【0051】

続いて、図5(b)に示すように、金属層105Aを金属配線105に加工する。ここで、各金属配線105における各素子電極102と反対側の一端には、略円形状をした金属ランドが配置される。この金属ランドは半導体素子101の表面上にマトリックス状に複数配置される。

【0052】

次に、図5(c)に示すように、前記各金属ランドを含む各金属配線105を覆うように絶縁樹脂層109を形成した後、当該各金属ランドが露出するように絶縁樹脂層109に複数の開口部をマトリックス状に形成する。

【0053】

次に、図5(d)に示すように、前記各金属ランド上にはんだボール106を形成する。はんだボール106の形成方法としては、色々な方法が考えられるが、例えば金属ランド上にフラックスを塗布した後にはんだボール106を搭載してリフロー加熱によりはんだボール106を一旦溶融させる方法、又は、金属ランド上にフラックス入りはんだ粉末(いわゆるはんだペースト)を塗布した後にリフロー加熱によりはんだ粉末を一旦溶融させ、その後、凝固させることによってはんだボール106を形成する方法等を用いてもよい。いずれの方法を用いた場合においても、リフロー加熱を行う際に、導電性突起体103上に設けられたCu含有層中のCu成分と、素子電極102上に設けられたSn含有金属層111中のSn成分とによって、SnCu合金層104が形成される結果、導電性突起体103と素子電極102との間に強固な接続信頼性が得られる。ここで、SnCu合金層104の厚さは約1μm程度までが良い。その理由は、SnCu合金層104の厚さが1μmを大きく超えた場合、機械的な衝撃などによりSnCu合金層104が破壊されるおそれがあるためである。また、前述のリフロー加熱を行うことにより、素子電極102への局地的な圧接によるストレスが解放されるため、内部応力に起因する素子電極102へのダメージを緩和できると同時に半導体素子101の反りも緩和できるという相乗効果が得られる。ここで、リフロー加熱の温度は、はんだボール106の金属物性としての液相温度を超える温度であり、近年の環境問題を鑑みた鉛フリーはんだ組成であれば220〜250℃が一般的である。また、はんだボール106の形成に伴うリフロー加熱に代えて、プリント基板への2次実装工程におけるリフロー加熱を利用することも可能である。この場合には、加熱回数が1回で済むという利点がある。

【0054】

尚、半導体装置の製造工程においては、通常、さまざまな温度の熱負荷が加えられる。実際、本実施形態においても、SnCu合金層104を形成するための加熱工程が必要となるが、仮に半導体装置の製造工程においてSnCu合金層104の形成に必要な熱が加えられなかったとしても、前述のように、プリント基板実装でのリフロー加熱を利用することができるため、高温加熱に対する耐性が弱い半導体装置に対しては、本実施形態は非常に有効となる。

【0055】

最後に、以上に述べた各工程が実施されたウエハをチップ(半導体装置100)毎に分割する。図6は、本実施形態の半導体装置100が複数設けられたウエハ10を、ウエハ10の表面に平行な軸の周りに回転するダイシングブレード112を用いて半導体装置100毎に分割する工程を説明する斜視図である。図6に示すように、各半導体装置100上に複数の外部電極端子つまりはんだボール106がマトリックス状に配置されており、ウエハ10を半導体装置100毎に分離することによって、図1に示す個片の半導体装置100を得ることができる。

【0056】

以上に説明した本実施形態によると、半導体素子101の素子電極102と、素子電極102上に設けられる導電性突起体103との間に、SnCu合金層104を形成するため、素子電極102と導電性突起体103との接続を強固にできるので、接続信頼性を向上させることができる。また、素子電極102と導電性突起体103との間に、SnCu合金層104を形成するため、仮に導電性突起体103の先端が鋭利な形状であったとしても、素子電極102と導電性突起体103とを接続する際の素子電極102へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0057】

尚、本実施形態において、導電性突起体103上に設けられたCu含有層中のCu成分と、素子電極102上に設けられたSn含有金属層111中のSn成分とによって、SnCu合金層104を形成したときに、当該Cu含有層の一部及び当該Sn含有金属層111の一部が残存してもよい。

【0058】

また、本実施形態において、Cu含有層を少なくとも表面部に有する導電性突起体103と対向する半導体素子101の素子電極102上にSn含有金属層111を形成することにより、SnCu合金層104を形成した。しかし、これに代えて、Sn含有層を少なくとも表面部に有する導電性突起体103と対向する半導体素子101の素子電極102上にCu含有層を形成することにより、SnCu合金層104を形成してもよい。この場合、素子電極102上にCu含有層を例えばめっき法により形成してもよい。或いは、めっき法に代えて、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法を用いてもよい。また、SnCu合金層104の形成後に、当該Sn含有層の一部及び当該Cu含有層の一部が残存してもよい。

【産業上の利用可能性】

【0059】

本発明は、絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において、接続信頼性の向上及び電極部へのダメージの緩和を可能とするものであり、接続信頼性が向上したWL−CSP等の実装を容易に行う上で有用である。

【符号の説明】

【0060】

1 半導体素子

2 素子電極

3 導電性突起体

5 導電性金属箔

6 はんだボ−ル

7 絶縁樹脂層

8 金属ランド

9 WL−CSP

10 ウエハ

100 半導体装

101 半導体素子

102 素子電極

103 導電性突起体

104 SnCu合金層

105 金属配線

105A 金属層

106 はんだボール

107、107A、107B 絶縁樹脂層

109 絶縁樹脂層

110 開口部

111 Sn含有合金層

112 ダイシングブレード

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

近年、情報通信機器や事務用電子機器の小型化及び高機能化に伴い、これらの機器に使用される半導体装置に対しては、小型化、薄型化、高密度化及び多端子化が要求されている。そのため、小型軽量多端子パッケージとして各種のCSP(Chip Scale Package:チップスケールパッケージ)が開発されている。

【0003】

特に、WL−CSP(ウエハレベルCSP)は、半導体素子の電極部と外部電極端子とを接続する金属配線をウエハ上に形成し、半導体装置の製造工程における最終段階でウエハを個々のパッケージごとに分離する技術であり、ベアチップと同等なサイズの極めて小型の半導体装置を実現する技術として注目されている。

【0004】

従来のWL−CSPは、別工程で銅箔上に作成した導電性突起体を、絶縁樹脂層中を貫通させて直接に半導体素子と積層させ、導電性突起体と半導体素子の電極部とを圧接接合することにより両者の電気的接続を行ったものである。ここで、銅箔と、絶縁性基体と、絶縁性基体を貫通して形成された複数の導電性突起体とを用いた構成であるB2 it法(ビー・スクェア・イット法:登録商標Buried−Bump−Interconnection Technology(株式会社東芝))が用いられている。

【0005】

以下、従来技術について図面を参照して説明する。

【0006】

図7は従来例に係る半導体装置の構成を示す断面図である。また、図8(a)〜(e)は、従来例に係る半導体装置の製造方法の各工程を示す断面図であり、図8(a)は、導電性突起体を有する金属箔を準備する工程を説明する断面図であり、図8(b)は、導電性突起体が絶縁樹脂層を貫通するように金属箔と絶縁樹脂層とを一体化する工程を説明する断面図であり、図8(c)は、絶縁樹脂層と一体化した導電性突起体と、半導体素子の素子電極とを対向させて絶縁樹脂層と半導体素子とを貼り合わせる工程を説明する断面図であり、図8(d)は、金属箔を所定のパターンの金属ランドに加工する工程を説明する断面図であり、図8(e)は、金属ランド上にはんだボールを形成する工程を説明する断面図である。

【0007】

図7に示すように、従来のWL−CSP9は、接続端子となる複数の素子電極2が表面に形成された半導体素子1と、各素子電極2を除いて半導体素子1を覆う絶縁樹脂層7と、半導体素子1上の各素子電極2と接続する複数の導電性突起体3と、各導電性突起体3の直上の金属ランドを覆って形成されたはんだボ−ル6とを備えている。ここで、WL−CSP9が設けられるウエハには半導体素子1が複数設けられている。また、導電性突起体3及び絶縁樹脂層7は前述のB2 it法によって形成されたものである。

【0008】

WL−CSP9の具体的な製造方法は次の通りである。

【0009】

まず、図8(a)に示すように、銅箔等の導電性金属箔5の一面上に、銀粒子等の導電性粉末、エポキシ樹脂等の樹脂及び溶剤を成分とする導電性ペーストを塗布した後に乾燥させることにより、円錐形状の導電性突起体3を形成する。

【0010】

次に、図8(b)に示すように、導電性突起体3が半硬化状の絶縁樹脂層7を貫通して導電性突起体3の頂部が絶縁樹脂層7から突出するように、導電性金属箔5と絶縁樹脂層7とを一体化する。その後、図8(c)に示すように、素子電極2を設けた半導体素子1を有するウエハと、導電性突起体3を設けた絶縁樹脂層7とを位置合わせし、積層プレスすることにより、導電性突起体3の頂部と、ウエハ上の接続端子である素子電極2とを直接圧接接合させる。この圧接接合により、絶縁樹脂層7から突出した導電性突起体3の頂部がつぶれ、導電性突起体3は円錐台形状となる。

【0011】

次に、図8(d)に示すように、導電性金属箔5をパターニングして、導電性突起体3と接続する金属ランド8を形成した後、図8(e)に示すように、金属ランド8を覆うようにはんだボ−ル6を形成する。

【0012】

尚、絶縁樹脂層7の厚さは任意に設定できるが、導電性突起体3が貫通できるようにすると共に絶縁性を確保するために、0.06〜0.1mmの厚さに設定する。また、端子ピッチは120μm以上に設定する。また、導電性突起体3の高さについては、絶縁樹脂層7を貫通する必要があることから、少なくとも使用する絶縁樹脂層7の厚さよりも大きく且つ素子電極2と圧接接合するのに必要十分な高さに設定する。さらに、導電性突起体3を形成する銅箔等の導電性金属箔5の厚さも任意に設定できるが、一般的な銅箔等の厚さである18μmに設定しても問題無い。

【0013】

以上に説明した半導体装置としては、例えば特許文献1に開示されている半導体装置が知られている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2004−193297号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

しかしながら、特許文献1に開示された構成に代表されるような従来の半導体装置には、次のような2つの問題点があると考えられる。

【0016】

第1の問題点は、導電性突起体3と素子電極2との接続信頼性の低下である。具体的には、導電性突起体3と素子電極2とを接続する圧接接合技術においては、接合材料や絶縁樹脂層材料が持つ物性により接合状態が変わり、中でも特に材料間の熱膨張係数の差は接合状態に大きい影響を及ぼすため、繰り返し熱応力を受けることによって接合界面に断線が生じるという不具合が起こる場合があることが報告されている。また、プリント基板への2次実装が完了した実装体において、熱的及び機械的な外力を受けた際のプリント基板の変形により半導体装置内部の接合界面にオープン不良が生じることも報告されている。

【0017】

第2の問題点は、素子電極の破壊ダメージである。具体的には、絶縁樹脂層7への貫通性を向上させるために、特許文献1に開示された構成においては導電性突起体3の先端を尖らせているので、導電性突起体3の頂部を半導体素子1の素子電極2に圧着させた際に、半導体素子1の素子電極2に圧力が集中し、素子電極2がダメージを受けて破壊されるおそれがある。特に、近年の配線ルールの縮小化やチップサイズのシュリンク化に伴って、配線層の薄化や配線層間絶縁膜の脆弱化が進んできているため、素子電極2の取り扱いが難しくなってきているので、実装が困難になってきている。

【0018】

本発明は、以上のような従来技術における問題点を解決するためになされたものであって、その目的は、高い接続信頼性を有し且つ実装しやすい半導体装置を提供することにある。

【課題を解決するための手段】

【0019】

前記の目的を達成するために、本発明に係る第1の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層が介在している。

【0020】

本発明に係る第1の半導体装置によると、半導体素子の電極部と、電極部上に設けられる導電性突起体との間に、錫及び銅を含む合金層が介在しているため、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫及び銅を含む合金層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0021】

本発明に係る第2の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体における少なくとも前記電極部と対向する表面部には銅含有層が形成されており、前記電極部における前記導電性突起体と対向する面上には錫含有層が形成されている。

【0022】

本発明に係る第2の半導体装置によると、半導体素子の電極部における導電性突起体と対向する面上には錫含有層が形成されていると共に、導電性突起体における電極部と対向する表面部には銅含有層が形成されているため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫含有層及び銅含有層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0023】

本発明に係る第3の半導体装置は、半導体素子と、前記半導体素子の一面上に配置された少なくとも1つの電極部と、前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、前記配線上に形成された外部端子とを備え、前記導電性突起体における少なくとも前記電極部と対向する表面部には錫含有層が形成されており、前記電極部における前記導電性突起体と対向する面上には銅含有層が形成されている。

【0024】

本発明に係る第3の半導体装置によると、半導体素子の電極部における導電性突起体と対向する面上には銅含有層が形成されていると共に、導電性突起体における電極部と対向する表面部には錫含有層が形成されているため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、銅含有層及び錫含有層が介在しているため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0025】

本発明に係る第1の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記ウエハにおける前記電極部の配置面側に、前記電極部と対向するように導電性突起体を準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備え、前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層を形成する工程をさらに備えている。

【0026】

本発明に係る第1の半導体装置の製造方法によると、半導体素子の電極部と、電極上に設けられる導電性突起体との間に、錫及び銅を含む合金層を形成するため、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0027】

本発明に係る第1の半導体装置の製造方法において、前記合金層を形成するための加熱を、前記外部端子を形成する際のリフロー加熱工程で実施してもよい。このようにすると、半導体素子の電極部への局地的な圧接によるストレスが解放されるため、内部応力に起因する電極部へのダメージを緩和できると共に半導体素子の反りも緩和できる。

【0028】

本発明に係る第1の半導体装置の製造方法において、前記ウエハが分割されてなる半導体装置をプリント基板上に実装する工程をさらに備え、前記合金層を形成するための加熱を、前記半導体装置を前記プリント基板上に実装する際のリフロー加熱工程で実施してもよい。このようにすると、半導体素子の電極部への局地的な圧接によるストレスが解放されるため、内部応力に起因する電極部へのダメージを緩和できると共に半導体素子の反りも緩和できる。

【0029】

本発明に係る第2の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記電極部の表面上に錫含有層を形成する工程と、前記ウエハにおける前記電極部の配置面側に、銅含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備えている。

【0030】

本発明に係る第2の半導体装置の製造方法によると、銅含有層を表面部に有する導電性突起体と対向する半導体素子の電極部上に錫含有層を形成するため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、錫含有層及び銅含有層が介在するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0031】

本発明に係る第3の半導体装置の製造方法は、少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、前記電極部の表面上に銅含有層を形成する工程と、前記ウエハにおける前記電極部の配置面側に、錫含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、前記配線上に外部端子を形成する工程と、前記ウエハを前記半導体素子毎に分割する工程とを備えている。

【0032】

本発明に係る第3の半導体装置の製造方法によると、錫含有層を表面部に有する導電性突起体と対向する半導体素子の電極部上に銅含有層を形成するため、電極部と導電性突起体との接続時に、電極部と導電性突起体との間に、錫及び銅を含む合金層を形成することができる。従って、電極部と導電性突起体との接続を強固にできるので、接続信頼性を向上させることができる。また、電極部と導電性突起体との間に、銅含有層及び錫含有層が介在するため、仮に導電性突起体の先端が鋭利な形状であったとしても、電極部と導電性突起体とを接続する際の電極部へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0033】

本発明に係る第2又は第3の半導体装置の製造方法において、前記錫含有層は、めっき法により形成されてもよいし、又は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されてもよい。

【0034】

本発明に係る第2又は第3の半導体装置の製造方法において、前記銅含有層は、めっき法により形成されてもよいし、又は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されてもよい。

【発明の効果】

【0035】

本発明によれば、絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において、接続信頼性を向上させることができると共に、電極部へのダメージを緩和して実装を簡単化することができる。

【図面の簡単な説明】

【0036】

【図1】図1は本発明の一実施形態に係る半導体装置の構成を示す断面図である。

【図2】図2は本発明の一実施形態に係る半導体装置の構成を示す斜視図である。

【図3】図3(a)〜(d)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図3(a)は、素子電極が形成されたウエハを準備する工程を説明する断面図であり、図3(b)は、半導体素子の裏面を研磨する工程を説明する断面図であり、図3(c)は、半導体素子の表面上に絶縁樹脂層を形成する工程を説明する断面図であり、図3(d)は、素子電極上にSn含有層を形成する工程を説明する断面図である。

【図4】図4(a)及び(b)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図4(a)は、導電性突起体を有する金属層及び絶縁樹脂層を準備する工程を説明する断面図であり、図4(b)は、導電性突起体が絶縁樹脂層を貫通するように金属層と絶縁樹脂層とを一体化する工程を説明する断面図である。

【図5】図5(a)〜(d)は本発明の一実施形態に係る半導体装置の製造方法の各工程を示す図であって、図5(a)は、絶縁樹脂層と一体化した導電性突起体と、別の絶縁樹脂層と一体化した半導体素子とを対向させる工程を説明する断面図であり、図5(b)は、開口部を通じて導電性突起体と素子電極とを接触させると共に金属層を金属配線に加工する工程を説明する断面図であり、図5(c)は、金属配線のうちはんだボール形成領域を除く領域を絶縁樹脂層によって覆う工程を説明する断面図であり、図5(d)は、絶縁樹脂層が開口されている金属配線上にはんだボールを形成する工程を説明する断面図である。

【図6】図6は、本発明の一実施形態に係る半導体装置が複数設けられたウエハをダイシングブレードを用いて各半導体装置ごとに分割する工程を説明する斜視図である。

【図7】図7は従来例に係る半導体装置の構成を示す断面図である。

【図8】図8(a)〜(e)は、従来例に係る半導体装置の製造方法の各工程を示す図であり、図8(a)は、導電性突起体を有する金属箔を準備する工程を説明する断面図であり、図8(b)は、導電性突起体が絶縁樹脂層を貫通するように金属箔と絶縁樹脂層とを一体化する工程を説明する断面図であり、図8(c)は、絶縁樹脂層と一体化した導電性突起体と、半導体素子の素子電極とを対向させて絶縁樹脂層と半導体素子とを貼り合わせる工程を説明する断面図であり、図8(d)は、金属箔を所定のパターンの金属ランドに加工する工程を説明する断面図であり、図8(e)は、金属ランド上にはんだボールを形成する工程を説明する断面図である。

【発明を実施するための形態】

【0037】

(実施形態)

以下、本発明の一実施形態に係る半導体装置及びその製造方法について、WL−CSP(ウェハレベルCSP)を例として、図面を参照しながら説明する。尚、各図において、同等の構成要素については同じ符号を用いることにより、重複する説明を省略する場合がある。

【0038】

図1及び図2はそれぞれ、本実施形態に係る半導体装置の構成を示す断面図及び斜視図である。ここで、図1は、図2のA−A’線における断面図である。また、図2では、半導体装置を構成する絶縁樹脂層等の一部を切り欠くことによって装置内部を部分的に露出させた状態を示している。

【0039】

図1及び図2に示すように、本実施形態の半導体装置100は、例えば直方体形状をした半導体素子101を有している。半導体素子101の表面上には複数の素子電極102が配置されている。また、半導体素子101の表面は保護膜(図示省略)によって覆われている。当該保護膜には半導体素子101の周縁に沿って複数の開口が形成されており、各開口から各素子電極102が露出している。

【0040】

また、図1及び図2に示すように、本実施形態の半導体装置100においては、半導体素子101上に設けられた素子電極102と、素子電極102に対向する位置に設けられた導電性突起体103とは、SnCu合金層104により接続されている。ここで、半導体素子101は、例えば集積回路などの半導体チップであり、その表面は、例えばポリイミド層からなる図示しない保護層によって覆われている。また、導電性突起体103は金属配線105の一部として形成されている。また、金属配線105上には、プリント基板実装をするための外部電極端子として、いわゆるはんだボール106が形成されている。金属配線105と半導体素子101との間には絶縁樹脂層107が設けられており、絶縁樹脂層107の一方の面は金属配線105と圧着しており、絶縁樹脂層107の他方の面は半導体素子101と圧着している。具体的には、半導体素子101は、素子電極102が設けられた電極面を絶縁樹脂層側に向けて絶縁樹脂層107に圧着されている。また、絶縁樹脂層107は素子電極102上に開口を有している。尚、絶縁樹脂層107の材料として、例えばエポキシ系熱硬化型樹脂等を用いてもよい。また、絶縁樹脂層107上及び金属配線105上には、外部電極端子(はんだボール106)形成領域が開口された絶縁樹脂層109が形成されている。

【0041】

次に、本実施形態の半導体装置の製造方法について、図面を参照しながら説明する。図3(a)〜(d)、図4(a)、(b)及び図5(a)〜(d)は、本実施形態の半導体装置の製造方法の各工程を示す、図2に示す半導体装置100のA−A’線に沿った断面図である。詳しくは、図3(a)は、素子電極が形成されたウエハを準備する工程を説明する断面図であり、図3(b)は、半導体素子の裏面を研磨する工程を説明する断面図であり、図3(c)は、半導体素子の表面上に絶縁樹脂層を形成する工程を説明する断面図であり、図3(d)は、素子電極上にSn含有層を形成する工程を説明する断面図である。また、図4(a)は、導電性突起体を有する金属層及び絶縁樹脂層を準備する工程を説明する断面図であり、図4(b)は、導電性突起体が絶縁樹脂層を貫通するように金属層と絶縁樹脂層とを一体化する工程を説明する断面図である。また、図5(a)は、絶縁樹脂層と一体化した導電性突起体と、別の絶縁樹脂層と一体化した半導体素子とを対向させる工程を説明する断面図であり、図5(b)は、開口部を通じて導電性突起体と素子電極とを接触させると共に金属層を金属配線に加工する工程を説明する断面図であり、図5(c)は、金属配線のうちはんだボール形成領域を除く領域を絶縁樹脂層によって覆う工程を説明する断面図であり、図5(d)は、絶縁樹脂層が開口されている金属配線上にはんだボールを形成する工程を説明する断面図である。

【0042】

まず、図3(a)に示すように、複数の半導体素子101を有するウエハを準備する。ここで、各半導体素子101の表面には、外部と電気的接続を行うための複数の素子電極102が配置されている。

【0043】

次に、図3(b)に示すとおり、各半導体素子101の裏面を研磨することにより、各半導体素子101の厚さを所定の厚さにする。各半導体素子101の厚さは、通常の場合、例えば350μm〜500μm程度であり、薄型化する場合、例えば100μm〜350μm程度とすることが好ましい。図示は省略しているが、各半導体素子101の裏面に、例えば電解めっき法又はスパッタリング法などにより、例えば銅や銀を主成分とする厚さ数μm程度から数十μm程度までの金属膜を形成してもよい。

【0044】

次に、図3(c)に示すように、各半導体素子101の表面(素子電極102の配置面:以下同じ)上に、例えば感光性の絶縁性樹脂を塗布して絶縁樹脂層107Aを形成した後、フォトリソグラフィ法を用いてパターン露光及び現像を順次行うことにより、各素子電極102が露出するように絶縁樹脂層107Aに複数の開口部110を形成する。ここで、絶縁樹脂層107Aの材料として、例えばポリイミドを用いてもよい。また、絶縁樹脂層107Aの厚さについては、フォトリソグラフィ法による露光性及び現像性を向上させる観点から例えば5μm〜50μm程度とすることが好ましく、約10μm程度とすることがより好ましい。

【0045】

尚、本実施形態において、コスト削減や工程数削減を目的として、絶縁樹脂層107Aの形成を省いてもよい。その場合、後述する絶縁樹脂層107Bにより同等の絶縁効果を得ることができる。

【0046】

次に、図3(d)に示すとおり、各素子電極102の上に、例えばめっき法などにより、Sn含有金属層111を形成する。Sn含有金属層111はSnのみから構成されていてもよいし、又はSnを主成分とする合金から構成されていてもよい。尚、Sn含有金属層111の形成方法として、めっき法に代えて、例えば、Snを主体とするペーストを印刷法などにより素子電極102上に塗布した後にリフロー加熱を行うことによって厚いSn含有層を形成できるプリコーティング法を用いてもよい。

【0047】

次に、図4(a)に示すように、導電性突起体103を有する金属層105A、及び絶縁樹脂層107Bを準備した後、図4(b)に示すように、導電性突起体103が絶縁樹脂層107Bを貫通するように、金属層105Aと絶縁樹脂層107Bとを一体化する。具体的には、絶縁樹脂層107Bを貫通した導電性突起体103の頂部は絶縁樹脂層107Bから突出して露出している。ここで、導電性突起体103の全体的な形状は、先端(頂部)に近づくにつれて細くなっている。これにより、絶縁樹脂層107Bに対する導電性突起体103の貫通性が向上する。また、導電性突起体103は、例えば導電性材料又は圧延金属などから構成されており、その表面には、例えば電解めっき法又は無電解めっき法により、銅層又は銅を主体とする合金層が設けられている。尚、導電性突起体103自体がCuから構成されている場合には、前述のめっき処理は省略可能であり、導電性突起体103の表面に防錆処理を施しておけばよい。また、導電性突起体103の高さは、絶縁樹脂層107Bの厚さと比べて同等又は高くなっている。これにより、後述する素子電極102への導電性突起体103の接合を確実に行うことが可能となる。

【0048】

次に、図5(a)に示すように、絶縁樹脂層107Bと一体化した導電性突起体103と、絶縁樹脂層107Aと一体化した半導体素子101上の素子電極102とを対向させた後、図5(b)に示すように、絶縁樹脂層107Aと絶縁樹脂層107Bとを貼り合わせる。ここで、絶縁樹脂層107Aの開口部110を通じて導電性突起体103と素子電極102とが電気的に接続される。

【0049】

本実施形態では、素子電極102と導電性突起体103との接続に際して、素子電極102上に比較的柔らかいSn含有金属層111が形成されているため、仮に導電性突起体103の先端が鋭利な形状であったとしても、導電性突起体103の素子電極102への接触時のダメージを軽減することができる。また、導電性突起体103に高さバラツキがあったとしても、素子電極102の一部が局地的に大きなダメージを受ける事態をSn含有金属層111によって回避することができる。

【0050】

尚、以下の説明では、絶縁樹脂層107A及び絶縁樹脂層107Bの積層体を単に絶縁樹脂層107と称するが、前述のように、絶縁樹脂層107A及び絶縁樹脂層107Bのいずれか一方を、コストや製造工程数の削減のために省略してもよい。

【0051】

続いて、図5(b)に示すように、金属層105Aを金属配線105に加工する。ここで、各金属配線105における各素子電極102と反対側の一端には、略円形状をした金属ランドが配置される。この金属ランドは半導体素子101の表面上にマトリックス状に複数配置される。

【0052】

次に、図5(c)に示すように、前記各金属ランドを含む各金属配線105を覆うように絶縁樹脂層109を形成した後、当該各金属ランドが露出するように絶縁樹脂層109に複数の開口部をマトリックス状に形成する。

【0053】

次に、図5(d)に示すように、前記各金属ランド上にはんだボール106を形成する。はんだボール106の形成方法としては、色々な方法が考えられるが、例えば金属ランド上にフラックスを塗布した後にはんだボール106を搭載してリフロー加熱によりはんだボール106を一旦溶融させる方法、又は、金属ランド上にフラックス入りはんだ粉末(いわゆるはんだペースト)を塗布した後にリフロー加熱によりはんだ粉末を一旦溶融させ、その後、凝固させることによってはんだボール106を形成する方法等を用いてもよい。いずれの方法を用いた場合においても、リフロー加熱を行う際に、導電性突起体103上に設けられたCu含有層中のCu成分と、素子電極102上に設けられたSn含有金属層111中のSn成分とによって、SnCu合金層104が形成される結果、導電性突起体103と素子電極102との間に強固な接続信頼性が得られる。ここで、SnCu合金層104の厚さは約1μm程度までが良い。その理由は、SnCu合金層104の厚さが1μmを大きく超えた場合、機械的な衝撃などによりSnCu合金層104が破壊されるおそれがあるためである。また、前述のリフロー加熱を行うことにより、素子電極102への局地的な圧接によるストレスが解放されるため、内部応力に起因する素子電極102へのダメージを緩和できると同時に半導体素子101の反りも緩和できるという相乗効果が得られる。ここで、リフロー加熱の温度は、はんだボール106の金属物性としての液相温度を超える温度であり、近年の環境問題を鑑みた鉛フリーはんだ組成であれば220〜250℃が一般的である。また、はんだボール106の形成に伴うリフロー加熱に代えて、プリント基板への2次実装工程におけるリフロー加熱を利用することも可能である。この場合には、加熱回数が1回で済むという利点がある。

【0054】

尚、半導体装置の製造工程においては、通常、さまざまな温度の熱負荷が加えられる。実際、本実施形態においても、SnCu合金層104を形成するための加熱工程が必要となるが、仮に半導体装置の製造工程においてSnCu合金層104の形成に必要な熱が加えられなかったとしても、前述のように、プリント基板実装でのリフロー加熱を利用することができるため、高温加熱に対する耐性が弱い半導体装置に対しては、本実施形態は非常に有効となる。

【0055】

最後に、以上に述べた各工程が実施されたウエハをチップ(半導体装置100)毎に分割する。図6は、本実施形態の半導体装置100が複数設けられたウエハ10を、ウエハ10の表面に平行な軸の周りに回転するダイシングブレード112を用いて半導体装置100毎に分割する工程を説明する斜視図である。図6に示すように、各半導体装置100上に複数の外部電極端子つまりはんだボール106がマトリックス状に配置されており、ウエハ10を半導体装置100毎に分離することによって、図1に示す個片の半導体装置100を得ることができる。

【0056】

以上に説明した本実施形態によると、半導体素子101の素子電極102と、素子電極102上に設けられる導電性突起体103との間に、SnCu合金層104を形成するため、素子電極102と導電性突起体103との接続を強固にできるので、接続信頼性を向上させることができる。また、素子電極102と導電性突起体103との間に、SnCu合金層104を形成するため、仮に導電性突起体103の先端が鋭利な形状であったとしても、素子電極102と導電性突起体103とを接続する際の素子電極102へのダメージを軽減することができるので、半導体装置の実装を容易に行うことができる。

【0057】

尚、本実施形態において、導電性突起体103上に設けられたCu含有層中のCu成分と、素子電極102上に設けられたSn含有金属層111中のSn成分とによって、SnCu合金層104を形成したときに、当該Cu含有層の一部及び当該Sn含有金属層111の一部が残存してもよい。

【0058】

また、本実施形態において、Cu含有層を少なくとも表面部に有する導電性突起体103と対向する半導体素子101の素子電極102上にSn含有金属層111を形成することにより、SnCu合金層104を形成した。しかし、これに代えて、Sn含有層を少なくとも表面部に有する導電性突起体103と対向する半導体素子101の素子電極102上にCu含有層を形成することにより、SnCu合金層104を形成してもよい。この場合、素子電極102上にCu含有層を例えばめっき法により形成してもよい。或いは、めっき法に代えて、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法を用いてもよい。また、SnCu合金層104の形成後に、当該Sn含有層の一部及び当該Cu含有層の一部が残存してもよい。

【産業上の利用可能性】

【0059】

本発明は、絶縁層を貫通する導電性突起体と半導体素子の電極部とが電気的に接続された半導体装置において、接続信頼性の向上及び電極部へのダメージの緩和を可能とするものであり、接続信頼性が向上したWL−CSP等の実装を容易に行う上で有用である。

【符号の説明】

【0060】

1 半導体素子

2 素子電極

3 導電性突起体

5 導電性金属箔

6 はんだボ−ル

7 絶縁樹脂層

8 金属ランド

9 WL−CSP

10 ウエハ

100 半導体装

101 半導体素子

102 素子電極

103 導電性突起体

104 SnCu合金層

105 金属配線

105A 金属層

106 はんだボール

107、107A、107B 絶縁樹脂層

109 絶縁樹脂層

110 開口部

111 Sn含有合金層

112 ダイシングブレード

【特許請求の範囲】

【請求項1】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層が介在していることを特徴とする半導体装置。

【請求項2】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体における少なくとも前記電極部と対向する表面部には銅含有層が形成されており、

前記電極部における前記導電性突起体と対向する面上には錫含有層が形成されていることを特徴とする半導体装置。

【請求項3】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体における少なくとも前記電極部と対向する表面部には錫含有層が形成されており、

前記電極部における前記導電性突起体と対向する面上には銅含有層が形成されていることを特徴とする半導体装置。

【請求項4】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記ウエハにおける前記電極部の配置面側に、前記電極部と対向するように導電性突起体を準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備え、

前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層を形成する工程をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法において、

前記合金層を形成するための加熱を、前記外部端子を形成する際のリフロー加熱工程で実施することを特徴とする半導体装置の製造方法。

【請求項6】

請求項4に記載の半導体装置の製造方法において、

前記ウエハが分割されてなる半導体装置をプリント基板上に実装する工程をさらに備え、

前記合金層を形成するための加熱を、前記半導体装置を前記プリント基板上に実装する際のリフロー加熱工程で実施することを特徴とする半導体装置の製造方法。

【請求項7】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記電極部の表面上に錫含有層を形成する工程と、

前記ウエハにおける前記電極部の配置面側に、銅含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備えていることを特徴とする半導体装置の製造方法。

【請求項8】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記電極部の表面上に銅含有層を形成する工程と、

前記ウエハにおける前記電極部の配置面側に、錫含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備えていることを特徴とする半導体装置の製造方法。

【請求項9】

請求項7又は8に記載の半導体装置の製造方法において、

前記錫含有層は、めっき法により形成されることを特徴とする半導体装置の製造方法。

【請求項10】

請求項7又は8に記載の半導体装置の製造方法において、

前記錫含有層は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されることを特徴とする半導体装置の製造方法。

【請求項11】

請求項7又は8に記載の半導体装置の製造方法において、

前記銅含有層は、めっき法により形成されることを特徴とする半導体装置の製造方法。

【請求項12】

請求項7又は8に記載の半導体装置の製造方法において、

前記銅含有層は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されることを特徴とする半導体装置の製造方法。

【請求項1】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層が介在していることを特徴とする半導体装置。

【請求項2】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体における少なくとも前記電極部と対向する表面部には銅含有層が形成されており、

前記電極部における前記導電性突起体と対向する面上には錫含有層が形成されていることを特徴とする半導体装置。

【請求項3】

半導体素子と、

前記半導体素子の一面上に配置された少なくとも1つの電極部と、

前記電極部を除いて前記半導体素子の前記一面を覆うように形成された絶縁層と、

前記電極部と電気的に接続する導電性突起体を有しており且つ前記絶縁層上に設けられた配線と、

前記配線上に形成された外部端子とを備え、

前記導電性突起体における少なくとも前記電極部と対向する表面部には錫含有層が形成されており、

前記電極部における前記導電性突起体と対向する面上には銅含有層が形成されていることを特徴とする半導体装置。

【請求項4】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記ウエハにおける前記電極部の配置面側に、前記電極部と対向するように導電性突起体を準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備え、

前記導電性突起体と前記電極部との間に、錫及び銅を含む合金層を形成する工程をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法において、

前記合金層を形成するための加熱を、前記外部端子を形成する際のリフロー加熱工程で実施することを特徴とする半導体装置の製造方法。

【請求項6】

請求項4に記載の半導体装置の製造方法において、

前記ウエハが分割されてなる半導体装置をプリント基板上に実装する工程をさらに備え、

前記合金層を形成するための加熱を、前記半導体装置を前記プリント基板上に実装する際のリフロー加熱工程で実施することを特徴とする半導体装置の製造方法。

【請求項7】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記電極部の表面上に錫含有層を形成する工程と、

前記ウエハにおける前記電極部の配置面側に、銅含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備えていることを特徴とする半導体装置の製造方法。

【請求項8】

少なくとも1つの電極部が一面上に配置された半導体素子が複数形成されたウエハを準備する工程と、

前記電極部の表面上に銅含有層を形成する工程と、

前記ウエハにおける前記電極部の配置面側に、錫含有層を少なくとも表面部に有する導電性突起体を当該表面部が前記電極部と対向するように準備する工程と、

前記ウエハにおける前記電極部の配置面と前記導電性突起体との間に絶縁層を準備する工程と、

前記導電性突起体が前記絶縁層を貫通するように前記導電性突起体と前記絶縁層とを一体化する工程と、

前記ウエハにおける前記電極部の配置面に前記絶縁層を貼り合わせると共に前記導電性突起体を前記電極部に電気的に接続する工程と、

前記絶縁層上に、前記導電性突起体と接続する配線を形成する工程と、

前記配線上に外部端子を形成する工程と、

前記ウエハを前記半導体素子毎に分割する工程とを備えていることを特徴とする半導体装置の製造方法。

【請求項9】

請求項7又は8に記載の半導体装置の製造方法において、

前記錫含有層は、めっき法により形成されることを特徴とする半導体装置の製造方法。

【請求項10】

請求項7又は8に記載の半導体装置の製造方法において、

前記錫含有層は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されることを特徴とする半導体装置の製造方法。

【請求項11】

請求項7又は8に記載の半導体装置の製造方法において、

前記銅含有層は、めっき法により形成されることを特徴とする半導体装置の製造方法。

【請求項12】

請求項7又は8に記載の半導体装置の製造方法において、

前記銅含有層は、印刷法による材料塗布後にリフロー加熱を行うプリコーティング法により形成されることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−60805(P2011−60805A)

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願番号】特願2009−205572(P2009−205572)

【出願日】平成21年9月7日(2009.9.7)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願日】平成21年9月7日(2009.9.7)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]