半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特にn型トランジスタ及びp型トランジスタを有している半導体装置及びその製造方法に関する。

【背景技術】

【0002】

MOSFET(金属−酸化膜−半導体電界効果トランジスタ)を高性能化するため、従来のシリコン酸化膜よりも比誘電率が高い金属酸化物(High−k)材料をゲート絶縁層に採用し、金属材料をゲート電極に採用したHigh−k/メタルゲート構造を備えた半導体デバイスの開発が進められている。High−k材料からなるHigh−kゲート絶縁膜は、誘電率が高い分、物理的な膜厚を厚くしてもゲート容量を維持して高い駆動電流を得ることができる。加えて、物理的な膜厚を厚くすることができるので、その分リーク電流を低減できるという効果も得られる。また、金属材料をゲート電極として用いたメタルゲート電極では、ポリシリコン電極の場合に発生するゲート電極の空乏化による実効的な絶縁層厚の増加が生じない。

【0003】

nMOSトランジスタにおいては、Siの伝導帯端(4.05eV)に近い仕事関数を持つ金属を用いたメタルゲート電極が閾値電圧の点から好ましい。一方、pMOSトランジスタにおいては、Siの価電子帯端(5.17eV)に近い仕事関数を持つ金属を用いたメタルゲート電極が閾値電圧の点から好ましい。しかし、nMOSトランジスタとpMOSトランジスタのそれぞれに異なる材料からなるメタルゲート電極を形成しようとすると、製造プロセスが複雑化し、製造コストも増加する。このため、メタルゲート電極の材料を、nMOSトランジスタとpMOSトランジスタとにおいて同一とする、デュアルキャップ・シングルメタルゲート(Dual Cap Single Metal Gate:DCSMG)−CMOSプロセスが検討されている(例えば、非特許文献1を参照。)。DCSMG−CMOSプロセスは、メタルゲート電極の下に閾値電圧を調整するためのキャップ層を挿入する。nMOSトランジスタと、pMOSトランジスタとでは、キャップ層に含まれる閾値電圧調整用の元素に異なる元素を用いる。DCSMG−CMOSプロセスでは、キャップ層中に含まれる金属元素がHigh−kゲート絶縁膜とその下に形成されたSiO2膜との界面まで拡散し、そこでダイポールを形成する。ダイポールの形成によりnMOSトランジスタ及びpMOSトランジスタのそれぞれに好ましい閾値電圧を実現できる。

【0004】

DCSMG−CMOSプロセスは、メタルゲート電極、キャップ層及びHigh−kゲート絶縁膜の積層構造が、ソースドレインの形成工程において高温に曝される。積層構造が高温に曝されると、High−kゲート絶縁膜中の酸素が抜け出して、酸素欠損が生じる。酸素欠損は正電荷として作用して、pMOSトランジスタでは閾値電圧が上昇する。高温熱処理によるpMOSトランジスタの閾値電圧上昇という問題に対して、高温熱処理後にゲート電極を作り直す、ゲートラストプロセスという方法が検討されている(例えば、特許文献1を参照。)。

【0005】

ゲートラストプロセスは、以下のように行われる。まず、High−kゲート絶縁膜を堆積した後、犠牲層として一度、ポリシリコンによる仮のゲート電極を形成する。この後、通常のゲート加工、ソースドレイン注入及び活性化のための高温熱処理が行われる。さらに、絶縁層によるトランジスタの埋め込み、CMP(Chemical Mechanical Polishing)による仮のゲート電極の頭出しをした後、仮のゲート電極及びHigh−kゲート絶縁膜を除去する。仮のゲート電極及びHigh−kゲート絶縁膜を除去して形成したトレンチ溝にHigh−kゲート絶縁膜を再度堆積する。再度堆積したHig−Kゲート絶縁膜の上に金属障壁層、仕事関数設定金属層及びキャップ層を有するメタルゲート電極を形成する。金属障壁層は、High−kゲート絶縁膜と仕事関数設定金属層との密着性を改善すると共にHigh−kゲート絶縁膜と金属層との直接の反応を抑制するために形成する。金属障壁層は、pMOSトランジスタ及びnMOSトランジスタに共通の材料を使用する。仕事関数設定金属層は、pMOSトランジスタ及びnMOSトランジスタで異なる材料を使用する。キャップ層は、pMOSトランジスタ及びnMOSトランジスタに共通の材料を使用する。ゲート電極を作り直すゲートラストプロセスでは、高温熱処理による影響を受けることなく、pMOSトランジスタに適切な閾値電圧を得ることができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2008−515190号公報

【非特許文献】

【0007】

【非特許文献1】C.S.Park et al., VLSI Technology Symposium p.208 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来のゲートラストプロセスは、トレンチ溝の中に形成する仕事金属設定金属層を、nMOSトランジスタとpMOSトランジスタとで異なる材料とするため、製造プロセスが複雑になるという問題がある。また、閾値電圧の調整は、金属障壁層越しに仕事関数設定金属層から金属元素を拡散することにより行う。仕事関数設定金属層はトレンチ溝の中に形成するため、金属障壁層よりもゲート長方向及びゲート幅方向において内側に存在する。従って、ゲート端まで十分に金属元素が拡散されず、閾値電圧の調整が困難になるという問題がある。

【0009】

さらに、従来のゲートラストプロセスではHigh−kゲート絶縁膜を活性化熱処理後にゲートのトレンチ溝内に再度堆積する。このため、High−kゲート絶縁膜の焼き締めを行うことができない。また、微細なトレンチ溝の中に膜を形成するため、膜厚が変動しやすい。このため、閾値電圧がばらつき、結果として信頼性の劣化も懸念される。

【0010】

本発明は、前記の問題を解決し、nMOSトランジスタ及びpMOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにすることを目的としている。

【課題を解決するための手段】

【0011】

前記の目的を達成するため、本発明は半導体装置を、熱処理によりゲート絶縁膜中に仕事関数調整用の元素を拡散させた後、ゲート電極だけを再形成した構成とする。

【0012】

具体的に、本発明に係る第1の半導体装置は、半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、第1トランジスタは、半導体基板の上に形成された第1ゲート絶縁膜と、第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、第2トランジスタは、半導体基板の上に形成された第2ゲート絶縁膜と、第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、第1ゲート電極及び第2ゲート電極はそれぞれ、断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含み、第1絶縁層及び第2絶縁層は平板状であり、第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいる。

【0013】

第1の半導体装置は、第1ゲート絶縁膜が仕事関数調整用の第1元素を含み、第1ゲート電極及び第2ゲート電極がそれぞれ断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含む構成としている。このため、第1トランジスタ及び第2トランジスタの閾値電圧を最適化しつつ、ゲート電極を作り別ける必要がない。また、ゲート絶縁膜及びゲート電極の膜厚及び組成等のばらつきを抑えて、閾値電圧のばらつきを生じにくくすることができる。

【0014】

第1の半導体装置において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムとすればよい。この場合において、第2トランジスタはp型であり、第2絶縁層は、仕事関数調整用の第2元素としてアルミニウム、チタン、タンタル又はハフニウムを含んでいる構成としてもよい。

【0015】

また、第1トランジスタはp型であり、第1元素は、アルミニウム、チタン、タンタル又はハフニウムとしてもよい。この場合において、第2トランジスタはn型であり、第2絶縁層は、仕事関数調整用の第2元素として希土類元素又はマグネシウムを含んでいる構成としてもよい。

【0016】

第1の半導体装置において、第1絶縁層は、シリコンを含む膜であり、第2絶縁層は、ハフニウム又はジルコニウムを含む膜であり、第1導電層は、窒化チタン又は窒化タンタルを含む膜からなり、第2導電層は、第1導電層よりも抵抗率が低い材料からなる構成としてもよい。

【0017】

第1の半導体装置において、第2導電層は、アルミニウム、銅又はタングステンとしてもよい。

【0018】

本発明に係る第2の半導体装置は、半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、第1トランジスタは、半導体基板の上に形成された第1ゲート絶縁膜と、第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、第2トランジスタは、半導体基板の上に形成された第2ゲート絶縁膜と、第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、第1ゲート電極及び第2ゲート電極はそれぞれ、第1導電層を含み、第1絶縁層及び第2絶縁層は平板状であり、第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいる。

【0019】

第1及び第2の半導体装置は、半導体基板における第1ゲート電極の側方に形成された第1ソースドレインと、半導体基板における第2ゲート電極の側方に形成された第2ソースドレインと、第1ソースドレイン又は第2ソースドレインと接続されたコンタクトプラグとをさらに備え、コンタクトプラグは、第1ゲート電極及び第2ゲート電極と同じ材料からなる構成としてもよい。

【0020】

本発明に係る半導体装置の製造方法は、素子分離領域により互いに分離された第1領域及び第2領域を有する半導体基板上の全面に、第1絶縁層を形成する工程(a)と、第1絶縁層の上に第2絶縁層を形成する工程(b)と、工程(a)よりも後に、第1領域に選択的に第1元素を含む第1キャップ層を形成する工程(c)と、工程(c)よりも後に、半導体基板上の全面に犠牲層を形成する工程(d)と、犠牲層、第2絶縁層及び第1絶縁層を含む第1ダミーゲート及び第2ダミーゲートをそれぞれ、第1領域及び第2領域に形成する工程(e)と、第1ダミーゲート及び第2ダミーゲートの側面上にそれぞれ、第1サイドウォール及び第2サイドウォールを形成する工程(f)と、第1ダミーゲート及び第1サイドウォールをマスクとして第1領域に第1導電型の不純物を選択的に注入して第1ソースドレインを形成し、第2ダミーゲート及び第2サイドウォールをマスクとして第2領域に第2導電型の不純物を選択的に注入して第2ソースドレインを形成する工程(g)と、工程(g)よりも後に、熱を加えることにより、第1ソースドレイン及び第2ソースドレインを活性化すると共に、第1領域において第1キャップ層に含まれる第1元素を第2絶縁層及び第1絶縁層中に拡散させる工程(h)と、工程(h)よりも後に、第1ダミーゲート及び第2ダミーゲートを覆う層間絶縁膜を形成した後、犠牲層を露出するように層間絶縁膜を研磨する工程(i)と、工程(i)よりも後に、犠牲層を除去することにより、第1サイドウォールに囲まれた第1トレンチ溝及び第2サイドウォールに囲まれた第2トレンチ溝を形成する工程(j)と、工程(j)よりも後に、第1トレンチ溝及び第2トレンチ溝に導電材料を埋め込んで第1ゲート電極及び第2ゲート電極を形成する工程(k)とを備え、第1ゲート電極及び第2ゲート電極は、同一の材料からなる。

【0021】

本発明の半導体装置の製造方法は、閾値電圧を最適化しつつ、第1ゲート電極及び第2ゲート電極を同一の材料により同一の工程において形成することを可能とする。また、トレンチ溝内に断面凹状の絶縁層及びキャップ層を形成する場合と異なり、ゲート端まで仕事関数調整用の第1元素を拡散させることができる。また、絶縁層及びキャップ層の膜厚の変動も小さくすることができるため、閾値電圧のばらつきを小さくすることができる。さらに、絶縁層を焼き締めることも可能となり、ゲート絶縁膜の信頼性を向上させることができる。その結果、工程を簡略化しつつ、半導体装置の閾値電圧を最適化し且つ信頼性を向上させることが可能となる。

【0022】

本発明の半導体装置の製造方法において、工程(k)は、半導体基板上の全面に、第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層及び第2導電層を順次形成した後、第1トレンチ溝及び第2トレンチ溝を除いて第1導電層及び第2導電層を除去する工程とすればよい。

【0023】

本発明の半導体装置の製造方法において、工程(k)は、半導体基板上の全面に、第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層を形成した後、第1トレンチ溝及び第2トレンチ溝を除いて第1導電層を除去する工程としてもよい。

【0024】

本発明の半導体装置の製造方法において、工程(c)は、工程(b)よりも後に行う構成としても、工程(b)よりも前に行う構成としてもよい。

【0025】

本発明の半導体装置の製造方法において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムとしても、第1トランジスタはp型であり、第1元素は、アルミニウム、チタン、タンタル又はハフニウムとしてもよい。

【0026】

本発明の半導体装置の製造方法は、工程(a)よりも後で且つ工程(d)よりも前に、第2領域に選択的に第2元素を含む第2キャップ層を形成する工程(l)をさらに備え、工程(h)において、第2領域において第2キャップ層に含まれる第2元素を第2絶縁層及び第1絶縁層中に拡散させる構成としてもよい。

【0027】

この場合において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムであり、第2トランジスタはp型であり、第2元素は、アルミニウム、チタン、タンタル又はハフニウムである構成としてもよい。

【0028】

本発明の半導体装置の製造方法は、工程(d)よりも後に、犠牲層の上にハードマスクを形成する工程(m)をさらに備え、第1ダミーゲート及び第2ダミーゲートは、ハードマスクを含み、工程(i)では、第1ダミーゲート及び第2ダミーゲートを覆うように層間絶縁膜を形成した後、ハードマスクをストッパとして層間絶縁膜を犠牲層が露出するまで研磨する構成としてもよい。

【0029】

本発明の半導体装置の製造方法において、工程(i)よりも後で且つ工程(k)よりも前に、層間絶縁膜に第1ソースドレイン又は第2ソースドレインを露出すコンタクトホールを形成する工程(n)をさらに備え、工程(k)では、コンタクトホールに導電材料で埋め込んで、第1ゲート電極及び第2ゲート電極と共に、コンタクトプラグを形成する構成としてもよい。

【発明の効果】

【0030】

本発明に係る半導体装置によれば、メタルゲート電極の材質を変えることなくnMOSトランジスタ及びpMOSトランジスタのそれぞれに適切な閾値電圧を備えた半導体装置を実現することができる。

【図面の簡単な説明】

【0031】

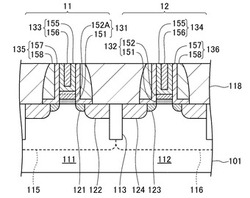

【図1】一実施形態に係る半導体装置を示す断面図である。

【図2】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図3】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図4】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図5】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図6】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図7】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図8】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図9】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図10】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図11】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図12】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図13】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図14】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図15】一実施形態に係る半導体装置の変形例を示す断面図である。

【図16】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図17】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図18】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図19】一実施形態に係る半導体装置の変形例を示す断面図である。

【図20】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図21】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図22】一実施形態に係る半導体装置の変形例を示す断面図である。

【図23】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図24】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図25】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図26】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図27】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図28】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図29】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【発明を実施するための形態】

【0032】

図1に示すように、一実施形態に係る半導体装置は、nMOSトランジスタ11とpMOSトランジスタ12とを備えている。nMOSトランジスタ11は、半導体基板101の第1領域111に形成されている。pMOSトランジスタ12は、素子分離領域113により第1領域111と分離された第2領域112に形成されている。nMOSトランジスタ11及びpMOSトランジスタ12は層間絶縁膜118に覆われており、通常は層間絶縁膜118の上に形成された配線等と接続されている。

【0033】

第1領域111にはpウェル115が形成され、第2領域112にはnウェル116が形成されている。pウェル115には、nMOSトランジスタ11のn型エクステンション・ポケット領域121とn型ソースドレイン122とが形成されている。nウェル116にはpMOSトランジスタ12のp型エクステンション・ポケット領域123とp型ソースドレイン124とが形成されている。第1領域111の上には、nMOSトランジスタ11の第1ゲート絶縁膜131、第1ゲート電極133及び第1サイドウォール135が形成されている。第2領域112の上には、pMOSトランジスタ12の第2ゲート絶縁膜132、第2ゲート電極134及び第2サイドウォール136が形成されている。

【0034】

第1ゲート絶縁膜131は、第1絶縁層151と、第1絶縁層151の上に形成された第2絶縁層152Aとを有している。第1絶縁層151は、シリコン酸化膜(SiO2膜)等からなる。第2絶縁層152AはHigh−k膜であり、ハフニウム(Hf)若しくはジルコニウム(Zr)等を含む酸化膜又は酸窒化膜等を用いることができる。また、HfSiON等のSiを含む膜であってもよい。第2絶縁層152Aは、仕事関数調整用の元素として、希土類元素又はマグネシウム(Mg)等を含んでいる。希土類元素とは、スカンジウム(Sc)、イットリウム(Y)、ランタン(La)、セリウム(Ce)、プラセオジウム(Pr)、ネオジム(Nd)、プロメチウム(Pm)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)又はルテチウム(Lu)であるが、中でも、Sc、Y、La、Ce、Pr、Gd、Dy及びLu等が好ましい。

【0035】

第1ゲート電極133は、窒化チタン(TiN)又は窒化タンタル(TaN)等からなり、断面凹状の第1導電層155と、凹部を埋めるように形成されたアルミニウム(Al)、銅(Cu)又はタングステン(W)等からなる第2導電層156とを有している。第2導電層156は、第1導電層155よりも抵抗率が低い材料からなることが好ましい。第1サイドウォール135は、第1ゲート絶縁膜131及び第1ゲート電極133の側面上に形成されており、断面L字状の内側サイドウォール157と内側サイドウォール157の上に形成された外側サイドウォール158とを有している。なお、内側サイドウォール157は断面L字状である必要はなく、断面I字状であってもよい。

【0036】

第2ゲート絶縁膜132は、第1絶縁層151と、第1絶縁層151の上に形成された第2絶縁層152とを有している。第1絶縁層151はSiO2等からなる。第2絶縁層152はHigh−k膜であり、ハフニウム(Hf)若しくはジルコニウム(Zr)等を含む酸化膜又は酸窒化膜等を用いることができる。また、HfSiON等のSiを含む膜であってもよい。第2絶縁層152は、仕事関数調整用の元素を含んでいない。第2ゲート電極134はTiN等からなる断面凹状の第1導電層155と、凹部を埋めるように形成されたAl等からなる第2導電層156とを有している。第2サイドウォール136は、第2ゲート絶縁膜132及び第2ゲート電極134の側面上に形成されており、断面L字状の内側サイドウォール157と内側サイドウォール157の上に形成された外側サイドウォール158とを有している。なお、内側サイドウォール157は断面L字状である必要はなく、断面I字状であってもよい。

【0037】

以下に、本実施形態の半導体装置の製造方法を説明する。まず、図2に示すように、Si基板等の半導体基板101の上部に素子分離領域113により互いに分離された第1領域111及び第2領域112を形成する。素子分離領域113は、半導体基板101の上部をエッチングして形成したトレンチに、化学気相堆積法(CVD法)等によりSiO2膜を埋め込んで形成すればよい。続いて、第1領域111にp型不純物を注入してpウェル115を形成し、第2領域112にn型不純物を注入してnウェル116を形成する。この後、半導体基板101上の全面に、厚さが1nm以下のSiO2膜である第1絶縁層151を形成する。SiO2からなる第1絶縁層151は、熱酸化法又はプラズマ酸化法等により形成すればよい。SiO2膜に代えて、シリコン酸窒化膜(SiON膜)又はシリコン窒化膜(SiN膜)等を用いることも可能である。

【0038】

次に、図3に示すように第1絶縁層151の上に、厚さが2nm以下のHf又はZrを含む金属酸化物等からなる第2絶縁層152を形成する。第2絶縁層152は、原子層堆積法(ALD法)又はCVD法等により形成すればよい。

【0039】

次に、図4に示すように第2絶縁層152の上に、厚さが0.5nm以下のキャップ層161を形成する。キャップ層161は、nMOSトランジスタにおける仕事関数調整用の元素であるLa若しくはSc等の希土類元素又はMg等を含む膜であり、例えばLa2O3とすればよい。キャップ層161は、物理蒸着法(PVD法)又はALD法等により形成すればよい。

【0040】

次に、図5に示すように第1領域111を覆い第2領域112を露出する、レジストマスク171を形成する。この後、レジストマスク171を用いてキャップ層161における第2領域112の上に形成された部分を選択的に除去する。

【0041】

次に、レジストマスク171を除去した後、図6に示すように半導体基板101上の全面に厚さが100nm程度のポリシリコンからなる犠牲層163を形成する。続いて、犠牲層163の上に、厚さが20nm以下のSiO2膜又はSiN膜等からなるハードマスク164を形成する。犠牲層163及びハードマスク164は、CVD法又はPVD法等により形成すればよい。また、ハードマスク164は必要に応じて形成すればよく、形成しなくてもよい。ハードマスク164を形成することにより、後の層間絶縁膜を形成する工程において、ダミーゲートの頭出しが容易となる。

【0042】

次に、図7に示すように第1絶縁層151からハードマスク164までを選択的に除去して、第1領域111に第1ダミーゲート166Aを形成し、第2領域112に第2ダミーゲート166Bを形成する。第1ダミーゲート166Aは、半導体基板101上に順次積層された第1絶縁層151、第2絶縁層152、キャップ層161、犠牲層163及びハードマスク164を有している。第2ダミーゲート166Bは、半導体基板101上に順次積層された第1絶縁層151、第2絶縁層152、犠牲層163及びハードマスク164を有している。

【0043】

次に、図8に示すように第1領域111にn型エクステンション・ポケット領域121及びn型ソースドレイン122を形成し、第2領域112にp型エクステンション・ポケット領域123及びp型ソースドレイン124を形成する。

【0044】

具体的にはまず、第1ダミーゲート166A及び第2ダミーゲート166Bの側面上にそれぞれ、内側サイドウォール157を形成する。内側サイドウォール157は、SiO2膜、シリコン酸窒化膜(SiON膜)又はSiN膜等とすればよい。この後、第1領域111において内側サイドウォール157越しにn型不純物を注入して、n型エクステンション・ポケット領域121を形成する。第2領域112において内側サイドウォール157越しにp型不純物を注入して、p型エクステンション・ポケット領域123を形成する。この後、内側サイドウォール157を覆うように、外側サイドウォール158を形成する。外側サイドウォール158は、SiO2膜、SiON膜又はSiN膜等とすればよい。第1領域111においては、第1ダミーゲート166Aの側面上に内側サイドウォール157及び外側サイドウォール158を有する第1サイドウォール135が形成される。第2領域112においては、第2ダミーゲート166Bの側面上に内側サイドウォール157及び外側サイドウォール158を有する第2サイドウォール136が形成される。第1領域111において、第1サイドウォール135をマスクとしてn型不純物を注入し、n型ソースドレイン122を形成し、第2領域112において第2サイドウォール136をマスクとしてp型不純物を注入し、p型ソースドレイン124を形成する。

【0045】

この後、1000℃〜1350℃の温度で、時間が0.1ms〜100msのミリセカンドアニールを行う。これにより、n型エクステンション・ポケット領域121、p型エクステンション・ポケット領域123、n型ソースドレイン122及びp型ソースドレイン124が活性化される。また、第1領域111においてキャップ層161中に含まれる仕事関数調整用の元素が第1絶縁層151と第2絶縁層152との界面近傍まで拡散し、第2絶縁層152は仕事関数調整用の元素を含む第2絶縁層152Aとなる。この際に、厚さが非常に薄いキャップ層161は、第2絶縁層152Aと混ざり合い、第2絶縁層152Aと一体となる。但し、キャップ層161の膜厚及び熱処理条件等によっては、キャップ層161が第2絶縁層152Aの上に残存する場合がある。キャップ層161が第2絶縁層152Aの上に残存していてもかまわない。仕事関数調整用の元素が、第1絶縁層151と第2絶縁層152の界面近傍に存在していればよく、通常は第1絶縁層151と第2絶縁層152との界面を越えて第1絶縁層151に拡散している。

【0046】

次に、図9に示すように半導体基板101上の全面にCVD法等により、SiO2膜等からなる層間絶縁膜118を形成する。

【0047】

次に、図10に示すように層間絶縁膜118をCMP法等により研磨して、第1ダミーゲート166A及び第2ダミーゲート166Bの犠牲層163が露出するようにする。層間絶縁膜118を研磨する際には、ハードマスク164をCMPストッパとして用いることができる。

【0048】

次に、図11に示すように、犠牲層163をエッチングし、トレンチ溝118aを形成する。トレンチ溝118aは、第1領域111においては第1サイドウォール135に囲まれており、第2領域112においては第2サイドウォール136に囲まれている。

【0049】

次に、図12に示すように半導体基板101上の全面に厚さが20nm以下の第1導電層155を形成する。第1導電層155は、TiN又はTaN等とすればよく、ALD法、PVD法、CVD法又は電界めっき法等により形成すればよい。

【0050】

次に、図13に示すように第1導電層155の上に厚さが10nm以下の第2導電層156を形成する。第2導電層156は、第1導電層155よりも抵抗率が低い材料からなることが好ましく、Al、Cu又はW等とすればよい。第2導電層156は、ALD法、PVD法、CVD法又は電界めっき法等により形成すればよい。

【0051】

次に、図14に示すようにCMP法等により、トレンチ溝118aの外側に形成された第1導電層155及び第2導電層156を除去する。これにより、第1領域111には第1ゲート電極133が形成され、第2領域112には第2ゲート電極134が形成される。

【0052】

以上のように、本実施形態の半導体装置の製造方法は、ゲート絶縁膜をソースドレインの形成後に再形成しない。このため、第1導電層及び第2導電層だけでなく、第1絶縁層及び第2絶縁層もトレンチ溝内に再形成する場合と異なり、第1絶縁層151及び第2絶縁層152は断面凹状ではなく平板状となる。また、第1絶縁層151及び第2絶縁層152のゲート長方向及びゲート幅方向の幅は等しくなる。

【0053】

本実施形態の半導体装置の製造方法によれば、nMOSトランジスタにおいてゲート電極の再形成前に仕事関数調整用の元素による閾値電圧調整を行うことができる。従って、キャップ層からゲート絶縁膜への仕事関数調整用の元素の拡散をトレンチ溝内にゲート絶縁膜を再形成する場合よりもはるかに均一に行うことができる。従って、仕事関数調整用の元素の拡散のばらつきによる閾値電圧の変動を抑えることができる。また、トレンチ溝内にゲート絶縁膜を再形成する場合よりもゲート絶縁膜の組成及び膜厚のばらつきを抑えることができ、組成及び膜厚のばらつきによる閾値電圧のばらつきも抑制することができる。さらに、High−k膜である第2絶縁層の焼き締めを行うことができるという利点もある。

【0054】

また、第1ゲート電極及び第2ゲート電極を、同一の材料を用いた同一のプロセスにより同時に形成することができる。従って、第1ゲート電極及び第2ゲート電極の形成が容易であり、プロセスの複雑化と高コスト化を避けることができる。また、トレンチ溝内に形成する第1ゲート電極及び第2ゲート電極の組成及び膜厚等のばらつきを抑えることができるため、閾値電圧のばらつきを小さくすることができる。

【0055】

本実施形態において、第1ゲート電極133及び第2ゲート電極134を、第1導電層155と第2導電層156との積層膜としたが、図15に示すように第1導電層155の単層としてもよい。この場合には、図16に示すようにトレンチ溝118aを埋めるように、厚さが50nm程度の第1導電層155を形成し、トレンチ溝118aの外側に堆積した第1導電層155を除去すればよい。

【0056】

本実施形態において、仕事関数調整用の元素を含むキャップ層161を第2絶縁層152の上に形成した。しかし、第1絶縁層151と第2絶縁層152との間にキャップ層161を形成してもよい。第1絶縁層151と第2絶縁層152との間にキャップ層161を形成する場合には、第2絶縁層152の上にキャップ層161を形成する場合よりも、第2絶縁層152と第1絶縁層151との界面近傍に形成されるダイポールの絶対量が増加する。このため、第2絶縁層上にキャップ層を形成した場合と比べ、キャップ層161の膜厚を薄くすることが可能となり、閾値電圧の調整がさらに容易となる。また、第1絶縁層151への仕事関数調整用の元素の拡散が生じやすくなるため、第1絶縁層151の誘電率が増加する。このため、第1絶縁層151の電気的な膜厚(Equivalent Oxide Thickness:EOT)を薄膜化することができ、MOSトランジスタの駆動電流を増加させることができる。なお、この場合には、第1絶縁層151と第2絶縁層152との間にキャップ層161が残存していてもよい。

【0057】

この場合には、図17に示すように、第1絶縁層151の上にキャップ層161を形成した後、図18に示すようにキャップ層161の第2領域112の上に形成された部分を選択的に除去した後、第2絶縁層152を形成する。この後、犠牲層の形成以降の工程は、先に示した工程と同様にして行えばよい。

【0058】

本実施形態においては、nMOSトランジスタ11の第1ゲート絶縁膜131が仕事関数調整用の元素を含む構成とした。しかし、図19に示すようにpMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む第2絶縁層152Bを有する構成としてもよい。

【0059】

この場合には、例えば第2絶縁層152を形成した後、図20に示すようにpMOSトランジスタにおける仕事関数調整用の元素である、Al、Ti、Ta又はHf等を含むキャップ層162を形成する。Al等は金属単体であっても、酸化物又は窒化物等となっていてもよい。次に、図21に示すように第2領域112を覆い第1領域111を露出するレジストマスク172を形成し、レジストマスク172を用いてキャップ層162における第1領域111の上に形成された部分を選択的に除去する。この後、エクステンション・ポケット領域及びソースドレインの形成並びに活性化等を行うことにより、キャップ層162中に含まれる第2元素が、第2領域112において第1絶縁層151と第2絶縁層152との界面近傍にまで拡散し、仕事関数調整用の元素を含む第2絶縁層152Bが形成される。さらに、先に示した工程と同様にして、犠牲層163の除去、第1ゲート電極及び第2ゲート電極の形成等を行えばよい。

【0060】

図19はキャップ層162が完全に拡散して、第2絶縁層152Bと一体となっている例を示しているが、第2絶縁層152Bの上にキャップ層162が残存していてもよい。

【0061】

pMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む構成とする場合も、キャップ層162を第1絶縁層151と第2絶縁層152との間に形成し、第1絶縁層151中に仕事関数調整用の元素を拡散させてもよい。

【0062】

さらに、図22に示すようにnMOSトランジスタ11の第1ゲート絶縁膜131及びpMOSトランジスタ12の第2ゲート絶縁膜132の両方が仕事関数調整用の元素を含む構成としてもよい。

【0063】

この場合には、図23に示すように第2絶縁層152を形成した後、pMOSトランジスタにおける仕事関数調整用の元素である、Al等を含むキャップ層162を形成する。次に、図24に示すように第2領域112を覆い第1領域111を露出するハードマスク175を形成し、ハードマスク175を用いてキャップ層162における第1領域111の上に形成された部分を選択的に除去する。次に、図25に示すように半導体基板101上の全面に、nMOSトランジスタにおける仕事関数調整用の元素である、La等を含むキャップ層161を形成する。次に、図26に示すようにハードマスク175の上に形成されたキャップ層161を除去した後、ハードマスク175を除去する。これにより、第1領域111にはLa等を含むキャップ層161が形成され、第2領域112にはAl等を含むキャップ層162が形成される。

【0064】

この後、先に示した工程と同様にしてエクステンション・ポケット領域及びソースドレインの形成並びに活性化等を行う。これにより第1領域111においては、キャップ層161中に含まれるLa等が第2絶縁層152中に拡散し、nMOSトランジスタ用の仕事関数調整用の元素を含む第2絶縁層152Aが形成される。一方、第2領域112においては、キャップ層162中に含まれるAl等が第2絶縁層152中に拡散し、pMOSトランジスタ用の仕事関数調整用の元素を含む第2絶縁層152Bが形成される。さらに、犠牲層の除去、第1ゲート電極及び第2ゲート電極の形成等を行えばよい。

【0065】

この場合においても、キャップ層を第1絶縁層と第2絶縁層との間に形成してもよい。また、一方のキャップ層を第2絶縁層の上に形成し、もう一方のキャップ層を第1絶縁層と第2絶縁層との間に形成してもよい。

【0066】

本実施形態の半導体装置の製造方法は、ソースドレインと接続されたコンタクトプラグを容易に形成できるという利点もある。例えば、図27に示すように犠牲層を除去してトレンチ溝118aを形成した後、層間絶縁膜118をエッチングして、n型ソースドレイン122及びp型ソースドレイン124を露出するコンタクトホール118bを形成する。次に、図28に示すように半導体基板101上の全面に第1導電層155及び第2導電層156を順次形成する。次に、図29に示すようにトレンチ溝118a及びコンタクトホール118bの外側に堆積した第1導電層155及び第2導電層156を除去する。これにより、第1ゲート電極133、第2ゲート電極134及びコンタクトプラグ138が同時に形成される。なお、コンタクトホール118bは、トレンチ溝118aよりも前に形成してもよい。第1導電層155の膜厚を50nm程度として、第1ゲート電極133、第2ゲート電極134及びコンタクトプラグ138を、第1導電層155の単層としてもよい。pMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む場合及びnMOSトランジスタ11の第1ゲート絶縁膜131及びpMOSトランジスタ12の第2ゲート絶縁膜132の両方が仕事関数調整用の元素を含む場合にも同様の方法によりコンタクトプラグを形成することができる。

【産業上の利用可能性】

【0067】

本発明に係る半導体装置及びその製造方法は、n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧を適切な値に調整でき、特に微細メタルゲート及びHigh−kゲート絶縁膜を有するMOSトランジスタを含む半導体装置に利用することができる。

【符号の説明】

【0068】

11 nMOSトランジスタ

12 pMOSトランジスタ

101 半導体基板

111 第1領域

112 第2領域

113 素子分離領域

115 pウェル

116 nウェル

118 層間絶縁膜

118a トレンチ溝

118b コンタクトホール

121 n型エクステンション・ポケット領域

122 n型ソースドレイン

123 p型エクステンション・ポケット領域

124 p型ソースドレイン

131 第1ゲート絶縁膜

132 第2ゲート絶縁膜

133 第1ゲート電極

134 第2ゲート電極

135 第1サイドウォール

136 第2サイドウォール

138 コンタクトプラグ

151 第1絶縁層

152 第2絶縁層

152A 仕事関数調整用の元素を含む第2絶縁層

152B 仕事関数調整用の元素を含む第2絶縁層

155 第1導電層

156 第2導電層

157 内側サイドウォール

158 外側サイドウォール

161 キャップ層

162 キャップ層

163 犠牲層

164 ハードマスク

166A 第1ダミーゲート

166B 第2ダミーゲート

171 レジストマスク

172 レジストマスク

175 ハードマスク

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特にn型トランジスタ及びp型トランジスタを有している半導体装置及びその製造方法に関する。

【背景技術】

【0002】

MOSFET(金属−酸化膜−半導体電界効果トランジスタ)を高性能化するため、従来のシリコン酸化膜よりも比誘電率が高い金属酸化物(High−k)材料をゲート絶縁層に採用し、金属材料をゲート電極に採用したHigh−k/メタルゲート構造を備えた半導体デバイスの開発が進められている。High−k材料からなるHigh−kゲート絶縁膜は、誘電率が高い分、物理的な膜厚を厚くしてもゲート容量を維持して高い駆動電流を得ることができる。加えて、物理的な膜厚を厚くすることができるので、その分リーク電流を低減できるという効果も得られる。また、金属材料をゲート電極として用いたメタルゲート電極では、ポリシリコン電極の場合に発生するゲート電極の空乏化による実効的な絶縁層厚の増加が生じない。

【0003】

nMOSトランジスタにおいては、Siの伝導帯端(4.05eV)に近い仕事関数を持つ金属を用いたメタルゲート電極が閾値電圧の点から好ましい。一方、pMOSトランジスタにおいては、Siの価電子帯端(5.17eV)に近い仕事関数を持つ金属を用いたメタルゲート電極が閾値電圧の点から好ましい。しかし、nMOSトランジスタとpMOSトランジスタのそれぞれに異なる材料からなるメタルゲート電極を形成しようとすると、製造プロセスが複雑化し、製造コストも増加する。このため、メタルゲート電極の材料を、nMOSトランジスタとpMOSトランジスタとにおいて同一とする、デュアルキャップ・シングルメタルゲート(Dual Cap Single Metal Gate:DCSMG)−CMOSプロセスが検討されている(例えば、非特許文献1を参照。)。DCSMG−CMOSプロセスは、メタルゲート電極の下に閾値電圧を調整するためのキャップ層を挿入する。nMOSトランジスタと、pMOSトランジスタとでは、キャップ層に含まれる閾値電圧調整用の元素に異なる元素を用いる。DCSMG−CMOSプロセスでは、キャップ層中に含まれる金属元素がHigh−kゲート絶縁膜とその下に形成されたSiO2膜との界面まで拡散し、そこでダイポールを形成する。ダイポールの形成によりnMOSトランジスタ及びpMOSトランジスタのそれぞれに好ましい閾値電圧を実現できる。

【0004】

DCSMG−CMOSプロセスは、メタルゲート電極、キャップ層及びHigh−kゲート絶縁膜の積層構造が、ソースドレインの形成工程において高温に曝される。積層構造が高温に曝されると、High−kゲート絶縁膜中の酸素が抜け出して、酸素欠損が生じる。酸素欠損は正電荷として作用して、pMOSトランジスタでは閾値電圧が上昇する。高温熱処理によるpMOSトランジスタの閾値電圧上昇という問題に対して、高温熱処理後にゲート電極を作り直す、ゲートラストプロセスという方法が検討されている(例えば、特許文献1を参照。)。

【0005】

ゲートラストプロセスは、以下のように行われる。まず、High−kゲート絶縁膜を堆積した後、犠牲層として一度、ポリシリコンによる仮のゲート電極を形成する。この後、通常のゲート加工、ソースドレイン注入及び活性化のための高温熱処理が行われる。さらに、絶縁層によるトランジスタの埋め込み、CMP(Chemical Mechanical Polishing)による仮のゲート電極の頭出しをした後、仮のゲート電極及びHigh−kゲート絶縁膜を除去する。仮のゲート電極及びHigh−kゲート絶縁膜を除去して形成したトレンチ溝にHigh−kゲート絶縁膜を再度堆積する。再度堆積したHig−Kゲート絶縁膜の上に金属障壁層、仕事関数設定金属層及びキャップ層を有するメタルゲート電極を形成する。金属障壁層は、High−kゲート絶縁膜と仕事関数設定金属層との密着性を改善すると共にHigh−kゲート絶縁膜と金属層との直接の反応を抑制するために形成する。金属障壁層は、pMOSトランジスタ及びnMOSトランジスタに共通の材料を使用する。仕事関数設定金属層は、pMOSトランジスタ及びnMOSトランジスタで異なる材料を使用する。キャップ層は、pMOSトランジスタ及びnMOSトランジスタに共通の材料を使用する。ゲート電極を作り直すゲートラストプロセスでは、高温熱処理による影響を受けることなく、pMOSトランジスタに適切な閾値電圧を得ることができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2008−515190号公報

【非特許文献】

【0007】

【非特許文献1】C.S.Park et al., VLSI Technology Symposium p.208 (2009)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来のゲートラストプロセスは、トレンチ溝の中に形成する仕事金属設定金属層を、nMOSトランジスタとpMOSトランジスタとで異なる材料とするため、製造プロセスが複雑になるという問題がある。また、閾値電圧の調整は、金属障壁層越しに仕事関数設定金属層から金属元素を拡散することにより行う。仕事関数設定金属層はトレンチ溝の中に形成するため、金属障壁層よりもゲート長方向及びゲート幅方向において内側に存在する。従って、ゲート端まで十分に金属元素が拡散されず、閾値電圧の調整が困難になるという問題がある。

【0009】

さらに、従来のゲートラストプロセスではHigh−kゲート絶縁膜を活性化熱処理後にゲートのトレンチ溝内に再度堆積する。このため、High−kゲート絶縁膜の焼き締めを行うことができない。また、微細なトレンチ溝の中に膜を形成するため、膜厚が変動しやすい。このため、閾値電圧がばらつき、結果として信頼性の劣化も懸念される。

【0010】

本発明は、前記の問題を解決し、nMOSトランジスタ及びpMOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにすることを目的としている。

【課題を解決するための手段】

【0011】

前記の目的を達成するため、本発明は半導体装置を、熱処理によりゲート絶縁膜中に仕事関数調整用の元素を拡散させた後、ゲート電極だけを再形成した構成とする。

【0012】

具体的に、本発明に係る第1の半導体装置は、半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、第1トランジスタは、半導体基板の上に形成された第1ゲート絶縁膜と、第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、第2トランジスタは、半導体基板の上に形成された第2ゲート絶縁膜と、第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、第1ゲート電極及び第2ゲート電極はそれぞれ、断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含み、第1絶縁層及び第2絶縁層は平板状であり、第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいる。

【0013】

第1の半導体装置は、第1ゲート絶縁膜が仕事関数調整用の第1元素を含み、第1ゲート電極及び第2ゲート電極がそれぞれ断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含む構成としている。このため、第1トランジスタ及び第2トランジスタの閾値電圧を最適化しつつ、ゲート電極を作り別ける必要がない。また、ゲート絶縁膜及びゲート電極の膜厚及び組成等のばらつきを抑えて、閾値電圧のばらつきを生じにくくすることができる。

【0014】

第1の半導体装置において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムとすればよい。この場合において、第2トランジスタはp型であり、第2絶縁層は、仕事関数調整用の第2元素としてアルミニウム、チタン、タンタル又はハフニウムを含んでいる構成としてもよい。

【0015】

また、第1トランジスタはp型であり、第1元素は、アルミニウム、チタン、タンタル又はハフニウムとしてもよい。この場合において、第2トランジスタはn型であり、第2絶縁層は、仕事関数調整用の第2元素として希土類元素又はマグネシウムを含んでいる構成としてもよい。

【0016】

第1の半導体装置において、第1絶縁層は、シリコンを含む膜であり、第2絶縁層は、ハフニウム又はジルコニウムを含む膜であり、第1導電層は、窒化チタン又は窒化タンタルを含む膜からなり、第2導電層は、第1導電層よりも抵抗率が低い材料からなる構成としてもよい。

【0017】

第1の半導体装置において、第2導電層は、アルミニウム、銅又はタングステンとしてもよい。

【0018】

本発明に係る第2の半導体装置は、半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、第1トランジスタは、半導体基板の上に形成された第1ゲート絶縁膜と、第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、第2トランジスタは、半導体基板の上に形成された第2ゲート絶縁膜と、第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、第1ゲート電極及び第2ゲート電極はそれぞれ、第1導電層を含み、第1絶縁層及び第2絶縁層は平板状であり、第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいる。

【0019】

第1及び第2の半導体装置は、半導体基板における第1ゲート電極の側方に形成された第1ソースドレインと、半導体基板における第2ゲート電極の側方に形成された第2ソースドレインと、第1ソースドレイン又は第2ソースドレインと接続されたコンタクトプラグとをさらに備え、コンタクトプラグは、第1ゲート電極及び第2ゲート電極と同じ材料からなる構成としてもよい。

【0020】

本発明に係る半導体装置の製造方法は、素子分離領域により互いに分離された第1領域及び第2領域を有する半導体基板上の全面に、第1絶縁層を形成する工程(a)と、第1絶縁層の上に第2絶縁層を形成する工程(b)と、工程(a)よりも後に、第1領域に選択的に第1元素を含む第1キャップ層を形成する工程(c)と、工程(c)よりも後に、半導体基板上の全面に犠牲層を形成する工程(d)と、犠牲層、第2絶縁層及び第1絶縁層を含む第1ダミーゲート及び第2ダミーゲートをそれぞれ、第1領域及び第2領域に形成する工程(e)と、第1ダミーゲート及び第2ダミーゲートの側面上にそれぞれ、第1サイドウォール及び第2サイドウォールを形成する工程(f)と、第1ダミーゲート及び第1サイドウォールをマスクとして第1領域に第1導電型の不純物を選択的に注入して第1ソースドレインを形成し、第2ダミーゲート及び第2サイドウォールをマスクとして第2領域に第2導電型の不純物を選択的に注入して第2ソースドレインを形成する工程(g)と、工程(g)よりも後に、熱を加えることにより、第1ソースドレイン及び第2ソースドレインを活性化すると共に、第1領域において第1キャップ層に含まれる第1元素を第2絶縁層及び第1絶縁層中に拡散させる工程(h)と、工程(h)よりも後に、第1ダミーゲート及び第2ダミーゲートを覆う層間絶縁膜を形成した後、犠牲層を露出するように層間絶縁膜を研磨する工程(i)と、工程(i)よりも後に、犠牲層を除去することにより、第1サイドウォールに囲まれた第1トレンチ溝及び第2サイドウォールに囲まれた第2トレンチ溝を形成する工程(j)と、工程(j)よりも後に、第1トレンチ溝及び第2トレンチ溝に導電材料を埋め込んで第1ゲート電極及び第2ゲート電極を形成する工程(k)とを備え、第1ゲート電極及び第2ゲート電極は、同一の材料からなる。

【0021】

本発明の半導体装置の製造方法は、閾値電圧を最適化しつつ、第1ゲート電極及び第2ゲート電極を同一の材料により同一の工程において形成することを可能とする。また、トレンチ溝内に断面凹状の絶縁層及びキャップ層を形成する場合と異なり、ゲート端まで仕事関数調整用の第1元素を拡散させることができる。また、絶縁層及びキャップ層の膜厚の変動も小さくすることができるため、閾値電圧のばらつきを小さくすることができる。さらに、絶縁層を焼き締めることも可能となり、ゲート絶縁膜の信頼性を向上させることができる。その結果、工程を簡略化しつつ、半導体装置の閾値電圧を最適化し且つ信頼性を向上させることが可能となる。

【0022】

本発明の半導体装置の製造方法において、工程(k)は、半導体基板上の全面に、第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層及び第2導電層を順次形成した後、第1トレンチ溝及び第2トレンチ溝を除いて第1導電層及び第2導電層を除去する工程とすればよい。

【0023】

本発明の半導体装置の製造方法において、工程(k)は、半導体基板上の全面に、第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層を形成した後、第1トレンチ溝及び第2トレンチ溝を除いて第1導電層を除去する工程としてもよい。

【0024】

本発明の半導体装置の製造方法において、工程(c)は、工程(b)よりも後に行う構成としても、工程(b)よりも前に行う構成としてもよい。

【0025】

本発明の半導体装置の製造方法において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムとしても、第1トランジスタはp型であり、第1元素は、アルミニウム、チタン、タンタル又はハフニウムとしてもよい。

【0026】

本発明の半導体装置の製造方法は、工程(a)よりも後で且つ工程(d)よりも前に、第2領域に選択的に第2元素を含む第2キャップ層を形成する工程(l)をさらに備え、工程(h)において、第2領域において第2キャップ層に含まれる第2元素を第2絶縁層及び第1絶縁層中に拡散させる構成としてもよい。

【0027】

この場合において、第1トランジスタはn型であり、第1元素は、希土類元素又はマグネシウムであり、第2トランジスタはp型であり、第2元素は、アルミニウム、チタン、タンタル又はハフニウムである構成としてもよい。

【0028】

本発明の半導体装置の製造方法は、工程(d)よりも後に、犠牲層の上にハードマスクを形成する工程(m)をさらに備え、第1ダミーゲート及び第2ダミーゲートは、ハードマスクを含み、工程(i)では、第1ダミーゲート及び第2ダミーゲートを覆うように層間絶縁膜を形成した後、ハードマスクをストッパとして層間絶縁膜を犠牲層が露出するまで研磨する構成としてもよい。

【0029】

本発明の半導体装置の製造方法において、工程(i)よりも後で且つ工程(k)よりも前に、層間絶縁膜に第1ソースドレイン又は第2ソースドレインを露出すコンタクトホールを形成する工程(n)をさらに備え、工程(k)では、コンタクトホールに導電材料で埋め込んで、第1ゲート電極及び第2ゲート電極と共に、コンタクトプラグを形成する構成としてもよい。

【発明の効果】

【0030】

本発明に係る半導体装置によれば、メタルゲート電極の材質を変えることなくnMOSトランジスタ及びpMOSトランジスタのそれぞれに適切な閾値電圧を備えた半導体装置を実現することができる。

【図面の簡単な説明】

【0031】

【図1】一実施形態に係る半導体装置を示す断面図である。

【図2】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図3】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図4】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図5】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図6】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図7】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図8】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図9】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図10】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図11】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図12】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図13】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図14】一実施形態に係る半導体装置の製造方法における一工程を示す断面図である。

【図15】一実施形態に係る半導体装置の変形例を示す断面図である。

【図16】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図17】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図18】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図19】一実施形態に係る半導体装置の変形例を示す断面図である。

【図20】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図21】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図22】一実施形態に係る半導体装置の変形例を示す断面図である。

【図23】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図24】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図25】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図26】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図27】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図28】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【図29】一実施形態に係る半導体装置の変形例の製造方法における一工程を示す断面図である。

【発明を実施するための形態】

【0032】

図1に示すように、一実施形態に係る半導体装置は、nMOSトランジスタ11とpMOSトランジスタ12とを備えている。nMOSトランジスタ11は、半導体基板101の第1領域111に形成されている。pMOSトランジスタ12は、素子分離領域113により第1領域111と分離された第2領域112に形成されている。nMOSトランジスタ11及びpMOSトランジスタ12は層間絶縁膜118に覆われており、通常は層間絶縁膜118の上に形成された配線等と接続されている。

【0033】

第1領域111にはpウェル115が形成され、第2領域112にはnウェル116が形成されている。pウェル115には、nMOSトランジスタ11のn型エクステンション・ポケット領域121とn型ソースドレイン122とが形成されている。nウェル116にはpMOSトランジスタ12のp型エクステンション・ポケット領域123とp型ソースドレイン124とが形成されている。第1領域111の上には、nMOSトランジスタ11の第1ゲート絶縁膜131、第1ゲート電極133及び第1サイドウォール135が形成されている。第2領域112の上には、pMOSトランジスタ12の第2ゲート絶縁膜132、第2ゲート電極134及び第2サイドウォール136が形成されている。

【0034】

第1ゲート絶縁膜131は、第1絶縁層151と、第1絶縁層151の上に形成された第2絶縁層152Aとを有している。第1絶縁層151は、シリコン酸化膜(SiO2膜)等からなる。第2絶縁層152AはHigh−k膜であり、ハフニウム(Hf)若しくはジルコニウム(Zr)等を含む酸化膜又は酸窒化膜等を用いることができる。また、HfSiON等のSiを含む膜であってもよい。第2絶縁層152Aは、仕事関数調整用の元素として、希土類元素又はマグネシウム(Mg)等を含んでいる。希土類元素とは、スカンジウム(Sc)、イットリウム(Y)、ランタン(La)、セリウム(Ce)、プラセオジウム(Pr)、ネオジム(Nd)、プロメチウム(Pm)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)又はルテチウム(Lu)であるが、中でも、Sc、Y、La、Ce、Pr、Gd、Dy及びLu等が好ましい。

【0035】

第1ゲート電極133は、窒化チタン(TiN)又は窒化タンタル(TaN)等からなり、断面凹状の第1導電層155と、凹部を埋めるように形成されたアルミニウム(Al)、銅(Cu)又はタングステン(W)等からなる第2導電層156とを有している。第2導電層156は、第1導電層155よりも抵抗率が低い材料からなることが好ましい。第1サイドウォール135は、第1ゲート絶縁膜131及び第1ゲート電極133の側面上に形成されており、断面L字状の内側サイドウォール157と内側サイドウォール157の上に形成された外側サイドウォール158とを有している。なお、内側サイドウォール157は断面L字状である必要はなく、断面I字状であってもよい。

【0036】

第2ゲート絶縁膜132は、第1絶縁層151と、第1絶縁層151の上に形成された第2絶縁層152とを有している。第1絶縁層151はSiO2等からなる。第2絶縁層152はHigh−k膜であり、ハフニウム(Hf)若しくはジルコニウム(Zr)等を含む酸化膜又は酸窒化膜等を用いることができる。また、HfSiON等のSiを含む膜であってもよい。第2絶縁層152は、仕事関数調整用の元素を含んでいない。第2ゲート電極134はTiN等からなる断面凹状の第1導電層155と、凹部を埋めるように形成されたAl等からなる第2導電層156とを有している。第2サイドウォール136は、第2ゲート絶縁膜132及び第2ゲート電極134の側面上に形成されており、断面L字状の内側サイドウォール157と内側サイドウォール157の上に形成された外側サイドウォール158とを有している。なお、内側サイドウォール157は断面L字状である必要はなく、断面I字状であってもよい。

【0037】

以下に、本実施形態の半導体装置の製造方法を説明する。まず、図2に示すように、Si基板等の半導体基板101の上部に素子分離領域113により互いに分離された第1領域111及び第2領域112を形成する。素子分離領域113は、半導体基板101の上部をエッチングして形成したトレンチに、化学気相堆積法(CVD法)等によりSiO2膜を埋め込んで形成すればよい。続いて、第1領域111にp型不純物を注入してpウェル115を形成し、第2領域112にn型不純物を注入してnウェル116を形成する。この後、半導体基板101上の全面に、厚さが1nm以下のSiO2膜である第1絶縁層151を形成する。SiO2からなる第1絶縁層151は、熱酸化法又はプラズマ酸化法等により形成すればよい。SiO2膜に代えて、シリコン酸窒化膜(SiON膜)又はシリコン窒化膜(SiN膜)等を用いることも可能である。

【0038】

次に、図3に示すように第1絶縁層151の上に、厚さが2nm以下のHf又はZrを含む金属酸化物等からなる第2絶縁層152を形成する。第2絶縁層152は、原子層堆積法(ALD法)又はCVD法等により形成すればよい。

【0039】

次に、図4に示すように第2絶縁層152の上に、厚さが0.5nm以下のキャップ層161を形成する。キャップ層161は、nMOSトランジスタにおける仕事関数調整用の元素であるLa若しくはSc等の希土類元素又はMg等を含む膜であり、例えばLa2O3とすればよい。キャップ層161は、物理蒸着法(PVD法)又はALD法等により形成すればよい。

【0040】

次に、図5に示すように第1領域111を覆い第2領域112を露出する、レジストマスク171を形成する。この後、レジストマスク171を用いてキャップ層161における第2領域112の上に形成された部分を選択的に除去する。

【0041】

次に、レジストマスク171を除去した後、図6に示すように半導体基板101上の全面に厚さが100nm程度のポリシリコンからなる犠牲層163を形成する。続いて、犠牲層163の上に、厚さが20nm以下のSiO2膜又はSiN膜等からなるハードマスク164を形成する。犠牲層163及びハードマスク164は、CVD法又はPVD法等により形成すればよい。また、ハードマスク164は必要に応じて形成すればよく、形成しなくてもよい。ハードマスク164を形成することにより、後の層間絶縁膜を形成する工程において、ダミーゲートの頭出しが容易となる。

【0042】

次に、図7に示すように第1絶縁層151からハードマスク164までを選択的に除去して、第1領域111に第1ダミーゲート166Aを形成し、第2領域112に第2ダミーゲート166Bを形成する。第1ダミーゲート166Aは、半導体基板101上に順次積層された第1絶縁層151、第2絶縁層152、キャップ層161、犠牲層163及びハードマスク164を有している。第2ダミーゲート166Bは、半導体基板101上に順次積層された第1絶縁層151、第2絶縁層152、犠牲層163及びハードマスク164を有している。

【0043】

次に、図8に示すように第1領域111にn型エクステンション・ポケット領域121及びn型ソースドレイン122を形成し、第2領域112にp型エクステンション・ポケット領域123及びp型ソースドレイン124を形成する。

【0044】

具体的にはまず、第1ダミーゲート166A及び第2ダミーゲート166Bの側面上にそれぞれ、内側サイドウォール157を形成する。内側サイドウォール157は、SiO2膜、シリコン酸窒化膜(SiON膜)又はSiN膜等とすればよい。この後、第1領域111において内側サイドウォール157越しにn型不純物を注入して、n型エクステンション・ポケット領域121を形成する。第2領域112において内側サイドウォール157越しにp型不純物を注入して、p型エクステンション・ポケット領域123を形成する。この後、内側サイドウォール157を覆うように、外側サイドウォール158を形成する。外側サイドウォール158は、SiO2膜、SiON膜又はSiN膜等とすればよい。第1領域111においては、第1ダミーゲート166Aの側面上に内側サイドウォール157及び外側サイドウォール158を有する第1サイドウォール135が形成される。第2領域112においては、第2ダミーゲート166Bの側面上に内側サイドウォール157及び外側サイドウォール158を有する第2サイドウォール136が形成される。第1領域111において、第1サイドウォール135をマスクとしてn型不純物を注入し、n型ソースドレイン122を形成し、第2領域112において第2サイドウォール136をマスクとしてp型不純物を注入し、p型ソースドレイン124を形成する。

【0045】

この後、1000℃〜1350℃の温度で、時間が0.1ms〜100msのミリセカンドアニールを行う。これにより、n型エクステンション・ポケット領域121、p型エクステンション・ポケット領域123、n型ソースドレイン122及びp型ソースドレイン124が活性化される。また、第1領域111においてキャップ層161中に含まれる仕事関数調整用の元素が第1絶縁層151と第2絶縁層152との界面近傍まで拡散し、第2絶縁層152は仕事関数調整用の元素を含む第2絶縁層152Aとなる。この際に、厚さが非常に薄いキャップ層161は、第2絶縁層152Aと混ざり合い、第2絶縁層152Aと一体となる。但し、キャップ層161の膜厚及び熱処理条件等によっては、キャップ層161が第2絶縁層152Aの上に残存する場合がある。キャップ層161が第2絶縁層152Aの上に残存していてもかまわない。仕事関数調整用の元素が、第1絶縁層151と第2絶縁層152の界面近傍に存在していればよく、通常は第1絶縁層151と第2絶縁層152との界面を越えて第1絶縁層151に拡散している。

【0046】

次に、図9に示すように半導体基板101上の全面にCVD法等により、SiO2膜等からなる層間絶縁膜118を形成する。

【0047】

次に、図10に示すように層間絶縁膜118をCMP法等により研磨して、第1ダミーゲート166A及び第2ダミーゲート166Bの犠牲層163が露出するようにする。層間絶縁膜118を研磨する際には、ハードマスク164をCMPストッパとして用いることができる。

【0048】

次に、図11に示すように、犠牲層163をエッチングし、トレンチ溝118aを形成する。トレンチ溝118aは、第1領域111においては第1サイドウォール135に囲まれており、第2領域112においては第2サイドウォール136に囲まれている。

【0049】

次に、図12に示すように半導体基板101上の全面に厚さが20nm以下の第1導電層155を形成する。第1導電層155は、TiN又はTaN等とすればよく、ALD法、PVD法、CVD法又は電界めっき法等により形成すればよい。

【0050】

次に、図13に示すように第1導電層155の上に厚さが10nm以下の第2導電層156を形成する。第2導電層156は、第1導電層155よりも抵抗率が低い材料からなることが好ましく、Al、Cu又はW等とすればよい。第2導電層156は、ALD法、PVD法、CVD法又は電界めっき法等により形成すればよい。

【0051】

次に、図14に示すようにCMP法等により、トレンチ溝118aの外側に形成された第1導電層155及び第2導電層156を除去する。これにより、第1領域111には第1ゲート電極133が形成され、第2領域112には第2ゲート電極134が形成される。

【0052】

以上のように、本実施形態の半導体装置の製造方法は、ゲート絶縁膜をソースドレインの形成後に再形成しない。このため、第1導電層及び第2導電層だけでなく、第1絶縁層及び第2絶縁層もトレンチ溝内に再形成する場合と異なり、第1絶縁層151及び第2絶縁層152は断面凹状ではなく平板状となる。また、第1絶縁層151及び第2絶縁層152のゲート長方向及びゲート幅方向の幅は等しくなる。

【0053】

本実施形態の半導体装置の製造方法によれば、nMOSトランジスタにおいてゲート電極の再形成前に仕事関数調整用の元素による閾値電圧調整を行うことができる。従って、キャップ層からゲート絶縁膜への仕事関数調整用の元素の拡散をトレンチ溝内にゲート絶縁膜を再形成する場合よりもはるかに均一に行うことができる。従って、仕事関数調整用の元素の拡散のばらつきによる閾値電圧の変動を抑えることができる。また、トレンチ溝内にゲート絶縁膜を再形成する場合よりもゲート絶縁膜の組成及び膜厚のばらつきを抑えることができ、組成及び膜厚のばらつきによる閾値電圧のばらつきも抑制することができる。さらに、High−k膜である第2絶縁層の焼き締めを行うことができるという利点もある。

【0054】

また、第1ゲート電極及び第2ゲート電極を、同一の材料を用いた同一のプロセスにより同時に形成することができる。従って、第1ゲート電極及び第2ゲート電極の形成が容易であり、プロセスの複雑化と高コスト化を避けることができる。また、トレンチ溝内に形成する第1ゲート電極及び第2ゲート電極の組成及び膜厚等のばらつきを抑えることができるため、閾値電圧のばらつきを小さくすることができる。

【0055】

本実施形態において、第1ゲート電極133及び第2ゲート電極134を、第1導電層155と第2導電層156との積層膜としたが、図15に示すように第1導電層155の単層としてもよい。この場合には、図16に示すようにトレンチ溝118aを埋めるように、厚さが50nm程度の第1導電層155を形成し、トレンチ溝118aの外側に堆積した第1導電層155を除去すればよい。

【0056】

本実施形態において、仕事関数調整用の元素を含むキャップ層161を第2絶縁層152の上に形成した。しかし、第1絶縁層151と第2絶縁層152との間にキャップ層161を形成してもよい。第1絶縁層151と第2絶縁層152との間にキャップ層161を形成する場合には、第2絶縁層152の上にキャップ層161を形成する場合よりも、第2絶縁層152と第1絶縁層151との界面近傍に形成されるダイポールの絶対量が増加する。このため、第2絶縁層上にキャップ層を形成した場合と比べ、キャップ層161の膜厚を薄くすることが可能となり、閾値電圧の調整がさらに容易となる。また、第1絶縁層151への仕事関数調整用の元素の拡散が生じやすくなるため、第1絶縁層151の誘電率が増加する。このため、第1絶縁層151の電気的な膜厚(Equivalent Oxide Thickness:EOT)を薄膜化することができ、MOSトランジスタの駆動電流を増加させることができる。なお、この場合には、第1絶縁層151と第2絶縁層152との間にキャップ層161が残存していてもよい。

【0057】

この場合には、図17に示すように、第1絶縁層151の上にキャップ層161を形成した後、図18に示すようにキャップ層161の第2領域112の上に形成された部分を選択的に除去した後、第2絶縁層152を形成する。この後、犠牲層の形成以降の工程は、先に示した工程と同様にして行えばよい。

【0058】

本実施形態においては、nMOSトランジスタ11の第1ゲート絶縁膜131が仕事関数調整用の元素を含む構成とした。しかし、図19に示すようにpMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む第2絶縁層152Bを有する構成としてもよい。

【0059】

この場合には、例えば第2絶縁層152を形成した後、図20に示すようにpMOSトランジスタにおける仕事関数調整用の元素である、Al、Ti、Ta又はHf等を含むキャップ層162を形成する。Al等は金属単体であっても、酸化物又は窒化物等となっていてもよい。次に、図21に示すように第2領域112を覆い第1領域111を露出するレジストマスク172を形成し、レジストマスク172を用いてキャップ層162における第1領域111の上に形成された部分を選択的に除去する。この後、エクステンション・ポケット領域及びソースドレインの形成並びに活性化等を行うことにより、キャップ層162中に含まれる第2元素が、第2領域112において第1絶縁層151と第2絶縁層152との界面近傍にまで拡散し、仕事関数調整用の元素を含む第2絶縁層152Bが形成される。さらに、先に示した工程と同様にして、犠牲層163の除去、第1ゲート電極及び第2ゲート電極の形成等を行えばよい。

【0060】

図19はキャップ層162が完全に拡散して、第2絶縁層152Bと一体となっている例を示しているが、第2絶縁層152Bの上にキャップ層162が残存していてもよい。

【0061】

pMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む構成とする場合も、キャップ層162を第1絶縁層151と第2絶縁層152との間に形成し、第1絶縁層151中に仕事関数調整用の元素を拡散させてもよい。

【0062】

さらに、図22に示すようにnMOSトランジスタ11の第1ゲート絶縁膜131及びpMOSトランジスタ12の第2ゲート絶縁膜132の両方が仕事関数調整用の元素を含む構成としてもよい。

【0063】

この場合には、図23に示すように第2絶縁層152を形成した後、pMOSトランジスタにおける仕事関数調整用の元素である、Al等を含むキャップ層162を形成する。次に、図24に示すように第2領域112を覆い第1領域111を露出するハードマスク175を形成し、ハードマスク175を用いてキャップ層162における第1領域111の上に形成された部分を選択的に除去する。次に、図25に示すように半導体基板101上の全面に、nMOSトランジスタにおける仕事関数調整用の元素である、La等を含むキャップ層161を形成する。次に、図26に示すようにハードマスク175の上に形成されたキャップ層161を除去した後、ハードマスク175を除去する。これにより、第1領域111にはLa等を含むキャップ層161が形成され、第2領域112にはAl等を含むキャップ層162が形成される。

【0064】

この後、先に示した工程と同様にしてエクステンション・ポケット領域及びソースドレインの形成並びに活性化等を行う。これにより第1領域111においては、キャップ層161中に含まれるLa等が第2絶縁層152中に拡散し、nMOSトランジスタ用の仕事関数調整用の元素を含む第2絶縁層152Aが形成される。一方、第2領域112においては、キャップ層162中に含まれるAl等が第2絶縁層152中に拡散し、pMOSトランジスタ用の仕事関数調整用の元素を含む第2絶縁層152Bが形成される。さらに、犠牲層の除去、第1ゲート電極及び第2ゲート電極の形成等を行えばよい。

【0065】

この場合においても、キャップ層を第1絶縁層と第2絶縁層との間に形成してもよい。また、一方のキャップ層を第2絶縁層の上に形成し、もう一方のキャップ層を第1絶縁層と第2絶縁層との間に形成してもよい。

【0066】

本実施形態の半導体装置の製造方法は、ソースドレインと接続されたコンタクトプラグを容易に形成できるという利点もある。例えば、図27に示すように犠牲層を除去してトレンチ溝118aを形成した後、層間絶縁膜118をエッチングして、n型ソースドレイン122及びp型ソースドレイン124を露出するコンタクトホール118bを形成する。次に、図28に示すように半導体基板101上の全面に第1導電層155及び第2導電層156を順次形成する。次に、図29に示すようにトレンチ溝118a及びコンタクトホール118bの外側に堆積した第1導電層155及び第2導電層156を除去する。これにより、第1ゲート電極133、第2ゲート電極134及びコンタクトプラグ138が同時に形成される。なお、コンタクトホール118bは、トレンチ溝118aよりも前に形成してもよい。第1導電層155の膜厚を50nm程度として、第1ゲート電極133、第2ゲート電極134及びコンタクトプラグ138を、第1導電層155の単層としてもよい。pMOSトランジスタ12の第2ゲート絶縁膜132が仕事関数調整用の元素を含む場合及びnMOSトランジスタ11の第1ゲート絶縁膜131及びpMOSトランジスタ12の第2ゲート絶縁膜132の両方が仕事関数調整用の元素を含む場合にも同様の方法によりコンタクトプラグを形成することができる。

【産業上の利用可能性】

【0067】

本発明に係る半導体装置及びその製造方法は、n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧を適切な値に調整でき、特に微細メタルゲート及びHigh−kゲート絶縁膜を有するMOSトランジスタを含む半導体装置に利用することができる。

【符号の説明】

【0068】

11 nMOSトランジスタ

12 pMOSトランジスタ

101 半導体基板

111 第1領域

112 第2領域

113 素子分離領域

115 pウェル

116 nウェル

118 層間絶縁膜

118a トレンチ溝

118b コンタクトホール

121 n型エクステンション・ポケット領域

122 n型ソースドレイン

123 p型エクステンション・ポケット領域

124 p型ソースドレイン

131 第1ゲート絶縁膜

132 第2ゲート絶縁膜

133 第1ゲート電極

134 第2ゲート電極

135 第1サイドウォール

136 第2サイドウォール

138 コンタクトプラグ

151 第1絶縁層

152 第2絶縁層

152A 仕事関数調整用の元素を含む第2絶縁層

152B 仕事関数調整用の元素を含む第2絶縁層

155 第1導電層

156 第2導電層

157 内側サイドウォール

158 外側サイドウォール

161 キャップ層

162 キャップ層

163 犠牲層

164 ハードマスク

166A 第1ダミーゲート

166B 第2ダミーゲート

171 レジストマスク

172 レジストマスク

175 ハードマスク

【特許請求の範囲】

【請求項1】

半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、

前記第1トランジスタは、

前記半導体基板の上に形成された第1ゲート絶縁膜と、

前記第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、

前記第2トランジスタは、

前記半導体基板の上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、

前記第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、前記半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、

前記第1ゲート電極及び第2ゲート電極はそれぞれ、断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含み、

前記第1絶縁層及び第2絶縁層は平板状であり、

前記第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいることを特徴とする半導体装置。

【請求項2】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2トランジスタはp型であり、前記第2絶縁層は、仕事関数調整用の第2元素としてアルミニウム、チタン、タンタル又はハフニウムを含んでいることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記第1トランジスタはp型であり、前記第1元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記第2トランジスタはn型であり、前記第2絶縁層は、仕事関数調整用の第2元素として希土類元素又はマグネシウムを含んでいることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第1絶縁層は、シリコンを含む膜であり、

前記第2絶縁層は、ハフニウム又はジルコニウムを含む膜であり、

前記第1導電層は、窒化チタン又は窒化タンタルを含む膜からなり、

前記第2導電層は、前記第1導電層よりも抵抗率が低い材料からなることを特徴とする請求項1〜5のいずれか1項に記載の半導体装置。

【請求項7】

前記第2導電層は、アルミニウム、銅又はタングステンからなることを特徴とする請求項6に記載の半導体装置。

【請求項8】

半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、

前記第1トランジスタは、

前記半導体基板の上に形成された第1ゲート絶縁膜と、

前記第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、

前記第2トランジスタは、

前記半導体基板の上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、

前記第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、前記半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、

前記第1ゲート電極及び第2ゲート電極はそれぞれ、第1導電層を含み、

前記第1絶縁層及び第2絶縁層は平板状であり、

前記第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいることを特徴とする半導体装置。

【請求項9】

前記半導体基板における前記第1ゲート電極の側方に形成された第1ソースドレインと、

前記半導体基板における前記第2ゲート電極の側方に形成された第2ソースドレインと、

前記第1ソースドレイン又は第2ソースドレインと接続されたコンタクトプラグとをさらに備え、

前記コンタクトプラグは、前記第1ゲート電極及び第2ゲート電極と同じ材料からなることを特徴とする請求項1〜8のいずれか1項に記載の半導体装置。

【請求項10】

素子分離領域により互いに分離された第1領域及び第2領域を有する半導体基板上の全面に、第1絶縁層を形成する工程(a)と、

前記第1絶縁層の上に第2絶縁層を形成する工程(b)と、

前記工程(a)よりも後に、前記第1領域に選択的に第1元素を含む第1キャップ層を形成する工程(c)と、

前記工程(c)よりも後に、前記半導体基板上の全面に犠牲層を形成する工程(d)と、

前記犠牲層、第2絶縁層及び第1絶縁層を含む第1ダミーゲート及び第2ダミーゲートをそれぞれ、前記第1領域及び第2領域に形成する工程(e)と、

前記第1ダミーゲート及び第2ダミーゲートの側面上にそれぞれ、第1サイドウォール及び第2サイドウォールを形成する工程(f)と、

前記第1ダミーゲート及び第1サイドウォールをマスクとして前記第1領域に第1導電型の不純物を選択的に注入して第1ソースドレインを形成し、前記第2ダミーゲート及び第2サイドウォールをマスクとして前記第2領域に第2導電型の不純物を選択的に注入して第2ソースドレインを形成する工程(g)と、

前記工程(g)よりも後に、熱を加えることにより、前記第1ソースドレイン及び第2ソースドレインを活性化すると共に、前記第1領域において前記第1キャップ層に含まれる前記第1元素を前記第2絶縁層及び第1絶縁層中に拡散させる工程(h)と、

前記工程(h)よりも後に、前記第1ダミーゲート及び第2ダミーゲートを覆う層間絶縁膜を形成した後、前記犠牲層が露出するように前記層間絶縁膜を研磨する工程(i)と、

前記工程(i)よりも後に、前記犠牲層を除去することにより、前記第1サイドウォールに囲まれた第1トレンチ溝及び前記第2サイドウォールに囲まれた第2トレンチ溝を形成する工程(j)と、

前記工程(j)よりも後に、前記第1トレンチ溝及び第2トレンチ溝に導電材料を埋め込んで第1ゲート電極及び第2ゲート電極を形成する工程(k)とを備え、

前記第1ゲート電極及び第2ゲート電極は、同一の材料からなることを特徴とする半導体装置の製造方法。

【請求項11】

前記工程(k)は、前記半導体基板上の全面に、前記第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層及び第2導電層を順次形成した後、前記第1トレンチ溝及び第2トレンチ溝を除いて前記第1導電層及び第2導電層を除去する工程であることを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項12】

前記工程(k)は、前記半導体基板上の全面に、前記第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層を形成した後、前記第1トレンチ溝及び第2トレンチ溝を除いて前記第1導電層を除去する工程であることを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項13】

前記工程(c)は、前記工程(b)よりも後に行うことを特徴とする請求項10〜12のいずれか1項に記載の半導体装置の製造方法。

【請求項14】

前記工程(c)は、前記工程(b)よりも前に行うことを特徴とする請求項10〜12のいずれか1項に記載の半導体装置の製造方法。

【請求項15】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項16】

前記第1トランジスタはp型であり、前記第1元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項17】

前記工程(a)よりも後で且つ前記工程(d)よりも前に、第2元素を含む第2キャップ層を前記第2領域に選択的に形成する工程(l)をさらに備え、

前記工程(h)において、前記第2領域において前記第2キャップ層に含まれる前記第2元素を前記第2絶縁層及び第1絶縁層中に拡散させることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項18】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであり、

前記第2トランジスタはp型であり、前記第2元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

前記工程(d)よりも後に、前記犠牲層の上にハードマスクを形成する工程(m)をさらに備え、

前記第1ダミーゲート及び第2ダミーゲートは、前記ハードマスクを含み、

前記工程(i)では、前記第1ダミーゲート及び第2ダミーゲートを覆うように前記層間絶縁膜を形成した後、前記ハードマスクをストッパとして前記層間絶縁膜を前記犠牲層が露出するまで研磨することを特徴とする請求項10〜18のいずれか1項に記載の半導体装置の製造方法。

【請求項20】

前記工程(i)よりも後で且つ前記工程(k)よりも前に、前記層間絶縁膜に前記第1ソースドレイン又は前記第2ソースドレインを露出すコンタクトホールを形成する工程(n)をさらに備え、

前記工程(k)では、前記コンタクトホールに前記導電材料で埋め込んで、前記第1ゲート電極及び第2ゲート電極と共に、コンタクトプラグを形成することを特徴とする請求項10〜19のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、

前記第1トランジスタは、

前記半導体基板の上に形成された第1ゲート絶縁膜と、

前記第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、

前記第2トランジスタは、

前記半導体基板の上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、

前記第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、前記半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、

前記第1ゲート電極及び第2ゲート電極はそれぞれ、断面凹形の第1導電層及び該第1導電層の上に形成された第2導電層を含み、

前記第1絶縁層及び第2絶縁層は平板状であり、

前記第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいることを特徴とする半導体装置。

【請求項2】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2トランジスタはp型であり、前記第2絶縁層は、仕事関数調整用の第2元素としてアルミニウム、チタン、タンタル又はハフニウムを含んでいることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記第1トランジスタはp型であり、前記第1元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記第2トランジスタはn型であり、前記第2絶縁層は、仕事関数調整用の第2元素として希土類元素又はマグネシウムを含んでいることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第1絶縁層は、シリコンを含む膜であり、

前記第2絶縁層は、ハフニウム又はジルコニウムを含む膜であり、

前記第1導電層は、窒化チタン又は窒化タンタルを含む膜からなり、

前記第2導電層は、前記第1導電層よりも抵抗率が低い材料からなることを特徴とする請求項1〜5のいずれか1項に記載の半導体装置。

【請求項7】

前記第2導電層は、アルミニウム、銅又はタングステンからなることを特徴とする請求項6に記載の半導体装置。

【請求項8】

半導体基板の上に形成された第1導電型の第1トランジスタ及び第2導電型の第2トランジスタを備え、

前記第1トランジスタは、

前記半導体基板の上に形成された第1ゲート絶縁膜と、

前記第1ゲート絶縁膜の上に形成された第1ゲート電極とを有し、

前記第2トランジスタは、

前記半導体基板の上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜の上に形成された第2ゲート電極とを有し、

前記第1ゲート絶縁膜及び第2ゲート絶縁膜はそれぞれ、前記半導体基板側から積層された第1絶縁層及び第2絶縁層を含み、

前記第1ゲート電極及び第2ゲート電極はそれぞれ、第1導電層を含み、

前記第1絶縁層及び第2絶縁層は平板状であり、

前記第1ゲート絶縁膜は、仕事関数調整用の第1元素を含んでいることを特徴とする半導体装置。

【請求項9】

前記半導体基板における前記第1ゲート電極の側方に形成された第1ソースドレインと、

前記半導体基板における前記第2ゲート電極の側方に形成された第2ソースドレインと、

前記第1ソースドレイン又は第2ソースドレインと接続されたコンタクトプラグとをさらに備え、

前記コンタクトプラグは、前記第1ゲート電極及び第2ゲート電極と同じ材料からなることを特徴とする請求項1〜8のいずれか1項に記載の半導体装置。

【請求項10】

素子分離領域により互いに分離された第1領域及び第2領域を有する半導体基板上の全面に、第1絶縁層を形成する工程(a)と、

前記第1絶縁層の上に第2絶縁層を形成する工程(b)と、

前記工程(a)よりも後に、前記第1領域に選択的に第1元素を含む第1キャップ層を形成する工程(c)と、

前記工程(c)よりも後に、前記半導体基板上の全面に犠牲層を形成する工程(d)と、

前記犠牲層、第2絶縁層及び第1絶縁層を含む第1ダミーゲート及び第2ダミーゲートをそれぞれ、前記第1領域及び第2領域に形成する工程(e)と、

前記第1ダミーゲート及び第2ダミーゲートの側面上にそれぞれ、第1サイドウォール及び第2サイドウォールを形成する工程(f)と、

前記第1ダミーゲート及び第1サイドウォールをマスクとして前記第1領域に第1導電型の不純物を選択的に注入して第1ソースドレインを形成し、前記第2ダミーゲート及び第2サイドウォールをマスクとして前記第2領域に第2導電型の不純物を選択的に注入して第2ソースドレインを形成する工程(g)と、

前記工程(g)よりも後に、熱を加えることにより、前記第1ソースドレイン及び第2ソースドレインを活性化すると共に、前記第1領域において前記第1キャップ層に含まれる前記第1元素を前記第2絶縁層及び第1絶縁層中に拡散させる工程(h)と、

前記工程(h)よりも後に、前記第1ダミーゲート及び第2ダミーゲートを覆う層間絶縁膜を形成した後、前記犠牲層が露出するように前記層間絶縁膜を研磨する工程(i)と、

前記工程(i)よりも後に、前記犠牲層を除去することにより、前記第1サイドウォールに囲まれた第1トレンチ溝及び前記第2サイドウォールに囲まれた第2トレンチ溝を形成する工程(j)と、

前記工程(j)よりも後に、前記第1トレンチ溝及び第2トレンチ溝に導電材料を埋め込んで第1ゲート電極及び第2ゲート電極を形成する工程(k)とを備え、

前記第1ゲート電極及び第2ゲート電極は、同一の材料からなることを特徴とする半導体装置の製造方法。

【請求項11】

前記工程(k)は、前記半導体基板上の全面に、前記第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層及び第2導電層を順次形成した後、前記第1トレンチ溝及び第2トレンチ溝を除いて前記第1導電層及び第2導電層を除去する工程であることを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項12】

前記工程(k)は、前記半導体基板上の全面に、前記第1トレンチ溝及び第2トレンチ溝を埋めるように第1導電層を形成した後、前記第1トレンチ溝及び第2トレンチ溝を除いて前記第1導電層を除去する工程であることを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項13】

前記工程(c)は、前記工程(b)よりも後に行うことを特徴とする請求項10〜12のいずれか1項に記載の半導体装置の製造方法。

【請求項14】

前記工程(c)は、前記工程(b)よりも前に行うことを特徴とする請求項10〜12のいずれか1項に記載の半導体装置の製造方法。

【請求項15】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項16】

前記第1トランジスタはp型であり、前記第1元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項17】

前記工程(a)よりも後で且つ前記工程(d)よりも前に、第2元素を含む第2キャップ層を前記第2領域に選択的に形成する工程(l)をさらに備え、

前記工程(h)において、前記第2領域において前記第2キャップ層に含まれる前記第2元素を前記第2絶縁層及び第1絶縁層中に拡散させることを特徴とする請求項10〜13のいずれか1項に記載の半導体装置の製造方法。

【請求項18】

前記第1トランジスタはn型であり、前記第1元素は、希土類元素又はマグネシウムであり、

前記第2トランジスタはp型であり、前記第2元素は、アルミニウム、チタン、タンタル又はハフニウムであることを特徴とする請求項17に記載の半導体装置の製造方法。

【請求項19】

前記工程(d)よりも後に、前記犠牲層の上にハードマスクを形成する工程(m)をさらに備え、

前記第1ダミーゲート及び第2ダミーゲートは、前記ハードマスクを含み、

前記工程(i)では、前記第1ダミーゲート及び第2ダミーゲートを覆うように前記層間絶縁膜を形成した後、前記ハードマスクをストッパとして前記層間絶縁膜を前記犠牲層が露出するまで研磨することを特徴とする請求項10〜18のいずれか1項に記載の半導体装置の製造方法。

【請求項20】

前記工程(i)よりも後で且つ前記工程(k)よりも前に、前記層間絶縁膜に前記第1ソースドレイン又は前記第2ソースドレインを露出すコンタクトホールを形成する工程(n)をさらに備え、

前記工程(k)では、前記コンタクトホールに前記導電材料で埋め込んで、前記第1ゲート電極及び第2ゲート電極と共に、コンタクトプラグを形成することを特徴とする請求項10〜19のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【公開番号】特開2012−186349(P2012−186349A)

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願番号】特願2011−49057(P2011−49057)

【出願日】平成23年3月7日(2011.3.7)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願日】平成23年3月7日(2011.3.7)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]