半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の微細化に伴い、自己整合による工程が多用されている。

半導体装置の製造方法における自己整合とは、既に形成されたパターンを次のプロセスのマスクとして利用し、マスクの位置合わせなしで次のプロセスを進めることである。

1つの例として、ゲート電極をマスクとしてイオン注入することによりソース・ドレイン領域を形成することがあげられる。この場合、ゲート電極の位置とソース・ドレイン領域の位置とをリソグラフィの制約なしに決定することができる。

【0003】

自己整合型のコンタクトホール(Self Align Contact:SAC)の場合は、コンタクトホールを加工するためのレジストパターンの開口を、コンタクト部分だけでなく、ゲート電極上に形成されたハードマスクの領域まで広げることができる。そして、レジストパターンと共にゲート電極上のハードマスクがエッチングのストッパーとなり、隣り合うゲート電極の間に所望のコンタクトホールが形成される。また、このときのレジストパターンの開口は、必ずしもホール形状だけではなく、ライン状に延びた開口としてもよい。この場合も、ゲート電極上のハードマスクがエッチングのストッパーとなって、隣り合うゲート電極の間にコンタクトホールが形成される。これにより、レジストパターンを形成するためのリソグラフィの難易度を下げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−079492号公報

【特許文献2】特開平10−032243号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0006】

実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

【0007】

また、実施形態に係る半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、前記導電膜上に、絶縁性であり、相互に平行に延びる複数本のハードマスクを形成する工程と、前記ハードマスクをマスクとして前記導電膜及び前記絶縁膜をエッチングすることにより、前記絶縁膜、前記導電膜及び前記ハードマスクが積層され、相互に平行に延びる複数本の積層体を形成する工程と、前記積層体間の空間の下部であって、少なくとも前記絶縁膜間の空間を含むが前記ハードマスク間の空間を含まない部分に犠牲材を埋め込む工程と、前記積層体の側面上であって、前記犠牲材上に前記絶縁側壁を形成する工程と、前記犠牲材を除去する工程と、前記半導体基板上に前記積層体を覆う層間絶縁膜を形成する工程と、前記層間絶縁膜に、前記半導体基板に到達する貫通孔を形成する工程と、前記貫通孔内に導電材料を埋め込んでコンタクトを形成する工程と、を備える。

【図面の簡単な説明】

【0008】

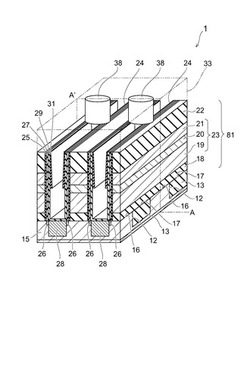

【図1】第1の実施形態に係る半導体装置を例示する斜視図である。

【図2】第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【図3】第2の実施形態に係る半導体装置を例示する斜視図である。

【図4】第2の実施形態に係る半導体装置を例示する断面図であり、図3に示すA−A’面による断面図である。

【図5】第3の実施形態に係る半導体装置を例示する斜視図である。

【図6】第3の実施形態に係る半導体装置を例示する断面図であり、図5に示すA−A’面による断面図である。

【図7】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図10】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】第4の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図13】図12に示すA−A’線による工程断面図である。

【図14】図12に示すB−B’線による工程断面図である。

【図15】図12に示すC−C’線による工程断面図である。

【図16】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図20】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図21】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図22】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図23】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図24】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図25】第4の実施形態に係る半導体装置のゲート電極の上部を例示する断面図である。

【図26】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図27】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図28】(a)及び(b)は、第4の実施形態の比較例に係る半導体装置のゲート電極の上部を例示する断面図である。

【図29】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図30】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図31】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図32】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図33】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図34】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図35】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図36】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図37】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図38】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図39】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図40】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図41】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図42】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図43】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図44】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

本実施形態は、半導体装置の実施形態である。

図1は、第1の実施形態に係る半導体装置を例示する斜視図である。

図2は、第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【0010】

先ず、第1の実施形態に係る半導体装置1の構成について説明する。

図1及び図2に示すように、半導体装置1においては、半導体基板、例えばシリコン基板10が設けられている。シリコン基板10の上面には、1つの方向に延びる複数の溝12が相互に平行に形成されている。溝12の内部には、絶縁材料、例えば酸化シリコン13が埋め込まれている。溝12の内部に酸化シリコン13が埋め込まれた領域をSTI領域(Shallow Trench Isolation)17とする。STI領域17に挟まれた領域を活性領域16とする。

【0011】

シリコン基板10には、シリコン基板10の上面から、溝12の底面より深い領域まで、不純物、例えばボロンが導入されて、ウェル15が形成されている。

シリコン基板10上には、相互に平行に延びる複数本の積層体81が設けられている。積層体81は、溝12と直交する方向に延びている。隣り合う積層体81の間には、積層体81がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。

【0012】

積層体81の最下部には、ゲート絶縁膜として、例えばシリコン酸化膜18が設けられている。シリコン酸化膜18上には、ゲート電極23が設けられている。ゲート電極23の構造は多層膜構造である。すなわち、ゲート電極23は、下から順に、ポリシリコン膜19、バリアメタル膜20、低抵抗金属膜21で構成されている。ポリシリコン膜19には、例えばリン等の不純物が導入されたポリシリコンによって形成されている。バリアメタル膜20としては、例えば窒化タングステン膜があげられる。低抵抗金属膜21としてはタングステン膜があげられる。低抵抗金属膜21上には、ハードマスク22が設けられている。ハードマスク22の材料としては、窒化シリコンがあげられる。

【0013】

シリコン基板10の上層部分におけるゲート電極23の直下域の両側には、不純物、例えばリンが導入された拡張領域26が形成されている。シリコン基板10の上層部分におけるゲート電極23の直下域間の領域であって、拡張領域26間の領域には、ソース・ドレイン領域28が形成されている。ソース・ドレイン領域28には、不純物、例えばリンが、拡張領域26に導入された濃度より高濃度で導入されている。また、ソース・ドレイン領域28には、不純物、例えばリンが、拡張領域26より深く導入されている。ソース・ドレイン領域28の表層には、シリサイド層、例えば、ニッケルシリサイド層(図示せず)が形成されている。

【0014】

積層体81の側面上には、エクステンション側壁25が設けられている。エクステンション側壁25の側面上には、ソース・ドレイン側壁27が設けられている。エクステンション側壁25の側面の端部を上から見た位置は、拡張領域26のゲート電極23側の端部を上から見た位置と略同一である。ソース・ドレイン側壁27の側面の端部を上から見た位置は、ソース・ドレイン領域28のゲート電極23側の端部を上から見た位置と略同一である。

【0015】

ソース・ドレイン側壁27の側面上及びシリコン基板10におけるゲート電極23の直下域間に位置する部分上には、ストッパー膜29が設けられている。すなわち、ストッパー膜29は、溝24の内面上に設けられているともいえる。ストッパー膜29のソース・ドレイン領域28上の部分は除去されている。

ゲート電極23の上部の両側面上には、絶縁側壁31が設けられている。絶縁側壁31の上端は、ハードマスク22の上面と一致している。絶縁側壁31の下端は、ゲート電極23におけるバリアメタル膜20の側面上に位置している。

したがって、ゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0016】

シリコン基板10上には、層間絶縁膜33が設けられている。なお、図1においては、図を見やすくするために、層間絶縁膜33を省略してある。層間絶縁膜33におけるソース・ドレイン領域28上にはコンタクトホール37が形成されている。コンタクトホール37の内部には、コンタクト38が設けられている。コンタクト38はソース・ドレイン領域28の表面におけるシリサイド層に接合されている。

【0017】

ゲート電極23におけるゲート絶縁膜に接する部分の側面とコンタクト23との間には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜の3つのシリコン窒化膜が形成されている。一方、ゲート電極23の上端部の側面は、上記3つのシリコン窒化膜に、絶縁側壁31を加えた4つのシリコン窒化膜が形成されている。さらに、ゲート電極23は上下でほぼ同じ幅をもつ柱状体に形成されている。したがって、コンタクト38において、絶縁側壁31によって挟まれていないシリコン基板10に近い部分は、絶縁側壁31で挟まれている部分より太く形成されている。

層間絶縁膜33におけるコンタクトホール37は、自己整合型のコンタクトホール37の開口によって、ゲート電極23上に形成されたハードマスクの領域まで広げて形成されている。よって、コンタクト38の層間絶縁膜33の部分は、絶縁側壁31によって挟まれた部分より広くなっている。

【0018】

次に、第1の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置1のゲート電極23に電圧を負荷する。そうすると、ゲート電極23とシリコン基板10との間に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。シリコン基板10のシリコン酸化膜18に覆われた部分がチャネルとして働き、反転層が形成される。そしてソース・ドレイン領域28の間に電圧を負荷すれば、反転層内をキャリアが移動し、電流が流れる。ゲート電極23の電圧を変化させることによって、ソース・ドレイン領域28の間を流れる電流量を制御する。

【0019】

次に、第1の実施形態に係る半導体装置の効果について説明する。

本実施形態においては、積層体81の上部の側面上には絶縁側壁31が設けられているため、ゲート電極23とコンタクト38との短絡が確実に防止される。一方、積層体81の下部、すなわちゲート電極23におけるゲート絶縁膜に接する部分の側面には絶縁側壁31が設けられていない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。したがって、微細化が進んで電極間の幅が狭くなっても、ソース・ドレイン領域28との間の導電性を確保しつつ、ゲート電極23との短絡を確実に防止して、自己整合型のコンタクト38を形成することができる。この結果、半導体装置1の高集積化を図ることができる。

【0020】

(第2の実施形態)

次に、第2の実施形態について説明する。

本実施形態は、リセス型トランジスタの半導体装置についてのものである。

図3は、第2の実施形態に係る半導体装置を例示する斜視図である。

図4は、第2の実施形態に係る半導体装置を例示する断面図であり、図3に示すA−A’面による断面図である。

先ず、第2の実施形態に係る半導体装置の構成について説明する。

図3及び図4に示すように、本実施形態に係る半導体装置2において、シリコン基板10には、STI領域17及び活性領域16が延びる方向に直交する方向に溝51が設けられている。

【0021】

溝51の内面上には、ゲート絶縁膜として、例えばシリコン酸化膜18が設けられている。また、溝51の内部には、導電材料、例えばポリシリコンが埋め込まれている。溝51の内部に埋め込まれたポリシリコンの部分を、下部導電部65という。ポリシリコンには、不純物、例えばリンが導入されている。

活性領域16の表層部分における溝51の外縁を含む領域には、不純物、例えばリンが導入された拡張領域26が形成されている。活性領域26の表層部分における溝を挟んで両側の拡張領域26の隣には、それぞれソース・ドレイン領域28が形成されている。

【0022】

また、溝51上には、溝51に沿って、溝51の幅と略等しい幅で、導電材料からなる柱状体が設けられている。この溝51上に設けられた柱状体は、溝51の内部に埋設された導電材料と同じ材料のポリシリコンからなり、溝51の内部に埋め込まれた下部導電部65と一体化している。溝51上に設けられたポリシリコンの柱状体を上部導電部66という。上部導電部66と下部導電部65を合わせて導電部67という。

【0023】

上部導電部66上には、バリアメタル膜20が設けられている。バリアメタル膜20としては、チタンと窒化チタンの積層膜及び窒化チタン膜が挙げられる。バリアメタル膜20上には、低抵抗金属膜21が設けられている。低抵抗金属膜21上には、ハードマスク22が設けられている。導電部67、バリアメタル膜20及び低抵抗金属膜21とから、ゲート電極23が形成される。

【0024】

ハードマスク22、低抵抗金属膜21及びバリアメタル膜20は積層して、柱状体62を構成している。柱状体62におけるバリアメタル膜20が、チタンと窒化チタンの積層膜である場合には、製造工程における酸化熱処理で、積層膜に含まれるチタンが酸化することがある。そこで、チタンの酸化を防ぐために、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20からなる積層体の側面上に、バリアメタル側壁61が設けられている。バリアメタル側壁61の材料としては、窒化シリコンがあげられる。バリアメタル側壁61が設けられている場合は、バリアメタル側壁61を含んだ積層構造を柱状体62という。

【0025】

上部導電部66及び柱状体62とで、柱状体63を構成する。また、柱状体63、下部導電部65及びシリコン酸化膜18を含む積層膜を積層体81という。

隣り合う柱状体63の間には、柱状体63がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。

積層体81における柱状体63の側面には、エクステンション側壁25とソース・ドレイン側壁27が設けられている。

【0026】

ソース・ドレイン側壁27の側面上及びシリコン基板10における柱状体63の直下域間に位置する部分上には、ストッパー膜29が設けられている。

積層体81における柱状体63の上部の両側面上には、絶縁側壁31が設けられている。本実施形態においてもゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われない。よって、コンタクト38における絶縁側壁31によって挟まれていない部分は、絶縁側壁31によって挟まれている部分よりも太くなっている。

本実施形態における上記以外の構成は、前述の第1の実施形態と同様であるので説明を省略する。

【0027】

次に、第2の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置2のゲート電極23に電圧を負荷する。そうすると、溝51の内面上に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。シリコン基板10の溝51に沿った領域がチャネルとして働き、反転層が形成される。

本実施形態における上記以外の動作は、前述の第1の実施形態と同様であるので、説明を省略する。

【0028】

次に、第2の実施形態に係る半導体装置の効果について説明する。

本実施形態においても、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

【0029】

また、リセス構造のトランジスタを製造することができ、ゲート電極23の幅を微細化しつつ、チャネル長を増加させることができる。また、ソース・ドレイン領域28の端が広がり、チャネルを流れる電流量を増加させることができる。

本実施形態における上記以外の効果は、前述の第1の実施形態と同様であるので説明を省略する。

【0030】

(第3の実施形態)

次に、第3の実施形態について説明する。

本実施形態は、フィン型トランジスタの半導体装置である。

図5は、第3の実施形態に係る半導体装置を例示する斜視図である。

図6は、第3の実施形態に係る半導体装置を例示する断面図であり、図5に示すA−A’面による断面図である。

先ず、本実施形態に係る半導体装置の構成について説明する。

図5及び図6に示すように、半導体装置3においては、半導体基板、例えばシリコン基板10が設けられている。

【0031】

シリコン基板10の上面には、1つの方向に延びるように形成された複数の柱状体75が平行に形成されている。柱状体75は、シリコン基板10と一体化しており、シリコン基板10から突出した形状となっている。柱状体75の下部の幅は、上部の幅より大きくなっている。柱状体75と柱状体75との間には、柱状体75の突出した高さより低くシリコン酸化膜73が形成されている。シリコン酸化膜73が形成されている領域をSTI領域74という。柱状体75のシリコン酸化膜73から上の部分をフィン72という。したがって、フィン72もシリコン基板10の上面に、1つの方向に延びるように形成されている。

【0032】

ゲート電極23は、フィン72上を含むシリコン基板10上に、フィン72が延びる方向に対して垂直な方向に延びるように設けられている。隣り合うゲート電極23の間には、ゲート電極23がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。溝24の幅方向の長さを「幅」という。ゲート絶縁膜として、例えばシリコン酸化膜18は、ゲート電極23におけるフィン72の上面上及び側面上に面する面に設けられている。

【0033】

ゲート電極23は、多層膜構造とされている。多層膜構造を構成する膜は、下からポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21とされている。低抵抗金属膜21上には、ハードマスク22が設けられている。ハードマスク22、ゲート電極23及びシリコン酸化膜18を含む積層膜を積層体81という。

フィン72の上面及び側面の上層部分におけるゲート電極23の直下域の両側には、拡張領域26が形成されている。フィン72の上面及び側面の上層部分におけるゲート電極23の直下域間の領域であって、拡張領域26間の領域には、ソース・ドレイン領域28が形成されている。

【0034】

積層体81の側面上には、フィン72を跨ぐようにエクステンション側壁25が設けられている。エクステンション側壁25の側面上には、フィン72を跨ぐようにソース・ドレイン側壁27が設けられている。

ソース・ドレイン側壁27の側面上及びフィン72におけるゲート電極23の直下域間に位置する部分上には、ストッパー膜29が設けられている。

【0035】

積層体81の上部の両側面上には、絶縁側壁31が設けられている。第3の実施形態においても、ゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われない。よって、コンタクト38における絶縁側壁31によって挟まれていない部分は、絶縁側壁31によって挟まれている部分よりも太くなっている。

本実施形態における上記以外の構成は、前述の第1及び第2の実施形態と同様であるので説明を省略する。

【0036】

次に、第3の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置3のゲート電極23に電圧を負荷する。そうすると、フィン72の上面上及び側面上に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。フィン72のシリコン酸化膜18で覆われた領域がチャネルとして働き、反転層が形成される。

本実施形態における上記以外の動作は、前述の第1及び第2の実施形態と同様であるので説明を省略する。

【0037】

次に、第3の実施形態に係る半導体装置の効果について説明する。

本実施形態においても、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

また、フィン構造のトランジスタを製造することができ、ゲート電極23の幅を微細化しつつ、ゲート電極23に接するチャネル面積を増大させ、チャネルを流れる電流量を増加させることができる。

本実施形態における上記以外の効果は、前述の第1及び第2の実施形態と同様である。

【0038】

(第4の実施形態)

次に、第4の実施形態について説明する。

本実施形態は、第1の実施形態に係る半導体装置の製造方法である。

図7〜図11は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図12は、第4の実施形態に係る半導体装置の製造方法を例示する工程平面図であり、

図13は、図12に示すA−A’線による工程断面図であり、

図14は、図12に示すB−B’線による工程断面図であり、

図15は、図12に示すC−C’線による工程断面図であり、

図16〜図24は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図25は、第4の実施形態に係る半導体装置のゲート電極の上部を例示する断面図である。

【0039】

先ず、図7に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。その後、シリコン基板10上にハードマスク11となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク11を形成する。ハードマスク11は、シリコン基板10上の1つの方向に平行に形成する。

【0040】

そして、図8に示すように、ハードマスク11をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分にSTI領域17となる溝12を形成する。このとき、ハードマスク11に覆われて、エッチングされない領域が活性領域16となる。

その後、図9に示すように、溝12及びハードマスク11を含むシリコン基板10上をシリコン酸化膜13で覆う。そして、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスクの表面が現れるまでシリコン酸化膜13を研磨し、シリコン酸化膜13の上面を平坦化する。

【0041】

次に、図10に示すように、ウェットエッチングによって、ハードマスク11(図9参照)の下面まで、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面まで、シリコン酸化膜13を除去する。その後、ウェットエッチングにより、ハードマスク11を除去する。シリコン基板10の上面が現れている領域が活性領域16である。また、溝12の中にシリコン酸化膜13が埋め込まれた領域がSTI領域17である。STI領域17ではシリコン酸化膜13の上面が表面に現れている。

【0042】

そして、図11に示すように、活性領域16及びSTI領域17を含むシリコン基板10の上面に、シリコン酸化膜14を形成する。その後、シリコン酸化膜14上から、イオン注入法によって、不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝12の底部より深い領域までとする。これによって、活性領域16においては、シリコン基板10の上面から、溝12の底部より深い領域に相当する深さまで、シリコン基板10中にボロンが導入される。STI領域17においては、溝12の底面から、溝12の底部より深い領域まで、シリコン基板10中にボロンが導入される。シリコン基板10におけるボロンが導入された領域がp形のウェル15となる。

【0043】

図12〜図15に示すように、上述の工程により、シリコン基板10上に、1つの方向に平行に延びるSTI領域17を形成する。そして、STI領域17の間に配置されるように活性領域16が形成される。

シリコン基板10の表面には、シリコン酸化膜14が形成されているが、図12においては、図示を省略してある。

【0044】

次に、図16に示すように、半導体基板10上のシリコン酸化膜14(図13〜図15参照)を除去し、シリコン基板10の上面上にゲート絶縁膜として、例えばシリコン酸化膜18を形成する。

その後、図17に示すように、シリコン酸化膜18上から、ゲート電極23の一部となるポリシリコン膜19を形成する。次に、ポリシリコン膜19上からバリアメタル膜20として、例えば窒化タングステン膜(WN)を形成する。そして、その上から低抵抗金属膜21として、例えばタングステン膜(W)を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21を含んでいる。

【0045】

低抵抗金属膜21上に、ハードマスク22を形成する。ハードマスク22は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク22は、STI領域17が延びる方向に直交する方向に延びる複数本の帯状の部分とする。

次に、図18に示すように、ハードマスク22をマスクとして、反応性イオンエッチングを行い、低抵抗金属膜21、バリアメタル膜20、ポリシリコン膜19及びゲート絶縁膜18を選択的に除去する。これによって、ゲート絶縁膜18、ポリシリコン膜19、バリアメタル膜20,低抵抗金属膜21及びハードマスク22が積層された積層体81が形成される。積層体81のうち、低抵抗金属膜21、バリアメタル膜20及びポリシリコン膜19により、ゲート電極23が形成される。一方、ハードマスク22で覆われていない部分の表面には、シリコン基板10が現れている。

【0046】

積層体81は、STI領域17が延びる方向に直交する方向に延びた柱状体として形成される。隣り合うゲート電極23の間には溝24が形成される。すなわち、形成された溝24は、ゲート電極23を分断している。溝24は、ゲート電極23が延びる方向と同じ方向に延びている。

【0047】

次に、図19に示すように、積層体81の側面上にエクステンション側壁25を形成する。エクステンション側壁25は、シリコン基板10上にシリコン窒化膜を形成した後、積層体81の側面上以外の部分を除去して形成する。そして、積層体81及びエクステンション側壁25をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体81及びエクステンション側壁25に覆われていない領域に拡張領域26を形成する。

【0048】

さらに、積層体81の側面上にソース・ドレイン側壁27を形成する。そして、積層体81、エクステンション側壁25、ソース・ドレイン側壁27をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体81、エクステンション側壁25及びソース・ドレイン側壁27に覆われていない領域にソース・ドレイン領域28を形成する。

ソース・ドレイン領域28には、拡張領域26に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域28には、拡張領域26より深くリンを注入する。

【0049】

その後、ニッケルを堆積した後、加熱することにより、ソース・ドレイン領域28の表面をシリサイド化する。次に、未反応のニッケルを除去する。

次に、ソース・ドレイン側壁27の側面上及びシリコン基板10における積層体81の直下域間に位置する部分上に、ストッパー膜29を形成する。ストッパー膜29は、シリコン基板10上にシリコン窒化膜を形成した後、ソース・ドレイン側壁27の側面上及びシリコン基板10における積層体81の直下域間に位置する部分上以外の部分を除去して形成する。これにより、積層体81の側面上には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29の3つのシリコン窒化膜が形成されている。

【0050】

次に、図20に示すように、溝24の内部の底部に、犠牲材30を埋め込む。犠牲材30の材料としては、炭素を含む材料があげられる。炭素を含む材料を溝24に埋め込む方法としては、CVD法等を用いて埋め込む方法があげられる。先ず、シリコン基板10上に、炭素、水素及び窒素を含む材料を堆積して膜を形成する。炭素の含有率が100%に近い膜も形成することができる。炭素、水素及び窒素を含む材料は、ゲート電極23間、すなわち溝24の下部であって、少なくともハードマスク22間の空間を含む部分に埋め込まれる。次に、溝24の内部の底部以外の部分を除去して犠牲材30を形成する。犠牲材30の上面は、ゲート電極23の低抵抗金属膜21が形成されている位置より下方とする。犠牲材30を埋め込む方法としては、CVD法の他、スパッタ法やスピン塗布法があげられる。スパッタ法は、炭素を含む材料をターゲットに用いて、スパッタリングにより炭素を含む材料を溝24に埋め込む。スピン塗布法は、炭素を含む材料をシリコン基板10上に塗布して、炭素を含む材料を溝24に埋め込む。埋め込んだ後は、CVD法と同様に、溝24の内部の底部以外の部分を除去して犠牲材30を形成する。

【0051】

次に、図21に示すように、積層体81の側面上に、絶縁側壁31を形成する。絶縁側壁31は、CVD法等によりシリコン基板10上にシリコン窒化膜を形成した後、積層体81の側面上以外の部分をRIE法により除去して形成する。絶縁側壁31の上端は積層体81の上面と一致する。絶縁側壁31の下端は、犠牲材30の上面と一致する。犠牲材30の上面をゲート電極23の低抵抗金属膜21が形成されている位置より下方としたので、絶縁側壁31の下端も、ゲート電極23の低抵抗金属膜21が形成されている位置より下方となる。したがって、ゲート電極23の上端部の側面は絶縁側壁31で覆われ、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0052】

その後、図22に示すように、アッシング法により、犠牲材30を除去する。これにより、積層体81のハードマスク22及び低抵抗金属膜21の側面上には、エクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の4つのシリコン窒化膜が形成されている。

一方、犠牲材30で覆われていた積層体81の側面上には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29の3つのシリコン窒化膜が形成されている。これらのシリコン窒化膜は、半導体装置1の製造過程において、一体化することはなく、半導体装置1が製造された後においても、区別することができる。

【0053】

次に、図23に示すように、溝24の内部に、例えばポリシラザン等のシリコン酸化膜32を埋め込み、CMP法によってハードマスク22の表面並びにエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の一端が現れるまでシリコン酸化膜32を研磨し、シリコン酸化膜32の上面を平坦化する。そして、層間絶縁膜33としてシリコン酸化膜を堆積し、その上に多層レジスト膜として、有機膜34、シリコン酸化膜35及びレジスト36を形成する。

【0054】

次に、図24に示すように、コンタクトホール37のパターニングを行う。自己整合型のコンタクトホール37におけるレジスト36の開口領域は、ソース・ドレイン領域28の上面におけるコンタクト38との接合部分に対応する領域だけではなく、ゲート電極23のハードマスク22に対応する領域まで広げられる。このとき、レジスト36及びハードマスク22がエッチングのストッパーとなる。そして、レジスト36をマスクとして、RIE法を行い、シリコン酸化膜35、有機膜34、層間絶縁膜33及びシリコン酸化膜32を選択的に除去する。このようにして、ゲート電極23間にソース・ドレイン領域28に到達するコンタクトホール37が形成される。

【0055】

自己整合型のコンタクトホール37におけるレジスト36のパターニングの形状は、ホール形状の他、溝24に沿ったライン形状の場合もある。このような場合でもゲート電極23のハードマスク25がエッチングのストッパーとなり、ゲート電極23間にコンタクトホール37が形成される。

その後、コンタクトホール37に、導電部材、例えばチタン等のバリアメタル及びタングステン等のメタル材料を埋め込み、コンタクト38を形成する。

このようにして、図1及び図2に示すように、半導体装置1が製造される。

【0056】

次に、本実施形態の効果について説明する。

図25に示すように、本実施形態においては、ハードマスク22及び低抵抗金属膜21の側面上にはエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の4つのシリコン窒化膜を含むシリコン窒化膜40が形成されている。なお、図25では、4つのシリコン窒化膜を区別していないが、これらのシリコン窒化膜は、半導体装置1の製造過程において、一体化することはなく、半導体装置1が製造された後においても、区別することができる。

【0057】

したがって、自己整合のコンタクトホール37の形成工程において、ハードマスク22及びシリコン窒化膜40の上面は広く露出している。コンタクトホール37を形成するエッチング時に、溝24の内部のシリコン酸化膜32では、シリコン酸化膜32から酸素が供給されることで、エッチングガスに含まれるカーボンが除去され、シリコン酸化膜32上にはエッチング生成物41が堆積しない。一方、ハードマスク22及びシリコン窒化膜40は、膜中に酸素を含まないため、カーボンが除去されず、エッチング生成物41が堆積される。

【0058】

絶縁側壁31が形成されて、レジスト36のパターニングで開口されたハードマスク22及びシリコン窒化膜40の上面の面積は広くなっているため、ハードマスク22及びシリコン窒化膜40の上面には、エッチングガスが供給されやすく、エッチング生成物41は、ハードマスク22及びシリコン窒化膜40上に厚く堆積し、エッチングのストッパーの役目をする。したがって、シリコン酸化膜32はエッチングが進むが、ハードマスク22及びシリコン窒化膜40はエッチングが進まず、ゲート電極23の低抵抗金属膜21とコンタクト38とは電気的な接触を起こすことがない。

【0059】

一方、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

また、犠牲材30の材料として、炭素を含む材料とすると、窒化シリコンを材料とするハードマスク22、バリアメタル側壁61、エクステンション側壁25及びソース・ドレイン側壁27並びに酸化シリコンを材料とするSTI領域17及びゲート絶縁膜はエッチングされずに、犠牲材30をエッチングすることができる。

したがって、本実施形態によれば、微細化が進んで電極の幅が狭くなっても自己整合型のコンタクトホールを形成することができるので、集積度が高い半導体装置を製造することができる。

【0060】

(第4の実施形態の比較例)

次に、第4の実施形態の比較例について説明する。

本比較例においては、絶縁側壁31を形成しない場合における半導体装置の製造方法である。

図26及び27は、第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

図28(a)及び(b)は、第4の実施形態の比較例に係る半導体装置のゲート電極の上部を例示する断面図である。

第4の実施形態における図7〜図19に示す工程は、比較例においても同様なので説明を省略する。

【0061】

図26に示すように、本比較例においては、絶縁側壁31を形成しないで、シリコン酸化膜32、層間絶縁膜33、有機膜34、シリコン酸化膜35及びレジスト36を形成する。

その後、図27に示すように、コンタクトホール37を形成し、コンタクトホール37に、コンタクト38を形成する。

本比較例においては、図27に示すように、ゲート電極23の低抵抗金属膜21とコンタクト38とが電気的な接触を起こしている。

【0062】

図28(a)及び(b)に示すように、本比較例においては、絶縁側壁31を形成していない。シリコン窒化膜40には、絶縁側壁31が含まれない。したがって、自己整合のコンタクトホール37の形成工程において、ハードマスク22及びシリコン窒化膜40の上面に露出している面積は、第4の実施形態の場合と比べて狭くなっている。よって、ハードマスク22及びシリコン窒化膜40の上面には、エッチングガスが供給されづらく、エッチングのストッパーとなるエッチングの生成物41が堆積しづらい。また、図28(b)に示すように、角部のエッチングはイオンの入射が完全に垂直ではないことから、傾斜形状となり平坦部に比べてエッチングが進みやすい。そのため、比較例におけるハードマスク22及びシリコン窒化膜40がエッチングされる。

それにより、ゲート電極23の低抵抗金属膜21とコンタクト38とが電気的な接触を起こしてしまう。

【0063】

(第5の実施形態)

次に、第5の実施形態について説明する。

本実施形態は、第2の実施形態に係る半導体装置の製造方法の実施形態である。

以下、図面を参照しつつ、本実施形態について説明する。

図29〜図38は、第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図7〜図15に示す工程を実施する。これらの工程については、説明を省略する。

【0064】

次に、図29に示すように、図12のB−B’線における断面に相当する断面においては、シリコン基板10上にハードマスク50となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク50を形成する。ハードマスク50は、STI領域17を形成するための溝12と直交する方向に延びている。

次に、図30に示すように、ハードマスク50をマスクとして、反応性イオンエッチングを行うことにより、シリコン酸化膜14及びシリコン基板10を選択的に除去する。これにより、溝51が形成される。

【0065】

また、図31に示すように、図12のC−C’線における断面に相当する断面においては、STI領域17においても、シリコン基板10上にハードマスク50となる膜として、シリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク50を形成する。

次に、図32に示すように、ハードマスク50をマスクとして、反応性イオンエッチングにより、シリコン酸化膜13及びシリコン酸化膜14を選択的に除去する。これにより、溝51が形成される。

このように、図12に示すB−B’線による活性領域における溝51の内部と、図12に示すC−C’線によるSTI領域における溝51の内部は同じ構成となっている。そこで、以後は活性領域16における工程断面図のみ示す。

【0066】

次に、図33に示すように、シリコン基板10上のハードマスク50及びシリコン酸化膜14を除去し(図29〜図32参照)、溝51の内面上及びシリコン基板10の上面上にゲート絶縁膜となるシリコン酸化膜18を形成する。次に、シリコン酸化膜18上からゲート電極23の一部となるポリシリコン膜19を形成する。このポリシリコン膜19にはリンが不純物として導入されている。ポリシリコン膜19は、溝51内を埋め込むように形成する。

【0067】

その後、ポリシリコン膜19上からバリアメタル膜20として、例えばチタンと窒化チタンの積層膜を積層する。そして、その上から低抵抗金属膜21として、例えばタングステン(W)膜を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル層20及び低抵抗金属層21を含んでいる。バリアメタル膜20の材料としては、チタンと窒化チタンの積層膜の他、窒化チタンがあげられる。

【0068】

そして、低抵抗金属層21上から、シリコン窒化膜56及び有機膜57を形成した後、その上に、シリコン酸化膜58を形成する。さらにシリコン酸化膜58上に、レジスト59を形成する。このとき、レジスト59の形成領域は、溝51の直上域と一致させる。

次に、レジスト59をマスクとして、シリコン酸化膜58をパターニングする。

その後、パターニングされたシリコン酸化膜58をマスクとして有機膜57及びシリコン窒化膜56を加工する。

【0069】

次に、図34に示すように、本実施形態では、シリコン酸化膜58及び有機膜57を除去し、パターニングされたシリコン窒化膜56をハードマスク22とする。

次に、図35に示すように、ハードマスク22をマスクとして反応性イオンエッチングを行い、低抵抗金属膜21及びバリアメタル膜20を選択的に除去する。これによって、ハードマスク22で覆われている部分には、低抵抗金属膜21及びバリアメタル膜20からなるゲート電極23の一部が形成される。

一方、ハードマスク22で覆われていない部分の表面には、ポリシリコン膜19が現れている。

【0070】

バリアメタル膜20として窒化チタンとチタンの積層膜を用いた場合は、ゲート電極加工後の後酸化のときにチタンが酸化されて劣化する可能性がある。

そこで、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜の側面上に、バリアメタル側壁61を形成する。バリアメタル側壁61の材料としては、例えば、シリコン窒化膜があげられる。バリアメタル側壁61は、CVD法(chemical vapor deposition:化学気相成長法)等により、シリコン窒化膜を形成した後、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜の側面上以外の部分を除去して形成する。

【0071】

バリアメタル側壁61を形成した場合は、バリアメタル側壁61、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜を柱状体62という。バリアメタル側壁61を形成しない場合は、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜を柱状体62という。

次に、ポリシリコン膜19の加工を行う。本実施形態においては、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21の三層構造とされている。したがって、ポリシリコン膜19は、ゲート電極23の最下層膜となっている。

【0072】

次に、図36に示すように、ポリシリコン膜19におけるゲート電極23の間に形成された部分を除去する。ゲート電極23の間のポリシリコン膜19の部分が除去されて、シリコン酸化膜18が表面に現れる。

その後、図37に示すように、ゲート電極23間のシリコン基板10上のシリコン酸化膜18、すなわち、ゲート絶縁膜となる溝51の内面上のシリコン酸化膜18以外のシリコン酸化膜18を除去する。溝51内には、シリコン酸化膜18が残存している。

柱状体62及び上部導電部66を含む積層膜を柱状体63という。また、柱状体63、下部導電部65及びシリコン酸化膜18を含む積層膜を積層体81という。

【0073】

そして、積層体81における柱状体63の側面上にエクステンション側壁25を形成する。次に、柱状体63及びエクステンション側壁25をマスクとして、シリコン基板10にリンをイオン注入して、拡張領域26を形成する。

さらに、積層体81における柱状体63の側面上にソース・ドレイン側壁27を形成する。そして、柱状体63、エクステンション側壁25及びソース・ドレイン側壁27をマスクとして、シリコン基板10にリンをイオン注入して、ソース・ドレイン領域28を形成する。

【0074】

次に、第4の実施形態における図19〜図22に示す工程を行って、ストッパー膜29、絶縁側壁31を形成する。本実施形態においても、ゲート電極23の上端部の側面は、絶縁側壁31で覆われ、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

さらに、第4の実施形態における図23〜図24に示す工程を行って、シリコン基板10上から層間絶縁膜33、多層レジスト膜を形成する。

そして、図38に示すように、自己整合型のコンタクトホール37を形成し、コンタクト38を設ける。

このようにして、図3及び図4に示すように、半導体装置2が製造される。

【0075】

次に、第5の実施形態に係る半導体装置の製造方法の効果について説明する。

リセス構造のトランジスタを実現でき、高集積化を図ることができる半導体装置を提供することができる。

本実施形態における上記以外の効果は、前述の第4の実施形態と同様であるので説明を省略する。

【0076】

(第6の実施形態)

次に、第6の実施形態に係る半導体装置の製造方法について説明する。

図39〜図44は、第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、各図の(a)は(b)に示すB−B’線による工程断面図であり、各図の(b)は、(a)に示すA−A’線による工程断面図である。

先ず、図39に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。その後、シリコン基板10上にハードマスク71となる膜として、例えばシリコン窒化膜を形成した後、フォトグラフィー法等でパターニングしてハードマスク71を形成する。ハードマスク71は、シリコン基板10上の1つの方向に平行に形成する。 そして、図40に示すように、ハードマスク71をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分を選択的に除去する。

【0077】

ハードマスク71で覆われた部分が柱状体75となる。柱状体75は、ハードマスク71と同様に、シリコン基板10上の1つの方向に平行に形成される。柱状体75は、シリコン基板10と一体化しており、シリコン基板10から突出した形状となる。柱状体75の延びる方向と垂直な方向を「幅」といい、柱状体75の幅方向に面する2つの面を「側面」という。柱状体75の下部の幅は、上部の幅より大きく形成する。

【0078】

次に、図41に示すように、ハードマスク71で覆われた柱状体75を含むシリコン基板10上をシリコン酸化膜73で覆う。そして、CMP法によって、ハードマスク71の表面が現れるまでシリコン酸化膜73を研磨し、シリコン酸化膜73の上面を平坦化する。

次に、図42に示すように、ハードマスク71(図41参照)をマスクとしてシリコン酸化膜73をドライエッチングにより下方に後退させる。そして、ハードマスク71を除去する。残留したシリコン酸化膜73がある領域をSTI領域74とする。柱状体75のシリコン酸化膜73から上の部分をフィン72という。したがって、フィン72もシリコン基板10の上面に、1つの方向に延びるように形成されている。また、フィン72の延びる方向と垂直な方向を「幅」といい、幅方向に面する2つの面を「側面」という。

【0079】

次に、図43に示すように、フィン72の上面上及び側面上にゲート絶縁膜として、例えばシリコン酸化膜18を形成する。

その後、シリコン酸化膜18上から、ゲート電極23の一部となるポリシリコン膜19を形成する。ポリシリコン膜19は、フィン72を覆うように、フィン72の高さ以上に形成する。

【0080】

そして、ポリシリコン膜19上からバリアメタル膜20として、例えば窒化タングステン膜を形成する。そして、その上から低抵抗金属膜21として、例えばタングステン膜を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21を含んでいる。

低抵抗金属膜21上に、ハードマスク22を形成する。ハードマスク22は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク22は、フィン72の方向に直行するように形成する。

【0081】

次に、ハードマスク22をマスクとして、反応性イオンエッチングを行い、低抵抗金属膜21、バリアメタル膜20、ポリシリコン膜19及びシリコン酸化膜18を選択的に除去する。これによって、ハードマスク22で覆われている部分には、低抵抗金属膜21、バリアメタル膜20及びポリシリコン膜19を含むゲート電極23が形成される。

一方、ハードマスク22で覆われていない部分の表面には、フィン72の上面及び側面が現れている。

【0082】

また、ハードマスク22、ゲート電極23及びシリコン酸化膜18を含む積層体81は、フィン72及びSTI領域74が延びる方向に直交する方向に延びた柱状体として形成する。隣り合う積層体81の間には溝24が形成される。すなわち、形成された溝24は、積層体81を分断している。溝24は、積層体81が延びる方向と同じ方向に延びている。

【0083】

次に、図44に示すように、第4の実施形態における図19〜図22の工程を行って、積層体81の側面上にエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31を形成する。エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29は、フィン72を跨ぐように、フィン72の上面上及び側面上に形成される。

また、本実施形態においても、ゲート電極の上端部の側面は、絶縁側壁31で覆われ、

ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0084】

そして、第4の実施形態における図23〜図24に示すような工程を行って、層間絶縁膜33、多層レジスト膜を形成する。そして、自己整合型のコンタクトホール37を形成し、コンタクト38を形成する。

このようにして、図5及び図6に示すように、半導体装置3が製造される。

【0085】

以上説明した実施形態によれば、高集積化を図ることができる半導体装置及びその製造方法を提供することができる。

【0086】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0087】

1、2、3:半導体装置、10:シリコン基板、11、22、50、71:ハードマスク、12、24、51、82:溝、13、14、18、32、35、58、73:シリコン酸化膜、15:ウェル、16:活性領域、17、74:STI領域、19:ポリシリコン膜、20:バリアメタル膜、21:低抵抗金属膜、23:ゲート電極、25:エクステンション側壁、26:拡張領域、27:ソース・ドレイン側壁、28:ソース・ドレイン領域、29:ストッパー膜、30:犠牲材、31:絶縁側壁、33:層間絶縁膜、34、57:有機膜、36、59:レジスト、37:コンタクトホール、38:コンタクト、40、56:シリコン窒化膜、41:生成物、61:バリアメタル側壁、62、63、75:柱状体、65:下部導電部、66上部導電部、67:導電部、72:フィン、81:積層体

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の微細化に伴い、自己整合による工程が多用されている。

半導体装置の製造方法における自己整合とは、既に形成されたパターンを次のプロセスのマスクとして利用し、マスクの位置合わせなしで次のプロセスを進めることである。

1つの例として、ゲート電極をマスクとしてイオン注入することによりソース・ドレイン領域を形成することがあげられる。この場合、ゲート電極の位置とソース・ドレイン領域の位置とをリソグラフィの制約なしに決定することができる。

【0003】

自己整合型のコンタクトホール(Self Align Contact:SAC)の場合は、コンタクトホールを加工するためのレジストパターンの開口を、コンタクト部分だけでなく、ゲート電極上に形成されたハードマスクの領域まで広げることができる。そして、レジストパターンと共にゲート電極上のハードマスクがエッチングのストッパーとなり、隣り合うゲート電極の間に所望のコンタクトホールが形成される。また、このときのレジストパターンの開口は、必ずしもホール形状だけではなく、ライン状に延びた開口としてもよい。この場合も、ゲート電極上のハードマスクがエッチングのストッパーとなって、隣り合うゲート電極の間にコンタクトホールが形成される。これにより、レジストパターンを形成するためのリソグラフィの難易度を下げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−079492号公報

【特許文献2】特開平10−032243号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0006】

実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

【0007】

また、実施形態に係る半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、前記導電膜上に、絶縁性であり、相互に平行に延びる複数本のハードマスクを形成する工程と、前記ハードマスクをマスクとして前記導電膜及び前記絶縁膜をエッチングすることにより、前記絶縁膜、前記導電膜及び前記ハードマスクが積層され、相互に平行に延びる複数本の積層体を形成する工程と、前記積層体間の空間の下部であって、少なくとも前記絶縁膜間の空間を含むが前記ハードマスク間の空間を含まない部分に犠牲材を埋め込む工程と、前記積層体の側面上であって、前記犠牲材上に前記絶縁側壁を形成する工程と、前記犠牲材を除去する工程と、前記半導体基板上に前記積層体を覆う層間絶縁膜を形成する工程と、前記層間絶縁膜に、前記半導体基板に到達する貫通孔を形成する工程と、前記貫通孔内に導電材料を埋め込んでコンタクトを形成する工程と、を備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る半導体装置を例示する斜視図である。

【図2】第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【図3】第2の実施形態に係る半導体装置を例示する斜視図である。

【図4】第2の実施形態に係る半導体装置を例示する断面図であり、図3に示すA−A’面による断面図である。

【図5】第3の実施形態に係る半導体装置を例示する斜視図である。

【図6】第3の実施形態に係る半導体装置を例示する断面図であり、図5に示すA−A’面による断面図である。

【図7】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図10】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】第4の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図13】図12に示すA−A’線による工程断面図である。

【図14】図12に示すB−B’線による工程断面図である。

【図15】図12に示すC−C’線による工程断面図である。

【図16】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図20】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図21】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図22】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図23】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図24】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図25】第4の実施形態に係る半導体装置のゲート電極の上部を例示する断面図である。

【図26】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図27】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図28】(a)及び(b)は、第4の実施形態の比較例に係る半導体装置のゲート電極の上部を例示する断面図である。

【図29】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図30】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図31】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図32】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図33】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図34】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図35】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図36】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図37】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図38】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図39】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図40】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図41】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図42】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図43】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【図44】(a)及び(b)は第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、(a)は(b)に示すB−B’線による工程断面図であり、(b)は(a)に示すA−A’線による工程断面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

本実施形態は、半導体装置の実施形態である。

図1は、第1の実施形態に係る半導体装置を例示する斜視図である。

図2は、第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【0010】

先ず、第1の実施形態に係る半導体装置1の構成について説明する。

図1及び図2に示すように、半導体装置1においては、半導体基板、例えばシリコン基板10が設けられている。シリコン基板10の上面には、1つの方向に延びる複数の溝12が相互に平行に形成されている。溝12の内部には、絶縁材料、例えば酸化シリコン13が埋め込まれている。溝12の内部に酸化シリコン13が埋め込まれた領域をSTI領域(Shallow Trench Isolation)17とする。STI領域17に挟まれた領域を活性領域16とする。

【0011】

シリコン基板10には、シリコン基板10の上面から、溝12の底面より深い領域まで、不純物、例えばボロンが導入されて、ウェル15が形成されている。

シリコン基板10上には、相互に平行に延びる複数本の積層体81が設けられている。積層体81は、溝12と直交する方向に延びている。隣り合う積層体81の間には、積層体81がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。

【0012】

積層体81の最下部には、ゲート絶縁膜として、例えばシリコン酸化膜18が設けられている。シリコン酸化膜18上には、ゲート電極23が設けられている。ゲート電極23の構造は多層膜構造である。すなわち、ゲート電極23は、下から順に、ポリシリコン膜19、バリアメタル膜20、低抵抗金属膜21で構成されている。ポリシリコン膜19には、例えばリン等の不純物が導入されたポリシリコンによって形成されている。バリアメタル膜20としては、例えば窒化タングステン膜があげられる。低抵抗金属膜21としてはタングステン膜があげられる。低抵抗金属膜21上には、ハードマスク22が設けられている。ハードマスク22の材料としては、窒化シリコンがあげられる。

【0013】

シリコン基板10の上層部分におけるゲート電極23の直下域の両側には、不純物、例えばリンが導入された拡張領域26が形成されている。シリコン基板10の上層部分におけるゲート電極23の直下域間の領域であって、拡張領域26間の領域には、ソース・ドレイン領域28が形成されている。ソース・ドレイン領域28には、不純物、例えばリンが、拡張領域26に導入された濃度より高濃度で導入されている。また、ソース・ドレイン領域28には、不純物、例えばリンが、拡張領域26より深く導入されている。ソース・ドレイン領域28の表層には、シリサイド層、例えば、ニッケルシリサイド層(図示せず)が形成されている。

【0014】

積層体81の側面上には、エクステンション側壁25が設けられている。エクステンション側壁25の側面上には、ソース・ドレイン側壁27が設けられている。エクステンション側壁25の側面の端部を上から見た位置は、拡張領域26のゲート電極23側の端部を上から見た位置と略同一である。ソース・ドレイン側壁27の側面の端部を上から見た位置は、ソース・ドレイン領域28のゲート電極23側の端部を上から見た位置と略同一である。

【0015】

ソース・ドレイン側壁27の側面上及びシリコン基板10におけるゲート電極23の直下域間に位置する部分上には、ストッパー膜29が設けられている。すなわち、ストッパー膜29は、溝24の内面上に設けられているともいえる。ストッパー膜29のソース・ドレイン領域28上の部分は除去されている。

ゲート電極23の上部の両側面上には、絶縁側壁31が設けられている。絶縁側壁31の上端は、ハードマスク22の上面と一致している。絶縁側壁31の下端は、ゲート電極23におけるバリアメタル膜20の側面上に位置している。

したがって、ゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0016】

シリコン基板10上には、層間絶縁膜33が設けられている。なお、図1においては、図を見やすくするために、層間絶縁膜33を省略してある。層間絶縁膜33におけるソース・ドレイン領域28上にはコンタクトホール37が形成されている。コンタクトホール37の内部には、コンタクト38が設けられている。コンタクト38はソース・ドレイン領域28の表面におけるシリサイド層に接合されている。

【0017】

ゲート電極23におけるゲート絶縁膜に接する部分の側面とコンタクト23との間には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜の3つのシリコン窒化膜が形成されている。一方、ゲート電極23の上端部の側面は、上記3つのシリコン窒化膜に、絶縁側壁31を加えた4つのシリコン窒化膜が形成されている。さらに、ゲート電極23は上下でほぼ同じ幅をもつ柱状体に形成されている。したがって、コンタクト38において、絶縁側壁31によって挟まれていないシリコン基板10に近い部分は、絶縁側壁31で挟まれている部分より太く形成されている。

層間絶縁膜33におけるコンタクトホール37は、自己整合型のコンタクトホール37の開口によって、ゲート電極23上に形成されたハードマスクの領域まで広げて形成されている。よって、コンタクト38の層間絶縁膜33の部分は、絶縁側壁31によって挟まれた部分より広くなっている。

【0018】

次に、第1の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置1のゲート電極23に電圧を負荷する。そうすると、ゲート電極23とシリコン基板10との間に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。シリコン基板10のシリコン酸化膜18に覆われた部分がチャネルとして働き、反転層が形成される。そしてソース・ドレイン領域28の間に電圧を負荷すれば、反転層内をキャリアが移動し、電流が流れる。ゲート電極23の電圧を変化させることによって、ソース・ドレイン領域28の間を流れる電流量を制御する。

【0019】

次に、第1の実施形態に係る半導体装置の効果について説明する。

本実施形態においては、積層体81の上部の側面上には絶縁側壁31が設けられているため、ゲート電極23とコンタクト38との短絡が確実に防止される。一方、積層体81の下部、すなわちゲート電極23におけるゲート絶縁膜に接する部分の側面には絶縁側壁31が設けられていない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。したがって、微細化が進んで電極間の幅が狭くなっても、ソース・ドレイン領域28との間の導電性を確保しつつ、ゲート電極23との短絡を確実に防止して、自己整合型のコンタクト38を形成することができる。この結果、半導体装置1の高集積化を図ることができる。

【0020】

(第2の実施形態)

次に、第2の実施形態について説明する。

本実施形態は、リセス型トランジスタの半導体装置についてのものである。

図3は、第2の実施形態に係る半導体装置を例示する斜視図である。

図4は、第2の実施形態に係る半導体装置を例示する断面図であり、図3に示すA−A’面による断面図である。

先ず、第2の実施形態に係る半導体装置の構成について説明する。

図3及び図4に示すように、本実施形態に係る半導体装置2において、シリコン基板10には、STI領域17及び活性領域16が延びる方向に直交する方向に溝51が設けられている。

【0021】

溝51の内面上には、ゲート絶縁膜として、例えばシリコン酸化膜18が設けられている。また、溝51の内部には、導電材料、例えばポリシリコンが埋め込まれている。溝51の内部に埋め込まれたポリシリコンの部分を、下部導電部65という。ポリシリコンには、不純物、例えばリンが導入されている。

活性領域16の表層部分における溝51の外縁を含む領域には、不純物、例えばリンが導入された拡張領域26が形成されている。活性領域26の表層部分における溝を挟んで両側の拡張領域26の隣には、それぞれソース・ドレイン領域28が形成されている。

【0022】

また、溝51上には、溝51に沿って、溝51の幅と略等しい幅で、導電材料からなる柱状体が設けられている。この溝51上に設けられた柱状体は、溝51の内部に埋設された導電材料と同じ材料のポリシリコンからなり、溝51の内部に埋め込まれた下部導電部65と一体化している。溝51上に設けられたポリシリコンの柱状体を上部導電部66という。上部導電部66と下部導電部65を合わせて導電部67という。

【0023】

上部導電部66上には、バリアメタル膜20が設けられている。バリアメタル膜20としては、チタンと窒化チタンの積層膜及び窒化チタン膜が挙げられる。バリアメタル膜20上には、低抵抗金属膜21が設けられている。低抵抗金属膜21上には、ハードマスク22が設けられている。導電部67、バリアメタル膜20及び低抵抗金属膜21とから、ゲート電極23が形成される。

【0024】

ハードマスク22、低抵抗金属膜21及びバリアメタル膜20は積層して、柱状体62を構成している。柱状体62におけるバリアメタル膜20が、チタンと窒化チタンの積層膜である場合には、製造工程における酸化熱処理で、積層膜に含まれるチタンが酸化することがある。そこで、チタンの酸化を防ぐために、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20からなる積層体の側面上に、バリアメタル側壁61が設けられている。バリアメタル側壁61の材料としては、窒化シリコンがあげられる。バリアメタル側壁61が設けられている場合は、バリアメタル側壁61を含んだ積層構造を柱状体62という。

【0025】

上部導電部66及び柱状体62とで、柱状体63を構成する。また、柱状体63、下部導電部65及びシリコン酸化膜18を含む積層膜を積層体81という。

隣り合う柱状体63の間には、柱状体63がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。

積層体81における柱状体63の側面には、エクステンション側壁25とソース・ドレイン側壁27が設けられている。

【0026】

ソース・ドレイン側壁27の側面上及びシリコン基板10における柱状体63の直下域間に位置する部分上には、ストッパー膜29が設けられている。

積層体81における柱状体63の上部の両側面上には、絶縁側壁31が設けられている。本実施形態においてもゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われない。よって、コンタクト38における絶縁側壁31によって挟まれていない部分は、絶縁側壁31によって挟まれている部分よりも太くなっている。

本実施形態における上記以外の構成は、前述の第1の実施形態と同様であるので説明を省略する。

【0027】

次に、第2の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置2のゲート電極23に電圧を負荷する。そうすると、溝51の内面上に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。シリコン基板10の溝51に沿った領域がチャネルとして働き、反転層が形成される。

本実施形態における上記以外の動作は、前述の第1の実施形態と同様であるので、説明を省略する。

【0028】

次に、第2の実施形態に係る半導体装置の効果について説明する。

本実施形態においても、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

【0029】

また、リセス構造のトランジスタを製造することができ、ゲート電極23の幅を微細化しつつ、チャネル長を増加させることができる。また、ソース・ドレイン領域28の端が広がり、チャネルを流れる電流量を増加させることができる。

本実施形態における上記以外の効果は、前述の第1の実施形態と同様であるので説明を省略する。

【0030】

(第3の実施形態)

次に、第3の実施形態について説明する。

本実施形態は、フィン型トランジスタの半導体装置である。

図5は、第3の実施形態に係る半導体装置を例示する斜視図である。

図6は、第3の実施形態に係る半導体装置を例示する断面図であり、図5に示すA−A’面による断面図である。

先ず、本実施形態に係る半導体装置の構成について説明する。

図5及び図6に示すように、半導体装置3においては、半導体基板、例えばシリコン基板10が設けられている。

【0031】

シリコン基板10の上面には、1つの方向に延びるように形成された複数の柱状体75が平行に形成されている。柱状体75は、シリコン基板10と一体化しており、シリコン基板10から突出した形状となっている。柱状体75の下部の幅は、上部の幅より大きくなっている。柱状体75と柱状体75との間には、柱状体75の突出した高さより低くシリコン酸化膜73が形成されている。シリコン酸化膜73が形成されている領域をSTI領域74という。柱状体75のシリコン酸化膜73から上の部分をフィン72という。したがって、フィン72もシリコン基板10の上面に、1つの方向に延びるように形成されている。

【0032】

ゲート電極23は、フィン72上を含むシリコン基板10上に、フィン72が延びる方向に対して垂直な方向に延びるように設けられている。隣り合うゲート電極23の間には、ゲート電極23がシリコン基板10の上面上で延びる方向に沿って溝24が設けられている。溝24の幅方向の長さを「幅」という。ゲート絶縁膜として、例えばシリコン酸化膜18は、ゲート電極23におけるフィン72の上面上及び側面上に面する面に設けられている。

【0033】

ゲート電極23は、多層膜構造とされている。多層膜構造を構成する膜は、下からポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21とされている。低抵抗金属膜21上には、ハードマスク22が設けられている。ハードマスク22、ゲート電極23及びシリコン酸化膜18を含む積層膜を積層体81という。

フィン72の上面及び側面の上層部分におけるゲート電極23の直下域の両側には、拡張領域26が形成されている。フィン72の上面及び側面の上層部分におけるゲート電極23の直下域間の領域であって、拡張領域26間の領域には、ソース・ドレイン領域28が形成されている。

【0034】

積層体81の側面上には、フィン72を跨ぐようにエクステンション側壁25が設けられている。エクステンション側壁25の側面上には、フィン72を跨ぐようにソース・ドレイン側壁27が設けられている。

ソース・ドレイン側壁27の側面上及びフィン72におけるゲート電極23の直下域間に位置する部分上には、ストッパー膜29が設けられている。

【0035】

積層体81の上部の両側面上には、絶縁側壁31が設けられている。第3の実施形態においても、ゲート電極23の上端部の側面は、絶縁側壁31で覆われている。一方、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われない。よって、コンタクト38における絶縁側壁31によって挟まれていない部分は、絶縁側壁31によって挟まれている部分よりも太くなっている。

本実施形態における上記以外の構成は、前述の第1及び第2の実施形態と同様であるので説明を省略する。

【0036】

次に、第3の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置3のゲート電極23に電圧を負荷する。そうすると、フィン72の上面上及び側面上に設けられたシリコン酸化膜18が、ゲート絶縁膜として働く。フィン72のシリコン酸化膜18で覆われた領域がチャネルとして働き、反転層が形成される。

本実施形態における上記以外の動作は、前述の第1及び第2の実施形態と同様であるので説明を省略する。

【0037】

次に、第3の実施形態に係る半導体装置の効果について説明する。

本実施形態においても、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

また、フィン構造のトランジスタを製造することができ、ゲート電極23の幅を微細化しつつ、ゲート電極23に接するチャネル面積を増大させ、チャネルを流れる電流量を増加させることができる。

本実施形態における上記以外の効果は、前述の第1及び第2の実施形態と同様である。

【0038】

(第4の実施形態)

次に、第4の実施形態について説明する。

本実施形態は、第1の実施形態に係る半導体装置の製造方法である。

図7〜図11は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図12は、第4の実施形態に係る半導体装置の製造方法を例示する工程平面図であり、

図13は、図12に示すA−A’線による工程断面図であり、

図14は、図12に示すB−B’線による工程断面図であり、

図15は、図12に示すC−C’線による工程断面図であり、

図16〜図24は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図25は、第4の実施形態に係る半導体装置のゲート電極の上部を例示する断面図である。

【0039】

先ず、図7に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。その後、シリコン基板10上にハードマスク11となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク11を形成する。ハードマスク11は、シリコン基板10上の1つの方向に平行に形成する。

【0040】

そして、図8に示すように、ハードマスク11をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分にSTI領域17となる溝12を形成する。このとき、ハードマスク11に覆われて、エッチングされない領域が活性領域16となる。

その後、図9に示すように、溝12及びハードマスク11を含むシリコン基板10上をシリコン酸化膜13で覆う。そして、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスクの表面が現れるまでシリコン酸化膜13を研磨し、シリコン酸化膜13の上面を平坦化する。

【0041】

次に、図10に示すように、ウェットエッチングによって、ハードマスク11(図9参照)の下面まで、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面まで、シリコン酸化膜13を除去する。その後、ウェットエッチングにより、ハードマスク11を除去する。シリコン基板10の上面が現れている領域が活性領域16である。また、溝12の中にシリコン酸化膜13が埋め込まれた領域がSTI領域17である。STI領域17ではシリコン酸化膜13の上面が表面に現れている。

【0042】

そして、図11に示すように、活性領域16及びSTI領域17を含むシリコン基板10の上面に、シリコン酸化膜14を形成する。その後、シリコン酸化膜14上から、イオン注入法によって、不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝12の底部より深い領域までとする。これによって、活性領域16においては、シリコン基板10の上面から、溝12の底部より深い領域に相当する深さまで、シリコン基板10中にボロンが導入される。STI領域17においては、溝12の底面から、溝12の底部より深い領域まで、シリコン基板10中にボロンが導入される。シリコン基板10におけるボロンが導入された領域がp形のウェル15となる。

【0043】

図12〜図15に示すように、上述の工程により、シリコン基板10上に、1つの方向に平行に延びるSTI領域17を形成する。そして、STI領域17の間に配置されるように活性領域16が形成される。

シリコン基板10の表面には、シリコン酸化膜14が形成されているが、図12においては、図示を省略してある。

【0044】

次に、図16に示すように、半導体基板10上のシリコン酸化膜14(図13〜図15参照)を除去し、シリコン基板10の上面上にゲート絶縁膜として、例えばシリコン酸化膜18を形成する。

その後、図17に示すように、シリコン酸化膜18上から、ゲート電極23の一部となるポリシリコン膜19を形成する。次に、ポリシリコン膜19上からバリアメタル膜20として、例えば窒化タングステン膜(WN)を形成する。そして、その上から低抵抗金属膜21として、例えばタングステン膜(W)を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21を含んでいる。

【0045】

低抵抗金属膜21上に、ハードマスク22を形成する。ハードマスク22は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク22は、STI領域17が延びる方向に直交する方向に延びる複数本の帯状の部分とする。

次に、図18に示すように、ハードマスク22をマスクとして、反応性イオンエッチングを行い、低抵抗金属膜21、バリアメタル膜20、ポリシリコン膜19及びゲート絶縁膜18を選択的に除去する。これによって、ゲート絶縁膜18、ポリシリコン膜19、バリアメタル膜20,低抵抗金属膜21及びハードマスク22が積層された積層体81が形成される。積層体81のうち、低抵抗金属膜21、バリアメタル膜20及びポリシリコン膜19により、ゲート電極23が形成される。一方、ハードマスク22で覆われていない部分の表面には、シリコン基板10が現れている。

【0046】

積層体81は、STI領域17が延びる方向に直交する方向に延びた柱状体として形成される。隣り合うゲート電極23の間には溝24が形成される。すなわち、形成された溝24は、ゲート電極23を分断している。溝24は、ゲート電極23が延びる方向と同じ方向に延びている。

【0047】

次に、図19に示すように、積層体81の側面上にエクステンション側壁25を形成する。エクステンション側壁25は、シリコン基板10上にシリコン窒化膜を形成した後、積層体81の側面上以外の部分を除去して形成する。そして、積層体81及びエクステンション側壁25をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体81及びエクステンション側壁25に覆われていない領域に拡張領域26を形成する。

【0048】

さらに、積層体81の側面上にソース・ドレイン側壁27を形成する。そして、積層体81、エクステンション側壁25、ソース・ドレイン側壁27をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における積層体81、エクステンション側壁25及びソース・ドレイン側壁27に覆われていない領域にソース・ドレイン領域28を形成する。

ソース・ドレイン領域28には、拡張領域26に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域28には、拡張領域26より深くリンを注入する。

【0049】

その後、ニッケルを堆積した後、加熱することにより、ソース・ドレイン領域28の表面をシリサイド化する。次に、未反応のニッケルを除去する。

次に、ソース・ドレイン側壁27の側面上及びシリコン基板10における積層体81の直下域間に位置する部分上に、ストッパー膜29を形成する。ストッパー膜29は、シリコン基板10上にシリコン窒化膜を形成した後、ソース・ドレイン側壁27の側面上及びシリコン基板10における積層体81の直下域間に位置する部分上以外の部分を除去して形成する。これにより、積層体81の側面上には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29の3つのシリコン窒化膜が形成されている。

【0050】

次に、図20に示すように、溝24の内部の底部に、犠牲材30を埋め込む。犠牲材30の材料としては、炭素を含む材料があげられる。炭素を含む材料を溝24に埋め込む方法としては、CVD法等を用いて埋め込む方法があげられる。先ず、シリコン基板10上に、炭素、水素及び窒素を含む材料を堆積して膜を形成する。炭素の含有率が100%に近い膜も形成することができる。炭素、水素及び窒素を含む材料は、ゲート電極23間、すなわち溝24の下部であって、少なくともハードマスク22間の空間を含む部分に埋め込まれる。次に、溝24の内部の底部以外の部分を除去して犠牲材30を形成する。犠牲材30の上面は、ゲート電極23の低抵抗金属膜21が形成されている位置より下方とする。犠牲材30を埋め込む方法としては、CVD法の他、スパッタ法やスピン塗布法があげられる。スパッタ法は、炭素を含む材料をターゲットに用いて、スパッタリングにより炭素を含む材料を溝24に埋め込む。スピン塗布法は、炭素を含む材料をシリコン基板10上に塗布して、炭素を含む材料を溝24に埋め込む。埋め込んだ後は、CVD法と同様に、溝24の内部の底部以外の部分を除去して犠牲材30を形成する。

【0051】

次に、図21に示すように、積層体81の側面上に、絶縁側壁31を形成する。絶縁側壁31は、CVD法等によりシリコン基板10上にシリコン窒化膜を形成した後、積層体81の側面上以外の部分をRIE法により除去して形成する。絶縁側壁31の上端は積層体81の上面と一致する。絶縁側壁31の下端は、犠牲材30の上面と一致する。犠牲材30の上面をゲート電極23の低抵抗金属膜21が形成されている位置より下方としたので、絶縁側壁31の下端も、ゲート電極23の低抵抗金属膜21が形成されている位置より下方となる。したがって、ゲート電極23の上端部の側面は絶縁側壁31で覆われ、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0052】

その後、図22に示すように、アッシング法により、犠牲材30を除去する。これにより、積層体81のハードマスク22及び低抵抗金属膜21の側面上には、エクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の4つのシリコン窒化膜が形成されている。

一方、犠牲材30で覆われていた積層体81の側面上には、エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29の3つのシリコン窒化膜が形成されている。これらのシリコン窒化膜は、半導体装置1の製造過程において、一体化することはなく、半導体装置1が製造された後においても、区別することができる。

【0053】

次に、図23に示すように、溝24の内部に、例えばポリシラザン等のシリコン酸化膜32を埋め込み、CMP法によってハードマスク22の表面並びにエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の一端が現れるまでシリコン酸化膜32を研磨し、シリコン酸化膜32の上面を平坦化する。そして、層間絶縁膜33としてシリコン酸化膜を堆積し、その上に多層レジスト膜として、有機膜34、シリコン酸化膜35及びレジスト36を形成する。

【0054】

次に、図24に示すように、コンタクトホール37のパターニングを行う。自己整合型のコンタクトホール37におけるレジスト36の開口領域は、ソース・ドレイン領域28の上面におけるコンタクト38との接合部分に対応する領域だけではなく、ゲート電極23のハードマスク22に対応する領域まで広げられる。このとき、レジスト36及びハードマスク22がエッチングのストッパーとなる。そして、レジスト36をマスクとして、RIE法を行い、シリコン酸化膜35、有機膜34、層間絶縁膜33及びシリコン酸化膜32を選択的に除去する。このようにして、ゲート電極23間にソース・ドレイン領域28に到達するコンタクトホール37が形成される。

【0055】

自己整合型のコンタクトホール37におけるレジスト36のパターニングの形状は、ホール形状の他、溝24に沿ったライン形状の場合もある。このような場合でもゲート電極23のハードマスク25がエッチングのストッパーとなり、ゲート電極23間にコンタクトホール37が形成される。

その後、コンタクトホール37に、導電部材、例えばチタン等のバリアメタル及びタングステン等のメタル材料を埋め込み、コンタクト38を形成する。

このようにして、図1及び図2に示すように、半導体装置1が製造される。

【0056】

次に、本実施形態の効果について説明する。

図25に示すように、本実施形態においては、ハードマスク22及び低抵抗金属膜21の側面上にはエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31の4つのシリコン窒化膜を含むシリコン窒化膜40が形成されている。なお、図25では、4つのシリコン窒化膜を区別していないが、これらのシリコン窒化膜は、半導体装置1の製造過程において、一体化することはなく、半導体装置1が製造された後においても、区別することができる。

【0057】

したがって、自己整合のコンタクトホール37の形成工程において、ハードマスク22及びシリコン窒化膜40の上面は広く露出している。コンタクトホール37を形成するエッチング時に、溝24の内部のシリコン酸化膜32では、シリコン酸化膜32から酸素が供給されることで、エッチングガスに含まれるカーボンが除去され、シリコン酸化膜32上にはエッチング生成物41が堆積しない。一方、ハードマスク22及びシリコン窒化膜40は、膜中に酸素を含まないため、カーボンが除去されず、エッチング生成物41が堆積される。

【0058】

絶縁側壁31が形成されて、レジスト36のパターニングで開口されたハードマスク22及びシリコン窒化膜40の上面の面積は広くなっているため、ハードマスク22及びシリコン窒化膜40の上面には、エッチングガスが供給されやすく、エッチング生成物41は、ハードマスク22及びシリコン窒化膜40上に厚く堆積し、エッチングのストッパーの役目をする。したがって、シリコン酸化膜32はエッチングが進むが、ハードマスク22及びシリコン窒化膜40はエッチングが進まず、ゲート電極23の低抵抗金属膜21とコンタクト38とは電気的な接触を起こすことがない。

【0059】

一方、溝24の底部に相当するゲート電極23の側面上には絶縁側壁31を形成していない。よって、ソース・ドレイン領域28の上面とコンタクト38との間の接合する面積を狭くすることがない。その結果、界面抵抗は増加しない。

また、犠牲材30の材料として、炭素を含む材料とすると、窒化シリコンを材料とするハードマスク22、バリアメタル側壁61、エクステンション側壁25及びソース・ドレイン側壁27並びに酸化シリコンを材料とするSTI領域17及びゲート絶縁膜はエッチングされずに、犠牲材30をエッチングすることができる。

したがって、本実施形態によれば、微細化が進んで電極の幅が狭くなっても自己整合型のコンタクトホールを形成することができるので、集積度が高い半導体装置を製造することができる。

【0060】

(第4の実施形態の比較例)

次に、第4の実施形態の比較例について説明する。

本比較例においては、絶縁側壁31を形成しない場合における半導体装置の製造方法である。

図26及び27は、第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

図28(a)及び(b)は、第4の実施形態の比較例に係る半導体装置のゲート電極の上部を例示する断面図である。

第4の実施形態における図7〜図19に示す工程は、比較例においても同様なので説明を省略する。

【0061】

図26に示すように、本比較例においては、絶縁側壁31を形成しないで、シリコン酸化膜32、層間絶縁膜33、有機膜34、シリコン酸化膜35及びレジスト36を形成する。

その後、図27に示すように、コンタクトホール37を形成し、コンタクトホール37に、コンタクト38を形成する。

本比較例においては、図27に示すように、ゲート電極23の低抵抗金属膜21とコンタクト38とが電気的な接触を起こしている。

【0062】

図28(a)及び(b)に示すように、本比較例においては、絶縁側壁31を形成していない。シリコン窒化膜40には、絶縁側壁31が含まれない。したがって、自己整合のコンタクトホール37の形成工程において、ハードマスク22及びシリコン窒化膜40の上面に露出している面積は、第4の実施形態の場合と比べて狭くなっている。よって、ハードマスク22及びシリコン窒化膜40の上面には、エッチングガスが供給されづらく、エッチングのストッパーとなるエッチングの生成物41が堆積しづらい。また、図28(b)に示すように、角部のエッチングはイオンの入射が完全に垂直ではないことから、傾斜形状となり平坦部に比べてエッチングが進みやすい。そのため、比較例におけるハードマスク22及びシリコン窒化膜40がエッチングされる。

それにより、ゲート電極23の低抵抗金属膜21とコンタクト38とが電気的な接触を起こしてしまう。

【0063】

(第5の実施形態)

次に、第5の実施形態について説明する。

本実施形態は、第2の実施形態に係る半導体装置の製造方法の実施形態である。

以下、図面を参照しつつ、本実施形態について説明する。

図29〜図38は、第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図7〜図15に示す工程を実施する。これらの工程については、説明を省略する。

【0064】

次に、図29に示すように、図12のB−B’線における断面に相当する断面においては、シリコン基板10上にハードマスク50となる膜として、例えばシリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク50を形成する。ハードマスク50は、STI領域17を形成するための溝12と直交する方向に延びている。

次に、図30に示すように、ハードマスク50をマスクとして、反応性イオンエッチングを行うことにより、シリコン酸化膜14及びシリコン基板10を選択的に除去する。これにより、溝51が形成される。

【0065】

また、図31に示すように、図12のC−C’線における断面に相当する断面においては、STI領域17においても、シリコン基板10上にハードマスク50となる膜として、シリコン窒化膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク50を形成する。

次に、図32に示すように、ハードマスク50をマスクとして、反応性イオンエッチングにより、シリコン酸化膜13及びシリコン酸化膜14を選択的に除去する。これにより、溝51が形成される。

このように、図12に示すB−B’線による活性領域における溝51の内部と、図12に示すC−C’線によるSTI領域における溝51の内部は同じ構成となっている。そこで、以後は活性領域16における工程断面図のみ示す。

【0066】

次に、図33に示すように、シリコン基板10上のハードマスク50及びシリコン酸化膜14を除去し(図29〜図32参照)、溝51の内面上及びシリコン基板10の上面上にゲート絶縁膜となるシリコン酸化膜18を形成する。次に、シリコン酸化膜18上からゲート電極23の一部となるポリシリコン膜19を形成する。このポリシリコン膜19にはリンが不純物として導入されている。ポリシリコン膜19は、溝51内を埋め込むように形成する。

【0067】

その後、ポリシリコン膜19上からバリアメタル膜20として、例えばチタンと窒化チタンの積層膜を積層する。そして、その上から低抵抗金属膜21として、例えばタングステン(W)膜を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル層20及び低抵抗金属層21を含んでいる。バリアメタル膜20の材料としては、チタンと窒化チタンの積層膜の他、窒化チタンがあげられる。

【0068】

そして、低抵抗金属層21上から、シリコン窒化膜56及び有機膜57を形成した後、その上に、シリコン酸化膜58を形成する。さらにシリコン酸化膜58上に、レジスト59を形成する。このとき、レジスト59の形成領域は、溝51の直上域と一致させる。

次に、レジスト59をマスクとして、シリコン酸化膜58をパターニングする。

その後、パターニングされたシリコン酸化膜58をマスクとして有機膜57及びシリコン窒化膜56を加工する。

【0069】

次に、図34に示すように、本実施形態では、シリコン酸化膜58及び有機膜57を除去し、パターニングされたシリコン窒化膜56をハードマスク22とする。

次に、図35に示すように、ハードマスク22をマスクとして反応性イオンエッチングを行い、低抵抗金属膜21及びバリアメタル膜20を選択的に除去する。これによって、ハードマスク22で覆われている部分には、低抵抗金属膜21及びバリアメタル膜20からなるゲート電極23の一部が形成される。

一方、ハードマスク22で覆われていない部分の表面には、ポリシリコン膜19が現れている。

【0070】

バリアメタル膜20として窒化チタンとチタンの積層膜を用いた場合は、ゲート電極加工後の後酸化のときにチタンが酸化されて劣化する可能性がある。

そこで、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜の側面上に、バリアメタル側壁61を形成する。バリアメタル側壁61の材料としては、例えば、シリコン窒化膜があげられる。バリアメタル側壁61は、CVD法(chemical vapor deposition:化学気相成長法)等により、シリコン窒化膜を形成した後、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜の側面上以外の部分を除去して形成する。

【0071】

バリアメタル側壁61を形成した場合は、バリアメタル側壁61、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜を柱状体62という。バリアメタル側壁61を形成しない場合は、ハードマスク22、低抵抗金属膜21及びバリアメタル膜20を含む多層膜を柱状体62という。

次に、ポリシリコン膜19の加工を行う。本実施形態においては、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21の三層構造とされている。したがって、ポリシリコン膜19は、ゲート電極23の最下層膜となっている。

【0072】

次に、図36に示すように、ポリシリコン膜19におけるゲート電極23の間に形成された部分を除去する。ゲート電極23の間のポリシリコン膜19の部分が除去されて、シリコン酸化膜18が表面に現れる。

その後、図37に示すように、ゲート電極23間のシリコン基板10上のシリコン酸化膜18、すなわち、ゲート絶縁膜となる溝51の内面上のシリコン酸化膜18以外のシリコン酸化膜18を除去する。溝51内には、シリコン酸化膜18が残存している。

柱状体62及び上部導電部66を含む積層膜を柱状体63という。また、柱状体63、下部導電部65及びシリコン酸化膜18を含む積層膜を積層体81という。

【0073】

そして、積層体81における柱状体63の側面上にエクステンション側壁25を形成する。次に、柱状体63及びエクステンション側壁25をマスクとして、シリコン基板10にリンをイオン注入して、拡張領域26を形成する。

さらに、積層体81における柱状体63の側面上にソース・ドレイン側壁27を形成する。そして、柱状体63、エクステンション側壁25及びソース・ドレイン側壁27をマスクとして、シリコン基板10にリンをイオン注入して、ソース・ドレイン領域28を形成する。

【0074】

次に、第4の実施形態における図19〜図22に示す工程を行って、ストッパー膜29、絶縁側壁31を形成する。本実施形態においても、ゲート電極23の上端部の側面は、絶縁側壁31で覆われ、ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

さらに、第4の実施形態における図23〜図24に示す工程を行って、シリコン基板10上から層間絶縁膜33、多層レジスト膜を形成する。

そして、図38に示すように、自己整合型のコンタクトホール37を形成し、コンタクト38を設ける。

このようにして、図3及び図4に示すように、半導体装置2が製造される。

【0075】

次に、第5の実施形態に係る半導体装置の製造方法の効果について説明する。

リセス構造のトランジスタを実現でき、高集積化を図ることができる半導体装置を提供することができる。

本実施形態における上記以外の効果は、前述の第4の実施形態と同様であるので説明を省略する。

【0076】

(第6の実施形態)

次に、第6の実施形態に係る半導体装置の製造方法について説明する。

図39〜図44は、第6の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、各図の(a)は(b)に示すB−B’線による工程断面図であり、各図の(b)は、(a)に示すA−A’線による工程断面図である。

先ず、図39に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。その後、シリコン基板10上にハードマスク71となる膜として、例えばシリコン窒化膜を形成した後、フォトグラフィー法等でパターニングしてハードマスク71を形成する。ハードマスク71は、シリコン基板10上の1つの方向に平行に形成する。 そして、図40に示すように、ハードマスク71をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分を選択的に除去する。

【0077】

ハードマスク71で覆われた部分が柱状体75となる。柱状体75は、ハードマスク71と同様に、シリコン基板10上の1つの方向に平行に形成される。柱状体75は、シリコン基板10と一体化しており、シリコン基板10から突出した形状となる。柱状体75の延びる方向と垂直な方向を「幅」といい、柱状体75の幅方向に面する2つの面を「側面」という。柱状体75の下部の幅は、上部の幅より大きく形成する。

【0078】

次に、図41に示すように、ハードマスク71で覆われた柱状体75を含むシリコン基板10上をシリコン酸化膜73で覆う。そして、CMP法によって、ハードマスク71の表面が現れるまでシリコン酸化膜73を研磨し、シリコン酸化膜73の上面を平坦化する。

次に、図42に示すように、ハードマスク71(図41参照)をマスクとしてシリコン酸化膜73をドライエッチングにより下方に後退させる。そして、ハードマスク71を除去する。残留したシリコン酸化膜73がある領域をSTI領域74とする。柱状体75のシリコン酸化膜73から上の部分をフィン72という。したがって、フィン72もシリコン基板10の上面に、1つの方向に延びるように形成されている。また、フィン72の延びる方向と垂直な方向を「幅」といい、幅方向に面する2つの面を「側面」という。

【0079】

次に、図43に示すように、フィン72の上面上及び側面上にゲート絶縁膜として、例えばシリコン酸化膜18を形成する。

その後、シリコン酸化膜18上から、ゲート電極23の一部となるポリシリコン膜19を形成する。ポリシリコン膜19は、フィン72を覆うように、フィン72の高さ以上に形成する。

【0080】

そして、ポリシリコン膜19上からバリアメタル膜20として、例えば窒化タングステン膜を形成する。そして、その上から低抵抗金属膜21として、例えばタングステン膜を形成する。本実施形態において、ゲート電極23は、ポリシリコン膜19、バリアメタル膜20及び低抵抗金属膜21を含んでいる。

低抵抗金属膜21上に、ハードマスク22を形成する。ハードマスク22は、低抵抗金属膜21上に、例えばシリコン窒化膜を形成し、その後、リソグラフィー法によりパターニングして形成する。ハードマスク22は、フィン72の方向に直行するように形成する。

【0081】

次に、ハードマスク22をマスクとして、反応性イオンエッチングを行い、低抵抗金属膜21、バリアメタル膜20、ポリシリコン膜19及びシリコン酸化膜18を選択的に除去する。これによって、ハードマスク22で覆われている部分には、低抵抗金属膜21、バリアメタル膜20及びポリシリコン膜19を含むゲート電極23が形成される。

一方、ハードマスク22で覆われていない部分の表面には、フィン72の上面及び側面が現れている。

【0082】

また、ハードマスク22、ゲート電極23及びシリコン酸化膜18を含む積層体81は、フィン72及びSTI領域74が延びる方向に直交する方向に延びた柱状体として形成する。隣り合う積層体81の間には溝24が形成される。すなわち、形成された溝24は、積層体81を分断している。溝24は、積層体81が延びる方向と同じ方向に延びている。

【0083】

次に、図44に示すように、第4の実施形態における図19〜図22の工程を行って、積層体81の側面上にエクステンション側壁25、ソース・ドレイン側壁27、ストッパー膜29及び絶縁側壁31を形成する。エクステンション側壁25、ソース・ドレイン側壁27及びストッパー膜29は、フィン72を跨ぐように、フィン72の上面上及び側面上に形成される。

また、本実施形態においても、ゲート電極の上端部の側面は、絶縁側壁31で覆われ、

ゲート電極23におけるゲート絶縁膜に接する部分の側面は、絶縁側壁31で覆われていない。

【0084】

そして、第4の実施形態における図23〜図24に示すような工程を行って、層間絶縁膜33、多層レジスト膜を形成する。そして、自己整合型のコンタクトホール37を形成し、コンタクト38を形成する。

このようにして、図5及び図6に示すように、半導体装置3が製造される。

【0085】

以上説明した実施形態によれば、高集積化を図ることができる半導体装置及びその製造方法を提供することができる。

【0086】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0087】

1、2、3:半導体装置、10:シリコン基板、11、22、50、71:ハードマスク、12、24、51、82:溝、13、14、18、32、35、58、73:シリコン酸化膜、15:ウェル、16:活性領域、17、74:STI領域、19:ポリシリコン膜、20:バリアメタル膜、21:低抵抗金属膜、23:ゲート電極、25:エクステンション側壁、26:拡張領域、27:ソース・ドレイン側壁、28:ソース・ドレイン領域、29:ストッパー膜、30:犠牲材、31:絶縁側壁、33:層間絶縁膜、34、57:有機膜、36、59:レジスト、37:コンタクトホール、38:コンタクト、40、56:シリコン窒化膜、41:生成物、61:バリアメタル側壁、62、63、75:柱状体、65:下部導電部、66上部導電部、67:導電部、72:フィン、81:積層体

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、

前記半導体基板上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極上に設けられた絶縁膜と、

を有する積層体と、

前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、

前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、

前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、

を備えたことを特徴とする半導体装置。

【請求項2】

前記コンタクトにおける前記絶縁側壁によって挟まれていない部分は、前記絶縁側壁によって挟まれている部分よりも太いことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板の上面には、前記積層体が延びる方向に延びる複数本の溝が形成されており、

前記ゲート絶縁膜は前記溝の内面上に設けられており、

前記ゲート電極の一部は、前記溝の内部に埋め込まれていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記半導体基板の上面には、前記積層体が延びる方向に交差する方向に延びる複数本のフィンが形成されており、

前記ゲート絶縁膜は前記フィンの上面上及び側面上に設けられていることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

半導体基板上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

前記導電膜上に、絶縁性であり、相互に平行に延びる複数本のハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記導電膜及び前記絶縁膜をエッチングすることにより、前記絶縁膜、前記導電膜及び前記ハードマスクが積層され、相互に平行に延びる複数本の積層体を形成する工程と、

前記積層体間の空間の下部であって、少なくとも前記絶縁膜間の空間を含むが前記ハードマスク間の空間を含まない部分に犠牲材を埋め込む工程と、

前記積層体の側面上であって、前記犠牲材上に前記絶縁側壁を形成する工程と、

前記犠牲材を除去する工程と、

前記半導体基板上に前記積層体を覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記半導体基板に到達する貫通孔を形成する工程と、

前記貫通孔内に導電材料を埋め込んでコンタクトを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項6】

前記犠牲材を埋め込む工程は、

炭素、窒素及び水素を含むガスを用いた化学気相成長法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項7】

前記犠牲材を埋め込む工程は、

スパッタ法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項8】

前記犠牲材を埋め込む工程は、

スピン塗布法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項9】

前記半導体基板に前記積層体が延びる方向に延びる複数本の溝を形成する工程をさらに備え、

前記絶縁膜を形成する工程においては、前記溝の内面上にも前記絶縁膜を形成し、

前記導電膜を形成する工程においては、前記溝を埋めるように前記導電膜を形成し、

前記ハードマスクを形成する工程においては、前記溝の直上域の一部を含むようにハードマスクを形成することを特徴とする請求項5〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項10】

前記半導体基板に前記積層体が延びる方向に交差する方向に延びる複数のフィンを形成する工程をさらに備え、

前記絶縁膜を形成する工程においては、前記フィンの側面上及び上面上にも前記絶縁膜を形成することを特徴とする請求項5〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項11】

前記積層体の側面上に、エクステンション側壁を形成する工程と、

前記積層体及び前記エクステンション側壁をマスクとして不純物を注入し、拡張領域を形成する工程と、

前記エクステンション側壁の側面上にソース・ドレイン側壁を形成する工程と、

前記積層体、前記エクステンション側壁及び前記ソース・ドレイン側壁をマスクとして不純物を注入し、拡張領域より不純物濃度が高いソース・ドレイン領域を形成する工程と、

前記絶縁側壁を形成する工程の前に、前記ソース・ドレイン側壁の側面上及び前記第1の不純物領域上にストッパー膜を形成する工程と、

をさらに備え、

前記エクステンション側壁、前記ソース・ドレイン側壁、前記ストッパー膜、前記絶縁側壁及び前記ハードマスクを、同じ材料を含むように形成することを特徴とする請求項5〜10のいずれか1つに記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、

前記半導体基板上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

前記ゲート電極上に設けられた絶縁膜と、

を有する積層体と、

前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、

前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、

前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、

を備えたことを特徴とする半導体装置。

【請求項2】

前記コンタクトにおける前記絶縁側壁によって挟まれていない部分は、前記絶縁側壁によって挟まれている部分よりも太いことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板の上面には、前記積層体が延びる方向に延びる複数本の溝が形成されており、

前記ゲート絶縁膜は前記溝の内面上に設けられており、

前記ゲート電極の一部は、前記溝の内部に埋め込まれていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記半導体基板の上面には、前記積層体が延びる方向に交差する方向に延びる複数本のフィンが形成されており、

前記ゲート絶縁膜は前記フィンの上面上及び側面上に設けられていることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

半導体基板上に絶縁膜を形成する工程と、

前記絶縁膜上に導電膜を形成する工程と、

前記導電膜上に、絶縁性であり、相互に平行に延びる複数本のハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記導電膜及び前記絶縁膜をエッチングすることにより、前記絶縁膜、前記導電膜及び前記ハードマスクが積層され、相互に平行に延びる複数本の積層体を形成する工程と、

前記積層体間の空間の下部であって、少なくとも前記絶縁膜間の空間を含むが前記ハードマスク間の空間を含まない部分に犠牲材を埋め込む工程と、

前記積層体の側面上であって、前記犠牲材上に前記絶縁側壁を形成する工程と、

前記犠牲材を除去する工程と、

前記半導体基板上に前記積層体を覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記半導体基板に到達する貫通孔を形成する工程と、

前記貫通孔内に導電材料を埋め込んでコンタクトを形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項6】

前記犠牲材を埋め込む工程は、

炭素、窒素及び水素を含むガスを用いた化学気相成長法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項7】

前記犠牲材を埋め込む工程は、

スパッタ法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項8】

前記犠牲材を埋め込む工程は、

スピン塗布法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記膜における前記導電膜の上端間及びそれよりも上方に位置する部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項9】

前記半導体基板に前記積層体が延びる方向に延びる複数本の溝を形成する工程をさらに備え、

前記絶縁膜を形成する工程においては、前記溝の内面上にも前記絶縁膜を形成し、

前記導電膜を形成する工程においては、前記溝を埋めるように前記導電膜を形成し、

前記ハードマスクを形成する工程においては、前記溝の直上域の一部を含むようにハードマスクを形成することを特徴とする請求項5〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項10】

前記半導体基板に前記積層体が延びる方向に交差する方向に延びる複数のフィンを形成する工程をさらに備え、

前記絶縁膜を形成する工程においては、前記フィンの側面上及び上面上にも前記絶縁膜を形成することを特徴とする請求項5〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項11】

前記積層体の側面上に、エクステンション側壁を形成する工程と、

前記積層体及び前記エクステンション側壁をマスクとして不純物を注入し、拡張領域を形成する工程と、

前記エクステンション側壁の側面上にソース・ドレイン側壁を形成する工程と、

前記積層体、前記エクステンション側壁及び前記ソース・ドレイン側壁をマスクとして不純物を注入し、拡張領域より不純物濃度が高いソース・ドレイン領域を形成する工程と、

前記絶縁側壁を形成する工程の前に、前記ソース・ドレイン側壁の側面上及び前記第1の不純物領域上にストッパー膜を形成する工程と、

をさらに備え、

前記エクステンション側壁、前記ソース・ドレイン側壁、前記ストッパー膜、前記絶縁側壁及び前記ハードマスクを、同じ材料を含むように形成することを特徴とする請求項5〜10のいずれか1つに記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【公開番号】特開2012−204689(P2012−204689A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−68929(P2011−68929)

【出願日】平成23年3月25日(2011.3.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月25日(2011.3.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]