半導体装置及びその製造方法

【課題】素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、CMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供する。

【解決手段】n−型ドリフト層114と、n−型ドリフト層114における活性領域R1に形成したp型半導体材料からなる複数の柱状埋込層118と、周辺耐圧領域R2に形成したリング状の第2トレンチ122、第2トレンチ122の内面に形成した絶縁膜124及び第2トレンチ122の内部に絶縁膜124を介して形成した導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分のn−型ドリフト層114を空乏化させる周辺耐圧構造120と、周辺領域R3に形成したp型半導体材料からなる1又は2以上の第2柱状埋込層130とを備える半導体装置100。

【解決手段】n−型ドリフト層114と、n−型ドリフト層114における活性領域R1に形成したp型半導体材料からなる複数の柱状埋込層118と、周辺耐圧領域R2に形成したリング状の第2トレンチ122、第2トレンチ122の内面に形成した絶縁膜124及び第2トレンチ122の内部に絶縁膜124を介して形成した導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分のn−型ドリフト層114を空乏化させる周辺耐圧構造120と、周辺領域R3に形成したp型半導体材料からなる1又は2以上の第2柱状埋込層130とを備える半導体装置100。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来、スーパージャンクション構造を有する半導体装置が知られている(例えば、特許文献1参照。)。

図13は、従来の半導体装置800の要部を示す断面図である。図13中、符号832は周辺絶縁膜を示し、符号850はカソード電極層を示す。

【0003】

従来の半導体装置800は、ショットキーバリアダイオードであって、図13に示すように、n+型の半導体基板812上と、n+型の半導体基板812上に位置するn−型ドリフト層814と、前記n−型ドリフト層814の内部に形成した複数の第1トレンチ816及び複数の第2トレンチ828と、第1トレンチ816及び第2トレンチ828の内部にエピタキシャル成長させて形成したp型半導体材料からなる複数の柱状埋込層818及び複数の第2柱状埋込層830と、n−型ドリフト層814、複数の柱状埋込層818及び複数の第2柱状埋込層830の上部に形成したショットキーバリアメタル層846とを備える。柱状埋込層818は、柱状埋込層818で挟まれた領域のn−型ドリフト層814とp型の柱状埋込層818との間でn型とp型との不純物総量がおおよそ等しくなる状態であるチャージバランスを取れるような濃度のp型不純物を含有し、活性領域R1に配設されている。第2柱状埋込層830は、ガードリングとしての機能を有し、活性領域R1を取り囲む周辺領域R3に数十本にわたって配設されている(例えば、特許文献1参照。)。

【0004】

従来の半導体装置800によれば、スーパージャンクション構造を有するため、高い逆耐圧特性を有するショットキーバリアダイオードとなる。

【0005】

また、従来の半導体装置800によれば、周辺領域R3には第2導電型半導体材料からなる数十本の第2柱状埋込層(ガードリング)830が設けられているため、逆バイアス時には、最外周の第2柱状埋込層より内側の第2柱状埋込層830及びn−型ドリフト層814が空乏化され、素子周辺部での耐圧を高くすることができる。

【0006】

しかしながら、従来の半導体装置800においては、素子周辺部での耐圧を高くするために、周辺領域R3に数十本の第2柱状埋込層830を設けているため、周辺領域の面積が大きくなり、ひいては半導体装置が大きくなってしまうという問題がある。

【0007】

そこで、本発明の発明者らは、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な半導体装置を想到し、特願2010−201299号(以下、先願という。)として既に出願している。

【0008】

図14は、先願に係る半導体装置900の要部を示す断面図である。図14中、符号912は半導体基板を示し、符号914はn−型ドリフト層を示し、符号916は埋込層トレンチを示し、符号946はショットキーバリアメタル層を示し、符号950はカソード電極層を示す。

【0009】

先願に係る半導体装置900は、従来の半導体装置800の場合と同様に、スーパージャンクション構造を有するショットキーバリアダイオードであって、図14に示すように、活性領域R1には、柱状埋込層で囲まれたn−型ドリフト層914との間でチャージバランスを取れるような濃度のp型半導体材料からなる複数の柱状埋込層918が配設されており、活性領域R1と周辺領域R3との間の周辺耐圧領域R2には、リング状の第2トレンチ922、第2トレンチ922の内面に形成された絶縁膜924及び第2トレンチ922の内部に絶縁膜924を介して形成された導電性材料層926を有する周辺耐圧構造920が配設されている。

【0010】

このため、先願に係る半導体装置900によれば、周辺耐圧領域R2には上記した周辺耐圧構造920が配設されているため、n−型ドリフト層914と柱状埋込層918との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造920の絶縁膜924が必要な耐圧の大部分を担うようになるため、従来の半導体装置800の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0011】

また、先願に係る半導体装置900によれば、周辺領域R3に数十本の第2柱状埋込層を設ける必要がなくなるため、従来の半導体装置800の場合よりも周辺領域R3の面積を小さくすることが可能となる。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2004−6595号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、本発明の発明者らの研究によれば、先願に係る半導体装置900においては、製造工程中に第1絶縁膜932が削られ過ぎることに起因して素子周辺部での耐圧が低下してしまう場合があるという問題があることがわかった。図15は、先願に係る半導体装置800を製造する製造工程の要部を説明するために示す図である。図15(a)はCMP(Chemical Mechanical Polishing)工程直前の断面図であり、図15(b)はCMP工程直後の断面図である。なお、図15中、符号917は柱状埋込層の本体部を示す。すなわち、先願に係る半導体装置900を製造する際には、図15(a)及び図15(b)に示すように、エピタキシャル成長法によって柱状埋込層918を形成する際に形成されてしまうキャップ部919をCMP法により除去する工程が必要となるが、先願に係る半導体装置900においては、活性領域R1と周辺領域R3とで表面構造が大きく異なるため、CMP工程を実施中に周辺耐圧領域R3の近傍で第1絶縁膜932が削られ過ぎてしまうことに起因して素子周辺部での耐圧が低下してしまう場合があるのである。なお、このような問題はスーパージャンクション構造を有する半導体装置だけに存在する問題ではなく、活性領域に柱状埋込層を有する半導体装置全般に存在する問題である。

【0014】

そこで、本発明は、このような問題を解決するためになされたものであり、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供することを目的とする。また、そのような半導体装置を製造可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

[1]本発明の半導体装置は、第1導電型の半導体層と、前記半導体層における活性領域に形成した第1トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる複数の柱状埋込層と、前記活性領域を囲む周辺耐圧領域に形成したリング状の第2トレンチ、当該第2トレンチの内面に形成した絶縁膜及び前記第2トレンチの内部に前記絶縁膜を介して形成した導電性材料層を有し、逆バイアス時には前記導電性材料層及び前記柱状埋込層に挟まれた部分の前記半導体層を空乏化させる周辺耐圧構造と、前記周辺耐圧領域を囲む周辺領域に形成した第3トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる1又は2以上の第2柱状埋込層とを備えることを特徴とする。

【0016】

[2]本発明の半導体装置においては、前記半導体層、前記複数の柱状埋込層及び前記1又は2以上の第2柱状埋込層は、単結晶シリコンからなることが好ましい。

【0017】

[3]本発明の半導体装置においては、前記複数の柱状埋込層は、各々が第1間隔で平行に形成され、前記複数の柱状埋込層のうち前記周辺耐圧構造に最も近い柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことが好ましい。

【0018】

[4]本発明の半導体装置においては、前記1又は2以上の第2柱状埋込層のうち前記周辺耐圧構造に最も近い第2柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことが好ましい。

【0019】

[5]本発明の半導体装置においては、前記第2柱状埋込層として、各々が前記第1間隔以下の間隔で平行に形成された2以上の第2柱状埋込層を備えることが好ましい。

【0020】

[6]本発明の半導体装置においては、前記柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことが好ましい。

【0021】

[7]本発明の半導体装置においては、前記第2柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことが好ましい。

【0022】

[8]本発明の半導体装置は、ショットキーバリアダイオードであってもよい。

【0023】

[9]本発明の半導体装置は、プレーナーゲート型MOSFETであってもよい。

【0024】

[10]本発明の半導体装置は、トレンチゲート型MOSFETであってもよい。

【0025】

[11]本発明の半導体装置は、プレーナーゲート型IGBTであってもよい。

【0026】

[12]本発明の半導体装置は、トレンチゲート型IGBTであってもよい。

【0027】

[13]本発明の半導体装置は、スーパージャンクション構造を有する半導体装置であってもよい。

【0028】

[14]本発明の半導体装置の製造方法は、本発明の半導体装置を製造するための半導体装置の製造方法であって、前記第1導電型の半導体層を準備する半導体層準備工程と、前記周辺耐圧領域に前記周辺耐圧構造を形成する周辺耐圧構造形成工程と、前記半導体層の表面に形成した所定パターンの第1絶縁膜をマスクとして前記活性領域及び前記周辺領域にそれぞれ前記第1トレンチ及び前記第3トレンチを形成し、前記第1トレンチ及び前記第3トレンチの内部に前記第1絶縁膜の表面の高さ位置を超える高さ位置まで第2導電型の半導体材料をエピタキシャル成長させることにより、前記活性領域に柱状埋込層を形成するとともに前記周辺領域に第2柱状埋込層を形成する埋込層形成工程と、前記柱状埋込層及び第2柱状埋込層を前記第1絶縁膜の表面の高さ位置までCMP法によって研磨して除去するCMP工程とを含むことを特徴とする。

【発明の効果】

【0029】

本発明の半導体装置によれば、周辺耐圧領域に上記した周辺耐圧構造を備えるため、第1導電型の半導体層と第2導電型の柱状埋込層との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造の絶縁膜が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0030】

また、本発明の半導体装置によれば、周辺領域にいわゆるダミーの柱状埋込層(第2柱状埋込層)を配設していることから、活性領域と周辺領域とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域の近傍で第1絶縁膜が削られ過ぎてしまうことがなくなり、その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0031】

さらにまた、本発明の半導体装置によれば、周辺領域ではなく周辺耐圧領域において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の高耐圧半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0032】

このため、本発明の半導体装置は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0033】

本発明の半導体装置の製造方法によれば、本発明の半導体装置を製造することができる。

【図面の簡単な説明】

【0034】

【図1】実施形態1に係る半導体装置100を説明するために示す図である。

【図2】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図3】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図4】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図5】実施形態2に係る半導体装置200を説明するために示す図である。

【図6】実施形態2に係る半導体装置200の製造方法を説明するために示す図である。

【図7】実施形態3に係る半導体装置300を説明するために示す図である。

【図8】実施形態3に係る半導体装置300の製造方法を説明するために示す図である。

【図9】実施形態4に係る半導体装置400を説明するために示す図である。

【図10】実施形態4に係る半導体装置400の製造方法を説明するために示す図である。

【図11】実施形態5に係る半導体装置500を説明するために示す図である。

【図12】実施形態5に係る半導体装置500の製造方法を説明するために示す図である。

【図13】従来の半導体装置800を説明するために示す図である。

【図14】先願に係る半導体装置900を説明するために示す図である。

【図15】先願に係る半導体装置900を製造する製造工程の要部を説明するために示す図である。

【発明を実施するための形態】

【0035】

以下、本発明の半導体装置及び半導体装置の製造方法について、図に示す実施の形態に基づいて説明する。

【0036】

[実施形態1]

1.実施形態1に係る半導体装置100の構成

まず、実施形態1に係る半導体装置100の構成を説明する。

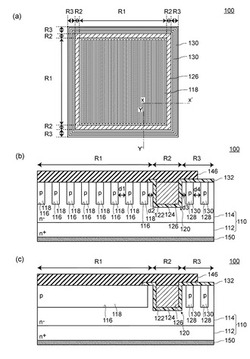

図1は、実施形態1に係る半導体装置100を説明するために示す図である。図1(a)は実施形態1に係る半導体装置100の平面図であり、図1(b)は図1(a)のX−X’断面図であり、図1(c)は図1(a)のY−Y’断面図である。なお、図1(a)においては、理解を容易にするために、柱状埋込層118、導電性材料層126及び第2柱状埋込層130のみを示している。

【0037】

実施形態1に係る半導体装置100は、スーパージャンクション構造を有するショットキーバリアダイオードであり、図1(a)に示すように、活性領域R1と、活性領域R1を囲む周辺耐圧領域R2と、周辺耐圧領域R2を囲む周辺領域R3とに分画されている。

【0038】

実施形態1に係る半導体装置100は、図1(b)に示すように、n−型ドリフト層114と、柱状埋込層118と、周辺耐圧構造120と、第2柱状埋込層130と、周辺絶縁膜132と、ショットキーバリアメタル層146と、カソード電極層150とを備える。

【0039】

n−型ドリフト層114は、n+型半導体基板112の上部にエピタキシャル成長させることにより形成されたものであって、n+型半導体基板112とn−型ドリフト層114とで半導体基体110を構成する。n−型ドリフト層114の厚さは、例えば10μmであり、n−型ドリフト層の不純物濃度は、例えば1.5×1016cm−3である。

【0040】

柱状埋込層118は、n−型ドリフト層114における活性領域R1に形成した第1トレンチ116の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。柱状埋込層118の本数は使用目的や構造に合わせて適宜変更することができる。p型半導体材料の不純物濃度は、例えば4.5×1016cm−3である。

【0041】

柱状埋込層118の底部の深さ位置は全て同じであり、後述する導電性材料層126の底部の深さ位置と等しい。柱状埋込層118の深さは、例えば5.5μmであり、幅は、例えば0.5μmである。柱状埋込層118は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1.5μmである。

【0042】

周辺耐圧構造120は、第2トレンチ122、絶縁膜124及び導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分を空乏化させる。柱状埋込層118のうち周辺耐圧構造120に最も近い柱状埋込層118と周辺耐圧構造120との間隔は、第1間隔d1より狭い第2間隔d2である。第2間隔d2は、例えば1.0μmである。

【0043】

第2トレンチ122は、周辺耐圧領域R2に形成されたリング状の溝で、例えば幅が2.5μmであり、深さが6.5μmである。実施形態1においては第2トレンチの形状を正方形としたが、長方形などの他の四角形、他の多角形、角を丸くした多角形及び円形としてもよい。

【0044】

絶縁膜124は、第2トレンチ122の内面に形成された熱酸化膜であり、厚さは例えば1.0μmである。

導電性材料層126は、第2トレンチ122の内部に絶縁膜124を介して形成され、例えば高濃度の不純物を含有するポリシリコンからなる。

【0045】

第2柱状埋込層130は、周辺領域R3に形成され、p型半導体材料からなる2本の柱状埋込層である。第2柱状埋込層130の本数は使用目的や構造に合わせて適宜変更することができる。p型半導体材料の不純物濃度は、例えば4.5×1016cm−3である。

【0046】

第2柱状埋込層130は、各々が第1間隔d1以下の第4間隔d4で平行に形成される。第2間隔d4は、例えば、1.0μmとすることができる。実施形態1においては、第2柱状埋込層130は、各々が第4間隔d4で等しい間隔で形成するが、第1間隔d1以下であればそれぞれ異なる間隔としてもよく、例えば、周辺耐圧構造120から離れるにつれて短くなっていくように形成してもよい。

【0047】

また、第2柱状埋込層130のうち周辺耐圧構造120に最も近い第2柱状埋込層と周辺耐圧構造120との間隔は、第1間隔d1より狭い第3間隔d3である。また、第2柱状埋込層130の底部の深さ位置は全て同じ深さで、導電性材料層126の底部の深さ位置と等しくなるように形成されている。第3間隔d3は、例えば1.0μmである。また、第2柱状埋込層130の底部の深さは、例えば5.5μmである。

【0048】

周辺絶縁膜132は、酸化膜からなる。ショットキーバリアメタル層146は、n−型ドリフト層114とはショットキー接合を形成し、柱状埋込層118及び導電性材料層126とはオーミック接合を形成する。ショットキーバリアメタル層146の材料は例えば白金であり、ショットキーバリアメタル層146の厚さは例えば200nmである。カソード電極層150は、電極材料である金属(例えば、ニッケル)を半導体基体110の裏面に蒸着して形成する。カソード電極層150の厚さは、例えば200nmである。

【0049】

実施形態1に係る半導体装置100は、図1(a)におけるY−Y’に沿った方向においても、図1(c)に示すように、周辺耐圧構造120の内側に柱状埋込層118が形成され、かつ、周辺耐圧構造120の外側に第2柱状埋込層130が形成されている。

【0050】

2.実施形態1に係る半導体装置100の製造方法

次に、実施形態1に係る半導体装置100の製造方法を以下に示す各工程に沿って説明する。

図2〜図4は、実施形態1に係る半導体装置の製造方法を説明するために示す図である。図2(a)〜図2(d)、図3(a)〜図3(d)及び図4(a)〜図4(d)は各工程図である。

【0051】

1.半導体層準備工程

まず、n+型半導体基板112と、n+型半導体基板112の表面側にエピタキシャル成長方により形成したn−型ドリフト層114とを有する半導体基体110を準備する(図2(a)参照。)。n+型半導体基板112としては、例えばシリコン基板を用いることができるが、炭化珪素SiCや窒化ガリウムGaNからなる基板を用いてもよい。

【0052】

2.周辺耐圧構造形成工程

次に、周辺耐圧構造120を形成する。周辺耐圧構造形成工程は、第2トレンチ形成工程と、絶縁膜形成工程と、導電性材料層形成工程とからなる。

【0053】

2−1.第2トレンチ形成工程

周辺耐圧構造形成工程においては、まず、n−型ドリフト層114の表面側からリング状の第2トレンチ122を形成する。具体的には、n−型ドリフト層114の表面に熱酸化法又はCVD法により第1絶縁膜である第1絶縁膜132’を形成した後、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、第2トレンチ形成部に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。次に、レジスト酸化膜を取り除き、その後、第1絶縁膜132’をマスクとしてn−型ドリフト層114をドライエッチングすることにより、n−型ドリフト層114の表面にリング状の第2トレンチ122を形成する(図2(b)参照。)。

【0054】

2−2.絶縁膜形成工程

周辺耐圧構造形成工程においては、ケミカルドライエッチングや犠牲酸化等で第2トレンチ122の底部及び側面のダメージ層を取り除きつつラウンド化を行った後、半導体基体110を熱酸化することにより第2トレンチ122の内部に絶縁膜124を形成する(図2(c)参照。)。なお、ここでは絶縁膜124を熱酸化により形成したが、CVD法にて形成してもよい。

【0055】

2−3.導電性材料層形成工程

周辺耐圧構造形成工程においては、次に、第2トレンチ122の内部に絶縁膜124を介して導電性材料層126を形成する。具体的には、n−型ドリフト層114の表面側から導電性材料126’を堆積させる(図2(d)参照。)。その後、n−型ドリフト層114の表面の高さ位置より上部に位置する導電性材料を除去することにより導電性材料層126を形成する(図3(a)参照)。)。

以上の周辺耐圧構造形成工程により周辺耐圧構造120が形成される。

【0056】

3.埋込層形成工程

次に、活性領域R1に柱状埋込層118を形成するとともに周辺領域R3に第2柱状埋込層130を形成する。埋込層形成工程は、第1トレンチ及び第3トレンチ形成工程と、柱状埋込層及び第2柱状埋込層形成工程とからなる。

【0057】

3−1.第1トレンチ及び第3トレンチ形成工程

第1トレンチ及び第3トレンチ形成工程においては、まず、導電性材料を熱酸化することにより導電性材料層126の上部にトレンチマスクとなる酸化膜を形成する(図3(b)参照。)。当該酸化膜は第1絶縁膜132’の一部を構成する。続いて、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、柱状埋込層及び第2柱状埋込層の形成位置に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。次に、レジスト膜を取り除き、その後、第1絶縁膜132’をマスクとしてn−型ドリフト層114をドライエッチングすることにより、n−型ドリフト層114の表面に第1トレンチ116及び第2トレンチ128を形成する(図3(c)参照。)。

【0058】

3−2.柱状埋込層及び第2柱状埋込層形成工程

埋込層形成工程においては、第1トレンチ116及び第2トレンチ128の内面について、ケミカルドライエッチングや犠牲酸化、水素アニール等により、第1トレンチ形成工程のドライエッチングによるダメージ層除去を行った後、p型不純物を含むドーパントガスを導入しながら第1絶縁膜132’表面の高さ位置を超える高さ位置までp型の単結晶シリコンをエピタキシャル成長させる。

このことにより活性領域R1に、第1絶縁膜132’表面の高さ位置までの本体部117と第1絶縁膜132’表面の高さ位置を超えた部分であるキャップ部119とからなる柱状埋込層118’を形成するとともに、周辺領域R3に第1絶縁膜132’表面の高さ位置までの本体部129と第1絶縁膜132’表面の高さ位置を超えた部分であるキャップ部131とからなる第2柱状埋込層130’を形成する(図3(d)参照。)。

【0059】

4.CMP工程

次に、埋込層形成工程で形成されたキャップ部119,131を第1絶縁膜132’の表面の高さ位置までCMP法によって研磨して除去する(図4(a)参照。)。

【0060】

5.周辺絶縁膜工程

次に、本体部117,129をドライエッチングによりn−型ドリフト層114の表面の高さ位置まで除去する。このことにより、柱状埋込層118及び第2柱状埋込層130が形成される(図4(b)参照。)。

その後、第1絶縁膜132’間に露出している柱状埋込層118及び第2柱状埋込層130の表面を熱酸化することで第2柱状埋込層130表面に後に周辺絶縁膜132となるための酸化膜を形成する。当該酸化膜は第1絶縁膜132’の一部を構成する。

その後、レジスト膜Mを形成し、写真工程を実施することにより、活性領域R1全体及び周辺耐圧領域R2の所定の部分に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。このとき、周辺領域R3に残った第1絶縁膜132’が周辺絶縁膜132となる(図4(c)参照。)。その後、レジスト膜Mを取り除く。

【0061】

6.電極形成工程

次に、周辺絶縁膜工程で設けた開口部に、n−型ドリフト層114とはショットキー接合を形成し、柱状埋込層118及び導電性材料層126とはオーミック接合を形成するショットキーバリアメタル層146を形成するとともに、半導体基体110の裏面側に位置するn+型半導体基板112の裏面側にカソード電極層150を形成する(図4(d)参照。)。

【0062】

上記の工程を順次実施することにより、実施形態1に係る半導体装置100を製造することができる。

【0063】

3.実施形態1に係る半導体装置100の効果

実施形態1に係る半導体装置100によれば、周辺耐圧領域R2に上記した周辺耐圧構造120を備えるため、n−型ドリフト層114とp型の柱状埋込層118との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造120の絶縁膜124が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0064】

また、実施形態1に係る半導体装置100によれば、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域120の近傍で第1絶縁膜132が削られ過ぎてしまうことがなくなり(図3(d)及び図4(a)並びに図15(a)及び図15(b)参照。)、その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0065】

さらにまた、本発明の半導体装置100によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0066】

このため、本発明の半導体装置100は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0067】

また、実施形態1に係る半導体装置100によれば、複数の柱状埋込層118は、第1間隔d1で平行に形成されているため、特定の部分に電界が集中することを防ぐことが可能となり、空乏層を広い範囲に広げることができる。このため、活性領域R1において耐圧を高くすることが可能となる。

【0068】

また、実施形態1に係る半導体装置100によれば、複数の柱状埋込層118のうち周辺耐圧構造120に最も近い柱状埋込層118と周辺耐圧構造120との間隔は、第1間隔d1より狭い第2間隔d2であるため、逆バイアス時に活性領域R1と周辺耐圧構造R2とで挟まれた領域を確実に空乏化することが可能となる。

【0069】

また、実施形態1に係る半導体装置100によれば、周辺耐圧構造120に最も近い第2柱状埋込層130と周辺耐圧構造120との間隔は、第1間隔d1より狭い第3間隔d3であるため、逆バイアス時に周辺耐圧領域R2と周辺領域R3とで挟まれた領域まで確実に空乏化することが可能となる。

【0070】

また、実施形態1に係る半導体装置100によれば、第2柱状埋込層130として、各々が第1間隔d1以下の間隔d4で平行に形成された2以上の第2柱状埋込層130を備えるため、逆バイアス時に空乏層を複数の第2柱状埋込層130のうち最外周の第2柱状埋込層130まで広げることが可能となり、素子周辺での耐圧をより一層高くすることが可能となる。

【0071】

また、実施形態1に係る半導体装置100によれば、柱状埋込層118の底部の深さ位置が、導電性材料層126の底部の深さ位置と等しいため、複数の柱状埋込層118から下方に伸びた空乏層の底部を滑らかにすることが可能となり、逆バイアス時に柱状埋込層の底部や周辺耐圧構造の底部に電界が集中することがなくなる。このため、活性領域R1から周辺耐圧領域R2にかけての耐圧を高くすることが可能となる。

【0072】

また、実施形態1に係る半導体装置100によれば、第2柱状埋込層130の底部の深さ位置が、導電性材料層126の底部の深さ位置と等しいため、周辺耐圧構造120及び第2柱状埋込層130から下方に伸びた空乏層の底部を滑らかにすることが可能となり、逆バイアス時に第2柱状埋込層の底部や周辺耐圧構造の底部に電界が集中することがなくなる。このため、周辺耐圧領域R2から周辺領域R3にかけての耐圧を高くすることが可能となる。

【0073】

また、実施形態1に係る半導体装置100は、スーパージャンクション構造を有する高耐圧の半導体装置であるため、半導体基体110における特定の部分に電界が集中することを抑制することが可能となり、空乏層をn−型ドリフト層及び柱状埋込層に広げることができる。そのため、活性領域における耐圧を高くすることが可能となる。

【0074】

また、実施形態1に係る半導体装置100によれば、図1(a)におけるY−Y’に沿った方向においても、図1(a)におけるX−X’に沿った方向の場合と同様に、周辺耐圧構造120の外側に第2柱状埋込層130が形成されているため、柱状埋込層を形成する過程で形成されてしまうキャップ部をCMP法により除去するCMP工程において、周辺領域にもキャップ部が形成されるため、図15(b)に示すように、周辺領域R3において第1絶縁膜132’が削れ過ぎてしまうことがなくなるこのため、CMP工程に起因して素子周辺での耐圧が低下してしまうことがなくなる(図3(d)及び図4(a)参照。)。

【0075】

[実施形態2]

図5は、実施形態2に係る半導体装置200を説明するために示す図である。図5(a)は実施形態2に係る半導体装置200の平面図であり、図5(b)は図5(a)におけるX−X’断面図を示す図であり、図5(c)は図5(a)におけるY−Y’断面図を示す図である。なお、図5(a)においては、図1(a)の場合と同様に、理解を容易にするために、柱状埋込層218、導電性材料層226及び第2柱状埋込層230のみを示す。図5(a)中、符号GPはゲートパッドを示す。

【0076】

図6は、実施形態2に係る半導体装置の製造方法を説明するために示す図である。図6(a)〜図6(d)は工程図である。なお、図6(a)〜図6(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に示す工程については図示を省略する。また、図6(c)〜図6(d)に示す工程は、一般的なプレーナーゲート型MOSFETの製造方法の場合と同様であるため、図6(c)〜図6(d)の間にある工程は図示を省略する。

【0077】

実施形態2に係る半導体装置200は、基本的には実施形態1に係る半導体装置100と同様の構成を有するが、図5(b)に示すように、半導体装置がプレーナーゲート型MOSFETである点が実施形態1に係る半導体装置100の場合と異なる。すなわち、実施形態2に係る半導体装置200は、図5(b)に示すように、ボディ領域234と、ソース領域236と、ゲート絶縁膜240及びゲート電極層242からなるゲート電極構造238と、ソース電極層246と、ドレイン電極層250とを備えるプレーナーゲート型MOSFETである。

【0078】

このように、実施形態2に係る半導体装置200は、半導体装置がプレーナーゲート型MOSFETである点が実施形態1に係る半導体装置100の場合とは異なるが、実施形態1に係る半導体装置100と同様の以下の特徴を有するため、実施形態1に係る半導体装置100が有する効果と同様の効果を有する。

【0079】

すなわち、実施形態2に係る半導体装置200によれば、図5(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造220を備えるため、n−型ドリフト層214とp型の柱状埋込層218との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造220の絶縁膜224が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0080】

また、実施形態2に係る半導体装置200によれば、図5(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層230)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域220の近傍で第1絶縁膜232が削られ過ぎてしまうことがなくなり(図6(b)及び図6(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0081】

さらにまた、実施形態2に係る半導体装置200によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0082】

このため、実施形態2に係る半導体装置200は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0083】

なお、実施形態2に係る半導体装置200は、半導体装置がプレーナーゲート型MOSFETである点以外の点では実施形態1に係る半導体装置100の場合と同様の構成を有するため、実施形態1に係る半導体装置100が有する効果のうち同様の効果を有する。

【0084】

[実施形態3]

図7は、実施形態3に係る半導体装置300を説明するために示す図である。図7(a)は実施形態3に係る半導体装置300の平面図であり、図7(b)は図7(a)におけるX−X’断面図を示す図であり、図7(c)は図7(a)におけるY−Y’断面図を示す図である。なお、図7(a)においては、図5(a)の場合と同様に、理解を容易にするために、柱状埋込層318、導電性材料層326及び第2柱状埋込層330のみを示す。図7(a)中、符号GPはゲートパッドを示す。

【0085】

図8は、実施形態3に係る半導体装置の製造方法を説明するために示す図である。図8(a)〜図8(d)は工程図である。なお、図8(a)〜図8(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図8(c)〜図8(d)に示す工程は、一般的なトレンチゲート型MOSFETの製造方法の場合と同様であるため、図8(c)〜図8(d)の間にある工程は図示を省略する。

【0086】

実施形態3に係る半導体装置300は、基本的には実施形態2に係る半導体装置200と同様の構成を有するが、図7(b)に示すように、半導体装置がトレンチゲート型MOSFETである点で実施形態2に係る半導体装置200の場合と異なる。すなわち、実施形態3に係る半導体装置300は、図7(b)に示すように、ボディ領域334と、ソース領域336と、ゲート絶縁膜340及びゲート電極層342からなるゲート電極構造338と、ソース電極層346と、ドレイン電極層350とを備えるトレンチゲート型MOSFETである。

【0087】

このように、実施形態3に係る半導体装置300は、半導体装置がトレンチゲート型MOSFETである点が実施形態2に係る半導体装置200の場合とは異なるが、実施形態2に係る半導体装置200と同様の以下の特徴を有するため、実施形態2に係る半導体装置200が有する効果と同様の効果を有する。

【0088】

すなわち、実施形態3に係る半導体装置300によれば、図7(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造320を備えるため、n−型ドリフト層314とp型の柱状埋込層318との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造320の絶縁膜324が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0089】

また、実施形態3に係る半導体装置300によれば、図7(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層330)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域320の近傍で第1絶縁膜332が削られ過ぎてしまうことがなくなり(図8(b)及び図8(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0090】

さらにまた、実施形態3に係る半導体装置300によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0091】

このため、実施形態3に係る半導体装置300は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0092】

なお、実施形態3に係る半導体装置300は、半導体装置がトレンチゲート型MOSFETである点以外の点では実施形態2に係る半導体装置200の場合と同様の構成を有するため、実施形態2に係る半導体装置200が有する効果のうち同様の効果を有する。

【0093】

[実施形態4]

図9は、実施形態4に係る半導体装置400を説明するために示す図である。図9(a)は実施形態4に係る半導体装置400の平面図であり、図9(b)は図9(a)におけるX−X’断面図を示す図であり、図9(c)は図9(a)におけるY−Y’断面図を示す図である。なお、図9(a)においては、図5(a)の場合と同様に、理解を容易にするために、柱状埋込層418、導電性材料層426及び第2柱状埋込層430のみを示す。図9(a)中、符号GPはゲートパッドを示す。

【0094】

図10は、実施形態4に係る半導体装置の製造方法を説明するために示す図である。図10(a)〜図10(d)は工程図である。なお、図10(a)〜図10(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図10(c)〜図10(d)に示す工程は、一般的なプレーナーゲート型IGBTの製造方法の場合と同様であるため、図10(c)〜図10(d)の間にある工程は図示を省略する。

【0095】

実施形態4に係る半導体装置400は、基本的には実施形態2に係る半導体装置200と同様の構成を有するが、図9(b)に示すように、半導体装置がプレーナーゲート型IGBTである点で実施形態2に係る半導体装置200の場合と異なる。すなわち、実施形態4に係る半導体装置400は、図9(b)に示すように、ボディ領域434と、エミッタ領域436と、ゲート絶縁膜440及びゲート電極層442からなるゲート電極構造438と、エミッタ電極層446と、コレクタ電極層450とを備え、実施形態2のn+型半導体基板212の代わりにp+型半導体層412を備えるプレーナーゲート型IGBTである。

【0096】

このように、実施形態4に係る半導体装置400は、半導体装置がプレーナーゲート型IGBTである点が実施形態2に係る半導体装置200の場合とは異なるが、実施形態2に係る半導体装置200と同様の以下の特徴を有するため、実施形態2に係る半導体装置200が有する効果と同様の効果を有する。

【0097】

すなわち、実施形態4に係る半導体装置400によれば、図9(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造420を備えるため、n−型ドリフト層414とp型の柱状埋込層418との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造420の絶縁膜424が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0098】

また、実施形態4に係る半導体装置400によれば、図9(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層430)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域420の近傍で第1絶縁膜432が削られ過ぎてしまうことがなくなり(図10(b)及び図10(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0099】

さらにまた、実施形態4に係る半導体装置400によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0100】

このため、実施形態4に係る半導体装置400は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0101】

なお、実施形態4に係る半導体装置400は、半導体装置がプレーナーゲート型IGBTである点以外の点では実施形態2に係る半導体装置200の場合と同様の構成を有するため、実施形態2に係る半導体装置200が有する効果のうち同様の効果を有する。

【0102】

[実施形態5]

図11は、実施形態5に係る半導体装置500を説明するために示す図である。図11(a)は実施形態5に係る半導体装置500の平面図であり、図11(b)は図11(a)におけるX−X’断面図を示す図であり、図11(c)は図11(a)におけるY−Y’断面図を示す図である。なお、図11(a)においては、図9(a)の場合と同様に、理解を容易にするために、柱状埋込層518、導電性材料層526及び第2柱状埋込層530のみを示す。図11(a)中、符号GPはゲートパッドを示す。

【0103】

図12は、実施形態5に係る半導体装置の製造方法を説明するために示す図である。図12(a)〜図12(d)は工程図である。なお、図12(a)〜図12(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図12(c)〜図12(d)に示す工程は、一般的なトレンチゲート型IGBTの製造方法の場合と同様であるため、図12(c)〜図12(d)の間にある工程は図示を省略する。

【0104】

実施形態5に係る半導体装置500は、基本的には実施形態4に係る半導体装置400と同様の構成を有するが、図11(b)に示すように、半導体装置がトレンチゲート型IGBTである点で実施形態4に係る半導体装置400の場合と異なる。すなわち、実施形態5に係る半導体装置500は、図11(b)に示すように、ボディ領域534と、エミッタ領域536と、ゲート絶縁膜540及びゲート電極層542からなるゲート電極構造538と、エミッタ電極層546と、コレクタ電極層550とを備えるトレンチゲート型IGBTである。

【0105】

このように、実施形態5に係る半導体装置500は、半導体装置がトレンチゲート型IGBTである点が実施形態4に係る半導体装置400の場合とは異なるが、実施形態4に係る半導体装置400と同様の以下の特徴を有するため、実施形態4に係る半導体装置400が有する効果と同様の効果を有する。

【0106】

すなわち、実施形態5に係る半導体装置500によれば、図11(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造520を備えるため、n−型ドリフト層514とp型の柱状埋込層518との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造520の絶縁膜524が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0107】

また、実施形態5に係る半導体装置500によれば、図11(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層530)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域520の近傍で第1絶縁膜532が削られ過ぎてしまうことがなくなり(図12(b)及び図12(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0108】

さらにまた、実施形態5に係る半導体装置500によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0109】

このため、実施形態5に係る半導体装置500は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0110】

なお、実施形態5に係る半導体装置500は、半導体装置がトレンチゲート型IGBTである点以外の点では実施形態4に係る半導体装置400の場合と同様の構成を有するため、実施形態4に係る半導体装置400が有する効果のうち同様の効果を有する。

【0111】

以上、本発明を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。その趣旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば、次のような変形も可能である。

【0112】

(1)上記各実施形態においては、ショットキーバリアダイオード、MOSFET及びIGBTを例にとって本発明の高耐圧半導体装置を説明したが、本発明はこれに限定されるものではない。周辺耐圧領域に周辺耐圧構造を形成することが可能な半導体装置であれば本発明を適用することが可能である。

【0113】

(2)上記各実施形態においては、第1導電型をn型とし、第2導電型をp型とした場合を例にとって本発明を説明したが、本発明はこれに限定されるものではない。例えば、第1導電型をp型とし、第2導電型をn型とした場合にも本発明を適用可能である。

【0114】

(3)上記各実施形態においては、柱状埋込層の上部にp+型半導体領域をさらに形成した高耐圧半導体装置に本発明の発明を適用してもよい。このような構成とすることにより、柱状埋込層とアノード電極層、ソース電極層又はエミッタ電極層と良好なオーミック接続を取ることが可能となる。

【符号の説明】

【0115】

100,200,300,400,500,800,900…半導体層装置、110,210,310,410,510,810,910…半導体基体、112,212,312…n+型半導体基板、114,214,314,414,514…n−型ドリフト層、116,216,316,416,516…第1トレンチ、117,129,217,229,317,329,417,429,517,529…本体部、118,118’,218,218’,318,318’,418,418’,518,518’,818,918,918’…柱状埋込層、119,131,219,231,319,331,419,431,519,531…キャップ部、120,220,320,420,520,920…周辺耐圧構造、122,222,322,422,522,922…第2トレンチ、124,224,324,424,524,924…絶縁膜、126,226,326,426,526,926…導電性材料層、128,228,328,428,528…第3トレンチ、130,130’,230,230’,330,330’,430,430’,530,530’…第2柱状埋込層、132,232,332,432,532,832,932…周辺絶縁膜、132’,232’,332’,432’,532’,932’…第1酸化膜、146,846,946…ショットキーバリアメタル層、150,850,950…カソード電極層、234,334、434,534…ボディ領域、236,336…ソース領域、238,338,438,538…ゲート電極構造、240,340,440,540…ゲート絶縁膜、242,342,442,542…ゲート電極層、244,344,444,544…層間絶縁膜、246,346…ソース電極層、250,350…ドレイン電極層、316a,516a…第4トレンチ、412,512…p+型半導体層、436,536…エミッタ領域、446,546…エミッタ電極層、450,550…コレクタ電極層、R1…活性領域、R2…周辺耐圧領域、R3…周辺領域

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来、スーパージャンクション構造を有する半導体装置が知られている(例えば、特許文献1参照。)。

図13は、従来の半導体装置800の要部を示す断面図である。図13中、符号832は周辺絶縁膜を示し、符号850はカソード電極層を示す。

【0003】

従来の半導体装置800は、ショットキーバリアダイオードであって、図13に示すように、n+型の半導体基板812上と、n+型の半導体基板812上に位置するn−型ドリフト層814と、前記n−型ドリフト層814の内部に形成した複数の第1トレンチ816及び複数の第2トレンチ828と、第1トレンチ816及び第2トレンチ828の内部にエピタキシャル成長させて形成したp型半導体材料からなる複数の柱状埋込層818及び複数の第2柱状埋込層830と、n−型ドリフト層814、複数の柱状埋込層818及び複数の第2柱状埋込層830の上部に形成したショットキーバリアメタル層846とを備える。柱状埋込層818は、柱状埋込層818で挟まれた領域のn−型ドリフト層814とp型の柱状埋込層818との間でn型とp型との不純物総量がおおよそ等しくなる状態であるチャージバランスを取れるような濃度のp型不純物を含有し、活性領域R1に配設されている。第2柱状埋込層830は、ガードリングとしての機能を有し、活性領域R1を取り囲む周辺領域R3に数十本にわたって配設されている(例えば、特許文献1参照。)。

【0004】

従来の半導体装置800によれば、スーパージャンクション構造を有するため、高い逆耐圧特性を有するショットキーバリアダイオードとなる。

【0005】

また、従来の半導体装置800によれば、周辺領域R3には第2導電型半導体材料からなる数十本の第2柱状埋込層(ガードリング)830が設けられているため、逆バイアス時には、最外周の第2柱状埋込層より内側の第2柱状埋込層830及びn−型ドリフト層814が空乏化され、素子周辺部での耐圧を高くすることができる。

【0006】

しかしながら、従来の半導体装置800においては、素子周辺部での耐圧を高くするために、周辺領域R3に数十本の第2柱状埋込層830を設けているため、周辺領域の面積が大きくなり、ひいては半導体装置が大きくなってしまうという問題がある。

【0007】

そこで、本発明の発明者らは、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な半導体装置を想到し、特願2010−201299号(以下、先願という。)として既に出願している。

【0008】

図14は、先願に係る半導体装置900の要部を示す断面図である。図14中、符号912は半導体基板を示し、符号914はn−型ドリフト層を示し、符号916は埋込層トレンチを示し、符号946はショットキーバリアメタル層を示し、符号950はカソード電極層を示す。

【0009】

先願に係る半導体装置900は、従来の半導体装置800の場合と同様に、スーパージャンクション構造を有するショットキーバリアダイオードであって、図14に示すように、活性領域R1には、柱状埋込層で囲まれたn−型ドリフト層914との間でチャージバランスを取れるような濃度のp型半導体材料からなる複数の柱状埋込層918が配設されており、活性領域R1と周辺領域R3との間の周辺耐圧領域R2には、リング状の第2トレンチ922、第2トレンチ922の内面に形成された絶縁膜924及び第2トレンチ922の内部に絶縁膜924を介して形成された導電性材料層926を有する周辺耐圧構造920が配設されている。

【0010】

このため、先願に係る半導体装置900によれば、周辺耐圧領域R2には上記した周辺耐圧構造920が配設されているため、n−型ドリフト層914と柱状埋込層918との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造920の絶縁膜924が必要な耐圧の大部分を担うようになるため、従来の半導体装置800の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0011】

また、先願に係る半導体装置900によれば、周辺領域R3に数十本の第2柱状埋込層を設ける必要がなくなるため、従来の半導体装置800の場合よりも周辺領域R3の面積を小さくすることが可能となる。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2004−6595号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、本発明の発明者らの研究によれば、先願に係る半導体装置900においては、製造工程中に第1絶縁膜932が削られ過ぎることに起因して素子周辺部での耐圧が低下してしまう場合があるという問題があることがわかった。図15は、先願に係る半導体装置800を製造する製造工程の要部を説明するために示す図である。図15(a)はCMP(Chemical Mechanical Polishing)工程直前の断面図であり、図15(b)はCMP工程直後の断面図である。なお、図15中、符号917は柱状埋込層の本体部を示す。すなわち、先願に係る半導体装置900を製造する際には、図15(a)及び図15(b)に示すように、エピタキシャル成長法によって柱状埋込層918を形成する際に形成されてしまうキャップ部919をCMP法により除去する工程が必要となるが、先願に係る半導体装置900においては、活性領域R1と周辺領域R3とで表面構造が大きく異なるため、CMP工程を実施中に周辺耐圧領域R3の近傍で第1絶縁膜932が削られ過ぎてしまうことに起因して素子周辺部での耐圧が低下してしまう場合があるのである。なお、このような問題はスーパージャンクション構造を有する半導体装置だけに存在する問題ではなく、活性領域に柱状埋込層を有する半導体装置全般に存在する問題である。

【0014】

そこで、本発明は、このような問題を解決するためになされたものであり、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供することを目的とする。また、そのような半導体装置を製造可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

[1]本発明の半導体装置は、第1導電型の半導体層と、前記半導体層における活性領域に形成した第1トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる複数の柱状埋込層と、前記活性領域を囲む周辺耐圧領域に形成したリング状の第2トレンチ、当該第2トレンチの内面に形成した絶縁膜及び前記第2トレンチの内部に前記絶縁膜を介して形成した導電性材料層を有し、逆バイアス時には前記導電性材料層及び前記柱状埋込層に挟まれた部分の前記半導体層を空乏化させる周辺耐圧構造と、前記周辺耐圧領域を囲む周辺領域に形成した第3トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる1又は2以上の第2柱状埋込層とを備えることを特徴とする。

【0016】

[2]本発明の半導体装置においては、前記半導体層、前記複数の柱状埋込層及び前記1又は2以上の第2柱状埋込層は、単結晶シリコンからなることが好ましい。

【0017】

[3]本発明の半導体装置においては、前記複数の柱状埋込層は、各々が第1間隔で平行に形成され、前記複数の柱状埋込層のうち前記周辺耐圧構造に最も近い柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことが好ましい。

【0018】

[4]本発明の半導体装置においては、前記1又は2以上の第2柱状埋込層のうち前記周辺耐圧構造に最も近い第2柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことが好ましい。

【0019】

[5]本発明の半導体装置においては、前記第2柱状埋込層として、各々が前記第1間隔以下の間隔で平行に形成された2以上の第2柱状埋込層を備えることが好ましい。

【0020】

[6]本発明の半導体装置においては、前記柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことが好ましい。

【0021】

[7]本発明の半導体装置においては、前記第2柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことが好ましい。

【0022】

[8]本発明の半導体装置は、ショットキーバリアダイオードであってもよい。

【0023】

[9]本発明の半導体装置は、プレーナーゲート型MOSFETであってもよい。

【0024】

[10]本発明の半導体装置は、トレンチゲート型MOSFETであってもよい。

【0025】

[11]本発明の半導体装置は、プレーナーゲート型IGBTであってもよい。

【0026】

[12]本発明の半導体装置は、トレンチゲート型IGBTであってもよい。

【0027】

[13]本発明の半導体装置は、スーパージャンクション構造を有する半導体装置であってもよい。

【0028】

[14]本発明の半導体装置の製造方法は、本発明の半導体装置を製造するための半導体装置の製造方法であって、前記第1導電型の半導体層を準備する半導体層準備工程と、前記周辺耐圧領域に前記周辺耐圧構造を形成する周辺耐圧構造形成工程と、前記半導体層の表面に形成した所定パターンの第1絶縁膜をマスクとして前記活性領域及び前記周辺領域にそれぞれ前記第1トレンチ及び前記第3トレンチを形成し、前記第1トレンチ及び前記第3トレンチの内部に前記第1絶縁膜の表面の高さ位置を超える高さ位置まで第2導電型の半導体材料をエピタキシャル成長させることにより、前記活性領域に柱状埋込層を形成するとともに前記周辺領域に第2柱状埋込層を形成する埋込層形成工程と、前記柱状埋込層及び第2柱状埋込層を前記第1絶縁膜の表面の高さ位置までCMP法によって研磨して除去するCMP工程とを含むことを特徴とする。

【発明の効果】

【0029】

本発明の半導体装置によれば、周辺耐圧領域に上記した周辺耐圧構造を備えるため、第1導電型の半導体層と第2導電型の柱状埋込層との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造の絶縁膜が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0030】

また、本発明の半導体装置によれば、周辺領域にいわゆるダミーの柱状埋込層(第2柱状埋込層)を配設していることから、活性領域と周辺領域とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域の近傍で第1絶縁膜が削られ過ぎてしまうことがなくなり、その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0031】

さらにまた、本発明の半導体装置によれば、周辺領域ではなく周辺耐圧領域において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の高耐圧半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0032】

このため、本発明の半導体装置は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0033】

本発明の半導体装置の製造方法によれば、本発明の半導体装置を製造することができる。

【図面の簡単な説明】

【0034】

【図1】実施形態1に係る半導体装置100を説明するために示す図である。

【図2】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図3】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図4】実施形態1に係る半導体装置100の製造方法を説明するために示す図である。

【図5】実施形態2に係る半導体装置200を説明するために示す図である。

【図6】実施形態2に係る半導体装置200の製造方法を説明するために示す図である。

【図7】実施形態3に係る半導体装置300を説明するために示す図である。

【図8】実施形態3に係る半導体装置300の製造方法を説明するために示す図である。

【図9】実施形態4に係る半導体装置400を説明するために示す図である。

【図10】実施形態4に係る半導体装置400の製造方法を説明するために示す図である。

【図11】実施形態5に係る半導体装置500を説明するために示す図である。

【図12】実施形態5に係る半導体装置500の製造方法を説明するために示す図である。

【図13】従来の半導体装置800を説明するために示す図である。

【図14】先願に係る半導体装置900を説明するために示す図である。

【図15】先願に係る半導体装置900を製造する製造工程の要部を説明するために示す図である。

【発明を実施するための形態】

【0035】

以下、本発明の半導体装置及び半導体装置の製造方法について、図に示す実施の形態に基づいて説明する。

【0036】

[実施形態1]

1.実施形態1に係る半導体装置100の構成

まず、実施形態1に係る半導体装置100の構成を説明する。

図1は、実施形態1に係る半導体装置100を説明するために示す図である。図1(a)は実施形態1に係る半導体装置100の平面図であり、図1(b)は図1(a)のX−X’断面図であり、図1(c)は図1(a)のY−Y’断面図である。なお、図1(a)においては、理解を容易にするために、柱状埋込層118、導電性材料層126及び第2柱状埋込層130のみを示している。

【0037】

実施形態1に係る半導体装置100は、スーパージャンクション構造を有するショットキーバリアダイオードであり、図1(a)に示すように、活性領域R1と、活性領域R1を囲む周辺耐圧領域R2と、周辺耐圧領域R2を囲む周辺領域R3とに分画されている。

【0038】

実施形態1に係る半導体装置100は、図1(b)に示すように、n−型ドリフト層114と、柱状埋込層118と、周辺耐圧構造120と、第2柱状埋込層130と、周辺絶縁膜132と、ショットキーバリアメタル層146と、カソード電極層150とを備える。

【0039】

n−型ドリフト層114は、n+型半導体基板112の上部にエピタキシャル成長させることにより形成されたものであって、n+型半導体基板112とn−型ドリフト層114とで半導体基体110を構成する。n−型ドリフト層114の厚さは、例えば10μmであり、n−型ドリフト層の不純物濃度は、例えば1.5×1016cm−3である。

【0040】

柱状埋込層118は、n−型ドリフト層114における活性領域R1に形成した第1トレンチ116の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。柱状埋込層118の本数は使用目的や構造に合わせて適宜変更することができる。p型半導体材料の不純物濃度は、例えば4.5×1016cm−3である。

【0041】

柱状埋込層118の底部の深さ位置は全て同じであり、後述する導電性材料層126の底部の深さ位置と等しい。柱状埋込層118の深さは、例えば5.5μmであり、幅は、例えば0.5μmである。柱状埋込層118は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1.5μmである。

【0042】

周辺耐圧構造120は、第2トレンチ122、絶縁膜124及び導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分を空乏化させる。柱状埋込層118のうち周辺耐圧構造120に最も近い柱状埋込層118と周辺耐圧構造120との間隔は、第1間隔d1より狭い第2間隔d2である。第2間隔d2は、例えば1.0μmである。

【0043】

第2トレンチ122は、周辺耐圧領域R2に形成されたリング状の溝で、例えば幅が2.5μmであり、深さが6.5μmである。実施形態1においては第2トレンチの形状を正方形としたが、長方形などの他の四角形、他の多角形、角を丸くした多角形及び円形としてもよい。

【0044】

絶縁膜124は、第2トレンチ122の内面に形成された熱酸化膜であり、厚さは例えば1.0μmである。

導電性材料層126は、第2トレンチ122の内部に絶縁膜124を介して形成され、例えば高濃度の不純物を含有するポリシリコンからなる。

【0045】

第2柱状埋込層130は、周辺領域R3に形成され、p型半導体材料からなる2本の柱状埋込層である。第2柱状埋込層130の本数は使用目的や構造に合わせて適宜変更することができる。p型半導体材料の不純物濃度は、例えば4.5×1016cm−3である。

【0046】

第2柱状埋込層130は、各々が第1間隔d1以下の第4間隔d4で平行に形成される。第2間隔d4は、例えば、1.0μmとすることができる。実施形態1においては、第2柱状埋込層130は、各々が第4間隔d4で等しい間隔で形成するが、第1間隔d1以下であればそれぞれ異なる間隔としてもよく、例えば、周辺耐圧構造120から離れるにつれて短くなっていくように形成してもよい。

【0047】

また、第2柱状埋込層130のうち周辺耐圧構造120に最も近い第2柱状埋込層と周辺耐圧構造120との間隔は、第1間隔d1より狭い第3間隔d3である。また、第2柱状埋込層130の底部の深さ位置は全て同じ深さで、導電性材料層126の底部の深さ位置と等しくなるように形成されている。第3間隔d3は、例えば1.0μmである。また、第2柱状埋込層130の底部の深さは、例えば5.5μmである。

【0048】

周辺絶縁膜132は、酸化膜からなる。ショットキーバリアメタル層146は、n−型ドリフト層114とはショットキー接合を形成し、柱状埋込層118及び導電性材料層126とはオーミック接合を形成する。ショットキーバリアメタル層146の材料は例えば白金であり、ショットキーバリアメタル層146の厚さは例えば200nmである。カソード電極層150は、電極材料である金属(例えば、ニッケル)を半導体基体110の裏面に蒸着して形成する。カソード電極層150の厚さは、例えば200nmである。

【0049】

実施形態1に係る半導体装置100は、図1(a)におけるY−Y’に沿った方向においても、図1(c)に示すように、周辺耐圧構造120の内側に柱状埋込層118が形成され、かつ、周辺耐圧構造120の外側に第2柱状埋込層130が形成されている。

【0050】

2.実施形態1に係る半導体装置100の製造方法

次に、実施形態1に係る半導体装置100の製造方法を以下に示す各工程に沿って説明する。

図2〜図4は、実施形態1に係る半導体装置の製造方法を説明するために示す図である。図2(a)〜図2(d)、図3(a)〜図3(d)及び図4(a)〜図4(d)は各工程図である。

【0051】

1.半導体層準備工程

まず、n+型半導体基板112と、n+型半導体基板112の表面側にエピタキシャル成長方により形成したn−型ドリフト層114とを有する半導体基体110を準備する(図2(a)参照。)。n+型半導体基板112としては、例えばシリコン基板を用いることができるが、炭化珪素SiCや窒化ガリウムGaNからなる基板を用いてもよい。

【0052】

2.周辺耐圧構造形成工程

次に、周辺耐圧構造120を形成する。周辺耐圧構造形成工程は、第2トレンチ形成工程と、絶縁膜形成工程と、導電性材料層形成工程とからなる。

【0053】

2−1.第2トレンチ形成工程

周辺耐圧構造形成工程においては、まず、n−型ドリフト層114の表面側からリング状の第2トレンチ122を形成する。具体的には、n−型ドリフト層114の表面に熱酸化法又はCVD法により第1絶縁膜である第1絶縁膜132’を形成した後、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、第2トレンチ形成部に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。次に、レジスト酸化膜を取り除き、その後、第1絶縁膜132’をマスクとしてn−型ドリフト層114をドライエッチングすることにより、n−型ドリフト層114の表面にリング状の第2トレンチ122を形成する(図2(b)参照。)。

【0054】

2−2.絶縁膜形成工程

周辺耐圧構造形成工程においては、ケミカルドライエッチングや犠牲酸化等で第2トレンチ122の底部及び側面のダメージ層を取り除きつつラウンド化を行った後、半導体基体110を熱酸化することにより第2トレンチ122の内部に絶縁膜124を形成する(図2(c)参照。)。なお、ここでは絶縁膜124を熱酸化により形成したが、CVD法にて形成してもよい。

【0055】

2−3.導電性材料層形成工程

周辺耐圧構造形成工程においては、次に、第2トレンチ122の内部に絶縁膜124を介して導電性材料層126を形成する。具体的には、n−型ドリフト層114の表面側から導電性材料126’を堆積させる(図2(d)参照。)。その後、n−型ドリフト層114の表面の高さ位置より上部に位置する導電性材料を除去することにより導電性材料層126を形成する(図3(a)参照)。)。

以上の周辺耐圧構造形成工程により周辺耐圧構造120が形成される。

【0056】

3.埋込層形成工程

次に、活性領域R1に柱状埋込層118を形成するとともに周辺領域R3に第2柱状埋込層130を形成する。埋込層形成工程は、第1トレンチ及び第3トレンチ形成工程と、柱状埋込層及び第2柱状埋込層形成工程とからなる。

【0057】

3−1.第1トレンチ及び第3トレンチ形成工程

第1トレンチ及び第3トレンチ形成工程においては、まず、導電性材料を熱酸化することにより導電性材料層126の上部にトレンチマスクとなる酸化膜を形成する(図3(b)参照。)。当該酸化膜は第1絶縁膜132’の一部を構成する。続いて、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、柱状埋込層及び第2柱状埋込層の形成位置に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。次に、レジスト膜を取り除き、その後、第1絶縁膜132’をマスクとしてn−型ドリフト層114をドライエッチングすることにより、n−型ドリフト層114の表面に第1トレンチ116及び第2トレンチ128を形成する(図3(c)参照。)。

【0058】

3−2.柱状埋込層及び第2柱状埋込層形成工程

埋込層形成工程においては、第1トレンチ116及び第2トレンチ128の内面について、ケミカルドライエッチングや犠牲酸化、水素アニール等により、第1トレンチ形成工程のドライエッチングによるダメージ層除去を行った後、p型不純物を含むドーパントガスを導入しながら第1絶縁膜132’表面の高さ位置を超える高さ位置までp型の単結晶シリコンをエピタキシャル成長させる。

このことにより活性領域R1に、第1絶縁膜132’表面の高さ位置までの本体部117と第1絶縁膜132’表面の高さ位置を超えた部分であるキャップ部119とからなる柱状埋込層118’を形成するとともに、周辺領域R3に第1絶縁膜132’表面の高さ位置までの本体部129と第1絶縁膜132’表面の高さ位置を超えた部分であるキャップ部131とからなる第2柱状埋込層130’を形成する(図3(d)参照。)。

【0059】

4.CMP工程

次に、埋込層形成工程で形成されたキャップ部119,131を第1絶縁膜132’の表面の高さ位置までCMP法によって研磨して除去する(図4(a)参照。)。

【0060】

5.周辺絶縁膜工程

次に、本体部117,129をドライエッチングによりn−型ドリフト層114の表面の高さ位置まで除去する。このことにより、柱状埋込層118及び第2柱状埋込層130が形成される(図4(b)参照。)。

その後、第1絶縁膜132’間に露出している柱状埋込層118及び第2柱状埋込層130の表面を熱酸化することで第2柱状埋込層130表面に後に周辺絶縁膜132となるための酸化膜を形成する。当該酸化膜は第1絶縁膜132’の一部を構成する。

その後、レジスト膜Mを形成し、写真工程を実施することにより、活性領域R1全体及び周辺耐圧領域R2の所定の部分に開口部を設け、当該開口部における第1絶縁膜132’をドライエッチングにより除去する。このとき、周辺領域R3に残った第1絶縁膜132’が周辺絶縁膜132となる(図4(c)参照。)。その後、レジスト膜Mを取り除く。

【0061】

6.電極形成工程

次に、周辺絶縁膜工程で設けた開口部に、n−型ドリフト層114とはショットキー接合を形成し、柱状埋込層118及び導電性材料層126とはオーミック接合を形成するショットキーバリアメタル層146を形成するとともに、半導体基体110の裏面側に位置するn+型半導体基板112の裏面側にカソード電極層150を形成する(図4(d)参照。)。

【0062】

上記の工程を順次実施することにより、実施形態1に係る半導体装置100を製造することができる。

【0063】

3.実施形態1に係る半導体装置100の効果

実施形態1に係る半導体装置100によれば、周辺耐圧領域R2に上記した周辺耐圧構造120を備えるため、n−型ドリフト層114とp型の柱状埋込層118との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造120の絶縁膜124が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0064】

また、実施形態1に係る半導体装置100によれば、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域120の近傍で第1絶縁膜132が削られ過ぎてしまうことがなくなり(図3(d)及び図4(a)並びに図15(a)及び図15(b)参照。)、その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0065】

さらにまた、本発明の半導体装置100によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0066】

このため、本発明の半導体装置100は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0067】

また、実施形態1に係る半導体装置100によれば、複数の柱状埋込層118は、第1間隔d1で平行に形成されているため、特定の部分に電界が集中することを防ぐことが可能となり、空乏層を広い範囲に広げることができる。このため、活性領域R1において耐圧を高くすることが可能となる。

【0068】

また、実施形態1に係る半導体装置100によれば、複数の柱状埋込層118のうち周辺耐圧構造120に最も近い柱状埋込層118と周辺耐圧構造120との間隔は、第1間隔d1より狭い第2間隔d2であるため、逆バイアス時に活性領域R1と周辺耐圧構造R2とで挟まれた領域を確実に空乏化することが可能となる。

【0069】

また、実施形態1に係る半導体装置100によれば、周辺耐圧構造120に最も近い第2柱状埋込層130と周辺耐圧構造120との間隔は、第1間隔d1より狭い第3間隔d3であるため、逆バイアス時に周辺耐圧領域R2と周辺領域R3とで挟まれた領域まで確実に空乏化することが可能となる。

【0070】

また、実施形態1に係る半導体装置100によれば、第2柱状埋込層130として、各々が第1間隔d1以下の間隔d4で平行に形成された2以上の第2柱状埋込層130を備えるため、逆バイアス時に空乏層を複数の第2柱状埋込層130のうち最外周の第2柱状埋込層130まで広げることが可能となり、素子周辺での耐圧をより一層高くすることが可能となる。

【0071】

また、実施形態1に係る半導体装置100によれば、柱状埋込層118の底部の深さ位置が、導電性材料層126の底部の深さ位置と等しいため、複数の柱状埋込層118から下方に伸びた空乏層の底部を滑らかにすることが可能となり、逆バイアス時に柱状埋込層の底部や周辺耐圧構造の底部に電界が集中することがなくなる。このため、活性領域R1から周辺耐圧領域R2にかけての耐圧を高くすることが可能となる。

【0072】

また、実施形態1に係る半導体装置100によれば、第2柱状埋込層130の底部の深さ位置が、導電性材料層126の底部の深さ位置と等しいため、周辺耐圧構造120及び第2柱状埋込層130から下方に伸びた空乏層の底部を滑らかにすることが可能となり、逆バイアス時に第2柱状埋込層の底部や周辺耐圧構造の底部に電界が集中することがなくなる。このため、周辺耐圧領域R2から周辺領域R3にかけての耐圧を高くすることが可能となる。

【0073】

また、実施形態1に係る半導体装置100は、スーパージャンクション構造を有する高耐圧の半導体装置であるため、半導体基体110における特定の部分に電界が集中することを抑制することが可能となり、空乏層をn−型ドリフト層及び柱状埋込層に広げることができる。そのため、活性領域における耐圧を高くすることが可能となる。

【0074】

また、実施形態1に係る半導体装置100によれば、図1(a)におけるY−Y’に沿った方向においても、図1(a)におけるX−X’に沿った方向の場合と同様に、周辺耐圧構造120の外側に第2柱状埋込層130が形成されているため、柱状埋込層を形成する過程で形成されてしまうキャップ部をCMP法により除去するCMP工程において、周辺領域にもキャップ部が形成されるため、図15(b)に示すように、周辺領域R3において第1絶縁膜132’が削れ過ぎてしまうことがなくなるこのため、CMP工程に起因して素子周辺での耐圧が低下してしまうことがなくなる(図3(d)及び図4(a)参照。)。

【0075】

[実施形態2]

図5は、実施形態2に係る半導体装置200を説明するために示す図である。図5(a)は実施形態2に係る半導体装置200の平面図であり、図5(b)は図5(a)におけるX−X’断面図を示す図であり、図5(c)は図5(a)におけるY−Y’断面図を示す図である。なお、図5(a)においては、図1(a)の場合と同様に、理解を容易にするために、柱状埋込層218、導電性材料層226及び第2柱状埋込層230のみを示す。図5(a)中、符号GPはゲートパッドを示す。

【0076】

図6は、実施形態2に係る半導体装置の製造方法を説明するために示す図である。図6(a)〜図6(d)は工程図である。なお、図6(a)〜図6(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に示す工程については図示を省略する。また、図6(c)〜図6(d)に示す工程は、一般的なプレーナーゲート型MOSFETの製造方法の場合と同様であるため、図6(c)〜図6(d)の間にある工程は図示を省略する。

【0077】

実施形態2に係る半導体装置200は、基本的には実施形態1に係る半導体装置100と同様の構成を有するが、図5(b)に示すように、半導体装置がプレーナーゲート型MOSFETである点が実施形態1に係る半導体装置100の場合と異なる。すなわち、実施形態2に係る半導体装置200は、図5(b)に示すように、ボディ領域234と、ソース領域236と、ゲート絶縁膜240及びゲート電極層242からなるゲート電極構造238と、ソース電極層246と、ドレイン電極層250とを備えるプレーナーゲート型MOSFETである。

【0078】

このように、実施形態2に係る半導体装置200は、半導体装置がプレーナーゲート型MOSFETである点が実施形態1に係る半導体装置100の場合とは異なるが、実施形態1に係る半導体装置100と同様の以下の特徴を有するため、実施形態1に係る半導体装置100が有する効果と同様の効果を有する。

【0079】

すなわち、実施形態2に係る半導体装置200によれば、図5(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造220を備えるため、n−型ドリフト層214とp型の柱状埋込層218との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造220の絶縁膜224が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0080】

また、実施形態2に係る半導体装置200によれば、図5(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層230)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域220の近傍で第1絶縁膜232が削られ過ぎてしまうことがなくなり(図6(b)及び図6(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0081】

さらにまた、実施形態2に係る半導体装置200によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0082】

このため、実施形態2に係る半導体装置200は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0083】

なお、実施形態2に係る半導体装置200は、半導体装置がプレーナーゲート型MOSFETである点以外の点では実施形態1に係る半導体装置100の場合と同様の構成を有するため、実施形態1に係る半導体装置100が有する効果のうち同様の効果を有する。

【0084】

[実施形態3]

図7は、実施形態3に係る半導体装置300を説明するために示す図である。図7(a)は実施形態3に係る半導体装置300の平面図であり、図7(b)は図7(a)におけるX−X’断面図を示す図であり、図7(c)は図7(a)におけるY−Y’断面図を示す図である。なお、図7(a)においては、図5(a)の場合と同様に、理解を容易にするために、柱状埋込層318、導電性材料層326及び第2柱状埋込層330のみを示す。図7(a)中、符号GPはゲートパッドを示す。

【0085】

図8は、実施形態3に係る半導体装置の製造方法を説明するために示す図である。図8(a)〜図8(d)は工程図である。なお、図8(a)〜図8(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図8(c)〜図8(d)に示す工程は、一般的なトレンチゲート型MOSFETの製造方法の場合と同様であるため、図8(c)〜図8(d)の間にある工程は図示を省略する。

【0086】

実施形態3に係る半導体装置300は、基本的には実施形態2に係る半導体装置200と同様の構成を有するが、図7(b)に示すように、半導体装置がトレンチゲート型MOSFETである点で実施形態2に係る半導体装置200の場合と異なる。すなわち、実施形態3に係る半導体装置300は、図7(b)に示すように、ボディ領域334と、ソース領域336と、ゲート絶縁膜340及びゲート電極層342からなるゲート電極構造338と、ソース電極層346と、ドレイン電極層350とを備えるトレンチゲート型MOSFETである。

【0087】

このように、実施形態3に係る半導体装置300は、半導体装置がトレンチゲート型MOSFETである点が実施形態2に係る半導体装置200の場合とは異なるが、実施形態2に係る半導体装置200と同様の以下の特徴を有するため、実施形態2に係る半導体装置200が有する効果と同様の効果を有する。

【0088】

すなわち、実施形態3に係る半導体装置300によれば、図7(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造320を備えるため、n−型ドリフト層314とp型の柱状埋込層318との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造320の絶縁膜324が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0089】

また、実施形態3に係る半導体装置300によれば、図7(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層330)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域320の近傍で第1絶縁膜332が削られ過ぎてしまうことがなくなり(図8(b)及び図8(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0090】

さらにまた、実施形態3に係る半導体装置300によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0091】

このため、実施形態3に係る半導体装置300は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0092】

なお、実施形態3に係る半導体装置300は、半導体装置がトレンチゲート型MOSFETである点以外の点では実施形態2に係る半導体装置200の場合と同様の構成を有するため、実施形態2に係る半導体装置200が有する効果のうち同様の効果を有する。

【0093】

[実施形態4]

図9は、実施形態4に係る半導体装置400を説明するために示す図である。図9(a)は実施形態4に係る半導体装置400の平面図であり、図9(b)は図9(a)におけるX−X’断面図を示す図であり、図9(c)は図9(a)におけるY−Y’断面図を示す図である。なお、図9(a)においては、図5(a)の場合と同様に、理解を容易にするために、柱状埋込層418、導電性材料層426及び第2柱状埋込層430のみを示す。図9(a)中、符号GPはゲートパッドを示す。

【0094】

図10は、実施形態4に係る半導体装置の製造方法を説明するために示す図である。図10(a)〜図10(d)は工程図である。なお、図10(a)〜図10(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図10(c)〜図10(d)に示す工程は、一般的なプレーナーゲート型IGBTの製造方法の場合と同様であるため、図10(c)〜図10(d)の間にある工程は図示を省略する。

【0095】

実施形態4に係る半導体装置400は、基本的には実施形態2に係る半導体装置200と同様の構成を有するが、図9(b)に示すように、半導体装置がプレーナーゲート型IGBTである点で実施形態2に係る半導体装置200の場合と異なる。すなわち、実施形態4に係る半導体装置400は、図9(b)に示すように、ボディ領域434と、エミッタ領域436と、ゲート絶縁膜440及びゲート電極層442からなるゲート電極構造438と、エミッタ電極層446と、コレクタ電極層450とを備え、実施形態2のn+型半導体基板212の代わりにp+型半導体層412を備えるプレーナーゲート型IGBTである。

【0096】

このように、実施形態4に係る半導体装置400は、半導体装置がプレーナーゲート型IGBTである点が実施形態2に係る半導体装置200の場合とは異なるが、実施形態2に係る半導体装置200と同様の以下の特徴を有するため、実施形態2に係る半導体装置200が有する効果と同様の効果を有する。

【0097】

すなわち、実施形態4に係る半導体装置400によれば、図9(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造420を備えるため、n−型ドリフト層414とp型の柱状埋込層418との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造420の絶縁膜424が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0098】

また、実施形態4に係る半導体装置400によれば、図9(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層430)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域420の近傍で第1絶縁膜432が削られ過ぎてしまうことがなくなり(図10(b)及び図10(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0099】

さらにまた、実施形態4に係る半導体装置400によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0100】

このため、実施形態4に係る半導体装置400は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0101】

なお、実施形態4に係る半導体装置400は、半導体装置がプレーナーゲート型IGBTである点以外の点では実施形態2に係る半導体装置200の場合と同様の構成を有するため、実施形態2に係る半導体装置200が有する効果のうち同様の効果を有する。

【0102】

[実施形態5]

図11は、実施形態5に係る半導体装置500を説明するために示す図である。図11(a)は実施形態5に係る半導体装置500の平面図であり、図11(b)は図11(a)におけるX−X’断面図を示す図であり、図11(c)は図11(a)におけるY−Y’断面図を示す図である。なお、図11(a)においては、図9(a)の場合と同様に、理解を容易にするために、柱状埋込層518、導電性材料層526及び第2柱状埋込層530のみを示す。図11(a)中、符号GPはゲートパッドを示す。

【0103】

図12は、実施形態5に係る半導体装置の製造方法を説明するために示す図である。図12(a)〜図12(d)は工程図である。なお、図12(a)〜図12(b)に示す工程は、図2(a)〜図3(d)に示す工程と同様であるため、図2(b)〜図3(c)に対応する工程については図示を省略する。また、図12(c)〜図12(d)に示す工程は、一般的なトレンチゲート型IGBTの製造方法の場合と同様であるため、図12(c)〜図12(d)の間にある工程は図示を省略する。

【0104】

実施形態5に係る半導体装置500は、基本的には実施形態4に係る半導体装置400と同様の構成を有するが、図11(b)に示すように、半導体装置がトレンチゲート型IGBTである点で実施形態4に係る半導体装置400の場合と異なる。すなわち、実施形態5に係る半導体装置500は、図11(b)に示すように、ボディ領域534と、エミッタ領域536と、ゲート絶縁膜540及びゲート電極層542からなるゲート電極構造538と、エミッタ電極層546と、コレクタ電極層550とを備えるトレンチゲート型IGBTである。

【0105】

このように、実施形態5に係る半導体装置500は、半導体装置がトレンチゲート型IGBTである点が実施形態4に係る半導体装置400の場合とは異なるが、実施形態4に係る半導体装置400と同様の以下の特徴を有するため、実施形態4に係る半導体装置400が有する効果と同様の効果を有する。

【0106】

すなわち、実施形態5に係る半導体装置500によれば、図11(b)に示すように、周辺耐圧領域R2に上記した周辺耐圧構造520を備えるため、n−型ドリフト層514とp型の柱状埋込層518との間のpn接合に逆バイアスが印加された場合には、周辺耐圧構造520の絶縁膜524が必要な耐圧の大部分を担うようになるため、先願に係る半導体装置900の場合と同様に、素子周辺部での耐圧を高くすることができる。

【0107】

また、実施形態5に係る半導体装置500によれば、図11(b)に示すように、周辺領域R3にいわゆるダミーの柱状埋込層(第2柱状埋込層530)を配設していることから、活性領域R1と周辺領域R3とで表面構造が大きく異なることがなくなるため、CMP工程を実施中に周辺耐圧領域520の近傍で第1絶縁膜532が削られ過ぎてしまうことがなくなり(図12(b)及び図12(c)参照。)。その結果、CMP工程に起因して素子周辺部での耐圧が低下してしまうことがなくなる。

【0108】

さらにまた、実施形態5に係る半導体装置500によれば、周辺領域R3ではなく周辺耐圧領域R2において耐圧を維持するようにしているため、第2柱状埋込層は2〜5本程度で十分であり、従来の半導体装置800の場合のように第2柱状埋込層を数十本設ける必要がなく、素子周辺部での耐圧を高くしながら周辺領域を小さくすることができる。

【0109】

このため、実施形態5に係る半導体装置500は、素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、上記したCMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置となる。

【0110】

なお、実施形態5に係る半導体装置500は、半導体装置がトレンチゲート型IGBTである点以外の点では実施形態4に係る半導体装置400の場合と同様の構成を有するため、実施形態4に係る半導体装置400が有する効果のうち同様の効果を有する。

【0111】

以上、本発明を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。その趣旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば、次のような変形も可能である。

【0112】

(1)上記各実施形態においては、ショットキーバリアダイオード、MOSFET及びIGBTを例にとって本発明の高耐圧半導体装置を説明したが、本発明はこれに限定されるものではない。周辺耐圧領域に周辺耐圧構造を形成することが可能な半導体装置であれば本発明を適用することが可能である。

【0113】

(2)上記各実施形態においては、第1導電型をn型とし、第2導電型をp型とした場合を例にとって本発明を説明したが、本発明はこれに限定されるものではない。例えば、第1導電型をp型とし、第2導電型をn型とした場合にも本発明を適用可能である。

【0114】

(3)上記各実施形態においては、柱状埋込層の上部にp+型半導体領域をさらに形成した高耐圧半導体装置に本発明の発明を適用してもよい。このような構成とすることにより、柱状埋込層とアノード電極層、ソース電極層又はエミッタ電極層と良好なオーミック接続を取ることが可能となる。

【符号の説明】

【0115】

100,200,300,400,500,800,900…半導体層装置、110,210,310,410,510,810,910…半導体基体、112,212,312…n+型半導体基板、114,214,314,414,514…n−型ドリフト層、116,216,316,416,516…第1トレンチ、117,129,217,229,317,329,417,429,517,529…本体部、118,118’,218,218’,318,318’,418,418’,518,518’,818,918,918’…柱状埋込層、119,131,219,231,319,331,419,431,519,531…キャップ部、120,220,320,420,520,920…周辺耐圧構造、122,222,322,422,522,922…第2トレンチ、124,224,324,424,524,924…絶縁膜、126,226,326,426,526,926…導電性材料層、128,228,328,428,528…第3トレンチ、130,130’,230,230’,330,330’,430,430’,530,530’…第2柱状埋込層、132,232,332,432,532,832,932…周辺絶縁膜、132’,232’,332’,432’,532’,932’…第1酸化膜、146,846,946…ショットキーバリアメタル層、150,850,950…カソード電極層、234,334、434,534…ボディ領域、236,336…ソース領域、238,338,438,538…ゲート電極構造、240,340,440,540…ゲート絶縁膜、242,342,442,542…ゲート電極層、244,344,444,544…層間絶縁膜、246,346…ソース電極層、250,350…ドレイン電極層、316a,516a…第4トレンチ、412,512…p+型半導体層、436,536…エミッタ領域、446,546…エミッタ電極層、450,550…コレクタ電極層、R1…活性領域、R2…周辺耐圧領域、R3…周辺領域

【特許請求の範囲】

【請求項1】

第1導電型の半導体層と、

前記半導体層における活性領域に形成した第1トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる複数の柱状埋込層と、

前記活性領域を囲む周辺耐圧領域に形成したリング状の第2トレンチ、当該第2トレンチの内面に形成した絶縁膜及び前記第2トレンチの内部に前記絶縁膜を介して形成した導電性材料層を有し、逆バイアス時には前記導電性材料層及び前記柱状埋込層に挟まれた部分の前記半導体層を空乏化させる周辺耐圧構造と、

前記周辺耐圧領域を囲む周辺領域に形成した第3トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる1又は2以上の第2柱状埋込層とを備えることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記半導体層、前記複数の柱状埋込層及び前記1又は2以上の第2柱状埋込層は、単結晶シリコンからなることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記複数の柱状埋込層は、各々が第1間隔で平行に形成され、

前記複数の柱状埋込層のうち前記周辺耐圧構造に最も近い柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置において、

前記1又は2以上の第2柱状埋込層のうち前記周辺耐圧構造に最も近い第2柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことを特徴とする半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記第2柱状埋込層として、各々が前記第1間隔以下の間隔で平行に形成された2以上の第2柱状埋込層を備えることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれかに記載の半導体装置において、

前記柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことを特徴とする半導体装置。

【請求項7】

請求項1〜6のいずれかに記載の半導体装置において、

前記第2柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことを特徴とする半導体装置。

【請求項8】

ショットキーバリアダイオードであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

プレーナーゲート型MOSFETであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項10】

トレンチゲート型MOSFETであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項11】

プレーナーゲート型IGBTであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項12】

トレンチゲート型IGBTであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項13】

スーパージャンクション構造を有する半導体装置であることを特徴とする請求項1〜12のいずれかに記載の半導体装置。

【請求項14】

請求項1に記載の半導体装置を製造するための半導体装置の製造方法であって、

第1導電型の半導体層を準備する半導体層準備工程と、

前記周辺耐圧領域に前記周辺耐圧構造を形成する周辺耐圧構造形成工程と、

前記半導体層の表面に形成した所定パターンの第1絶縁膜をマスクとして前記活性領域及び前記周辺領域にそれぞれ前記第1トレンチ及び前記第3トレンチを形成し、前記第1トレンチ及び前記第3トレンチの内部に前記第1絶縁膜の表面の高さ位置を超える高さ位置まで第2導電型半導体材料をエピタキシャル成長させることにより、前記活性領域に柱状埋込層を形成するとともに前記周辺領域に第2柱状埋込層を形成する埋込層形成工程と、

前記柱状埋込層及び第2柱状埋込層を前記第1絶縁膜の表面の高さ位置までCMP法によって研磨して除去するCMP工程とを含むことを特徴とする半導体装置の製造方法。

【請求項1】

第1導電型の半導体層と、

前記半導体層における活性領域に形成した第1トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる複数の柱状埋込層と、

前記活性領域を囲む周辺耐圧領域に形成したリング状の第2トレンチ、当該第2トレンチの内面に形成した絶縁膜及び前記第2トレンチの内部に前記絶縁膜を介して形成した導電性材料層を有し、逆バイアス時には前記導電性材料層及び前記柱状埋込層に挟まれた部分の前記半導体層を空乏化させる周辺耐圧構造と、

前記周辺耐圧領域を囲む周辺領域に形成した第3トレンチの内部にエピタキシャル成長させて形成した第2導電型半導体材料からなる1又は2以上の第2柱状埋込層とを備えることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記半導体層、前記複数の柱状埋込層及び前記1又は2以上の第2柱状埋込層は、単結晶シリコンからなることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記複数の柱状埋込層は、各々が第1間隔で平行に形成され、

前記複数の柱状埋込層のうち前記周辺耐圧構造に最も近い柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置において、

前記1又は2以上の第2柱状埋込層のうち前記周辺耐圧構造に最も近い第2柱状埋込層と前記周辺耐圧構造との間隔は、前記第1間隔より狭いことを特徴とする半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記第2柱状埋込層として、各々が前記第1間隔以下の間隔で平行に形成された2以上の第2柱状埋込層を備えることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれかに記載の半導体装置において、

前記柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことを特徴とする半導体装置。

【請求項7】

請求項1〜6のいずれかに記載の半導体装置において、

前記第2柱状埋込層の底部の深さ位置は、前記導電性材料層の底部の深さ位置と等しいことを特徴とする半導体装置。

【請求項8】

ショットキーバリアダイオードであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

プレーナーゲート型MOSFETであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項10】

トレンチゲート型MOSFETであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項11】

プレーナーゲート型IGBTであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項12】

トレンチゲート型IGBTであることを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項13】

スーパージャンクション構造を有する半導体装置であることを特徴とする請求項1〜12のいずれかに記載の半導体装置。

【請求項14】

請求項1に記載の半導体装置を製造するための半導体装置の製造方法であって、

第1導電型の半導体層を準備する半導体層準備工程と、

前記周辺耐圧領域に前記周辺耐圧構造を形成する周辺耐圧構造形成工程と、

前記半導体層の表面に形成した所定パターンの第1絶縁膜をマスクとして前記活性領域及び前記周辺領域にそれぞれ前記第1トレンチ及び前記第3トレンチを形成し、前記第1トレンチ及び前記第3トレンチの内部に前記第1絶縁膜の表面の高さ位置を超える高さ位置まで第2導電型半導体材料をエピタキシャル成長させることにより、前記活性領域に柱状埋込層を形成するとともに前記周辺領域に第2柱状埋込層を形成する埋込層形成工程と、

前記柱状埋込層及び第2柱状埋込層を前記第1絶縁膜の表面の高さ位置までCMP法によって研磨して除去するCMP工程とを含むことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−204795(P2012−204795A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−70728(P2011−70728)

【出願日】平成23年3月28日(2011.3.28)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月28日(2011.3.28)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]