半導体装置及びその製造方法

【課題】MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供する。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MIM(Metal Insulator Metal)キャパシタを備えた半導体装置とその製造方法に関するものである。

【背景技術】

【0002】

MIMキャパシタは、電極(Metal)/絶縁膜(Insulator)/電極(Metal)の積層構造を有する。

従来のMIMキャパシタを有する半導体装置は、特許文献3の図7に示されるように、半導体基板の一方の面上に内部電極と絶縁膜と外部電極との積層構造を有するMIMキャパシタが形成された構造を有している。

例えば、高周波(RF)デバイスにおいては、高周波短絡回路を形成するために、容量の大きいMIMキャパシタが必要とされている。

しかしながら、上記従来構造では、大容量のMIMキャパシタが基板面積を占有するため、デバイスの縮小化が難しい。デバイスサイズの縮小化を考慮すれば、キャパシタの容量には制限があり、回路構成上どうしても大容量のキャパシタが必要な場合には、集積回路からいったん外部に配線を引き出し、チップコンデンサ等を外付けすることで対応している。

【0003】

特許文献1、2では、半導体基板を貫通するバイアホールの内部にMIMキャパシタを設けた半導体装置が提案されている(特許文献1の第1図、特許文献2の図1等)。かかる構成では、MIMキャパシタの基板占有面積を小さくでき、チップを小型化しつつ大きな容量を得ることができる。

【0004】

特許文献3には、半導体チップの少なくとも側面または裏面にMIMキャパシタを設けた半導体装置が提案されている(請求項1、図1、図2)。かかる構成では、MIMキャパシタの基板占有面積を小さくでき、チップを小型化しつつ大きな容量を得ることができる。

特許文献3に記載の半導体装置の製造方法では、半導体基板の主表面上のスクライブラインとなるべき領域を一定の深さでエッチングし凹部を形成する工程と、半導体基板主表面に形成された電子回路の配線の一部を凹部上まで形成する工程と、半導体基板の主表面を保護し半導体基板をスクライブラインに沿ってダイシングし半導体チップに分割する工程と、半導体チップの側面および裏面に内部電極を形成する工程と、内部電極上に絶縁膜を堆積する工程と、絶縁膜上に外部電極を形成する工程と、半導体チップをリードフレーム上にダイスボンドし電気的に外部と接続する工程とを含んでいる(請求項5、図3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平03-99461号公報

【特許文献2】特開平11-195751号公報

【特許文献3】特開平07-106515号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1、2の構成は、バイアホールを持たない半導体チップには適用できない。また、特許文献1、2の構成では、バイアホール内に形成できるMIMキャパシタの最大容量は、バイアホールの内面積によって決まる。そのため、それ以上の容量が必要な場合(例えば平滑コンデンサではできるだけ大きな容量が必要となる)には基板面上にMIMキャパシタを延設する必要があるため、MIMキャパシタの基板占有面積が増大してしまい、チップの小型化が難しい。

【0007】

特許文献1〜3の半導体装置はいずれも、裏面側が半導体パッケージ等に実装される。これらの半導体装置では、裏面側がグランド電位に固定され、キャパシタへの入力電圧をグランド電位にすることしかできず、デバイスの出力側にしか使用することができない。デバイスの入力側にキャパシタを必要とする場合、チップの巨大化を防ぐためには外付けのチップコンデンサ等が必要となる。

【課題を解決するための手段】

【0008】

本発明の半導体装置は、

半導体チップと、

前記半導体チップの表面に形成された電子回路と、

前記半導体チップの少なくとも1つの側面に形成され、前記半導体チップ側から内部電極と絶縁膜と外部電極との積層構造を有するMIM(Metal Insulator Metal)キャパシタとを備え、

前記半導体チップの前記表面上から前記側面に形成された前記MIMキャパシタ上に平面的に延びて、前記MIMキャパシタの前記内部電極に接触した表面電極を備えたものである。

【0009】

本発明の半導体装置においては、半導体チップの少なくとも1つの側面にMIMキャパシタが形成されている。したがって、本発明の半導体装置においては、バイアホールを必須とせず、MIMキャパシタが半導体チップの表面を占有することなく大きなMIMキャパシタ面積が得られ、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

さらに、本発明の半導体装置は、半導体チップの表面上から半導体チップの側面に形成されたMIMキャパシタ上に平面的に延びて、MIMキャパシタの内部電極に接触した表面電極を備えている。かかる構成では、MIMキャパシタの表面電極又は外部電極に任意の電位を印加することができるので、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い。

【発明の効果】

【0010】

本発明によれば、MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供することができる。

【図面の簡単な説明】

【0011】

【図1A】第1実施形態に係る半導体装置の一態様を示す要部断面図である。

【図1B】第1実施形態に係る半導体装置の他の態様を示す要部断面図である。

【図2A】図1Bの半導体装置の製造工程図である。

【図2B】図1Bの半導体装置の製造工程図である。

【図2C】図1Bの半導体装置の製造工程図である。

【図2D】図1Bの半導体装置の製造工程図である。

【図3A】図1Bの半導体装置の実装例を示す要部断面図である。

【図3B】図1Bの半導体装置の他の実装例を示す要部断面図である。

【図3C】図1Bの半導体装置の他の実装例を示す要部断面図である。

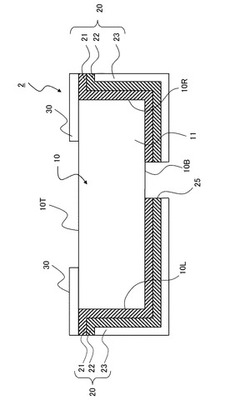

【図4】第2実施形態に係る半導体装置を示す要部断面図である。

【図5A】図4の半導体装置の製造工程図である。

【図5B】図4の半導体装置の製造工程図である。

【図5C】図4の半導体装置の製造工程図である。

【図5D】図4の半導体装置の製造工程図である。

【発明を実施するための形態】

【0012】

「第1実施形態」

図面を参照して、本発明に係る第1実施形態の半導体装置の構成について説明する。図1A及び図1Bは本実施形態に係る半導体装置の態様を示す要部断面図である。図2A〜図2Dは図1Bの半導体装置の製造工程図である。図面上は視認しやすくするため、各部材の縮尺や位置は適宜実際のものとは異ならせて、簡略化してある。

【0013】

図1A及び図1Bに示す半導体装置1A、1Bは、半導体チップ10に少なくとも1つのMIM(Metal Insulator Metal)キャパシタ20が形成されたものである。

半導体チップ10は、半導体基板11の表面10T(図示上面)に半導体素子及び配線等が形成されて、電子回路が形成されたものである。

【0014】

図1Aに示す態様では、半導体チップ10の1つの側面10L(図示左側面)に、MIMキャパシタ20が形成されている。

図1Bに示す態様では、半導体チップ10の2つの側面10L(図示左側面)、10R(図示右側面)に、MIMキャパシタ20が形成されている。

いずれの態様において、MIMキャパシタ20は、半導体チップ10側から内部電極21と絶縁膜(容量膜)22と外部電極23との積層構造を有している。

【0015】

半導体装置1A、1Bには、半導体チップ10の表面10T上から側面に形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30が設けられている。表面電極30の数は、半導体チップ10の側面に形成されたMIMキャパシタ20の数に対応している。

【0016】

図示するように、MIMキャパシタ20の内部電極21は、半導体チップ10の側面10L又は側面10Rと表面電極30の半導体チップ10より張り出した部分の下面に跨って、断面視L字状に屈曲して形成されている。この内部電極21上に、内部電極21の形状に沿って断面視L字状の絶縁膜22が積層され、その上に平坦な外部電極23が積層されている。

内部電極21/絶縁膜22/外部電極23の積層パターンは、内部電極21が表面電極30に接し、外部電極23が表面電極30に接しないものであればよく、適宜設計変更できる。

【0017】

半導体基板11としては特に制限なく、GaAs基板等が挙げられる。

内部電極21及び外部電極23の主成分は導電性金属であれば特に制限なく、TiPtAu、TiAu、及びAl等が挙げられる。内部電極21と外部電極23の主成分は同一でも非同一でもよい。内部電極21及び外部電極23の厚さは特に制限なく、500〜10000Å程度が好ましい。

絶縁膜(容量膜)22としては特に制限なく、SiN膜等が挙げられる。絶縁膜の厚さは特に制限なく、750〜5000Å程度の範囲内で、所望の容量密度が得られる厚さとする。例えば、1000Å厚のSiN膜、100μm×100μmの面積サイズの場合、約7pFの容量が得られる。

【0018】

図2A〜図2Dを参照して、上記の半導体装置1Bの製造方法例について説明する。

【0019】

[工程(1)]

はじめに、複数の半導体チップ10を形成可能な半導体基板11を用意する。

上記の半導体基板11の各チップ形成領域の表面10Tに、半導体素子及び配線等を含む電子回路を形成する。その後必要に応じて、半導体基板11の裏面側を部分的に除去して、基板11を薄板化することができる。このとき、半導体基板11の表面10Tを支持基板等に保持させてもよい。

【0020】

[工程(2)]

次に図2Aに示すように、半導体基板11の表面10Tに、複数の半導体装置1Bの表面電極30を、互いに隣接する半導体チップ10の表面電極30同士が繋がるようにパターン形成する。

【0021】

[工程(3)]

次に図2Bに示すように、表面電極30を残したまま半導体基板11を裏面側からエッチングし、半導体基板11を複数の半導体チップ10に分割する(エッチカット)。

【0022】

[工程(4)〜工程(5)]

次に図2B〜図2Dに示すように、複数の半導体チップ10の側面10L、10RにMIMキャパシタ20を形成し(工程(4))、互いに隣接する半導体チップ10の表面電極30を分離する(工程(5))。

【0023】

図示する例では、工程(4)〜工程(5)を以下のように実施している。

複数の半導体チップ10に分割した半導体基板11に対して、裏面10B側から内部電極21の材料をスパッタするなどして、各半導体チップ10の裏面10B、各半導体チップ10の側面10L、10R、及び表面電極30の裏面10B側の露出面に内部電極21を成膜し、さらにその上に絶縁膜22を同様のパターンで成膜する。

次に、半導体基板11の裏面10B側に所定パターンのフォトレジスト膜を形成し、これをマスクとして外部電極23の材料をスパッタするなどして、外部電極23をパターン成膜する。このとき、各半導体チップ10の側面10L、10R上にのみ外部電極23をパターン成膜する。

その後、半導体基板11の裏面10B上の内部電極21と絶縁膜22、及び互いに隣接する半導体チップ10間の表面電極30と内部電極21と絶縁膜22の積層部分をエッチング除去する。

工程(4)〜工程(5)における各層の成膜とパターニングは適宜変更可能である。

以上のようにして、半導体装置1Bが製造される。

【0024】

上記の半導体装置1Bは、図3A〜図3Cに例を示すように、セラミック製等の半導体パッケージに実装することができる。図3A〜図3Cにおいて、同じ構成要素については同じ参照符号を付してある。

【0025】

図3A〜図3Cに示す例ではいずれも、半導体装置1Bが半導体パッケージ50の内底面に絶縁性半田51を介して実装されている(図3Cでは、絶縁性半田51の図示を省略)。半導体装置1Bの側面10L、10Rに形成された2個のMIMキャパシタ20に対して、それぞれリード線61、62が接続されている。リード線61、62としては、銅線に金メッキを施したものなどが使用できる。

いずれの例においても、リード線61、62は表面電極30又はMIMキャパシタ20の外部電極23に導通されている。

【0026】

図3Aに示す例では半導体パッケージ50内に図示右側方からリード線61が挿入され、その先端が半導体チップ10の図示右側面10Rに形成されたMIMキャパシタ20の外部電極23に圧着されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、半導体チップ10の図示左側面10Lに形成されたMIMキャパシタ20の内部電極21に接触する表面電極30とリード線62とがワイヤボンディングにより接続されている。

【0027】

図3Bに示す例では、半導体パッケージ50の図示右内壁面に内部電極52が形成されており、半導体パッケージ50に図示右側方から挿入されたリード線61の先端が内部電極52に圧着されている。そして、半導体装置1Bの図示右側面10Rに形成されたMIMキャパシタ20の外部電極23が内部電極52に当接されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、その先端が半導体チップ10の図示左側面10L(図示左側面)に形成されたMIMキャパシタ20の外部電極23に圧着されている。

【0028】

図3Cに示す例では、半導体パッケージ50内に図示右側方からリード線61が挿入され、その先端が半導体チップ10の図示右側面10Rに形成されたMIMキャパシタ20の外部電極23に圧着されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、その先端が半導体チップ10の図示左側面10L(図示左側面)に形成されたMIMキャパシタ20の外部電極23に圧着されている。

【0029】

リード線61、62と表面電極30又はMIMキャパシタ20の外部電極23との導電接続構造は適宜設計変更可能である。

【0030】

本実施形態の半導体装置1A、1Bにおいては、MIMキャパシタ20が半導体チップ10の側面10L、若しくは10L及び10Rに形成されている。

本実施形態では、MIMキャパシタ20が半導体チップ10の1つ又は2つの側面に形成されているが、3つ以上の側面にMIMキャパシタ20を設けてもよい。

本実施形態の半導体装置1A、1Bにおいては、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

【0031】

「背景技術の項」で挙げた特許文献1、2のように、バイアホール内にMIMキャパシタを形成する場合、例えば、基板厚さが100μmのとき、半径50μmφのストレートなバイアホールの内面積は15700μm2であり、このバイアホールが半導体チップに6個ある場合、105975μm2が最大MIMキャパシタ面積となる。

これに対して、半導体チップの側面にMIMキャパシタを形成する場合、例えば、チップサイズが1000μm×1000μm、基板厚さ100μmの条件で、MIMキャパシタの面積を最大400000μm2にすることができる。

本実施形態の構成では、このような大きな容量を実現しつつも、MIMキャパシタ20が半導体チップ10の表面を占有することなく、バイアホールを用いた構成よりもMIMキャパシタ20の基板占有面積を低減できる。

本実施形態の半導体装置1A、1Bは、バイアホールのない半導体チップにも適用可能であり、適用範囲が広い。

【0032】

さらに本実施形態の半導体装置1A、1Bは、半導体チップ10の表面10T上から半導体チップ10の側面に形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。かかる構成では、図3A〜図3Cに例示したように、MIMキャパシタ20の内部電極21と導通された表面電極30又は外部電極23にリード線61、62等を介して任意の電位を印加することができるので、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い。したがって、本実施形態では、「背景技術の項」で挙げた特許文献1〜3のように裏面側がグランド電位に固定されることなく、デバイスの入力側と出力側のいずれにも使用できる。

本実施形態の半導体装置1A、1Bでは、外付けのチップコンデンサ等が不要であり、デバイスの小型化を図ることができる。

【0033】

以上のように、本実施形態によれば、MIMキャパシタ20を備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い半導体装置1A、1Bを提供することができる。

【0034】

「第2実施形態」

図面を参照して、本発明に係る第2実施形態の半導体装置の構成について説明する。図4は本実施形態に係る半導体装置の要部断面図である。図5A〜図5Dは図4の半導体装置の製造工程図である。第1実施形態と同じ構成要素については同じ参照符号を付して、説明を省略する。

【0035】

第1実施形態では、半導体チップ10の少なくとも1つの側面にMIMキャパシタが形成された態様について説明したが、MIMキャパシタは半導体チップ10の少なくとも1つの側面と裏面に形成されてもよい。

【0036】

図4に示す半導体装置2では、半導体チップ10の1つの側面10L(図示左側面)から裏面10Bに跨って形成されたMIMキャパシタ20と、半導体チップ10の他方の側面10R(図示右側面)から裏面10Bに跨って形成されたMIMキャパシタ20(計2つのMIMキャパシタ20)が形成されている。2つのMIMキャパシタ20間には、開口部25が形成されている。

MIMキャパシタ20の積層構造は、第1実施形態と同様である。

【0037】

本実施形態においても、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した2つの表面電極30が設けられている。表面電極30の数は、半導体チップ10の側面に形成されたMIMキャパシタ20の数に対応している。

半導体チップ10の側面10L、10Rに形成されたMIMキャパシタ20と表面電極30との接続構造は第1実施形態と同様である。

【0038】

図5A〜図5Dを参照して、上記の半導体装置2の製造方法例について説明する。

【0039】

[工程(1)]

はじめに、複数の半導体チップ10を形成可能な半導体基板11を用意する。

上記の半導体基板11の各チップ形成領域の表面10Tに、半導体素子及び配線等を含む電子回路を形成する。その後必要に応じて、半導体基板11の裏面側を部分的に除去して、基板11を薄板化することができる。このとき、半導体基板11の表面を支持基板等に保持させてもよい。

【0040】

[工程(2)]

次に図5Aに示すように、半導体基板11の表面10Tに、複数の半導体装置2の表面電極30を、互いに隣接する半導体チップ10の表面電極30同士が繋がるように形成する。

【0041】

[工程(3)]

次に図5Bに示すように、表面電極30を残したまま半導体基板11を裏面側からエッチングし、半導体基板11を複数の半導体チップ10に分割する(エッチカット)。

【0042】

[工程(4)〜工程(5)]

次に図5B〜図5Dに示すように、複数の半導体チップ10にそれぞれMIMキャパシタ20を形成し(工程(4))、互いに隣接する半導体チップ10の表面電極30を分離する(工程(5))。

【0043】

図示する例では、工程(4)〜工程(5)を以下のように実施している。

複数の半導体チップ10に分割した半導体基板11に対して、裏面10B側から内部電極21の材料をスパッタするなどして、各半導体チップ10の裏面10B、各半導体チップ10の側面10L、10R、及び表面電極30の裏面10B側の露出面に内部電極21を成膜し、さらにその上に絶縁膜22を同様のパターンで成膜する。

次に、半導体基板11の裏面10B側に所定パターンのフォトレジスト膜を形成し、これをマスクとして外部電極23の材料をスパッタするなどして、外部電極23をパターン成膜する。このとき、各半導体チップ10の側面10L、10R及び裏面10B上に、開口部25を有する外部電極23をパターン成膜する。

その後、半導体基板11の裏面10B上の開口部25領域の内部電極21と絶縁膜22の積層部分、及び互いに隣接する半導体チップ10間の表面電極30と内部電極21と絶縁膜22の積層部分をエッチング除去する。

工程(4)〜工程(5)における各層の成膜とパターニングは適宜変更可能である。

以上のようにして、半導体装置2が製造される。

【0044】

本実施形態の半導体装置2においては、MIMキャパシタ20が半導体チップ10の少なくとも1つの側面と裏面に形成されている。したがって、本実施形態においても、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

【0045】

第1実施形態で説明したように、「背景技術の項」で挙げた特許文献1、2のように、バイアホール内にMIMキャパシタを形成する場合、例えば、基板厚さ100μmのとき、半径50μmφのストレートなバイアホールの内面積は15700μm2であり、このバイアホールが半導体チップに6個ある場合、105975μm2が最大MIMキャパシタ面積となる。

例えば、チップサイズが1000μm×1000μm、基板厚さ100μmの条件で、半導体チップの側面及び裏面の全体にMIMキャパシタを形成する場合、MIMキャパシタの面積を最大1400000μm2にすることができる。この面積はバイアホールを用いた上記従来構成に比して約12倍の面積に相当する。本実施形態の構成では、このような巨大容量を実現しつつも、MIMキャパシタ20が半導体チップ10の表面を占有することなく、バイアホールを用いた構成よりもMIMキャパシタ20の基板占有面積を低減できる。

【0046】

本実施形態の半導体装置2においても、半導体チップ10の表面10T上から半導体チップ10の側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。かかる構成では、第1実施形態と同様に、MIMキャパシタ20の内部電極21と接続された表面電極30又は外部電極23にリード線等を介して任意の電位を印加することができるので、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い。したがって、本実施形態においても、「背景技術の項」で挙げた特許文献1〜3のように裏面側がグランド電位に固定されることなく、デバイスの入力側と出力側のいずれにも使用できる。

本実施形態の半導体装置2においても、外付けのチップコンデンサ等が不要であり、デバイスの小型化を図ることができる。

【0047】

以上説明したように、本実施形態によっても、MIMキャパシタ20を備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い半導体装置2を提供することができる。

【0048】

「設計変更」

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更可能である。

【符号の説明】

【0049】

1A、1B、2 半導体装置

10 半導体チップ

10T 表面

10B 裏面

10L、10R 側面

11 半導体基板

20 MIMキャパシタ

21 内部電極

22 絶縁膜

23 外部電極

30 表面電極

50 半導体パッケージ

61、62 リード線

【技術分野】

【0001】

本発明は、MIM(Metal Insulator Metal)キャパシタを備えた半導体装置とその製造方法に関するものである。

【背景技術】

【0002】

MIMキャパシタは、電極(Metal)/絶縁膜(Insulator)/電極(Metal)の積層構造を有する。

従来のMIMキャパシタを有する半導体装置は、特許文献3の図7に示されるように、半導体基板の一方の面上に内部電極と絶縁膜と外部電極との積層構造を有するMIMキャパシタが形成された構造を有している。

例えば、高周波(RF)デバイスにおいては、高周波短絡回路を形成するために、容量の大きいMIMキャパシタが必要とされている。

しかしながら、上記従来構造では、大容量のMIMキャパシタが基板面積を占有するため、デバイスの縮小化が難しい。デバイスサイズの縮小化を考慮すれば、キャパシタの容量には制限があり、回路構成上どうしても大容量のキャパシタが必要な場合には、集積回路からいったん外部に配線を引き出し、チップコンデンサ等を外付けすることで対応している。

【0003】

特許文献1、2では、半導体基板を貫通するバイアホールの内部にMIMキャパシタを設けた半導体装置が提案されている(特許文献1の第1図、特許文献2の図1等)。かかる構成では、MIMキャパシタの基板占有面積を小さくでき、チップを小型化しつつ大きな容量を得ることができる。

【0004】

特許文献3には、半導体チップの少なくとも側面または裏面にMIMキャパシタを設けた半導体装置が提案されている(請求項1、図1、図2)。かかる構成では、MIMキャパシタの基板占有面積を小さくでき、チップを小型化しつつ大きな容量を得ることができる。

特許文献3に記載の半導体装置の製造方法では、半導体基板の主表面上のスクライブラインとなるべき領域を一定の深さでエッチングし凹部を形成する工程と、半導体基板主表面に形成された電子回路の配線の一部を凹部上まで形成する工程と、半導体基板の主表面を保護し半導体基板をスクライブラインに沿ってダイシングし半導体チップに分割する工程と、半導体チップの側面および裏面に内部電極を形成する工程と、内部電極上に絶縁膜を堆積する工程と、絶縁膜上に外部電極を形成する工程と、半導体チップをリードフレーム上にダイスボンドし電気的に外部と接続する工程とを含んでいる(請求項5、図3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平03-99461号公報

【特許文献2】特開平11-195751号公報

【特許文献3】特開平07-106515号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1、2の構成は、バイアホールを持たない半導体チップには適用できない。また、特許文献1、2の構成では、バイアホール内に形成できるMIMキャパシタの最大容量は、バイアホールの内面積によって決まる。そのため、それ以上の容量が必要な場合(例えば平滑コンデンサではできるだけ大きな容量が必要となる)には基板面上にMIMキャパシタを延設する必要があるため、MIMキャパシタの基板占有面積が増大してしまい、チップの小型化が難しい。

【0007】

特許文献1〜3の半導体装置はいずれも、裏面側が半導体パッケージ等に実装される。これらの半導体装置では、裏面側がグランド電位に固定され、キャパシタへの入力電圧をグランド電位にすることしかできず、デバイスの出力側にしか使用することができない。デバイスの入力側にキャパシタを必要とする場合、チップの巨大化を防ぐためには外付けのチップコンデンサ等が必要となる。

【課題を解決するための手段】

【0008】

本発明の半導体装置は、

半導体チップと、

前記半導体チップの表面に形成された電子回路と、

前記半導体チップの少なくとも1つの側面に形成され、前記半導体チップ側から内部電極と絶縁膜と外部電極との積層構造を有するMIM(Metal Insulator Metal)キャパシタとを備え、

前記半導体チップの前記表面上から前記側面に形成された前記MIMキャパシタ上に平面的に延びて、前記MIMキャパシタの前記内部電極に接触した表面電極を備えたものである。

【0009】

本発明の半導体装置においては、半導体チップの少なくとも1つの側面にMIMキャパシタが形成されている。したがって、本発明の半導体装置においては、バイアホールを必須とせず、MIMキャパシタが半導体チップの表面を占有することなく大きなMIMキャパシタ面積が得られ、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

さらに、本発明の半導体装置は、半導体チップの表面上から半導体チップの側面に形成されたMIMキャパシタ上に平面的に延びて、MIMキャパシタの内部電極に接触した表面電極を備えている。かかる構成では、MIMキャパシタの表面電極又は外部電極に任意の電位を印加することができるので、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い。

【発明の効果】

【0010】

本発明によれば、MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供することができる。

【図面の簡単な説明】

【0011】

【図1A】第1実施形態に係る半導体装置の一態様を示す要部断面図である。

【図1B】第1実施形態に係る半導体装置の他の態様を示す要部断面図である。

【図2A】図1Bの半導体装置の製造工程図である。

【図2B】図1Bの半導体装置の製造工程図である。

【図2C】図1Bの半導体装置の製造工程図である。

【図2D】図1Bの半導体装置の製造工程図である。

【図3A】図1Bの半導体装置の実装例を示す要部断面図である。

【図3B】図1Bの半導体装置の他の実装例を示す要部断面図である。

【図3C】図1Bの半導体装置の他の実装例を示す要部断面図である。

【図4】第2実施形態に係る半導体装置を示す要部断面図である。

【図5A】図4の半導体装置の製造工程図である。

【図5B】図4の半導体装置の製造工程図である。

【図5C】図4の半導体装置の製造工程図である。

【図5D】図4の半導体装置の製造工程図である。

【発明を実施するための形態】

【0012】

「第1実施形態」

図面を参照して、本発明に係る第1実施形態の半導体装置の構成について説明する。図1A及び図1Bは本実施形態に係る半導体装置の態様を示す要部断面図である。図2A〜図2Dは図1Bの半導体装置の製造工程図である。図面上は視認しやすくするため、各部材の縮尺や位置は適宜実際のものとは異ならせて、簡略化してある。

【0013】

図1A及び図1Bに示す半導体装置1A、1Bは、半導体チップ10に少なくとも1つのMIM(Metal Insulator Metal)キャパシタ20が形成されたものである。

半導体チップ10は、半導体基板11の表面10T(図示上面)に半導体素子及び配線等が形成されて、電子回路が形成されたものである。

【0014】

図1Aに示す態様では、半導体チップ10の1つの側面10L(図示左側面)に、MIMキャパシタ20が形成されている。

図1Bに示す態様では、半導体チップ10の2つの側面10L(図示左側面)、10R(図示右側面)に、MIMキャパシタ20が形成されている。

いずれの態様において、MIMキャパシタ20は、半導体チップ10側から内部電極21と絶縁膜(容量膜)22と外部電極23との積層構造を有している。

【0015】

半導体装置1A、1Bには、半導体チップ10の表面10T上から側面に形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30が設けられている。表面電極30の数は、半導体チップ10の側面に形成されたMIMキャパシタ20の数に対応している。

【0016】

図示するように、MIMキャパシタ20の内部電極21は、半導体チップ10の側面10L又は側面10Rと表面電極30の半導体チップ10より張り出した部分の下面に跨って、断面視L字状に屈曲して形成されている。この内部電極21上に、内部電極21の形状に沿って断面視L字状の絶縁膜22が積層され、その上に平坦な外部電極23が積層されている。

内部電極21/絶縁膜22/外部電極23の積層パターンは、内部電極21が表面電極30に接し、外部電極23が表面電極30に接しないものであればよく、適宜設計変更できる。

【0017】

半導体基板11としては特に制限なく、GaAs基板等が挙げられる。

内部電極21及び外部電極23の主成分は導電性金属であれば特に制限なく、TiPtAu、TiAu、及びAl等が挙げられる。内部電極21と外部電極23の主成分は同一でも非同一でもよい。内部電極21及び外部電極23の厚さは特に制限なく、500〜10000Å程度が好ましい。

絶縁膜(容量膜)22としては特に制限なく、SiN膜等が挙げられる。絶縁膜の厚さは特に制限なく、750〜5000Å程度の範囲内で、所望の容量密度が得られる厚さとする。例えば、1000Å厚のSiN膜、100μm×100μmの面積サイズの場合、約7pFの容量が得られる。

【0018】

図2A〜図2Dを参照して、上記の半導体装置1Bの製造方法例について説明する。

【0019】

[工程(1)]

はじめに、複数の半導体チップ10を形成可能な半導体基板11を用意する。

上記の半導体基板11の各チップ形成領域の表面10Tに、半導体素子及び配線等を含む電子回路を形成する。その後必要に応じて、半導体基板11の裏面側を部分的に除去して、基板11を薄板化することができる。このとき、半導体基板11の表面10Tを支持基板等に保持させてもよい。

【0020】

[工程(2)]

次に図2Aに示すように、半導体基板11の表面10Tに、複数の半導体装置1Bの表面電極30を、互いに隣接する半導体チップ10の表面電極30同士が繋がるようにパターン形成する。

【0021】

[工程(3)]

次に図2Bに示すように、表面電極30を残したまま半導体基板11を裏面側からエッチングし、半導体基板11を複数の半導体チップ10に分割する(エッチカット)。

【0022】

[工程(4)〜工程(5)]

次に図2B〜図2Dに示すように、複数の半導体チップ10の側面10L、10RにMIMキャパシタ20を形成し(工程(4))、互いに隣接する半導体チップ10の表面電極30を分離する(工程(5))。

【0023】

図示する例では、工程(4)〜工程(5)を以下のように実施している。

複数の半導体チップ10に分割した半導体基板11に対して、裏面10B側から内部電極21の材料をスパッタするなどして、各半導体チップ10の裏面10B、各半導体チップ10の側面10L、10R、及び表面電極30の裏面10B側の露出面に内部電極21を成膜し、さらにその上に絶縁膜22を同様のパターンで成膜する。

次に、半導体基板11の裏面10B側に所定パターンのフォトレジスト膜を形成し、これをマスクとして外部電極23の材料をスパッタするなどして、外部電極23をパターン成膜する。このとき、各半導体チップ10の側面10L、10R上にのみ外部電極23をパターン成膜する。

その後、半導体基板11の裏面10B上の内部電極21と絶縁膜22、及び互いに隣接する半導体チップ10間の表面電極30と内部電極21と絶縁膜22の積層部分をエッチング除去する。

工程(4)〜工程(5)における各層の成膜とパターニングは適宜変更可能である。

以上のようにして、半導体装置1Bが製造される。

【0024】

上記の半導体装置1Bは、図3A〜図3Cに例を示すように、セラミック製等の半導体パッケージに実装することができる。図3A〜図3Cにおいて、同じ構成要素については同じ参照符号を付してある。

【0025】

図3A〜図3Cに示す例ではいずれも、半導体装置1Bが半導体パッケージ50の内底面に絶縁性半田51を介して実装されている(図3Cでは、絶縁性半田51の図示を省略)。半導体装置1Bの側面10L、10Rに形成された2個のMIMキャパシタ20に対して、それぞれリード線61、62が接続されている。リード線61、62としては、銅線に金メッキを施したものなどが使用できる。

いずれの例においても、リード線61、62は表面電極30又はMIMキャパシタ20の外部電極23に導通されている。

【0026】

図3Aに示す例では半導体パッケージ50内に図示右側方からリード線61が挿入され、その先端が半導体チップ10の図示右側面10Rに形成されたMIMキャパシタ20の外部電極23に圧着されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、半導体チップ10の図示左側面10Lに形成されたMIMキャパシタ20の内部電極21に接触する表面電極30とリード線62とがワイヤボンディングにより接続されている。

【0027】

図3Bに示す例では、半導体パッケージ50の図示右内壁面に内部電極52が形成されており、半導体パッケージ50に図示右側方から挿入されたリード線61の先端が内部電極52に圧着されている。そして、半導体装置1Bの図示右側面10Rに形成されたMIMキャパシタ20の外部電極23が内部電極52に当接されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、その先端が半導体チップ10の図示左側面10L(図示左側面)に形成されたMIMキャパシタ20の外部電極23に圧着されている。

【0028】

図3Cに示す例では、半導体パッケージ50内に図示右側方からリード線61が挿入され、その先端が半導体チップ10の図示右側面10Rに形成されたMIMキャパシタ20の外部電極23に圧着されている。

半導体パッケージ50内に図示左側方からリード線62が挿入され、その先端が半導体チップ10の図示左側面10L(図示左側面)に形成されたMIMキャパシタ20の外部電極23に圧着されている。

【0029】

リード線61、62と表面電極30又はMIMキャパシタ20の外部電極23との導電接続構造は適宜設計変更可能である。

【0030】

本実施形態の半導体装置1A、1Bにおいては、MIMキャパシタ20が半導体チップ10の側面10L、若しくは10L及び10Rに形成されている。

本実施形態では、MIMキャパシタ20が半導体チップ10の1つ又は2つの側面に形成されているが、3つ以上の側面にMIMキャパシタ20を設けてもよい。

本実施形態の半導体装置1A、1Bにおいては、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

【0031】

「背景技術の項」で挙げた特許文献1、2のように、バイアホール内にMIMキャパシタを形成する場合、例えば、基板厚さが100μmのとき、半径50μmφのストレートなバイアホールの内面積は15700μm2であり、このバイアホールが半導体チップに6個ある場合、105975μm2が最大MIMキャパシタ面積となる。

これに対して、半導体チップの側面にMIMキャパシタを形成する場合、例えば、チップサイズが1000μm×1000μm、基板厚さ100μmの条件で、MIMキャパシタの面積を最大400000μm2にすることができる。

本実施形態の構成では、このような大きな容量を実現しつつも、MIMキャパシタ20が半導体チップ10の表面を占有することなく、バイアホールを用いた構成よりもMIMキャパシタ20の基板占有面積を低減できる。

本実施形態の半導体装置1A、1Bは、バイアホールのない半導体チップにも適用可能であり、適用範囲が広い。

【0032】

さらに本実施形態の半導体装置1A、1Bは、半導体チップ10の表面10T上から半導体チップ10の側面に形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。かかる構成では、図3A〜図3Cに例示したように、MIMキャパシタ20の内部電極21と導通された表面電極30又は外部電極23にリード線61、62等を介して任意の電位を印加することができるので、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い。したがって、本実施形態では、「背景技術の項」で挙げた特許文献1〜3のように裏面側がグランド電位に固定されることなく、デバイスの入力側と出力側のいずれにも使用できる。

本実施形態の半導体装置1A、1Bでは、外付けのチップコンデンサ等が不要であり、デバイスの小型化を図ることができる。

【0033】

以上のように、本実施形態によれば、MIMキャパシタ20を備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い半導体装置1A、1Bを提供することができる。

【0034】

「第2実施形態」

図面を参照して、本発明に係る第2実施形態の半導体装置の構成について説明する。図4は本実施形態に係る半導体装置の要部断面図である。図5A〜図5Dは図4の半導体装置の製造工程図である。第1実施形態と同じ構成要素については同じ参照符号を付して、説明を省略する。

【0035】

第1実施形態では、半導体チップ10の少なくとも1つの側面にMIMキャパシタが形成された態様について説明したが、MIMキャパシタは半導体チップ10の少なくとも1つの側面と裏面に形成されてもよい。

【0036】

図4に示す半導体装置2では、半導体チップ10の1つの側面10L(図示左側面)から裏面10Bに跨って形成されたMIMキャパシタ20と、半導体チップ10の他方の側面10R(図示右側面)から裏面10Bに跨って形成されたMIMキャパシタ20(計2つのMIMキャパシタ20)が形成されている。2つのMIMキャパシタ20間には、開口部25が形成されている。

MIMキャパシタ20の積層構造は、第1実施形態と同様である。

【0037】

本実施形態においても、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した2つの表面電極30が設けられている。表面電極30の数は、半導体チップ10の側面に形成されたMIMキャパシタ20の数に対応している。

半導体チップ10の側面10L、10Rに形成されたMIMキャパシタ20と表面電極30との接続構造は第1実施形態と同様である。

【0038】

図5A〜図5Dを参照して、上記の半導体装置2の製造方法例について説明する。

【0039】

[工程(1)]

はじめに、複数の半導体チップ10を形成可能な半導体基板11を用意する。

上記の半導体基板11の各チップ形成領域の表面10Tに、半導体素子及び配線等を含む電子回路を形成する。その後必要に応じて、半導体基板11の裏面側を部分的に除去して、基板11を薄板化することができる。このとき、半導体基板11の表面を支持基板等に保持させてもよい。

【0040】

[工程(2)]

次に図5Aに示すように、半導体基板11の表面10Tに、複数の半導体装置2の表面電極30を、互いに隣接する半導体チップ10の表面電極30同士が繋がるように形成する。

【0041】

[工程(3)]

次に図5Bに示すように、表面電極30を残したまま半導体基板11を裏面側からエッチングし、半導体基板11を複数の半導体チップ10に分割する(エッチカット)。

【0042】

[工程(4)〜工程(5)]

次に図5B〜図5Dに示すように、複数の半導体チップ10にそれぞれMIMキャパシタ20を形成し(工程(4))、互いに隣接する半導体チップ10の表面電極30を分離する(工程(5))。

【0043】

図示する例では、工程(4)〜工程(5)を以下のように実施している。

複数の半導体チップ10に分割した半導体基板11に対して、裏面10B側から内部電極21の材料をスパッタするなどして、各半導体チップ10の裏面10B、各半導体チップ10の側面10L、10R、及び表面電極30の裏面10B側の露出面に内部電極21を成膜し、さらにその上に絶縁膜22を同様のパターンで成膜する。

次に、半導体基板11の裏面10B側に所定パターンのフォトレジスト膜を形成し、これをマスクとして外部電極23の材料をスパッタするなどして、外部電極23をパターン成膜する。このとき、各半導体チップ10の側面10L、10R及び裏面10B上に、開口部25を有する外部電極23をパターン成膜する。

その後、半導体基板11の裏面10B上の開口部25領域の内部電極21と絶縁膜22の積層部分、及び互いに隣接する半導体チップ10間の表面電極30と内部電極21と絶縁膜22の積層部分をエッチング除去する。

工程(4)〜工程(5)における各層の成膜とパターニングは適宜変更可能である。

以上のようにして、半導体装置2が製造される。

【0044】

本実施形態の半導体装置2においては、MIMキャパシタ20が半導体チップ10の少なくとも1つの側面と裏面に形成されている。したがって、本実施形態においても、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができる。

【0045】

第1実施形態で説明したように、「背景技術の項」で挙げた特許文献1、2のように、バイアホール内にMIMキャパシタを形成する場合、例えば、基板厚さ100μmのとき、半径50μmφのストレートなバイアホールの内面積は15700μm2であり、このバイアホールが半導体チップに6個ある場合、105975μm2が最大MIMキャパシタ面積となる。

例えば、チップサイズが1000μm×1000μm、基板厚さ100μmの条件で、半導体チップの側面及び裏面の全体にMIMキャパシタを形成する場合、MIMキャパシタの面積を最大1400000μm2にすることができる。この面積はバイアホールを用いた上記従来構成に比して約12倍の面積に相当する。本実施形態の構成では、このような巨大容量を実現しつつも、MIMキャパシタ20が半導体チップ10の表面を占有することなく、バイアホールを用いた構成よりもMIMキャパシタ20の基板占有面積を低減できる。

【0046】

本実施形態の半導体装置2においても、半導体チップ10の表面10T上から半導体チップ10の側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。かかる構成では、第1実施形態と同様に、MIMキャパシタ20の内部電極21と接続された表面電極30又は外部電極23にリード線等を介して任意の電位を印加することができるので、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い。したがって、本実施形態においても、「背景技術の項」で挙げた特許文献1〜3のように裏面側がグランド電位に固定されることなく、デバイスの入力側と出力側のいずれにも使用できる。

本実施形態の半導体装置2においても、外付けのチップコンデンサ等が不要であり、デバイスの小型化を図ることができる。

【0047】

以上説明したように、本実施形態によっても、MIMキャパシタ20を備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタ20の内部電極21と外部電極23の電位の設定自由度が高い半導体装置2を提供することができる。

【0048】

「設計変更」

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更可能である。

【符号の説明】

【0049】

1A、1B、2 半導体装置

10 半導体チップ

10T 表面

10B 裏面

10L、10R 側面

11 半導体基板

20 MIMキャパシタ

21 内部電極

22 絶縁膜

23 外部電極

30 表面電極

50 半導体パッケージ

61、62 リード線

【特許請求の範囲】

【請求項1】

半導体チップと、

前記半導体チップの表面に形成された電子回路と、

前記半導体チップの少なくとも1つの側面に形成され、前記半導体チップ側から内部電極と絶縁膜と外部電極との積層構造を有するMIM(Metal Insulator Metal)キャパシタとを備え、

前記半導体チップの前記表面上から前記側面に形成された前記MIMキャパシタ上に平面的に延びて、前記MIMキャパシタの前記内部電極に接触した表面電極を備えた半導体装置。

【請求項2】

前記MIMキャパシタは、前記半導体チップの少なくとも1つの前記側面から前記裏面に跨って形成された請求項1に記載の半導体装置。

【請求項3】

前記MIMキャパシタの前記表面電極又は前記外部電極にリード線が導通された請求項1又は2に記載の半導体装置。

【請求項4】

請求項1〜3のいずれかに記載の半導体装置の製造方法であって、

複数の前記半導体チップを形成可能な半導体基板を用意する工程(1)と、

前記半導体基板の前記表面に、前記複数の半導体装置の前記表面電極を、互いに隣接する前記半導体チップの前記表面電極同士が繋がるように形成する工程(2)と、

前記表面電極を残したまま前記半導体基板を裏面側からエッチングし、前記半導体基板を複数の前記半導体チップに分割する工程(3)と、

前記複数の半導体チップに前記MIMキャパシタを形成する工程(4)と、

互いに隣接する前記半導体チップの前記表面電極を分離する工程(5)とを順次有する半導体装置の製造方法。

【請求項5】

工程(5)は、

前記半導体基板の裏面側から前記内部電極を成膜する工程と、

前記半導体基板の裏面側から前記絶縁膜を成膜する工程と

前記半導体基板の裏面側から前記外部電極を成膜する工程とを含む請求項4に記載の製造方法。

【請求項1】

半導体チップと、

前記半導体チップの表面に形成された電子回路と、

前記半導体チップの少なくとも1つの側面に形成され、前記半導体チップ側から内部電極と絶縁膜と外部電極との積層構造を有するMIM(Metal Insulator Metal)キャパシタとを備え、

前記半導体チップの前記表面上から前記側面に形成された前記MIMキャパシタ上に平面的に延びて、前記MIMキャパシタの前記内部電極に接触した表面電極を備えた半導体装置。

【請求項2】

前記MIMキャパシタは、前記半導体チップの少なくとも1つの前記側面から前記裏面に跨って形成された請求項1に記載の半導体装置。

【請求項3】

前記MIMキャパシタの前記表面電極又は前記外部電極にリード線が導通された請求項1又は2に記載の半導体装置。

【請求項4】

請求項1〜3のいずれかに記載の半導体装置の製造方法であって、

複数の前記半導体チップを形成可能な半導体基板を用意する工程(1)と、

前記半導体基板の前記表面に、前記複数の半導体装置の前記表面電極を、互いに隣接する前記半導体チップの前記表面電極同士が繋がるように形成する工程(2)と、

前記表面電極を残したまま前記半導体基板を裏面側からエッチングし、前記半導体基板を複数の前記半導体チップに分割する工程(3)と、

前記複数の半導体チップに前記MIMキャパシタを形成する工程(4)と、

互いに隣接する前記半導体チップの前記表面電極を分離する工程(5)とを順次有する半導体装置の製造方法。

【請求項5】

工程(5)は、

前記半導体基板の裏面側から前記内部電極を成膜する工程と、

前記半導体基板の裏面側から前記絶縁膜を成膜する工程と

前記半導体基板の裏面側から前記外部電極を成膜する工程とを含む請求項4に記載の製造方法。

【図1A】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図3A】

【図3B】

【図3C】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図3A】

【図3B】

【図3C】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【公開番号】特開2012−221990(P2012−221990A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−82830(P2011−82830)

【出願日】平成23年4月4日(2011.4.4)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月4日(2011.4.4)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]